#### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2019-216021 (P2019-216021A)

(43) 公開日 令和1年12月19日(2019.12.19)

| (51) Int.Cl.<br><b>HO5B</b> 33/10<br><b>HO1L</b> 27/32<br><b>HO1L</b> 51/50 | F I<br>(2006.01) HO5B<br>(2006.01) HO1 L<br>(2006.01) HO5B | 33/10<br>27/32<br>33/14                     | A                                                                                                                       | テーマコー<br>3 K 1 O 7<br>4 K O 2 9<br>5 C O 9 4                          | , ,,,                                                    |

|-----------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------|

| HO5B 33/12                                                                  | (2006.01) HO5B                                             | 33/12                                       | В                                                                                                                       | 5G435                                                                 |                                                          |

| HO5B 33/02                                                                  | <b>(2006.01)</b> HO5B<br>審本課立 #                            | 33/02<br>≐≣≢abri                            | 頁の数 9 O L                                                                                                               | (全 16 頁)                                                              | 鼻紋百に纏え                                                   |

|                                                                             | 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一                      |                                             |                                                                                                                         | (土 10 貝)                                                              | 最終頁に続く<br>                                               |

| (21) 出願番号<br>(22) 出願日                                                       | 特願2018-112642 (P2018-112642)<br>平成30年6月13日 (2018.6.13)     | (71) 出願人<br>(74) 代理人<br>(72) 発明者<br>Fターム (参 | 502356528<br>株式会社ジャノ<br>東京都港区西第<br>110000154<br>特許業務法人は<br>濱田 夕慎<br>東京都港区西第<br>社ジャパンディ<br>考) 3K107 AA01<br>EE21<br>GG54 | 所橋三丁目 7 a<br>はるか国際特割<br>所橋三丁目 7 a<br>アスプレイ内<br>BB01 CC05<br>FF06 GG04 | 新 1 号<br>中事務所<br>番 1 号 株式会<br>6 CC33 CC45<br>6 GG28 GG33 |

|                                                                             |                                                            |                                             | 4K029 AA11<br>DB06                                                                                                      |                                                                       | :                                                        |

|                                                                             |                                                            |                                             | 5CO94 AA43<br>DA15                                                                                                      |                                                                       |                                                          |

|                                                                             |                                                            |                                             | DAIO                                                                                                                    |                                                                       | 最終頁に続く                                                   |

# (54) 【発明の名称】表示装置及びその製造方法

# (57)【要約】

【課題】マスクのアライメント回数を減らすことを目的 とする。

【解決手段】フルカラー画像を表示するための複数の画素PXのそれぞれが複数色(赤R、緑G、青B)の副画素SPXから構成される。複数の画素PXは同一色(赤R、緑G、青B)の副画素群SPXを含む。複数色(赤R、緑G、青B)の副画素SPXのそれぞれがエレクトロルミネセンスによる発光を得るための多層構造を有する。複数色(赤R、緑G、青B)のそれぞれごとに、同一色(赤R、緑G又は青B)の副画素群SPXのそれぞれの多層構造の複数層を、精細マスク58R(又は58G、58B)を使用した連続的複数回の蒸着によって、基板10に形成する。精細マスク58R(又は58G、58B)は、同一色(赤R、緑G又は青B)の副画素群SPXそれぞれに対応する複数の開口60を有する。【選択図】図7

#### 【特許請求の範囲】

#### 【請求項1】

フルカラー画像を表示するための複数の画素のそれぞれが複数色の副画素から構成され 、前記複数の画素は同一色の副画素群を含み、前記複数色の副画素のそれぞれがエレクト

ロルミネセンスによる発光を得るための多層構造を有する表示装置の製造方法であって、 前記複数色のそれぞれごとに、前記同一色の副画素群のそれぞれの前記多層構造の複数 層を、精細マスクを使用した連続的複数回の蒸着によって、基板に形成する工程を含み、

前記精細マスクは、前記同一色の副画素群それぞれに対応する複数の開口を有することを特徴とする表示装置の製造方法。

#### 【請求項2】

請求項1に記載された表示装置の製造方法において、

前記連続的複数回の蒸着の前に、前記精細マスクを前記基板に対して位置合わせする工程をさらに含むことを特徴とする表示装置の製造方法。

#### 【請求項3】

請求項1又は2に記載された表示装置の製造方法において、

前記複数色の副画素のそれぞれの前記多層構造の少なくとも 1 層を、全体マスクを使用 した蒸着によって、一括して形成する工程をさらに含み、

前記全体マスクは、前記複数の画素を全体的に含む大きさの開口を有することを特徴とする表示装置の製造方法。

## 【請求項4】

請求項3に記載された表示装置の製造方法において、

前記全体マスクを使用した蒸着の前に、前記全体マスクを前記基板に対して位置合わせする工程をさらに含むことを特徴とする表示装置の製造方法。

#### 【請求項5】

請求項4に記載された表示装置の製造方法において、

前記多層構造は、前記複数色の副画素のそれぞれごとに分離された画素電極と、前記複数色の副画素のために一体化した共通電極と、前記画素電極と前記共通電極の間に積層された複数のエレクトロルミネセンス層と、を含み、

前記複数のエレクトロルミネセンス層の2層以上を、前記連続的複数回の蒸着によって形成し.

前記共通電極を、前記全体マスクを使用した蒸着によって形成することを特徴とする表示装置の製造方法。

#### 【請求項6】

請求項5に記載された表示装置の製造方法において、

前記複数のエレクトロルミネセンス層の他の少なくとも 1 層を、前記全体マスクを使用 した蒸着によって形成することを特徴とする表示装置の製造方法。

# 【請求項7】

請求項5又は6に記載された表示装置の製造方法において、

前記多層構造は、前記共通電極の上に、段階的に屈折率を変化させて光取出し効率を向上させるための複数の光学調整層をさらに含み、

前記複数の光学調整層の2層以上を、前記連続的複数回の蒸着によって形成することを特徴とする表示装置の製造方法。

## 【請求項8】

請求項7に記載された表示装置の製造方法において、

前記複数の光学調整層の他の少なくとも1層を、前記全体マスクを使用した蒸着によって形成することを特徴とする表示装置の製造方法。

#### 【請求項9】

複数の画素電極と、

前記複数の画素電極のそれぞれごとに分離されて積層された2層以上のエレクトロルミネセンス層と、

10

20

30

40

前記2層以上のエレクトロルミネセンス層の上にある共通電極と、

前記複数の画素電極のそれぞれごとに分離されて前記共通電極の上に積層された2層以上の光学調整層と、

を含み、

前記2層以上のエレクトロルミネセンス層の周縁の相互のずれは、第1範囲内にあり、 前記2層以上の光学調整層の周縁の相互のずれは、第2範囲内にあり、

前記 2 層以上のエレクトロルミネセンス層の前記周縁と前記 2 層以上の光学調整層の前記周縁のずれは、前記第 1 範囲及び前記第 2 範囲のいずれよりも大きいことを特徴とする表示装置。

【発明の詳細な説明】

10

【技術分野】

[00001]

本発明は、表示装置及びその製造方法に関する。

【背景技術】

[0002]

有機エレクトロルミネッセンスを使用した3色(R,G,B)の発光層がサイドバイサイド方式で並ぶディスプレイが知られている(特許文献1~3)。その製造プロセスでは、色ごとに開口位置や大きさの異なるマスクを使用して3色の発光層を蒸着し、これにより色ごとの塗り分けを実現する。また、必要に応じて形成される電子注入層、電子輸送層、正孔注入層及び正孔輸送層の厚みが色ごとに異なることがある。

20

30

40

【先行技術文献】

【特許文献】

[0003]

【 特 許 文 献 1 】 米 国 特 許 出 願 公 開 第 2 0 1 4 / 6 5 7 5 0 号 明 細 書

【 特 許 文 献 2 】 米 国 特 許 出 願 公 開 第 2 0 1 4 / 1 9 1 2 0 2 号 明 細 書

【特許文献3】米国特許出願公開第2012/104430号明細書

【発明の概要】

【発明が解決しようとする課題】

[0004]

塗り分けにおいて、マスクのアライメント精度が重要である。アライメントはマスクが変わる毎にその都度実施する必要があり、塗り分けでは2~3 umのずれでも大きな影響となり得る。加えて、複数回の塗り分けがそれぞれある一定の規格内に入らなければならない。したがって、マスクのアライメント回数は少ないことが好ましい。

[0005]

本発明は、マスクのアライメント回数を減らすことを目的とする。

【課題を解決するための手段】

[0006]

本発明に係る表示装置の製造方法は、フルカラー画像を表示するための複数の画素のそれぞれが複数色の副画素から構成され、前記複数の画素は同一色の副画素群を含み、前記複数色の副画素のそれぞれがエレクトロルミネセンスによる発光を得るための多層構造を有する表示装置の製造方法であって、前記複数色のそれぞれごとに、前記同一色の副画素群のそれぞれの前記多層構造の複数層を、精細マスクを使用した連続的複数回の蒸着によって、基板に形成する工程を含み、前記精細マスクは、前記同一色の副画素群それぞれに対応する複数の開口を有することを特徴とする。

[0007]

本発明によれば、精細マスクを使用した蒸着を連続的で複数回行うので、精細マスクの アライメント回数を減らすことができる。

[0008]

本発明に係る表示装置は、複数の画素電極と、前記複数の画素電極のそれぞれごとに分離されて積層された2層以上のエレクトロルミネセンス層と、前記2層以上のエレクトロ

ルミネセンス層の上にある共通電極と、前記複数の画素電極のそれぞれごとに分離されて前記共通電極の上に積層された2層以上の光学調整層と、を含み、前記2層以上のエレクトロルミネセンス層の周縁の相互のずれは、第1範囲内にあり、前記2層以上のエレクトロルミネセンス層の前記周縁と前記2層以上の光学調整層の前記周縁のずれは、前記第1範囲及び前記第2範囲のいずれよりも大きいことを特徴とする。

【図面の簡単な説明】

- [0009]

- 【図1】本発明の実施形態に係る表示装置の平面図である。

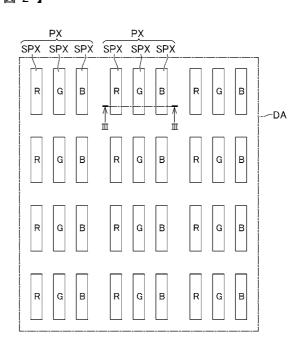

- 【図2】表示領域の一部の拡大図である。

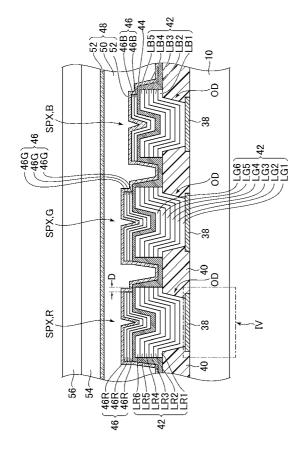

- 【図3】図2に示す表示装置の111-111線断面の概略図である。

- 【図4】図3に示す表示装置のIV部分の拡大図である。

- 【図5】図1に示す表示装置の回路図である。

- 【図 6 】表示装置の製造方法で使用する複数の精細マスクのそれぞれの一部を示す図である。

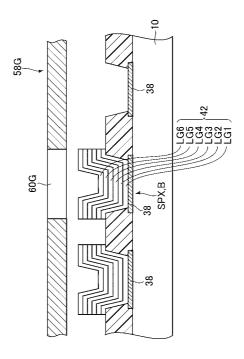

- 【図7】精細マスクを使用したプロセスを示す図である。

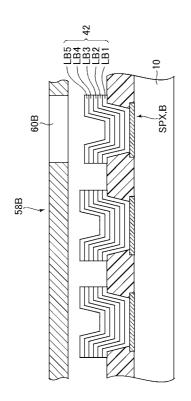

- 【図8】他の精細マスクを使用したプロセスを示す図である。

- 【図9】さらに他の精細マスクを使用したプロセスを示す図である。

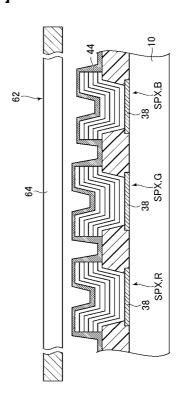

- 【図10】全体マスクを使用したプロセスを示す図である。

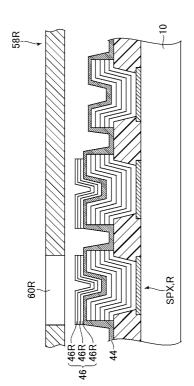

- 【図11】赤の副画素群に複数の光学調整層を形成するプロセスを示す図である。

- 【図12】緑の副画素群に複数の光学調整層を形成するプロセスを示す図である。

- 【図13】青の副画素群に複数の光学調整層を形成するプロセスを示す図である。

- 【図14】連続的複数回の蒸着を行うための製造装置の全体構造を示す図である。

- 【図15】製造装置の変形例を示す図である。

- 【図16】多層構造の変形例1を示す図である。

- 【図17】多層構造の変形例2を示す図である。

- 【図18】多層構造の変形例3を示す図である。

- 【発明を実施するための形態】

- [0010]

以下、本発明の実施形態について図面を参照して説明する。但し、本発明は、その要旨を逸脱しない範囲において様々な態様で実施することができ、以下に例示する実施形態の記載内容に限定して解釈されるものではない。

[0011]

図面は、説明をより明確にするため、実際の態様に比べ、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。本明細書と各図において、既出の図に関して説明したものと同様の機能を備えた要素には、同一の符号を付して、重複する説明を省略することがある。

[0012]

さらに、本発明の詳細な説明において、ある構成物と他の構成物の位置関係を規定する際、「上に」「下に」とは、ある構成物の直上あるいは直下に位置する場合のみでなく、特に断りの無い限りは、間にさらに他の構成物を介在する場合を含むものとする。

[ 0 0 1 3 ]

図1は、本発明の実施形態に係る表示装置の平面図である。表示装置は、実際には、折り曲げて使用するので、図1は、表示装置を折り曲げる前の展開図である。表示装置は、ディスプレイDPを含む。ディスプレイDPは、可撓性を有しており、画像が表示される表示領域DAの外側にある屈曲対応領域BAで折り曲げられるようになっている。ディスプレイDPには、画像を表示するための素子を駆動するための集積回路チップCPが搭載されている。ディスプレイDPには、表示領域DAの外側で、フレキシブルプリント基板FPが接続されている。表示装置は、例えば、有機エレクトロルミネセンス表示装置である。

10

20

30

#### [0014]

図2は、表示領域DAの一部の拡大図である。表示領域DAでは、フルカラー画像が表示される。フルカラー画像を表示するための複数の画素PXのそれぞれは、複数色(例えば赤R、緑G及び青B)の副画素SPXから構成されている。複数の画素PXは、同一色の副画素群SPXを含む。

## [0015]

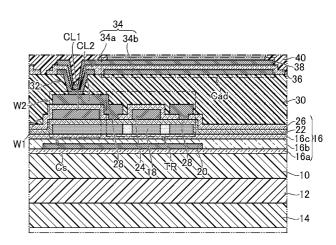

図3は、図2に示す表示装置のIII-III線断面の概略図である。図4は、図3に示す表示装置のIV部分の拡大図である。図4において、基板10は、ポリイミド樹脂からなるが、シートディスプレイ又はフレキシブルディスプレイを構成するために十分な可撓性を有する基材であれば他の樹脂を用いてもよい。基板10の裏面には、感圧接着剤12を介して、補強フィルム14が貼り付けられている。

#### [0016]

基板10上に、バリア無機膜16(アンダーコート層)が積層されている。バリア無機膜16は、シリコン酸化膜16a、シリコン窒化膜16b及びシリコン酸化膜16cの三層積層構造である。最下層のシリコン酸化膜16aは、基板10との密着性向上のため、中層のシリコン窒化膜16bは、外部からの水分及び不純物のブロック膜として、最上層のシリコン酸化膜16cは、シリコン窒化膜16b中に含有する水素原子が薄膜トランジスタTRの半導体層18側に拡散しないようにするブロック膜として、それぞれ設けられるが、特にこの構造に限定するものではなく、さらに積層があってもよいし、単層あるいは二層積層であってもよい。

#### [0017]

薄膜トランジスタTRを形成する箇所に合わせて付加膜20を形成してもよい。付加膜20は、チャネル裏面からの光の侵入等による薄膜トランジスタTRの特性の変化を抑制したり、導電材料で形成して所定の電位を与えることで、薄膜トランジスタTRにバックゲート効果を与えたりすることができる。ここでは、シリコン酸化膜16aを形成した後、薄膜トランジスタTRが形成される箇所に合わせて付加膜20を島状に形成し、その後シリコン窒化膜16b及びシリコン酸化膜16cを積層することで、バリア無機膜16に付加膜20を封入するように形成しているが、この限りではなく、基板10上にまず付加膜20を形成し、その後にバリア無機膜16を形成してもよい。

## [0018]

バリア無機膜16上に薄膜トランジスタTRが形成されている。ポリシリコン薄膜トランジスタを例に挙げて、ここではNchトランジスタのみを示しているが、Pchトランジスタを同時に形成してもよい。薄膜トランジスタTRの半導体層18は、チャネル領域とソース・ドレイン領域との間に、低濃度不純物領域を設けた構造を採る。ゲート絶縁膜22としてはここではシリコン酸化膜を用いる。ゲート電極24は、MoWから形成された第1配線層W1の一部である。第1配線層W1は、ゲート電極24に加え、第1保持容量線CL1を有する。第1保持容量線CL1と半導体層18(ソース・ドレイン領域)との間で、ゲート絶縁膜22を介して、保持容量Csの一部が形成される。

# [0019]

ゲート電極24の上に、層間絶縁膜26(シリコン酸化膜及びシリコン窒化膜)が積層されている。層間絶縁膜26の上に、ソース・ドレイン電極28となる部分を含む第2配線層W2が形成されている。ここでは、Ti、Al及びTiの三層積層構造を採用する。層間絶縁膜26を介して、第1保持容量線CL1(第1配線層W1の一部)と第2保持容量線CL2(第2配線層W2の一部)とで、保持容量Csの他の一部が形成される。

#### [0020]

ソース・ドレイン電極 2 8 を覆うように平坦化有機膜 3 0 が設けられている。平坦化有機膜 3 0 は、 C V D (Chemical Vapor Deposition)等により形成される無機絶縁材料に比べ、表面の平坦性に優れることから、感光性アクリル等の樹脂が用いられる。

## [0021]

平坦化有機膜30は、画素コンタクト部32では除去されて、その上に酸化インジウム

20

10

30

40

スズ (Indium Tin Oxide: ITO) 膜 3 4 が形成されている。酸化インジウムスズ膜 3 4 は、相互に分離された第 1 透明導電膜 3 4 a 及び第 2 透明導電膜 3 4 b を含む。

# [0022]

平坦化有機膜30の除去により表面が露出した第2配線層W2は、第1透明導電膜34aにて被覆される。第1透明導電膜34aを被覆するように、平坦化有機膜30の上にシリコン窒化膜36が設けられている。シリコン窒化膜36は、画素コンタクト部32に開口を有し、この開口を介してソース・ドレイン電極28に導通するように画素電極38が積層されている。画素電極38は、反射電極として形成され、酸化インジウム亜鉛膜、Ag膜、酸化インジウム亜鉛膜の三層積層構造になっている。ここで、酸化インジウム亜鉛膜に代わって酸化インジウムスズ膜を用いてもよい。画素電極38は、画素コンタクト部32から側方に拡がり、薄膜トランジスタTRの上方に至る。

#### [0023]

第2透明導電膜34bは、画素コンタクト部32に隣接して、画素電極38の下方(さらにシリコン窒化膜36の下方)に設けられている。第2透明導電膜34b、シリコン窒化膜36及び画素電極38は重なっており、これらによって付加容量Cadが形成される

#### [0024]

平坦化有機膜30の上であって例えば画素コンタクト部32の上方に、バンク(リブ)と呼ばれて隣同士の画素領域の隔壁となる絶縁有機膜40が形成されている(図3参照)。絶縁有機膜40としては平坦化有機膜30と同じく感光性アクリル等が用いられる。図3に示すように、絶縁有機膜40は、画素電極38の表面を発光領域として露出するように開口され、その開口端はなだらかなテーパー形状となるのが好ましい。開口端が急峻な形状になっていると、その上に形成されるエレクトロルミネセンス層42のカバレッジ不良を生ずる。

#### [0025]

図2に示す複数色(赤R、緑G、青B)の副画素SPXのそれぞれは、エレクトロルミネセンスによる発光を得るための多層構造を有する(図3参照)。多層構造は、複数色(赤R、緑G、青B)の副画素SPXのそれぞれごとに分離された画素電極38を含む。多層構造は、画素電極38の上に積層された複数のエレクトロルミネセンス層42を含む。2層以上(図3の例では全て)のエレクトロルミネセンス層42が、複数の画素電極38のそれぞれごとに分離されて積層されている。

# [0026]

赤Rの副画素SPXにおいて、複数のエレクトロルミネセンス層42は、下から順に、第1層LR1(正孔注入層及び正孔輸送層)、第2層LR2(正孔輸送層)、第3層LR3(電子ブロッキング層)、第4層LR4(発光層)、第5層LR5(正孔ブロッキング層及び電子輸送層)、第6層LR6(電子注入層)を含む。

# [0027]

緑 G の副画素 S P X において、複数のエレクトロルミネセンス層 4 2 は、下から順に、第 1 層 L G 1 (正孔注入層及び正孔輸送層)、第 2 層 L G 2 (正孔輸送層)、第 3 層 L G 3 (電子ブロッキング層)、第 4 層 L G 4 (発光層)、第 5 層 L G 5 (正孔ブロッキング層及び電子輸送層)、第 6 層 L G 6 (電子注入層)を含む。

#### [0028]

青Bの副画素SPXにおいて、複数のエレクトロルミネセンス層42は、下から順に、下から順に、第1層LB1(正孔注入層及び正孔輸送層)、第2層LB2(電子ブロッキング層)、第3層LB3(発光層)、第4層LB4(正孔ブロッキング層及び電子輸送層)、第5層LB5(電子注入層)を含む。

#### [0029]

電子注入層は、無機材料からなり、それ以外のエレクトロルミネセンス層42は有機材料からなる。正孔輸送層及び発光層は、副画素SPXの色ごとに厚みや材料が異なるが、それ以外のエレクトロルミネセンス層42は副画素SPXの色にかかわらず特性が共通す

10

20

30

40

る。

#### [0030]

いずれの色(赤R,緑G,青B)の副画素SPXにおいても、2層以上のエレクトロルミネセンス層42の周縁の相互のずれは、第1範囲内にある。第1範囲は、きわめて小さく、ほとんどずれが無いということができる。

## [0031]

図3に示すように、多層構造は、複数色(赤R、緑G、青B)の副画素SPXのために一体化した共通電極44を含む。共通電極44は、2層以上のエレクトロルミネセンス層42の上にある。ここでは、トップエミッション構造としているため、共通電極44は透明である。例えば、Mg層及びAg層を、エレクトロルミネセンス層42からの出射光が透過する程度の薄膜として形成する。画素電極38が陽極となり、共通電極44が陰極となる。複数の画素電極38と、共通電極44と、複数の画素電極38のそれぞれの中央部と共通電極44の間に介在するエレクトロルミネセンス層42とで発光素子ODが構成される。

#### [0032]

多層構造は、共通電極 4 4 の上に、段階的に屈折率を変化させて光取出し効率を向上させるための複数の光学調整層 4 6 (キャップ層)を含む。 2 層以上の光学調整層 4 6 は、画素電極 3 8 ごとに分離されて共通電極 4 4 の上に積層されている。赤Rの副画素SPXにおいて複数の光学調整層 4 6 R が積層し、緑Gの副画素SPXにおいて複数の光学調整層 4 6 B が積層する。この例では、光学調整層 4 6 R 及び光学調整層 4 6 G の層数は等しく、光学調整層 4 6 B はこれらよりも層数が少ない。

#### [0033]

光学調整層46は、表示領域DAの全体にわたって共通電極44に載って光取り出し効率を向上させる。光学調整層46の膜厚及び屈折率は、エレクトロルミネセンス層42からの発光強度及び発光波長に応じて選定される。光学調整層46の形成材料には、公知の無機化合物を用いる。光学調整層46の形成材料の屈折率は、1.0以上であることが好ましい。光学調整層46の厚みは、特に限定されないが、通常、光を効果的に出射させるために、5nm~100nmが好ましい。

# [0034]

いずれの色(赤R,緑G,青B)の副画素SPXにおいても、図3に示す2層以上の光学調整層46の周縁の相互のずれは、第2範囲内にある。第2範囲は、きわめて小さく、ほとんどずれが無いということができる。2層以上のエレクトロルミネセンス層42の周縁と2層以上の光学調整層46の周縁のずれDは、第1範囲及び第2範囲のいずれよりも大きい。

## [0035]

共通電極 4 4 の上に封止層 4 8 が形成されている。封止層 4 8 は、エレクトロルミネセンス層 4 2 を、外部からの水分侵入を防止することを機能の一としており、高いガスバリア性が要求される。封止層 4 8 は、有機膜 5 0 及びこれを上下で挟む一対の無機膜 5 2 (例えばシリコン窒化膜)の積層構造になっている。一対の無機膜 5 2 は、有機膜 5 0 の周囲で、接触して重なる(図示せず)。封止層 4 8 には、保護層 5 4 及び偏光板 5 6 (例えば円偏光板)が積層される。

## [0036]

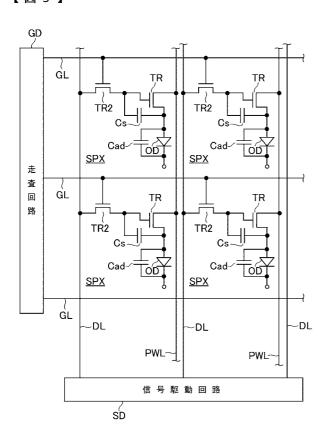

図5は、図1に示す表示装置の回路図である。回路は、走査回路GDに接続される複数の走査線LGと、信号駆動回路SDに接続される複数の信号線DLを有する。図1に示す集積回路チップCP内に信号駆動回路SDが配置されている。隣接する2つの走査線LGと隣接する2つの信号線DLとで囲まれる領域が1つの副画素SPXである。副画素SPXは、駆動トランジスタとしての薄膜トランジスタTR及びスイッチとしての薄膜トランジスタTR2と保持容量Csを含む。走査線LGにゲート電圧が印加されることにより、薄膜トランジスタTR2がON状態となり、信号線DLから映像信号が供給され、保持容

10

20

30

40

量 C s に電荷が蓄積される。保持容量 C s に電荷が蓄積されることにより、薄膜トランジスタTRがON状態となり、電源線PWLから発光素子ODに電流が流れる。この電流により発光素子ODが発光する。発光素子ODに並列に付加容量 C a d が接続されている。

#### [0037]

#### [表示装置の製造方法]

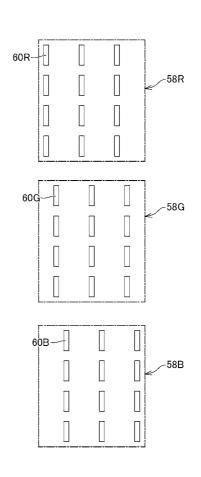

図6は、表示装置の製造方法で使用する複数の精細マスクのそれぞれの一部を示す図である。本実施形態では、精細マスク58R,58G,58Bを用意する。精細マスク58R,58G,58Bは、それぞれ、同一色(赤R、緑G又は青B)の副画素群SPXそれぞれに対応する複数の開口60R,60Bを有する。

#### [0038]

[連続的複数回の蒸着(1)]

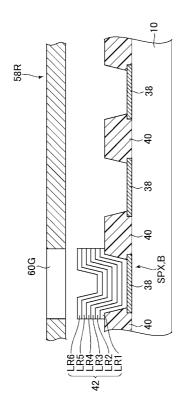

図 7 は、精細マスク 5 8 R を使用したプロセスを示す図である。ここでは、赤 R の副画素群 S P X 用の精細マスク 5 8 R を、基板 1 0 (図 4 )を含む構造体に対して位置合わせする。このアライメントは、例えば、基板 1 0 に設けられたマーク(図示せず)と精細マスク 5 8 R に設けられたマーク(図示せず)を使用して行う。

#### [0039]

そして、赤Rの副画素群SPXの多層構造の2層以上(例えば全てのエレクトロルミネセンス層42)を、精細マスク58Rを使用した連続的複数回の蒸着によって、基板10に形成する。具体的には、第1層LR1~第6層LR6を形成する。

#### [0040]

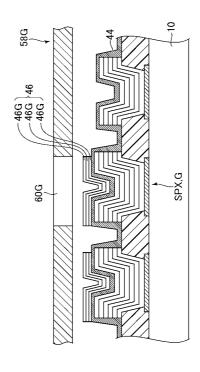

図8は、精細マスク58Gを使用したプロセスを示す図である。ここでは、緑Gの副画素群SPX用の精細マスク58Gを、基板10(図4)を含む構造体に対して位置合わせする。このアライメントは、例えば、基板10に設けられたマーク(図示せず)と精細マスク58Gに設けられたマーク(図示せず)を使用して行う。

#### [0041]

そして、緑Gの副画素群SPXの多層構造の2層以上(例えば全てのエレクトロルミネセンス層42)を、精細マスク58Gを使用した連続的複数回の蒸着によって、基板10に形成する。具体的には、第1層LG1~第6層LG6を形成する。

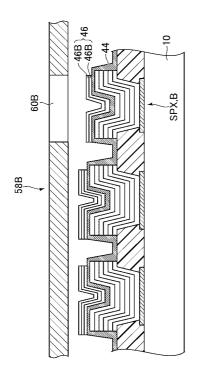

## [0042]

図9は、精細マスク58Bを使用したプロセスを示す図である。ここでは、青Bの副画素群SPX用の精細マスク58Bを、基板10(図4)を含む構造体に対して位置合わせする。このアライメントは、例えば、基板10に設けられたマーク(図示せず)と精細マスク58Bに設けられたマーク(図示せず)を使用して行う。

# [0043]

そして、青 B の副画素群 S P X の多層構造の 2 層以上(例えば全てのエレクトロルミネセンス層 4 2 )を、精細マスク 5 8 B を使用した連続的複数回の蒸着によって、基板 1 0 に形成する。具体的には、第 1 層 L B 1 ~ 第 5 層 L B 5 を形成する。

#### [0044]

本実施形態によれば、精細マスク 5 8 R , 5 8 G , 5 8 B のそれぞれを使用して蒸着を連続的に複数回行う。そのため、精細マスク 5 8 R , 5 8 G , 5 8 B のそれぞれのアライメント回数を減らすことができる。

## [0045]

## 「一括蒸着]

図10は、全体マスクを使用したプロセスを示す図である。本実施形態では、全体マスク62を用意する。全体マスク62は、表示領域DAの全体にわたって全ての画素PX(図2参照)を全体的に含む大きさの開口64を有する。全体マスク62を、基板10(図4)を含む構造体に対して位置合わせする。このアライメントは、例えば、基板10に設けられたマーク(図示せず)と全体マスク62に設けられたマーク(図示せず)を使用して行う。

# [0046]

10

20

30

40

そして、複数色(赤R、緑G、青B)の副画素SPXのそれぞれの多層構造の少なくとも1層(例えば共通電極44)を、全体マスク62を使用した蒸着によって、一括して形成する。

# [0047]

[連続的複数回の蒸着(2)]

本実施形態では、共通電極44の上に複数の光学調整層46を蒸着によって形成する。 蒸着には、図6に示す精細マスク58R,58G,58Bを使用する。

#### [0048]

図11は、赤の副画素群SPXに複数の光学調整層46を形成するプロセスを示す図である。ここでは、図7で使用した精細マスク58Rを使用する。精細マスク58Rを、基板10(図4)を含む構造体に対して位置合わせする。このアライメントは、例えば、基板10に設けられたマーク(図示せず)と精細マスク58Rに設けられたマーク(図示せず)を使用して行う。

# [0049]

そして、赤Rの副画素群SPXの複数の光学調整層46の2層以上(例えば全ての光学調整層46R)を、精細マスク58Rを使用した連続的複数回の蒸着によって、基板10に形成する。

#### [0050]

図12は、緑の副画素群SPXに複数の光学調整層46を形成するプロセスを示す図である。ここでは、図8で使用した精細マスク58Gを使用する。精細マスク58Gを、基板10(図4)を含む構造体に対して位置合わせする。このアライメントは、例えば、基板10に設けられたマーク(図示せず)と精細マスク58Gに設けられたマーク(図示せず)を使用して行う。

#### [0051]

そして、緑 G の副画素群 S P X の複数の光学調整層 4 6 の 2 層以上(例えば全ての光学調整層 4 6 G)を、精細マスク 5 8 G を使用した連続的複数回の蒸着によって、基板 1 0 に形成する。

## [0052]

図13は、青の副画素群SPXに複数の光学調整層46を形成するプロセスを示す図である。ここでは、図9で使用した精細マスク58Bを使用する。精細マスク58Bを、基板10(図4)を含む構造体に対して位置合わせする。このアライメントは、例えば、基板10に設けられたマーク(図示せず)と精細マスク58Bに設けられたマーク(図示せず)を使用して行う。

# [0053]

そして、青Bの副画素群SPXの複数の光学調整層46の2層以上(例えば全ての光学調整層46B)を、精細マスク58Bを使用した連続的複数回の蒸着によって、基板10に形成する。

#### [0054]

# 「製造装置の全体構造]

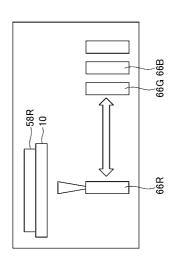

図14は、連続的複数回の蒸着を行うための製造装置の全体構造を示す図である。本実施形態では、上述したように、精細マスク58R(又は58G,58B)を使用して、アライメントを1回行った後に複数回の蒸着を連続して行う。異なる蒸着を別々のチャンバで行うには基板10の搬送が必要である。しかし、アライメントされた精細マスク58R(又は58G,58B)及び基板10を搬送すると、振動によって位置ずれが生じるおそれがある。そこで、本実施形態では、精細マスク58R(又は58G,58B)及び基板10を移動させずに、蒸着源66R(又は66G,66B)を移動させる。例えば、図14に示す製造装置では、精細マスク58R(又は58G,58B)及び基板10の位置は固定され、蒸着源66R(又は66G,66B)を移動させることで、連続的複数回の蒸着を行うようになっている。

## [0055]

50

10

20

30

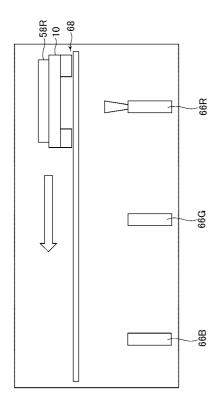

図15は、製造装置の変形例を示す図である。この例では、精細マスク58R(又は58G,58B)及び基板10を、磁気浮上機構68によって、蒸着源66R(又は66G,66B)の上方に搬送する。磁気浮上機構68を利用するので、精細マスク58R(又は58G,58B)及び基板10に振動を与えることがなく、位置ずれが生じることもない。

## [0056]

#### 「変形例 ]

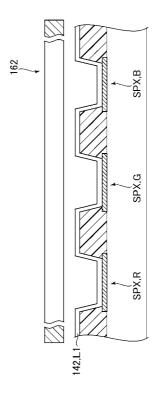

図16は、多層構造の変形例1を示す図である。この例では、例えば、赤R、緑G及び青Bの副画素SPXの第1層L1が連続一体化している。製造プロセスでは、複数のエレクトロルミネセンス層142の少なくとも1層(第1層L1)を、全体マスク162を使用した蒸着によって形成する。その後のプロセスは、上述した実施形態で説明した内容(図3参照)が該当する。

## [0057]

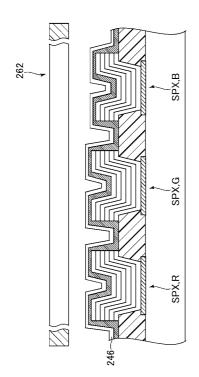

図17は、多層構造の変形例2を示す図である。この例では、例えば、赤R、緑G及び青Bの副画素SPXの光学調整層246が連続一体化している。製造プロセスでは、少なくとも1層(図17では1層のみ)の光学調整層246を、全体マスク262を使用した蒸着によって形成する。その後、上述した実施形態で説明したように、図示しない他の光学調整層を相互に分離して積層する。また、エレクトロルミネセンス層の形成についても、上述した実施形態の内容が該当する。

# [0058]

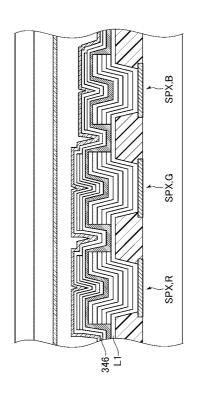

図18は、多層構造の変形例3を示す図である。この例では、赤R、緑G及び青Bの第1層L1が連続一体化している。その形成方法は、図16に示す内容を適用する。また、赤R、緑G及び青Bの副画素SPXの光学調整層346が連続一体化している。その形成方法は、図17に示す内容を適用する。本変形例は、第1変形例及び第2変形例の組み合わせである。ただし、図17では、複数の光学調整層246の最下層を連続一体化したのに対して、図18では、複数の光学調整層346の最上層を連続一体化してある。

#### [0059]

本発明は、上述した実施形態に限定されるものではなく種々の変形が可能である。例えば、実施形態で説明した構成は、実質的に同一の構成、同一の作用効果を奏する構成又は同一の目的を達成することができる構成で置き換えることができる。

#### 【符号の説明】

# [0060]

基板、12 感圧接着剤、14 補強フィルム、16 バリア無機膜、16a シリコン酸化膜、 1 6 b シリコン窒化膜、 1 6 c シリコン酸化膜、 1 8 半導体層、 2 0 付加膜、2 2 ゲート絶縁膜、24 ゲート電極、26 層間絶縁膜、28 ドレ イン電極、30 平坦化有機膜、32 画素コンタクト部、34 酸化インジウムスズ膜 3 4 a 第 1 透明導電膜、3 4 b 第 2 透明導電膜、3 6 シリコン窒化膜、3 8 素電極、40 絶縁有機膜、42 エレクトロルミネセンス層、44 共通電極、46 光学調整層、46B 光学調整層、46G 光学調整層、46R 光学調整層、48 止層、50 有機膜、52 無機膜、54 保護層、56 偏光板、58B 精細マスク 、58G 精細マスク、58R 精細マスク、60 開口、60B 開口、60G 開口、62 全体マスク、64 開口、66B 蒸着源、66G 6R 蒸着源、68 磁気浮上機構、142 エレクトロルミネセンス層、162 マスク、 2 4 6 光学調整層、 2 6 2 全体マスク、 3 4 6 光学調整層、 B A 屈曲対 応領域、CL1 第1保持容量線、CL2 第2保持容量線、CP 集積回路チップ、C ad 付加容量、Cs 保持容量、DA 表示領域、DL 信号線、DP ディスプレイ 、FP フレキシブルプリント基板、GD 走査回路、L1 第1層、LB1 LB2 第2層、LB3 第3層、LB4 第4層、LB5 第5層、LG 走 査 線 、 L 第 5 層、 L G 1 第 1 層、LG2 第 2 層、LG3 第 3 層、LG4 第 4 層、LG5 G 6 第 6 層 、 L R 1 第 1 層 、 L R 2 第 2 層 、 L R 3 第 3 層 、 L R 4 第 4 層 、 L

10

20

30

40

R 5 第 5 層、L R 6 第 6 層、O D 発光素子、P W L 電源線、P X 画素、S D 信号駆動回路、SPX 副画素、TR 薄膜トランジスタ、TR2 薄膜トランジスタ、 W 1 第 1 配線層、W 2 第 2 配線層。

【図1】

【図2】

【図3】 【図4】

【図5】

【図7】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

# フロントページの続き

| (51) Int.CI. |       |           | FΙ      |       |       | テーマコード(参考) |

|--------------|-------|-----------|---------|-------|-------|------------|

| G 0 9 F      | 9/30  | (2006.01) | G 0 9 F | 9/30  | 3 6 5 |            |

| G 0 9 F      | 9/00  | (2006.01) | G 0 9 F | 9/00  | 3 3 8 |            |

| C 2 3 C      | 14/04 | (2006.01) | C 2 3 C | 14/04 | Α     |            |

F ターム(参考) 5G435 AA17 BB05 CC09 CC12 FF02 HH02 KK05

| 专利名称(译)        | 显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|

| 公开(公告)号        | JP2019216021A                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2019-12-19 |  |  |

| 申请号            | JP2018112642                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2018-06-13 |  |  |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                                                                                                                                                                                                                                                                                                                                                          |         |            |  |  |

| 申请(专利权)人(译)    | 有限公司日本显示器                                                                                                                                                                                                                                                                                                                                                                                          |         |            |  |  |

| [标]发明人         | 濱田夕慎                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |

| 发明人            | 濱田 夕慎                                                                                                                                                                                                                                                                                                                                                                                              |         |            |  |  |

| IPC分类号         | H05B33/10 H01L27/32 H01L51/50 H05B33/12 H05B33/02 G09F9/30 G09F9/00 C23C14/04                                                                                                                                                                                                                                                                                                                      |         |            |  |  |

| FI分类号          | H05B33/10 H01L27/32 H05B33/14.A H05B33/12.B H05B33/02 G09F9/30.365 G09F9/00.338 C23C14 /04.A                                                                                                                                                                                                                                                                                                       |         |            |  |  |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC05 3K107/CC33 3K107/CC45 3K107/EE21 3K107/FF06 3K107 /GG04 3K107/GG28 3K107/GG33 3K107/GG54 4K029/AA11 4K029/AA25 4K029/BA62 4K029/BB03 4K029/CA01 4K029/DB06 4K029/HA03 4K029/HA04 5C094/AA43 5C094/AA46 5C094/BA27 5C094 /CA19 5C094/CA24 5C094/DA15 5C094/EA07 5C094/FA01 5C094/GB01 5G435/AA17 5G435/BB05 5G435/CC09 5G435/CC12 5G435/FF02 5G435/HH02 5G435/KK05 |         |            |  |  |

| 外部链接           | <u>Espacenet</u>                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |

# 摘要(译)

解决方案:为了减少掩模对准的次数。解决方案:用于显示全彩色图像的多个像素PX中的每个像素都是由多种颜色的子像素SPX(红色R,绿色G,以及蓝色的B)。多个像素PX包含相同颜色(红色R,绿色G或蓝色B)的子像素组SPX。多种颜色(红色R,绿色G和蓝色B)的每个子像素SPX具有用于通过电致发光获得发光的多层结构。在多种颜色(红色R,绿色G和蓝色B)中的每一个中,每个具有多个具有相同颜色(红色R,绿色G或蓝色B)的多重结构的层通过使用限定掩模58R(或58G和58B)连续多次蒸发在基板10上形成子像素组SPX的子像素组SPX。定义掩模58R(或58G和58B)具有多个开口60,对应于相同颜色(红色R,绿色G或蓝色B)的子像素组SPX.SELECTEDDRAWING:图7