# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2005-173420 (P2005-173420A)

(43) 公開日 平成17年6月30日 (2005.6.30)

| (51) Int.C1. <sup>7</sup> | F I                          |                   |              | テーマコー        | <br>ド (参考) |

|---------------------------|------------------------------|-------------------|--------------|--------------|------------|

| GO9G 3/30                 | GO9G                         | 3/30              | J            | 3K007        |            |

| GO9G 3/20                 | GO9G                         | 3/30              | K            | 5C080        |            |

| HO5B 33/14                | G09G                         | 3/20              | 611H         |              |            |

|                           | G09G                         | 3/20              | 622A         |              |            |

|                           | G09G                         | 3/20              | 623A         |              |            |

|                           | 審査請求 未                       | 請求請求              | 頃の数1 OL      | (全 18 頁)     | 最終頁に続く     |

| (21) 出願番号                 | 特願2003-415889 (P2003-415889) | (71) 出願人          | 000001007    |              |            |

| (22) 出願日                  | 平成15年12月15日 (2003.12.15)     | キヤノン株式会社          |              |              |            |

|                           |                              | 東京都大田区下丸子3丁目30番2号 |              |              |            |

|                           |                              | (74)代理人           | 100096828    |              |            |

|                           |                              |                   | 弁理士 渡辺       | 2 敬介         |            |

|                           |                              | (74)代理人           |              |              |            |

|                           |                              |                   | 弁理士 山口       | 芳広           |            |

|                           |                              | (72)発明者           |              |              |            |

|                           |                              |                   |              | [下丸子3丁目3     | 30番2号 キ    |

|                           |                              |                   | ヤノン株式会       | 社内           |            |

|                           |                              | (72)発明者           |              |              |            |

|                           |                              |                   |              | 下丸子3丁目3      | 30番2号 キ    |

|                           |                              | ヤノン株式会社内          |              |              |            |

|                           |                              | F <i>タ</i> ーム (参  | 考) 3K007 AB3 |              |            |

|                           |                              |                   | 5C080 AA0    |              | EE28 FF11  |

|                           |                              |                   | 11(          | )2 JJ03 JJ04 | JJ05       |

#### (54) 【発明の名称】表示装置

# (57)【要約】

【課題】 電流駆動型の E L 表示装置において、列制御 回路から出力される電流信号のばらつきを効率よく検出 する。

【解決手段】 画素回路 8 と列制御回路 4 との間にスイッチ 5 を設け、列制御回路 4 から出力される電流信号を該スイッチ 5 の切り替えによって共通出力線 1 3 に総和電流 I o u t として出力する構造とし、列走査制御回路 1 においては、シフトレジスタ 2 の進みと、ゲート回路 3 からのサンプリング信号の出力タイミングとを独立して制御することにより、検査対象となる列制御回路 4 にのみ所定のサンプリング信号を入力してサンプリングを行い、電流信号を検出する。

【選択図】 図1

#### 【特許請求の範囲】

## 【請求項1】

画素回路を複数個マトリクス配置し、各行の画素回路を共通に走査線に接続し、各列の画素回路を共通にデータ線に接続してなる画像表示部と、走査線を順次選択すると同時に、選択した行の各画素の表示に応じたレベルの電流信号を当該画素回路が接続されたデータ線に印加する駆動回路とを備え、画像表示を行う表示装置であって、データ線毎に、

該当映像信号のサンプリングを制御するサンプリング信号を出力する列走査制御回路と、列走査制御回路から出力されたサンプリング信号によって、映像信号をサンプリングして各画素回路に入力する電流信号をデータ線に出力する列制御回路と、

該列制御回路から出力された電流信号の転送先を、共通出力線と画素回路に接続されたデータ線との間で切り替えるスイッチと、

を有し、

第 1 の期間において、上記各列走査制御回路が、第 1 の制御信号の入力によって順次サンプリング信号を出力し、上記スイッチが列制御回路と画素回路とを接続し、

第2の期間において、第2の制御信号の入力によって、任意の列走査制御回路が任意の期間にサンプリング信号を出力し、上記スイッチが全列制御回路と共通出力線とを接続し、各列制御回路から出力された電流信号を該共通出力線より総和電流として出力することを特徴とする表示装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明は、外部より入力された映像信号に基づいて、各画素回路に表示に応じた電流信号を入力して画像を表示する表示装置、特に、エレクトロルミネッセンス(EL)素子を用いた表示装置に関する。

#### 【背景技術】

## [0002]

EL素子や液晶素子などを用いて構成されたフラットな表示装置においては、複数行、複数列に配置した画素を、行毎に走査線に、列毎にデータ線に共通に接続し、行走査回路より各走査線を選択すると同時に、列走査回路より各データ線に所定の表示信号を印加して、選択された該当行の画素に所定の表示を行わせるマトリクス駆動が一般的である。

[0003]

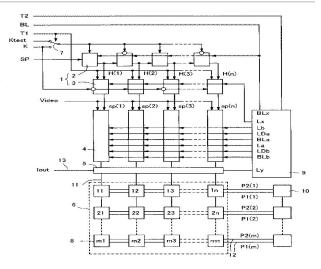

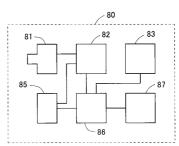

図9に、従来の電流駆動型 E L 表示装置の表示パネルの構成例を示す。図中、1は列走査制御回路、2はシフトレジスタ、3はゲート回路、4は列制御回路、6は表示部、8は画素回路、9はタイミング制御回路、10は行走査制御回路、11はデータ線、12は走査線である。

#### [0004]

図9において、列走査制御回路1はシフトレジスタ2とゲート回路3で構成され、当該表示パネル外部より入力されるクロック信号K、スタート信号SP、及びタイミング制御回路9より入力される制御信号Lxにより、サンプリング信号sp(1)~sp(n)を順次列制御回路4に出力する。

[0005]

列制御回路4には、列走査制御回路1から出力されたサンプリング信号sp(q)(q=1~n)と、当該表示パネル外部より映像信号(点順次RGBビデオ電圧信号;Video)、基準電圧信号REF、及び、タイミング制御回路9より制御信号La,Lbが入力される。各列制御回路4においては、サンプリング信号sp(q)の入力タイミングに応じて、映像信号Videoをサンプルホールドし、電圧-電流変換した電流信号i(data)をデータ線11に出力する。

#### [0006]

各列制御回路4は、サンプルホールド及び電圧・電流変換にかかる回路を2系統有し、

20

10

30

40

各回路において行毎に相補的にサンプルホールドを行う。さらに、各列制御回路4から出力される電流信号i(data)は、映像信号Videoを線順次化した信号である。

[0007]

表示部6は、複数の画素回路8をn列×m行に配置し、同一行の画素回路8は共通に走査線12に接続し、同一列の画素回路8は共通にデータ線11に接続されている。表示部6においては、各データ線11への電流信号i(data)の出力に応じて、行走査制御回路10より、各行の走査線12に順次走査信号P1(r),P2(r)(r=1~m)が出力され、該当行の画素回路8において電流プログラミング動作が行われ、入力された電流信号i(data)が記憶され、該電流プログラミング動作終了後に記憶された電流信号i(data)のレベルに応じた電流がEL素子に供給されて、該EL素子が所定の輝度で発光する。

[00008]

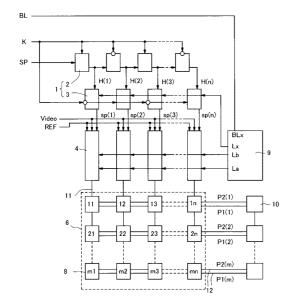

図10に、図9の列走査制御回路1の構成例を示す。

[0009]

図10の回路において、シフトレジスタ2はクロックドインバータによるフリップフロップの縦続接続により構成されている。図中の K b はクロック信号 K の極性反転信号であり、クロック信号 K , K b が、縦続接続される隣接フリップフロップで互いに逆の入力となっている。ゲート回路 3 は、A N D ゲートで構成されており、対応するシフトレジスタ2のフリップフロップ出力と、該フリップフロップの入力側クロックドインバータに入力されるクロック信号 K , K b とは逆極性のクロック信号が入力される。

[0010]

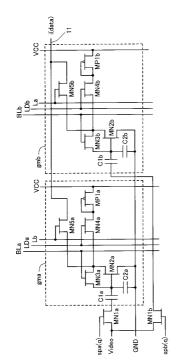

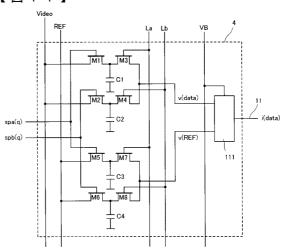

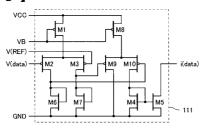

図 1 1 に、図 9 の列制御回路 4 の構成例を示す。図中 1 1 1 は電圧電流変換回路、M 1 ~ M 8 はトランジスタ、C 1 ~ C 4 は容量である。尚、以下の説明において、トランジスタのソース、ドレイン、ゲートをそれぞれ、/S、/D、/Gと記載する。

[0011]

図11の回路において、入力された映像信号Videoと基準電圧信号REFはそれぞれ、M1/S,M2/S、及び、M5/S,M6/Sに入力される。spa(a),spb(a)は、列走査制御回路1から出力されたサンプリング信号sp(a)であり、図11の回路のM1/G,M5/G、及び、M2/G,M6/Gに入力される。M1/D,M2/D,M5/D,M6/DにはそれぞれC1,C2,C3,C4が接続されるとともに、M3/S,M4/S,M7/S,M8/Sが接続される。M3/DとM4/D、及び、M7/DとM8/Dは各々接続されてv(data)及びv(REF)として電圧電流変換回路111には基準電流設定バイアスVBが入力され、制御信号La及びLbに応じて電流信号i(data)を出力する

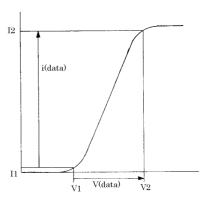

図 1 1 の列制御回路 4 中の電圧電流変換回路 1 1 1 の構成例を図 1 3 に示す。図中、 M 1 ~ M 1 0 はトランジスタである。

[ 0 0 1 2 ]

図13の回路において、第1のソースカップル回路M2,M3の各ドレインにM6/D,M7/Dが接続されており、M6,M7はそれぞれソースが接地され、ドレインとゲートが短絡されている。さらに、ソースが電源VCCに接続され、ゲートが基準電流バイアスVBに接続された第2の基準電流源として動作するM8を設け、M8/Dを第2のソースカップル回路M9,M10のソースに接続し、M9/G及びM10/Gを各々M7/D,M6/Dに接続する。そして、M10/DからM4及びM5のカレントミラー回路を介して、電流データi(data)を出力する。図13において、M6及びM7の電流駆動能力をM9及びM10より小さくするため、M6及びM7のゲート領域のW/L比を、M9及びM10のゲート領域のW/L比より小さくしておく。このように設計された図13の電圧電流変換回路の電圧電流変換特性を図14に示す。当該回路によれば、電圧電流変換特性の線形性を崩すことなく、黒レベルV1における黒電流11を小さくすることができる。

[0013]

50

10

20

30

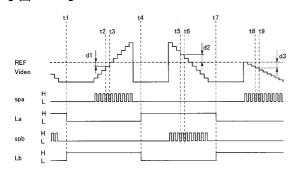

図11の列制御回路4の動作を図12のタイムチャートにより説明する。

## [0014]

[0015]

[0016]

上記 t 1 ~ t 7 間の動作を t 7 以降、繰り返し、映像信号 V i d e o は水平走査周期毎に更新される線順次信号に変換される。

[ 0 0 1 7 ]

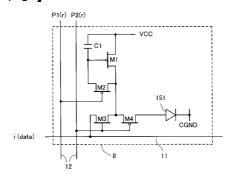

図 1 5 に、図 9 の画素回路 8 の構成例を示す。図中、 1 5 1 は E L 素子、 M 1 ~ M 4 はトランジスタ、 C 1 は容量である。

[0018]

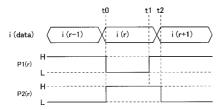

図 1 5 の画素回路 8 は、電流設定方式の構成例であり、走査線 1 2 より走査信号 P 1 ( r ) , P 2 ( r ) ( r = 1 ~ m ) が、データ線 1 1 より電流信号 i ( d a t a ) が入力される。 M 4 / D は接地された E L 素子 1 5 1 の電流注入端子に接続されている。当該画素回路 8 の動作を図 1 6 のタイムチャートにより説明する。

[0019]

時刻 t 0 以前において、該当 r 行の P 1 (r), P 2 (r)はH及びLであるので、M 2 及び M 3 はともにオフであり、M 4 がオンであるため、容量 C 1 及び M 1 のゲート電に保持された充電電圧によって決定された M 1 / G電圧によって E L 素子 1 5 1に電流が注入され、これに応じて該 E L 素子 1 5 1は発光している。時刻 t 0 において、該当 r 行の P 1 (r), P 2 (r)が L、Hに変化するとともに、r 行目の電流信号 i (r)が 定する。 M 2 , M 3 がともにオンし、 M 4 がオフするため、該当 r 行の E L 素子 1 5 1 は消灯する。さらに、 M 2 に電流信号 i (r)が供給されるため、これに応じて M 2 / G電圧が設定され、容量 C 1 及び M 1 のゲート容 H が充電される。電流信号 i (r)が確定している時刻 t 1 において、P 1 (r)は再び H に変化して M 2 はオフとなり、 M 1 / G電圧の設定動作が終了して保持動作に移行する。時刻 t 2 において、P 2 (r)は L に変化して M 1 への電流供給を停止するとともに M 4 がオンして M 1 / G電圧で設定された M 1 のドレイン電流が E L 素子 1 5 1 に注入され、E L 素子 1 5 1 が発光を開始する。

[ 0 0 2 0 ]

アクティブマトリクス駆動する表示装置において、表示パネルはTFT回路までの製造工程で不良品の検査を行うことが望まれており、画素回路の検査を行うことを目的として、画素回路の駆動トランジスタの電流を、シフトレジスタ等の走査信号で開閉される点順次スイッチを介して共通線に出力して検査する方法が、特許文献1に開示されている。また、画素回路の駆動トランジスタのソースまたはドレインに接続されるデータドライバと、該駆動トランジスタのゲートに接続される走査線ドライバの不良を検査することを目的

10

20

30

40

として、各データ線ドライバの出力をスイッチを介して共通線に出力する方法が特許文献 2に開示されている。

[0021]

さらに、アクティブマトリクス駆動の E L 表示装置は、列制御回路に含まれる電圧電流変換回路のトランジスタ特性ばらつきが列単位の輝度ばらつきとなり、縦縞の画像劣化となるため、映像信号レベルに対する電流変換出力を補正することが望まれており、電圧プログラミング型パネルにおける補正方法が特許文献 3 に開示されている。

[0022]

【特許文献 1 】特開平9-265063号公報

【特許文献 2 】特公平 8 - 2 7 4 6 3 号公報

【特許文献3】特開2002-278513公報

【発明の開示】

【発明が解決しようとする課題】

[0023]

電流プログラミング型のEL表示装置においては、図9に示したように、列制御回路4がデータ線11に線順次化電流信号i(data)を出力し、一般にその1列あたりの電流値は数μΑ以下と非常に小さい。

[0024]

先に示した特許文献1に開示された方法では、点順次動作する水平切り替えスイッチを介して電流信号を出力するため、非常に小さい1画素(列)の電流を共通線に出力しなければならず、共通線または外部の検出系回路まで含んだ経路の容量負荷を駆動するのに長時間が必要となってしまう。

[0025]

また、特許文献 2 に開示された方法は、特定の画素回路において点順次動作の出力を共通線に出力したものであり、同一時間では 1 つのデータ線の画素情報を共通線に出力していることになるため、非常に小さな 1 画素(列)の電流を共通線に出力しなければならず、やはり長時間が必要になってしまう。

[0026]

特許文献 3 に開示された技術は、電圧プログラミング型における画素回路の電力供給線の電流測定に関するものであるが、実動作時の電流測定素子が影響し、階調性を崩す原因となる。また、電流プログラミング型 E L 表示装置において映像信号を線順次化する場合には、階調性への影響の問題に加え、列制御回路の線順次化電流出力を測定することは、例えば図 1 3 の M 5 の ソースのみに電力を供給する電力線の電流を測定することになり、新たな電力線が必要となる。

[0027]

本発明の課題は、上記問題を解決し、製造工程において、列制御回路や列制御回路による電圧 - 電流変換特性のばらつきを、簡易な構成によって高精度に、且つ短時間で検出する手段を提供し、表示のばらつきのない表示装置を提供することにある。

【課題を解決するための手段】

[0028]

本発明は、画素回路を複数個マトリクス配置し、各行の画素回路を共通に走査線に接続し、各列の画素回路を共通にデータ線に接続してなる画像表示部と、走査線を順次選択すると同時に、選択した行の各画素の表示に応じたレベルの電流信号を当該画素回路が接続されたデータ線に印加する駆動回路とを備え、画像表示を行う表示装置であって、データ線毎に、

該当映像信号のサンプリングを制御するサンプリング信号を出力する列走査制御回路と、列走査制御回路から出力されたサンプリング信号によって、映像信号をサンプリングして各画素回路に入力する電流信号をデータ線に出力する列制御回路と、

該列制御回路から出力された電流信号の転送先を、共通出力線と画素回路に接続されたデータ線との間で切り替えるスイッチと、

10

20

30

40

を有し、

第 1 の期間において、上記各列走査制御回路が、第 1 の制御信号の入力によって順次サンプリング信号を出力し、上記スイッチが列制御回路と画素回路とを接続し、

第2の期間において、第2の制御信号の入力によって、任意の列走査制御回路が任意の期間にサンプリング信号を出力し、上記スイッチが全列制御回路と共通出力線とを接続し、各列制御回路から出力された電流信号を該共通出力線より総和電流として出力することを特徴とする表示装置。

# 【発明の効果】

#### [0029]

本発明によれば、列制御回路出力電流を共通出力線に出力できるようにすることにより、列制御回路からの出力電流値を比較的大きな総和電流値として検出することが可能な構成にできる。そのため、外部容量負荷のドライブ能力を上げ、上記電流値の検出時間を短縮することができる。さらに、シフトレジスタの進みと該シフトレジスタを含む列制御回路からのサンプリング信号の出力とを独立して制御するため、必要な列制御回路のみサンプリングを行い、他の列制御回路ではサンプリング動作を省略することができるため、検出時間を大幅に短縮することができる。よって、本発明によれば、表示装置製造工程におけるTFTパネルの検査時間、輝度ムラ補正のための電流ばらつき検出時間を大幅に短縮し、製造コストを削減して、高画質の画像表示が可能な表示パネルをより安価に提供することができる。

#### 【発明を実施するための最良の形態】

#### [0030]

本発明の表示装置は、サンプリング信号を出力する列走査制御回路において、第1の制御信号と第2の制御信号を切り替えて入力しうるように構成し、第1の制御信号が入力される第1の期間においては、従来と同様の列毎に順次サンプリング信号を出力する構成し、第2の制御信号が入力される第2の期間においては、任意の列走査制御回路においては、任意の列走査制御回路においては、年発明にかかる列走査制御回路においては、第2の期間において、各シフトレジスタを独立に動作させる。さらに、本発明においては、映像信号をサンプリングする列制御回路と画素回路との間にスイッチを設け、該スイッチの切り替えによって、上記第1の期間においては、列制御回路から出力された電流信号をそのまま画素回路に転送するが、第2の期間においては、全てのデータ線を共通出力線に接続し、列制御回路から出力された電流信号を総和電流として出力する。

#### [0031]

上記構成により、本発明においては、通常の表示駆動時には、上記第1の期間の動作を行うが、列制御回路のばらつき等を検査する際には、上記第2の期間の動作を行う。従来、同様の検査を行う場合には、シフトレジスタが順次動作することから、1列のデータ線のみから電流信号を取り出すか、或いは、1列のデータ線にのみ所定のレベルの電流信号が出力されるような映像信号を列制御回路に供給し、サンプリング動作は全ての列制御回路で行っていた。本発明においては、上記したように、各シフトレジスタを独立して動作させるため、検査対象の列制御回路のみサンプリング動作を行い、検査対象でない列制御回路のサンプリング動作を省略することができる。即ち、省略したサンプリング動作にかかる期間分、検査にかかる時間を短縮することができる。

#### [0032]

図1に、本発明の表示装置の一実施形態の EL表示パネルの構成例を示す。図中、5,7はスイッチ、13は共通出力線であり、図9と同じ部材には同じ符号を付した。図9の従来の表示パネルとの違いを説明する。

#### [0033]

図 1 において、スイッチ 7 の共通端子はシフトレジスタ 2 のクロック入力端子に接続され、被選択端子の一方には、従来同様のクロック信号 K (第 1 の制御信号)が、他方には制御信号 K t e s t (第 2 の制御信号)が入力される。スイッチ 7 は、制御信号 T 1 = L

20

30

の時(第1の期間)にクロック信号 K を、 T 1 = H の時(第2の期間)に K t e s t を選択してシフトレジスタ2に入力させる。

#### [0034]

さらに、図1において、列制御回路4と画素回路8との間には、スイッチ5が配置され、その共通端子が、各列制御回路4の出力側に接続され、被選択端子の一方が画素回路8に接続されたデータ線11に、他方が共通出力線13に接続されている。スイッチ5は、制御信号Ly=Lの時(第1の期間)に各列制御回路4をデータ線11に接続し、Ly=Hの時(第2の期間)に全列制御回路4を共通出力線13に接続する。

#### [0035]

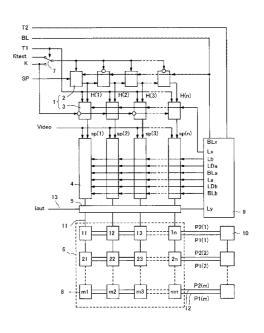

図2に、図1の列走査制御回路1の構成例を示す。

#### [0036]

図2の回路が、図10の従来の列走査制御回路と異なる点は、ANDゲート回路が3入力となっており、2入力NANDゲートが追加されている点である。2入力NANDゲートの一方の入力端子には、制御信号T1が入力され、他方の入力端子には各列のシフトレジスタの出力が入力される。また、NANDゲートの出力端子は、前段のANDゲートの入力端子に接続されている。

#### [0037]

図2の回路において、制御信号 T 1 = L の時、N A N D ゲートの出力は、もう一方の入力に係わらず H であるので、当該回路においては、図 1 0 の回路と全く同じ動作を行う。即ち、通常の表示動作である。

#### [0038]

図2の回路において、制御信号T1=Hの時、シフトレジスタ2においては、制御信号T1によって制御されるスイッチ7より制御信号Ktestが入力される。クロックドインバータにより構成されるシフトレジスタ2は、スタート信号SPの入力後、シフトを制御する制御信号Ktestの立ち上がり、立ち下がりに応じてシフトレジスト信号H(a)を出力する。列走査制御回路1の出力はANDゲート出力であり、制御信号T1がLの時は、該当列のシフトレジスタ出力がHの期間において、クロック信号K、Kbに応じたパルスが出力される。制御信号T1=Hの時は、該当列のシフトレジスタ出力がH、且つ、1つ後段のシフトレジスタ出力がLの期間においてクロック信号K,Kbに応じたパルスが出力される。

#### [0039]

以上の構成により、制御信号 T 1 = L の第 1 の期間においては、シフトレジスタ 2 と列走査制御回路 1 の出力のタイミングは、同一のクロック信号 K , K b により制御され、第 q 列のサンプリング信号の立ち下がりと同時に、第 q + 1 列のサンプリング信号出力が立ち上がり、第 q 列目の列制御回路 4 において、第 q 列目の映像信号 V i d e o のサンプリング及び電圧 - 電流変換動作後、第 q + 1 列目のサンプリング信号出力の立ち上がりにおいて、第 q + 1 列目の列制御回路 4 は、第 q + 1 列目の映像信号サンプリング及び電圧 - 電流変換動作を開始する。

#### [0040]

また、制御信号T1=Hの第2の期間においては、シフトレジスタ2の進みと、列走査制御回路1の出力タイミングを独立に制御可能となるため、第 q 列の列走査制御回路1の出力の立ち下がりにおいて、第 q + 1 列目の列走査制御回路1の出力の立ち上がりが発生することはなく、第 q 列目の映像信号サンプリング及び電圧・電流変換動作後、第 q + 1 列目の列制御回路4は、サンプリング信号の入力待機状態でいることができる。

#### [0041]

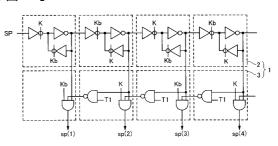

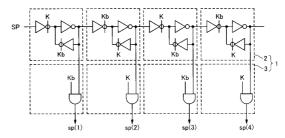

図1の列制御回路4の構成例を図3に示す。図中、MN1a~MN5a,MN1b~MN5bはn型トランジスタ、MP1a,MP1bはp型トランジスタ、C1a,C1b,C2a,C2bは容量、VCCは電源であり、点線で囲まれたgmaとgmbは同じ構成の電圧電流変換回路である。図3の列制御回路の動作において、前記列走査制御回路の出力サンプリング信号は、図2に図示しないOR回路によってブランキング信号BLが選択

10

20

30

的に論理加算される。

## [0042]

図3の構成において、MN1aはgma回路のサンプリングスイッチ、MN1bはgmb回路のサンプリングスイッチである。サンプリングスイッチMN1a,MN1bのゲートには、それぞれサンプリング信号spa(q),spb(q)が入力される。MN1a,MN1bのソース(またはドレイン)は映像信号Videoが入力される。MN1a,MN1bのドレイン(またはソース)は、それぞれgma,gmbの容量C1a,C1bの一端に接続されている。以下、gmaについて説明する。

#### [0043]

C1aの他端は、一方が接地された容量C2aの他端に接続されると同時に、ソースが接地されているMN2aのゲートに接続されている。MN2aのゲート・ドレイン間を接続するMN3aのゲートには、制御信号BLaが入力される。MN2a/DはさらにMN4a,MN5aに接続されており、MN4a/Gに入力される制御信号LDaに応じて、ダイオード接続されたMP1aを介して電源VCCとの間の経路を形成する。また、MN2a/Dは、制御信号Lbでオン・オフを制御されるMN5aを介してデータ線11に接続されている。

#### [0044]

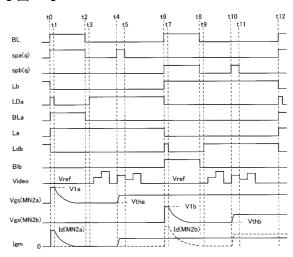

図 3 の回路の動作を図 4 のタイムチャートにより説明する。尚、トランジスタのゲート・ソース間電圧を V g s ( x )、ドレイン電流を I d ( y ) と記す ( x 、 y はトランジスタ番号)。

#### [0045]

V C C - V g s ( M P 1 a ) = V g s ( M N 2 a ) + G N D ( 1 ) の関係である、スレッシュ電圧 V t h 以上の電圧 V 1 a となる。

## [0046]

# [0047]

時刻 t 2 ~ t 3 間において、M N 1 a , M N 3 a , M N 4 a , M N 5 a はオフとなり、 V g s ( M N 2 a ) は V t h リセット動作終了の状態を保持する。

#### [0048]

時刻 t 3 ~ t 4 間において、M N 4 a はオンし、M N 1 a , M N 3 a , M N 5 a がオフであり、V g s ( M N 2 a ) は、V t h リセット動作終了の状態を保持し、ドレイン電流 I d ( M N 2 a ) = 0 である。

# [0049]

時刻 t 4 ~ t 5 間において、MN1a, MN4aはオンし、MN3a, MN5aはオフであり、映像信号 Videoの入力端子には、該当する列に表示する映像電圧信号が入力され、サンプリング動作が行われる。サンプリング動作が十分定常状態に収束した時刻 t 5 において、Vgs(MN2a)は、Video入力レベルV(Video)と、Vthリセット動作時のVideo入力レベルVrefに応じて、

# [0050]

50

40

20

30

40

50

#### 【数1】

$$Vgs (MN2a) = \{V (Video) - Vref\} \times \frac{C1a}{C1a + C2a} + Vt$$

(2)

となり、電圧 - 電流変換結果 i ( d a t a ) となる M N 2 a のドレイン電流は、 V t = V t h であるので、

#### [0051]

# 【数2】

Id (MN2a) =

$$\beta \times \frac{W}{L} \times \left[ \{ V \ (V \ i \ d \ e \ o) \ -V \ r \ e \ f \} \times \frac{C \ 1 \ a}{C \ 1 \ a + C \ 2 \ a} \right]^2$$

(3)

$= \mu \cdot C \circ x$

μ:移動度、Cox:ゲート酸化膜容量、W:ゲート幅、L:ゲート長となる。ドレイン電流 Id (MN2a)は、Vthリセット動作時のVideo入力電圧と差電圧の二乗に応じた電流に変換される。また、各列及びgma-gmbによる電圧・電流変換ばらつきは、が支配的となることが上記式(3)よりわかる。

#### [0052]

時刻 t 5 ~ t 6 間においては、時刻 t 3 ~ t 4 間と同様の状態であり、MN 2 a のドレイン電流は、時刻 t 5 の状態を保持する。

#### [0053]

時刻 t 6 ~ t 1 2 間においては、MN5 aがオンし、MN1 a , MN3 a , MN4 aがオフであり、MN2 aのドレインは、MN5 aを介して、データ線 1 1 に接続されている。この時、Id(MN2 a)は時刻 t 5 の状態を保持している。gmbは時刻 t 6 ~ t 1 2 間において、gmaの時刻 t 0 ~ t 6 と同様の動作を行う。

#### [0054]

以上の動作によって、列制御回路4においては、gma,gmbがそれぞれ相補的にサンプリングホールドを担当し、映像信号Videoを電圧-電流変換した線順次電流i(data)をデータ線11に出力する。

# [0055]

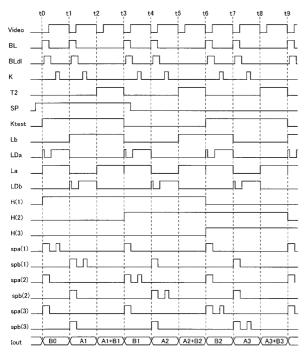

次に、制御信号Ly=Hの時の動作を図5のタイムチャートにより説明する。

#### [0056]

制御信号 L y は、外部より入力される制御信号 T 1 により制御され、 T 1 = L の時、 L y = L で、 T 1 = H の時、 L y = H である。 T 1 = H となると、シフトレジスタ 2 のクロック入力端子には、制御信号 K t e s t が入力される。

# [0057]

図 5 において、時刻 t 0 以前に、スタート信号 S P 及び制御信号 K t e s t がいずれも H となることによって、第 1 列のシフトレジスタ 2 の出力 H ( 1 ) = H となり、第 2 列目のシフトレジスタ 2 は出力 H ( 2 ) = H となるための、 K t e s t = H の入力待機状態である。

#### [0058]

時刻 t 0 ~ t 1 間において、ブランキング信号 B L = H、次いでクロック信号 K = Hが入力されると、第 1 列のサンプリング信号 s p a ( 1 ) には、ブランキング信号 B L = H入力期間に V t h リセット動作用パルス、及び、クロック信号 K = H入力期間に映像信号 V i d e o サンプリング用パルスがそれぞれ出力される。第 1 列目以外のサンプリング信号 s p a ( 2 ) ~ s p a ( n ) には、ブランキング信号 B L = H入力期間に、 V t h リセット動作用のパルスのみが出力される。

#### [0059]

時刻 t 1 ~ t 2 間において、ブランキング信号 B L = H、次いでクロック信号 K = Hが入力されると、第 1 列のサンプリング信号 s p b ( 1 ) には、ブランキング信号 B L = H入力期間に V t h リセット動作用パルス、及び、クロック信号 K = H入力期間に映像信号

#### [0060]

#### [0061]

時刻 t 3 ~ t 6 間において、 K t e s t = H が入力されると、シフトレジスタ 2 は 1 段進み、第 2 列目がアクティブとなり、 t 0 ~ t 3 間の第 1 列目の列制御回路 1 と同様の動作を、第 2 列目の列制御回路 1 が行う。具体的に説明する。

#### [0062]

時刻 t 3 ~ t 4 間において、ブランキング信号 B L = H、次いでクロック信号 K = Hが入力されると、第 2 列のサンプリング信号 s p a (2)には、ブランキング信号 B L = H入力期間に V t h リセット動作用パルス、及び、クロック信号 K = H入力期間に映像信号 V i d e o サンプリング用パルスがそれぞれ出力される。第 2 列目以外のサンプリング信号 s p a (1), s p a (3) ~ s p a (n)には、ブランキング信号 B L = H入力期間に、V t h リセット動作用のパルスのみが出力される。

#### [0063]

また、当該期間には、時刻 t 1 ~ t 2 間に g m b によりサンプリングされた第 1 列目の線順次電流 i ( d a t a ) 、及び、第 2 列目 ~ 第 n 列目の g m b の V t h リセット電流 (ゼロ電流)の総和電流が共通出力線 1 3 に出力されている。

# [0064]

時刻 t 4 ~ t 5 間において、ブランキング信号 B L = H、次いでクロック信号 K = Hが入力されると、第 2 列のサンプリング信号 s p b (2)には、ブランキング信号 B L = H入力期間に V t h リセット動作用パルス、及び、クロック信号 K = H入力期間に映像信号 V i d e o サンプリング用パルスがそれぞれ出力される。第 2 列目以外のサンプリング信号 s p b (1), s p b (3) ~ s p b (n)には、ブランキング信号 B L = H入力期間に、V t h リセット動作用のパルスのみが出力される。

# [0065]

また、当該期間には、時刻 t 3 ~ t 4 間に g m a によりサンプリングされた第 2 列目の線順次電流 i ( d a t a)、及び、第 1 列目と第 3 列目 ~ 第 n 列目の g m a の V t h リセット電流(ゼロ電流)の総和電流が共通出力線 1 3 に出力されている。

#### [0066]

# [0067]

50

10

20

30

20

30

40

50

時刻 t 6 以降は、対象列を順次、第3列、第4列と、クロック信号Kの立ち上がり、立ち下がりに応じて進めながら、時刻 t 0 からの動作を繰り返す。

#### [0068]

以上の動作により、図5のIoutに示されるように、順次、

第1列目のgma出力電流と、他の列のgmaのVthリセット電流の総和電流

第1列目のgma,gmb出力電流と、他の列のgma,gmbのVthリセット電流の総和電流

第1列目のgmb出力電流と、他の列のgmbのVthリセット電流の総和電流

第2列目のgma出力電流と、他の列のgmaのVthリセット電流の総和電流

第2列目のgma,gmb出力電流と、他の列のgma,gmbのVthリセット電流の総和電流

第2列目のgmb出力電流と、他の列のgmbのVthリセット電流の総和電流

第3列目のgma出力電流と、他の列のgmaのVthリセット電流の総和電流

第3列目のgma,gmb出力電流と、他の列のgma,gmbのVthリセット電流の総和電流

第3列目のgmb出力電流と、他の列のgmbのVthリセット電流の総和電流と、各タイミングにおいて列走査制御回路1の出力によって選択された列制御回路1の電圧・電流変換出力i(data)を、他の列のVthリセット電流との総和電流として共通出力線13に出力することができ、Vthリセット電流は、理想的にはゼロであるため、総和電流は1列ごとの電圧・電流変換出力を示すことになる。

#### [0069]

また、通常、表示パネルには、R(赤)、G(緑)、B(青)の3色に相当する例えば3本の映像信号Videoが入力される。上記説明において、RGB3本の映像信号Videoに有効レベルを入力すれば、gma,gmbの和電流を出力するタイミング(例えば、図5のt2~t3間)では、gma,gmbのRGB分の計6回路分の電圧・電流変換出力i(data)を取り出すことができ、画素回路8に供給されるべき電流信号i(data)の6倍の電流をパネル外部に出力することにより、外部の容量性負荷のドライブ能力も6倍にでき、検出時間を短縮することができる。必要に応じて、例えばRGB3本の映像信号Videoのうち、1本のみ有効レベルを印加し、他の2本には、Vthリセット時の印加電圧を与えておけば、有効レベルを印加した系の列制御回路の出力のみを評価することもできる。

# [0070]

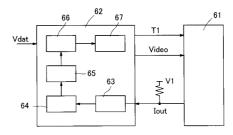

図 6 に、本発明の表示装置における列毎の電流信号のばらつきの補正のシステムを示す。図中、 6 1 は表示パネル、 6 2 は外部制御部、 6 3 は A / D コンバータ、 6 4 , 6 6 は 演算回路、 6 5 はメモリ、 6 7 は D A C である。

#### [0071]

図6において、図5で説明したタイミング及び動作によって、制御信号T1=Hにおいて、各列に同一レベルの映像信号Videoを入力したときの各列制御回路4の出力電流 i(data)をIoutに出力させることができる。Ioutに出力された総和電流を、例えば抵抗によって電圧変換し、外部制御部62に取り込み、演算回路64において各列の電流値のばらつきを検出し、表示パネル61における電流値が均一になるような映像信号Videoに対する補正係数を算出し、各列補正係数をメモリ65に格納する。補正係数は例えば、各列の電流値が検出した総和電流の最小値となるように、電流値が大きい列の映像信号Videoを圧縮する係数を演算する。制御信号T1=Lにおける通常の表示駆動において、外部制御部62に入力されるデジタル映像信号Vdatは、メモリ65に格納された各列の補正係数に応じて演算回路66において圧縮され、DAC67によってD/A変換されたアナログの映像信号Videoが表示パネル61に出力される。

#### [0072]

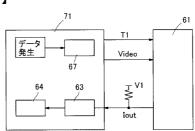

図 7 に、本発明の表示装置の製造時における列制御回路の検査システムを示す。図中、7 1 は検査装置であり、図 6 と同じ部材には同じ符号を付した。

#### [0073]

図7において、図5で説明したタイミング及び動作によって、制御信号T1=Hにおい て、各列に同一レベルの映像信号Videoを入力したときの各列制御回路4の出力電流 i(data)をIoutに出力させることができる。Ioutに出力された総和電流を 、例えば抵抗によって電圧変換し、検査装置71に取り込み、演算回路64において各列 の電流値を検出し、前列の検出値の最大値、最小値、平均値を演算し、これらの値の比較 によって、列制御回路の良否を判定する。例えば、任意の列のRGB及びgma,gmb の6回路分の電流信号と、その他の列のVthリセット電流の総和電流を検出する場合、 (該当列の検出値/平均値) < (5/6)の場合を不合格とする、(最大値/最小値) < ( 6 / 5 )で不合格とする、或いは、 8 0 % < (第 q 列目の検出値 / 第 q + 1 列目の検出 値)<120%以外を不合格とする、などである。判定基準は、各列の検出値、及び最大 値、最小値、平均値によって様々に設定することができる。列制御回路4の6回路分以下 の電流を検出する場合でも、第q列目の検出において、1列分のサンプリング信号を出力 すればよいので、全列分のサンプリング信号を出力させて、該当列以外のゼロ電流をサン プリングし、該当列及び電圧・電流結果を検出することに比べると、サンプリングに必要 な 時 間 は 、 例 え ば 3 2 0 列 の 表 示 パ ネ ル で は 、 1 / 3 2 0 と な る 。 検 出 時 間 は 、 例 え ば 列 制御回路の2回路分のサンプリング期間と列制御回路の総和電流の出力期間の和となる。 従って、従来におけるサンプリング期間と総和電流の出力期間を同じとすると、本発明に よればサンプリング期間が1/320となりほぼ無視できるため、検出時間を約1/3と することができる。

[0074]

図 8 に、本発明の表示装置を用いたデジタルビデオカメラ或いはデジタルスチルカメラの構成例を示す。図中 8 0 はシステム全体、 8 1 は撮影部、 8 2 は映像信号処理部、 8 3 は表示パネル、 8 5 はメモリ、 8 6 は C P U 、 8 7 は操作部である。

#### [0075]

図8のシステムにおいては、撮影部81で撮影した映像またはメモリ85に記憶された映像を、映像信号処理部82で信号処理し、表示パネル83で見ることができる。CPU86では、操作部87からの入力によって、撮影部81、メモリ85、映像信号処理部86などを制御して、状況に適した撮影、記録、再生、表示を行う。映像信号処理部82~表示パネル83間において、Ioutによる列電流の総和電流検出及び補正を行い、良好な画像を表示する。総和電流の検出(第2の期間)は、電源起動時または、垂直プランキング期間など、画面に画像を表示しない期間に行う。

[0076]

上記本発明の説明においては、画素回路がEL素子を備えたEL表示装置を例に挙げて述べたが、本発明の表示装置はこれに限定されるものではなく、電流プログラミング方式の表示装置であれば、好ましく適用される。

【図面の簡単な説明】

[0077]

- 【図1】本発明の表示装置の一実施形態のEL表示パネルの構成を示す図である。

- 【 図 2 】 図 1 の 表 示 パ ネ ル の 列 走 査 制 御 回 路 の 構 成 例 を 示 す 図 で あ る 。

- 【図3】図1の表示パネルの列制御回路の構成例を示す図である。

- 【図4】図3の回路の動作のタイムチャートである。

- 【図5】図1,図3の回路の動作のタイムチャートである。

- 【 図 6 】 本 発 明 の 表 示 装 置 に お け る 列 毎 の 電 流 信 号 の ば ら つ き の 補 正 の シ ス テ ム を 示 す 図 で あ る 。

- 【 図 7 】 本 発 明 の 表 示 装 置 の 製 造 時 に お け る 列 制 御 回 路 の 検 査 シ ス テ ム を 示 す 図 で あ る 。

- 【図8】本発明の表示装置を用いたデジタルビデオカメラ或いはデジタルスチルカメラの 構成例を示す図である。

- 【図9】従来の電流駆動型 E L 表示装置の表示パネルの構成例を示す図である。

- 【図10】図9の表示パネルの列走査制御回路の構成例を示す図である。

20

30

40

```

【図11】図9の表示パネルの列制御回路の構成例を示す図である。

【図12】図11の列制御回路の動作のタイムチャートである。

【図13】図11の列制御回路中の電圧電流変換回路の構成例を示す図である。

【図14】図13の電圧電流変換回路の電圧・電流変換特性を示す図である。

【図15】図9の表示パネルの画素回路8の構成例を示す図である。

【図16】図15の画素回路の動作のタイムチャートである。

【符号の説明】

[0078]

1

列走查制御回路

シフトレジスタ

10

ゲート回路群

列制御回路

4

5,7 スイッチ

6

表示部

8

画素回路

タイミング制御回路

行 走 査 制 御 回 路

1 0

1 1

データ線

1 2 走査線

13 共通出力線

20

6 1

表示パネル

62 外部制御回路

6 3 A / D コンバータ

6 4 , 6 6 演算回路

メモリ

6 5

6 7

DAC

7 1

検査装置

8 0

システム

8 1

撮影部

82 映像信号処理回路

30

8 3

表示パネル

8 5

メモリ

CPU

8 6

8 7 操作部

1 1 1 電圧電流変換回路

151 EL素子

BL ブランキング信号

BLa、BLb 制御信号

C 1 ~ C 4 , C 1 a , C 2 a , C 1 b , C 2 b 容量

K、Kb クロック信号

40

gma,gmb 電圧電流変換回路

i (data)

電流信号

Iout 共通出力線出力

Ktest 制御信号

LDa, LDb

制御信号

Lx,Ly 制御信号

La, Lb 制御信号

M1~M8, MN1a~MN5a, MN1b~MN5b, MP1a, MP1b トラン

```

ジスタ

P1(r)、P2(r) 走査信号

REF 基準電圧信号

SP スタート信号

sp、spa(q)、spb(q) サンプリング信号

T 1 , T 2 制御信号,

VB 基準電流設定バイアス

VCC 電源線

【図1】

Vdat デジタル映像信号

Video 映像信号

# Lx Lb LDa BLa La LDb BLb P2(1) P1(1)

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

# 【図9】

# 【図10】

【図11】

【図12】

【図14】

【図13】

【図15】

# 【図16】

# フロントページの続き

| (51) Int.CI. <sup>7</sup> | FΙ            |         | テーマコード(参考) |

|---------------------------|---------------|---------|------------|

|                           | G 0 9 G 3/20  | 6 2 3 R |            |

|                           | G 0 9 G 3/20  | 6 2 4 B |            |

|                           | G 0 9 G 3/20  | 6 4 1 D |            |

|                           | G 0 9 G 3/20  | 6 7 0 Q |            |

|                           | H 0 5 B 33/14 | Α       |            |

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|

| 公开(公告)号        | <u>JP2005173420A</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2005-06-30 |  |  |

| 申请号            | JP2003415889                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2003-12-15 |  |  |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |  |  |

| 申请(专利权)人(译)    | 佳能公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |  |  |

| [标]发明人         | 井関正己川野藤雄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |

| 发明人            | 井関 正己<br>川野 藤雄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |  |  |

| FI分类号          | G09G3/30.J G09G3/30.K G09G3/20.611.H G09G3/20.622.A G09G3/20.623.A G09G3/20.623.R G09G3 /20.624.B G09G3/20.641.D G09G3/20.670.Q H05B33/14.A G09G3/325 G09G3/3266 G09G3/3275 G09G3/3283                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |  |  |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 5C080/AA06 5C080/BB05 5C080/DD05 5C080 /EE28 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 3K107/AA01 3K107/BB01 3K107 /CC31 3K107/CC45 3K107/EE03 3K107/GG56 5C380/AA01 5C380/AA02 5C380/AB06 5C380/AB34 5C380/AC09 5C380/BA28 5C380/BA38 5C380/BA39 5C380/BB02 5C380/BB03 5C380/BB04 5C380 /CA02 5C380/CA05 5C380/CA08 5C380/CA13 5C380/CA23 5C380/CA24 5C380/CA29 5C380/CA30 5C380/CA51 5C380/CA52 5C380/CA54 5C380/CA57 5C380/CB01 5C380/CB16 5C380/CB17 5C380 /CC13 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC53 5C380/CC63 5C380/CD014 5C380/CE11 5C380/CE19 5C380/CF01 5C380/CF07 5C380/CF10 5C380/CF17 5C380/CF23 5C380/CF26 5C380 /CF28 5C380/CF31 5C380/CF32 5C380/CF33 5C380/CF43 5C380/CF48 5C380/CF49 5C380/CF51 5C380/CF62 5C380/DA02 5C380/DA06 5C380/DA47 5C380/FA03 5C380/FA18 5C380/FA28 5C380 /GA04 5C380/GA05 5C380/HA13 |         |            |  |  |

| 代理人(译)         | 渡边圭佑<br>山口 芳広                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |  |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |  |  |

# 摘要(译)

解决的问题:为了有效地检测从电流驱动型EL显示装置中的列控制电路输出的电流信号的变化。 在像素电路8和列控制电路4之间设置有开关5,并且通过切换开关5将从列控制电路4输出的电流信号作为总电流lout输出到公共输出线13的结构。 在列扫描控制电路1中,通过独立地控制移位寄存器2的进程和来自门电路3的采样信号的输出定时,由列控制电路4仅执行预定采样以进行检查。 输入信号并执行采样以检测电流信号。 [选型图]图1