(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-145296

(P2004-145296A)

(43) 公開日 平成16年5月20日(2004.5.20)

| (51) Int.Cl. <sup>7</sup> |              | F 1  |      |      | テーマコード (参考) |

|---------------------------|--------------|------|------|------|-------------|

| <b>G09G</b>               | <b>3/30</b>  | GO9G | 3/30 | J    | 3K007       |

| <b>G09G</b>               | <b>3/20</b>  | GO9G | 3/20 | 611H | 5C058       |

| <b>H04N</b>               | <b>5/70</b>  | GO9G | 3/20 | 623L | 5C080       |

| <b>H05B</b>               | <b>33/14</b> | GO9G | 3/20 | 624B |             |

|                           |              | GO9G | 3/20 | 641D |             |

審査請求 未請求 請求項の数 17 O L (全 26 頁) 最終頁に続く

|              |                              |            |                                                                            |

|--------------|------------------------------|------------|----------------------------------------------------------------------------|

| (21) 出願番号    | 特願2003-305081 (P2003-305081) | (71) 出願人   | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号                                 |

| (22) 出願日     | 平成15年8月28日 (2003.8.28)       | (74) 代理人   | 100096828<br>弁理士 渡辺 敏介                                                     |

| (31) 優先権主張番号 | 特願2002-256432 (P2002-256432) | (74) 代理人   | 100110870<br>弁理士 山口 芳広                                                     |

| (32) 優先日     | 平成14年9月2日 (2002.9.2)         | (72) 発明者   | 川崎 素明<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内                                   |

| (33) 優先権主張国  | 日本国 (JP)                     | (72) 発明者   | 井関 正己<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内                                   |

|              |                              | F ターム (参考) | 3K007 AB03 AB17 BA06 DB03 GA00<br>5C058 AA12 BA04 BA06 BA33 BB06<br>最終頁に続く |

(54) 【発明の名称】電流信号出力回路および該電流信号出力回路を用いた表示装置及び情報表示装置

(57) 【要約】 (修正有)

【課題】 ばらつきを抑制した出力を得られる電流信号出力回路を実現する。

【解決手段】 電流信号制御回路は第1から第6のスイッチ、第1、2の容量素子、第1、2のトランジスタを備え、第1スイッチの第1、2端子は夫々電圧信号線と第1容量素子の第1端子に、第1容量素子の第2端子は第1トランジスタのゲート電極に、第3スイッチの第1、2端子は夫々第1トランジスタのゲート電極と第2主電極に、第1トランジスタの第1、2主電極は夫々第1電源と第4スイッチの第1端子に、第2スイッチの第1、2端子は夫々電圧信号線と第2容量素子の第1端子に、第2容量素子の第2端子は第2トランジスタのゲート電極に、第5スイッチの第1、2端子は夫々第2トランジスタのゲート電極と第2主電極に、第2トランジスタの第1、2主電極は夫々第1電源と第6スイッチの第1端子に接続され、第1から第6スイッチを制御し、第4、6スイッチから電流を出力する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

入力される電圧信号に応じて電流信号を出力する電流信号出力回路であって、

電流信号制御回路を有しており、

該電流信号制御回路は、

少なくとも、第1から第6のスイッチと、第1、第2の容量素子と、第1、第2のトランジスタとを備えており、

第1のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第1のスイッチの第2端子は第1の容量素子の第1端子に接続され、

第1の容量素子の第2端子は第1のトランジスタのゲート電極に接続され、

第3のスイッチの第1端子と第2端子とは第1のトランジスタのゲート電極と第2主電極とに夫々接続され、

第1のトランジスタの第1主電極は第1の電源に接続され、

第1のトランジスタの第2主電極は第4のスイッチの第1端子に接続され、

第2のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第2のスイッチの第2端子は第2の容量素子の第1端子に接続され、

第2の容量素子の第2端子は第2のトランジスタのゲート電極に接続され、

第5のスイッチの第1端子と第2端子とは第2のトランジスタのゲート電極と第2主電極とに夫々接続され、

第2のトランジスタの第1主電極は第1の電源に接続され、

第2のトランジスタの第2主電極は第6のスイッチの第1端子に接続され、

第4及び第6のスイッチの第2端子は互いに接続されて前記電流信号を出力する電流信号出力端子とされ、

第1から第6のスイッチの制御端子は、夫々第1から第6の制御信号線に接続されていることを特徴とする電流信号出力回路。

**【請求項 2】**

入力される電圧信号に応じて電流信号を出力する電流信号出力回路であって、

電流信号制御回路を有しており、

該電流信号制御回路は、

少なくとも、第1から第8のスイッチと、第1、第2の容量素子と、第1から第4のトランジスタとを備えており、

第1のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第1のスイッチの第2端子は第1の容量素子の第1端子に接続され、

第1の容量素子の第2端子は第1のトランジスタのゲート電極に接続され、

第3のスイッチの第1端子と第2端子とは第1のトランジスタのゲート電極と第2主電極とに夫々接続され、

第1のトランジスタの第1主電極は第1の電源に接続され、

第1のトランジスタの第2主電極は第4のスイッチの第1端子と第7のスイッチの第1端子とに接続され、

第7のスイッチの第2端子は第3のトランジスタの第1主電極に接続され、

第3のトランジスタはゲート電極と第1主電極又は第2主電極とが短絡されており且つ第2主電極は第2の電源に接続され、

第2のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第2のスイッチの第2端子は第2の容量素子の第1端子に接続され、

第2の容量素子の第2端子は第2のトランジスタのゲート電極に接続され、

第5のスイッチの第1端子と第2端子とは第2のトランジスタのゲート電極と第2主電極とに夫々接続され、

第2のトランジスタの第1主電極は第1の電源に接続され、

第2のトランジスタの第2主電極は第6のスイッチの第1端子と第8のスイッチの第1端子とに接続され、

10

20

30

40

50

第8のスイッチの第2端子は第4のトランジスタの第1主電極に接続され、

第4のトランジスタはゲート電極と第1主電極又は第2主電極とが短絡されており且つ

第2主電極は第2の電源に接続され、

第4及び第6のスイッチの第2端子は互いに接続されて外部に前記電流信号を出力する

電流信号出力端子とされ、

第1から第8のスイッチの制御端子は、夫々第1から第8の制御信号線に接続されてい

ることを特徴とする電流信号出力回路。

【請求項3】

第3のスイッチと第7のスイッチの双方が導通する期間を設ける及び／又は第5のスイッ

チと第8のスイッチの双方が導通する期間を設けたことを特徴とする請求項2に記載の電

流信号出力回路。 10

【請求項4】

入力される電圧信号に応じて電流信号を出力する電流信号出力回路であって、

電流信号制御回路を有しており、

該電流信号制御回路は、

少なくとも、第1及び第3のスイッチと、第1の容量素子と、第1のトランジスタとを

備えており、

第1のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第1のスイッチ

の第2端子は第1の容量素子の第1端子に接続され、

第1の容量素子の第2端子は第1のトランジスタのゲート電極に接続され、 20

第3のスイッチの第1端子と第2端子とは第1のトランジスタのゲート電極と第2主電

極とに夫々接続され、

第1のトランジスタの第1主電極は第1の電源に接続されていることを特徴とする電流

信号出力回路。

【請求項5】

前記第3のスイッチを介して第1のトランジスタのゲート電極を充電した後、第1のトラン

ジスタのゲート電極の電圧が閾値電圧に近づくように放電させてから、前記第1のスイッ

チに与えられる電圧信号に応じた電圧に第1のトランジスタのゲート電極を充電し、該充

電された状態に応じた電流信号を前記第1のトランジスタの第2主電極から電流信号を

出力する請求項4に記載の電流信号出力回路。 30

【請求項6】

入力される電圧信号に応じて電流信号を出力する電流信号出力回路であって、

電流信号制御回路を有しており、

該電流信号制御回路は、

少なくとも、第1のスイッチと、第1の容量素子と、第1のトランジスタとを備えてお

り、

第1のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第1のスイッチ

の第2端子は第1の容量素子の第1端子に接続され、

第1の容量素子の第2端子は第1のトランジスタのゲート電極に接続され、

第1のトランジスタの第1主電極は第1の電源に接続されていることを特徴とする電流

信号出力回路。 40

【請求項7】

前記第1のトランジスタのゲート電極の電圧が閾値電圧に近づくように放電させてから、

前記第1のスイッチに与えられる電圧信号に応じた電圧に第1のトランジスタのゲート電

極を充電し、該充電された状態に応じた電流信号を前記第1のトランジスタの第2主電極

から出力する請求項6に記載の電流信号出力回路。

【請求項8】

第1のスイッチに与えられる電圧信号が基準レベルになっている期間において、前記第1

のトランジスタのゲート電極の電圧が閾値電圧に近づくように放電させることを特徴とす

る請求項5もしくは7に記載の電流信号出力回路。 50

**【請求項 9】**

請求項 4 から 8 のいずれかに記載の電流信号制御回路を少なくとも 2 つ有しており、一方の電流信号制御回路において前記電流信号を出力しているときに、他方の電流信号制御回路において第 1 のトランジスタのゲート電極を電圧信号に応じた電圧に充電することを特徴とする電流信号出力回路。

**【請求項 10】**

請求項 1 から 9 のいずれかに記載の電流信号出力回路と、複数の表示素子とを備えており、前記電流信号出力回路が複数の前記表示素子に対して順次前記電流信号を供給することを特徴とする表示装置。

**【請求項 11】**

請求項 9 に記載の電流信号出力回路と、複数の表示素子とを備えており、前記電流信号出力回路が複数の前記表示素子に対して順次前記電流信号を供給するように構成されており、前記電流信号出力回路を構成する少なくとも 2 つの電流信号制御回路と前記複数の表示素子それぞれとの対応関係が非固定的に制御されることを特徴とする表示装置。

**【請求項 12】**

前記電流信号出力回路と、該電流信号出力回路が順次電流信号を供給する複数の表示素子とからなる組を複数備えており、各組に属する表示素子によって表示素子のマトリックスが構成されており、前記電流信号出力回路は該マトリックスの列方向の制御を行うものであり、更に該マトリックスの行方向の制御を行う行制御回路を有する請求項 10 もしくは 11 に記載の表示装置。

**【請求項 13】**

請求項 1 から 3 のいずれかに記載の電流信号出力回路を備えており、該電流信号出力信号からの信号の供給を受ける表示素子を 2 次元の領域に複数配置した表示装置であって、

第 4 及び第 6 のスイッチを選択的に動作させる機能を有し、表示する映像信号のフレームによって第 4 及び第 6 のスイッチの動作を奇数行または偶数行で変更したことを特徴とする表示装置。

**【請求項 14】**

請求項 1 乃至 10 のいずれかに記載の電流信号出力回路を複数備えており、該電流信号出力回路から信号の供給を受けてそれぞれ異なる色の光を出力する複数の表示素子とを備えた表示装置において、

電圧信号として 3 色の映像信号群が少なくとも入力されるものであり、3 つの電流信号制御回路を一組とし、該一組の電流信号制御回路から出力される各色の映像信号に対応する電流信号を、映像信号フレーム単位で前記一組の電流信号制御回路に含まれる 3 つの電流信号制御回路間で切り替えて出力させる表示装置。

**【請求項 15】**

前記表示素子が、エレクトロルミネセンス素子を少なくとも含む請求項 10 から 14 のいずれかに記載の表示装置。

**【請求項 16】**

前記表示素子が画素回路を有しており、該画素回路は前記電流信号出力回路からの信号に對応した電圧値を保持し、該保持した電圧値に応じた電流値を出力するものである請求項 10 から 15 のいずれかに記載の表示装置。

**【請求項 17】**

情報表示装置であって、情報入力部と、該情報入力部に入力される情報に基づいて表示を行う請求項 10 から 16 のいずれかに記載の表示装置とを有する情報表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、電流信号を出力する電流信号出力回路に関する。また該電流信号出力回路を用いた表示装置に関する。

**【背景技術】**

10

20

30

40

50

## 【0002】

従来から種々の表示装置が知られている。表示装置の一例としてエレクトロルミネセンス素子を用いた表示装置がある。その例が、特許文献1に記載されている。

## 【0003】

## 【特許文献1】米国特許第6373454号明細書

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0004】

本発明者は、表示装置の構成として種々の構成を検討してきた。

## 【0005】

以下にエレクトロルミネセンス素子を用いた表示装置として検討してきた構成を説明する。

## 【0006】

エレクトロルミネセンス(EL)素子は一般にTFTで構成された画素表示回路を2次元に配列したパネル型画像表示システム(以後ELパネルと言う)等に応用されている。このEL素子の発光設定方式としては電圧設定方式と電流設定方式とを挙げることができる。

## 【0007】

## &lt;電圧設定方式によるELパネル&gt;

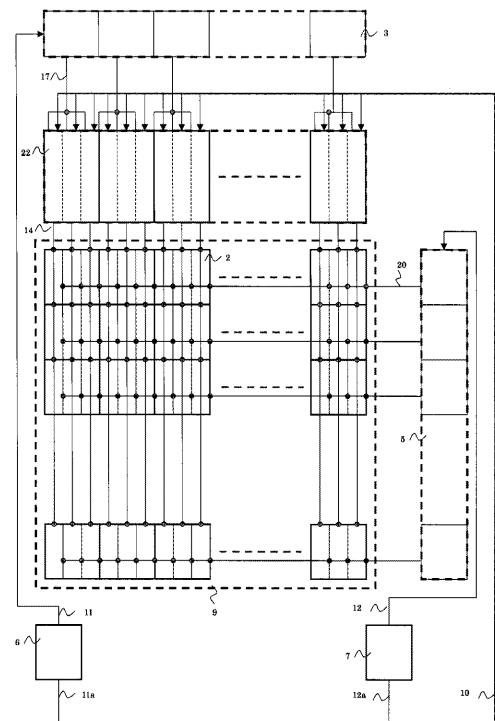

電圧設定方式によるカラー化したELパネルの回路構成を図12に示す。

10

20

## 【0008】

入力映像信号10は、赤、緑、青(RGB)各色ごとに設けられたELパネルの水平画素数の3倍数設けられた列制御回路22に適宜入力される。また、水平走査制御信号11aは入力回路6に入力され水平走査制御信号11を出力し、該水平走査制御信号11は水平画素数のレジスタからなる水平シフトレジスタ3に入力される。水平走査制御信号11は水平クロック信号と水平走査開始信号からなる。そして水平シフトレジスタ3の各端子から出力される水平サンプリング信号群17は各々が受け持つ列制御回路22に入力される。

## 【0009】

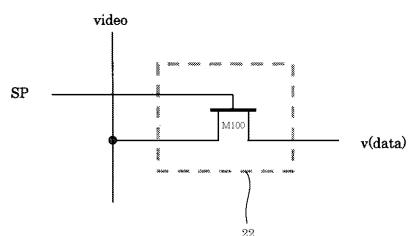

列制御回路22の構成は、図14に示す様に水平サンプリング信号SPがM100/Gに接続され、M100/Sに入力映像信号video(ここではRGBの1つ)が接続され、M100/Dに列制御信号14である映像電圧データv(data)を出力する非常に簡単な構成である。

30

## 【0010】

尚、本明細書中においては説明の便宜上、トランジスタのゲート電極、ソース電極、ドレイン電極をそれぞれ/G、/S、/Dの略号にて示し、また信号とそれを供給する信号線とを区別せずに表現する。

## 【0011】

画像表示領域9には各々同等の構成を有する画素回路2が2次元に配置され、各々RGBのEL表示素子の駆動を受け持ち、3個対の画素回路2で1画素の表示を受け持つことになる。

40

## 【0012】

列制御回路22から出力される映像電圧データv(data)は、同じ列に配置された画素回路2群に入力される。また、垂直走査制御信号12aは入力回路7を介して垂直走査制御信号12を出力し、該垂直走査制御信号12はELパネルの垂直画素数に等しいレジスタを含む垂直シフトレジスタ5に入力される。この垂直走査制御信号12は垂直クロック信号と垂直走査開始信号からなる。そして垂直シフトレジスタの各出力端子から出力される行制御信号20は、同じ行に配置されている画素回路2に入力される。

## 【0013】

[電圧設定方式の画素回路]

50

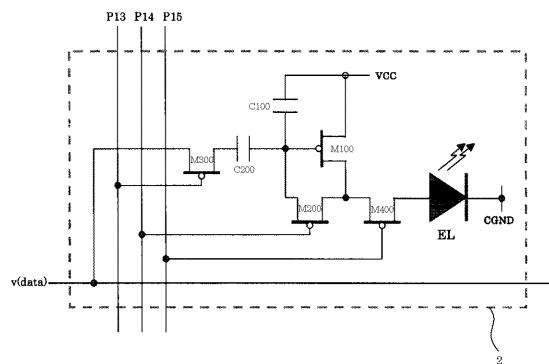

電圧設定方式の画素回路2の構成を図13に示す。

【0014】

電圧データ $v$ (data)はM300/Sに接続される。また、行制御信号P13、P14、P15に対応し、各々M300/G、M200/G、M400/Gに接続される。M300/Dは容量C200に接続され、容量C200はソースが電源に接続されたM100/Gと容量C100に接続される。そしてM100/DとM100/Gは各々M200/DとM200/Sに接続され、M100/DはM400/Sに接続されM400/Dは一端が接地されたEL素子の電流注入端子に接続される。

【0015】

次に図12のELパネルの動作について図15のタイムチャートを使用して説明する。

(a)は入力映像信号videoを示し、(b)は水平サンプリング信号SP、(c)～(e)は該当行の行制御信号P13～P15を示す。尚、図15では3水平期間、つまり3行期間を示している。

【0016】

まず入力映像信号の水平プランキング期間内の時間t1～t2において各水平サンプリングパルスSPは一斉にHレベルに変化し、このとき入力映像信号であるプランキング電圧が列制御信号14とされる。尚、図15(b)のSPにおいては、該当列の水平サンプリング信号を太線で示している。

【0017】

時刻t5以前(発光保持期間)

時間t1～t5において該当行の画素回路2の行制御信号P13～P15は、各々Hレベル、Hレベル、Lレベルになっており、時間t1～t2において各水平サンプリングパルスSPが一斉にHレベルに変化しても、該当画素回路2のM200、M300、M400が各々OFF、OFF、ONのままであるので、容量C100及びM100のゲート容量の保持電圧である該当画素回路2のM100/G電圧によって決定されるM100のドレイン電流が該当EL素子に注入され発光を継続している。尚、水平プランキング期間内の時間t1～t2においては、入力映像信号video電圧は図15に示すように黒レベル近傍の電圧Vb1である。

【0018】

時刻t5～t9(発光設定期間)

時刻t5において、該当行の行制御信号P13及びP15はLレベル及びHレベルに変化する。時間t5～t6において、再び各水平サンプリングパルスSPは一斉にHレベルに変化するとともに、このとき入力映像信号であるプランキング電圧が列制御信号14とされる。

【0019】

このとき、該当行の図13に示す画素回路2において、M400はOFFして該当EL素子への電流供給は無くなるため該当EL素子は消灯する。またM200及びM300は各々ON及びON状態になっているので(VCC-M100/G)電圧がM100の閾電圧Vthに漸近するように容量C100、C200及びM100のゲート容量は放電動作するため、M100のドレイン電流は非常に小さい値にリセットされる。尚、水平プランキング期間内の時間t5～t6においても、入力映像信号video電圧は図15に示すようにt1～t2と同様に黒レベル近傍の電圧Vb1である。

【0020】

時刻t6において、SP及びP14は各々Lレベル及びHレベルになるが、該当画素回路2の(VCC-M100/G)電圧は引き続きM100の閾電圧Vthである。

【0021】

時間t7～t8において該当列のSPがHレベルになり、この時の入力映像信号値d2がv(data)として該当画素回路2に入力される。このとき該当画素回路2のM100/G電圧は電圧Vだけ電圧変化する。電圧Vは概略(1)式に示される。

【0022】

10

20

30

40

50

$$V = -d_2 \times C_{200} \div (C_{200} + C_{100} + C_{(M100)}) \quad \dots \quad (1)$$

【0023】

ここで、 $C_{(M100)}$ は該当画素回路2内のM100のゲート入力容量を示している。

【0024】

時刻t8において再びSPはLレベルに変化して(1)式で示されるM100/G電圧の変化は保持され、時刻t9までこの状態を保持する。

【0025】

時刻t9以降(発光保持期間)

時刻t9において、P13及びP15は再びHレベル及びLレベルに変化して、該当画素回路2のM300及びM400はOFF及びON状態になる。こうして変化した該当画素回路のM100/G電圧によって決定されるM100のドレイン電流が該当EL素子に注入され、発光量の変化が起り、この状態が保持される。10

【0026】

時間t9~t10及び時間t11~t12において該当のSP信号はHレベルに変化するが、該当画素回路2のM300がOFFであるので該当EL素子の発光動作に影響はない。

【0027】

(1)式は、発光量が入力映像信号videoの水平プランキング期間中のVb1を基準とした電圧値(d2)によって設定できることを意味している。画素回路2のM100のドレイン電流Idは、(2)式によって概略示すことができる。20

【0028】

$$I_d = \times V^2 \quad \dots \quad (2)$$

【0029】

EL素子は基本的に注入電流に比例した発光動作をするので、図12で示した電圧設定方式のELパネルにおいて、各画素のEL素子の発光量はプランキング電圧を基準とした入力映像信号レベルの2乗に比例した値で制御可能であることが(2)式より分かる。電圧設定方式のELパネルは、画素回路2を除くと実績のある液晶パネルの回路構成を流用できる。

【0030】

<電流設定方式によるELパネル>

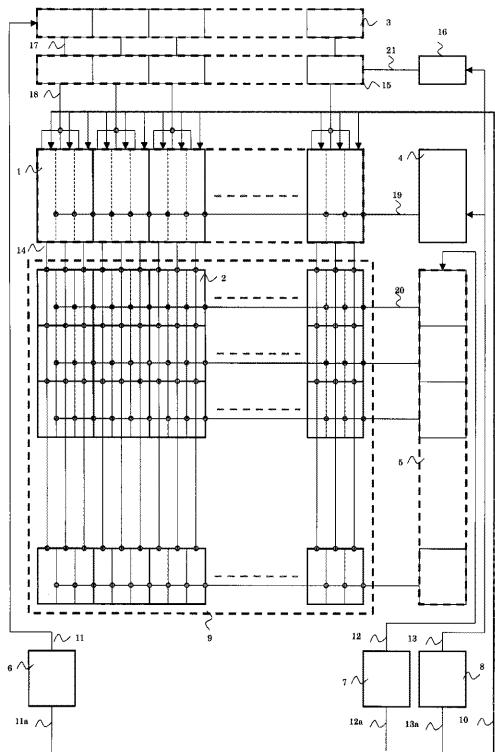

電流設定方式によるカラー化したELパネルの回路構成を図3に示す。まず、図12の電圧設定方式によるELパネルとの違いについて説明する。

【0031】

補助列制御信号13aは入力回路8を介して補助列制御信号13を出力し、該補助列制御信号13はゲート回路4及び16に入力される。また、水平シフトレジスタ3の各端子に出力される水平サンプリング信号群17はゲート回路15に入力され、変換された水平サンプリング信号群18が列制御回路1に入力される。ゲート回路15にはゲート回路16から出力される制御信号21が入力される。列制御回路1にはゲート回路4から出力される制御信号19が入力される。40

【0032】

[列制御回路]

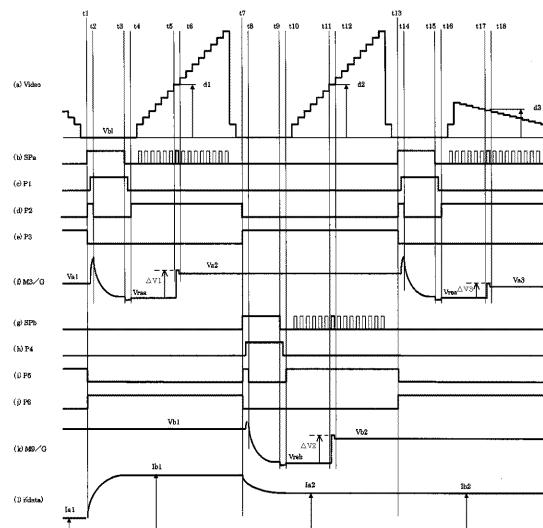

電流設定方式のELパネルの水平画素数と同数配列される列制御回路1の構成を図8に示す。

【0033】

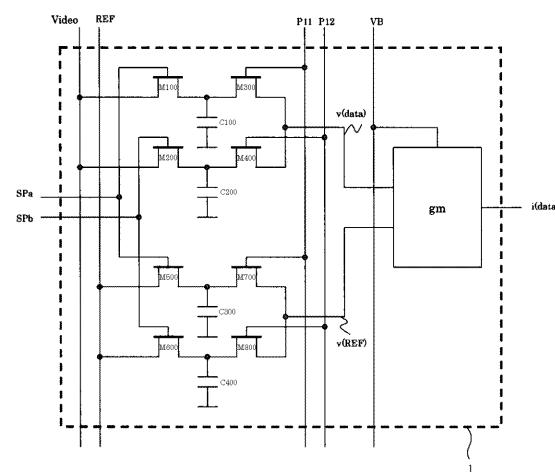

入力映像情報は入力映像信号video及び基準信号REFであり、各々M100/S、M200/S及びM500/S、M600/Sに入力される。また、ゲート回路15より出力される水平サンプリング信号群18は各々SPa及びSPbからなり、列制御回路1のM100/G、M500/G及びM200/G、M600/Gに接続される。そしてM100/D、M200/D、M500/D及びM600/Dには各々容量C100、C50

200、C300及びC400が接続されるとともに、M300/S、M400/S、M700/S、及びM800/Sが接続される。制御信号19はP11及びP12であり各々M300/G、M700/G及びM400/G、M800/Gに接続される。M300/DとM400/D及びM700/DとM800/Dは各々接続されてv(data)及びv(REF)として電圧電流変換回路gmに入力される。また、電圧電流変換回路gmには基準電流設定バイアスVBが入力され列制御信号14として使用される電流信号i(data)を出力する。

#### 【0034】

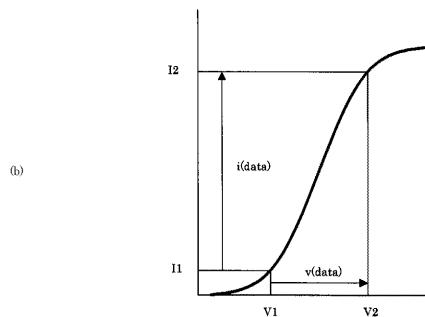

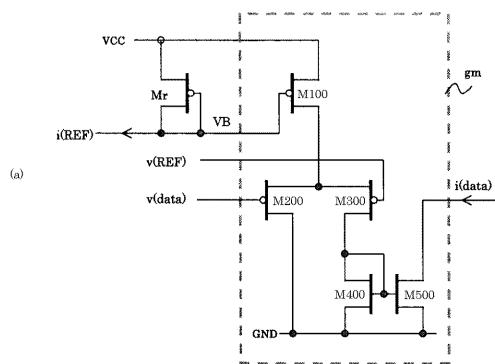

電圧電流変換回路の構成例を図10(a)に示す。基本的動作は一般的なので説明は省くが、留意点としては省電力を目指すELパネルにおいて例えば200ppiELパネルを想定すると、各画素のEL素子への注入電流が小さく、最大電流で $1\mu A$ を大きく下回り $100nA$ を想定していることである。この条件で、できる限り線形な電圧電流変換特性を得るためにには、M200、M300のゲート領域のW/L比を小さくして、電流駆動能力を小さくしておく必要がある。

#### 【0035】

図10(b)に図10(a)の電圧電流変換特性を示す。図10(a)の電圧電流変換回路では最小電圧V1(黒レベル)における最小電流I1(黒電流)をゼロ電流にする設計が難しい。黒電流I1がゼロ電流にできないと画像表示パネルとして重要なコントラストが確保できなくなる。

#### 【0036】

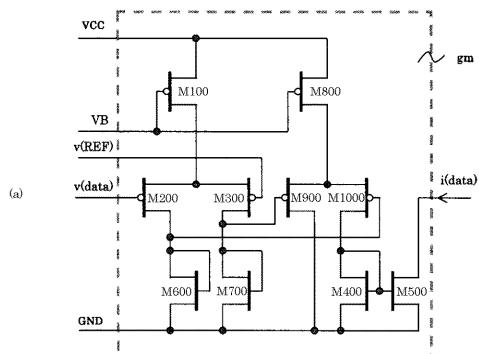

この点に関して対策した電圧電流変換回路の構成例を図11(a)に示す。第1のソースカッフル回路M200、M300の各ドレイン端子に各々ソースが接地されドレインとゲートが短絡されたM600、M700を接続する。さらにソースが電源に接続されゲートが基準電流バイアスVBに接続された第2の基準電流源として動作するM800を設け、M800/Dを第2のソースカッフル回路M900、M1000に接続し、M900/G及びM1000/Gを各々M700/D、M600/Dに接続する。そしてM1000/Dから図10(a)の電圧電流変換回路と同様にM400及びM500のカレントミラー回路を介して列制御信号14となる電流信号i(data)を出力する。図11(a)においてM600及びM700の電流駆動能力をM900及びM1000より小さくするため、M600及びM700のゲート領域のW/L比をM900及びM1000のゲート領域のW/L比より小さくしておく。

#### 【0037】

このように設計された図11(a)の電圧電流変換回路の電圧電流変換特性を図11(b)に示す。黒レベルV1における黒電流I1が小さくすることができるとともに、電圧電流変換特性の線形性を崩すことなく実現できる。

#### 【0038】

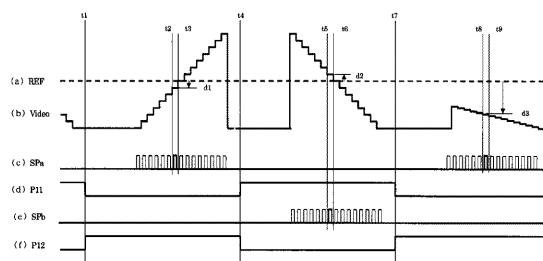

列制御回路の動作を図9のタイムチャートで説明する。

#### 【0039】

時刻t1において制御信号P11、P12は各々Lレベル、Hレベルに変化する。

#### 【0040】

時間t1～t4の入力映像信号の有効期間において水平サンプリング信号群SPaが発生する。この時間t2～t3において該当列のSPaが発生して、この時点のvideο及びREFを容量C100及びC300にサンプリングして時刻t3以降ホールドする。

#### 【0041】

時刻t4において、制御信号P11、P12は各々Hレベル、Lレベルに変化し、電圧電流変換回路に入力される(v(data)-v(REF))はd1となり、時間t2～t3に取り込まれた映像情報に基づいて時間t4～t7の間電流信号i(data)を列制御信号14として出力する。

#### 【0042】

時間t4～t7の入力映像信号の有効期間において水平サンプリング信号群SPbが発

10

20

30

40

50

生し、時間  $t_5 \sim t_6$ において該当列の S P b が発生してこの時点の入力 v i d e o 及び R E F が容量 C 2 0 0 及び C 4 0 0 にサンプリングされ、時刻  $t_6$  以降ホールドされる。

#### 【 0 0 4 3 】

時刻  $t_7$ において、制御信号 P 1 1、P 1 2 は再び各々 L レベル、H レベルに変化し、電圧電流変換回路に入力される ( $v(\text{data}) - v(\text{REF})$ ) は d 2 となり、時間  $t_5 \sim t_6$  に取り込まれた映像情報に基づいて時間  $t_7$  から 1 水平走査期間、電流信号 i (data) を列制御信号 1 4 として出力する。

#### 【 0 0 4 4 】

時間  $t_7$  から 1 水平走査期間の入力映像信号の有効期間において再び水平サンプリング信号群 S P a が発生し、時間  $t_8 \sim t_9$ において該当列の S P a 発生してこの時点の入力 v i d e o 及び R E F が容量 C 2 0 0 及び C 4 0 0 にサンプリングされ時刻  $t_9$  以降ホールドされる。 10

#### 【 0 0 4 5 】

以上の動作を繰り返すことによって、列制御信号 1 4 である電流信号 i (data) は入力映像信号 v i d e o の水平走査周期毎に更新される線順次信号に変換される。

#### 【 0 0 4 6 】

##### 〔 電流設定方式の画素回路 〕

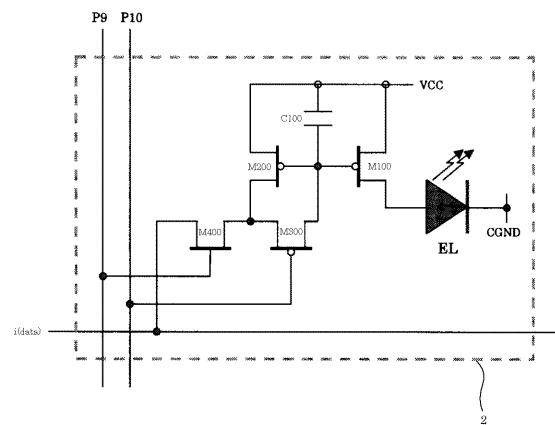

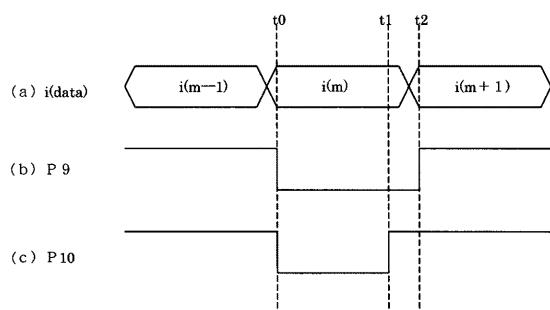

図 6 は電流設定方式の画素回路 2 の構成例である。P 9 及び P 1 0 が行制御信号 2 0 に対応し、列制御信号 1 4 として電流信号 i (data) が入力され、M 1 0 0 / D は接地された E L 素子の電流注入端子に接続されている。 20

#### 【 0 0 4 7 】

図 7 のタイムチャートを使用して動作を説明する。時刻  $t_0$  以前において、該当 m 行の P 9 及び P 1 0 は H レベルであるので M 3 0 0 及び M 4 0 0 は共に OFF であり容量 C 1 0 0 及び M 1 0 0 のゲート容量に保持された充電電圧によって決定された M 1 0 0 / G 電圧によって E L 素子に電流が注入され、これに応じて該当 E L 素子は発光している。 30

#### 【 0 0 4 8 】

時刻  $t_0$  において、該当行の P 9、P 1 0 は共に L レベルに変化するとともに、m 行目の電流信号 i (m) が確定する。即ち、M 3 0 0、M 4 0 0 がともに ON になるため M 2 0 0 に電流信号 i (m) が供給され、これに応じて M 2 0 0 / G 電圧が設定され容量 C 1 0 0 及び M 1 0 0、M 2 0 0 のゲート容量は充電され、電流信号 i (m) に対応した電流が該当 E L 素子に注入され始める。 30

#### 【 0 0 4 9 】

電流信号 i (m) が確定している時刻  $t_1$  において、P 1 0 は H レベルに変化して M 3 0 0 は OFF 状態になり、M 2 0 0 / G 電圧の設定動作は終了して保持動作に移行する。時刻  $t_2$  において P 9 も H レベルに変化して M 2 0 0 への電流供給を停止するが、電流信号 i (m) によって設定された M 2 0 0 / G 電圧は保持されたままであり、引き続き再設定された注入電流によって該当 E L 素子が再設定されて発光を継続する。 40

#### 【 0 0 5 0 】

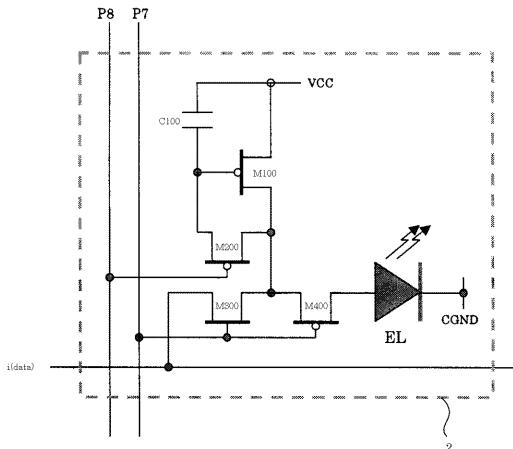

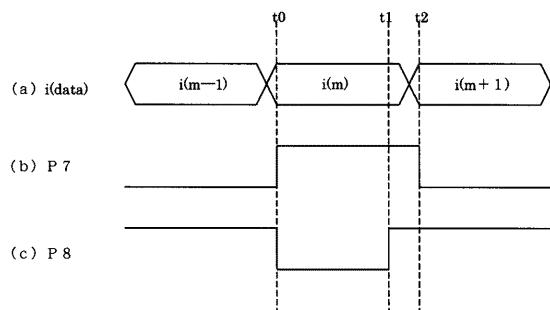

図 4 は電流設定方式の画素回路 2 の他の構成例である。P 7 及び P 8 が行制御信号 2 0 に対応し、列制御信号 1 4 として電流信号 i (data) が入力され、M 4 0 0 / D は接地された E L 素子の電流注入端子に接続されている。 40

#### 【 0 0 5 1 】

図 5 のタイムチャートを使用して動作を説明する。時刻  $t_0$  以前において、該当 m 行の P 7 及び P 8 は各々 L レベル及び H レベルであるので M 2 0 0 及び M 3 0 0 は共に OFF であり M 4 0 0 が ON であるので容量 C 1 0 0 及び M 1 0 0 のゲート容量に保持された充電電圧によって決定された M 1 0 0 / G 電圧によって E L 素子に電流が注入されこれに応じて該当 E L 素子は発光している。 50

#### 【 0 0 5 2 】

時刻  $t_0$  において、該当行の P 7 及び P 8 は各々 H レベル及び L レベルに変化するとともに、m 行目の電流信号 i (m) が確定する。M 2 0 0、M 3 0 0 がともに ON し M 4 0 0 50

0 が OFF するため、該当行 E L 素子への電流注入は停止して該当行の E L 素子は消灯する。さらに M 1 0 0 に電流信号  $i_m$  が供給されるため、これに応じて M 1 0 0 / G 電圧が設定され容量 C 1 0 0 及び M 1 0 0 のゲート容量は充電される。

#### 【 0 0 5 3 】

電流信号  $i_m$  が確定している時刻  $t_1$  において、P 8 は再び H レベルに変化して M 2 0 0 は OFF 状態になり、M 1 0 0 / G 電圧の設定動作は終了して保持動作に移行する。

#### 【 0 0 5 4 】

時刻  $t_2$  において P 7 は L レベルに変化して M 1 0 0 への電流供給を停止するとともに M 4 0 0 が ON して M 1 0 0 / G 電圧で設定された M 1 0 0 のドレイン電流が該当 E L 素子に注入されこれに応じて該当 E L 素子は時刻  $t_1$  以前の再設定された発光を開始しこれを再び設定されるまで継続する。10

#### 【 0 0 5 5 】

本発明は以上の検討結果を踏まえ、これまで知られていなかった新規な電流信号出力回路を実現し、特にばらつきを抑制した出力を得られる電流信号出力回路を実現することを課題とする。また、それを用いて表示むらの少ない表示装置を実現することを課題とする。10

#### 【 課題を解決するための手段 】

#### 【 0 0 5 6 】

本発明に係る電流信号出力回路の発明の一つは以下のように構成される。すなわち、20

入力される電圧信号に応じて電流信号を出力する電流信号出力回路であって、

電流信号制御回路を有しており、

該電流信号制御回路は、

少なくとも、第 1 から第 6 のスイッチと、第 1 、第 2 の容量素子と、第 1 、第 2 のトランジスタとを備えており、

第 1 のスイッチの第 1 端子は電圧信号を与える電圧信号線に接続され、第 1 のスイッチの第 2 端子は第 1 の容量素子の第 1 端子に接続され、20

第 1 の容量素子の第 2 端子は第 1 のトランジスタのゲート電極に接続され、

第 3 のスイッチの第 1 端子と第 2 端子とは第 1 のトランジスタのゲート電極と第 2 主電極とに夫々接続され、30

第 1 のトランジスタの第 1 主電極は第 1 の電源に接続され、

第 1 のトランジスタの第 2 主電極は第 4 のスイッチの第 1 端子に接続され、

第 2 のスイッチの第 1 端子は電圧信号を与える電圧信号線に接続され、第 2 のスイッチの第 2 端子は第 2 の容量素子の第 1 端子に接続され、30

第 2 の容量素子の第 2 端子は第 2 のトランジスタのゲート電極に接続され、

第 5 のスイッチの第 1 端子と第 2 端子とは第 2 のトランジスタのゲート電極と第 2 主電極とに夫々接続され、40

第 2 のトランジスタの第 1 主電極は第 1 の電源に接続され、

第 2 のトランジスタの第 2 主電極は第 6 のスイッチの第 1 端子に接続され、

第 4 及び第 6 のスイッチの第 2 端子は互いに接続されて前記電流信号を出力する電流信号出力端子とされ、40

第 1 から第 6 のスイッチの制御端子は、夫々第 1 から第 6 の制御信号線に接続されていることを特徴とする電流信号出力回路、である。

#### 【 0 0 5 7 】

なお本発明においては、スイッチの第 1 端子、第 2 端子とは、スイッチがその間の導通を制御するところの 2 端子を意味しており、スイッチの導通はスイッチの制御端子に入力される制御信号により制御される。また、トランジスタの第 1 主電極、第 2 主電極とは、ゲート電極以外の 2 電極、即ちソース電極とドレイン電極とのいずれかを表している。また、容量素子の第 1 端子、第 2 端子とは、容量素子の 2 端子の各々を便宜上示すものに過ぎず、特別区別する意味を有するものではない。50

## 【0058】

本発明に係る電流信号出力回路の他の発明は以下のように構成される。すなわち、

入力される電圧信号に応じて電流信号を出力する電流信号出力回路であって、

電流信号制御回路を有しており、

該電流信号制御回路は、

少なくとも、第1から第8のスイッチと、第1、第2の容量素子と、第1から第4のトランジスタとを備えており、

第1のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第1のスイッチの第2端子は第1の容量素子の第1端子に接続され、

第1の容量素子の第2端子は第1のトランジスタのゲート電極に接続され、

第3のスイッチの第1端子と第2端子とは第1のトランジスタのゲート電極と第2主電極とに夫々接続され、

第1のトランジスタの第1主電極は第1の電源に接続され、

第1のトランジスタの第2主電極は第4のスイッチの第1端子と第7のスイッチの第1端子とに接続され、

第7のスイッチの第2端子は第3のトランジスタの第1主電極に接続され、

第3のトランジスタはゲート電極と第1主電極又は第2主電極とが短絡されており且つ第2主電極は第2の電源に接続され、

第2のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第2のスイッチの第2端子は第2の容量素子の第1端子に接続され、

第2の容量素子の第2端子は第2のトランジスタのゲート電極に接続され、

第5のスイッチの第1端子と第2端子とは第2のトランジスタのゲート電極と第2主電極とに夫々接続され、

第2のトランジスタの第1主電極は第1の電源に接続され、

第2のトランジスタの第2主電極は第6のスイッチの第1端子と第8のスイッチの第1端子とに接続され、

第8のスイッチの第2端子は第4のトランジスタの第1主電極に接続され、

第4のトランジスタはゲート電極と第1主電極又は第2主電極とが短絡されており且つ第2主電極は第2の電源に接続され、

第4及び第6のスイッチの第2端子は互いに接続されて外部に前記電流信号を出力する電流信号出力端子とされ、

第1から第8のスイッチの制御端子は、夫々第1から第8の制御信号線に接続されていることを特徴とする電流信号出力回路である。

## 【0059】

具体的には、第3のスイッチと第7のスイッチの双方が導通する期間を設ける及び/又は第5のスイッチと第8のスイッチの双方が導通する期間を設けるようにすると好適である。

## 【0060】

また本発明に係る電流信号出力回路の他の発明として、以下を挙げることができる。すなわち、

入力される電圧信号に応じて電流信号を出力する電流信号出力回路であって、

電流信号制御回路を有しており、

該電流信号制御回路は、

少なくとも、第1及び第3のスイッチと、第1の容量素子と、第1のトランジスタとを備えており、

第1のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第1のスイッチの第2端子は第1の容量素子の第1端子に接続され、

第1の容量素子の第2端子は第1のトランジスタのゲート電極に接続され、

第3のスイッチの第1端子と第2端子とは第1のトランジスタのゲート電極と第2主電極とに夫々接続され、

10

20

30

40

50

第1のトランジスタの第1主電極は第1の電源に接続されていることを特徴とする電流信号出力回路である。

【0061】

ここで、前記第3のスイッチを介して第1のトランジスタのゲート電極を充電した後、第1のトランジスタのゲート電極の電圧が閾値電圧に近づくように放電させてから、前記第1のスイッチに与えられる電圧信号に応じた電圧に第1のトランジスタのゲート電極を充電し、該充電された状態に応じた電流信号を前記第1のトランジスタの第2主電極から電流信号を出力する構成を好適に採用できる。また、前記第3のスイッチの第2端子には第3のスイッチを介して第1のトランジスタのゲート電極を充電するための電流供給経路が接続されている構成を好適に採用できる。該電流供給経路に流れる電流を制御するスイッチを更に有する構成を好適に採用できる。

10

【0062】

本発明に係る電流信号出力回路の他の発明は以下のように構成される。すなわち、

入力される電圧信号に応じて電流信号を出力する電流信号出力回路であって、

電流信号制御回路を有しており、

該電流信号制御回路は、

少なくとも、第1のスイッチと、第1の容量素子と、第1のトランジスタとを備えており、

第1のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第1のスイッチの第2端子は第1の容量素子の第1端子に接続され、

20

第1の容量素子の第2端子は第1のトランジスタのゲート電極に接続され、

第1のトランジスタの第1主電極は第1の電源に接続されていることを特徴とする電流信号出力回路である。

【0063】

ここで、前記第1のトランジスタのゲート電極の電圧が閾値電圧に近づくように放電させてから、前記第1のスイッチに与えられる電圧信号に応じた電圧に第1のトランジスタのゲート電極を充電し、該充電された状態に応じた電流信号を前記第1のトランジスタの第2主電極から出力する構成を好適に採用できる。

【0064】

また、前記第1のトランジスタのゲート電極の電圧が閾値電圧に近づくように放電させる構成においては、第1のスイッチに与えられる電圧信号が基準レベルになっている期間において、前記第1のトランジスタのゲート電極の電圧が閾値電圧に近づくように放電させる構成を好適に採用できる。

30

【0065】

また請求項4から8のいずれかに記載の電流信号制御回路を少なくとも2つ有しており、一方の電流信号制御回路において前記電流信号を出力しているときに、他方の電流信号制御回路において第1のトランジスタのゲート電極を電圧信号に応じた電圧に充電する構成を好適に採用できる。各電流信号制御回路が前記第1のトランジスタの第2主電極から出力される電流信号を外部に出力するか否かを制御するスイッチを有しており、一方の電流信号制御回路の該スイッチが第1のトランジスタの第2主電極から出力される電流信号を外部に出力する状態にあるときに、他方の電流信号制御回路の該スイッチが第1のトランジスタの第2主電極から出力される電流信号を外部に出力しない状態に制御しておく構成を好適に採用できる。

40

【0066】

また本発明は表示装置の発明として、上記の電流信号出力回路と、複数の表示素子とを備えており、前記電流信号出力回路が複数の前記表示素子に対して順次前記電流信号を供給することを特徴とする表示装置の発明を含んでいる。

【0067】

特に、請求項9に記載の電流信号出力回路と、複数の表示素子とを備えており、前記電流信号出力回路が複数の前記表示素子に対して順次前記電流信号を供給するように構成さ

50

れており、前記電流信号出力回路を構成する少なくとも2つの電流信号制御回路と前記複数の表示素子それぞれとの対応関係が非固定的に制御されることを特徴とする表示装置の発明を含んでいる。電流信号出力回路を構成する少なくとも2つの電流信号制御回路と前記複数の表示素子それぞれとの対応関係が非固定的に制御されるとは、複数の表示素子に対する電流信号の順次の供給を複数回行う際に、ある一巡の順次供給の際に所定の表示素子に対して一方の電流信号制御回路からの出力電流が供給された場合には、該一巡に続く一巡など前記一巡とは異なる一巡の順次供給の際には前記所定の表示素子に対しては他方の電流信号制御回路からの出力電流が供給されるようによることを言う。複数の表示素子により画面を構成する場合、例えば1フレーム毎など画面の更新（表示画面の内容が変化しない場合を含む）ごとに各表示素子に対応する電流信号制御回路が変化する構成が特に好適である。

#### 【0068】

なお、表示装置としては前記電流信号出力回路を列方向信号の入力に用い、更に業方向信号の制御を行う行方向制御回路を持つ構成を好適に採用できる。具体的には、請求項10もしくは11に記載の電流信号出力回路と、該電流信号出力回路が順次電流信号を供給する複数の表示素子とを組として、該組を複数備えており、各組に属する表示素子によって表示素子のマトリックスが構成されており、前記電流信号出力回路は該マトリックスの列方向の制御を行うものであり、更に該マトリックスの行方向の制御を行う行制御回路を有する構成を好適に採用できる。

#### 【0069】

また、上記第4のスイッチ及び第6のスイッチを持つ構成に関して言うと、電流信号出力回路を備えており、該電流信号出力信号からの信号の供給を受ける表示素子を2次元の領域に複数配置した表示装置であって、

第4及び第6のスイッチを選択的に動作させる機能を有し、表示する映像信号のフレームによって第4及び第6のスイッチの動作を奇数行または偶数行で変更する表示装置を好適に採用できる。第4及び第6のスイッチに相当する他のスイッチがなければ第4及び第6のスイッチを相補的に動作させればよい。

#### 【0070】

また、電流信号制御回路と表示素子との対応関係を非固定にする構成として、電流信号制御回路が各色に対応する信号を切り替えながら出力する構成を好適に採用できる。

#### 【0071】

なお、以上の構成における表示素子としては、電子放出素子と該電子放出素子が放出する電子によって発光する発光体とを組み合わせたものなど種々の構成の表示素子を採用できるが、特に好適なのはエレクトロルミネセンス素子を用いた表示素子である。更に具体的に言うと、エレクトロルミネセンス素子と該エレクトロルミネセンス素子を駆動する画素回路とを有する表示素子を好適に用いることができる。

#### 【0072】

また前記表示素子が画素回路を有しており、該画素回路は前記電流信号出力回路からの信号に対応した電圧値を保持し、該保持した電圧値に応じた電流値を出力するものである構成を特に好適に採用できる。

#### 【発明の効果】

#### 【0073】

本発明によると、良質な電流信号を発生することができる。また良質な表示を実現することができる。

#### 【発明を実施するための最良の形態】

#### 【0074】

以下に本発明に係る各実施の形態を説明するが、特に次に示す具体的な問題点を解消できるような実施の形態を説明している。

#### 【0075】

本発明者は、以下に示す具体的な課題に着目した。

10

20

30

40

50

【 0 0 7 6 】

まず図13の電圧設定方式の画素回路を用いた場合、閾電圧  $V_{th}$  のトランジスタ間バラツキをリセットできているが、チャネルの移動度  $\mu$  バラツキが主因の駆動係数のバラツキに対して対応できていない。チャネルの移動度  $\mu$  バラツキを抑えるには電流駆動トランジスタM100のゲート領域面積を拡大するのが良いが、画素回路面積への制約の大きい200ppiを目指す小型且つ高精細パネルでは駆動トランジスタM100のゲート領域面積によって駆動係数のバラツキを大きく改善できない。

〔 0 0 7 7 〕

従って、特に小型の表示パネルを想定した場合に、個々の画素の輝度がランダムに変動した固定ノイズを有した画像となり高画質な表示パネルを実現できないという問題がある。

[ 0 0 7 8 ]

また、図4の電流設定方式の画素回路を用いた場合、個々の画素回路2においては、小型且つ高精細な表示パネルにおいても閾電圧V<sub>t h</sub>及び駆動係数のバラツキのリセットが可能であるが、電流設定方式の場合、点順次信号から線順次信号に電圧電流変換して電流信号*i*(data)を列制御信号14として出力する列制御回路が必要になる。

【 0 0 7 9 】

しかし、図10(a)及び図11(a)で示すソースカップル回路及びカレントミラーレンジを含む電圧電流変換回路  $g_m$  では TFT の閾電圧  $V_{th}$  及び駆動係数  $\beta$  のバラツキによって各画素列の電圧電流変換特性が均一化されず画像として縦縞の固定パターンを有する表示パネルとなり、高画質化が困難である。

【 0 0 8 0 】

また、上記のように入力映像信号に忠実な電流信号を画素回路に出力しようとすると、制御回路の構成が複雑化し、表示パネルの小型化に適したものとは言えなかった。

〔 0 0 8 1 〕

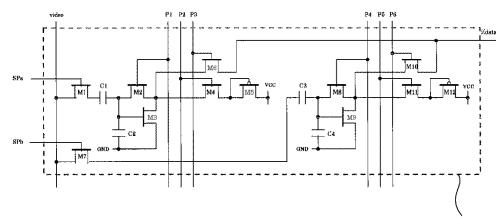

図1は図3に示すような電流設定方式のELパネルに使用する、エレクトロルミネンス素子駆動制御回路に含まれる電流信号制御回路（以下では主に列制御回路として記す）の一実施形態である。以下、図1に示す具体的な実施態様を参照して本発明を詳細に説明するが、本発明はこの形態に限定されるものではない。

【 0 0 8 2 】

図1に示す好ましい形態においては、列制御回路1は、少なくとも、第1から第8のスイッチ(M1、M7、M2、M6、M8、M10、M4、M11)と、第1、第2の容量素子(C1、C3)と、第1から第4のトランジスタ(M3、M9、M5、M12)とを含み、第1のスイッチM1の第1端子は情報電圧信号を与える情報電圧信号線(映像信号video)に接続され、第1のスイッチM1の第2端子は第1の容量素子C1の第1端子に接続され、第1の容量素子C1の第2端子は第1のトランジスタM3のゲート電極に接続され、第3のスイッチM2の第1端子と第2端子とは第1のトランジスタM3のゲート電極と第2主電極とに夫々接続され、第1のトランジスタM3の第1主電極は第1の電源(GND)に接続され、第1のトランジスタM3の第2主電極は第4のスイッチM6の第1端子と第7のスイッチM4の第1端子とに接続され、第7のスイッチM4の第2端子は第3のトランジスタM5の第1主電極に接続され、第3のトランジスタM5はゲート電極と第1主電極又は第2主電極とが短絡されており且つ第2主電極は第2の電源(VCC)に接続され、第2のスイッチM7の第1端子は情報電圧信号を与える情報電圧信号線(映像信号video)に接続され、第2のスイッチM7の第2端子は第2の容量素子C3の第1端子に接続され、第2の容量素子C3の第2端子は第2のトランジスタM9のゲート電極に接続され、第5のスイッチM8の第1端子と第2端子とは第2のトランジスタM9のゲート電極と第2主電極とに夫々接続され、第2のトランジスタM9の第1主電極は第1の電源GNDに接続され、第2のトランジスタM9の第2主電極は第6のスイッチM10の第1端子と第8のスイッチM11の第1端子とに接続され、第8のスイッチM11の第2端子は第4のトランジスタM12の第1主電極に接続され、第4のトランジスタM12

12はゲート電極と第1主電極又は第2主電極とが短絡されており且つ第2主電極は第2の電源VCCに接続され、第4及び第6のスイッチM6及びM10の第2端子は互いに接続されて外部に前記電流信号を出力する電流信号出力端子とされ、第1から第8のスイッチ(M1、M7、M2、M6、M8、M10、M4、M11)の制御端子は、夫々第1から第8の制御信号線(SPa、SPb、P1、P3、P4、P6、P2、P5)に接続されている。なお、図1の形態においては、列制御回路1は第3の容量素子(C2)及び第4の容量素子(C4)をも含み、第3の容量素子C2の第1端子は第1の電源に接続され、第2端子は第1のトランジスタM3のゲート電極に接続され、第4の容量素子C4の第1端子は第1の電源に接続され、第2端子は第2のトランジスタM9のゲート電極に接続されているが、これらC2、C4はM3及びM9のゲート入力容量(チャネル容量)のみで実現してもよく、この場合容量C2及びC4は必要ない。

10

## 【0083】

次に、トランジスタのチャネル特性を図1に示すようにM1はnチャネル、M5はpチャネルというように特定した場合について、より具体的に本発明の構成を示し、その動作を説明するが、これは一例に過ぎず、第1の電源GNDと、第2の電源VCCとの間の電位の関係や、各トランジスタのチャネル特性を逆転させたりした場合には、それに合わせて適宜構成を変更すれば良い。

## 【0084】

列制御回路1には、映像信号video、サンプリング信号SPa、SPb、制御信号19であるP1～P6が入力される。

20

## 【0085】

映像信号videoはM1/S及びM7/Sに接続されサンプリング信号SPa及びSPbは各々M1/G、M7/Gに接続される。M1/Dは容量C1に接続され容量C1の他端は一端が接地された容量C2とソースが接地されたM3/Gに接続される。M3/D及びM3/GはM2/D及びM2/Sと接続され、M2/GにはP1が接続される。M3/DはM4/Sと接続され、M4/Dはソースが電源VCCに接続されゲートとドレインが短絡されたM5に接続され、M4/GにはP2が接続される。さらにM3/DにはM6/Sが接続され、M6/Dは電流信号i(data)を出力する端子に接続され、M6/GはP3と接続されている。一方、M7/Dは容量C3に接続され容量C3の他端は一端が接地された容量C4とソースが接地されたM9/Gに接続される。M9/D及びM9/GはM8/D及びM8/Sと接続され、M8/GにはP4が接続される。M9/DはM11/Sと接続され、M11/Dはソースが電源VCCに接続されゲートとドレインが短絡されたM12に接続され、M11/GにはP5が接続される。さらにM9/DにはM10/Sが接続され、M10/Dは電流信号i(data)を出力する端子に接続され、M10/GはP6と接続されている。また各トランジスタのゲートサイズ(W、L)及び容量値は、

30

M1 = M7、M3 = M9、M2 = M8、M5 = M12、C1 = C3、C2 = C4 . . .

・(3)

となっている。

40

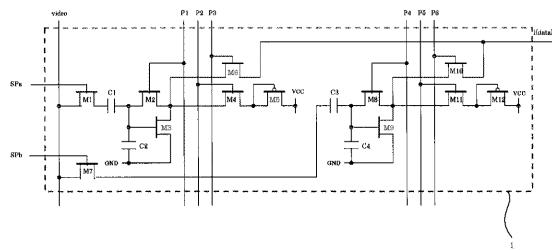

## 【0086】

## 〔列制御回路の動作説明〕

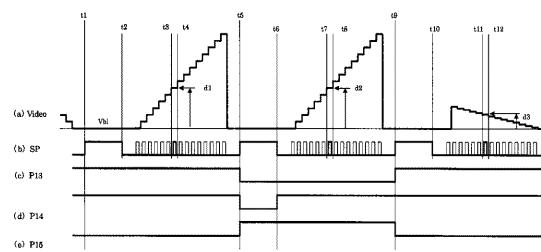

図2は図1の動作を説明するタイムチャートである。図2は映像信号の3水平走査期間、ELパネルからすると3行分の動作を示したものである。

## 【0087】

時刻t1直前

SPa、SPbは各々L、Lレベルであり、P1～P6は各々L、L、H、L、H、Lレベルである。したがって、各SW動作をするトランジスタは

M1 = OFF、M2 = OFF、M4 = OFF、M6 = ON

M7 = OFF、M8 = OFF、M11 = ON、M10 = OFFとなる。

## 【0088】

50

この時、M<sub>3</sub>及びM<sub>9</sub>は各々ゲート電極に付随する容量に充電された保持電圧V<sub>a1</sub>及びV<sub>b1</sub>によって電流駆動している。即ち、M<sub>3</sub>/D電流I<sub>a1</sub>が電流信号i(data)に出力され列制御信号14となる。M<sub>9</sub>/D電流はM<sub>12</sub>に供給されM<sub>9</sub>/D電圧が決定される。

#### 【0089】

時刻t<sub>1</sub>～t<sub>7</sub>

時刻t<sub>1</sub>において、入力映像信号v<sub>ide</sub>oはブランкиングレベルV<sub>b1</sub>になっているとともに、S<sub>P</sub>a、P<sub>2</sub>、P<sub>3</sub>、P<sub>5</sub>、P<sub>6</sub>は各々H、H、L、L、Hレベルに変化する。

#### 【0090】

10

したがって、各SW動作をするトランジスタは

M<sub>1</sub>=ON、M<sub>2</sub>=OFF、M<sub>4</sub>=ON、M<sub>6</sub>=OFF

M<sub>7</sub>=OFF、M<sub>8</sub>=OFF、M<sub>11</sub>=OFF、M<sub>10</sub>=ONとなる。

#### 【0091】

この時、M<sub>9</sub>/G電圧のV<sub>b1</sub>によって駆動されたM<sub>9</sub>/D電流I<sub>b1</sub>がM<sub>3</sub>/D電流I<sub>b2</sub>に替わって電流信号i(data)に出力されるようになる。電流信号i(data)はELパネルの列長を通過し多数の列画素数に対応する素子に接続する為、大きな寄生容量を駆動しなければならないので、図に示すように画素回路への有効電流供給遷移I<sub>a1</sub>～I<sub>b1</sub>に時間を要する。時刻t<sub>2</sub>になる前にP<sub>1</sub>はHレベルになりM<sub>2</sub>=ONとなり、この時点から時刻t<sub>2</sub>の短時間においてM<sub>3</sub>/GはM<sub>5</sub>によって充電される。

20

#### 【0092】

時刻t<sub>2</sub>でM<sub>3</sub>/GのM<sub>5</sub>による充電動作は停止して、M<sub>3</sub>/Gは自身の閾電圧V<sub>th</sub>に漸近するように自己放電動作を行う。

#### 【0093】

時刻t<sub>3</sub>においてS<sub>P</sub>aはLレベルに変化してM<sub>1</sub>=OFFになる。時刻t<sub>4</sub>になる前にP<sub>1</sub>がLレベルに変化しM<sub>2</sub>=OFFになり、この時点でM<sub>3</sub>の自己放電動作は終了する。この時点から時刻t<sub>4</sub>までの期間、M<sub>2</sub>及びM<sub>4</sub>はともにOFFになりM<sub>3</sub>/Dは急速にLレベルに変化する為、ドレイン・ゲート容量などによってM<sub>3</sub>/Gは図に示すように多少電圧降下が発生する。

30

#### 【0094】

P<sub>2</sub>がHレベルに変化する時刻t<sub>4</sub>においてM<sub>4</sub>=ONになるので再びM<sub>3</sub>/Dは上昇する為、再びM<sub>3</sub>/Gは図に示すように再び電圧上昇しほぼ元の状態に戻る。この時点でM<sub>3</sub>/Gは自身の閾電圧V<sub>th</sub>近傍であるのでM<sub>3</sub>/D電流はほとんどゼロである。時刻t<sub>1</sub>～t<sub>7</sub>の映像信号v<sub>ide</sub>oの有効期間内では、水平サンプリング信号群S<sub>P</sub>aが発生するがS<sub>P</sub>bは発生しない。時刻t<sub>5</sub>～t<sub>6</sub>において該当する列の水平サンプリング信号S<sub>P</sub>aが発生して自身の閾電圧V<sub>th</sub>近傍に保持されているM<sub>3</sub>/G電圧を、この時点でのブランкиングレベルを基準とする映像信号レベルd<sub>1</sub>によって遷移電圧V<sub>1</sub>変化させる。

#### 【0095】

V<sub>1</sub>は(4)式で概略示される。

40

#### 【0096】

$$V_1 = d_1 \times C_1 \div (C_1 + C_2 + C(M_3)) \quad \dots \quad (4)$$

#### 【0097】

C(M<sub>3</sub>)はM<sub>3</sub>ゲート入力容量を示す。このときM<sub>3</sub>/D電流は(2)式で示される。該当するS<sub>P</sub>aがLレベルに変化するとM<sub>1</sub>=OFFなり、M<sub>1</sub>の寄生容量動作によって多少電圧降下したV<sub>a2</sub>に変化して再びM<sub>3</sub>/G電圧は保持状態になる。

#### 【0098】

時刻t<sub>7</sub>～t<sub>13</sub>

時刻t<sub>7</sub>において、入力映像信号v<sub>ide</sub>oはブランкиングレベルV<sub>b1</sub>になっているとともに、S<sub>P</sub>b、P<sub>2</sub>、P<sub>3</sub>、P<sub>5</sub>、P<sub>6</sub>は各々H、L、H、H、Lレベルに変化する

50

。

### 【 0 0 9 9 】

したがって、各 SW 動作をするトランジスタは

$M_1 = OFF$ 、 $M_2 = OFF$ 、 $M_4 = ON$ 、 $M_6 = OFF$

$M_7 = ON$ 、 $M_8 = OFF$ 、 $M_{11} = OFF$ 、 $M_{10} = OFF$  となる。

### 【 0 1 0 0 】

この時、 $M_3 / G$  電圧の  $V_{a2}$  によって駆動された  $M_3 / D$  電流  $I_{a2}$  が  $M_9 / D$  電流  $I_{b1}$  に替わって電流信号  $i(data)$  に出力されるようになる。電流信号  $i(data)$  は EL パネルの列長を通過し多数の列画素数に対応する素子に接続する為、大きな寄生容量を駆動しなければならないので、図に示すように画素回路への有効電流供給遷移  $I_{b1} - I_{a2}$  に時間を要する。時刻  $t_8$  になる前に  $P_4$  は H レベルになり  $M_8 = ON$  となり、この時点から時刻  $t_8$  までの短時間において  $M_9 / G$  は  $M_{12}$  によって充電される。

10

### 【 0 1 0 1 】

時刻  $t_8$  で  $M_9 / G$  の  $M_{12}$  による充電動作は停止して、 $M_9 / G$  は自身の閾電圧  $V_{th}$  に漸近するように自己放電動作を行う。

### 【 0 1 0 2 】

時刻  $t_9$  において  $S_P b$  は L レベルに変化して  $M_7 = OFF$  になる。時刻  $t_{10}$  になる前に  $P_4$  が L レベルに変化し  $M_8 = OFF$  になり、この時点で  $M_9$  の自己放電動作は終了する。この時点から時刻  $t_{10}$  までの期間、 $M_8$  及び  $M_{11}$  はともに  $OFF$  になり  $M_9 / D$  は急速に L レベル変化する為、ドレイン - ゲート容量などによって  $M_9 / G$  は図に示すように多少電圧降下が発生する。

20

### 【 0 1 0 3 】

$P_5$  が H レベルに変化する時刻  $t_{10}$  において  $M_{11} = ON$  になるので再び  $M_9 / D$  は上昇する為、再び  $M_9 / G$  は図に示すように再び電圧上昇しほぼ元の状態に戻る。この時点で  $M_9 / G$  は自身の閾電圧  $V_{th}$  近傍であるので  $M_9 / D$  電流はほとんどゼロである。時刻  $t_7 \sim t_{13}$  の映像信号  $v_{ideo}$  の有効期間内で水平サンプリング信号群  $S_P b$  が発生するが  $S_P a$  は発生しない。

20

### 【 0 1 0 4 】

時間  $t_{11} \sim t_{12}$  において該当する列の水平サンプリング信号  $S_P b$  が発生して自身の閾電圧  $V_{th}$  近傍に保持されている  $M_9 / G$  電圧を、この時点でのプランキングレベルを基準とする映像信号レベル  $d_2$  によって遷移電圧  $V_2$  だけ変化させる。 $V_2$  は(5)式で概略示される。

30

### 【 0 1 0 5 】

$$V_2 = d_2 \times C_3 \div (C_3 + C_4 + C(M_9)) \quad \dots \quad (5)$$

$C(M_9)$  は  $M_9$  ゲート入力容量を示す。このとき  $M_9 / D$  電流は(2)式で示される。該当する  $S_P b$  が L レベルに変化すると  $M_7 = OFF$  なり、 $M_7$  の寄生容量動作によって多少電圧降下した  $V_{b2}$  に変化して再び  $M_9 / G$  電圧は保持状態になる。

30

### 【 0 1 0 6 】

時刻  $t_{13} \sim 1$  水平走査期間

時刻  $t_{13}$  において、入力映像信号  $v_{ideo}$  はプランキングレベル  $V_{b1}$  になつているとともに、 $S_P a$ 、 $P_2$ 、 $P_3$ 、 $P_5$ 、 $P_6$  は各々 H、H、L、L、H レベルに変化する。

40

### 【 0 1 0 7 】

したがって、各 SW 動作をするトランジスタは

$M_1 = ON$ 、 $M_2 = OFF$ 、 $M_4 = ON$ 、 $M_6 = OFF$

$M_7 = OFF$ 、 $M_8 = OFF$ 、 $M_{11} = OFF$ 、 $M_{10} = ON$  となる。

### 【 0 1 0 8 】

この時、 $M_9 / G$  電圧の  $V_{b2}$  によって駆動された  $M_9 / D$  電流  $I_{b2}$  が  $M_3 / D$  電流  $I_{a2}$  に替わって電流信号  $i(data)$  に出力されるようになる。電流信号  $i(data)$  は EL パネルの列長を通過し多数の列画素数に対応する素子に接続する為、大きな寄

50

生容量を駆動しなければならないので、I a 2 と I b 2 とが異なる場合には、I b 1 I a 2 の変化と同様に画素回路への有効電流供給遷移 I a 2 → I b 2 の変化に時間要する。時刻 t 1 4 になる前に P 1 は H レベルになり M 2 = ON となり、この時点から時刻 t 1 4 の短時間において M 3 / G は M 5 によって充電される。

#### 【0109】

時刻 t 1 4 で M 3 / G の M 5 による充電動作は停止して M 3 / G は自身の閾電圧 V t h に漸近するように自己放電動作を行う。

#### 【0110】

時刻 t 1 5 において S P a は L レベルに変化して M 1 = OFF になる。時刻 t 1 6 になる前に P 1 が L レベルに変化し M 2 = OFF になり、この時点で M 3 の自己放電動作は終了する。この時点から時刻 t 1 6までの期間、M 2 及び M 4 はともに OFF になり M 3 / D は急速に L レベルに変化する為、ドレイン - ゲート容量などによって M 3 / G は図に示すように多少電圧降下が発生する。

#### 【0111】

P 2 が H レベルに変化する時刻 t 1 6 において M 4 = ON になるので再び M 3 / D は上昇する為、再び M 3 / G は図に示すように再び電圧上昇しほぼ元の状態に戻る。この時点で M 3 / G は自身の閾電圧 V t h 近傍であるので M 3 / D 電流はほとんどゼロである。

#### 【0112】

時間 t 1 6 ~ t 1 7 の映像信号 v i d e o の有効期間内では、水平サンプリング信号群 S P a が発生するが S P b は発生しない。

#### 【0113】

時間 t 1 7 ~ t 1 8 において該当する列の水平サンプリング信号 S P a が発生し、自身の閾電圧 V t h 近傍に保持されている M 3 / G 電圧を、この時点でのブランкиングレベルを基準とする映像信号レベル d 3 によって遷移電圧 V 3 だけ変化させる。

#### 【0114】

V 3 は(6)式で概略示される。

#### 【0115】

$$V 3 = d 3 \times C 1 \div (C 1 + C 2 + C (M 3)) \quad \dots \quad (6)$$

#### 【0116】

C (M 3) は M 3 ゲート入力容量を示す。このとき M 3 / D 電流は(2)式で示される。該当する S P a が L レベルに変化すると M 1 = OFF となり、M 1 の寄生容量動作によって多少電圧降下した V a 2 に変化して再び M 3 / G 電圧は保持状態になる。

#### 【0117】

本発明の E L パネルは、図 3 に示すようなアクティブマトリクス型の電流設定方式の E L パネルにおいて、列制御回路 1 として上記本発明の電流信号制御回路を用いることにより実現され、列制御回路 1 を上記のように制御する以外は従来と同様にして動作させることができる。従って、画素回路 2 についても、言うまでもなく図 4 や図 6 に示す形態のものが使用できる。

#### 【0118】

また本発明は、エレクトロルミネセンス素子と一緒に配置され、入力される電流信号に応じて各々のエレクトロルミネセンス素子に注入電流を供給する画素回路が、2 次元の領域に複数配置されたエレクトロルミネセンスパネルにおいて、外部から入力される情報電圧信号に応じて画素回路に対して電流信号を供給するための電流信号制御回路を複数備え、夫々の電流信号制御回路が、单一の情報電圧信号を入力とし、該当する制御回路書き込み期間に入力される情報電圧信号に対応した第 1 の電圧値を保持し、該保持した第 1 の電圧値に対応した電流信号を制御回路出力期間に選択された画素回路に出力する機能を有し、夫々の画素回路が、該当する画素回路書き込み期間に入力される電流信号に対応した第 2 の電圧値を保持し、該保持した第 2 の電圧値に対応した注入電流をエレクトロルミネセンス素子に対して該当する発光期間に供給し続ける機能を有するものを含んでいる。

#### 【0119】

10

20

30

40

50

このようなエレクトロルミネセンスパネルは、上記に詳述した本発明の電流信号制御回路を用い、図4～図7に示すような電流設定方式の画素回路を用いた図3のようなELパネルをその具体的な実施形態として包むものである。図1、図2に基づく本発明の電流信号制御回路の構成及び動作についての説明、及び図4～図7に基づく従来の画素回路の構成及び動作についての説明と対応させると、次のようになる。

#### 【0120】

まず、電流信号制御回路が入力する単一の情報電圧信号とは、videoに対応し、図8に示すような従来例と異なり基準信号REFは不要である。

#### 【0121】

該当する制御回路書き込み期間とは、図1のような一つの電流信号制御回路において、サンプリング信号SPaにより、第1のスイッチM1がONしている期間（例えば図2におけるt5～t6の間のSPaがHである期間）等に対応する。この期間に該当する電流信号制御回路に入力された情報電圧信号に対応した第1の電圧値は、例えば、第1の容量素子C1にて保持し、C1にゲート電極が接続された第1のトランジスタM3を出力手段として用いて前記保持した第1の電圧値に対応した電流信号を出力することができる。この電流信号は、制御回路出力期間に選択された画素回路に出力するが、制御回路出力期間とは、図1のような一つの電流信号制御回路において、第4の制御信号P3により第4のスイッチM6がONしている期間（例えば図2におけるt7～t13のP3がHである期間）等に対応している。また、画素回路が選択されているとは、例えば図4に示すような画素回路2の場合には、図5におけるt0～t2の期間のように、行制御信号のP7がHでありM300がONしてM100/Gの設定動作の状態にあることを指しており、これは画素回路書き込み期間である。

10

20

30

#### 【0122】

夫々の画素回路において、上記画素回路書き込み期間に電流信号制御回路から入力される電流信号に対応した第2の電圧値は、例えば図4の画素回路の場合には、第2電圧保持手段として容量素子C100を利用して保持し、C100にゲート電極が接続されたトランジスタM3を注入手段として用いて前記保持した第2の電圧値に対応した注入電流をEL素子に対して該当する発光期間に供給し続けることができる。ここで該当する発光期間とは、例えば図5におけるt2以降のP7がLでありM300がOFFし、M400がONしてEL素子に注入電流が供給できる期間である。

30

#### 【0123】

以上説明したような本発明は、入力映像信号video等の情報電圧信号を基に線順次電流信号i(data)を出力することができるものである。

#### 【0124】

図1の列制御回路1には電圧設定回路が搭載されているので、電流駆動トランジスタであるM3及びM9の動作に留意する必要がある。ELパネルにおいて、列制御回路1は画素回路に比べると面積的な余裕があるため、M3及びM9のゲート面積を大きくできる。一般にTFTの基本サイズの駆動係数バラツキは20%pp程度であるが、本発明のようにM3及びM9のゲート面積を大きくできることにより、例えばこれらを画素回路に設ける場合よりも16倍のサイズで構成した場合、駆動係数バラツキを1/4の5%pp程度とすることが期待できる。

40

#### 【0125】

さらに図2で示す動作において、SPa、P1、P2、P3とSPb、P4、P5、P6の各々のペアの制御信号を、映像信号フレーム毎に受け持つ水平走査期間を奇数偶数と切り替え、第4及び第6のスイッチ(M6、M10)を相補的に動作させると、各画素の電流信号i(data)はM3及びM9によって発生したものになるので駆動係数バラツキはさらに1/2の3.5%ppになる。

#### 【0126】

また、該当列の列制御回路の処理する色を決定せず映像信号フレーム毎に入力映像信号によって、例えばRG B、GB R、B R Gの様に切り替え、同一画素の3色

50

の列制御回路 1 からの電流信号  $i$  (data) を切り替えるようにすることもできる。即ち、情報電圧信号として 3 色の映像信号群が少なくとも入力されるものであるとき、3つの列制御回路を一組とし、該一組の列制御回路から出力される各色の映像信号に対応する電流信号を、映像信号フレーム単位で前記一組の列制御回路に含まれる 3 つの列制御回路間で切り替えて出力させるようにする。この場合、駆動係数バラツキ はさらに 1 / 3 の 2 . 0 % pp にできる。

#### 【0127】

また、本発明において、S P a、P 1、P 2、P 3 を使用する M 1 ~ M 6 及び C 1、C 2 を含む第 1 のブロックと、S P b、P 4，P 5，P 6 を使用する M 7 ~ M 1 2 及び C 3、C 4 を含む第 2 のブロックとにより交互に電流信号  $i$  (data) を出力させることにより、サンプリング信号 S P a 群又は S P b 群の終了時点から各列制御回路から所望の電流出力が得られるため、このような構成が好ましい。しかしながら、サンプリング信号 S P a 群の終了時点から次の行制御開始タイミングまで該当画素回路に電流供給するように構成すると、図 1 の列制御回路は S P b、P 4，P 5，P 6 を使用せず M 7 ~ M 1 2、C 3、C 4 を除く列制御回路に構成しても良い。

10

#### 【0128】

また、図 1 において、P 2、M 4、M 5 及び P 5、M 1 1、M 1 2 から構成される、M 3 / D 及び M 9 / D のバイアス回路及び M 3 / G 及び M 9 / G の充電回路は、無くても本発明の基本的概念を崩すものでは無い。

20

#### 【0129】

さらに、図 2 において、P 1 及び P 2 の変化タイミングは時刻 t 1、t 3、t 1 3、t 1 5 として S P a と等しくしても良い。また、P 4 及び P 5 の変化タイミングは時刻 t 8、t 1 0 として S P b と等しくしても良い。

#### 【0130】

また、本発明においてはトランジスタとして、通常、特性のばらつきが問題となる T F T を用いた場合に顕著な効果を有するものであるが、単結晶シリコンを用いた絶縁ゲート型電界効果トランジスタで回路を構成した場合にも広く適用できるものである。

20

#### 【0131】

以上説明した様に本発明を適用した E L 素子駆動制御回路を使用した場合、T F T 等の絶縁ゲート型電界効果トランジスタの素子特性バラツキを簡単な回路構成によって高精細表示の要望を損うこと無く大幅に軽減できるため、均一な特性を有する表示画像が得られる E L パネルを実現でき、高精細 E L パネルの小型化にも著しい効果を有するものとなる。

30

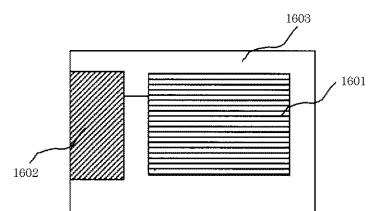

#### 【0132】

図 1 6 は上記実施形態で説明した E L パネルを表示装置として用いた情報表示装置の構成を説明する図である。この情報表示装置は携帯電話、携帯コンピュータ、スチルカメラもしくはビデオカメラのいずれかの形態をとる。もしくはそれらの各機能の複数を実現する装置である。上記実施形態で説明してきた E L パネルに相当するのが表示装置 1 6 0 1 である。符号 1 6 0 2 は情報入力部である。携帯電話の場合には情報入力部はアンテナを含んで構成され、例えば P D A や携帯パソコンの場合には情報入力部はネットワークに対するインターフェース部を含んで構成され、スチルカメラやムービーカメラの場合には情報入力部は C C D や C M O S などによるセンサ部を含んで構成される。符号 1 6 0 3 は情報入力部 1 6 0 2 と表示装置 1 6 0 1 を保持する筐体である。

40

#### 【図面の簡単な説明】

#### 【0133】

【図 1】エレクトロルミネセンス素子駆動制御回路に含まれる列制御回路の一実施形態である。

【図 2】図 1 の列制御回路の動作を説明するタイムチャートである。

【図 3】電流設定方式による E L パネル全体の回路図である。

【図 4】電流設定方式の画素回路である。

50

【図5】図4の画素回路の動作を説明するタイムチャートである。

【図6】電流設定方式の画素回路である。

【図7】図6の画素回路の動作を説明するタイムチャートである。

【図8】電流設定方式のEL素子駆動制御回路に含まれる列制御回路の一例である。

【図9】図8の列制御回路の動作を説明するタイムチャートである。

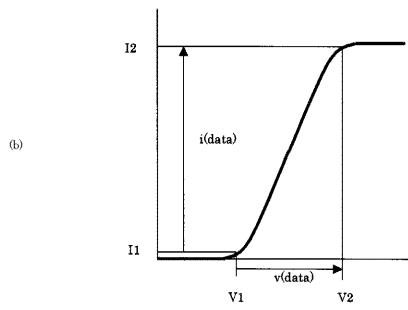

【図10】図8の形態の列制御回路に使用される電圧電流変換回路を説明するための図である。(a)は回路図である。(b)は(a)の回路の電圧電流変換特性を説明する図である。

【図11】図8の形態の列制御回路に使用される別の電圧電流変換回路を説明するための図である。(a)は回路図である。(b)は(a)の回路の電圧電流変換特性を説明する図である。 10

【図12】電圧設定方式によるELパネル全体の回路図である。

【図13】電圧設定方式による画素回路である。

【図14】電圧設定方式による列制御回路である。

【図15】図12のELパネルの動作を説明するタイムチャートである。

【図16】情報表示装置の構成を示す図である。

#### 【符号の説明】

##### 【0134】

1 列制御回路

20

2 画素回路

3 水平シフトレジスタ

4 ゲート回路

5 垂直シフトレジスタ

6, 7, 8 入力回路

9 画素表示領域

10 入力映像信号

11, 11a 水平走査制御信号

12, 12a 垂直走査制御信号

13, 13a 補助列制御信号

14 列制御信号

30

15 水平サンプリング信号ゲート回路

16 ゲート回路

17 水平サンプリング信号

18 水平サンプリング信号

19 制御信号

20 行制御信号

21 制御信号

22 列制御回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図15】

【図14】

【図16】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 4 2 A |

| H 0 4 N | 5/70  | A       |

| H 0 5 B | 33/14 | A       |

F ターム(参考) 5C080 AA06 BB05 CC03 DD05 EE29 EE30 FF11 HH09 JJ02 JJ03

JJ04 JJ05 KK04 KK07 KK43

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 电致发光装置的驱动方法及显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP2004145296A5</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2006-08-10 |

| 申请号            | JP2003305081                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2003-08-28 |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 佳能公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 川崎素明<br>井関正己                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 川崎 素明<br>井関 正己                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H04N5/70 H01L51/50 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| CPC分类号         | G09G3/325 G09G3/3241 G09G3/3283 G09G2300/0819 G09G2300/0842 G09G2300/0852 G09G2300/0861 G09G2310/0297 G09G2310/066 G09G2320/0238 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.H G09G3/20.623.L G09G3/20.624.B G09G3/20.641.D G09G3/20.642.A H04N5/70.A H05B33/14.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 3K007/AB03 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 5C058/AA12 5C058/BA04 5C058/BA06 5C058/BA33 5C058/BB06 5C080/AA06 5C080/BB05 5C080/CC03 5C080/DD05 5C080/EE29 5C080/EE30 5C080/FF11 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/KK04 5C080/KK07 5C080/KK43 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB06 5C380/AB34 5C380/AC08 5C380/AC09 5C380/AC11 5C380/AC12 5C380/BA11 5C380/BA38 5C380/BA39 5C380/BB02 5C380/CA08 5C380/CA12 5C380/CA13 5C380/CB01 5C380/CB16 5C380/CB17 5C380/CC13 5C380/CC14 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC53 5C380/CC63 5C380/CC64 5C380/CD014 5C380/CD024 5C380/CF07 5C380/CF26 5C380/DA02 5C380/DA06 |         |            |

| 代理人(译)         | 渡辺圭佑<br>山口 芳広                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 优先权            | 2002256432 2002-09-02 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 其他公开文献         | JP4416456B2<br>JP2004145296A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

#### 摘要(译)

一种电流信号输出电路，能够获得变化被抑制的输出。电流信号控制电路包括第一至第六开关，第一和第二电容元件以及第一和第二晶体管，并且第一开关的第一和第二端子分别具有电压信号线和第一信号线。对于一个电容性元件的第一端子，第一电容性元件的第二端子至第一晶体管的栅极，第三电容的第一和第二端子分别至第一晶体管的栅极和第二主电极，第一晶体管的第一和第二主电极分别是第一电源和第四开关的第一端子，第二开关的第一和第二端子分别是电压信号线和第二电容元件的第一端子，第二电容元件的第二端子是第二晶体管的栅电极，第五开关的第一端子和第二端子分别是第二晶体管的栅电极和第二主电极，以及第二晶体管的第一主电极和第二主电极。电极分别连接到第一电源和第六开关的第一端子，控制第一到第六开关，并从第四和第六开关输出电流。[选型图]图1