(19)日本国特許庁( J P )

(12) 公開特許公報 ( A ) (11)特許出願公開番号

特開2003 - 330387

(P2003 - 330387A)

(43)公開日 平成15年11月19日(2003.11.19)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I           | テマコード(参考)       |

|--------------------------|------|---------------|-----------------|

| G 0 9 F 9/30             | 330  | G 0 9 F 9/30  | 330 Z 3 K 0 0 7 |

|                          | 338  |               | 338 5 C 0 9 4   |

| H 0 5 B 33/14            |      | H 0 5 B 33/14 | A               |

審査請求 未請求 請求項の数 7 O L (全 8 数)

(21)出願番号 特願2003 - 20588(P2003 - 20588)

(22)出願日 平成15年1月29日(2003.1.29)

(31)優先権主張番号 特願2002 - 59557(P2002 - 59557)

(32)優先日 平成14年3月5日(2002.3.5)

(33)優先権主張国 日本(JP)

(71)出願人 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(72)発明者 野口 幸宏

大阪府守口市京阪本通2丁目5番5号 三洋電

機株式会社内

(72)発明者 松本 昭一郎

大阪府守口市京阪本通2丁目5番5号 三洋電

機株式会社内

(74)代理人 100105924

弁理士 森下 賢樹

最終頁に続く

(54)【発明の名称】表示装置

(57)【要約】

【課題】 表示装置における電圧降下に起因する画素の輝度の低下を軽減する。

【解決手段】 表示装置 100において、有機発光素子OLEDに電流を供給する電源供給線Vddの断面積を、輝度データを流すデータ線DLおよび走査信号を流す走査線SLの断面積よりも大きくする。これにより、電源供給線Vddの低抵抗化を図り、電圧降下の影響を軽減する。

**【特許請求の範囲】**

【請求項1】 複数の光学素子と、前記光学素子のそれぞれに電気エネルギーを供給する電源供給線と、前記光学素子のそれぞれに制御信号を送る信号線と、を備え、前記電源供給線の抵抗は、前記信号線の抵抗よりも低いことを特徴とする表示装置。

【請求項2】 前記電源供給線の断面積は、前記信号線の断面積よりも大きいことを特徴とする請求項1に記載の表示装置。10

【請求項3】 前記電源供給線の幅は、前記信号線の幅よりも広いことを特徴とする請求項1または2に記載の表示装置。

【請求項4】 前記電源供給線を含む層の厚さは、前記信号線を含む層の厚さよりも厚いことを特徴とする請求項1から3のいずれかに記載の表示装置。

【請求項5】 前記電源供給線を構成する材料の電気抵抗率は、前記信号線を構成する材料の電気抵抗率よりも低いことを特徴とする請求項1から4のいずれかに記載の表示装置。20

【請求項6】 前記信号線は、前記光学素子のそれぞれの輝度を制御するための輝度データを送るデータ線であることを特徴とする請求項1から5のいずれかに記載の表示装置。

【請求項7】 前記信号線は、前記光学素子のそれぞれの表示タイミングを制御するための走査信号を送る走査線であることを特徴とする請求項1から5のいずれかに記載の表示装置。

**【発明の詳細な説明】****【0001】**

【発明の属する技術分野】本発明は表示装置に関するもので、特に、電圧降下に起因するアクティブマトリクス型表示装置における画素の輝度の低下を改善する技術に関するものである。

**【0002】**

【従来の技術】有機エレクトロルミネッセンス表示装置（以下、「有機EL表示装置」または「有機ELパネル」ともいう）が、新たな平面型表示装置として注目されている。とくに、薄膜トランジスタ（Thin Film Transistor：以下、「TFT」ともいう）をスイッチング素子として備えるアクティブマトリクス型有機EL表示装置は、現在広く普及している液晶表示装置にとって代わる次世代表示装置の最有力候補であり、実用化に向けて熾烈な開発競争の最中にいる。

【0003】有機EL素子は液晶表示素子と異なり、素子自身が発光するため、液晶表示装置では必須の構成であったバックライトが不要となり、装置のさらなる薄型化、軽量化が期待できる。また、自発光することを利用して、液晶表示装置のバックライトなど、発光装置としての利用も期待されている。

**【0004】**

【発明が解決しようとする課題】有機EL素子は、電流が流れることにより発光する電流駆動型光学素子であるから、表示のために有機EL素子が発光している間、有機EL素子に電流が流れ続ける。このとき、有機EL素子に電流を供給する電源供給線の電圧降下により有機EL素子の輝度が低下することがある。アクティブマトリクス型有機EL表示装置では、電圧降下の影響により、同じ輝度データを設定した画素の輝度がばらつくことがあり、表示品位の低下をもたらす要因となっていた。

【0005】本発明は、こうした課題に鑑みてなされたものであり、その目的は、表示装置における画素の輝度の低下を改善する技術の提供にある。

**【0006】**

【課題を解決するための手段】本発明のある態様は表示装置に関するもので、この表示装置は、複数の光学素子と、光学素子のそれぞれに電気エネルギーを供給する電源供給線と、光学素子のそれぞれに制御信号を送る信号線と、を備え、電源供給線の抵抗は、信号線の抵抗よりも低い。これにより、電圧降下に起因する光学素子の輝度の低下およびばらつきを改善することができる。

【0007】電源供給線の断面積は、信号線の断面積よりも大きくてよい。これにより、電源供給線の低抵抗化を図ることができる。電源供給線の幅は、信号線の幅よりも広くてよい。電源供給線を含む層の厚さは、信号線を含む層の厚さよりも厚くてよい。層厚を厚くすることで、光学素子の開口率を下げずに断面積を大きくすることができるという利点がある。電源供給線を構成する材料の電気抵抗率は、信号線を構成する材料の電気抵抗率よりも低くてもよい。

【0008】信号線は、光学素子のそれぞれの輝度を制御するための輝度データを送るデータ線であってよい。信号線は、光学素子のそれぞれの表示タイミングを制御するための走査信号を送る走査線であってよい。データ線および走査線は、各光学素子に電圧信号を送るが、定常状態では電流が流れないので、電圧降下の影響が少ない。したがって、データ線および走査線の断面積を電源供給線よりも小さくしておくことで、光学素子の開口率を向上させることができる。

【0009】なお、以上の構成要素の任意の組合せ、本発明の表現を方法、装置、システム、などの間で変換したものもまた、本発明の態様として有効である。

**【0010】**

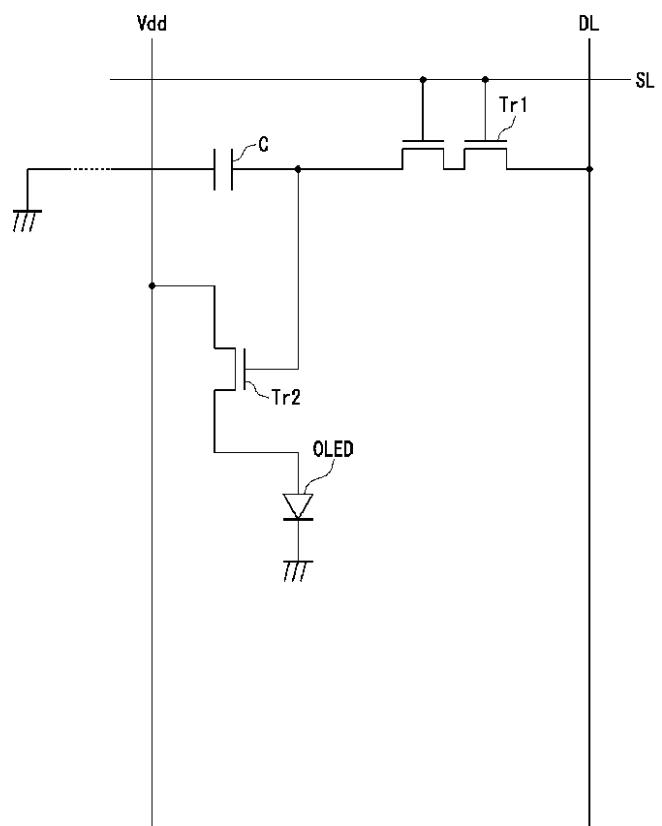

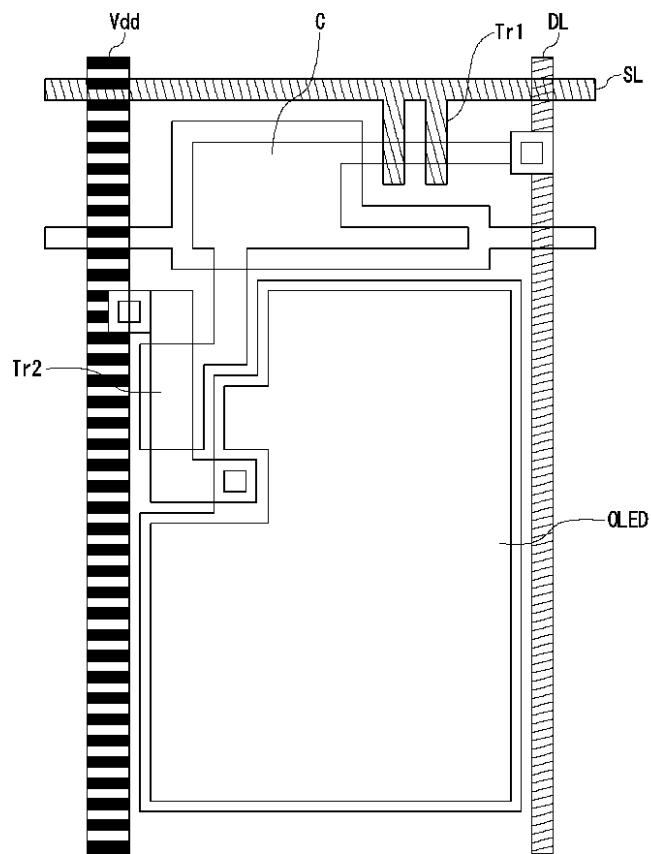

【発明の実施の形態】（第1の実施の形態）図1は、第1の実施の形態に係る表示装置100の1画素分の回路構成を示す。この回路は、有機発光素子OLEDと、有機発光素子OLEDを制御するための2つのトランジスタTr1およびTr2と、保持容量Cと、走査信号を送る走査線SLと、輝度データを送るデータ線DLと、有機発光素子OLEDに電流を供給する電源供給線Vdd

とを備える。

【0011】電源供給線Vddは、有機発光素子OLEDを発光させるための電流を供給する。データ線DLは、有機発光素子OLEDのそれぞれの輝度を制御するための輝度データの信号を流す。走査線SLは、有機発光素子OLEDのそれぞれの発光タイミングを制御するための走査信号を流す。これらの配線は、通常、定電圧源に接続されている。

【0012】第1のトランジスタ（以下、「スイッチングトランジスタ」ともいう）Tr1は、ゲート電極が走査線SLに接続され、ドレイン電極（またはソース電極）がデータ線DLに接続され、ソース電極（またはドレイン電極）が第2のトランジスタ（以下、「駆動用トランジスタ」ともいう）Tr2のゲート電極に接続される。本実施の形態では、スイッチングトランジスタは、2つのゲート電極を有するダブルゲート構造をとっているが、別の形態では、シングルゲート構造または3以上のゲート電極を有するマルチゲート構造であってもよい。また、スイッチングトランジスタTr1は、nチャネルトランジスタであってもpチャネルトランジスタであってもよい。

【0013】駆動用トランジスタTr2は、ソース電極（またはドレイン電極）が有機発光素子OLEDの陽極に接続され、ドレイン電極（またはソース電極）が電源供給線Vddに接続される。駆動用トランジスタTr2も、スイッチングトランジスタTr1と同様に、シングルゲート構造であってもマルチゲート構造であってもよく、nチャネルトランジスタであってもpチャネルトランジスタであってもよい。

【0014】有機発光素子OLEDは、陽極が駆動用トランジスタTr2のソース電極（またはドレイン電極）に接続され、陰極は接地される。保持容量Cの一端は、スイッチングトランジスタTr1のドレイン電極（またはソース電極）と駆動用トランジスタTr2のゲート電極に接続され、他端は、図示しない配線に接続され接地される。保持容量Cの他端は、電源供給線Vddに接続されてもよい。

【0015】以上の構成によってなされる動作を説明する。有機発光素子OLEDの輝度データの書きのためには走査線SLの走査信号がハイになると、スイッチングトランジスタTr1がオンとなり、データ線DLに入力された輝度データが駆動用トランジスタTr2および保持容量Cに設定される。すると、その輝度データに応じた電流が駆動用トランジスタTr2のソース-ドレイン間に流れ、この電流が有機発光素子OLEDに流れることにより有機発光素子OLEDが発光する。走査線SLの走査信号がローになると、スイッチングトランジスタTr1がオフとなるが、駆動用トランジスタTr2のゲート電圧は保持されるので、有機発光素子OLEDは引き続き設定された輝度データに応じて発光する。

10

20

30

40

50

【0016】次の走査タイミングになると、再び走査線SLの走査信号がハイになり、スイッチングトランジスタTr1がオンとなって、データ線DLに入力された新たな輝度データが駆動用トランジスタTr2および保持容量Cに設定される。これにより、有機発光素子OLEDは、新たな輝度データに応じて発光する。

【0017】有機発光素子OLEDは、電流が流れることにより発光するので、発光中は有機発光素子OLEDに電流を供給し続ける必要がある。アクティブマトリクス型表示装置など、電源供給線Vddが複数の画素の有機発光素子OLEDに電流を供給する構成になっている場合は、それぞれの有機発光素子OLEDに電流が流れることで電圧降下が生じる。一般に、電源供給線Vddは、定電圧源に接続されているので、定電圧源から離れた画素ほど電圧降下の影響を受けて低い電圧が印加されることになる。駆動用トランジスタTr2のソース電極（またはドレイン電極）に印加される電圧が低下すると、駆動用トランジスタTr2のソース-ドレイン間電圧が低下し、有機発光素子OLEDの動作点が駆動用トランジスタTr2の特性の飽和領域から外れる結果、有機発光素子OLEDに流れる電流が少くなり、輝度が低下してしまう。また、駆動用トランジスタTr2がpチャネル型のトランジスタであった場合は、電源供給線Vddに接続される側の電極がソース電極となるが、電源供給線Vddに電圧降下が生じると、同じ輝度データが画素に設定され同じ電圧がゲート電極に印加されても、定電圧源から離れた画素ほど低い電圧がソース電極に印加されることになり、ゲート-ソース電圧が同じにならず、同じ輝度で発光しないため、輝度のばらつきが生じてしまう。このような輝度の低下およびばらつきは、表示装置の大画面化が進み、より多くの画素がマトリクス状に配置されると、より顕著になることが容易に予想される。電圧降下に起因する輝度の低下およびばらつきを改善することは、表示装置の大画面化、高輝度化のために非常に重要である。

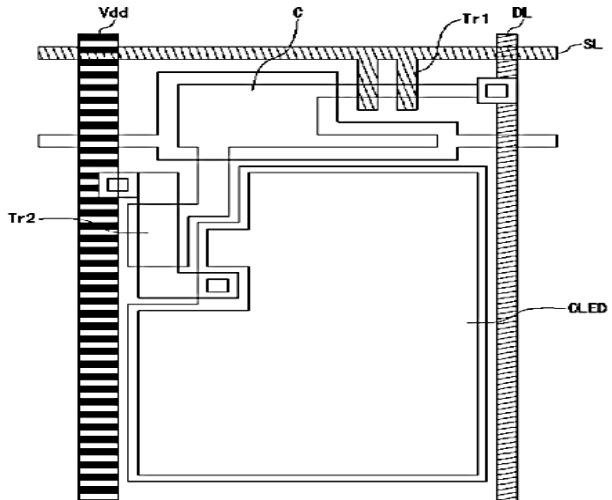

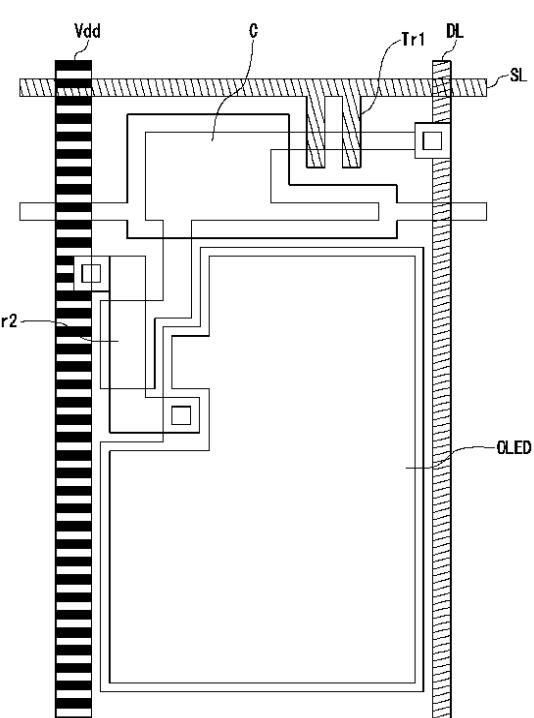

【0018】図2は、第1の実施の形態に係る表示装置100の上面を模式的に示す。図2は、図1と同様に、1画素分の回路が形成された部分の上面を示す。図2に示すように、本実施の形態では、電源供給線Vddの配線の幅を、データ線DLおよび走査線SLの配線の幅よりも広くしている。これにより、電源供給線Vdd、データ線DL、および走査線SLを同種の材料により構成した場合であっても、電源供給線Vddの抵抗をデータ線DLおよび走査線SLの抵抗よりも低く抑えることができる。データ線DLおよび走査線SLは、各画素のトランジスタの電極に電圧信号を送るために設けられており、過渡的に電流は流れますが、定常的に流れることはないので、電圧降下の影響は小さい。このため、これらの配線の幅を電源供給線Vddよりも狭くすることで、有機発光素子OLEDの開口率を向上させることができ

る。

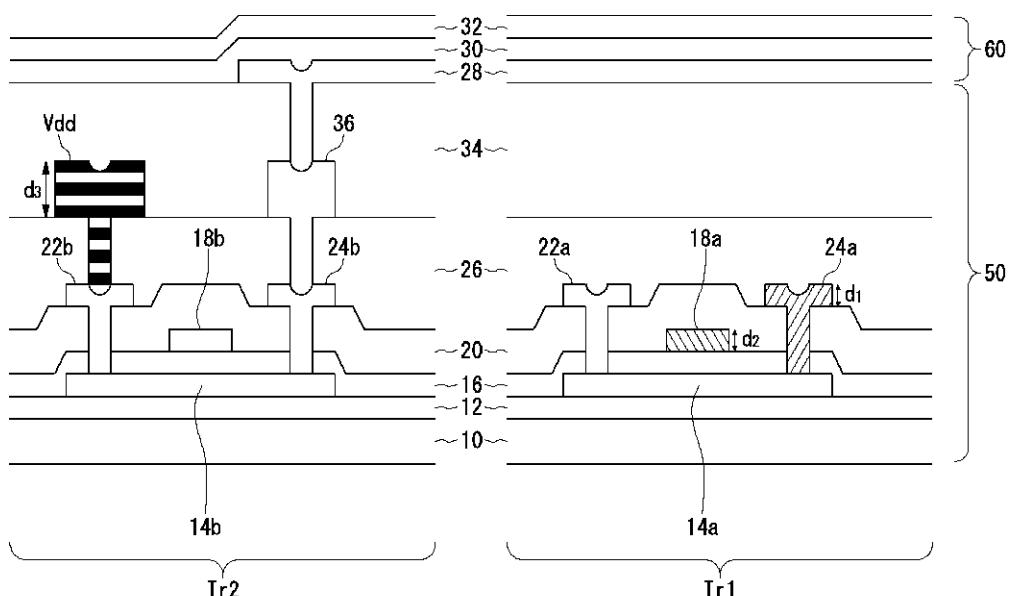

【0019】(第2の実施の形態)図3は、第2の実施の形態に係る表示装置100の断面構造を概略的に示す。図3では、図1に示した1画素分の回路のうち、スイッチングトランジスタTr1、駆動用トランジスタTr2、および有機発光素子OLEDが形成された部分の断面構造を示す。本実施の形態の表示装置100の回路構成は、図1および図2に示した第1の実施の形態の回路と同様であってもよいし、その他任意の回路構成であってもよい。表示装置100は、絶縁性基板10の上に設けられた、絶縁層12、能動層14、ゲート絶縁層16、ゲート電極18、層間絶縁層20、ドレイン電極22、ソース電極24、第1の平坦化層26、および第2の平坦化層34を含むTFT基板50と、画素電極28、発光素子層30、および対向電極32を含む有機発光素子60とを備える。

【0020】この表示装置100を製造する手順を説明する。基板10は、石英、ガラス、無アルカリガラス、ガラスセラミック、シリコン、金属、プラスチックなどの絶縁性材料により形成された基板であってよい。基板10の上に、酸化ケイ素SiO<sub>2</sub>、窒化ケイ素SiN、窒化酸化ケイ素SiO<sub>x</sub>N<sub>y</sub>などの材料を、プラズマCVD法などにより積層し、絶縁層12を形成する。この絶縁層12は、ガラスなどの材料により形成された基板10を用いた場合に、ナトリウムイオンなどの不純物が基板10から能動層14に侵入するのを防ぐために設けられている。このような不純物侵入の恐れがない基板10を用いる場合には、絶縁層12を設けなくてもよい。

【0021】絶縁層12の上に、プラズマCVD法などにより非晶質シリコン(amorphous silicon:以下、「a-Si」ともいう)膜を形成する。つづいて、そのa-Si膜の表面にXeClエキシマレーザビームを照射してアニール処理を行うことにより、a-Si膜を溶融再結晶化して多結晶シリコン(poly-silicon:以下、「p-Si」ともいう)膜に改質する。さらに、p-Si膜を島化エッティングすることにより、能動層14を形成する。

【0022】能動層14の上に、CVD法により酸化ケイ素SiO<sub>2</sub>、窒化ケイ素SiNなどを全面に蒸着し、ゲート絶縁層16を形成する。ゲート絶縁層16の上に、クロム、モリブデンなどの高融点金属からなる導電材料をスパッタ法などにより成膜し、ホトリソグラフィ技術およびドライエッティング技術を用いて、能動層14と重畳するようにゲート電極18を形成する。このとき、このゲート電極18に接続する配線(図示せず)も形成する。走査線SLは、スイッチングトランジスタTr1のゲート電極18aに接続されるため、ゲート電極18aと同じ層に形成されてもよい。このとき、走査線SLの厚みはd2となる。

【0023】つづいて、ゲート電極18をマスクとし

て、p-Siの能動層14に対し、ゲート絶縁層16を通してN型またはP型のイオンを注入する。これにより、能動層14のうちゲート電極18に覆われていない部分にN型またはP型の不純物イオンが注入される。不純物イオンの種類は、形成すべきトランジスタの種別に応じて選択されればよい。ゲート電極18の直下の能動層14は、真性または実質的に真性なp-Si膜のままである。

【0024】さらに、能動層14の幅よりも狭い幅に、ゲート電極18およびゲート絶縁層16を覆うレジストを形成する。つづいて、このレジストをマスクとして再びイオン注入を行う。レジストで覆われていなかった部分の能動層14は、不純物イオンが高濃度に注入されており、ソース領域およびドレイン領域となる。レジストで覆われていた部分の能動層14は、不純物イオンが低濃度に注入された、いわゆるLDD領域となる。

【0025】レジストを除去した後、プラズマCVD法によりSiO<sub>2</sub>、SiNなどを全面に蒸着して、層間絶縁層20を形成する。つづいて、ソース領域およびドレイン領域に対応する位置に、層間絶縁層20を貫通して能動層14に到達するようにコンタクトホールを形成し、そのコンタクトホールにアルミニウムなどの金属を充填してドレイン電極22およびソース電極24を形成する。このとき、ドレイン電極22およびソース電極24に接続する配線(図示せず)も形成する。データ線DLは、スイッチングトランジスタTr1のソース電極(またはドレイン電極)24aに接続されるので、ソース電極(またはドレイン電極)24aと同じ層に形成されてもよい。このとき、データ線DLの厚みはd1となる。

【0026】さらに、その上に、有機樹脂などの材料を堆積させて第1の平坦化層26を形成する。これにより、トランジスタなどの回路を形成した部分を覆い、基板表面を平坦化する。有機発光素子60の形成に先立ってTFT基板50の表面を平坦化しておくことは、有機発光素子60の発光不良を防止するために非常に重要である。

【0027】第1の平坦化層26の、駆動用トランジスタTr2のドレイン電極(またはソース電極)22bおよび24bに対応する位置に、第1の平坦化層26を貫通して電極22bおよび24bに到達するようにコンタクトホールを形成し、その上から金属などの導電性材料を充填し、パターニングすることにより、電源供給線Vddおよび上層の画素電極28とのコンタクト部36を形成する。このとき、電源供給線Vddの厚みd3を、データ線DLの厚みd1および走査線SLの厚みd2よりも厚くすることで、画素の開口面積を減少させずに、電源供給線Vddの断面積を増大させることができ、電源供給線Vdd、データ線DL、および走査線SLを同種の材料により構成した場合であっても、電源供給線V

$d$  の抵抗をデータ線 D L および走査線 S L の抵抗よりも低く抑えることができる。この例のように、電源供給線 V d d を、データ線 D L および走査線 S L を配線した層と異なる層に配線することにより、電源供給線 V d d の厚みを他の配線よりも厚くすることが容易となる。電源供給線 V d d を、データ線 D L または走査線 S L と同じ層に配線するときは、電源供給線 V d d の幅を広くしてもよいし、電源供給線 V d d の配線工程とデータ線 D L または走査線 S L の配線工程を分けて、それぞれが所定の厚みになるように形成してもよいし、双方を一度に形成した後、データ線 D L または走査線 S L をエッチングにより薄くしてもよい。いずれの方法によても、電源供給線 V d d を含む層の厚さを、データ線 D L または走査線 S L を含む層の厚さよりも厚くすることで、電源供給線 V d d の低抵抗化を実現し、電圧降下の影響を軽減することができる。なお、このとき、電源供給線 V d d の厚さを厚くすることに加えて、第1の実施の形態と同様に、電源供給線 V d d の配線幅をデータ線 D L または走査線 S L の配線幅よりも広くし、さらに断面積の増大を図ってもよい。

【0028】第1の平坦化層 2 6 の上に、有機樹脂などの材料を堆積させて第2の平坦化層 3 4 を形成する。第2の平坦化層 3 4 のコンタクト部 3 6 に対応する位置に、第2の平坦化層 3 4 を貫通してコンタクト部 3 6 に到達するようにコンタクトホールを形成し、その上から透明電極材料である酸化インジウム・スズ (Indium Tin Oxide : ITO) を堆積させ、パターン化して画素電極 2 8 を形成する。本実施の形態では、画素電極 2 8 は陽極である。陽極の材料としては、ITOのほか、酸化スズ ( $SnO_2$ )、または酸化インジウム ( $In_2O_3$ ) 等が例示されるが、一般的には、ホール注入効率や表面抵抗の低さから ITO が用いられる。

【0029】画素電極 2 8 の上に、発光素子層 3 0 が形成される。発光素子層 3 0 は、有機発光材料を含む発光層のほか、その上下に正孔輸送層および電子輸送層を設けてもよい。一般に、これらの有機層は、複数の形成室を備えるマルチチャンバー型製造装置にて真空蒸着法を用いて形成される。発光層の材料としては、アルミニウム錯体 (Alq3)、またはキナクリドン誘導体を含むビス (ベンゾキノリノラト) ベリリウム錯体 (bis(1-hydroxybenzo[h]quinolinate) beryllium : Be bq 2) 等が例示される。正孔輸送層の材料としては、N,N'-ジフェニル-N,N'-ジ(3-メチルフェニル)-1,1'-ビフェニル-4,4'-ジアミン (N,N'-diphenyl-N,N'-di(3-methylphenyl)-1,1'-biphenyl-4,4'-diamine : TPD)、4,4',4''-トリス(3-メチルフェニルフェニルアミノ)トリフェニルアミン (4,4',4''-tris(3-methylphenylamino)triphenylamine : MTDAT A)、N,N'-ジ(ナフタレン-1-イル)-N,N'-ジフェニル-ベンジジン (N,N'-Di(naphthalene-1-yl)-N,N'-diphenyl-

benzidine : NPB)、等が例示される。電子輸送層の材料としては、Alq3 または Be bq 2 等が例示される。

【0030】発光素子層 3 0 の上に、対向電極 3 2 が形成される。本実施の形態では、対向電極 3 2 は陰極である。陰極の材料としては、例えば、リチウムを微量に含むアルミニウム合金、マグネシウムインジウム合金、またはマグネシウム銀合金等が例示される。対向電極 3 2 は、電子輸送層側から順に、フッ化リチウム (LiF) 層およびアルミニウム (Al) 層を備えた 2 層構造であってもよい。以上の工程により、本実施の形態の表示装置 100 が製造される。

【0031】(第3の実施の形態) 本実施の形態では、電源供給線 V d d を構成する材料の電気抵抗率を、データ線 D L または走査線 S L を構成する材料の電気抵抗率よりも低くすることにより、電源供給線 V d d の抵抗を低く抑える。本実施の形態の表示装置 100 の回路構成は、図1に示した第1の実施の形態の回路構成と同様であり、回路の動作も第1の実施の形態と同様である。また、本実施の形態の表示装置 100 を製造する方法は、図3を参照して第2の実施の形態で説明した製造方法と同様である。本実施の形態では、電源供給線 V d d をアルミニウム、データ線 D L をアルミニウム - ネオジウム合金、走査線 S L をモリブデンにより、それぞれ構成する。

【0032】摂氏 20 度におけるアルミニウムの電気抵抗率は  $2.69 \mu \Omega \cdot cm$ 、モリブデンの電気抵抗率は  $5.7 \mu \Omega \cdot cm$  である。アルミニウム - ネオジウム合金の電気抵抗率はネオジウムの含有量によって変化するが、総じてアルミニウム単体の電気抵抗率よりも高い。したがって、上述の材料により表示装置 100 の各配線を構成することにより、電源供給線 V d d の抵抗をデータ線 D L および走査線 S L の抵抗よりも低くすることができる。

【0033】本実施の形態では、データ線 D L を構成する材料として、エレクトロマイグレーションを改善するという観点からアルミニウム - ネオジウム合金を用いたが、その他に、アルミニウム単体、アルミニウム - チタン合金、アルミニウム - 銅合金、アルミニウム - シリコン合金などであってもよいし、その他の金属、合金、化合物などであってもよい。また、走査線 S L を構成する材料として、ウイスカ・ヒロックを改善するという観点からモリブデンを用いたが、その他に、クロムやチタンなどの高融点金属、モリブデン - シリコン、チタン - シリコン、タンゲステン - シリコンなどの化合物などであってもよい。電源供給線 V d d を構成する材料は、電気抵抗率が低いものが好ましく、データ線 D L または走査線 S L を構成する材料よりも電気抵抗率の低い材料を選択するのがよい。たとえば、アルミニウムの他、銀、銅、金などであってもよいし、その他の金属、合金、化

合物などであってもよく、多層構造としてもよい。

【0034】このように、本実施の形態では、電源供給線Vddを低抵抗な材料で構成することにより、電源供給線Vddの抵抗を低くし、電圧降下の影響を軽減する。さらに、第1の実施の形態と同様、電源供給線Vddの幅を広くすることにより、または、第2の実施の形態と同様、電源供給線Vddを含む層の厚さを厚くすることにより、または、それら双方を組み合わせることにより、電源供給線Vddの断面積を大きくし、低抵抗化を図ってもよい。

【0035】以上、本発明を実施の形態をもとに説明した。この実施の形態は例示であり、それらの各構成要素や各処理プロセスの組合せにいろいろな変形が可能などと、またそうした変形例も本発明の範囲にあることは当業者に理解されるところである。以下、こうした例を述べる。

【0036】電源供給線Vdd、データ線DL、および走査線SLを配線する層は、上述の例に限られず、いずれの層に配線されてもよい。

【0037】実施の形態では、スイッチングトランジスタTr1および駆動用トランジスタTr2は、ゲート電極18が能動層14の上層にあるトップゲート方式であったが、ゲート電極18が能動層14の下層にあるボトムゲート方式であってもよい。

【0038】実施の形態では、有機発光素子を例にとって説明したが、光学素子は、無機発光素子であってもよく、液晶表示素子であってもよい。実施の形態では、駆動用トランジスタTr2の電極は、有機発光素子60の陽極に接続されていたが、別の形態では、有機発光素子60の陰極に接続されてもよい。

\*【0039】スイッチングトランジスタは、二つ以上直列におかれてもよい。その際、電流増幅率など、それらのトランジスタの特性を異ならせててもよい。例えば、駆動用トランジスタに近い側のスイッチングトランジスタの電流増幅率を低めに設定すれば、漏れ電流を減らす効果が大きい。さらに、これらのスイッチングトランジスタと駆動用トランジスタの特性を変えてもよい。例えば、駆動用トランジスタの電流増幅率を小さくした場合、同じ輝度レンジに対応する設定データのレンジが広がるため、輝度の制御が容易になる。

【0040】

【発明の効果】本発明によれば、表示装置の表示品位を向上させることができる。

【図面の簡単な説明】

【図1】実施の形態に係る表示装置の1画素分の回路構成を示す図である。

【図2】実施の形態に係る表示装置の上面を模式的に示す図である。

【図3】実施の形態に係る表示装置の断面を模式的に示す図である。

【符号の説明】

10 基板、 12 絶縁層、 14 能動層、 16

ゲート絶縁層、 18 ゲート電極、 20 層間絶

縁層、 22 ドレイン電極、 24 ソース電極、

26 平坦化層、 28 画素電極、 30 発光素子

層、 32 対向電極、 50 TFT基板、 60

有機発光素子、 100 表示装置、 Vdd 電源供給

線、 DL データ線、 SL 走査線、 OLEO

有機発光素子。

\*30

【図3】

【図1】

100

【図2】

100

フロントページの続き

F ターム(参考) 3K007 AB02 AB17 BA06 DB03 GA00

5C094 AA04 AA10 AA55 BA03 BA27

CA19 DA13 DB01 DB04 EA04

EA07 EA10 FB01 FB12 FB20

|                |                                                                                                                                                                                                                                                                                                                     |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2003330387A</a>                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2003-11-19 |

| 申请号            | JP2003020588                                                                                                                                                                                                                                                                                                        | 申请日     | 2003-01-29 |

| [标]申请(专利权)人(译) | 三洋电机株式会社                                                                                                                                                                                                                                                                                                            |         |            |

| 申请(专利权)人(译)    | 三洋电机株式会社                                                                                                                                                                                                                                                                                                            |         |            |

| [标]发明人         | 野口幸宏<br>松本昭一郎                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 野口幸宏<br>松本昭一郎                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | H01L51/50 G09F9/30 G09G3/32 H01L27/32 H05B33/14                                                                                                                                                                                                                                                                     |         |            |

| CPC分类号         | H01L27/3276 G09G3/3225 G09G2300/0426 G09G2300/0809 G09G2300/0842 G09G2320/0223<br>H01L2251/558                                                                                                                                                                                                                      |         |            |

| FI分类号          | G09F9/30.330.Z G09F9/30.338 H05B33/14.A G09F9/30.330 G09F9/30.365 G09F9/30.365.Z H01L27/32                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 3K007/AB02 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 5C094/AA04 5C094/AA10 5C094/AA55 5C094/BA03 5C094/BA27 5C094/CA19 5C094/DA13 5C094/DB01 5C094/DB04 5C094/EA04 5C094/EA07 5C094/EA10 5C094/FB01 5C094/FB12 5C094/FB20 3K107/AA01 3K107/BB01 3K107/CC33 3K107/CC36 3K107/DD39 3K107/EE03 3K107/FF04 3K107/FF15 |         |            |

| 代理人(译)         | 森下Kenju                                                                                                                                                                                                                                                                                                             |         |            |

| 优先权            | 2002059557 2002-03-05 JP                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                           |         |            |

## 摘要(译)

解决的问题：减轻由于显示装置中的电压降引起的像素的亮度降低。在显示装置100中，使向有机发光元件OLED供给电流的电源线Vdd的截面积比通过亮度数据的数据线DL和通过扫描信号的扫描线SL的截面积大。这减小了电源线Vdd的电阻并且减小了电压降的影响。