(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-266667

(P2005-266667A)

(43) 公開日 平成17年9月29日(2005.9.29)

(51) Int.Cl.<sup>7</sup>

**G09F 9/00**

**G09F 9/30**

**H05B 33/06**

**H05B 33/10**

**H05B 33/14**

F 1

G09F 9/00

G09F 9/30

G09F 9/30

HO5B 33/06

HO5B 33/10

338

330Z

365Z

HO5B 33/06

HO5B 33/10

テーマコード(参考)

3K007

5C094

5G435

審査請求 未請求 請求項の数 16 O L (全 17 頁) 最終頁に続く

(21) 出願番号

(22) 出願日

特願2004-82477 (P2004-82477)

平成16年3月22日 (2004.3.22)

(71) 出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100086298

弁理士 船橋 國則

(72) 発明者 芝崎 孝宜

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 浅野 慎

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

F ターム(参考) 3K007 AB06 AB11 AB13 AB18 BA06

CC05 DB03 EA00 FA03

最終頁に続く

(54) 【発明の名称】表示装置の製造方法および表示装置

## (57) 【要約】

【課題】駆動電圧の低い状態で、各有機EL素子における非発光欠陥が低減可能であるとともに、発光寿命も長く、生産性にも優れた表示装置の製造方法および表示装置を提供する。

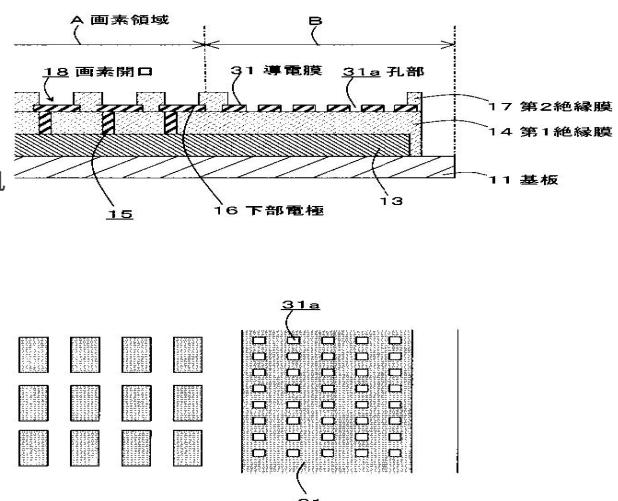

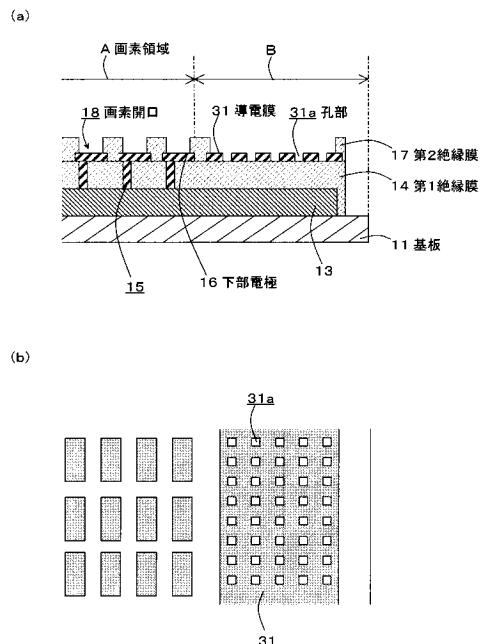

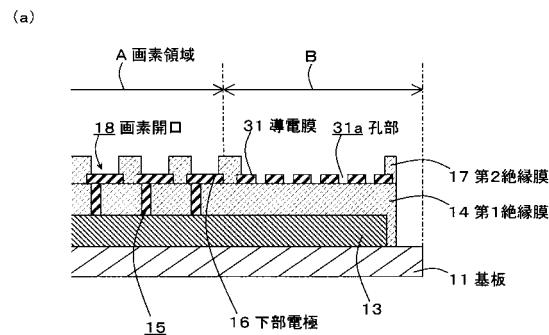

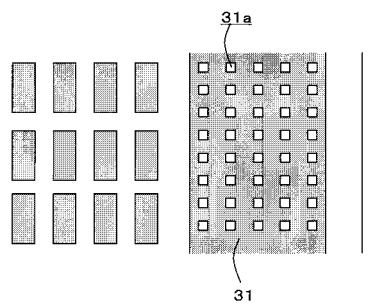

【解決手段】基板11上に下部電極16と上部電極とで有機層を挟持してなる複数の画素が配列形成された画素領域Aを有する表示装置の製造方法および表示装置であって、基板11上に第1絶縁膜14を形成する第1工程と、画素領域A内の第1絶縁膜14上に各画素に対応する複数の下部電極16を形成するとともに、画素領域Aの外側の周辺領域Bの第1絶縁膜14上に導電膜31を形成し、導電膜31に第1絶縁膜14に達する孔部31aを形成する第2工程と、下部電極16および導電膜31が設けられた基板11にベーク処理を行う第3工程とを有することを特徴とする表示装置の製造方法および表示装置である。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

基板上に下部電極と上部電極とで有機層を挟持してなる複数の画素が配列形成された画素領域を有する表示装置の製造方法であって、

前記基板上に絶縁膜を形成する第1工程と、

前記画素領域内の前記絶縁膜上に、前記各画素に対応する複数の前記下部電極を形成するとともに、前記画素領域の外側の前記絶縁膜上に導電膜を形成し、当該導電膜に前記絶縁膜に達する孔部を形成する第2工程と、

前記下部電極および前記導電膜が設けられた前記基板にペーク処理を行う第3工程とを有する

ことを特徴とする表示装置の製造方法。

**【請求項 2】**

請求項1記載の表示装置の製造方法において、

前記下部電極と前記導電膜が同一材料で形成されている

ことを特徴とする表示装置の製造方法。

**【請求項 3】**

請求項1記載の表示装置の製造方法において、

前記第2工程では、

前記導電膜の全域に渡って略均等に配置されるように、複数の前記孔部を形成することを特徴とする表示装置の製造方法。

**【請求項 4】**

請求項1記載の表示装置の製造方法において、

前記第2工程と前記第3工程との間に、

前記下部電極および前記導電膜を覆う状態で、前記絶縁膜上に素子分離絶縁膜を形成し、当該素子分離絶縁膜に前記各下部電極の表面を露出する画素開口を形成するとともに、前記導電膜上の素子分離絶縁膜を除去して前記導電膜の表面を露出する工程を行い、

前記第3工程の後に、

前記下部電極上に有機層を形成し、当該有機層、前記素子分離絶縁膜および前記導電膜を覆う状態で、上部電極を形成することで、当該上部電極と前記導電膜とを接続することを特徴とする表示装置の製造方法。

**【請求項 5】**

請求項4記載の表示装置の製造方法において、

前記導電膜の表面を露出する工程では、

当該導電膜の端部を前記素子分離絶縁膜で覆う状態で、前記導電膜上の素子分離絶縁膜を除去する

ことを特徴とする表示装置の製造方法。

**【請求項 6】**

基板上に、下部電極と上部電極とで有機層を挟持してなる複数の画素が配列形成された画素領域を有する表示装置であって、

前記基板上に設けられた絶縁膜と、

前記画素領域内の前記絶縁膜上に設けられた前記各画素に対応する複数の前記下部電極と、

前記画素領域の外側の前記絶縁膜上に設けられるとともに、前記絶縁膜に達する孔部が設けられた導電膜とを備えた

ことを特徴とする表示装置。

**【請求項 7】**

請求項6記載の表示装置において、

前記下部電極と前記導電膜が同一材料である

ことを特徴とする表示装置。

**【請求項 8】**

10

20

30

40

50

請求項 6 記載の表示装置において、

前記孔部が複数設けられており、前記導電膜の全域に渡って略均等に配置されていることを特徴とする表示装置。

【請求項 9】

請求項 6 記載の表示装置において、

前記絶縁膜上に設けられ、前記導電膜を露出した状態で、前記各下部電極を露出する前記画素開口が設けられた素子分離絶縁膜と、

前記下部電極上に設けられた有機層と、

前記有機層、前記素子分離絶縁膜および前記導電膜を覆う状態で設けられた上部電極とを備え、当該上部電極と前記導電膜とが接続された

10

ことを特徴とする表示装置。

【請求項 10】

請求項 9 記載の表示装置において、

前記導電膜の端部が前記素子分離絶縁膜で覆われている

ことを特徴とする表示装置。

【請求項 11】

基板上に、下部電極と上部電極とで有機層を挟持してなる複数の画素が配列形成された画素領域を有する表示装置の製造方法であって、

前記基板上に、前記各画素に対応する複数の前記下部電極を形成する第 1 工程と、

前記下部電極を覆う状態で、前記基板上に絶縁膜を形成し、当該絶縁膜に前記各下部電極の表面を露出する画素開口を形成する第 2 工程と、

20

前記画素領域の外側の前記絶縁膜上に導電膜を形成するとともに、当該導電膜に前記絶縁膜に達する孔部を形成する第 3 工程と、

前記導電膜が設けられた前記基板にベーク処理を行う第 4 工程とを有する

ことを特徴とする表示装置の製造方法。

【請求項 12】

請求項 11 記載の表示装置の製造方法において、

前記第 3 工程では、

前記導電膜の全域に渡って略均等に配置されるように、複数の前記孔部を形成する

30

ことを特徴とする表示装置の製造方法。

【請求項 13】

請求項 11 記載の表示装置の製造方法において、

前記第 4 工程の後に、

前記下部電極上に有機層を形成し、当該有機層、前記絶縁膜および前記導電膜を覆う状態で、上部電極を形成することで、当該上部電極と前記導電膜とを接続する

ことを特徴とする表示装置の製造方法。

【請求項 14】

基板上に、下部電極と上部電極とで有機層を挟持してなる複数の画素が配列形成された画素領域を有する表示装置であって、

前記画素領域内の前記基板上に設けられた各画素に対応する複数の前記下部電極と、

40

前記基板上に設けられるとともに、前記各下部電極を露出する画素開口が設けられた絶縁膜と、

前記画素領域の外側の前記絶縁膜上に設けられるとともに、前記絶縁膜に達する孔部が形成された導電膜とを備えた

ことを特徴とする表示装置。

【請求項 15】

請求項 14 記載の表示装置において、

前記孔部が複数設けられており、前記導電膜の全域に渡って略均等に配置されていることを特徴とする表示装置。

【請求項 16】

50

請求項 1 4 記載の表示装置において、

前記下部電極上に設けられた有機層と、

前記有機層、前記絶縁膜および前記導電膜を覆う状態で設けられた上部電極とを備え、

当該上部電極と前記導電膜とが接続された

ことを特徴とする表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置の製造方法およびこれによって得られる表示装置に関し、特に、有機電界発光素子（有機EL素子）を備えた表示装置の製造方法および表示装置に関するものである。

10

【背景技術】

【0002】

有機EL素子は、下部電極と上部電極との間に、発光層を含む有機層を挟持してなり、低電圧直流駆動による高輝度発光が可能な発光素子として注目されている。

【0003】

このような有機EL素子を備えたアクティブマトリクス型の表示装置（すなわち、有機ELディスプレイ）は、基板上の各画素に薄膜トランジスタ（Thin film Transistor ( TFT )）を備えている。そして、各画素となる有機EL素子は、このTFTに接続された状態で画素毎にパターン形成された下部電極と、下部電極上に設けられた有機層と、この有機層を覆う状態で設けられた上部電極で構成されている。このうち上部電極は、例えば複数の画素を覆うベタ膜として形成され、複数の画素間に共通の上部電極として用いられている。

20

【0004】

このようなアクティブマトリクス型の表示装置においては、有機EL素子の開口率を確保するために、基板の反対側から光を取り出す上面発光型として構成することが有効になる。このため、上部電極は、光透過性を確保するために、酸化インジウム錫（Indium Tin Oxide (ITO)）、酸化インジウム亜鉛（Indium Zinc Oxide (IZO)）などの透明導電性酸化物あるいはAl, MgAgなどを光透過性を有する程度に薄膜化したものが用いられるが、これらはシート抵抗が高いために電圧降下が増加する。また、有機ELディスプレイの大型化、高輝度化を図るための駆動電流の増加によっても、電圧降下が増加し易い傾向にあった。

30

【0005】

上述したような電圧降下の増加による、有機ELディスプレイの輝度の低下や表示ムラ等の面内輝度の不均一を防止するため、画素開口間の絶縁膜上および画素領域の外側の絶縁膜上に金属材料からなる補助配線を形成し、この補助電極に上部電極を接続させる表示装置の例が報告されている（例えば、特許文献1参照）。

40

【0006】

【特許文献1】特開2002-318556号公報

【0007】

このような補助配線が設けられた表示装置の例を図8に示す。この表示装置10は、上面発光型の有機ELディスプレイであり、基板11上に画素、すなわち有機EL素子（図示省略）が配列された画素領域Aを有している。ここでは、補助配線として、この画素領域Aの外側の周辺領域Bに、画素領域Aを囲う額縁状に導電膜31が配置された例について説明する。この導電膜31は、基板11の端部に設けられた駆動回路12に接続されるとともに、画素共通の上部電極（図示省略）と接続されるものである。

50

【0008】

また、この表示装置10の製造方法について、図9(a)のX-X'断面図を用いて説明する。まず、ガラスなどの絶縁材料からなる基板11上に、複数のTFTが配列形成されたTFTアレイ13を形成する。次に、このTFTアレイ13が形成された基板11上

50

に、スピニコート法によりポジ型感光性ポリベンゾオキサゾールからなる第1絶縁膜14を塗布形成する。その後、露光を行い、現像することで、第1絶縁膜14にTFTと接続するためのコンタクトホール15を形成する。次に、この基板11にベーク処理を行い、ポリベンゾオキサゾールからなる第1絶縁膜14を硬化させる。

## 【0009】

次に、スパッタ法により、コンタクトホール15を埋め込む状態で、第1絶縁膜14上に、ITO膜、Ag合金膜、ITO膜が基板11側から順次積層された導電材料層(図示省略)を成膜する。続いて、通常のリソグラフィ技術によって形成したレジストパターン(図示省略)をマスクに用いたエッチングにより、この導電材料層をパターニングする。これにより、画素領域A内の第1絶縁膜14上に、コンタクトホール15を介してTFTに接続され、各画素に対応する下部電極16を配列形成するとともに、画素領域Aの外側の周辺領域Bに、導電膜31を形成する。この導電膜31は、画素領域Aを囲う額縁状であり、駆動回路12(前記図8(a)参照)と接続させる。ここで、この導電膜31は、後工程で形成する上部電極と接続し、補助配線として機能させることで、表示装置における面内輝度および輝度の均一性を向上させるため、500μm程度以上の幅で設けられる。この導電膜31の幅の上限に関しては、輝度および輝度の均一性のみを考慮する場合には幅は広ければ広いほど好ましい。その後、レジストパターンを除去する。

## 【0010】

次に、下部電極16が設けられた第1絶縁膜14上に、再びスピニコート法によりポジ型感光性ポリベンゾオキサゾールからなる第2絶縁膜17を塗布形成する。その後、露光を行い、現像することで、第2絶縁膜17に、各画素、すなわち、有機EL素子を形成するための画素開口18を形成し、下部電極16の表面を露出するとともに、周辺領域Bの導電膜31の表面も露出する。次に、窒素(N<sub>2</sub>)雰囲気下でこの基板11にベーク処理を行うことでポリベンゾオキサゾールからなる第2絶縁膜17を硬化させた後、酸素(O<sub>2</sub>)プラズマにより、基板11の前処理を行う。

## 【0011】

次いで、図9(b)に示すように、真空雰囲気下で、蒸着法により、各色の有機EL素子32(赤色有機EL素子32R、緑色有機EL素子32G、青色有機EL素子32B)を形成する画素開口18(前記図9(a)参照)内の下部電極16上に、各色の有機層19、すなわち、赤色有機層19R、緑色有機層19G、青色有機層19Bをそれぞれ形成する。

## 【0012】

次に、真空雰囲気を維持し、有機層19上、第2絶縁膜17上および導電膜31上を覆う状態で、例えばフッ化リチウム(LiF)からなる電子注入層(図示省略)を形成する。その後、真空蒸着法により、電子注入層上に半透過性のMgAg合金からなる上部電極20を形成する。これにより、電子注入層を介して、導電膜31と上部電極20とが接続される。

## 【0013】

次いで、スパッタ法により、上部電極20上に、例えば酸化インジウム亜鉛(Indium Zinc Oxide(IZO))からなる透明導電層(図示省略)を形成する。

## 【0014】

その後、化学的気相成長(Chemical Vapor Deposition(CVD))法により、透明導電層上に窒化シリコン(SiN<sub>x</sub>)からなる保護膜21を成膜する。次に、保護膜21上および基板11の周縁部上に、熱硬化性の樹脂22を塗布し、この樹脂22上にガラスからなる基板23を張り合わせた状態で、加熱することで樹脂封止を行う。

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0015】

上述したような表示装置の製造方法では、第1絶縁膜14および第2絶縁膜17は、通常、ポリベンゾオキサゾール等の有機系絶縁膜で形成されるため、水分などを含有した状

10

20

30

40

50

態となり易いことから、成膜後のベーク処理によって硬化させるとともにこれらの膜中に含まれる水分など等を除去している。しかし、基板11の周辺領域Bにおける第1絶縁膜14上に、補助配線として導電膜31を形成する場合には、第2絶縁膜17を成膜した後のベーク処理の際に、第1絶縁膜14上が導電膜31で覆われた状態となる。このため、第1絶縁膜14中に残存している水分などの脱ガスが抑制される傾向にあった。このため、第1絶縁膜14中の水分などにより、画素領域Aの周縁の有機EL素子32から徐々に劣化が進行し、非発光欠陥が生じたり、発光寿命が短くなるといった問題が生じていた。また、有機EL素子32の劣化にともない、駆動電圧が高くなるといった問題も生じていた。

#### 【0016】

さらに、導電膜31で覆われた第1絶縁膜14からの水分などを確実に除去するためには、高温条件または長時間のベーク処理を行う必要があり、生産性の点でも問題があった。

#### 【0017】

このため、駆動電圧の低い状態で、各有機EL素子における非発光欠陥が低減可能であるとともに、発光寿命も長く、生産性にも優れた有機ELディスプレイが望まれていた。

#### 【課題を解決するための手段】

#### 【0018】

上述したような課題を解決するために、本発明における表示装置の第1の製造方法は、基板上に下部電極と上部電極とで有機層を挟持してなる複数の画素が配列形成された画素領域を有する表示装置の製造方法であって、次のような工程を順次行うことと特徴としている。まず、基板上に絶縁膜を形成する工程を行う。次に、画素領域内の絶縁膜上に各画素に対応する複数の下部電極を形成するとともに、画素領域の外側の絶縁膜上に導電膜を形成し、この導電膜に絶縁膜に達する孔部を形成する工程を行う。その後、下部電極および導電膜が設けられた基板にベーク処理を行う。

#### 【0019】

また、このような製造方法により得られる本発明の第1の表示装置は、基板上に、下部電極と上部電極とで有機層を挟持してなる複数の画素が配列形成された画素領域を有する表示装置であって、基板上に設けられた絶縁膜と、画素領域内の絶縁膜上に設けられた各画素に対応する複数の下部電極と、画素領域の外側の絶縁膜上に設けられるとともに、絶縁膜に達する孔部が形成された導電膜とを備えたことを特徴としている。

#### 【0020】

このような表示装置の第1の製造方法およびこれによって得られる第1の表示装置によれば、導電膜に絶縁膜に達する孔部を形成した後、ベーク処理を行うことにより、ベーク処理の際に、この孔部から、導電膜の下層の絶縁膜に含有される水分などが放出され、除去される。このため、例えば上記導電膜が補助配線として設けられており、この導電膜が広い面積を有して形成されたとしても、導電膜の下層の絶縁膜に水分などが残存することが防止され、この水分などに起因する画素、すなわち有機EL素子の劣化が防止される。

#### 【0021】

また、本発明における表示装置の第2の製造方法は、基板上に、下部電極と上部電極とで有機層を挟持してなる複数の画素が配列形成された画素領域を有する表示装置の製造方法であって、次のような工程を順次行うことと特徴としている。まず、画素領域内の基板上に、各画素に対応する複数の下部電極を形成する工程を行う。次に、この下部電極を覆う状態で、基板上に絶縁膜を形成し、絶縁膜に下部電極の表面を露出する画素開口を形成する工程を行う。次いで、画素領域の外側の絶縁膜上に導電膜を形成するとともに、導電膜に絶縁膜に達する孔部を形成する工程を行う。その後、導電膜が設けられた基板にベーク処理を行う。

#### 【0022】

また、このような製造方法により得られる本発明の第2の表示装置は、基板上に、下部電極と上部電極とで有機層を挟持してなる複数の画素が配列された画素領域を有する表示

10

20

30

40

50

装置であって、画素領域内の基板上に設けられた各画素に対応する複数の下部電極と、基板上に設けられるとともに、下部電極を露出する画素開口が設けられた絶縁膜と、画素領域の外側の絶縁膜上に設けられるとともに、絶縁膜に達する孔部が形成された導電膜とを備えたことを特徴としている。

#### 【0023】

このような表示装置の第2の製造方法およびこれによって得られる第2の表示装置によれば、導電膜に絶縁膜に達する孔部を形成した後、ベーク処理を行うことにより、ベーク処理の際に、導電膜の下層の絶縁膜に含有される水分などが、この孔部から脱ガスされる。このため、例えば上記導電膜が補助配線として設けられており、この導電膜が広い面積を有して形成されたとしても、導電膜の下層の絶縁膜に水分などが残存することが防止され、この水分などに起因する有機EL素子の劣化が防止される。

#### 【発明の効果】

#### 【0024】

以上説明したように、本発明における表示装置の製造方法およびこれにより得られる表示装置によれば、絶縁膜に残存した水分などに起因する有機EL素子の劣化が防止されるため、有機EL素子の非発光欠陥を低減することができるとともに発光寿命を向上させることができ、駆動電圧を低く維持することができる。また、高温条件下または長時間のベーク処理を行わなくても、絶縁膜に含まれる水分などが確実に除去されるため、生産性を向上させることができる。

#### 【発明を実施するための最良の形態】

#### 【0025】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。

#### 【0026】

ここでは、上面発光型の有機ELディスプレイを例にとり、各部材の詳細な構成を製造工程順に説明する。なお、背景技術で説明したものと同様の構成には同一の番号を付して説明する。

#### 【0027】

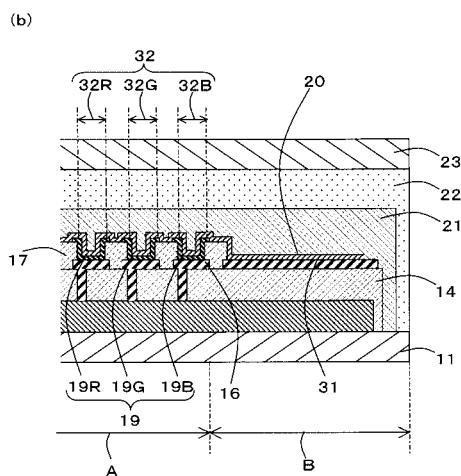

まず、図1(a)に示すように、例えばガラスなどの絶縁材料からなる基板11上に、複数のTFTが配列形成されたTFTアレイ13を形成する。次に、このTFTアレイ13が形成された基板11上に、例えばスピンドルコート法によりポジ型感光性ポリベンゾオキサゾールからなる第1絶縁膜14を塗布形成する。この第1絶縁膜14は、基板11の表面側に生じた凹凸を平坦化する平坦化膜として機能する。そして、この第1絶縁膜14が、請求項1および請求項6の絶縁膜に相当する。なお、ここでは第1絶縁膜14にポリベンゾオキサゾールを使用したが、他にもポジ型感光性ポリイミドなどの絶縁材料を使用しても良い。

#### 【0028】

その後、この第1絶縁膜14に露光を行い、現像することで、第1絶縁膜14にTFTと接続するためのコンタクトホール15を形成する。続いて、この状態の基板11に、N<sub>2</sub>等の不活性ガス雰囲気下でベーク処理を行うことで、ポリベンゾオキサゾールからなる第1絶縁膜14を硬化するとともに、第1絶縁膜14中に含まれる水分などを除去する。

#### 【0029】

次いで、コンタクトホール15を埋め込む状態で、第1絶縁膜14上に、ITO膜、Ag合金膜、ITO膜が基板11側から順次積層された導電材料層(図示省略)を成膜する。この導電材料層の膜厚は、例えば基板11側から、ITO膜/Ag合金膜/ITO膜=約30nm/約100nm/約10nmであることとする。ここで、Ag合金膜が、後工程でこの導電材料層をパターニングして形成する下部電極の反射層となる。

#### 【0030】

続いて、通常のリソグラフィ技術によって形成したレジストパターン(図示省略)をマスクに用いたエッチングにより、この導電材料層をパターニングする。これにより、画素領域A内の第1絶縁膜14上に、コンタクトホール15を介してTFTに接続され、各画

10

20

30

40

50

素に対応する下部電極 16 を配列形成するとともに、画素領域 A の外側の周辺領域 B の第 1 絶縁膜 14 上に、導電膜 31 を形成する。この導電膜 31 は、約 3 mm の幅で画素領域 A を囲う額縁状に形成するとともに、駆動回路（図示省略）と接続させる。ここで、この導電膜 31 は、補助配線として機能し、後工程で形成する上部電極と接続して、配線抵抗を低下させることで、輝度を向上させるとともに、良好な面内輝度分布を得るために設けられるものである。このため、導電性に優れた材料で形成されることが好ましく、その幅は広い方が好ましい。

#### 【 0 0 3 1 】

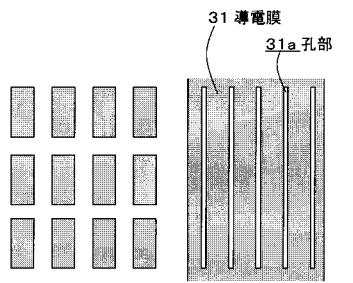

そして、この導電膜 31 に、第 1 絶縁膜 14 に達する状態の複数の孔部 31a を形成する。ここでは、図 1 (b) に示すように、導電膜 31 に、例えば 20  $\mu$ m  $\times$  20  $\mu$ m の矩形状の孔部 31a を幅方向および長さ方向にそれぞれ 100  $\mu$ m の間隔を有して形成することとする。

#### 【 0 0 3 2 】

ここで、孔部 31a は、後工程で、第 1 絶縁膜 14 (前記図 1 (a) 参照) 上にパターン形成される第 2 絶縁膜 17 (前記図 1 (a) 参照) にペーク処理を行う際、導電膜 31 の下層の第 1 絶縁膜 14 に残存する水分などを放出して除去するものである。ここでは、複数の孔部 31a が導電膜 31 に配列形成されることとしたが、例えば 20  $\mu$ m  $\times$  20  $\mu$ m の矩形状の孔部 31a が 1 つであったとしても、その孔部 31a 周囲の第 1 絶縁膜 14 における水分などは除去される。ただし、第 1 絶縁膜 14 に残存する水分などを確実に除去するためには、後工程で形成する上部電極と導電膜 31 とを接続させた後の電圧降下を許容範囲内で抑えられる範囲で、孔部 31a の開口面積が広く、また、開口数が多いほど好ましい。さらに、導電膜 31 の全域にわたって、孔部 31a が均等に配置されることが好ましい。また、孔部 31a の形状については、特に限定されることなく、図 2 に示すように、導電膜 31 にスリット状の孔部 31a を形成してもよい。

#### 【 0 0 3 3 】

次に、再び図 1 (a) に示すように、下部電極 16 および導電膜 31 が設けられた第 1 絶縁膜 14 上に、例えば再びスピンドルコート法によりポジ型感光性ポリベンゾオキサゾールからなる第 2 絶縁膜 17 を塗布形成する。その後、露光を行い、現像、硬化することで、画素領域 A 内に各画素、すなわち、有機 EL 素子を形成するための画素開口 18 を形成して、下部電極 16 の表面を露出するとともに、周辺領域 B の導電膜 31 の表面も露出する。この際、導電膜 31 の端部は、第 2 絶縁膜 17 で覆われた状態とする。これにより、第 2 絶縁膜 17 は画素間を分離するための素子分離膜として機能するとともに、導電膜 31 の端部を覆う保護膜としても機能する。ここで、第 2 絶縁膜 17 が、請求項 1 および請求項 6 の素子分離絶縁膜に相当する。なお、ここでは第 2 絶縁膜 17 にポリベンゾオキサゾールを使用したが、他にもポジ型感光性ポリイミドなどの絶縁材料を使用しても良い。

#### 【 0 0 3 4 】

ここで、導電膜 31 が酸化し易い材料で形成されている場合には、導電膜 31 の端部の酸化を防ぐため、第 2 絶縁膜 17 で導電膜 31 の端部を覆うことによる好ましい。本実施形態では、導電膜 31 が ITO 膜 / Ag 合金膜 / ITO 膜からなる積層膜で形成されているため、導電膜 31 の端部が覆われることにより、酸化され易い Ag 合金膜の酸化が防止される。ただし、導電膜 31 が酸化され難い材料である場合には、この導電膜 31 の端部は露出されていても構わない。

#### 【 0 0 3 5 】

続いて、この状態の基板 11 に、N<sub>2</sub> 等の不活性ガス雰囲気下でペーク処理を行うことで、ポリベンゾオキサゾールを硬化するとともに、第 1 絶縁膜 14 および第 2 絶縁膜 17 に含まれる水分などを除去する。この際、周辺領域 B の第 1 絶縁膜 14 上を覆う導電膜 31 には、複数の孔部 31a が設けられているため、これらの孔部 31a から、第 1 絶縁膜 14 に残存する水分などが放出されて、除去される。

#### 【 0 0 3 6 】

この後、微小異物を除去するために純水でスピンドル洗浄を行った後、真空雰囲気下でペー

10

20

30

40

50

ク処理を行う。これにより、第1絶縁膜14および第2絶縁膜17に吸着した水分が除去される。続いて、真空雰囲気を維持した状態で前処理室に搬送し、O<sub>2</sub>プラズマによって基板11の前処理を行い、次に、真空雰囲気を維持した状態で、後述するように次の工程である有機層の蒸着を行う。上記のようなプロセスにすることで、ベーク処理後の工程は真空雰囲気に維持されることから、大気中の水分などの基板11上への吸着が防止されるため、好ましい。

#### 【0037】

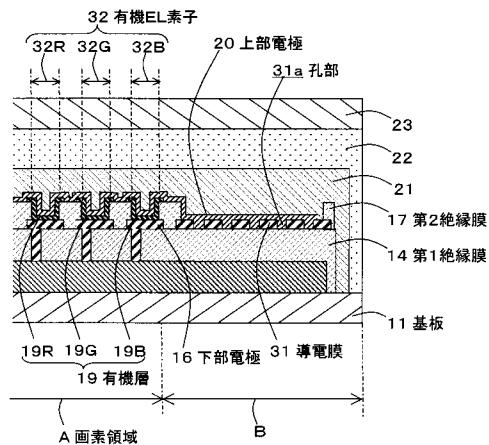

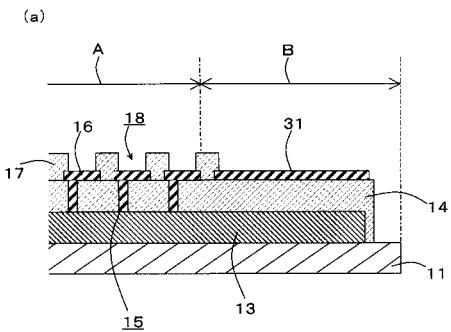

次に、真空雰囲気を維持した状態で、図3に示すように、画素開口18（前記図1（a）参照）内の下部電極16上に、各色の有機EL素子32（赤色有機EL素子32R、緑色有機EL素子32G、青色有機EL素子32B）における有機層19、すなわち、赤色有機層19R、緑色有機層19G、青色有機層19Bをそれぞれ形成する。

#### 【0038】

この場合には、例えば真空雰囲気下で、青色有機層19Bを蒸着するためのチャンバーに基板11を搬送し、基板11上に蒸着マスク（図示省略）をアライメントして、底部に下部電極16が露出された画素開口18の内壁を覆う状態で、正孔注入層、正孔輸送層、発光層、電子輸送層を順次蒸着することで、青色有機層19Bを、約200nmの膜厚で形成する。

#### 【0039】

次いで、真空雰囲気を維持した状態で、赤色有機層19Rを蒸着するためのチャンバーに基板11を搬送し、基板11上に蒸着マスク（図示省略）をアライメントして、青色の有機層19Bと同様に、赤色有機層19Rを約150nmの膜厚で形成する。

#### 【0040】

その後、真空雰囲気を維持した状態で、緑色有機層19Gを蒸着するためのチャンバーに基板11を搬送し、基板11上に蒸着マスク（図示省略）をアライメントして、青色有機層19Bと同様に、緑色有機層19Gを約100nmの膜厚で形成する。

#### 【0041】

以上のように、各有機層19を形成した後、真空雰囲気を維持した状態で、基板11上に蒸着マスク（図示省略）をアライメントして、例えば蒸着法により、有機層19上、第2絶縁膜17上および導電膜31上に、例えばLiFからなる電子注入層（図示省略）を約1nmの膜厚で形成する。その後、この蒸着マスクを用いた真空蒸着法により、電子注入層上に例えば半透過性のMgAg合金からなる上部電極20を約10nmの膜厚で形成する。これにより、電子注入層を介して導電膜31と上部電極20とが接続される。

#### 【0042】

次いで、例えばスパッタ法により、上部電極20を蒸着する際に用いた蒸着マスクを基板11上にアライメントして、上部電極20上に、例えばIZOからなる透明導電層（図示省略）を100nmの膜厚で形成する。

#### 【0043】

その後、CVD法により、マスクをアライメントした状態で、透明導電層上に窒化シリコン（SiN<sub>x</sub>）からなる保護膜21を1umの膜厚で形成する。次に、保護膜21上および基板11の周縁部上に、熱硬化性の樹脂22を塗布し、この樹脂22上に例えばガラスからなる基板23を張り合わせた状態で、加熱することで樹脂封止を行う。

#### 【0044】

以上のような製造方法により、有機層19の発光層で生じた光を、Ag合金膜を含む下部電極16側で反射させ、半透過性のMgAg合金で形成された上部電極20側から取り出す、上面発光型の有機ELディスプレイを得ることができる。

#### 【0045】

このような表示装置の製造方法およびこれにより得られる表示装置によれば、画素領域Aの外側の周辺領域Bに配置される導電膜31に、第1絶縁膜14に達する孔部31aを形成した後、ベーク処理を行うことにより、孔部31aから第1絶縁膜14に含有される水分などが放出され、除去される。このため、第1絶縁膜14に水分などが残存すること

が防止され、水分などに起因する有機EL素子32の劣化が防止される。

【0046】

したがって、有機EL素子32の非発光欠陥を低減することができるとともに発光寿命を向上させることができ、駆動電圧を低く維持することができる。また、高温条件下または長時間のベーク処理を行わなくても、第1絶縁膜14に含まれる水分などが確実に除去されるため、生産性を向上させることができる。

【0047】

また、本実施形態では、下部電極16と導電膜31とが同一材料で形成されることから、下部電極16および導電膜31を同一工程で形成することができるとともに、導電膜31に形成する孔部31aも同一工程で形成することから、製造工程が増えることなく、生産性に優れている。

【0048】

なお、ここでは、導電膜31が画素領域Aを囲う額縁状に形成される例について説明したが、導電膜31の形状は上記に限定されるものではなく、例えば周辺領域Bにおいて、画素領域Aを挟む状態で、ある程度の幅を有する長尺状の導電膜31が駆動回路と接続された状態で配置されたような構成であってもよい。

【0049】

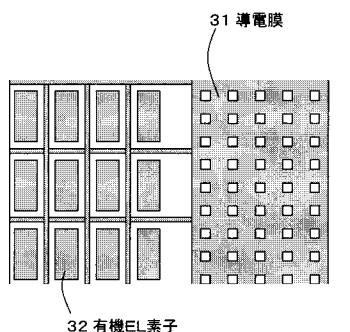

また、周辺領域Bにのみ導電膜31が設けられた例について説明したが、図4に示すように、配列形成された有機EL素子32からなる各画素間の第1絶縁膜14上に格子状に導電膜31が設けられた構成であってもよい。この場合には、図1(a)を用いて説明したように、第1絶縁膜14上に導電材料層を成膜し、画素領域Aに下部電極16を配列形成するとともに、周辺領域Bに導電膜31を形成する際に、各画素間に格子状に配置される状態で、周辺領域Bの導電膜31と接続されるように、導電材料層をパターニングする。

【0050】

(第2実施形態)

第1実施形態では、上面発光型の有機ELディスプレイを例にとり説明したが、本実施形態では、有機層で生じた光を下部電極側から取り出す下面発光型の有機ELディスプレイについて図5(a)および図5(b)を用いて説明する。なお、第1実施形態と同様の構成には、同一の番号を付して説明することとする。

【0051】

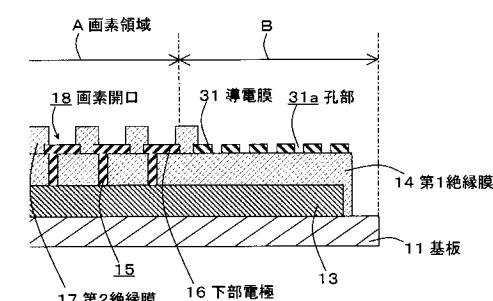

また、図5(a)に示すように、TFTアレイ13が形成された基板11上に、第1絶縁膜14を塗布形成し、第1絶縁膜14にTFTと接続するためのコンタクトホール15を形成した後、基板11にベーク処理を行うまでの工程は、第1実施形態と同様に行うこととする。

【0052】

次に、例えばスパッタ法により、コンタクトホール15を埋め込む状態で、第1絶縁膜14上に、例えばITO膜からなる導電材料層(図示省略)を、約100nmの膜厚で成膜する。続いて、通常のリソグラフィ技術によって形成したレジストパターン(図示省略)をマスクに用いたエッチングにより、この導電材料層をパターニングする。これにより、画素領域A内の第1絶縁膜14上に、コンタクトホール15を介してTFTに接続され、各画素に対応する下部電極16を配列形成する。

【0053】

次いで、例えばスパッタ法により、この下部電極16を覆う状態で、第1絶縁膜14上に、下部電極16を形成するITOよりも導電性の良好なアルミニウムネオジウム(A1Nd)からなる導電材料層(図示省略)を、約300nmの膜厚で成膜する。続いて、通常のリソグラフィ技術によって形成したレジストパターン(図示省略)をマスクに用いたエッチングにより、この導電材料層をパターニングする。この際、下部電極16上にも導電材料層が成膜されるが、A1NdはITOに対して十分にエッチング選択比がとれる材料であるため、問題ない。

## 【0054】

これにより、画素領域Aの外側の周辺領域Bに、第1実施形態と同様に、画素領域Aを囲う形状に、約3mmの幅の導電膜31を形成するとともに、この導電膜31に、第1絶縁膜14に達する状態の複数の孔部31aを形成する。

## 【0055】

次に、下部電極16が設けられた第1絶縁膜14上に、例えば再びスピンドル法によりポジ型感光性ポリベンゾオキサゾールからなる第2絶縁膜17を塗布形成する、その後、露光を行い、現像することで、画素領域A内に各画素、すなわち、有機EL素子を形成するための画素開口18を形成して、下部電極16の表面を露出するとともに、周辺領域Bの導電膜31の表面も露出する。この際、第1実施形態では、導電膜31の端部を第2絶縁膜17で覆うこととしたが、本実施形態で導電膜31に用いられるAlNdは酸化しやすい材料ではないことから、導電膜31の端部は、露出された状態とする。なお、ここでは第2絶縁膜17にポリベンゾオキサゾールを使用したが、他にもポジ型感光性ポリイミドなどの絶縁材料を使用しても良い。

## 【0056】

続いて、この状態の基板11に、第1実施形態と同様に、N<sub>2</sub>等の不活性ガス雰囲気下でベーク処理を行うことで、ポリベンゾオキサゾールを硬化するとともに、第1絶縁膜14および第2絶縁膜17に含まれる水分などを除去する。この際、周辺領域Bの第1絶縁膜14上を覆う導電膜31には、複数の孔部31aが設けられているため、これらの孔部31aから、第1絶縁膜14に残存する水分などが放出されて、除去される。

## 【0057】

この後、微小異物を除去するために純水でスピンドル洗浄を行った後、真空雰囲気下でベーク処理を行う。これにより、第1絶縁膜14および第2絶縁膜17に吸着した水分が除去される。続いて、真空雰囲気を維持した状態で前処理室に搬入し、O<sub>2</sub>プラズマによって基板11の前処理を行い、次に、真空雰囲気を維持した状態で、後述するように次の工程である有機層の蒸着を行う。上記のようなプロセスにすることで、ベーク処理後の工程は真空雰囲気に維持されることから、大気中の水分などの基板11上への吸着が防止されるため、好ましい。

## 【0058】

次に、真空雰囲気を維持した状態で、図5(b)に示すように、第1実施形態と同様の方法により、画素開口18内の下部電極16上に、各色の有機EL素子32(赤色有機EL素子32R、緑色有機EL素子32G、青色有機EL素子32B)における有機層19(赤色有機層19R、緑色有機層19G、青色有機層19B)をそれぞれ形成する。

## 【0059】

次いで、真空雰囲気を維持した状態で、基板11上に蒸着マスク(図示省略)をアライメントして、例えば蒸着法により、各有機層19上、第2絶縁膜17上および導電膜31上に、例えばLiFからなる電子注入層(図示省略)を約1nmの膜厚で形成する。その後、この蒸着マスクを用いた真空蒸着法により、電子注入層上に例えばアルミニウム(A1)からなる反射性を有する上部電極20を約100nmの膜厚で形成する。これにより、電子注入層を介して導電膜31と上部電極20とが接続される。

## 【0060】

その後、CVD法により、マスクをアライメントした状態で、上部電極20上にSiN<sub>x</sub>からなる保護膜21を1umの膜厚で形成する。次に、保護膜21上および基板11の周縁部上に、熱硬化性の樹脂22を塗布し、この樹脂22上に例えばガラスからなる基板23を張り合わせた状態で、加熱することで樹脂封止を行う。

## 【0061】

以上のような製造方法により、有機層19の発光層で生じた光を、A1からなる上部電極20側で反射させ、透過性のITO膜からなる下部電極16側から取り出す、有機ELディスプレイを得ることができる。

## 【0062】

10

20

30

40

50

このような製造方法およびこれによって得られる表示装置であっても、画素領域Aの外側の周辺領域Bに配置される導電膜31に、第1絶縁膜14に達する孔部31aを形成することから、第1実施形態と同様の効果を奏することができる。

【0063】

また、本実施形態によれば、導電膜31を下部電極16よりも導電性の良好な材料で形成することにより、この導電膜31を上部電極20と接続して、配線抵抗を低下させることで、輝度を向上させるとともに、良好な面内輝度分布を得ることができる。

【0064】

なお、本実施形態のように、導電膜31を下部電極16とは異なる材料で形成する製造方法は、第1実施形態で説明した上面発光型の表示装置でも適用可能である。ただし、特に、下面発光型の表示装置であって、下部電極16が陽極となる構成の場合には、下部電極16に透過性を有するITO膜が用いられることが多く、ITO膜は比較的抵抗の高い材料であることから、下部電極16よりも高い導電性を有する材料で、導電膜31を形成することが好ましい。

【0065】

(変形例)

上述したように、下部電極16よりも高い導電性を有する材料で導電膜31を形成する場合には、第2絶縁膜17上に導電膜31を形成してもよい。この場合の表示装置の製造方法について、第2実施形態と同様に、下面発光型の表示装置を例にとり、図6を用いて説明する。ここで、TFTアレイ13が形成された基板11上に、第1絶縁膜14を塗布形成し、第1絶縁膜14にTFTと接続するためのコンタクトホール15を形成した後、基板11にペーク処理を行うまでの工程は、図5(a)を用いて説明した第2実施形態と同様の方法で行うこととする。また、ここまで構成が、請求項11および請求項14の基板に相当する。

【0066】

次に、図6に示すように、第2実施形態と同様の方法により、画素領域A内の第1絶縁膜14上に、コンタクトホール15を介してTFTに接続され、各画素に対応する下部電極16を配列形成する。次いで、下部電極16が設けられた第1絶縁膜14上に、例えば再びスピニコート法によりポジ型感光性ポリベンゾオキサゾールからなる第2絶縁膜17を塗布形成する。この第2絶縁膜17が、請求項11および請求項14の絶縁膜に相当する。なお、ここでは第2絶縁膜17にポリベンゾオキサゾールを使用したが、他にもポジ型感光性ポリイミドなどの絶縁材料を使用しても良い。

【0067】

その後、露光を行い、現像することで、画素領域A内に各画素、すなわち、有機EL素子32を形成するための画素開口18を形成して、下部電極16の表面を露出する。続いて、この状態の基板11に、N<sub>2</sub>等の不活性ガス雰囲気下でペーク処理を行うことで、ポリベンゾオキサゾールを硬化するとともに、第1絶縁膜14および第2絶縁膜17に含まれる水分などを除去する。

【0068】

次に、例えばスパッタ法により、下部電極16上および第2絶縁膜17上に、下部電極16を形成するITOよりも導電性の良好なAlNdからなる導電材料層(図示省略)を、約300nmの膜厚で成膜する。この際、画素開口18内に露出された下部電極16上にも導電材料層が成膜されるが、AlNdはITOに対して十分にエッティング選択比がとれる材料であるため、問題ない。

【0069】

続いて、通常のリソグラフィ技術によって形成したレジストパターン(図示省略)をマスクに用いたエッティングにより、この導電材料層をパターニングする。これにより、画素領域Aの外側の周辺領域Bに、画素領域Aを囲う形状に、約3mmの幅の導電膜31を形成するとともに、この導電膜31に、第2絶縁膜14に達する状態の複数の孔部31aを形成する。ここでは、第1実施形態と同様に、この導電膜31に、例えば20μm×20

10

20

30

40

50

$\mu\text{m}$ の矩形状の孔部31aを幅方向および長さ方向にそれぞれ100 $\mu\text{m}$ の間隔を有して形成することとする。その後、レジストパターンを除去する。

【0070】

この後、微小異物を除去するために純水でスピン洗浄を行った後、真空雰囲気下でこの状態の基板11にベーク処理を行う。これにより、第1絶縁膜14および第2絶縁膜17に吸着した水分が除去される。この際、周辺領域Bの第2絶縁膜17上を覆う導電膜31には、複数の孔部31aが設けられているため、これらの孔部31aから第1絶縁膜14および第2絶縁膜17に残存する水分などが放出されて、除去される。続いて、真空雰囲気を維持した状態で前処理室に搬送し、O<sub>2</sub>プラズマによって基板11の前処理を行い、次に、真空雰囲気を維持した状態で、後述するように次の工程である有機層の蒸着を行う。上記のようなプロセスにすることで、ベーク処理後の工程は真空雰囲気に維持されることから、大気中の水分などの基板11上への吸着が防止されるため、好ましい。

【0071】

この後の工程は、真空雰囲気を維持した状態で、図3(b)を用いて説明した第2実施形態と同様の方法により行うこととする。

【0072】

このような表示装置の製造方法およびこれによって得られる表示装置であっても、画素領域Aの外側の周辺領域Bに配置される導電膜31に、第2絶縁膜17に達する孔部31aを形成した後、この状態の基板11にベーク処理を行うことから、第1実施形態と同様の効果を奏すことができる。

【0073】

なお、上述したような第2絶縁膜17上に導電膜31が配置された構成の変形例については、第1実施形態で説明した上面発光型の表示装置においても適用可能である。また、このような構成の表示装置において、図4を用いて説明したような、画素間に補助配線が形成された構成をとる場合には、第2絶縁膜14上に導電材料層を成膜し、パターニングして、周辺領域Bに画素領域Aを囲う状態の導電膜31を形成する際に、各画素間に格子状に配置される状態で、周辺領域Bの導電膜31と接続されるように、導電材料層をパターニングする。

【0074】

以上説明した表示装置については、下部電極16を陽極とし、上部電極20を陰極とした構成について説明したが、下部電極16が陰極であり、上部電極20が陽極であってもよい。この場合には、下部電極16が露出された画素開口18内に、電子注入層を介して、電子輸送層、発光層、正孔輸送層、正孔注入層の順に積層された有機層19を形成し、この状態の基板11の全面を覆う状態で、上部電極20を形成する。

【0075】

また、第1実施形態では上面発光型の表示装置、第2実施形態では下面発光型の表示装置について説明したが、下部電極16と上部電極20を半透過性の材料で形成した、両面から発光光を取り出すような両面発光型の表示装置であっても、本発明は適用可能である。

【実施例】

【0076】

さらに、本発明の具体的な実施例について説明する。

【0077】

(実施例1)

上記第1実施形態と同様の方法により、図3に示す上面発光型の表示装置を製造した。また、これに対する比較例として、第1絶縁膜14の周辺領域Bに、孔部31aが設けられていない状態の導電膜31を、画素領域Aを囲う形状で約3mmの幅で形成した表示装置を製造した。

【0078】

これらの表示装置について、80の恒温機内に約1000h保存した場合の非点灯画

10

20

30

40

50

素数の経時的变化について、図7のグラフに示す。このグラフは、横軸に保存時間、縦軸に非点灯画素数を示している。このグラフに示すように、実施例1の表示装置については、約1000h経過した後も非点灯画素数が増加することなく良好な画像表示が得られたが、比較例1の表示装置は、経時的に非点灯画素数が増加し、画像表示が悪化することが確認された。

【0079】

(実施例2)

上記第2実施形態と同様の方法により、図5(b)に示す下面発光型の表示装置を製造した。また、これに対する比較例2として、第1絶縁膜14の周辺領域Bに、孔部31aが設けられていない状態の導電膜31を、画素領域Aを囲う形状で約3mmの幅で形成した表示装置を製造した。

【0080】

これらの表示装置について、80の恒温機内に約1000h保存した場合の非点灯画素数の経時的变化について、図7のグラフに示す。このグラフに示すように、実施例2の表示装置については、約1000h経過後も非点灯画素数が増加することなく良好な画像表示が得られたが、比較例2の表示装置は、経時的に非点灯画素数が増加し、画像表示が悪化することが確認された。

【0081】

これらの結果から、実施例1、2の表示装置は比較例1、2の表示装置と比較して、非点灯画素数の増加が防止されるため、非発光欠陥が少なく、発光寿命も長いことが示唆された。

【図面の簡単な説明】

【0082】

【図1】本発明の表示装置の製造方法に係る第1実施形態を説明するための断面図(a)および上面図(b)である。

【図2】本発明の表示装置の製造方法に係る第1実施形態を説明するための上面図である。

【図3】本発明の表示装置の製造方法に係る第1実施形態を説明するための断面図である。

【図4】本発明の表示装置の製造方法に係る第1実施形態を説明するための上面図である。

【図5】本発明の表示装置の製造方法に係る第2実施形態を説明するための断面図である。

【図6】本発明の表示装置の製造方法に係る第2実施形態の変形例を説明するための断面図である。

【図7】本発明の実施例および比較例における非点灯画素数の経時変化を示すグラフである。

【図8】従来の表示装置の製造方法を説明するための上面図である。

【図9】従来の表示装置の製造方法を説明するための断面図である。

【符号の説明】

【0083】

11…基板、14…第1絶縁膜、16…下部電極、17…第2絶縁膜、19…有機層、20…上部電極、31…導電膜、31a…孔部、32…有機EL素子、A…画素領域

【図1】

(b)

【図2】

【図3】

【図4】

【図5】

(b)

【図6】

【図8】

【図7】

【図9】

## フロントページの続き

(51)Int.Cl.<sup>7</sup>

H 05 B 33/22

F I

H 05 B 33/14

A

H 05 B 33/22

Z

テーマコード(参考)

F ターム(参考) 5C094 AA04 AA38 AA42 AA48 AA55 BA03 BA12 BA27 CA19 CA24

DA13 DB01 EA04 EA05 EA07 FA01 FB01 FB20 GB10

5G435 AA13 AA17 BB05 CC09 CC12 HH12 HH14 KK05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于制造显示装置的方法和设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP2005266667A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2005-09-29 |

| 申请号            | JP2004082477                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2004-03-22 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 芝崎孝宜<br>浅野慎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 芝崎 孝宜<br>浅野 慎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | H05B33/06 G09F9/00 G09F9/30 H01J1/62 H01L27/32 H01L51/50 H05B33/10 H05B33/14 H05B33/22                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| CPC分类号         | H01L27/3276 H01L27/3246 H01L27/3258 H01L51/524 H01L51/5253                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| FI分类号          | G09F9/00.338 G09F9/30.330.Z G09F9/30.365.Z H05B33/06 H05B33/10 H05B33/14.A H05B33/22.Z<br>G09F9/30.330 G09F9/30.365 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 3K007/AB06 3K007/AB11 3K007/AB13 3K007/AB18 3K007/BA06 3K007/CC05 3K007/DB03 3K007/<br>/EA00 3K007/FA03 5C094/AA04 5C094/AA38 5C094/AA42 5C094/AA48 5C094/AA55 5C094/BA03<br>5C094/BA12 5C094/BA27 5C094/CA19 5C094/CA24 5C094/DA13 5C094/DB01 5C094/EA04 5C094/<br>/EA05 5C094/EA07 5C094/FA01 5C094/FB01 5C094/FB20 5C094/GB10 5G435/AA13 5G435/AA17<br>5G435/BB05 5G435/CC09 5G435/CC12 5G435/HH12 5G435/HH14 5G435/KK05 3K107/AA01 3K107/<br>/BB01 3K107/CC12 3K107/CC21 3K107/CC26 3K107/CC45 3K107/DD89 3K107/DD90 3K107/EE03<br>3K107/GG26 |         |            |

| 代理人(译)         | 船桥 国则                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 其他公开文献         | JP4608921B2<br>JP2005266667A5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

## 摘要(译)

要解决的问题：提供一种制造显示装置的方法，该方法允许各个有机EL元件的非发光缺陷在低驱动电压状态下减少并且具有长的发光寿命并且具有优异的生产率，并且提供显示设备。SOLUTION：制造具有像素区域A的显示装置的方法，其中具有保持在下电极16和上电极之间的有机层的多个像素排列在基板11上；第一步骤是在基板11上形成第一绝缘膜14；第二步骤，在像素区域A内形成与第一绝缘膜14上的各个像素对应的多个下电极16，在像素区域外侧的周边区域B中的第一绝缘膜14上形成导电膜31A，和在导电膜31中形成延伸到第一绝缘膜14的孔部分；以及第三步骤，烘烤具有下电极16和形成在其上的导电膜31的基板11。Z