(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3997109号

(P3997109)

(45) 発行日 平成19年10月24日(2007.10.24)

(24) 登録日 平成19年8月10日(2007.8.10)

(51) Int.C1.

F 1

|            |           |           |      |

|------------|-----------|-----------|------|

| GO9G 3/30  | (2006.01) | GO9G 3/30 | J    |

| GO9G 3/20  | (2006.01) | GO9G 3/20 | 611H |

| HO1L 51/50 | (2006.01) | GO9G 3/20 | 611Z |

|            |           | GO9G 3/20 | 612E |

|            |           | GO9G 3/20 | 624B |

請求項の数 4 (全 17 頁) 最終頁に続く

(21) 出願番号

特願2002-132287 (P2002-132287)

(22) 出願日

平成14年5月8日(2002.5.8)

(65) 公開番号

特開2003-323156 (P2003-323156A)

(43) 公開日

平成15年11月14日(2003.11.14)

審査請求日

平成17年4月28日(2005.4.28)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100096828

弁理士 渡辺 敏介

(74) 代理人 100110870

弁理士 山口 芳広

(72) 発明者 川崎 素明

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者 大村 昌伸

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

審査官 西島 篤宏

最終頁に続く

(54) 【発明の名称】 E L 素子駆動回路及び表示パネル

## (57) 【特許請求の範囲】

## 【請求項 1】

注入電流で発光動作するエレクトロルミネッセンス(E L)素子を発光させるE L素子駆動回路において、

E L素子と、第1、第2及び第3のトランジスタと、コンデンサーと、第1、第2及び第3のスイッチと、を少なくとも備え、

前記第1トランジスタと第2トランジスタとは、第1主電極同士及びゲート電極同士が互いに接続され、

前記コンデンサーは、前記第1トランジスタの第1主電極とゲート電極との間に接続され、

前記E L素子は、前記第1トランジスタの第2主電極に接続され、

前記第1スイッチは、前記第2トランジスタの第2主電極とゲート電極との間に接続され、

前記第2スイッチは、前記E L素子への注入電流を規定する信号電流を供給するための信号供給線と前記第2トランジスタの第2主電極との間に接続され、

前記第3トランジスタは、第1主電極が電源に接続され、第2主電極が前記第1トランジスタの第1主電極に接続され、第1主電極と第2主電極との間の電位差により所定の方向に電流が流れるようにゲート電極と第1主電極又は第2主電極とが短絡され、

前記第3スイッチは、電源と前記第1トランジスタの第1主電極との間に接続され、

前記第1スイッチ及び第2スイッチが短絡されているときに前記第3スイッチを開放させ

、第1スイッチ及び第2スイッチが開放しているときは前記第3スイッチを短絡させるように構成されていることを特徴とするE L素子駆動回路。

【請求項2】

請求項1に記載のE L素子駆動回路をマトリクス状に複数接続したことを特徴とする表示パネル。

【請求項3】

請求項1に記載のE L素子駆動回路において、該E L素子駆動回路が少なくとも画素表示回路と信号供給回路とを含み、

前記画素表示回路は、前記E L素子と、前記第1及び第2のトランジスタと、前記コンデンサーと、前記第1、第2及び第3のスイッチと、を含み、さらに第4のスイッチを備えた回路であり、

前記信号供給回路は、前記第3のトランジスタを含み、

前記画素表示回路と前記信号供給回路とは、少なくともノイズ抑制線と前記信号供給線により接続され、

前記第3トランジスタの第2主電極と前記第1トランジスタの第1主電極とは、前記ノイズ抑制線と前記第4スイッチとを介して接続され、

前記第1スイッチ及び第2スイッチが短絡されているときに前記第3スイッチを開放し前記第4スイッチを短絡し、第1スイッチ及び第2スイッチが開放しているときは前記第3スイッチを短絡し前記第4スイッチを開放させるように構成されていることを特徴とするE L素子駆動回路。

10

20

【請求項4】

少なくとも請求項3に記載のE L素子駆動回路を複数含み、画素表示回路はマトリクス状に接続され、該マトリクス状に接続された画素表示回路のうち1ラインに属する画素表示回路を1組として、各組の画素表示回路を各組毎に1つずつ配置された信号供給回路のそれぞれに共通に接続したことを特徴とする表示パネル。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、電流を注入して発光するエレクトロルミネッセンス素子の駆動回路に関するものである。

30

【0002】

【従来の技術】

エレクトロルミネッセンス素子（以後E L素子と言う）は、E L素子を含む画素表示回路をマトリクス状に複数配置した表示パネル型画像表示システム（以後表示パネルと言う）等に応用されている。一般に表示パネルは大面積であり単結晶シリコン基板上に形成できない為、ガラス基板上に形成された薄膜トランジスタ（TFT）プロセスで形成される。

【0003】

このE L素子の駆動回路には、主に電圧設定方式と電流設定方式との2つの方式が存在する。

【0004】

40

〔電圧設定方式〕

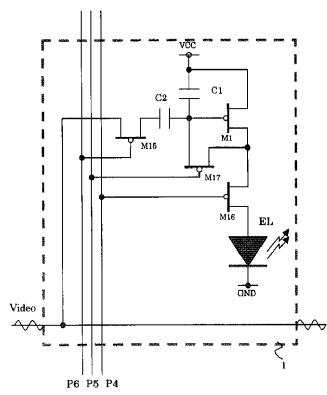

先ず図9を用いて電圧設定方式を説明する。図9は従来の電圧設定方式による画素表示回路の回路図である。

【0005】

映像信号を入力するための信号供給線V i d e oは制御パルスP 6によってゲート電極が制御されたMOSトランジスタM 15（本明細書中ではMOSトランジスタをMの略記号にて表す）のソース電極（M 15 / S）（本明細書中ではMOSトランジスタのソース電極を / S、ドレイン電極を / D、ゲート電極を / Gの略記号にて表す）に入力され、M 15のドレイン電極（M 15 / D）はコンデンサーC 2に接続される。コンデンサーC 2の他端は電源V C Cに一端が接続されたコンデンサーC 1に接続されるとともに、ソース電

50

極が電源 V C C に接続された M 1 のゲート電極 ( M 1 / G ) と制御パルス P 5 によってゲートが制御された M 1 7 / S に接続される。 M 1 / D 及び M 1 7 / D はゲートが制御パルス P 4 で制御された M 1 6 / S に接続され、 M 1 6 / D は E L 素子の電流注入端子に接続され、 E L 素子の他端は接地 G N D に接続される。

#### 【 0 0 0 6 】

表示パネルにおいて画素表示回路 1 は多数配列され、例えば Q V G A ( 3 2 0 × 2 4 0 ) の場合、信号供給線 V i d e o は 2 4 0 個の画素表示回路 1 に引き回され接続され、制御パルス P 4 ~ P 6 は 3 2 0 個の画素表示回路 1 に引き回され接続される。

#### 【 0 0 0 7 】

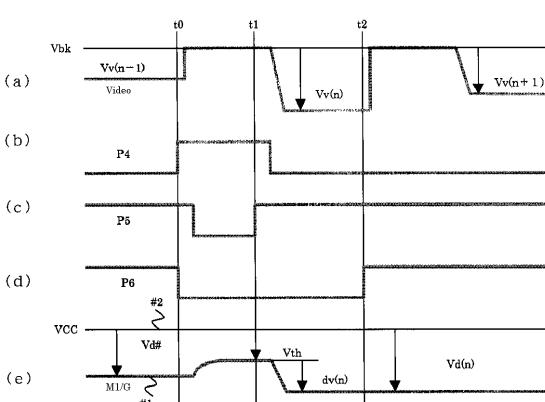

図 9 の画素表示回路 1 の動作を図 1 0 のタイムチャートを使用して説明する。図 1 0 ( a ) ~ ( e ) は、各々、信号供給線 V i d e o 、制御パルス P 4 、制御パルス P 5 、制御パルス P 6 及び M 1 / G の電圧状態を示す。

#### 【 0 0 0 8 】

( 時刻 t 0 において )

信号供給線 V i d e o の電圧は一行前の画素表示回路 1 の発光設定を行う信号レベル V v ( n - 1 ) であり、 P 4 = L 、 P 5 = H 、 P 6 = H から M 1 5 = O F F 、 M 1 6 = O N 、 M 1 7 = O F F であり、 M 1 / G の電圧は該当画素表示回路 1 が前回制御されてコンデンサー C 1 に充電された電圧 V d # に保持されており、この電圧 V d # によって決定される電流が E L 素子に注入され E L 素子は発光している。

#### 【 0 0 0 9 】

( 時刻 t 0 において )

P 4 = H 、 P 6 = L になり M 1 5 = O N 、 M 1 6 = O F F になる。続いて信号供給線 V i d e o を黒レベル V b k ( 最大電圧 ) にし、続いて P 5 = L にして M 1 7 = O N にする。この時点において M 1 は自己放電状態になり、コンデンサー C 1 の電圧は放電され M 1 / G の電圧は上昇する。

#### 【 0 0 1 0 】

ところで M O S トランジスタの電流電圧特性は 1 ) 式の五極管特性で概略示すことができる。

#### 【 0 0 1 1 】

【 数 1 】

$$\begin{aligned} I_{d s} &= k \times \Delta V \\ \Delta V &= V_{g s} - V_{t h} \end{aligned} \quad \boxed{1)$$

#### 【 0 0 1 2 】

ここで、 I d s はドレイン電流、 k は駆動計数、 V g s はゲート・ソース間電圧、 V t h はしきい値電圧である。

#### 【 0 0 1 3 】

1 ) 式から理解できるように V g s = V t h に近づくと I d s は小さくなるため、 M 1 の自己放電動作は弱くなる。従って M 1 / G は図 1 0 ( e ) に示すように V t h に漸近する。さらにコンデンサー C 2 は端子間電圧が ( V c c - V t h - V b k ) になるように放電される。

#### 【 0 0 1 4 】

( 時刻 t 1 において )

P 5 = H となるため M 1 7 = O F F になり、続いて P 4 = L となるため M 1 6 = O N になり、続いて信号供給線 V i d e o を所望レベル V v ( n ) 下降させて M 1 / G の電圧を 2 ) 式で示される電圧 d v ( n ) だけ下降させる。

#### 【 0 0 1 5 】

【 数 2 】

10

20

30

40

$$d v (n) = [C_2 \div (C_1 + C_2)] \times V_v (n) \quad 2)$$

## 【0016】

2) 式中では、C<sub>1</sub>、C<sub>2</sub>は、コンデンサーC<sub>1</sub>、C<sub>2</sub>の電気容量を表している。

## 【0017】

d v (n)はV v (n)の遷移速度に基本的に依存しない。d v (n)は1)式のVに相当しこれによってトランジスタM<sub>1</sub>は電流をEL素子に注入する。

## 【0018】

(時刻t<sub>2</sub>において)

P<sub>6</sub> = HとなるためM<sub>15</sub> = OFFになり、引き続き該当トランジスタM<sub>1</sub>は電流をEL素子に注入して発光動作を次回の発光設定動作まで持続する。時刻t<sub>2</sub>以降は次行の画素表示回路1に対して同様な発光設定動作を行う。 10

## 【0019】

以上述べた図9の画素表示回路1の発光設定動作においては、一旦M<sub>1</sub> / GをV<sub>th</sub>電圧である黒レベルにリセットしてから設定電圧V<sub>v</sub>を入力し、2)式で示される駆動電流を発生する誤差電圧d v (n)をM<sub>1</sub> / Gに設定できる。このため表示パネルの各画素表示回路1内の各トランジスタM<sub>1</sub>のTFTプロセスによって助長されるV<sub>th</sub>のバラツキ及び配線抵抗による各電源V<sub>CC</sub>の電位変動に影響されること無くEL素子への注入電流を設定できる。

## 【0020】

20

## 〔電流設定方式〕

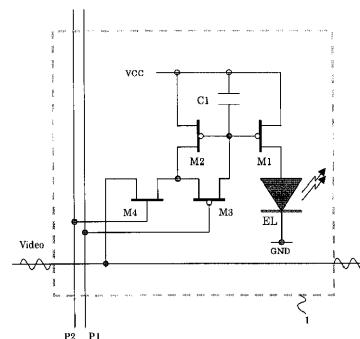

次に図6を用いて電流設定方式を説明する。図6は従来の電流設定方式による画素表示回路の回路図である。

## 【0021】

信号供給線V<sub>ideo</sub>には、入力映像電圧信号を信号供給回路によって電流信号に変換した映像信号電流が入力される。信号供給線V<sub>ideo</sub>はゲートが制御パルスP<sub>2</sub>で制御されたM<sub>4</sub> / Sに接続され、M<sub>4</sub> / Dはソース電極が電源V<sub>CC</sub>に接続されたM<sub>2</sub> / Dとゲートを制御パルスP<sub>1</sub>で制御されたM<sub>3</sub> / Sとに接続される。M<sub>2</sub> / Gは一端を電源V<sub>CC</sub>に接続されたコンデンサーC<sub>1</sub>とM<sub>3</sub> / Dとソース電極が電源V<sub>CC</sub>に接続されたM<sub>1</sub> / Gとに接続される。M<sub>1</sub> / DはEL素子の電流注入端子に接続され、EL素子の他端は30接地GNDされる。

## 【0022】

図6の画素表示回路1の動作を図7のタイムチャートを使用して説明する。図7(a)~(d)は、各々、信号供給線V<sub>ideo</sub>に供給される電流映像信号、制御パルスP<sub>1</sub>、制御パルスP<sub>2</sub>、M<sub>1</sub> / G電圧を示す。

## 【0023】

(時刻t<sub>0</sub>以前において)

信号供給線V<sub>ideo</sub>には一行前の画素表示回路1への設定電流I<sub>d</sub>(n-1)になっており、また、P<sub>1</sub> = H、P<sub>2</sub> = LからM<sub>3</sub> = OFF及びM<sub>4</sub> = OFFになっている。またM<sub>1</sub> / Gには前回発光設定動作によって決定された電圧V<sub>d#</sub>(n)が電源V<sub>CC</sub>から与えられており、V<sub>d#</sub>(n)によって決定されるM<sub>1</sub>からの出力電流が該当EL素子に注入され発光している。 40

## 【0024】

(時刻t<sub>0</sub>において)

信号供給線V<sub>ideo</sub>は図6の該当画素表示回路1の発光設定をする電流I<sub>d</sub>(n)に変化するとともに、P<sub>1</sub> = L、P<sub>2</sub> = HからM<sub>3</sub> = ON及びM<sub>4</sub> = ONに変化する。このため信号供給線V<sub>ideo</sub>に供給された電流I<sub>d</sub>(n)はM<sub>2</sub>に供給され、M<sub>2</sub>は1)式を満たすようにM<sub>2</sub> / G電圧が変化し、コンデンサーC<sub>1</sub>が充電され図7(d)の様にここに接続されているM<sub>1</sub> / Gが電圧V<sub>d#</sub>(n)から電圧V<sub>d</sub>(n)になる変化を開始し、時刻t<sub>1</sub>までに終了する。 50

## 【0025】

(時刻  $t_1$  において)

$P_1 = H$  より  $M_3 = OFF$  に変化し、コンデンサー  $C_1$  の充電動作は停止するため、 $M_1 / G$  は電圧  $V_{th}(n)$  のまま保持状態になる。

## 【0026】

(時刻  $t_2$  において)

$P_2 = L$  より  $M_4 = OFF$  に変化してトランジスタ  $M_2$  への電流供給は無くなるため、 $M_2 / G$  に加えられている電圧  $V_{th}(n)$  のため発生する  $M_2$  の出力電流により  $M_2 / D$  は急速に電位上昇し電源  $V_{CC}$  になる。このとき  $M_2$  は抵抗動作領域になり  $M_2$  の出力電流は無くなりこの状態で安定する。このとき  $M_1 / G$  電圧は変化が起こらず電圧  $V_{th}(n)$  のままであり、次回の発光設定動作まで電圧  $V_{th}(n)$  によって決定されるトランジスタ  $M_1$  からの出力電流が  $EL$  素子に注入されこの条件の発光を持続する。10

## 【0027】

(時刻  $t_2$  以降において)

信号供給線  $V_{idle}$  は次行の画素表示回路 1 を発光設定する設定電流  $I_d(n+1)$  に変化するとともに、該当画素表示回路 1 においては  $P_1 = H$  及び  $P_2 = L$  のまま次回の発光設定動作まで変化しない。そして次行の画素表示回路 1 の発光設定動作が同様に開始される。

## 【0028】

以上説明した電流設定方式においても、表示パネルが例えば  $QVGA(320 \times 240)$  の場合、信号供給線  $V_{idle}$  は 240 個の画素表示回路 1 に引き回され接続され、制御パルス  $P_1, P_2$  は 320 個の画素表示回路 1 に引き回され接続される。電流設定方式の場合、各画素表示回路 1 におけるトランジスタ  $M_1$  と  $M_2$  の駆動特性を相対的に確保できた場合、各トランジスタの遷移電圧  $V_{th}$  及び 1 ) 式における駆動係数  $k$  の絶対値バラツキの影響を受けずに論理的に  $EL$  素子への注入電流を設定できる。各画素表示回路 1 のトランジスタ  $M_1$  と  $M_2$  の駆動特性を相対的に確保することは 2 つのトランジスタが近接して配置されることによって TFT プロセスにおいても比較的容易に実現できる。このため電流設定方式によれば基本的には小電流から広い D レンジで設定でき、均一化した高品位の画像を表示パネルに表示できる。20

## 【0029】

## 【発明が解決しようとする課題】

しかしながら、従来の  $EL$  素子を駆動する図 9 に示す電圧駆動方式及び図 6 に示す電流駆動方式は以下に示す課題をもっている。

## 【0030】

## 〔図 9 の電圧駆動方式の課題〕

課題 1 (トランジスタの駆動係数  $k$  のバラツキ)

1 ) 式から理解できるように MOS トランジスタの出力電流  $I_{ds}$  は各画素表示回路 1 において変動する駆動係数  $k$  によって決定されているため、表示パネルの各画素の発光レベルを均一化することが困難である。そして発光レベルを均一化するためには難しい TFT プロセスの改良に依存しなければならない。40

## 【0031】

## 課題 2 (ホワイトバランスの確保)

また発光電流は誤差電圧  $v$  の 2 乗で決定される為、RGB の発光エネルギーのバランスによるホワイトバランス調整が難しいとともに、ドリフトに敏感であり表示画像の重要要素であるホワイトバランスを保証するのが難しい。

## 【0032】

課題 3 (  $V_{th}$  電圧へのリセット期間の確保 )

さらに、画素表示回路 1 内の  $M_1 / G$  の  $V_{th}$  へのリセット動作期間 ( $t_0 \sim t_1$ ) は、完全にリセット動作するためには長い時間を必要とする。なぜならば、 $M_1 / G$  が  $V_{th}$  に漸近するほどトランジスタ  $M_1$  の自己放電動作が弱まる為である。このため微小発光領50

域の発光設定が難しく、画像の階調性を確保するのが難しく、高画質表示パネルを実現するのが難しい。

【0033】

〔図6の電流駆動方式の課題〕

例えばQVGA表示パネルのサイズが2インチの場合、各色のEL素子の最大所望注入電流は100nA～200nA程度の微小電流であり、またコントラストを確保する為の最小所望電流は1nA以下の極小電流を必要としており信号供給線Videoにこの微小電流～極小電流を供給する必要がある。ところで1)式で示されるMOSトランジスタ特性式を変形すると、3)式になる。

【0034】

【数3】

$$\Delta V = \sqrt{I_{ds}} \div k$$

$$r_e = \frac{d \Delta V}{d I_{ds}} = \frac{1}{k \times \sqrt{I_{ds}}} \quad 3)$$

$$\Delta V = V_{gs} - V_{th}$$

【0035】

信号供給線Videoの電位を決定する画素表示回路1のトランジスタM2の動抵抗 $r_e$  20

は、本発明者が経験しているTFTプロセスにおいて $r_e$  (100nA) 1M、 $r_e$

(1nA) 10Mと言う非常に高抵抗になる。

【0036】

課題4(信号供給線Videoへのノイズ混入)

前述したように信号供給線Videoは多数の画素表示回路1と引き回されながら接続される為、このような高抵抗線には外乱ノイズが容易に混入する。前述のように図7(e) 20

は信号供給線Videoにノイズが混入した場合のM1/G電圧の様子を示している。

【0037】

時刻 $t_0$ ～ $t_1$ 以外の期間では $M3 = OFF$ なので該当画素表示回路1のM1/Gに信号供給線Videoが接続されずノイズ混入は無い。しかし時刻 $t_0$ ～ $t_1$ においては $M3 = ON$ 及び $M4 = ON$ なのでM1/Gにはノイズが混入する。このため時刻 $t_1$ の時 $M3 = OFF$ に変化してM1/G電圧が保持状態に移行したとき電圧 $V_d(n)$ がノイズ混入がないときの所望値に対して電圧 $V_d$ の誤差が生じることになる。これにより、トランジスタM1は所望出力電流からずれた出力電流をEL素子に注入してしまい当然発光量もずれてしまう。

【0038】

ノイズは管理できるものでないから各画素表示回路1におけるノイズ混入による発光量ずれも異なるので安定した表示画像が得られない。またノイズ混入による影響もRGB映像信号が小さい場合に顕著になり、さらに画像のS/N悪化をもたらす。

【0039】

EL素子が必要とする注入電流は小さく、一般に駆動能力の低い(駆動係数kが小さい)TFTプロセスにおいても駆動誤差電圧( $V_{gs} - V_{th}$ )は遷移電圧 $V_{th}$ の1/10程度であり、ノイズ混入によるM1/G電圧の誤差は大きな影響を及ぼすことになる。このため電流設定方式においては表示パネルを外乱ノイズから隔離する必要があるが、表示パネルの発光面をシールドすることは難しい。

【0040】

また信号供給線Videoの抵抗値を抑える為、画素表示回路1のトランジスタM2のサイズを大きくして設定電流 $I_{ds}$ を大きくしてM2の動抵抗値 $r_e$ を抑えることが考えられるが、3)式より、設定電流 $I_{ds}$ を10倍に増やしても $r_e$ は1/10にしかならない。またこの方法では画素サイズが制限された表示パネル用の画素表示回路1には大き

10

20

30

40

50

なトランジスタM2を搭載できず、特に消費電流を抑える必要がある小型表示パネルでは解決法にならない。

#### 【0041】

本発明は上記課題に鑑みなされたものであり、これらの課題を解決することが可能となるEL素子駆動回路、及びそれを備えた表示パネルを提供することを目的とするものである。

#### 【0042】

##### 【課題を解決するための手段】

上記課題を解決するための第1の発明は、

注入電流で発光動作するエレクトロルミネッセンス(EL)素子を発光させるEL素子駆動回路において、

EL素子と、第1、第2及び第3のトランジスタと、コンデンサーと、第1、第2及び第3のスイッチと、を少なくとも備え、

前記第1トランジスタと第2トランジスタとは、第1主電極同士及びゲート電極同士が互いに接続され、

前記コンデンサーは、前記第1トランジスタの第1主電極とゲート電極との間に接続され、

前記EL素子は、前記第1トランジスタの第2主電極に接続され、

前記第1スイッチは、前記第2トランジスタの第2主電極とゲート電極との間に接続され、

前記第2スイッチは、前記EL素子への注入電流を規定する信号電流を供給するための信号供給線と前記第2トランジスタの第2主電極との間に接続され、

前記第3トランジスタは、第1主電極が電源に接続され、第2主電極が前記第1トランジスタの第1主電極に接続され、第1主電極と第2主電極との間の電位差により所定の方向に電流が流れるようにゲート電極と第1主電極又は第2主電極とが短絡され、

前記第3スイッチは、電源と前記第1トランジスタの第1主電極との間に接続され、

前記第1スイッチ及び第2スイッチが短絡されているときに前記第3スイッチを開放され、第1スイッチ及び第2スイッチが開放しているときは前記第3スイッチを短絡させるように構成されていることを特徴とするEL素子駆動回路である。

#### 【0043】

上記課題を解決するための第2の発明は、上記第1の発明のEL素子駆動回路をマトリクス状に複数接続したことを特徴とする表示パネルである。

#### 【0044】

本発明は、上記第1の発明において、

前記EL素子駆動回路が少なくとも画素表示回路と信号供給回路とを含み、

前記画素表示回路は、前記EL素子と、前記第1及び第2のトランジスタと、前記コンデンサーと、前記第1、第2及び第3のスイッチと、を含み、さらに第4のスイッチを備えた回路であり、

前記信号供給回路は、前記第3のトランジスタを含み、

前記画素表示回路と前記信号供給回路とは、少なくともノイズ抑制線と前記信号供給線とにより接続され、

前記第3トランジスタの第2主電極と前記第1トランジスタの第1主電極とは、前記ノイズ抑制線と前記第4スイッチとを介して接続され、

前記第1スイッチ及び第2スイッチが短絡されているときに前記第3スイッチを開放し前記第4スイッチを短絡し、第1スイッチ及び第2スイッチが開放しているときは前記第3スイッチを短絡し前記第4スイッチを開放させるように構成されていることをその好ましい態様として含むものである。

#### 【0045】

上記課題を解決するための第3の発明は、

少なくとも、上記画素表示回路と信号供給回路とを備える発明に記載のEL素子駆動回路

10

20

30

40

50

を複数含み、画素表示回路はマトリクス状に接続され、該マトリクス状に接続された画素表示回路のうち 1 ラインに属する画素表示回路を 1 組として、各組の画素表示回路を各組毎に 1 つずつ配置された信号供給回路のそれぞれに共通に接続したことを特徴とする表示パネルである。

【 0 0 4 6 】

【発明の実施の形態】

(実施の形態 1 )

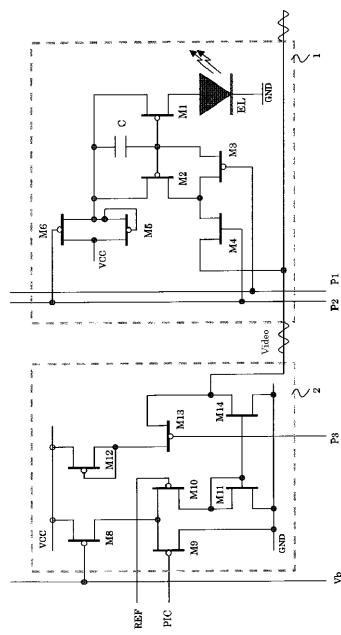

図 1 は本発明の E L 素子駆動回路の実施形態 1 を示す回路図である。本形態においては、電圧として入力された映像信号 P I C を映像電流信号に変換する信号供給回路 2 と画素表示回路 1 とに分かれた構成となっており、本発明における第 1 の発明の回路構成が画素表示回路 1 に含まれた形態となっているが、本発明の形態はこれに限られるものではない。 10

【 0 0 4 7 】

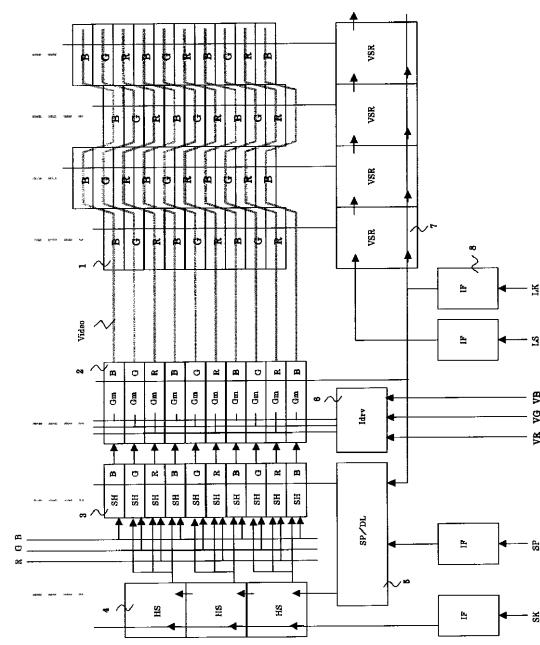

ここで、図 1 の構成を説明する前に、表示パネルにおいて電流設定方式を使用した場合の構成例を説明する。

【 0 0 4 8 】

〔電流設定方式の表示パネルの構成〕

図 8 は電流設定方式による表示パネルの全体ブロック図である。図 8 において、1 は画素表示回路、2 は信号供給回路、3 はサンプルホールド回路、4 は水平(列)走査シフトレジスタ、5 はパルス発生回路、6 は基準電流発生回路、7 は垂直(行)走査シフトレジスタ、8 は入力回路、V i d e o は信号供給線であり、S K は画素クロック信号、S P は水平(列)開始信号、V R 、V G 、V B は R G B 各色の基準電流設定電圧、L K は垂直(行)走査クロック信号である。 20

【 0 0 4 9 】

入力映像電圧信号は R G B 信号であり、R G B 各画素ごとに発光設定する為、各サンプルホールド回路 3 に入力される。画素クロック S K は入力回路 8 を介して 1 番目の水平(列)シフトレジスタ 4 に入力される。垂直(行)走査クロック L K は入力回路 8 を介して、パルス発生回路 5 と垂直(行)走査シフトレジスタ 7 群の 1 番目に入力されるとともに信号供給回路 2 群に入力される。垂直(行)走査クロック L K はパルス発生回路 5 において奇数行 / 偶数行を識別するために 2 分周されてサンプルホールド回路 3 群に入力される。水平(列)シフトレジスタ 4 は図のように R G B 各組に 1 つ配置される。水平(列)開始信号 S P は入力回路 8 を介してパルス発生回路 5 に入力され、2 本の水平(列)開始信号に変換され水平(列)シフトレジスタ 4 群に入力される。 30

【 0 0 5 0 】

サンプルホールド回路 3 は、順次入力される R G B 映像電圧信号に対応する為、2 個のサンプルホールド回路を内蔵して、奇数行用の映像信号入力時は 1 番目のサンプルホールド回路はサンプル動作して 2 番目のサンプルホールド回路がホールド動作し、偶数行用の映像信号入力時は 2 番目のサンプルホールド回路はサンプル動作して 1 番目のサンプルホールド回路がホールド動作し、常に R G B 映像情報を出力できるようにしておく。

【 0 0 5 1 】

各サンプルホールド回路 3 の R G B 出力映像信号 P I C は各信号供給回路 2 に入力される。R G B 基準電流設定電圧 V R 、V G 、V B は基準電流発生回路 6 に入力され、各色用の基準電流 I o R 、I o G 、I o B を発生する為のバイアス電圧 V b R 、V b G 、V b B を発生して各色の各信号供給回路 2 群に入力して、基準電流 I o R 、I o G 、I o B を各信号供給回路 2 で発生させる。このように基準電流を各色ごとに設定する理由は、E L 素子の電流発光変換特性が R G B 各色で異なることが一般的であることに対応するためである。 40

【 0 0 5 2 】

各信号供給回路 2 では各色の電圧で入力された映像信号 P I C を、内部で発生した基準電流に関係する映像電流信号 I d に変換して、各垂直(列)の画素表示回路 1 群に引き回して接続された信号供給線 V i d e o に供給する。 50

## 【0053】

垂直(行)走査シフトレジスタ7の出力である行制御パルスは各行の画素表示回路1群に供給される。

## 【0054】

図8において行間において各色の画素表示回路1が1.5画素ずれた配列をしているのは、特にQVGA等の低解像度表示パネルにおける色の縦ビートを削減する為のスクリーン角を形成する為のものである。また図示していないが、入力RGB映像信号は対ノイズ性を考慮して基準信号とともに入力するのが一般的であり、このとき各サンプルホールド回路3では映像信号と同様に基準信号をサンプルホールドして出力し、映像信号PICTとともに基準信号REFを各信号供給回路2に入力する。

10

## 【0055】

また、垂直(行)走査クロックLKはブランкиング信号の機能を持っており、信号供給回路2の出力電流信号Idが各列の画素表示回路1群内で使用されない期間の処理を行う為に信号供給回路2に入力されている。

## 【0056】

## 〔図1の画素表示回路1、信号供給回路2の説明〕

図1において、1は画素表示回路、2は信号供給回路、Cはコンデンサー、ELはEL素子、M1は第1トランジスタ、M2は第2トランジスタ、M3は第1スイッチ、M4は第2スイッチ、M5は第3トランジスタ、M6は第3スイッチ、Videoは信号供給線、VCCは電源、GNDは接地、REFは基準信号、PICTは映像信号である。

20

## 【0057】

本発明の第1主電極、第2主電極とは、ソース電極とドレイン電極とのいずれかを夫々示しており、以下においては第1主電極がソース電極、第2主電極がドレイン電極である形態を示す。従って図1の形態はMOSトランジスタの夫々の極性を適切に設計して配線した一例を示したものであり、MOSトランジスタの極性を適宜変更して本発明と同じ機能を有するように構成しても構わない。この事は、後述の実施の形態2においても同様である。

## 【0058】

図1における信号供給回路2は、従来の電流設定方式を使用した図6の画素表示回路1に対して使用されるものと同じものであるが、まず電流変換回路2について説明する。

30

## 【0059】

サンプルホールド回路3から映像信号PICTと基準信号REFとが、ソース電極同士が互いに接続されたM9/G及びM10/Gに各々入力される。バイアス電圧Vbはソース電極が電源VCCに接続されたM8/Gに入力され、M8/Dから基準電流IoをM9/S(M10/S)に供給する。M9/Dは接地GNDに接続され、M10/Dからは基準信号REFに対する映像信号PICTのレベル差と基準電流Ioに関連し変換された映像電流信号が出力され、図1に示すようにトランジスタM11とM14からなるカレントミラーレ路によってM14/Dより発光設定電流信号Idを信号供給線Videoに出力する。

## 【0060】

M14/Dはゲートが制御パルスP3によって制御されたM13/Dに接続され、M13/Sはソースが電源VCCに接続されドレインとゲートが短絡されたトランジスタM12に接続される。制御パルスP3は垂直(行)走査クロックLKであり、信号供給線Videoに出力される発光設定電流信号Idが接続された画素表示回路1群に供給されないブランкиング期間においてM13=ONになり、トランジスタM12によって画素表示回路1により決定される信号供給線Videoの近傍電位に規定する。

40

## 【0061】

次に、図1の画素表示回路1と図6の従来の画素表示回路1との相違点を説明し、本発明の構成の特徴を明確にする。即ち、図1の本発明の構成においては、M1/S、M2/S及びコンデンサーC1が接続されたノードは、電源VCCに直接接続されるのではなく、ソース電極が電源VCCに接続されゲート電極が制御パルスP2で制御されたM6/Dに

50

接続されるとともに、ソース電極が電源VCCに接続されゲート電極とドレイン電極とが短絡されたトランジスタM5に接続される。

【0062】

このような構成とすることにより、後述の説明で明らかとなるように、信号供給線Vide oから混入するノイズによりコンデンサーCに与えられる電位差が所定の値からずれることを防止することができる。

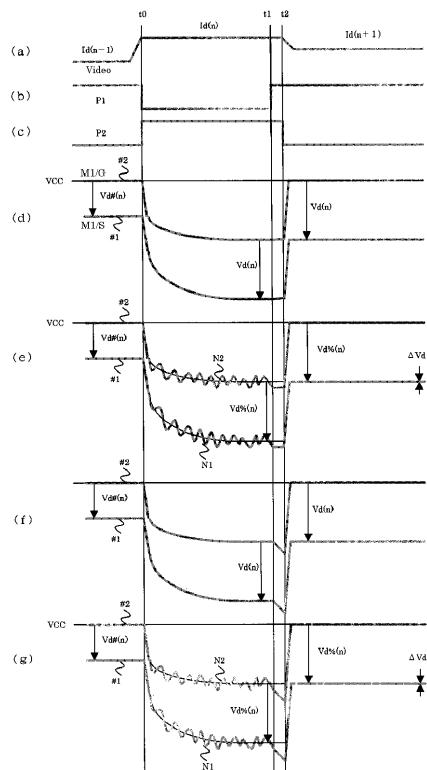

【0063】

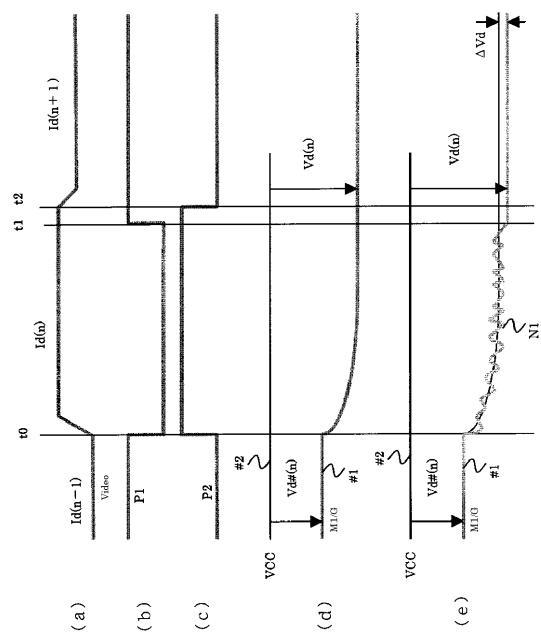

図1の画素表示回路1の動作を図3のタイムチャートを使用して説明する。図3(a)～(c)はVide oから入力される発光設定電流信号、制御パルスP1、制御パルスP2のレベルを示しており、図7のタイムチャートと同様である。図3(d)の#1及び#2はM1/G(M2/G)及びM1/S(M2/G)の信号を示す。

10

【0064】

(時刻t0以前において)

M3=OFF、M4=OFF、M6=ONである為、M2/S(M1/S)は電源VCCになり、図6の画素表示回路1と同様に前回電流設定によって電圧Vd#(n)がM1/Gに与えられ、トランジスタM1からの出力電流によってEL素子は設定された発光を行っている。

【0065】

(時刻t0において)

M3=ON、M4=ONに変化し、M6はOFFする為、このとき信号供給線Vide oに供給される設定電流Id(n)がトランジスタM5に供給されることによりM2/Sは1)式を満たすM5のVgsに向かって電圧降下始めるとともに、トランジスタM2に設定電流Id(n)が供給される為、M2/GはM2/Sからさらに1)式を満たすM2のVgsに向かって電圧降下始める。そして時刻t1までにトランジスタM5とM2によるコンデンサーC1への充電動作を終了し、M2/Sに対するM2/Gの電圧は図6の画素表示回路1と同様に設定電流をM1に発生する設定電圧Vd(n)になる。

20

【0066】

(時刻t1において)

M3=OFFに変化するが、M2/S(M1/S)電圧に対してM1/G(M2/G)電圧は設定電圧Vd(n)のままである。

30

【0067】

(時刻t2において)

M4=OFF及びM6=ONに変化し、M2/S(M1/S)電圧は電源VCCに変化するが、M2/S(M1/S)電圧に対してM1/G(M2/G)電圧はコンデンサーCにより設定電圧Vd(n)のまま保持され、トランジスタM1の出力電流がEL素子に供給され次回の発光設定動作が開始されるまで設定した発光動作を行う。次行の画素表示回路1の発光設定動作を同様に開始する。

【0068】

図3(e)は電流設定方式の課題であった信号供給線Vide oへのノイズ混入に対する図1の画素表示回路1の動作を示すものである。該当表示回路1はトランジスタM2がONしている期間t0～t1において信号供給線Vide oへのノイズ混入により、図3(e)の#1及び#2の様にM2/G及びM2/Sがノイズ信号で変動するが、これらは類似した波形となる。なぜならば、前述したように信号供給線Vide oに供給される設定電流は微小電流～極小電流である為、トランジスタM6の動抵抗は1M～10Mが想定され、このような高抵抗においてコンデンサーC1は期間t0～t1に比べて短い期間で変動するノイズ信号に対して電圧保持動作になることによってM2/GとM2/Sのノイズ混入による変動N1とN2はほとんど等しくなるからである。このため信号供給線Vide oにノイズ混入があってもM2/Sに対するM2/Gの電圧は所望電圧Vd(n)にほとんど等しい設定電圧Vd%(n)とすることができます。このため時刻t1以降のM1/Gに与えられる設定電圧Vd%(n)は所望設定電圧Vd(n)にほとんど等しく、

40

50

したがってトランジスタM 1の出力電流による発光するEL素子はおおよそ所望発光動作を行うことができる。

【0069】

なお、図1の画素表示回路1におけるトランジスタM 3、M 4、M 5のP型/N型のタイプを限定しているものではなく、トランジスタM 3、M 4は制御パルスP 1、P 2の極性を変えれば容易に構成できることは明確である。

【0070】

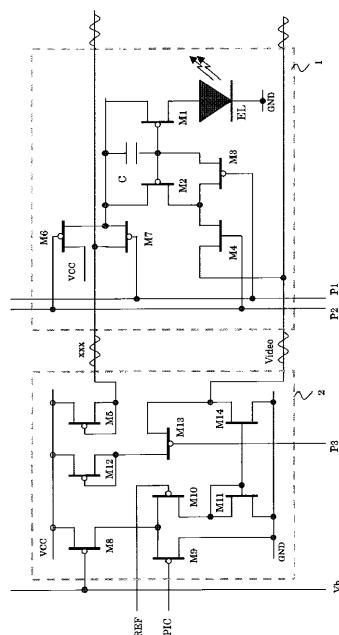

(実施の形態2)

図2は本発明のEL素子駆動回路の実施形態2を示す回路図である。図2において、図1と同じ符号は同じ要素を示している。また、M 7は第4スイッチである。

10

【0071】

まず、図2で示される本形態と前記の図1の形態との、画素表示回路1と信号供給回路2との構成の差異について説明する。

【0072】

画素表示回路1と信号供給回路2とは、信号供給線Vide oの他にノイズ抑制線×××により接続されている。ノイズ抑制線×××は信号供給線Vide oと同様に該当列の画素表示回路1群に引き回され接続される。

【0073】

図2の画素表示回路1においては、M 2/S、M 1/S及びコンデンサーC 1が接続されたノードには、ソース電極がノイズ抑制線×××に接続されゲート電極が制御パルスP 2で制御された第4スイッチM 7のドレイン電極が接続される。

20

【0074】

また、本形態においては、第3トランジスタM 5は信号供給回路2に含まれている。

【0075】

次に動作を図3のタイムチャートの(f)を使用して説明する。

【0076】

(時刻t 0以前において)

M 3 = OFF、M 4 = OFF、M 7 = OFFでありM 6 = ONしている為、M 2/S (M 1/S)は電源VCCになり、図6の画素表示回路1と同様に前回電流設定によって電圧Vd#(n)がM 1/Gに与えられ、トランジスタM 1からの出力電流によってEL素子は設定された発光を行っている。

30

【0077】

(時刻t 0において)

M 3 = ON、M 4 = ON及びM 6 = OFFに変化し、M 7 = ONとなる為、このとき信号供給線Vide oに供給される設定電流Id(n)がノイズ抑制線×××を介して信号供給回路2内のトランジスタM 5に供給される。したがってM 2/S電圧は1)式を満たすM 5のVgsに向かって電圧降下始めるとともに、トランジスタM 2に設定電流Id(n)が供給される為M 2/GはM 2/Sからさらに1)式を満たすM 2のVgsに向かって電圧降下始める。そして時刻t 1までにトランジスタM 5とM 2によるコンデンサーC 1への充電動作を終了し、M 2/Sに対するM 2/Gの電圧は図6の画素表示回路1と同様に設定電流をM 1に発生する設定電圧Vd(n)になる。

40

【0078】

(時刻t 1において)

M 3 = OFF、M 7 = OFFに変化するためノイズ抑制線×××は該当画素表示回路1から切り離され、信号供給線Vide oに供給されている設定電流Id(n)によってM 2/S電圧は電圧降下を開始する。しかし設定電流Id(n)は微小～極小であるためこの電圧降下は急激なものではなく、M 1/S (M 2/S)電圧に対してM 1/G (M 2/G)電圧は設定電圧Vd(n)のままである。

【0079】

(時刻t 2において)

50

$M4 = OFF$ 、 $M6 = ON$ に変化して、 $M1 / S$  ( $M2 / S$ ) の時刻  $t_1$  からの電圧降下は停止して  $M1 / S$  ( $M2 / S$ ) は急速に電源  $VCC$  になる。この過程において  $M1 / G$  ( $M2 / G$ ) 電圧は、コンデンサー  $C$  により電源  $VCC$  から設定電圧  $Vd(n)$  のまま保持され、トランジスタ  $M1$  の出力電流が  $EL$  素子に供給され次回の発光設定動作が開始されるまで設定した発光動作を行う。そして次行の画素表示回路 1 の発光設定動作を同様に開始する。

#### 【0080】

このような本形態によれば、 $M2 / G$  及び  $M2 / S$  のノイズ混入による変動  $N1$  及び  $N2$  は、ノイズ抑制線  $\times \times \times$  が信号供給線  $Vide$  と同様に引き回されることから実施の形態 1 の画素表示回路 1 の動作よりもさらに類似した波形となり、より高いノイズ抑制効果が得られるとともに、期間  $t_0 \sim t_1$  に比べて長周期のノイズ変動に対しても  $M2 / S$  に対する  $M2 / G$  の電圧を設定電圧にほぼ等しい  $Vd\% (n)$  にできる。このため時刻  $t_2$  以降の  $M1 / G$  に与えられる設定電圧  $Vd\% (n)$  は所望設定電圧  $Vd(n)$  にほとんど等しく、したがってトランジスタ  $M1$  の出力電流により発光する  $EL$  素子はおおよそ所望発光動作を行うことができる。尚、図 3 (g) は、本形態においても図 3 (e) に示した実施の形態 1 の形態の効果と同様な効果が得られることを明示したものである。

#### 【0081】

本形態においても、図 2 の画素表示回路 1 におけるトランジスタ  $M3$ 、 $M4$ 、 $M7$  の P 型 / N 型のタイプを限定してしているものではなく、各トランジスタのゲート制御パルス信号を適宜入力すれば、容易に構成できることは明確である。

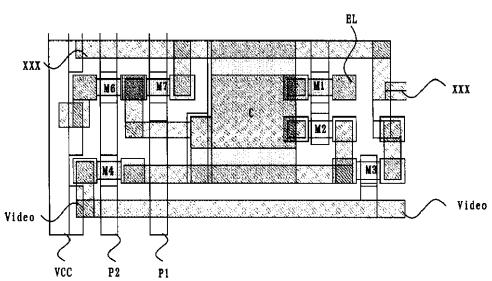

#### 【0082】

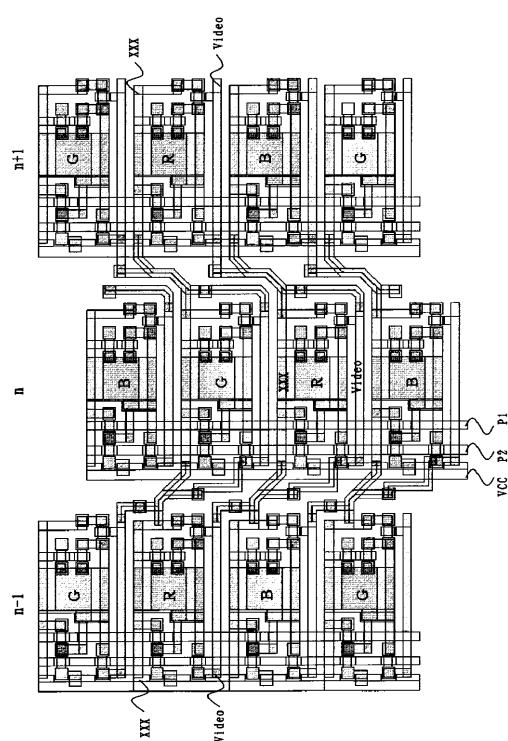

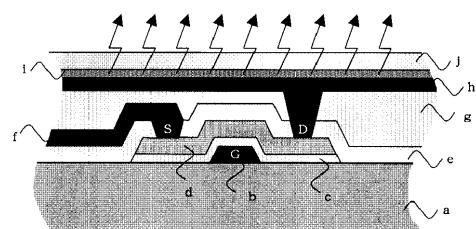

表示パネルの画素表示回路 1 において前述したようにスペース的な制約は非常に大きい。図 2 の画素表示回路 1 に関して TFT プロセスを想定したレイアウト構成の一例を図 4 に示す。また、その際に使用した TFT プロセスの構造の概念図を図 11 に示す。

#### 【0083】

ガラス基板  $a$  の上に、他の配線にも使用できるゲート配線層  $b$  を設け、そのゲート配線層  $b$  の上に薄い絶縁層であるゲート酸化膜層  $c$  を設け、その上にポリシリコン層  $d$  を設け、その上に第 1 の配線絶縁層  $e$  を設け、第 1 の配線絶縁層  $e$  の結線個所にスルーホールを設けておき、その上に第 1 の配線層  $f$  を設け、その上に比較的厚い第 2 の配線絶縁層  $g$  を設けたあと表面を平滑化しておき、 $EL$  素子の電流注入端子に接続されるノード個所にスルーホールを設けたのち第 2 の配線層  $h$  を該当  $EL$  素子の発光領域に設け、その上に  $EL$  発光層  $i$  を設けた後に前面に透明導体 (ITO) 層  $j$  を設ける構成である。

#### 【0084】

図 11 に示したポリシリコン層  $d$  の領域に形成されるトランジスタは、 $EL$  素子を駆動するトランジスタ  $M1$  を示している。

#### 【0085】

以上説明した TFT プロセスを一般にボトムゲート方式といいゲート配線層  $b$  の配線使用条件に制約があるがトランジスタ特性に良いとされている。

#### 【0086】

図 11 の TFT プロセスで構成した図 4 の画素表示回路 1 のレイアウトにおいては、表示パネルにおける行配線となる電源  $VCC$ 、制御パルス  $P1$ 、 $P2$  はゲート配線層  $b$  を使用し、列配線となる信号供給線  $Vide$  及びノイズ抑制線  $\times \times \times$  は第 1 の配線層  $f$  を使用している。コンデンサー  $C1$  はゲート配線層  $b$ 、ゲート酸化膜層  $c$  及びポリシリコン層  $d$  で構成している。尚、図 4 において  $EL$  と記したノード  $M1 / D$  が  $EL$  素子の電流注入端子への接続パッドであり図 4 には第 2 の配線層  $h$ 、 $EL$  発光層  $i$ 、透明導体層  $j$  は省略している。

#### 【0087】

表示パネルにおいて画素表示回路 1 を前述したように 配列することは非常に重要である。図 5 は図 4 の画素表示回路 1 のレイアウトを使用して 配列レイアウトを実現したものである。

10

20

30

40

50

## 【0088】

配列レイアウトにおいては列配線数の制約が大きいが、図2の画素表示回路1におけるノイズ抑制線×××の結線される信号供給回路2は、信号供給線Vide oと異なり、何れかの色の信号供給回路2に接続されれば良いので、列配線への制約が減少できる。例えば図5においてR色のノイズ抑制線×××は最も近接した行のB色の画素表示回路1のノイズ抑制線×××を介して接続している。

## 【0089】

図2の画素表示回路1の使用トランジスタ数=6は図6、図9に示す従来の電流設定方式及び電圧設定方式の使用トランジスタ数=4に比べて2つ多い。しかし、電圧設定方式の場合、コンデンサーC2を必要とし、これはトランジスタより大きくなる。また、従来の電流設定方式においても対ノイズ性を向上させるため図6のトランジスタM2を大きくして信号供給線Vide oに供給される設定電流を増やす為、トランジスタ数=4であるこれら2つのEL素子駆動回路にレイアウト上の優位性はない。

10

## 【0090】

さらに、図5の配列の画素表示回路1のレイアウトにおいては、実用化されている4μルールのTFTプロセスで列方向が190ppi、行方向は200ppiを実現できる。進化の著しいTFTプロセスの微細化によって列方向も目標である200ppiの実現性は極めて高い。

## 【0091】

20

## 【発明の効果】

以上説明した様に本発明のEL素子駆動回路を使用した場合、従来の電圧設定方式に比べて使用する回路素子の特性バラツキの影響を受けずにEL素子の発光動作を行うことができ、従来の電流設定方式に比べて信号供給線へのノイズ混入によるEL素子の発光動作誤差(変動)を著しく減少させるとともに、駆動回路レイアウトの制約を最小限にでき、高画質のEL素子を使用した表示パネルを実現できる効果がある。

## 【図面の簡単な説明】

【図1】本発明のEL素子駆動回路の一実施形態を示す回路図である。

【図2】本発明のEL素子駆動回路の別の実施形態を示す回路図である。

【図3】図1、図2に示した形態のEL素子駆動回路の動作を説明するためのタイムチャートである。

30

【図4】図2に示した形態のEL素子駆動回路に含まれる画素表示回路の回路レイアウトの一例である。

【図5】図4の形態の回路レイアウトを有する画素表示回路を複数配置したタイプの表示パネルの回路レイアウトである。

【図6】従来の電流設定方式による画素表示回路の回路図である。

【図7】図6の画素表示回路の動作を説明するためのタイムチャートである。

【図8】電流設定方式による表示パネルの全体ブロック図である。

【図9】従来の電圧設定方式による画素表示回路の回路図である。

【図10】図9の画素表示回路の動作を説明するためのタイムチャートである。

【図11】TFTプロセスの構成概念図である。

40

## 【符号の説明】

- 1 画素表示回路

- 2 信号供給回路

- 3 サンプルホールド回路

- 4 水平(列)走査シフトレジスタ

- 5 パルス発生回路

- 6 基準電流発生回路

- 7 垂直(行)走査シフトレジスタ

- 8 入力回路

- C コンデンサー

50

E L E L 素子

M 1 第1トランジスタ

M 2 第2トランジスタ

M 3 第1スイッチ

M 4 第2スイッチ

M 5 第3トランジスタ

M 6 第3スイッチ

M 7 第4スイッチ

× × × ノイズ抑制線

V i d e o 信号供給線

V C C 電源

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 6 4 1 D

H 05 B 33/14 A

(56)参考文献 特開2003-216100 (JP, A)

特開2003-150104 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00- 3/38

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | EL元件驱动电路和显示板                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP3997109B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2007-10-24 |

| 申请号            | JP2002132287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2002-05-08 |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 佳能公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 当前申请(专利权)人(译)  | 佳能公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| [标]发明人         | 川崎素明<br>大村昌伸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 川崎 素明<br>大村 昌伸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 G09G3/32 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G09G3/3241 G09G3/3233 G09G3/3283 G09G3/3291 G09G2300/0417 G09G2300/0814 G09G2300/0819 G09G2300/0842 G09G2300/0852 G09G2300/0861 G09G2310/0254 G09G2310/06 G09G2320/0233 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.H G09G3/20.611.Z G09G3/20.612.E G09G3/20.624.B G09G3/20.641.D H05B33/14.A G09G3/20.680.H G09G3/3225 G09G3/3275 G09G3/3283 H01L29/78.614                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 3K007/AB04 3K007/AB17 3K007/DB03 3K007/GA04 3K107/AA01 3K107/AA06 3K107/BB01 3K107/CC08 3K107/CC32 3K107/CC33 3K107/CC43 3K107/EE03 3K107/EE57 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/CC03 5C080/DD05 5C080/DD30 5C080/EE30 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C380/AA01 5C380/AB06 5C380/AB21 5C380/AB23 5C380/AB34 5C380/AB41 5C380/BA08 5C380/BA38 5C380/BA39 5C380/BB23 5C380/CA02 5C380/CA13 5C380/CA21 5C380/CC01 5C380/CC04 5C380/CC11 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC63 5C380/CC64 5C380/CD014 5C380/CD016 5C380/CD024 5C380/CE04 5C380/CF07 5C380/DA49 5C380/HA20 5F110/AA30 5F110/BB02 5F110/CC07 5F110/DD02 5F110/FF02 5F110/GG02 5F110/GG13 5F110/NN72 5F110/QQ19 |         |            |

| 代理人(译)         | 渡辺圭佑<br>山口 芳広                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 其他公开文献         | JP2003323156A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

**摘要(译)**

要解决的问题：提供一种显示面板，其中对驱动电路布局施加的约束最小化，同时减少由于电路元件的特性的分散和噪声侵入信号而导致的EL元件的发光操作中的误差。用于提供视频信号的电源线也被减少，并且使用提供高图像质量的EL元件。

ŽSOLUTION：选择当前设定系统作为驱动系统。具有用于弱电流的大动态电阻特性的晶体管（M5）插入在确定EL元件的注入电流量的电压设定晶体管（M2）和电源（VCC）之间。为了抑制由信号供给线（视频）侵入的噪声引起的电容器（C）的端子间电压的波动。Ž

$$I_d\,s=k\times\Delta V$$

$$\Delta V = V_{g\;s} - V_{t\;h}$$