(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-157514

(P2010-157514A)

(43) 公開日 平成22年7月15日(2010.7.15)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>H05B 33/26</b> (2006.01) | H05B 33/26 | Z 3K107     |

| <b>G09F 9/30</b> (2006.01)  | G09F 9/30  | 349C 5C080  |

| <b>H01L 27/32</b> (2006.01) | G09F 9/30  | 338 5C094   |

| <b>G09G 3/30</b> (2006.01)  | G09F 9/30  | 365Z 5C380  |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/30  | J           |

審査請求 有 請求項の数 11 O L (全 24 頁) 最終頁に続く

|            |                                   |          |                                        |

|------------|-----------------------------------|----------|----------------------------------------|

| (21) 出願番号  | 特願2010-17669 (P2010-17669)        | (71) 出願人 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号 |

| (22) 出願日   | 平成22年1月29日 (2010.1.29)            | (74) 代理人 | 100120640<br>弁理士 森 幸一                  |

| (62) 分割の表示 | 特願2008-11004 (P2008-11004)<br>の分割 | (74) 代理人 | 100118290<br>弁理士 吉井 正明                 |

| 原出願日       | 平成20年1月21日 (2008.1.21)            | (74) 代理人 | 100094363<br>弁理士 山本 孝久                 |

|            |                                   | (72) 発明者 | 山下 淳一<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

|            |                                   | (72) 発明者 | 山本 哲郎<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

最終頁に続く

(54) 【発明の名称】 E L表示パネル及び電子機器

## (57) 【要約】

【課題】 内部散乱光の影響による閾値電圧変動を抑制するパネル構造を提案する。

【解決手段】 アクティブマトリクス駆動方式に対応した画素構造を有する E L表示パネルに、内部散乱光を遮光する構造を採用する。すなわち、画素回路を構成するサンプリングトランジスタのチャネル層よりも上層に位置する金属配線材料の一部パターンを、サンプリングトランジスタのチャネル領域を塞ぐようにレイアウトする。

【選択図】 図 1 3

**【特許請求の範囲】****【請求項 1】**

映像信号の書き込みを制御するサンプリングトランジスタと、当該サンプリングトランジスタによって書き込まれた映像信号に応じて有機EL素子を駆動する駆動トランジスタとを含む、アクティブマトリクス駆動方式に対応した画素回路を備え、

前記画素回路は、前記駆動トランジスタの移動度を補正する機能を有し、

前記サンプリングトランジスタはチャネル層を有する薄膜トランジスタであり、

前記サンプリングトランジスタのチャネル層よりも上層に位置する金属配線材料の一部パターンが、前記サンプリングトランジスタのチャネル領域を塞ぐようにレイアウトされてなる

10

有機EL表示パネル。

**【請求項 2】**

映像信号の書き込みを制御するサンプリングトランジスタと、当該サンプリングトランジスタによって書き込まれた映像信号に応じて有機EL素子を駆動する駆動トランジスタとを含む、アクティブマトリクス駆動方式に対応した画素回路を備え、

前記画素回路は、前記駆動トランジスタの移動度を補正する機能を有し、

前記サンプリングトランジスタはチャネル層を有する薄膜トランジスタであり、

前記サンプリングトランジスタのチャネル領域を塞ぐように遮光パターンがレイアウトされてなる

20

有機EL表示パネル。

**【請求項 3】**

前記移動度の補正は、前記サンプリングトランジスタのオン期間において、前記駆動トランジスタを流れる電流の大きさに応じてなされる

請求項1または請求項2に記載の有機EL表示パネル。

**【請求項 4】**

前記移動度の補正は、前記サンプリングトランジスタのオン期間において、前記有機EL素子に接続された保持容量に充電された電位に基づいてなされる

請求項3に記載の有機EL表示パネル。

**【請求項 5】**

前記一部パターンは、前記サンプリングトランジスタの主電極との間に印加される最大電圧がカットオフ電圧以下に設定された固定電位線に接続される

30

請求項1に記載の有機EL表示パネル。

**【請求項 6】**

前記一部パターンは、前記サンプリングトランジスタの主電極との間に印加される最大電圧がカットオフ電圧以下に設定されたパルス信号線に接続される

請求項1に記載の有機EL表示パネル。

**【請求項 7】**

前記一部パターンは、前記サンプリングトランジスタのゲート電極の制御線に接続される

40

請求項1に記載の有機EL表示パネル。

**【請求項 8】**

前記遮光パターンは、金属原子を注入した半導体材料で形成される

請求項2に記載の有機EL表示パネル。

**【請求項 9】**

前記遮光パターンは、有機材料で形成される

請求項2に記載の有機EL表示パネル。

**【請求項 10】**

映像信号の書き込みを制御するサンプリングトランジスタと、当該サンプリングトランジスタによって書き込まれた映像信号に応じて有機EL素子を駆動する駆動トランジスタとを含む、アクティブマトリクス駆動方式に対応した画素回路を備え、

50

前記画素回路は、前記駆動トランジスタの移動度を補正する機能を有し、

前記サンプリングトランジスタはチャネル層を有する薄膜トランジスタであり、

前記サンプリングトランジスタのチャネル層よりも上層に位置する金属配線材料の一部

パターンが、前記サンプリングトランジスタのチャネル領域を塞ぐようにレイアウトされ

てなる

有機 E L 表示パネルと、

システム全体の動作を制御するシステム制御部と、

前記システム制御部に対する操作入力を受け付ける操作入力部と

を有する電子機器。

#### 【請求項 11】

映像信号の書き込みを制御するサンプリングトランジスタと、当該サンプリングトラン

ジスタによって書き込まれた映像信号に応じて有機 E L 素子を駆動する駆動トランジスタ

とを含む、アクティブマトリクス駆動方式に対応した画素回路を備え、

前記画素回路は、前記駆動トランジスタの移動度を補正する機能を有し、

前記サンプリングトランジスタはチャネル層を有する薄膜トランジスタであり、

前記サンプリングトランジスタのチャネル領域を塞ぐように遮光パターンがレイアウトされ

てなる

有機 E L 表示パネルと、

システム全体の動作を制御するシステム制御部と、

前記システム制御部に対する操作入力を受け付ける操作入力部と

を有する電子機器。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

この明細書で説明する発明は、アクティブマトリクス駆動方式で駆動制御される E L 表

示パネルに関する。なお、この明細書で提案する発明は、 E L 表示パネルを搭載する各種

の電子機器としての側面も有する。

##### 【背景技術】

##### 【0002】

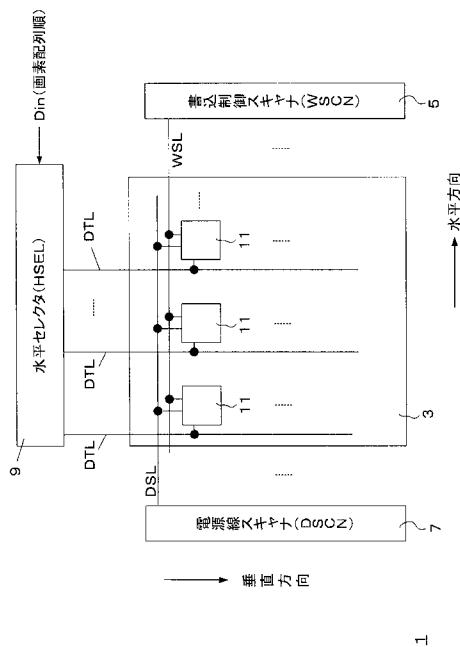

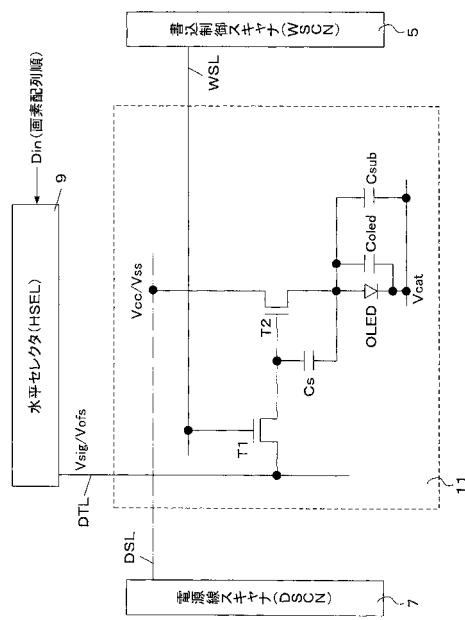

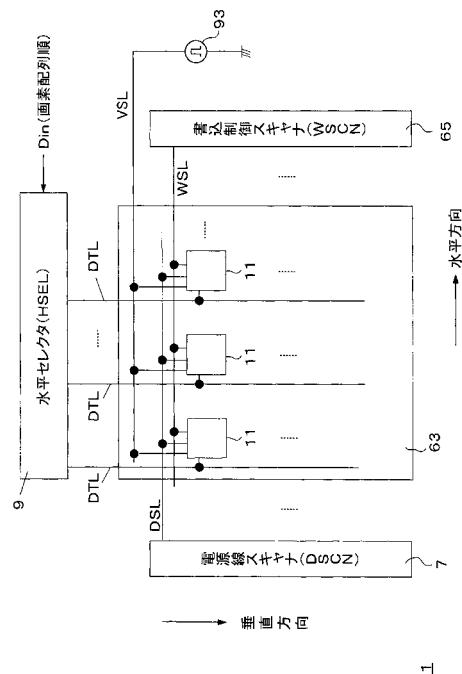

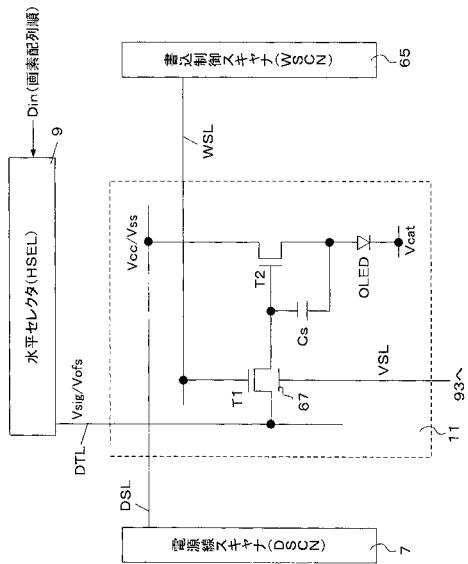

図 1 に、アクティブマトリクス駆動型の有機 E L パネルに用いられる回路ブロックの構

成例を示す。図 1 に示す有機 E L パネル 1 は、画素アレイ部 3 と、その駆動回路である書

込制御スキヤナ 5 、電源線スキヤナ 7 及び水平セレクタ 9 とで構成される。

##### 【0003】

画素アレイ部 3 は、信号線 D T L と書込制御線 W S L の各交点にサブ画素 11 を配置し

たマトリクス構造を有している。サブ画素 11 は、1 画素を構成する画素構造の最小単位

である。例えばホワイトユニットとしての 1 画素は、有機 E L 材料の異なる 3 つのサブ画

素 ( R ( 赤 ) 画素、 G ( 緑 ) 画素、 B ( 青 ) 画素 ) の集合体として構成される。

##### 【0004】

この明細書で説明するサブ画素 11 は、アクティブ駆動方式に対応する。従って、サブ

画素 11 は、発光領域 ( 有機 E L 素子 ) と画素回路とで形成されている。なお、発光領域

を構成する有機 E L 素子は電流発光素子である。従って、有機 E L パネルの輝度階調は、

各画素に対応する有機 E L 素子に流れる電流量により制御される。この電流の供給を一定

期間継続するのが画素回路の機能である。

##### 【先行技術文献】

##### 【特許文献】

##### 【0005】

参考までに、アクティブマトリクス駆動方式を採用する有機 E L パネルディスプレイに

関する文献を例示する。

【特許文献 1】特開 2003 - 255856 号公報

【特許文献 2】特開 2003 - 271095 号公報

10

20

30

40

50

【特許文献3】特開2004-133240号公報

【特許文献4】特開2004-029791号公報

【特許文献5】特開2004-093682号公報

【発明の概要】

【発明が解決しようとする課題】

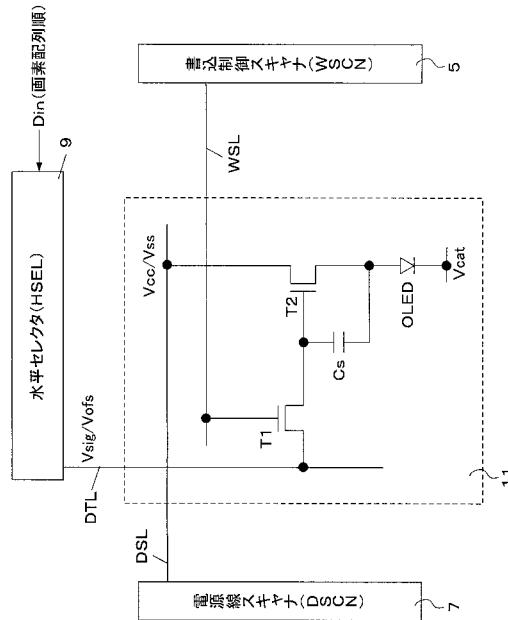

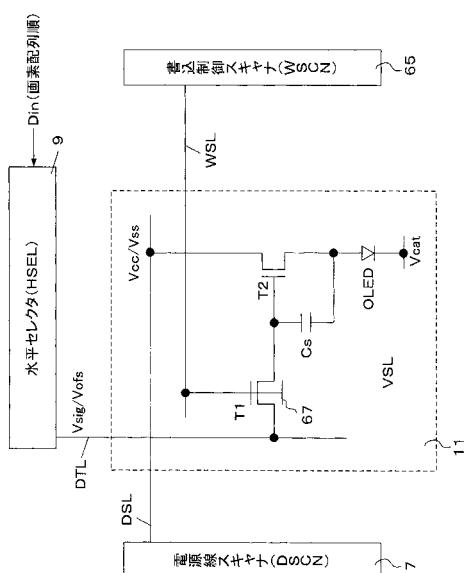

【0006】

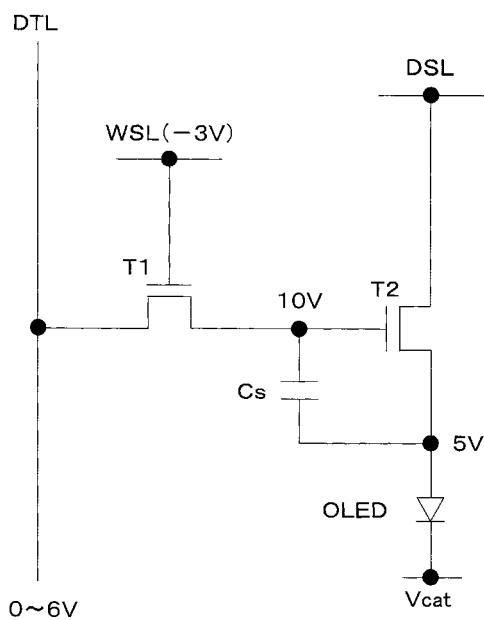

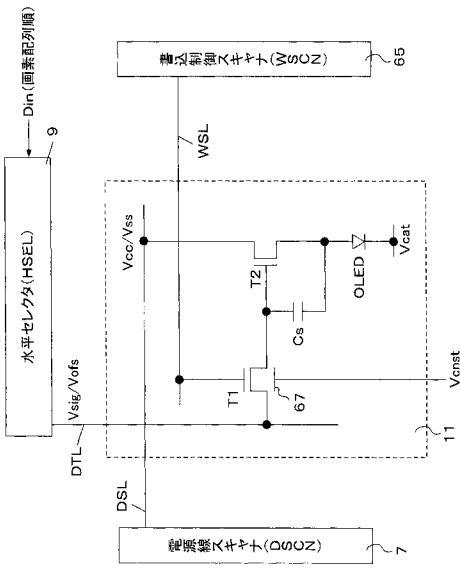

図2に、サブ画素11を構成する最も単純な画素回路の一つを示す。図2に示す画素回路は、薄膜トランジスタT1、T2及び保持容量Csで構成される。以下、薄膜トランジスタT1を「サンプリングトランジスタT1」といい、薄膜トランジスタT2を「駆動トランジスタT2」という。

10

【0007】

サンプリングトランジスタT1は、対応画素の階調に対応する信号電位Vsigの保持容量Csへの書き込みを制御するNチャネル型の薄膜トランジスタである。また、駆動トランジスタT2は、保持容量Csに保持された信号電位Vsigに応じて定まるゲート・ソース間電圧Vgsに基づいて駆動電流Idsを有機EL素子OLEDに供給するNチャネル型の薄膜トランジスタである。

【0008】

書込制御スキャナ5は、サンプリングトランジスタT1のオン・オフ動作を制御する回路デバイスである。また、電源線スキャナ7は、電源線DSLを高電位Vccと低電位Vssで駆動する回路デバイスである。水平セレクタ9は、信号線DTLを画素データDinに対応する信号電位Vsigと閾値補正用の基準電位Vofsで駆動する回路デバイスである。

20

【0009】

なお、発光期間中の電源線DSLは高電位Vccで駆動され、当該電源線DSLから駆動トランジスタT2を通じて有機EL素子OLEDに駆動電流Idsが供給される。因みに、発光期間中の駆動トランジスタT2は、常に飽和領域で動作している。すなわち、駆動トランジスタT2は、信号電位Vsigに応じた大きさの駆動電流Idsを有機EL素子OLEDに供給する定電流源として動作する。

【0010】

この駆動電流Idsは、次式で与えられる。

$$I_{ds} = k \cdot \mu \cdot (V_{gs} - V_{th})^2 \quad (式1)$$

30

因みに、μは、駆動トランジスタT2の多数キャリアの移動度である。また、Vthは、駆動トランジスタT2の閾値電圧である。また、kは、(W/L) · Cox / 2で与えられる係数である。ここで、Wはチャネル幅、Lはチャネル長、Coxは単位面積当たりのゲート容量である。

【0011】

ところで、画素回路11の形成には、高温ポリシリコンプロセスだけでなく、低温ポリシリコンプロセスやアモルファスシリコンプロセスの適用も可能である。ただし、低温ポリシリコンプロセスやアモルファスシリコンプロセスを用いて形成した薄膜トランジスタには、閾値電圧Vthや移動度μに特性バラツキが現れ易くなる。

【0012】

特に駆動トランジスタT2の特性バラツキは、駆動電流Idsの大きさに直接影響する。すなわち、信号電位Vsigは同じでも、有機EL素子の輝度階調に違いが現れる。この輝度差が一定以上大きくなると、画面上でも輝度差が視認される。

そこで、この種の画素回路では、閾値電圧Vthや移動度μの補正技術が従来より提案されている。

【0013】

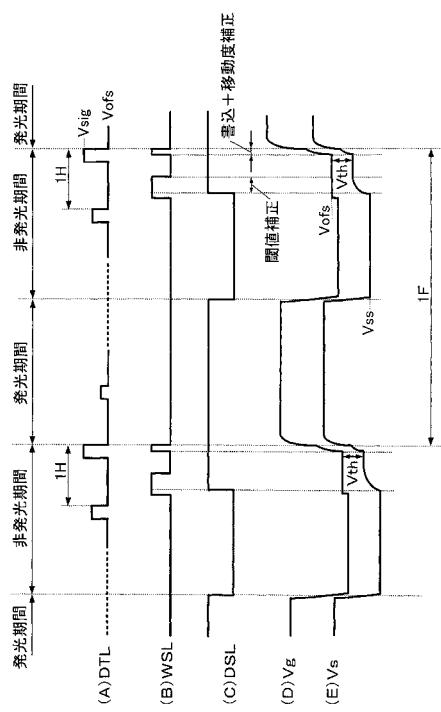

図3に、出願人によって提案されている特性補正機能付きの駆動動作例を示す。なお図3は、画素アレイ部3を構成する垂直解像度数分の水平ラインのうちのある1つの水平ラインの駆動動作例である。1フレーム期間は非発光期間と発光期間で構成され、非発光間に前述した特性補正動作が実行される。

50

## 【0014】

なお図3(A)はある信号線DTLの波形図を示し、図3(B)は書込制御線WSLの波形図を示し、図3(C)は電源線DSLの波形図を示している。また図3(D)は駆動トランジスタT2のゲート電位Vgの波形図を示し、図3(E)は駆動トランジスタT2のソース電位Vsの波形図を示す。

## 【0015】

図3に示す駆動動作の内容を簡単に説明する。図3に示す駆動動作では、非発光期間の開始タイミングで電源線DSLの電位が低電位Vssに切り替え制御される。これに伴い、駆動トランジスタT2のソース電位Vsは、低電位Vssに達するよう低下する。なお、カソード電位Vcatに有機EL素子OLEDの閾値電圧Vthelを加算した電位Vcat + Vthelよりもソース電位Vsが低下した時点で、有機EL素子OLEDは自動的に消灯する。

10

## 【0016】

また、この動作の際、駆動トランジスタT2のゲート電極はオープン状態にあるので、ソース電位Vsの電位低下に連動してゲート電位Vgも低下する。

次に、駆動トランジスタT2の閾値補正動作を説明する。駆動トランジスタT2の閾値補正動作は、電源線DSLが再び高電位Vccに制御されることで開始される。なお、ここでの高電位Vccは、次の発光期間の終了時点まで継続される。

## 【0017】

なお、サンプリングトランジスタT1は、電源線DSLが高電位Vccに立ち上がる前にオン状態に制御され、駆動トランジスタT2のゲート電位Vgがオフセット電位Vofsに固定される。これにより、駆動トランジスタT2のゲート・ソース間電圧Vgsは、その閾値電圧Vthより広い電圧Vofs - Vssにプリセットされる。

20

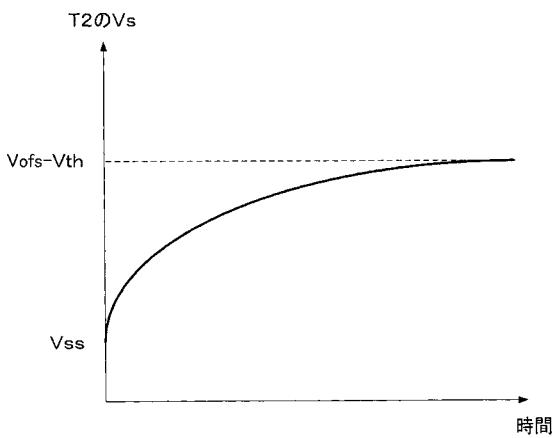

このプリセット状態において、電源線DSLが高電位Vccに切り換えられると、駆動トランジスタT2に電流が流れ、図4に示すように、ソース電位Vsが上昇する。

## 【0018】

この電流は、保持容量Csと有機EL素子OLEDに寄生する容量を充電するように流れ。寄生容量の充電に伴い、駆動トランジスタT2のソース電位Vsは上昇する。そして、ソース電位VsがVofs - Vthに達した時点で駆動トランジスタT2は自動的にカットオフ動作する。これにより、閾値補正が完了する。なお、Vofs - Vthは、Vcat + Vthelよりも小さい条件を満たすので、この時点で有機EL素子OLEDが発光することはない。

30

## 【0019】

この後、サンプリングトランジスタT1は、一度オフ制御される。この後、信号線DTLに信号電位Vsigが印加されたタイミングで、サンプリングトランジスタT1は再びオン制御される。これにより、駆動トランジスタT2のゲート・ソース間電圧Vgsは再び閾値電圧Vthより大きくなり、信号電位Vsigに応じた大きな電流が流れ始める。これが書込兼移動度補正動作である。

## 【0020】

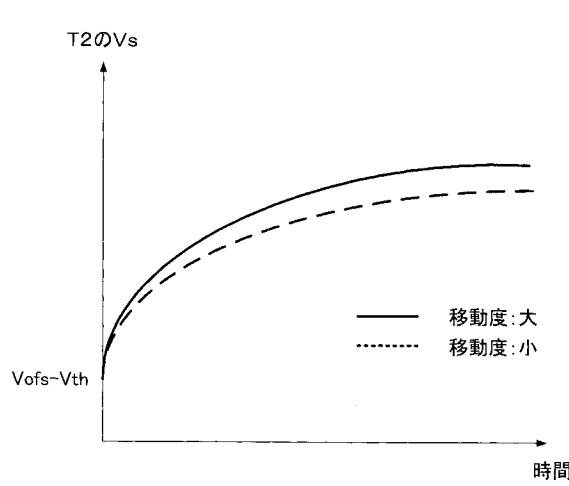

この場合も、電流は、保持容量Csと有機EL素子OLEDの寄生容量を充電するように流れ。なお、駆動トランジスタT2に流れる電流は移動度μの大きさに依存し、移動度μの大きい駆動トランジスタT2には大きな電流が流れ、移動度μの小さい駆動トランジスタT2には小さい電流が流れ。

40

## 【0021】

結果的に、移動度μの大きい駆動トランジスタT2のソース電位Vsの上昇は、移動度μの小さい駆動トランジスタT2のソース電位Vsの上昇よりも大きくなる。図5に、移動度μの大きさの違いによる駆動トランジスタT2のソース電位Vsの変化の違いを示す。

この移動度補正動作が終了すると、サンプリングトランジスタT1はオフ制御され、駆動トランジスタT2の駆動電流Ids'は有機EL素子OLEDへと流れ始める。これによ

50

り、有機EL素子OLEDの新たな発光期間が開始される。

#### 【0022】

ところで、前述した駆動動作で実行される補正動作は、駆動トランジスタT2の特性バラツキの補正を目的とする。すなわち、サンプリングトランジスタT1の特性バラツキの補正動作は用意されていない。これは、サンプリングトランジスタT1がスイッチング駆動され、特性バラツキの影響が小さいことが一因である。

#### 【0023】

ただし、サンプリングトランジスタT1の閾値電圧V<sub>th</sub>の変動は（すなわち、オン期間の変動は）、駆動トランジスタT2の移動度補正の動作点の変動を発生させ、移動度補正の精度に影響する。すなわち、輝度レベルを変動させる原因になる。

10

#### 【0024】

閾値電圧V<sub>th</sub>を変動させる原因の一つに、発光期間中の逆（負）バイアスがある。図6に、発光期間中の電位状態を示す。図6は、信号電位V<sub>sig</sub>が白階調時の電位状態である。因みに、有機EL素子OLEDのアノード電位V<sub>el</sub>（駆動トランジスタT2のソース電位V<sub>s</sub>）は5Vであり、駆動トランジスタT2のゲート電位V<sub>g</sub>は10Vである。

#### 【0025】

一方、サンプリングトランジスタT1のゲート電位V<sub>g</sub>は-3Vであり、サンプリングトランジスタT1が継続的に逆（負）バイアスに制御される。このバイアス状態は、サンプリングトランジスタT1の閾値電圧V<sub>th</sub>を低下させる方向に作用する。しかも、この閾値電圧V<sub>th</sub>の変化は、パネル内の散乱光がサンプリングトランジスタT1に入射することで増幅される。

20

#### 【0026】

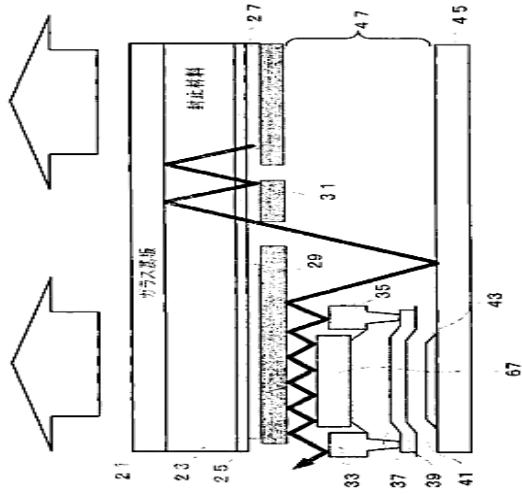

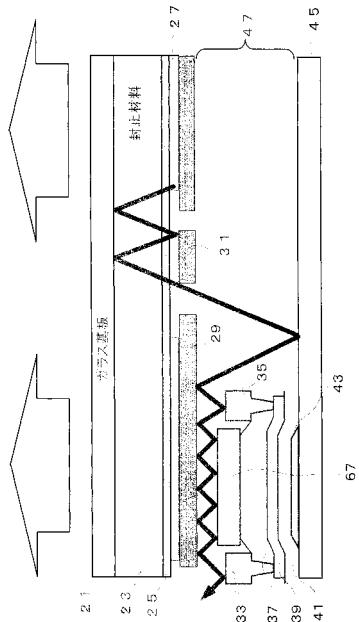

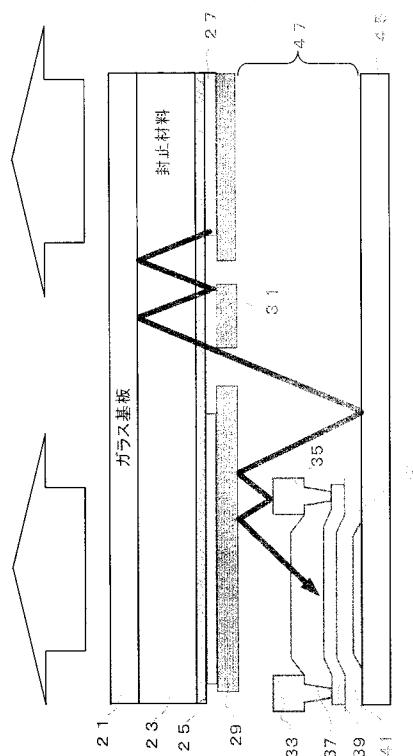

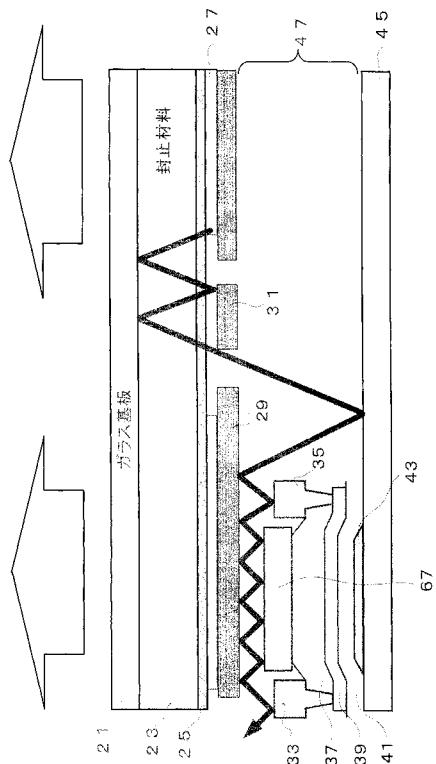

図7に、トップエミッショントラニジスタ構造を有する有機ELパネルの断面構造例を示す。なお、トップエミッショントラニジスタ構造とは、封止基板側から光が射出されるタイプのパネル構造をいうものとする。図中、封止基板は、ガラス基板21が相当する。もっとも、封止基板には、プラスチックフィルムその他の透過性材料も使用することができる。

20

#### 【0027】

封止基板21の下層には透過性の高い封止材料23が塗布される。封止材料23の下層には、有機EL素子OLEDを形成するカソード電極25、有機層27、アノード電極29が順番に形成される。なお、カソード電極25は光透過性材料で形成されている。一方、アノード電極29は金属材料で形成される。

30

#### 【0028】

また図7の場合、アノード電極29とアノード電極29との隙間部分に補助配線31が配置される。補助配線31は、カソード電極25にカソード電位を供給する配線であり、アノード電極29と同じ金属材料で形成される。この補助配線31は、パネルサイズが大きい場合に用いられることが多い、パネルサイズが小さい場合には用いられないことが多い。有機EL素子OLEDの下部には、画素回路が形成される。図7は、ボトムゲート型の薄膜トランジスタの例である。

#### 【0029】

図7の場合、ソース電極33、ドレイン電極35、層間膜37、ポリシリコン層（チャネル層）39、ゲート酸化膜41、ゲート電極43が画素回路を構成する構造である。これら画素回路は、駆動素子が形成される基板（いわゆる回路基板）としてのガラス基板45の表面に形成される。なお、ガラス基板45と有機EL素子OLEDの下層電極層であるアノード電極29との間には層間膜47が形成されている。

40

#### 【0030】

さて、矢印付きの太線で示した内部散乱光の説明に戻る。本来、有機EL素子OLEDで発生された光は、パネル内部から封止基板の外側へと射出される。

しかし、散乱光の一部はパネル内部で反射を繰り返し、図中の矢印で示すように、隣接画素を構成するサンプリングトランジスタT1のチャネル領域に入射する可能性がある。

#### 【0031】

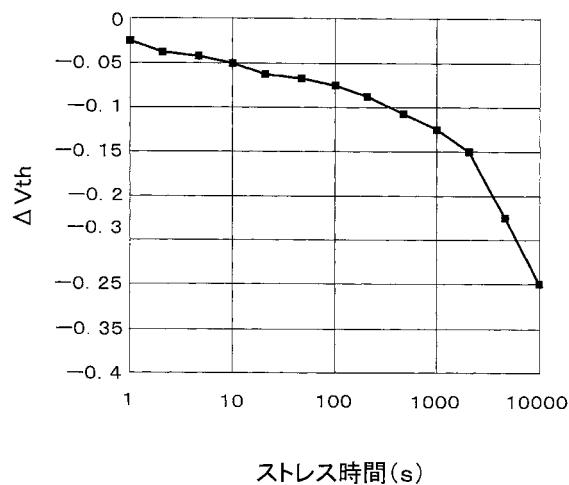

50

図8に、内部散乱光の入射と逆(負)バイアスの印加状態が継続する場合の閾値電圧V<sub>th</sub>の特性変動を測定した結果の一例を示す。

図8に示すように、ストレス時間が長いほど閾値電圧V<sub>th</sub>は徐々に低下し、1000秒を越える当たりから閾値電圧V<sub>th</sub>の低下量が増加する。

#### 【0032】

なお、発明者らの実験では、発光色の違いによらず、同様の閾値電圧V<sub>th</sub>の低下効果を確認することができた。なお、閾値電圧V<sub>th</sub>の低下効果は、波長が短ほど大きいことが確認された。すなわち、青色に対応するサブ画素11から発生した内部散乱光の影響が最も大きかった。

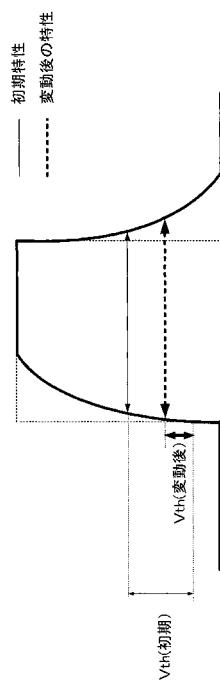

#### 【0033】

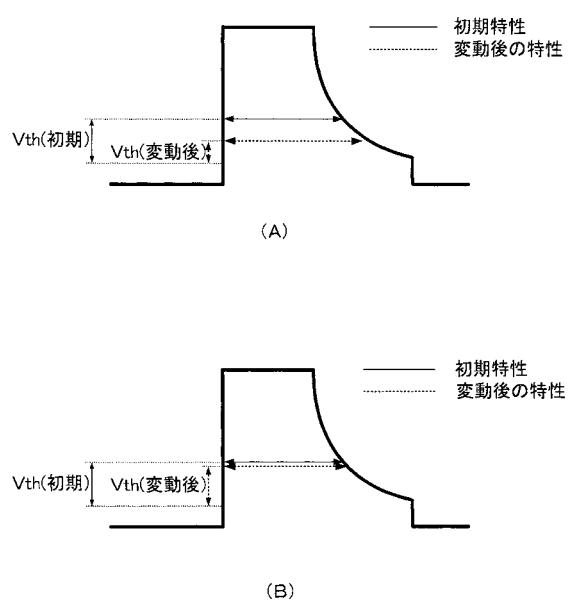

さて、サンプリングトランジスタT1の閾値電圧V<sub>th</sub>が下がると、図9に示すように、サンプリングトランジスタT1のオン期間は長くなる。

図9では、トランジエント特性を強調して表している。サンプリングトランジスタT1におけるオン期間の長期化は、移動度補正時間の増加として現れる。すなわち、移動度補正の動作点の変動として現れる。

#### 【0034】

移動度補正動作中は、駆動トランジスタT2のソース電位V<sub>s</sub>の上昇を伴うので、補正時間が長くなるとその分、ゲート・ソース間電圧V<sub>gs</sub>を小さくするように作用する。

この移動度補正後の駆動電流I<sub>ds</sub>の大きさは、次式で表すことができる。

$$I_{ds} = k \cdot \mu \cdot \{(V_{sig} - V_{ofs}) / [1 + (V_{sig} - V_{ofs}) \cdot k \cdot \mu \cdot t/C]\}^2 \quad (\text{式2})$$

式2からも分かるように、補正時間tが長いほど駆動電流I<sub>ds</sub>の大きさが小さくなる。

#### 【0035】

すなわち、サンプリングトランジスタT1の閾値電圧V<sub>th</sub>の変動が大きいと、結果的に本来の大きさよりも駆動電流I<sub>ds</sub>が小さくなってしまう。従って、閾値電圧V<sub>th</sub>の変動を加速させる内部散乱光のサンプリングトランジスタT1への入射を抑制する技術が必要であると発明者らは考える。

#### 【0036】

なお、式2に現れる“C”は、サブ画素11内の各容量成分の総和で与えられる。すなわち、“C”は、図10に示すように、保持容量C<sub>s</sub>と、有機EL素子OLED自体の容量成分C<sub>oled</sub>と、有機EL素子OLEDと並列に接続される容量成分C<sub>sub</sub>との総和として与えられる。もっとも、サブ画素11によっては、薄膜トランジスタ構造の容量成分C<sub>sub</sub>が存在しない場合もある。

また、式2に現れる“t”は、次式で与えられる。

$$t = C / (k \cdot \mu \cdot V_{sig}) \quad (\text{式3})$$

#### 【課題を解決するための手段】

#### 【0037】

発明者らは、アクティブマトリクス駆動方式に対応した画素構造を有するEL表示パネルに、内部散乱光の遮光構造を追加することを提案する。

すなわち、画素回路を構成する薄膜トランジスタのチャネル層よりも上層に位置する金属配線材料の一部パターンを、薄膜トランジスタのチャネル領域を塞ぐようにレイアウトする構造を提案する。この構造の採用により、内部散乱光の薄膜トランジスタへの入射を防ぐことができる。

#### 【0038】

なお、前述した金属配線材料による一部パターンは、薄膜トランジスタの主電極との間に印加される最大電圧がカットオフ電圧以下に設定された固定電位線に接続されることが望ましい。もっとも、前述した金属配線材料による一部パターンは、薄膜トランジスタの主電極との間に印加される最大電圧がカットオフ電圧以下に設定されたパルス信号線に接続されていても良いし、薄膜トランジスタのゲート電極の制御線に接続されていても良い。

#### 【0039】

10

20

30

40

50

ところで、内部散乱光の遮光は必ずしも金属配線材料に限る必要はない。すなわち、遮光性能を有するパターン（遮光パターン）であれば、少なくとも内部散乱光の薄膜トランジスタへの入射量を低減することができる。

#### 【0040】

例えば前述した遮光パターンは、金属原子を注入した半導体材料でも良い。また例えば前述した遮光パターンは、ブラックフィルタその他の有機材料でも良い。金属配線材料以外の遮光パターンの場合、金属配線材料に比べて遮光性能が劣るが内部散乱光の入射光量は確実に低下するので閾値電圧  $V_{th}$  の低下速度を小さくできる。

#### 【0041】

また、発明者らは、前述した構造を有するEL表示パネルを搭載した電子機器を提案する。

10

ここで、電子機器は、EL表示パネルと、システム全体の動作を制御するシステム制御部と、システム制御部に対する操作入力を受け付ける操作入力部とで構成する。

#### 【発明の効果】

#### 【0042】

発明者らの提案する発明では、薄膜トランジスタの閾値電圧  $V_{th}$  の低下を加速させる原因であった内部散乱光のチャネル領域への到達を防ぐ又は到達する光量を小さくすることができる。この結果、移動度補正時の動作点変動（補正時間長の増加）を最小化できる。

#### 【図面の簡単な説明】

#### 【0043】

【図1】有機ELパネルの機能ブロック構成を説明する図である。

20

【図2】画素回路と駆動回路との接続関係を説明する図である。

#### 【図3】図2に示す画素回路の駆動動作例を示す図である。

【図4】閾値補正動作時における駆動トランジスタのソース電位の変化を説明する図である。

【図5】移動度補正動作時における駆動トランジスタのソース電位の変化を説明する図である。

#### 【図6】発光期間中における画素回路内の電位関係を説明する図である。

#### 【図7】内部散乱光の伝搬経路を説明する図である。

#### 【図8】サンプリングトランジスタの閾値電圧変動を説明する図である。

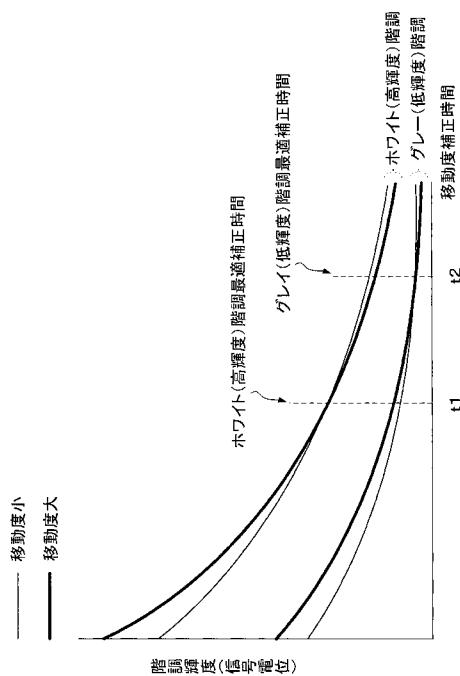

【図9】閾値電圧の変動と移動度補正時間の関係を説明する図である。

30

【図10】駆動電流に作用する容量成分を説明する図である。

#### 【図11】有機ELパネルの外観構成例を示す図である。

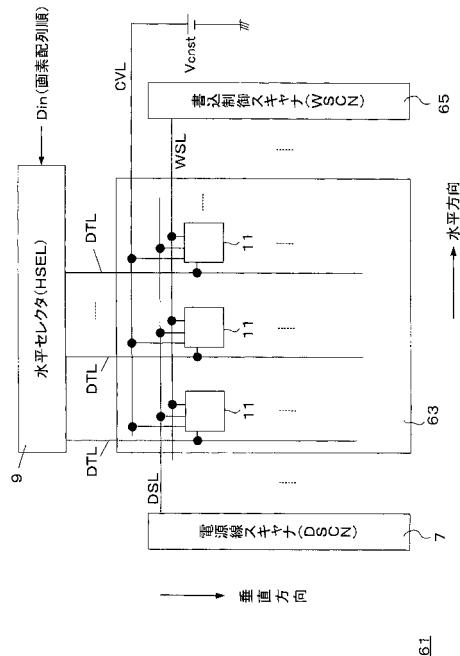

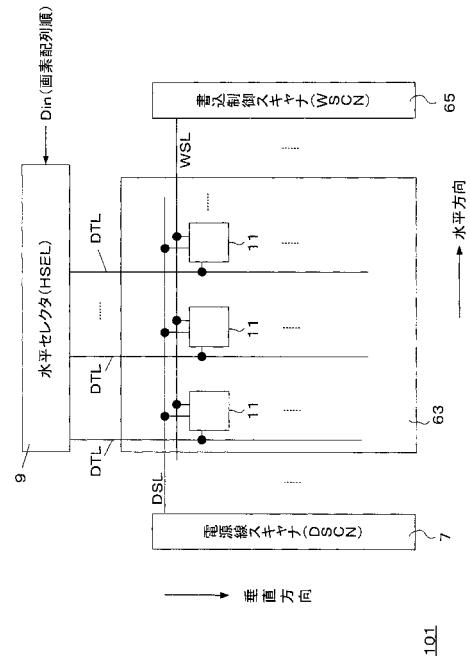

#### 【図12】画素回路と駆動回路との接続関係を説明する図である。

#### 【図13】遮光パターンを使用する場合の内部散乱光の伝搬経路を説明する図である。

#### 【図14】形態例1に係る画素回路の構成例を示す図である。

#### 【図15】階調輝度と最適な移動度補正時間との関係を説明する図である。

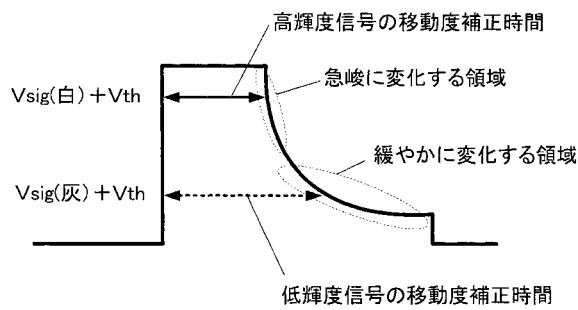

【図16】階調輝度に応じた移動度補正時間の最適化に使用する書き制御信号の信号波形を説明する図である。

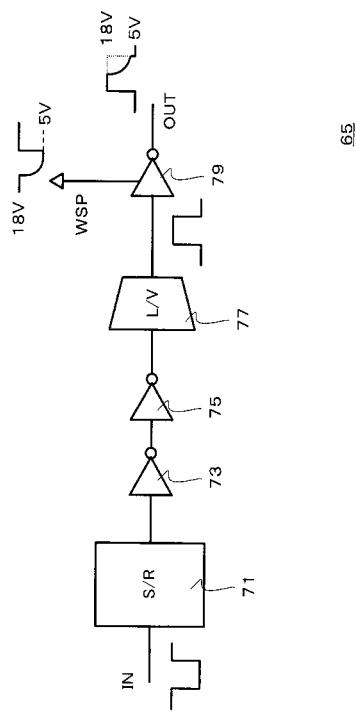

#### 【図17】形態例において提案する書き制御スキャナの回路構成を説明する図である。

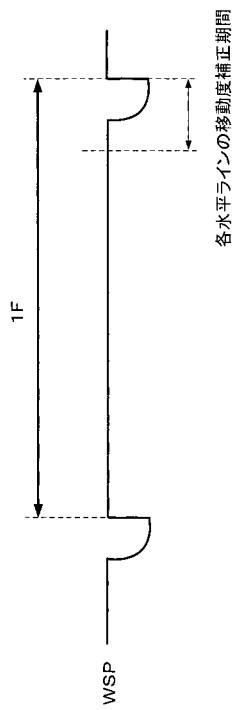

#### 【図18】形態例において提案する電源電圧パルスの波形例を説明する図である。

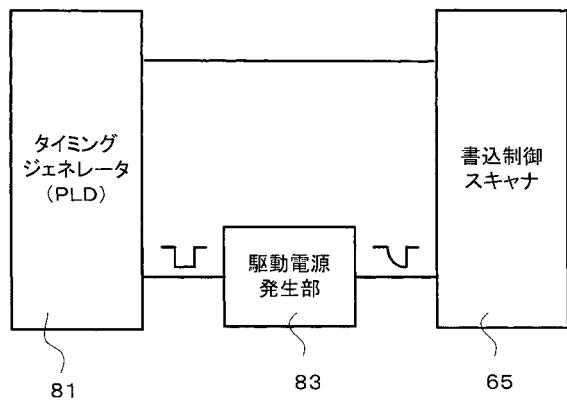

#### 【図19】電源電圧パルスの発生回路系を説明する図である。

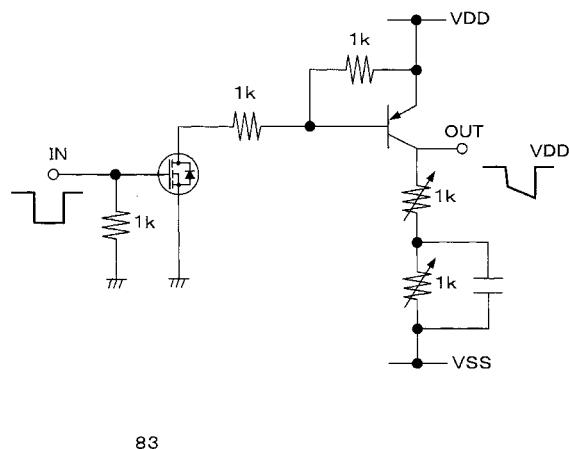

#### 【図20】駆動電源発生部の内部構成例を説明する図である。

【図21】遮光パターンと図16に示す書き制御信号を組み合わせる場合の技術的な効果を説明する図である。

#### 【図22】他の給電形態を説明する図である。

#### 【図23】画素回路内の接続形態を説明する図である。

#### 【図24】他の給電形態を説明する図である。

#### 【図25】画素回路内の接続形態を説明する図である。

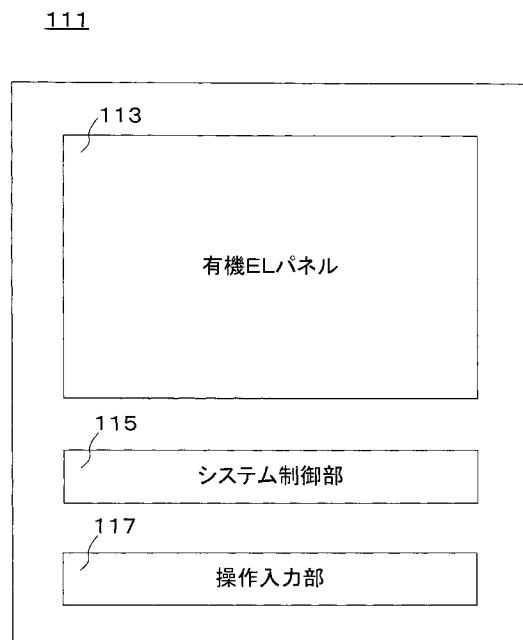

#### 【図26】電子機器の概念構成例を示す図である。

20

30

40

50

【図27】電子機器の商品例を示す図である。

【図28】電子機器の商品例を示す図である。

【図29】電子機器の商品例を示す図である。

【図30】電子機器の商品例を示す図である。

【図31】電子機器の商品例を示す図である。

【発明を実施するための形態】

【0044】

以下、発明を、アクティブマトリクス駆動型の有機ELパネルに適用する場合について説明する。

なお、本明細書で特に図示又は記載されない部分には、当該技術分野の周知又は公知技術を適用する。また以下に説明する形態例は、発明の一つの形態例であって、これらに限定されるものではない。

【0045】

(A) 外観構成

なお、この明細書では、画素アレイ部と駆動回路（例えば書き込み制御スキャナ及び電源線スキャナ）と同じ半導体プロセスを用いて同じ基板上に形成した表示パネルだけではなく、例えば特定用途向けICとして製造された駆動回路を画素アレイ部の形成された基板上に実装したものも有機ELパネルと呼ぶ。

【0046】

図11に、有機ELパネルの外観構成例を示す。有機ELパネル51は、支持基板53のうち画素アレイ部の形成領域に対向基板55を貼り合わせた構造を有している。

【0047】

支持基板53は、ガラス、プラスチックその他の基材で構成される。トップエミッショング構造の場合、支持基板53の表面には画素回路が形成される。すなわち、支持基板53が回路基板に相当する。一方、ボトムエミッショング構造の場合、支持基板53の表面には有機EL素子が形成される。すなわち、支持基板53が封止基板に相当する。

【0048】

対向基板55も、ガラス、プラスチックその他の透明部材を基材とする。対向基板55は、封止材料を挟んで支持基板53の表面を封止する部材である。なお、トップエミッショング構造の場合、対向基板55が封止基板に相当する。また、ボトムエミッショング構造の場合、対向基板55が回路基板に相当する。

【0049】

なお、有機ELパネル51には、外部信号や駆動電源を入力するためのFPC（フレキシブルプリントサーキット）57が配置される。

【0050】

(B) 形態例1

(B-1) システム構成

図12に、有機ELパネル61のシステム構成例を示す。なお図12には、図1との対応部分に同一符号を付して示す。

図12に示す有機ELパネル61は、画素アレイ部63と、その駆動回路である書き込み制御スキャナ65、電源線スキャナ7及び水平セレクタ9とで構成される。

【0051】

(1) 画素アレイ部の構成

画素アレイ部63の画素構造は、図1に示す画素構造と同じである。すなわち、画素アレイ部63は、信号線DTLと書き込み制御線WSLの各交点にサブ画素11を配置したマトリクス構造を有している。構造上の違いは、サンプリングトランジスタT1のチャネル層の全体を覆うように、チャネル層の上層に遮光パターン67がレイアウトされる点である。

【0052】

ここでの遮光パターン67が、特許請求の範囲における「一部パターン」又は「遮光パ

10

20

30

40

50

ターン」に対応する。

図13に、遮光パターン67とサンプリングトランジスタT1のチャネル層との位置関係を示す。図13に示すように、遮光パターン67は、サンプリングトランジスタT1のチャネル層よりも上層に、チャネル層の全体を覆うようにレイアウトされる。因みに、遮光パターン67は、周辺パターンから独立又は分離したパターンとして形成される。

#### 【0053】

なお、遮光パターン67は、信号線DTLと同じ金属材料（例えばアルミニウム、モリブデン等）で形成される。

従って、アノード電極29で反射されてパネル内部に戻ってきた内部散乱光は、遮光パターン67の表面で再び入射方向に反射される。このため、内部散乱光がチャネル層に入射されることはない。

#### 【0054】

ここでの遮光パターン67は、金属配線層（ソース電極33及びドレイン電極35）の形成時に同時に形成することができる。このため、プロセスの追加は無く、製造コストの増加はない。ただし、遮光パターン67と主電極との隙間が小さすぎると、ショートサーキットが形成されるおそれがある。従って、遮光パターン67と主電極との間には十分な隙間を確保するものとする。

#### 【0055】

なお、遮光パターン67は、サンプリングトランジスタT1だけでなく、駆動トランジスタT2のチャネル層の全体を覆うようにレイアウトすることが望ましい。もっとも、駆動トランジスタT2については、閾値補正機能が用意されている。従って、この形態例のように、サンプリングトランジスタT1についてのみ、そのチャネル層の全体を覆う構成を採用しても良い。

#### 【0056】

また、この形態例の場合、遮光パターン67は、サンプリングトランジスタT1の主電極（ソース電極33、ドレイン電極35）の形成時に同時に形成することができる。従って、遮光パターン67を追加しても製造コストが上昇することはない。

ところで、遮光パターン67は、固定電源線CVLを通じて固定電位V<sub>cnst</sub>に制御する。なお、固定電位V<sub>cnst</sub>の電源はパネル上のいずれかの位置に配置される。

#### 【0057】

ここでの固定電位V<sub>cnst</sub>は、書き制御線WSLによるオン制御期間以外においてサンプリングトランジスタT1をオン動作させないような電位（すなわち、カットオフ電圧）以下に設定しておくものとする。すなわち、固定電位V<sub>cnst</sub>は、書き制御線WSLによるオン制御期間以外においてサンプリングトランジスタT1の主電極に印加される可能性のある全ての電位よりも閾値電圧以上高くならないように設定される。

#### 【0058】

勿論、固定電位V<sub>cnst</sub>の設定には、サンプリングトランジスタT1の閾値電圧V<sub>th</sub>の経時変化も考慮する。すなわち、変動分を考慮して予め十分なマージンを用意する。これにより、予期せぬタイミングでサンプリングトランジスタT1がオン動作し、保持容量C<sub>s</sub>の保持電位が変化するのを防ぐことができる。

#### 【0059】

##### (2) 書き制御スキャナの構成

図14に、画素回路11と各駆動回路との接続関係を示す。図14に示すように、画素回路11と各駆動回路との接続関係は、図2に示す接続関係と同じである。すなわち、書き制御スキャナ65によって駆動制御される書き制御線WSLは、サンプリングトランジスタT1のゲート電極と接続され、電源線スキャナ7によって駆動制御される電源線DSLは、駆動トランジスタT2の一方の主電極と接続される。

#### 【0060】

この形態例に特徴的な部分は、書き制御スキャナ65である。この書き制御スキャナ65に新たな機能は、階調輝度の違いによる移動度補正時間の最適化技術である。

10

20

30

40

50

図15に、階調輝度と対応する最適な移動度補正時間との関係を示す。なお図15の横軸は移動度補正時間であり、図15の縦軸は階調輝度（信号電位  $V_{sig}$ ）である。

#### 【0061】

図15に示すように、高輝度（ホワイト階調）の場合、移動度  $\mu$  が大きい駆動トランジスタT2の輝度レベルと移動度  $\mu$  が小さい駆動トランジスタT2の輝度レベルは、移動度補正時間が  $t_1$  の時点で同じになる。すなわち、高輝度画素の移動度補正時間は  $t_1$  であることが望まれる。

#### 【0062】

一方、低輝度（グレー階調）の場合、移動度  $\mu$  が大きい駆動トランジスタT2の輝度レベルと移動度  $\mu$  が小さい駆動トランジスタT2の輝度レベルは、移動度補正時間が  $t_2$  の時点で同じになる。すなわち、低輝度画素の移動度補正時間は  $t_2$  であることが望まれる。

10

#### 【0063】

従って、移動度補正時間を固定する駆動方式を採用すると、特定の輝度レベル以外の画素回路では移動度補正時間に過不足が発生してしまう。この過不足は、最悪の場合、輝度ムラやスジとして視認されてしまう。

そこで、書込制御スキャナ65には、各画素の輝度レベルに応じて各画素回路の移動度補正時間を自動調整する機能を搭載する。

#### 【0064】

すなわち、高輝度レベルに対応する画素回路では移動度補正時間が自動的に短くなり、低輝度レベルに対応する画素回路では移動度補正時間が自動的に長くなるように調整される駆動機能を採用する。

20

なお、移動度補正時間は、サンプリングトランジスタT1のオン動作時間として与えられる。

#### 【0065】

そこで、この形態例の場合には、移動度補正期間に対応するサンプリングトランジスタT1の書込制御信号を図16に示す波形に制御できる機能を搭載する書込制御スキャナ65を提案する。図16に示す書込制御信号は、急峻に電位が低下する波形領域と緩やかに電位が低下する波形領域を有している。

30

#### 【0066】

この書込制御信号の採用により、高輝度画素では、サンプリングトランジスタT1のゲート・ソース間電圧  $V_{gs}$  が、波形が急峻に変化する領域で閾値電圧  $V_{th}$  より小さくなる（自動的にカットオフする）。一方、低輝度画素では、サンプリングトランジスタT1のゲート・ソース間電圧  $V_{gs}$  が、波形が緩やかに変化する領域で閾値電圧  $V_{th}$  より小さくなる（自動的にカットオフする）。

#### 【0067】

このことは、信号電位  $V_{sig}$  の大きさに応じて各画素の移動度補正時間が自動的に調整され、信号電位  $V_{sig}$  が異なっても最適な移動度補正動作が確保されることを意味する。

図17に、前述した書込制御信号を発生する書込制御スキャナ65の部分構成例を示す。なお、図17に示す構成は、1つの水平ラインに対応する構成である。従って、画面内の垂直方向には、図17に示す構成の回路が垂直解像度数分だけ配置される。

40

#### 【0068】

以下では、この部分回路も書込制御スキャナ65と呼ぶ。書込制御スキャナ65は、シフトレジスタ71、2段のインバータ回路73、75で構成されるバッファ回路、レベルシフタ77及び1段のインバータ回路79で構成される出力バッファ回路で構成される。

この構成自体は一般的である。特徴的な構成は、インバータ回路79に供給される電源電圧パルスWSPの波形レベルが図16に示す特性で低下する点である。

#### 【0069】

勿論、この波形レベルの低下が出現するタイミングは、図18に示すように、各水平ラインの移動度補正期間に位相同期して実行される必要がある。

50

図19に、書込制御スキャナ65に供給される電源電圧パルスWSPを発生する回路デバイスの構成を示す。

#### 【0070】

電源電圧パルスWSPは、タイミングジェネレータ81と駆動電源発生部83により生成される。タイミングジェネレータ81は、書込制御スキャナ65だけでなく、電源線スキャナ7及び水平スキャナ9に駆動パルス(矩形波)を供給する回路デバイスである。なお、駆動パルスの立ち下がりタイミングは、移動度補正の開始タイミングに対して所定時間だけ遅れたタイミングに設定される。

#### 【0071】

駆動電源発生部83は、矩形波状の駆動パルスに基づいて、立ち下がり時の波形が2段階に折れ曲がる駆動電圧パルスWSP(図18)を発生する回路デバイスである。10

図20に、駆動電源発生部83の回路例を示す。図20に示す駆動電源発生部83は、2個のトランジスタと、1個の容量と、3個の固定抵抗と、2個の可変抵抗により構成される。

#### 【0072】

駆動電源発生部83は、駆動パルスをアナログ処理し、立ち下がり時の波形が2段階に折れ曲がる電源電圧パルスWSPを発生する。すなわち、1段目の立ち下がり波形の傾斜角度が大きく、2段目の立ち下がり波形の傾斜が小さい電源電圧パルスWSPを発生する。20

#### 【0073】

##### (B-2) 駆動動作及び効果

この形態例の場合、移動度補正期間の動作以外は、前述した図3の駆動動作と同じである。なお、各サブ画素11からパネル表面に射出される光束の一部は、内部散乱光としてガラス基板21の内側に残留する。

#### 【0074】

しかし、この形態例の場合には、サンプリングトランジスタT1のチャネル層の上面に配置した遮光パターン67により、チャネル層への内部散乱光の入射が遮光される。

かくして、サンプリングトランジスタT1の閾値電圧Vthの変動は抑制され、移動度補正時間の最適状態が維持される。

#### 【0075】

しかも、この内部散乱光の遮光は、この形態例で提案する移動度補正動作時の駆動方式との組み合わせにおいてより高い効果が期待できる。30

前述したように、この形態例の場合には、信号電位Vsigの大きさに応じて移動度補正時間が自動的に最適化されるように、移動度補正の開始から一定時間後に電源電圧パルスWSPが2段階に低下する波形を採用する。

#### 【0076】

このため、図21(A)に示すように、閾値電圧Vthの変動が大きくなると、移動度補正時間が大きく変化してしまう。特に、電源電圧パルスWSPが急峻に低下する領域が最適な移動度補正時間である信号電位Vsigの場合、閾値電圧Vthが低下すると、サンプリングトランジスタT1のオン時間が大きく変化してしまう。このことは、移動度補正時間の電源電圧パルスWSPの波形を2段階に鈍らせて低下させる駆動方式に固有の問題である。40

#### 【0077】

しかし、この形態例の場合には、内部散乱光の遮光により閾値電圧Vthの変化を最小化できるので、図21(B)に示すように、実際の移動度補正時間が各信号電位Vsigについて最適化された移動度補正時間から大きく変化することを防ぐことができる。

このように、内部散乱光の遮光はそれ自体でも移動度補正時間の動作点の安定に寄与できるだけでなく、移動度補正時間長の最適化技術と組み合わせることにより、より高い効果を実現することができる。

#### 【0078】

10

20

30

40

50

(C) 他の形態例

(C-1) 遮光パターンへの他の給電例

前述した形態例の場合には、遮光パターン 67 に固定電位  $V_{cnst}$  を給電する場合について説明した。しかし、遮光パターン 67 をパルス電源で駆動しても良い。なお、パネルの断面構造は図 13 に示す構造と同じであるものとする。

【0079】

図 22 に有機 EL パネルの構造例を示し、図 23 に画素回路内の接続例を示す。図 22 及び図 23 に示す有機 EL パネル 91 の場合、遮光パターン 67 は、可変電源線 VSL を通じてパルス電圧源 93 に接続される。なお図 22 では、パルス電圧源 93 が全ての画素回路 11 に接続されているように描いているが、パルス電圧源 93 は水平ライン単位で用意されていても良い。画素回路 11 の動作タイミングは水平ライン単位で制御されるためである。

【0080】

勿論、パルス電圧源 93 が発生する電位は、書込制御線 WSL によるオン制御期間以外においてサンプリングトランジスタ T1 をオン動作させないような電位（すなわち、カットオフ電圧）以下に設定しておくものとする。この条件を満たす限り、駆動パルスの切り替えタイミングは任意である。勿論この場合も、パルス電圧源 93 が発生する電位は、サンプリングトランジスタ T1 の閾値電圧  $V_{th}$  の経時変化を考慮する。

【0081】

図 24 に有機 EL パネルの構造例を示し、図 25 に画素回路内の接続例を示す。図 24 及び図 25 に示す有機 EL パネル 101 の場合、遮光パターン 67 は書込制御線 WSL に接続される。すなわち、サンプリングトランジスタ T1 はダブルゲート構造の薄膜トランジスタを構成する。この接続例は、図 22 及び図 23 に示した給電例の一例に当たる。

【0082】

(C-2) 遮光パターンの材料

前述した形態例の場合には、遮光パターン 67 が薄膜トランジスタ T2 の電極配線と同じ金属材料である場合について説明した。すなわち、遮光パターン 67 が内部散乱光の全てを入射方向に反射できる材料を想定した。しかし、遮光パターン 67 は、電極配線とは異なる金属材料で形成されていても良い。

【0083】

なお、遮光パターン 67 は内部散乱光の全てを入射方向に反射することができなくても良い。透過する光量を減少することができれば閾値電圧の変動効果を低減することができれば、一定の効果を期待できるからである。例えば、遮光パターン 67 は、金属原子を注入した半導体材料でも良い。また例えば、遮光パターン 67 は、ブラックフィルタその他の濃色系の有機材料でも良い。

【0084】

(C-3) 他の画素回路例

前述した形態例では、画素回路 11 が 2 個の薄膜トランジスタ T1、T2 と 1 個の保持容量 Cs とで構成される場合について説明した。

しかし、本発明は、画素回路 11 の構造とは無関係である。従って、画素回路 11 の構成やその駆動方法は任意である。

また、形態例の場合には、薄膜トランジスタ T1 がボトムゲート構造の場合について説明した。しかし、薄膜トランジスタ T1 はトップゲート構造でも良い。

【0085】

(C-4) 他のパネル構造

前述した形態例の場合には、EL 表示パネルがトップエミッション構造の場合について説明した。

しかし、EL 表示パネルはボトムエミッション構造でも良い。ここで、ボトムエミッション構造とは、回路基板側から光が射出されるタイプのパネル構造をいうものとする。

【0086】

(C - 5) 製品例

(a) 電子機器

前述の説明では、有機ELパネルを例に発明を説明した。しかし、前述した有機ELパネルは、各種の電子機器に実装した商品形態でも流通される。以下、他の電子機器への実装例を示す。

【0087】

図26に、電子機器111の概念構成例を示す。電子機器111は、前述した有機ELパネル113、システム制御部115及び操作入力部117で構成される。システム制御部115で実行される処理内容は、電子機器111の商品形態により異なる。また、操作入力部117は、システム制御部115に対する操作入力を受け付けるデバイスである。操作入力部117には、例えばスイッチ、ボタンその他の機械式インターフェース、グラフィックインターフェース等が用いられる。

【0088】

なお、電子機器111は、機器内で生成される又は外部から入力される画像や映像を表示する機能を搭載していれば、特定の分野の機器には限定されない。

図27に、その他の電子機器がテレビジョン受像機の場合の外観例を示す。テレビジョン受像機121の筐体正面には、フロントパネル123及びフィルターガラス125等で構成される表示画面127が配置される。表示画面127の部分が、形態例で説明した有機ELパネルに対応する。

【0089】

また、この種の電子機器111には、例えばデジタルカメラが想定される。図28に、デジタルカメラ131の外観例を示す。図28(A)が正面側(被写体側)の外観例であり、図28(B)が背面側(撮影者側)の外観例である。

【0090】

デジタルカメラ131は、保護カバー133、撮像レンズ部135、表示画面137、コントロールスイッチ139及びシャッターボタン141で構成される。このうち、表示画面137の部分が、形態例で説明した有機ELパネルに対応する。

【0091】

また、この種の電子機器111には、例えばビデオカメラが想定される。図29に、ビデオカメラ151の外観例を示す。

ビデオカメラ151は、本体153の前方に被写体を撮像する撮像レンズ155、撮影のスタート/ストップスイッチ157及び表示画面159で構成される。このうち、表示画面159の部分が、形態例で説明した有機ELパネルに対応する。

【0092】

また、この種の電子機器111には、例えば携帯端末装置が想定される。図30に、携帯端末装置としての携帯電話機161の外観例を示す。図30に示す携帯電話機161は折りたたみ式であり、図30(A)が筐体を開いた状態の外観例であり、図30(B)が筐体を折りたたんだ状態の外観例である。

【0093】

携帯電話機161は、上側筐体163、下側筐体165、連結部(この例ではヒンジ部)167、表示画面169、補助表示画面171、ピクチャーライト173及び撮像レンズ175で構成される。このうち、表示画面169及び補助表示画面171の部分が、形態例で説明した有機ELパネルに対応する。

【0094】

また、この種の電子機器111には、例えばコンピュータが想定される。図31に、ノート型コンピュータ181の外観例を示す。

ノート型コンピュータ181は、下型筐体183、上側筐体185、キーボード187及び表示画面189で構成される。このうち、表示画面189の部分が、形態例で説明した有機ELパネルに対応する。

【0095】

10

20

30

40

50

これらその他、電子機器 111 には、オーディオ再生装置、ゲーム機、電子ブック、電子辞書等が想定される。

### 【0096】

#### (C-6) 他の表示デバイス例

前述の形態例においては、発明を有機ELパネルに適用する場合について説明した。

しかし、前述した駆動技術は、その他のEL表示装置に対しても適用することができる。例えばLEDを配列する表示装置その他のダイオード構造を有する発光素子を画面上に配列した表示装置に対しても適用できる。例えば無機ELパネルにも適用できる。

### 【0097】

#### (C-7) その他

前述した形態例には、発明の趣旨の範囲内で様々な変形例が考えられる。また、本明細書の記載に基づいて創作される又は組み合わせられる各種の変形例及び応用例も考えられる。

### 【符号の説明】

#### 【0098】

31...補助配線、61...有機ELパネル、63...画素アレイ部、65...書き制御スイッチ、67...遮光パターン、81...タイミングジェネレータ、83...駆動電源発生部

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 1 1】

51

【図 1 2】

61

【図 1 3】

2.1

2.3

2.5

2.7

封止材料

3.1

31

35

37

39

41

43

45

47

67

【図 1 4】

【図 15】

【図 16】

【図 17】

【図 18】

【図 19】

【図 20】

【図 21】

【図 22】

【図 2 3】

【図 2 4】

【図 2 5】

【図 2 6】

【図 27】

【図 28】

【図 29】

【図 30】

【図 3 1】

181

---

フロントページの続き

|                         |                      |            |

|-------------------------|----------------------|------------|

| (51) Int.CI.            | F I                  | テーマコード(参考) |

| H 0 1 L 51/50 (2006.01) | G 0 9 G 3/20 6 2 4 B |            |

|                         | G 0 9 G 3/20 6 1 1 H |            |

|                         | G 0 9 G 3/20 6 4 2 A |            |

|                         | G 0 9 G 3/20 6 4 1 D |            |

|                         | G 0 9 G 3/20 6 8 0 H |            |

|                         | H 0 5 B 33/14 A      |            |

(72)発明者 内野 勝秀

東京都港区港南1丁目7番1号 ソニー株式会社内

F ターム(参考) 3K107 AA01 BB01 CC02 CC21 CC33 DD39 EE03 EE27 HH04 HH05

5C080 AA06 BB05 CC03 DD05 EE29 FF11 HH09 JJ02 JJ03 JJ04

JJ05 JJ06 KK01 KK07 KK43 KK47

5C094 AA16 AA21 AA53 BA03 BA23 BA27 CA19 DA13 DB01 ED15

FA02 FB01 FB12 FB14 GA10 HA06 HA07

5C380 AA01 AA02 AA03 AB06 AB11 AB12 AB18 AB22 AB23 AB24

AB34 AB45 AC07 AC08 AC09 AC11 BA31 BA38 BA39 BA45

BB02 BD05 CB14 CB20 CB26 CB31 CC02 CC03 CC04 CC06

CC07 CC27 CC30 CC33 CC41 CC62 CC71 CD012 CD032 CE01

CF07 CF22 CF23 CF24 CF25 CF41 CF42 CF43 DA02 DA06

DA47

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | EL显示板和电子设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2010157514A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2010-07-15 |

| 申请号            | JP2010017669                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2010-01-29 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 山下淳一<br>山本哲郎<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 山下 淳一<br>山本 哲郎<br>内野 勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | H05B33/26 G09F9/30 H01L27/32 G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | H05B33/26.Z G09F9/30.349.C G09F9/30.338 G09F9/30.365.Z G09G3/30.J G09G3/20.624.B G09G3 /20.611.H G09G3/20.642.A G09G3/20.641.D G09G3/20.680.H H05B33/14.A G09F9/30.365 G09G3 /3233 G09G3/3266 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC02 3K107/CC21 3K107/CC33 3K107/DD39 3K107/EE03 3K107 /EE27 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/CC03 5C080/DD05 5C080/EE29 5C080/FF11 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5C080/KK01 5C080/KK07 5C080/KK43 5C080/KK47 5C094/AA16 5C094/AA21 5C094/AA53 5C094/BA03 5C094 /BA23 5C094/BA27 5C094/CA19 5C094/DA13 5C094/DB01 5C094/ED15 5C094/FA02 5C094/FB01 5C094/FB12 5C094/FB14 5C094/GA10 5C094/HA06 5C094/HA07 5C380/AA01 5C380/AA02 5C380 /AA03 5C380/AB06 5C380/AB11 5C380/AB12 5C380/AB18 5C380/AB22 5C380/AB23 5C380/AB24 5C380/AB34 5C380/AB45 5C380/AC07 5C380/AC08 5C380/AC09 5C380/AC11 5C380/BA31 5C380 /BA38 5C380/BA39 5C380/BA45 5C380/BB02 5C380/BD05 5C380/CB14 5C380/CB20 5C380/CB26 5C380/CB31 5C380/CC02 5C380/CC03 5C380/CC04 5C380/CC06 5C380/CC07 5C380/CC27 5C380 /CC30 5C380/CC33 5C380/CC41 5C380/CC62 5C380/CC71 5C380/CD012 5C380/CD032 5C380 /CE01 5C380/CF07 5C380/CF22 5C380/CF23 5C380/CF24 5C380/CF25 5C380/CF41 5C380/CF42 5C380/CF43 5C380/DA02 5C380/DA06 5C380/DA47 |         |            |

| 代理人(译)         | 森浩一<br>吉井正明<br>山本隆久                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 其他公开文献         | <a href="#">JP5007844B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

**摘要(译)**

要解决的问题：提供一种面板结构，其抑制由于内部散射光的影响引起的阈值电压波动。解决方案：具有符合有源矩阵驱动方法的像素结构的EL显示面板具有提供屏蔽内部散射光的结构。具体地，位于构成像素电路的采样晶体管的沟道层上方的层上的金属布线材料的图案的一部分被布置为阻挡采样晶体管的沟道区域。