(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-65292

(P2006-65292A)

(43) 公開日 平成18年3月9日(2006.3.9)

(51) Int.CI.

F 1

テーマコード(参考)

**G09G** 3/30 (2006.01)

**G09G** 3/20 (2006.01)

**G09G** 3/36 (2006.01)

**H01L** 51/50 (2006.01)

G09G 3/30 Z 3K007

G09G 3/20 612A 5C006

G09G 3/20 621J 5C080

G09G 3/20 621L

G09G 3/20 622B

審査請求 有 請求項の数 24 O L (全 27 頁) 最終頁に続く

(21) 出願番号 特願2005-169174 (P2005-169174)

(22) 出願日 平成17年6月9日 (2005.6.9)

(31) 優先権主張番号 特願2004-216891 (P2004-216891)

(32) 優先日 平成16年7月26日 (2004.7.26)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107076

弁理士 藤岡 英吉

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 青木 幸司

長野県諏訪市大和3丁目3番5号 セイコ

エプソン株式会社内

F ターム(参考) 3K007 AB18 BA06 DB03 GA03 GA04

最終頁に続く

(54) 【発明の名称】電気光学パネルの駆動回路及び駆動方法、並びに電気光学装置、及びこれを備えた電子機器

## (57) 【要約】

【課題】 例えば、有機ELパネルの如き電気光学パネルを駆動するための駆動回路が静電破壊されることを低減する。

【解決手段】 ダイオード158a(j)は、第3X側電源線503a及び第4X側電源線504aの間に設けられており、第3X側電源線503a及び第4X側電源線504aの一方の電源線で発生した静電気を他方に逃がす電流経路159(j)(但し、j=1, 2, ..., n)を構成する。電流経路159(j)は、第3X側電源線503a及び第4X側電源線504aのうち一方の電源線で発生した静電気によってX側レベルシフタ152に含まれる增幅回路152a(j)及びバッファ156a(j)が静電破壊されることを低減する。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

画像表示領域に複数の画素部が設けられた電気光学パネルを駆動するための電気光学パネルの駆動回路であって、

電源回路から複数の電位の電源が夫々供給される複数の電源線と、

前記複数の画素部に画像信号を供給すべきタイミングを規定する転送信号を出力するシフトレジスタと、

前記複数の電源線のうち少なくとも相異なる電位が供給される一の電源線及び他の電源線に接続されており該一の電源線及び該他の電源線を介して供給される前記相異なる電位の電源を用いて前記出力された転送信号の電圧を高めるレベルシフタと、

前記一の電源線及び前記他の電源線の間に設けられ、前記一の電源線及び前記他の電源線のうち一方に印加された静電気を他方に逃がす電気経路を提供するダイオードを有する静電保護回路と

を備えたことを特徴とする電気光学パネルの駆動回路。

**【請求項 2】**

当該駆動回路は、前記電圧を高められた転送信号に応じて前記画像信号を前記電気光学パネルに配線された信号線を介して前記画素部に供給することによって、前記電気光学パネルを駆動するデータ線駆動回路を含むことを特徴とする請求項 1 に記載の電気光学パネルの駆動回路。

**【請求項 3】**

前記電気光学パネルは、電流駆動型の電気光学パネルであり、

前記データ線駆動回路は、前記電圧を高められた転送信号に応じて前記画像信号をサンプリング又はラッチして前記信号線に供給することを特徴とする請求項 2 に記載の電気光学パネルの駆動回路。

**【請求項 4】**

当該駆動回路は、前記電圧を高められた転送信号を走査信号として前記電気光学パネルに配線された複数の走査線を介して前記画素部に供給することによって、前記電気光学パネルを駆動する走査線駆動回路を含むことを特徴とする請求項 1 に記載の電気光学パネルの駆動回路。

**【請求項 5】**

前記電気光学パネルは、有機 E L パネルであることを特徴とする請求項 1 から 4 の何れか一項に記載の電気光学パネルの駆動回路。

**【請求項 6】**

前記ダイオードは、前記一の電源線及び前記他の電源線の間に並列に複数接続されていること

を特徴とする請求項 1 から 5 の何れか一項に記載の電気光学パネルの駆動回路。

**【請求項 7】**

前記静電保護回路は、前記レベルシフタの各段毎に、個別に設けられていることを特徴とする請求項 1 から 6 の何れか一項に記載の電気光学パネルの駆動回路。

**【請求項 8】**

前記静電保護回路は、前記レベルシフタの複数段毎に、個別に設けられていることを特徴とする請求項 1 から 6 の何れか一項に記載の電気光学パネルの駆動回路。

**【請求項 9】**

前記レベルシフタの出力側に接続されており、前記一の電源線及び前記他の電源線に接続されており前記相異なる電位の電源を用いて前記電圧を高められた転送信号をバッファリングするバッファを更に備えたことを特徴とする請求項 1 から 8 の何れか一項に記載の電気光学パネルの駆動回路。

**【請求項 10】**

前記一の電源線及び前記他の電源線は、前記複数の電源線のうち最高電位の電源を供給する最高電源線及び最低電位の電源を供給する最低電源線のうち少なくとも一方を含み、

10

20

30

40

50

前記電気経路は、前記最高電源線へ通ずる経路及び前記最低電位線へ通ずる経路のうち少なくとも一方を含むことを特徴とする請求項1から9の何れか一項に記載の電気光学パネルの駆動回路。

【請求項11】

複数の単位回路からなる電子回路と、前記複数の単位回路に共通に電源を供給する電源線とを有する駆動回路において、

前記電源線から前記複数の単位回路の各々に接続するための電源入力線を有し、前記電源入力線に保護回路を形成したこと

を特徴とする駆動回路。

【請求項12】

当該駆動回路は、画像表示領域に複数の画素部が設けられた電気光学パネルを駆動するための電気光学パネルの駆動回路であり、前記電源線は、少なくとも相異なる電位を供給する一の電源線及び他の電源線を含み、前記単位回路は、前記複数の画素部に画像信号を供給すべきタイミングを規定する転送信号を出力するシフトレジスタ、及び前記相異なる電位を用いて前記出力された転送信号の電圧を高めるレベルシフタを含むこと

を特徴とする請求項11に記載の駆動回路。

【請求項13】

当該駆動回路は、前記電圧を高められた転送信号に応じて前記画像信号を前記電気光学パネルに配線された信号線を介して前記画素部に供給することによって、前記電気光学パネルを駆動するデータ線駆動回路を含むこと

を特徴とする請求項12に記載の駆動回路。

【請求項14】

前記電気光学パネルは、電流駆動型の電気光学パネルであり、

前記データ線駆動回路は、前記電圧を高められた転送信号に応じて前記画像信号をサンプリング又はラッチして前記信号線に供給すること

を特徴とする請求項13に記載の駆動回路。

【請求項15】

当該駆動回路は、前記電圧を高められた転送信号を走査信号として前記電気光学パネルに配線された複数の走査線を介して前記画素部に供給することによって、前記電気光学パネルを駆動する走査線駆動回路を含むこと

を特徴とする請求項12から14の何れか一項に記載の駆動回路。

【請求項16】

前記電気光学パネルは、有機ELパネルであること

を特徴とする請求項11から15の何れか一項に記載の電気光学パネルの駆動回路。

【請求項17】

前記保護回路は、ダイオードであること

を特徴とする請求項11から16の何れか一項に記載の駆動回路。

【請求項18】

前記保護回路は、前記レベルシフタの各段毎に、個別に設けられていること

を特徴とする請求項11から17の何れか一項に記載の駆動回路。

【請求項19】

前記保護回路は、前記レベルシフタの複数段毎に、個別に設けられていること

を特徴とする請求項11から18の何れか一項に記載の駆動回路。

【請求項20】

前記レベルシフタの出力側に接続されており、且つ前記一の電源線及び前記他の電源線に接続されており前記相異なる電位の電源を用いて前記電圧を高められた転送信号をバッファリングするバッファを更に備えたこと

を特徴とする請求項11から19の何れか一項に記載の駆動回路。

【請求項21】

前記一の電源線及び前記他の電源線は、前記複数の電源線のうち最高電位の電源を供給

10

20

30

40

50

する最高電源線及び最低電位の電源を供給する最低電源線のうち少なくとも一方を含み、

前記保護回路によって提供される電気経路は、前記最高電源線へ通ずる経路及び前記最低電位線へ通ずる経路のうち少なくとも一方を含むこと

を特徴とする請求項 11 から 20 の何れか一項に記載の駆動回路。

#### 【請求項 22】

画像表示領域に複数の画素部が設けられた電気光学パネルを駆動するための電気光学パネルの駆動方法であって、

電源回路から複数の電位の電源を複数の電源線に夫々供給する工程と、

シフトレジスタによって前記複数の画素部に画像信号を供給すべきタイミングを規定する転送信号を出力する工程と、

前記複数の電源線のうち少なくとも相異なる電位が供給される一の電源線及び他の電源線に接続されたレベルシフタによって、該一の電源線及び該他の電源線を介して供給される前記相異なる電位の電源を用いて前記出力された転送信号の電圧を高める工程と、

前記一の電源線及び前記他の電源線の間に設けられたダイオードによって、前記一の電源線及び前記他の電源線のうち一方に印加された静電気を他方に逃がす電気経路を提供する工程と

を備えたことを特徴とする電気光学パネルの駆動方法。

#### 【請求項 23】

請求項 1 から 10 の何れか一項に記載の電気光学パネルの駆動回路及び前記電気光学パネルを備えたこと

を特徴とする電気光学装置。

#### 【請求項 24】

請求項 23 記載の電気光学装置を具備してなること

を特徴とする電子機器。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、例えば、有機ELパネルのような電気光学パネルの駆動回路及びその駆動方法、並びに該電気光学パネルの駆動回路を備えてなる電気光学装置、及びこれを備えた電子機器の技術分野に関する。

##### 【背景技術】

##### 【0002】

例えば、有機ELパネルの如き電気光学パネルを駆動する駆動回路は、外部からの電源供給を受けて走査線やデータ線を駆動する内蔵回路として電気光学パネルの基板に作り込まれたり、或いは外付けIC回路として該基板に後付けされたりする。このような駆動回路の劣化又は破壊の要因としては、特に電気光学装置の組み立て時又は運搬時に問題となる静電気放電のストレスによる破壊、即ち静電破壊が挙げられる。組み立て時等に駆動回路或いは電気光学装置の周辺で静電気が発生し、これが駆動回路に接続された配線に印加されると、駆動回路が劣化又は破壊されかねない。

##### 【0003】

そこで、このような静電気による駆動回路の劣化又は破壊を防止するために、保護回路が、駆動回路の信号入出力に關係する信号経路に設けられる（例えば、特許文献 1 及び 2 参照）。より具体的には、保護回路は、例えば駆動回路外部からクロック信号、反転クロック信号、スタートパルス等の各種信号が入力される入力端子に対して入力保護回路として設けられる。或いは、走査信号、エンドパルス等の駆動回路外部への各種信号が出力される出力端子に対して出力保護回路として設けられる。

##### 【0004】

また、絶縁ゲート型トランジスタ回路装置の内部において、フローティング状態の回路部分に蓄積された静電気を効果的に放電することによって、静電気による素子の破壊を防止する技術も提案されている（例えば、特許文献 3。）。

10

20

30

40

50

## 【0005】

【特許文献1】特開平10-294383号公報

【特許文献2】特開2003-308050号公報

【特許文献3】特開2000-98338号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0006】

しかしながら、有機ELパネルを駆動するドライバ回路において、外部からドライバ回路に侵入する静電気の対策としてドライバ回路の外部に保護ダイオードを設けた場合には、ドライバ回路の内部で生じた静電気をドライバ回路の外部に逃がすことが困難である。例えば、ドライバ回路が備えるレベルシフタ、シフトレジスタ、或いはバッファ等を駆動するための電源を供給するための電源線を形成する工程において、該電源線をパターニングした際のレジストを剥離する際に該電源線に静電気が発生することがある。このような静電気は、ドライバ回路が備えるレベルシフタと該レベルシフタに接続されたバッファを静電破壊することができ、有機ELパネルの製造プロセスにおける歩留まりの低下を招く原因になる。

## 【0007】

よって、本発明は上記問題点に鑑みてなされたものであり、例えば、有機ELパネルの如き電気光学パネルを駆動するための駆動回路が静電破壊されることを低減することができる電気光学パネルの駆動回路、その駆動方法、及び駆動回路、並びに電気光学装置及びこれを備えた電子機器を提供することを課題とする。

## 【課題を解決するための手段】

## 【0008】

本発明に係る電気光学パネルの駆動回路は上記課題を解決するために、画像表示領域に複数の画素部が設けられた電気光学パネルを駆動するための電気光学パネルの駆動回路であって、電源回路から複数の電位の電源が夫々供給される複数の電源線と、前記複数の画素部に画像信号を供給すべきタイミングを規定する転送信号を出力するシフトレジスタと、前記複数の電源線のうち少なくとも相異なる電位が供給される一の電源線及び他の電源線に接続されており該一の電源線及び該他の電源線を介して供給される前記相異なる電位の電源を用いて前記出力された転送信号の電圧を高めるレベルシフタと、前記一の電源線及び前記他の電源線の間に設けられ、前記一の電源線及び前記他の電源線のうち一方に印加された静電気を他方に逃がす電気経路を提供するダイオードを有する静電保護回路とを備える。

## 【0009】

本発明に係る電気光学パネルの駆動回路によれば、その動作時には、電気光学パネルを駆動するための各種信号をシフトレジスタから所定のタイミングで転送し、レベルシフタは該シフトレジスタから転送された各種信号の電圧レベルをレベルシフトして転送信号として出力する。駆動回路は、転送信号に応じて、例えば画像信号をデータ線を介して電気光学パネルに供給し、電気光学パネルを駆動する。この際、駆動回路は、レベルシフタに相異なる電位を供給する一の電源線と他の電源線とを備えており、これら2本の電源線によって供給される電源によってレベルシフタは駆動される。

## 【0010】

本発明では特に、一の電源線と他の電源線との間には、ダイオードを有する静電保護回路が設けられており、該静電保護回路は、前記一の電源線及び前記他の電源線のうち一方に印加された静電気を他方に逃がす電気経路を提供する。したがって、電気光学パネルに駆動回路が内蔵されてなる或いは外付けされてなる電気光学装置の製造時等において、レベルシフタに接続された一及び他の電源線間に、静電気による比較的高い電圧が生じても、電気経路を介して静電気等を逃がすことによって、レベルシフタが静電破壊されることを抑制することが可能となる。例えば、電気光学パネルの組み立て時や運搬時等、或いは動作時に駆動回路内部で発生する静電気によってレベルシフタが静電破壊されることを低

10

20

30

40

50

減することができる。

【0011】

更に、レベルシフタが静電破壊されることを抑制することができるため、レベルシフタに電気的に接続されたシフトレジスタ等が静電破壊されることも抑制することができ、駆動回路全体を静電気から保護することも可能である。

【0012】

本発明に係る電気光学パネルの駆動回路の一態様では、当該駆動回路は、前記電圧を高められた転送信号に応じて前記画像信号を前記電気光学パネルに配線された信号線を介して前記画素部に供給することによって、前記電気光学パネルを駆動するデータ線駆動回路を含む。

10

【0013】

この態様によれば、特に、駆動周波数が走査線駆動回路に比べて高いことからレベルシフタが好適に用いられるデータ線駆動回路に係る該レベルシフタやシフトレジスタを、静電気等から保護することが可能となる。

【0014】

本発明に係る電気光学パネルの駆動回路の他の態様では、前記電気光学パネルは、電流駆動型の電気光学パネルであり、前記データ線駆動回路は、前記電圧を高められた転送信号に応じて前記画像信号をサンプリング又はラッチして前記信号線に供給する。

20

【0015】

この態様においては、電流駆動型の電気光学パネルを駆動するためには、相対的に大きい電流の画像信号を供給することが重要であり、該画像信号をサンプリング又はラッチするためには、相対的に大きいサイズの TFT 等の大型スイッチが用いられる。そして、該大型スイッチを制御するために、転送信号の電圧も、レベルシフタによって増幅されることになる。このように電圧が高められた転送信号に応じて、画像信号上の画像信号が、前述の大型スイッチによりサンプリング又はラッチされて信号線に供給される。したがって、この態様によれば、画像信号をサンプリング又はラッチするための転送信号の電圧を増幅することによって、十分な電流の画像信号を供給することで、電流駆動型の電気光学パネルを良好に駆動することが可能となる。

【0016】

或いは本発明に係る電気光学パネルの駆動回路の他の態様では、当該駆動回路は、前記電圧を高められた転送信号を走査信号として前記電気光学パネルに配線された複数の走査線を介して前記画素部に供給することによって、前記電気光学パネルを駆動する走査線駆動回路を含む。

30

【0017】

この態様によれば、転送信号を走査信号として出力する走査線駆動回路に係るレベルシフタ及びシフトレジスタを、静電気等から保護することが可能となる。

【0018】

本発明に係る電気光学パネルの駆動回路の他の態様では、前記電気光学パネルは、有機ELパネルであってもよい。

40

【0019】

この態様によれば、有機ELパネルを発光させるための駆動電流を十分に供給することができる。すなわち、転送信号の電圧がシフトレジスタによってレベルシフトされていることから、該転送信号に応じて有機ELパネルに供給されるが画像信号の電圧もレベルシフトされており、該画像信号に応じた高い電流を有機ELパネルが備える画素に含まれる有機EL素子に流すことが可能である。したがって、有機EL素子の発光量を十分に確保することができ、該有機ELパネルの画質を高めることができある。

【0020】

本発明に係る電気光学パネルの駆動回路の他の態様では、前記ダイオードは、前記一の電源線及び前記他の電源線の間に並列に複数接続されていてもよい。

【0021】

50

この態様によれば、前記一の電源線及び前記他の電源線の間に並列に複数接続された複数のダイオードの中に不具合が生じた場合でも、不具合が生じたダイオードを除く他のダイオードによって電流経路を提供することができる。したがって、これら電源線に生じた静電気を該電流経路を介して確実に放出することができ、静電気によって駆動回路が静電破壊されることを抑制することが可能である。

#### 【0022】

本発明に係る電気光学パネルの駆動回路の他の態様では、前記静電保護回路は、前記レベルシフタの各段毎に、個別に設けられていてもよい。

#### 【0023】

この態様によれば、レベルシフタ近傍の電源線で発生した静電気を該レベルシフタ近傍に配置されたダイオードによって放出することができ、レベルシフタの各段を確実に静電気から保護することができる。

#### 【0024】

本発明に係る電気光学パネルの駆動回路の他の態様では、前記静電保護回路は、前記レベルシフタの複数段毎に、個別に設けられていてもよい。

#### 【0025】

この態様によれば、レベルシフタの複数段毎に個別にダイオードを設けておくことにより、レベルシフタの各段毎にダイオードを設ける場合に比べてダイオードの個数を低減することができる。ダイオードの個数を低減した場合でも、一の電源線及び他の電源線はレベルシフタの複数段毎に設けられたダイオードによって電流経路が構成されており、該電流経路を介してこれら電源線に生じた静電気を放出することができる。また、ダイオードの個数を減らすことにより、電気光学パネルの耐久性を高めながら、該電気光学パネルの製造に要するコストを低減することも可能である。

#### 【0026】

本発明に係る電気光学パネルの駆動回路の他の態様では、前記レベルシフタの出力側に接続されており、前記一の電源線及び前記他の電源線に接続されており前記相異なる電位の電源を用いて前記電圧を高められた転送信号をバッファリングするバッファを更に備える。

#### 【0027】

この態様によれば、バッファにより転送信号の波形或いは出力タイミングを整えることができ、該転送信号をより確実に供給することができる。

#### 【0028】

本発明に係る電気光学パネルの駆動回路の他の態様では、前記一の電源線及び前記他の電源線は、前記複数の電源線のうち最高電位の電源を供給する最高電源線及び最低電位の電源を供給する最低電源線のうち少なくとも一方を含み、前記電気経路は、前記最高電源線へ通ずる経路及び前記最低電位線へ通ずる経路のうち少なくとも一方を含む。

#### 【0029】

この態様によれば、静電保護回路は、対応する電源線上における電位を、電源回路から供給される電源のうち、最高電位の電源と同等の電位以下又は最低電位の電源と同等の電位以上として維持する。よって、この態様によれば、当該駆動回路の動作時において、複数の電源線上における電位を、最高電位の電源と同等の電位以下であって最低電位の電源と同等の電位以上に維持することが可能となる。

#### 【0030】

本発明に係る駆動回路は上記課題を解決するために、複数の単位回路からなる電子回路と、前記複数の単位回路に共通に電源を供給する電源線とを有する駆動回路において、前記電源線から前記複数の単位回路の各々に接続するための電源入力線を有し、前記電源入力線に保護回路を形成している。

#### 【0031】

本発明に係る駆動回路によれば、同様に、例えば、電気光学パネルの組み立て時や運搬時等、或いは動作時に駆動回路内部で発生する静電気によって複数の単位回路が静電破壊

10

20

30

40

50

されることを低減することができる。

【0032】

本発明に係る駆動回路の一の態様においては、当該駆動回路は、画像表示領域に複数の画素部が設けられた電気光学パネルを駆動するための電気光学パネルの駆動回路であり、前記電源線は、少なくとも相異なる電位を供給する一の電源線及び他の電源線を含み、前記単位回路は、前記複数の画素部に画像信号を供給すべきタイミングを規定する転送信号を出力するシフトレジスタ、及び前記相異なる電位を用いて前記出力された転送信号の電圧を高めるレベルシフタを含む。

【0033】

この態様によれば、レベルシフタが静電破壊されることを抑制することができるため、レベルシフタに電気的に接続されたシフトレジスタ等が静電破壊されることも抑制することができ、駆動回路全体を静電気から保護することも可能である。

【0034】

この態様においては、当該駆動回路は、前記電圧を高められた転送信号に応じて前記画像信号を前記電気光学パネルに配線された信号線を介して前記画素部に供給することによって、前記電気光学パネルを駆動するデータ線駆動回路を含む。

【0035】

この態様によれば、特に、駆動周波数が走査線駆動回路に比べて高いことからレベルシフタが好適に用いられるデータ線駆動回路に係る該レベルシフタやシフトレジスタを、静電気等から保護することが可能となる。

【0036】

この態様においては、前記電気光学パネルは、電流駆動型の電気光学パネルであり、前記データ線駆動回路は、前記電圧を高められた転送信号に応じて前記画像信号をサンプリング又はラッチして前記信号線に供給する。

【0037】

この態様によれば、同様に、画像信号をサンプリング又はラッチするための転送信号の電圧を増幅することによって、十分な電流の画像信号を供給することで、電流駆動型の電気光学パネルを良好に駆動することが可能となる。

【0038】

このような態様においては、当該駆動回路は、前記電圧を高められた転送信号を走査信号として前記電気光学パネルに配線された複数の走査線を介して前記画素部に供給することによって、前記電気光学パネルを駆動する走査線駆動回路を含む。

【0039】

この態様によれば、転送信号を走査信号として出力する走査線駆動回路に係るレベルシフタ及びシフトレジスタを、静電気等から保護することが可能となる。

【0040】

本発明に係る駆動回路の一の態様においては、前記電気光学パネルは、有機ELパネルであってもよい。

【0041】

この態様によれば、同様に、有機EL素子の発光量を十分に確保することができ、該有機ELパネルの画質を高めることが可能である。

【0042】

本発明に係る駆動回路の他の態様においては、前記保護回路は、ダイオードである。

【0043】

この態様によれば、電源線に生じた静電気を該電流経路を介して確実に放出することができ、静電気によって駆動回路が静電破壊されることを抑制することができる。

【0044】

本発明に係る駆動回路の他の態様においては、前記保護回路は、前記レベルシフタの各段毎に、個別に設けられている。

【0045】

10

20

30

40

50

この態様によれば、レベルシフタ近傍の電源線で発生した静電気を該レベルシフタ近傍に配置されたダイオードによって放出することができ、レベルシフタの各段を確実に静電気から保護することができる。

【0046】

本発明に係る駆動回路の他の態様においては、前記保護回路は、前記レベルシフタの複数段毎に、個別に設けられている。

【0047】

この態様によれば、ダイオードの個数を低減した場合でも、一の電源線及び他の電源線はシフトレジスタの複数段毎に設けられたダイオードによって電流経路が構成されており、該電流経路を介してこれら電源線に生じた静電気を放出することが可能である。

10

【0048】

本発明に係る駆動回路の他の態様においては、前記レベルシフタの出力側に接続されており、且つ前記一の電源線及び前記他の電源線に接続されており前記相異なる電位の電源を用いて前記電圧を高められた転送信号をバッファリングするバッファを更に備える。

【0049】

この態様によれば、バッファにより転送信号の波形或いは出力タイミングを整えることができ、該転送信号をより確実に供給することができる。

【0050】

本発明に係る駆動回路の他の態様においては、前記一の電源線及び前記他の電源線は、前記複数の電源線のうち最高電位の電源を供給する最高電源線及び最低電位の電源を供給する最低電源線のうち少なくとも一方を含み、前記保護回路によって提供される電気経路は、前記最高電源線へ通ずる経路及び前記最低電位線へ通ずる経路のうち少なくとも一方を含む。

20

【0051】

この態様によれば、当該駆動回路の動作時において、複数の電源線上における電位を、最高電位の電源と同等の電位以下であって最低電位の電源と同等の電位以上に維持することが可能となる。

【0052】

本発明に係る電気光学パネルの駆動方法は上記課題を解決するために、画像表示領域に複数の画素部が設けられた電気光学パネルを駆動するための電気光学パネルの駆動方法であって、電源回路から複数の電位の電源を複数の電源線に夫々供給する工程と、シフトレジスタによって前記複数の画素部に画像信号を供給すべきタイミングを規定する転送信号を出力する工程と、前記複数の電源線のうち少なくとも相異なる電位が供給される一の電源線及び他の電源線に接続されたレベルシフタによって、該一の電源線及び該他の電源線を介して供給される前記相異なる電位の電源を用いて前記出力された転送信号の電圧を高める工程と、前記一の電源線及び前記他の電源線の間に設けられたダイオードによって、前記一の電源線及び前記他の電源線のうち一方に印加された静電気を他方に逃がす電気経路を提供する工程とを備える。

30

【0053】

本発明に係る電気光学パネルの駆動方法によれば、前述した本発明に係る電気光学パネルの駆動回路の場合と同様に、電気経路を介して静電気等を逃がすことによって、レベルシフタが静電破壊されることを効果的に抑制することが可能となる。

40

【0054】

本発明に係る電気光学装置は上記課題を解決するために、上述した電気光学パネルの駆動回路及び前記電気光学パネルを備える。

【0055】

本発明に係る電気光学装置によれば、電源線で発生した静電気によって駆動回路が静電破壊されることを抑制することができ、該電気光学装置の耐久性を高めることができ。さらに、電気光学装置を製造プロセスにおける歩留まりを向上させることができ、電気光学装置のコストが低減されることになる。

50

## 【0056】

本発明に係る電子機器は上記課題を解決するために、上述した電気光学装置を具備してなる。

## 【0057】

本発明に係る電子機器によれば、上述した本発明の電気光学装置を具備してなるので、歩留まりが高く且つ故障し難く、高品位の表示が可能な、投射型表示装置、液晶テレビ、携帯電話、電子手帳、ワードプロセッサ、ビューファインダ型又はモニタ直視型のビデオテープレコーダ、ワークステーション、テレビ電話、POS端末、タッチパネルなどの各種電子機器を実現できる。また、本発明の電子機器として、例えば電子ペーパなどの電気泳動装置の他に、液晶装置、有機EL表示装置、電子放出素子を利用した表示装置(Field Emission Display及びSurface-Conduction Electron-Emitter Display)等も実現することが可能である。

10

## 【0058】

本発明のこのような作用及び他の利得は次に説明する実施の形態から明らかにされる。

## 【発明を実施するための最良の形態】

## 【0059】

以下、本発明の実施形態を図面を参照しながら詳細に説明する。なお、以下の実施形態は、本発明に係る電気光学パネルの駆動回路を TFT アクティブマトリクス駆動形式の有機EL表示装置に適用したものである。

20

## 【0060】

## [第1実施形態]

## (有機EL表示装置の構成)

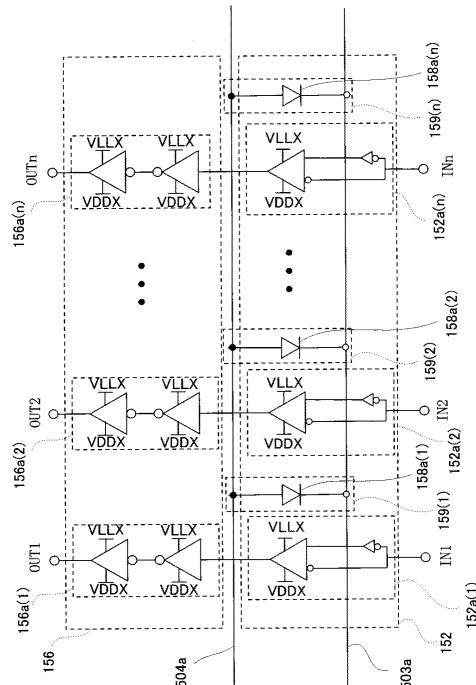

先ず、本実施形態に係る有機EL表示装置の全体構成及び各画素部の構成について、図1及び図2を参照して説明する。図1は、本実施形態に係る有機EL表示装置の全体構成を示すブロック図であり、図2は各画素部の構成を示すブロック図である。

30

## 【0061】

図1において、本発明に係る「電気光学装置」の一例である有機EL表示装置1は、主要部として、本発明に係る「電気光学パネル」の一例である有機ELパネル100、本発明に係る「電気光学パネルの駆動回路」の一例である駆動回路120、画像信号処理回路300、タイミングジェネレータ400、及び電源回路500を備える。

30

## 【0062】

有機ELパネル100は、画素スイッチング用のスイッチング素子として素子基板上の画像表示領域110に形成されたスイッチング用トランジスタ76、駆動用トランジスタ74、及び該素子基板上に形成される有機EL素子72を備える。有機EL素子72は、例えば、陰極、電子輸送層、発光層、正孔輸送層、透明電極及びガラス板が重ねて配置されて構成されており、有機EL素子で発生した光の出射側に配置される対向基板をガラス板としてもよい。有機ELパネル100が備える各画素部70は電流供給線117と接続されており、後述するように、駆動用トランジスタ74がオン状態になった時に該電流供給線117から有機EL素子72を駆動するための駆動電流が供給される。

40

## 【0063】

タイミングジェネレータ400は、有機ELパネル100の各部で使用される各種タイミング信号を出力する。タイミングジェネレータ400の一部であるタイミング信号出力手段により、最小単位のクロックであり各画素を走査するためのドットクロックが作成され、このドットクロックに基づいて、Yクロック信号YCK、反転Yクロック信号YCKB、Xクロック信号XCK、反転Xクロック信号XCKB、Y転送開始パルスDY及びX転送開始パルスDXが生成される。

40

## 【0064】

画像信号処理回路300は、外部から入力画像データが入力されると、この入力画像データに基づいて画像信号を生成する。画像信号はデータ線駆動回路150に含まれるラッチ回路等でラッチ又はサンプリングされ、画像信号供給線L1を介して有機ELパネル1

50

00に供給される。尚、本実施形態においては、説明を簡略化するため、画像信号供給線は一本設けられているが、本発明はこれに限定されるものではなく、RGB各色の光を発光する有機EL素子を各画素に形成すると共に、画像信号をRGB各色に対応するR信号、G信号、及びB信号を供給するための信号供給線を設けておいてもよい。この場合には、画像信号供給線を3本設け、3本の画像信号供給線から各色の画素に画像信号を供給すればよい。また、RGB各色を発光する有機EL素子に駆動電流を供給する電流供給線を、各色に発光する有機EL素子毎に設けてよい。

【0065】

電源回路500は、複数の電位の電源を生成して有機ELパネル100に供給する。

【0066】

本実施形態では、特に、有機ELパネル100は、駆動回路内蔵型であり、その素子基板上に、本発明に係る「駆動回路」の一例として、走査線駆動回路130及びデータ線駆動回路150を含む駆動回路120が構築されている。駆動回路120は、好ましくは、画像表示領域110に作り込まれる各画素に係るスイッチング用トランジスタ76及び駆動用トランジスタ74の如き各種素子と共に、素子基板の周辺領域に作り込まれる。但し、このような駆動回路は、少なくとも部分的に外付けICとして構成され、周辺領域に後付けされてもよい。

【0067】

有機ELパネル100は更に、その素子基板の中央を占める画像表示領域110に、縦横に配線されたデータ線114及び走査線112を備える。データ線114及び走査線112は、それらの交点に対応する各画素部70が備える有機EL素子72に駆動電流を流すための駆動用トランジスタ74及び該駆動用トランジスタ74の動作をオン・オフするスイッチング用トランジスタ76に電気的に接続されている。尚、本実施形態では特に、走査線112の総本数をm本（但し、mは2以上の自然数）とし、データ線114の総本数をn本（但し、nは2以上の自然数）として説明する。

【0068】

データ線駆動回路150は、画像信号供給線L1から供給される画像信号を各データ線114に順次供給する。

【0069】

走査線駆動回路130は、走査線112を介して走査信号をマトリクス状に配列された画素部70の行毎に供給する。

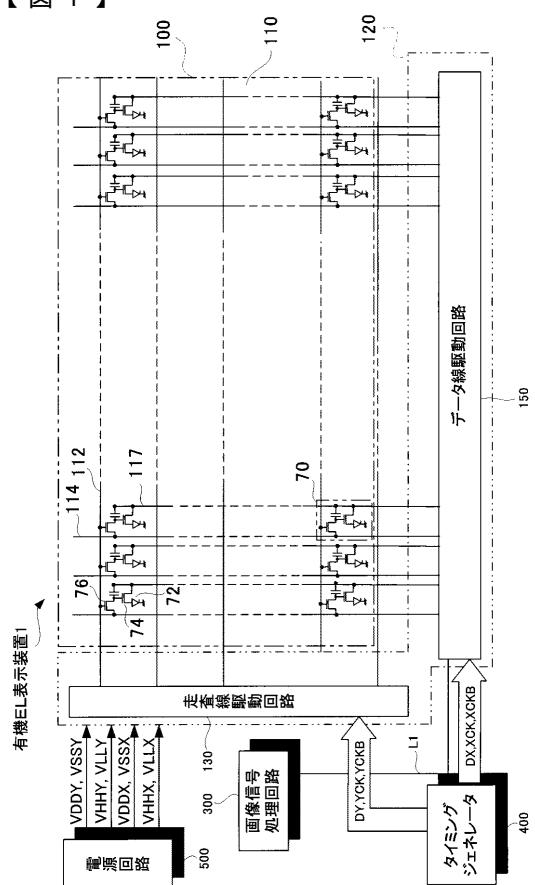

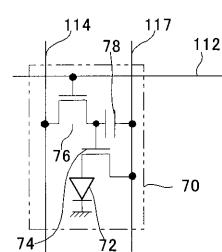

【0070】

図2において、画素部70は、表示素子である有機EL素子72と、該有機EL素子72に駆動電流を供給するための駆動用トランジスタ74と、該駆動用トランジスタ74の動作をオン・オフするためのスイッチング用トランジスタ76とを備える。

【0071】

スイッチング用トランジスタ76のソース電極には、データ線駆動回路150より画像信号が供給されるデータ線114が電気的に接続されている一方、スイッチング用トランジスタ76のゲート電極には、後述する走査信号を供給する走査線112が電気的に接続される。スイッチング用トランジスタ76のドレイン電極には、保持容量78が接続されている。各画素部70は、走査線112とデータ線114との各交点に対応して、マトリクス状に配列されている。

【0072】

走査線112は、スイッチング用トランジスタ76のゲート電極に電気的に接続され、データ線114は、スイッチング用トランジスタのソース電極に電気的に接続されている。電流供給線117は、駆動用トランジスタ74のソース電極及び保持容量78に接続されている。

【0073】

保持容量78は、駆動用トランジスタ76のゲート電極に電気的にされており、データ線114を介して画素部70に供給されるデータ信号に応じた電圧を駆動用トランジスタ

10

20

30

40

50

74のゲート電極に印加する。

【0074】

駆動用トランジスタ74のソース電極には、電流供給線117が電気的に接続されている。駆動用トランジスタ74のゲート電極に印加された電圧によって駆動用トランジスタ74の動作がオン・オフされる結果、該駆動用トランジスタ74は、駆動電流を電流供給線117から有機EL素子72に供給する。

【0075】

尚、図1及び図2に例示した画素回路の構成の他にも、例えば4個など複数のTFT、複数の容量等を含んでなる、電流プログラム方式の画素回路、電圧プログラム型の画素回路、電圧比較方式の画素回路、サブフレーム方式の画素回路等の各種方式の画素回路を採用することが可能となる。

【0076】

(データ線駆動回路の構成)

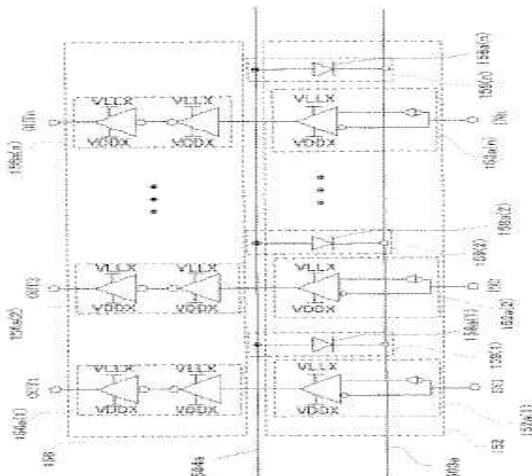

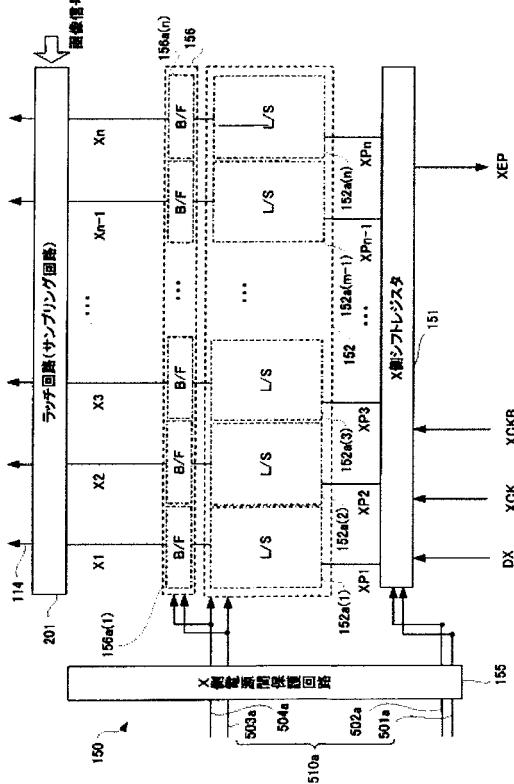

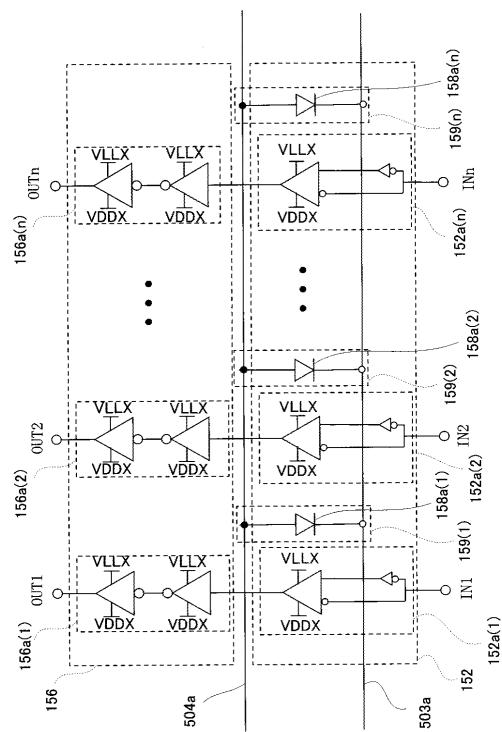

次に、図3及び図4を参照して、駆動回路120におけるデータ線駆動回路150の詳細な構成について説明する。図3は、データ線駆動回路150の構成を示すブロック図であり、図4はX側レベルシフタ152の構成の一例を示すブロック図である。

【0077】

図3及び図4において、データ線駆動回路150の主要部は、X側シフトレジスタ151と、X側レベルシフタ152と、X側バッファ156と、ラッチ又はサンプリング回路201とを主たる構成要素とする。

【0078】

X側シフトレジスタ151には、タイミングジェネレータ400からXクロック信号XCK、反転Xクロック信号XCKB、及びX転送開始パルスDXが入力される。X側シフトレジスタ151は、X転送開始パルスDXが入力されると、Xクロック信号XCK及び反転Xクロック信号XCKBに同期して、X側転送パルスXP1、XP2、XP3、…、XPn-1、XPnを順次生成し、X側レベルシフタ152に送り出す。X側シフトレジスタ151は、n本のデータ線114に対応してn段より構成されており、第1段目から第n段目に向かう方向で、各段よりX側転送パルスXP1、XP2、XP3、…、XPn-1、XPnが順次出力される。そして、X側シフトレジスタ151の最終段より、X側転送パルスXPnが当該X側シフトレジスタ151のX側エンドパルスXEPとしても出力される。

【0079】

X側レベルシフタ152は、X側シフトレジスタ151から受け取ったX側転送パルスXP1、XP2、XP3、…、XPn-1、XPnの電圧を夫タレベルシフトし、X側駆動信号X1、X2、X3、…、Xn-1、Xnとして夫々出力する。

【0080】

ラッチ回路又はサンプリング回路201は、画像信号処理回路から供給される画像信号を、X側レベルシフタ152からX側駆動信号X1、X2、X3、…、Xn-1、Xnが夫々出力されるタイミングで、ラッ칭又はサンプリングする。このようにラッ칭又はサンプリングされた画像信号は、データ線駆動回路150から順次データ線114に供給される。

【0081】

尚、後述する図4において説明するように、X側レベルシフタ152の各段を、該各段に入力されるX側転送パルスXP1、XP2、XP3、…、XPn-1、XPnの電圧をレベルシフトするための電圧增幅回路152a(j)(但し、j=1、2、…、n)として示す。

【0082】

X側バッファ156は、X側レベルシフタ152から出力されたX側駆動信号X1、X2、X3、…、Xn-1、Xnの波形等を整えて、ラッチ回路又はサンプリング回路201に供給する。X側バッファ156の各段を、電圧增幅回路152a(j)に接続さ

10

20

30

40

50

れるバッファ回路 156a(j) (但し、j = 1, 2, ..., n) として示す。

【0083】

データ線駆動回路 150 を駆動するための電源は、図 1 に示す電源回路 500 から供給される 4 つの電源 (第 1 X 側電源 VHHX、第 2 X 側電源 VDDX、第 3 X 側電源 VSSX、及び第 4 X 側電源 VLLX) である。電源回路 500 から供給される 4 つの電源は、第 1 X 側電源線 501a、第 2 X 側電源線 502a、第 3 X 側電源線 503a、及び第 4 X 側電源線 504a を含む X 側電源線群 510a を介してデータ線駆動回路 150 に供給される。なお、4 つの電源を電位が高い順に示すと、第 1 X 側電源 VHHX、第 2 X 側電源 VDDX、第 3 X 側電源 VSSX、第 4 X 側電源 VLLX の順になり、これら 4 つの電源が上述した 4 本の電源線のうちどの電源線を介して夫々供給されるかについては、駆動回路の設計等に基づく各種態様に応じて異なる。

【0084】

X 側シフトレジスタ 151 は、第 1 X 側電源線 501a 及び第 2 X 側電源線 502a に電気的に接続されている。よって、X 側転送パルス X P1、X P2、X P3、..., X Pn-1、X Pn は、第 1 X 側電源線 501a 及び第 2 X 側電源線 502a の夫々から供給される電源の電位間の電圧を有する。本実施形態においては、例えば、第 1 X 側電源線 501a が第 2 X 側電源 VDDX を供給し、第 2 X 側電源線 502a が第 3 X 側電源 VSSX を供給する。すなわち、X 側転送パルス X P1、X P2、X P3、..., X Pn-1、X Pn の電圧は、第 2 X 側電源 VDDX の電位及び第 3 X 側電源 VSSX の電位間の電圧になる。

【0085】

後述するように、第 1 X 側電源線 501a 及び第 2 X 側電源線 502a が供給する電源は、4 つの電源のうち相異なる電位の電源であればよい。例えば、第 1 X 側電源線 501a が第 1 X 側電源 VHHX を供給し、第 2 X 側電源線 502a が第 2 X 側電源 VDDX を供給する場合もある。但し、第 1 X 側電源線 501a 及び第 2 X 側電源線 502a が供給する電源は、X 側レベルシフタ 152 に含まれる電圧增幅回路 152a(j) (但し、j = 1, 2, ..., n) を駆動するための電源との組み合わせを検討した上で決定される。

【0086】

X 側レベルシフタ 152 は、電源回路 500 から供給される電源のうち第 3 X 側電源線 503a 及び第 4 X 側電源線 504a を介して供給される電源によって駆動される。よって、X 側転送パルス X P1、X P2、X P3、..., X Pn-1、X Pn の電圧は、第 3 X 側電源線 503a の電位と第 4 X 側電源線 504a の電位間の電圧へレベルシフトされ、X 側駆動信号 X1、X2、X3、..., Xn-1、Xn として出力される。本実施形態においては、例えば、第 3 X 側電源線 503a が第 2 X 側電源 VDDX を供給し、第 4 X 側電源線 504a が第 4 X 側電源 VLLX を供給する。すなわち、X 側転送パルス X P1、X P2、X P3、..., X Pn-1、X Pn は、第 2 X 側電源 VDDX の電位及び第 3 X 側電源 VSSX の電位間の電圧から、第 2 X 側電源 VDDX 及び第 4 X 側電源 VLLX の電位間の電圧へレベルシフトされた後、X 側駆動信号 X1、X2、X3、..., Xn-1、Xn として出力される。

【0087】

X 側レベルシフタ 152 を構成する電圧增幅回路 152a(j) 每にダイオード 158(j) (但し、j = 1, 2, ..., n) が設けられている。本実施形態においては、本発明に係る「一の電源線」の一例である第 3 X 側電源線 503a が第 2 X 側電源 VDDX を供給し、本発明に係る「他の電源線」の一例である第 4 X 側電源線 504a が第 4 X 側電源 VLLX を供給していることから、ダイオード 158(j) と電圧增幅回路 152a(j) は、X 側レベルシフタ 152 を駆動するための電源を供給する第 3 X 側電源線 503a と第 4 X 側電源線 504a との間で並列に接続されている。

【0088】

X 側バッファ 156 の各段を構成する X 側バッファ 156a(j) は、電圧增幅回路 1

10

20

30

40

50

52a(j)と同様に、第3X側電源線503a及び第4X側電源線504aを介して供給される電源によって駆動される。本実施形態においては、第3X側電源線503aが第2X側電源VDDXを供給し、第4X側電源線504aが第4X側電源VLLXを供給する。したがって、X側バッファ156a(j)も、電圧增幅回路152a(j)と同様に第2X側電源VDDX及び第4X側電源VLLXによって駆動される。

#### 【0089】

ダイオード158a(j)は、第3X側電源線503a及び第4X側電源線504aの間に設けられており、第3X側電源線503a及び第4X側電源線504aの一方の電源線で発生した静電気を他方に逃がす電流経路159(j)(但し、j=1、2、・・・、n)を構成する。電流経路159(j)は、第3X側電源線503a及び第4X側電源線504aのうち一方の電源線で発生した静電気によってX側レベルシフタ152に含まれる増幅回路152a(j)及びバッファ156a(j)が静電破壊されることを低減する。

#### 【0090】

本実施形態においては、複数のダイオード158a(j)が第3X側電源線503a及び第4X側電源線504aの間に並列に設けられていることにより、X側レベルシフタ152の各段を構成する電圧增幅回路152a(j)の近傍の電源線で静電気が発生した場合でも、複数のダイオード158a(j)によって形成される電流経路159(j)(但し、j=1、2、・・・、n)を介して該静電気を速やかに放出することができる。すなわち、電流経路159(j)が本発明に係る「静電保護回路」に相当する。

#### 【0091】

なお、ダイオード158a(j)は、X側レベルシフタ152の内部に設けられているのではなく、X側電源間保護回路155に含まれる。すなわち、図4は、ダイオード158a(j)及び電圧增幅回路152a(j)等の電気的な接続状態を示す図であり、ダイオード158a(j)は、X側レベルシフタ152の外部に設けられている。該第3X側電源線503a及び第4X側電源線504aの間に並列に接続された複数のダイオード156a(j)によれば、これらダイオード156a(j)のうち一つのダイオードに不具合があった場合でも、他のダイオードによって電流経路が確保され、X側レベルシフタ152が静電破壊されることを抑制することができる。なお、X側レベルシフタ152の静電破壊を抑制することが可能になることによって、X側レベルシフタ152に電気的に接続されているX側シフトレジスタ151が静電破壊されることを抑制することもでき、データ線駆動回路150全体を静電気から保護することが可能である。

#### 【0092】

本実施形態においては、ダイオード158a(j)は、電圧增幅回路152a(j)毎に一つずつ設けられているが、電流経路を構成するダイオードは、例えば、複数の電圧增幅回路152a(j)を一群とした電圧增幅回路群に一つ設けられていてもよく、一の電圧增幅回路群と並列に設けられたダイオードに不具合が生じた場合でも、他の電圧增幅回路群と並列に設けられたダイオードによって電源線に発生した静電気を逃がすことが可能である。また、電圧增幅回路152a(j)毎にダイオード158a(j)を設ける場合に比べて、ダイオードの個数を低減し、且つ電流経路を確保することができる。

#### 【0093】

有機EL表示装置1において、例えば、有機ELパネル100の組み立て時又は運搬時などの非動作時に又は電源供給が行われている動作時に、特に駆動回路120或いはこれに接続された各種配線に静電気が発生する場合がある。該駆動回路120のうちデータ線駆動回路150を構成するX側シフトレジスタ151、X側レベルシフタ152、或いはバッファ156に静電気が印加されると、X側シフトレジスタ151、X側レベルシフタ152、或いはバッファ156の一部又は全部が破壊される場合がある。また、X側シフトレジスタ151、X側レベルシフタ152、或いはバッファが破壊されない場合であっても、これら駆動回路の構成要素が劣化してしまう恐れがある。特に、X側電源線群510aに含まれる電源線は、該電源線を形成する際の製造プロセスにおいて静電気を発生さ

10

20

30

40

50

せることがある。本発明に係る「静電保護回路」の一例である電流経路 159(j)を含むX側電源間保護回路155を、X側電源線群510aに対して設けることにより、一の電源線で発生した静電気を他の電源線に逃がすことができ、駆動回路120が静電破壊されることを抑止することができる。

【0094】

データ線駆動回路150においては、当該データ線駆動回路150に外部から信号が入力される入力端子側、及び当該データ線駆動回路150より外部に信号が出力される出力端子側のうち少なくとも一方に対しても保護回路が設けられていてもよい。例えば、図3で示したように、データ線駆動回路150は、X側電源線群510aに対して設けられるX側電源間保護回路155の他に、データ線駆動回路150の入力端子側に対して設けられるX側入力保護回路と、出力端子側に対して設けられるX側出力保護回路とを備えていてもよい。より具体的には、図3において、X側入力保護回路は、例えばXクロック信号XCK、反転Xクロック信号XCKB、及びX転送開始パルスDXが入力される信号線に対して設けられていればよい。X側出力保護回路は、X側エンドパルスXEPが出力される信号線に対して設けられており、X側出力保護回路をX側駆動信号X1、X2、X3、・・・、Xn-1、Xnが出力される信号線に対して設けておいてもよい。

また、X側電源間保護回路155は、有機ELパネル100の駆動時にも、X側電源線群510aにおける4種の電位の高低関係が予め設定された関係に維持されるように、電流経路159(j)によって通電することができる。即ち、有機ELパネル100の駆動時にも、データ線駆動回路150は、X側電源間保護回路155による通電の影響を殆ど受けすことなく動作することができる。

本実施形態においては、主にデータ線駆動回路について説明したが、本発明に係る電気光学パネルの駆動回路の構成は、データ線駆動回路に限定されるものではなく、電気光学パネルに走査信号を供給する走査線駆動回路にも適用な構成である。したがって、走査線駆動回路にダイオードを設けることによって走査線駆動回路で発生した静電気を外部に放出することが可能であり、走査線駆動回路を静電気から保護することができる。

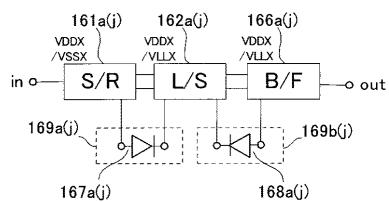

【0095】

[第2実施形態]

次に、本発明に係る有機ELパネルの駆動回路の他の実施形態について、図5を参照しながら説明する。なお、以下で説明する第2の実施の形態から第4の実施の形態に係る有機EL表示装置は、ダイオードが接続される位置を除いて第1の実施の形態で説明した有機EL表示装置と同様の構成であることから、共通部分については同一の符号を用いて説明する。さらに、第2の実施の形態から第4の実施の形態においては、X側シフトレジスタ、X側レベルシフタ、及びX側バッファを構成する各段のうち任意の段についてのみ説明する。

【0096】

本実施形態に係る有機EL表示装置の駆動回路に含まれる静電保護回路は、X側シフトレジスタを駆動する電源を供給する電源線の間に設けられたダイオード167a(j)と、X側レベルシフタを駆動する電源を供給する電源線の間に設けられたダイオード168a(j)によって、X側シフトレジスタ及びX側レベルシフタの両方に対して夫々静電気を逃がすための電流経路を提供した例である。図5は、図2に示したX側シフトレジスタ151、X側レベルシフタ152、及びX側バッファ156の各段のうちの一つを抜き出して示したブロック図である。

【0097】

図5において、データ線駆動回路150に含まれるX側シフトレジスタ151を構成する各段S/R161a(j)(但し、j=1、2、・・・、n)、X側レベルシフタ152に含まれる各段L/S162a(j)(但し、j=1、2、・・・、n)、及びX側バッファB/F166a(j)(但し、j=1、2、・・・、n)、該データ線駆動回路の入力側からS/R161a(j)、L/S162a(j)、B/F166a(j)の順に電気的に接続されている。

10

20

30

40

50

## 【0098】

S / R 1 6 1 a ( j ) は、第 1 X 側電源線 5 0 1 a から供給される第 2 X 側電源 V D D X と第 2 X 側電源線 5 0 2 a から供給される第 3 X 側電源 V S S X とにより駆動される。L / S 1 6 2 a ( j ) 及び B / F 1 6 6 a ( j ) は、第 3 X 側電源線 5 0 3 a から供給される第 2 X 側電源 V D D X と第 4 X 側電源線 5 0 4 a から供給される第 4 X 側電源 V L L X とにより駆動される。すなわち、本実施形態においては、第 3 X 側電源線 5 0 3 a が本発明に係る「一の電源線」に相当し、第 4 X 側電源線 5 0 4 a が本発明に係る「他の電源線」に相当する。

## 【0099】

本発明に係る「ダイオード」の一例であるダイオード 1 6 7 a ( j ) 及び 1 6 8 a ( j ) は静電気を逃がすための電流経路 1 6 9 a ( j ) と 1 6 9 b ( j ) を夫々構成する。 10

## 【0100】

ダイオード 1 6 7 a ( j ) は、S / R 1 6 1 a ( j ) に第 2 X 側電源 V D D X 及び第 3 X 側電源 V S S X を供給する 2 本の電源線の間に、該 S / R 1 6 1 a ( j ) と電気的に並列に接続されている。本実施形態においては、第 2 X 側電源 V D D X 及び第 3 X 側電源 V S S X を供給する 2 本の電源線は第 1 X 側電源線 5 0 1 a 及び第 2 X 側電源線 5 0 2 a であり、ダイオード 1 6 7 a ( j ) はこれら 2 本の電源線のうち一方で発生した静電気を他方に逃がす電流経路 1 6 8 a ( j ) を提供することによって、静電気から S / R 1 6 1 a ( j ) を保護することができる。

## 【0101】

ダイオード 1 6 8 a ( j ) は、L / S 1 6 2 a ( j ) に第 2 X 側電源 V D D X 及び第 4 X 側電源 V L L X を供給する 2 本の電源線の間に、該 L / S 1 6 2 a ( j ) と電気的に並列に接続されている。第 2 X 側電源 V D D X 及び第 4 X 側電源 V L L X を供給する 2 本の電源線は、第 3 X 側電源線 5 0 3 a 及び第 4 X 側電源線 5 0 4 a であり、ダイオード 1 6 8 a ( j ) はこれら 2 本の電源線のうちの一方で発生した静電気を他方に逃がす電流経路 1 6 9 a ( j ) を提供することによって、静電気から L / S 1 6 2 a ( j ) を静電気から保護することができる。なお、本実施形態においては、S / R 1 6 1 a ( j ) と L / S 1 6 2 a ( j ) 、及び L / S 1 6 2 a ( j ) と B / F 1 6 6 a ( j ) において、夫々電源線を共用していることから、第 1 X 側電源線 5 0 1 a 、第 2 X 側電源線 5 0 2 a 、第 3 X 側電源線 5 0 3 a 及び第 4 X 側電源線 5 0 4 a の何れかの電源線で発生した静電気を他の電源線に逃がすことが可能である。より具体的には、第 4 X 側電源 V L L X から電源を供給する第 4 X 側電源線 5 0 4 a に第 2 X 側電源 V D D X より高電位の静電気が印加された場合、ダイオード 1 6 8 a ( j ) を含む電流経路 1 6 9 a ( j ) は、静電気を第 4 X 側電源線 5 0 4 a から第 3 X 側電源線 5 0 3 a に放出する。第 2 X 側電源 V D D X から電源を供給する第 3 X 側電源線 5 0 3 a に第 4 X 側電源 V L L X より低電位の静電気が印加された場合、ダイオード 1 6 8 a ( j ) を含む電流経路 1 6 9 b ( j ) は、静電気を第 3 X 側電源線 5 0 3 a から第 4 X 側電源線 5 0 4 a に放出する。 20

## 【0102】

従って、第 3 X 側電源線 5 0 3 a 及び第 4 X 側電源線 5 0 4 a に静電気が印加されても、第 3 X 側電源線 5 0 3 a 及び第 4 X 側電源線 5 0 4 a 間に発生する不慮の電圧を電気経路より低電位の静電気が印加された場合、ダイオード 1 6 8 a ( j ) を含む電流経路を介して分散して除去することが可能となる。同様に、第 1 X 側電源線 5 0 1 a 及び第 2 X 側電源線 5 0 2 a との間にダイオード 1 6 7 a ( j ) によって電流経路 1 6 9 a ( j ) が形成されていることから、第 1 X 側電源線 5 0 1 a 及び第 2 X 側電源線 5 0 2 a に発生した静電気に起因する不慮の電圧を該電流経路 1 6 9 a ( j ) を介して放出することが可能である。したがって、ダイオード 1 6 7 a ( j ) 及び 1 6 8 a ( j ) によれば、S / R 1 6 1 a ( j ) 、L / S 1 6 2 a ( j ) 、及び B / F 1 6 6 a ( j ) の全てを静電気から保護することが可能である。 40

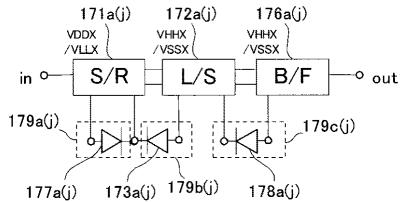

## 【0103】

[第 3 実施形態]

次に、本発明に係る有機ELパネルの駆動回路の他の実施形態について、図6を参照しながら説明する。図6は、本実施形態に係る駆動回路の一部を示すブロック図である。本実施形態に係る有機ELパネルの駆動回路は、第2の実施形態に係る有機ELパネルの駆動回路の変形例であり、X側シフトレジスタ及びX側レベルシフタに電源を供給する3本の電源線間に電流経路を形成し、これら電源線のうち一の電源線で発生した静電気を他の電源線に逃がすことができる点に特徴を有する。

## 【0104】

図6において、駆動回路に含まれるX側シフトレジスタの各段S/R171a(j)、X側レベルシフタの各段L/S172a(j)、及びX側バッファの各段B/F176a(j)は、該データ駆動回路の入力側からS/R171a(j)、L/S172a(j)、及びB/F176a(j)の順で直列に電気的に接続されている。したがって、タイミングジェネレータ及び画像信号処理回路から該駆動回路に入力される各種信号は、S/R171a(j)から所定のタイミングでL/S172a(j)に転送パルスとして転送され、該転送パルスはL/S172a(j)によって電圧がレベルシフトされた駆動信号としてB/F176a(j)を介して出力される。

## 【0105】

S/R171a(j)は、第2X側電源VDDX及び第3X側電源VSSXによって駆動される。第1X側電源線501aが第2X側電源VDDXをS/R171a(j)に供給し、第2X側電源線502aが第3X側電源VSSXをS/R171a(j)に供給する。第1X側電源線501aと第2X側電源線502aとの間には、S/R171a(j)と並列にダイオード177a(j)が電気的に接続されており、ダイオード177a(j)が第1X側電源線501a及び第2X側電源線502aの一方の電源線に発生した静電気を他方に放出する電流経路179a(j)を構成する。

## 【0106】

ダイオード177a(j)のアノード側は、第2X側電源線502aに電気的に接続され、カソード側は第1X側電源線501aに電気的に接続されている。したがって、第3X側電源VSSXから電源が供給される第2X側電源線502aに第2X側電源VDDXより高電位の静電気が印加された場合、ダイオード177a(j)は、静電気を第2X側電源線502aから第1X側電源線501aに放出する。第2X側電源VDDXから電源が供給される第1X側電源線501aに第3X側電源VSSXより低電位の静電気が印加された場合、ダイオード177a(j)は、静電気を第1X側電源線501aから第2X側電源線502aに放出する。ダイオード177a(j)によれば、第1X側電源線501a及び第2X側電源線502aの一方の電源線で発生した静電気を放出することができ、S/R171a(j)を静電気から保護することができる。

## 【0107】

L/S172a(j)は、第1X側電源VHHX及び第3X側電源VSSXによって駆動される。第3X側電源線503aが第1X側電源VHHXをL/S172a(j)に供給し、第4X側電源線504aが第3X側電源VSSXをL/S172a(j)に供給する。第3X側電源線503aと第4X側電源線504aとの間には、L/S172a(j)と並列にダイオード178a(j)が電気的に接続されており、ダイオード178a(j)が第3X側電源線503a及び第4X側電源線504aの一方の電源線に発生した静電気を他方に放出する電流経路179c(j)を構成する。

## 【0108】

なお、S/R171a(j)に第3X側電源VSSXを供給する第2X側電源線502aとL/S172a(j)に第3X側電源VSSXを供給する第4X側電源線504aとは共に第3X側電源VSSXを供給することから、第1X側電源線501a、第2X側電源線502a及び第3X側電源線503aとの間においてこれら電源線に発生した静電気を相互に放出するための電流経路179b(j)がダイオード173a(j)によって形成されている。したがって、ダイオード177a(j)、173a(j)及び178a(j)によれば、3本の電源線の何れかの電源線で発生した静電気からS/R171a(j)

) 及び L / S 1 7 2 a ( j ) を保護することが可能である。

【 0 1 0 9 】

B / F 1 7 6 a ( j ) は、第 1 X 側電源 V H H X 及び第 3 X 側電源 V S S X によって駆動される。第 3 X 側電源線 5 0 3 a が第 1 X 側電源 V H H X を B / F 1 7 6 a ( j ) に供給し、第 4 X 側電源線 5 0 4 a が第 3 X 側電源 V S S X を B / F 1 7 6 a ( j ) に供給する。第 3 X 側電源線 5 0 3 a と第 4 X 側電源線 5 0 4 a との間には、B / F 1 7 6 a ( j ) と並列にダイオード 1 7 9 c ( j ) が電気的に接続されており、ダイオード 1 7 9 c ( j ) が第 3 X 側電源線 5 0 3 a 及び第 4 X 側電源線 5 0 4 a の一方の電源線に発生した静電気を他方に放出する電流経路 1 7 8 a ( j ) を構成する。したがって、ダイオード 1 7 9 c ( j ) によれば、第 3 X 側電源線 5 0 3 a 及び第 4 X 側電源線 5 0 4 a のうち一方の電源線で発生した静電気から L / S 1 7 2 a ( j ) 及び B / F 1 7 6 a ( j ) を保護することが可能である。

【 0 1 1 0 】

このように、第 1 X 側電源線 5 0 1 a 、第 2 X 側電源線 5 0 2 a 、第 3 X 側電源線 5 0 3 a 及び第 4 X 側電源線 5 0 4 a に発生した静電気をダイオード 1 7 7 a ( j ) 、1 7 8 a ( j ) 、及び 1 7 9 a ( j ) によって分散して除去することが可能である。したがって、これら電源線間に発生する不慮の電圧が発生した場合でも、X 側レベルシフタ、X 側バッファ、及び X 側シフトレジスタを含む駆動回路全体を静電気等に起因する不慮の電圧から保護することができる。

【 0 1 1 1 】

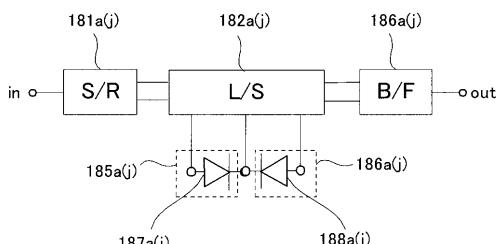

【第 4 実施形態】

次に、図 7 を参照しながら、本発明に係る有機 E L パネルの駆動回路の他の実施形態について説明する。図 7 は、本実施形態に係る有機 E L パネルの駆動回路の一部を示すプロック図である。本実施形態に係る有機 E L パネルの駆動回路は、有機 E L パネルを駆動するための X 側レベルシフタを構成する各段が、4 つの電源線 ( 第 1 X 側電源 V H H X 、第 2 X 側電源 V D D X 、第 3 X 側電源 V S S X 、第 4 X 側電源 V L L X ) のうち 3 種の電源によって駆動され、該 3 種の電源間に電流経路を設けることによってこれら 3 種の電源線に発生した静電気を分散して除去することができる点に特徴を有する。なお、X 側レベルシフタ 1 6 2 の 3 種の電源を供給するために X 側シフトレジスタに電源を供給する第 1 X 側電源線 5 0 1 a 或いは第 2 X 側電源線 5 0 2 a の一方が X 側レベルシフタ 1 5 1 に電源を供給するための電源線として共用される。

【 0 1 1 2 】

図 7 において、X 側レベルシフタ 1 5 2 を構成する各段 L / S 1 8 2 a ( j ) は、第 1 X 側電源 V H H X 、第 2 X 側電源 V D D X 、及び第 3 X 側電源 V S S X によって駆動される。本実施形態においては、例えば、第 3 X 側電源線 5 0 3 a が第 1 X 側電源 V H H X を L / S 1 8 2 a ( j ) に供給し、第 4 X 側電源線 5 0 4 a が第 3 X 側電源線 V S S X を L / S 1 8 2 a ( j ) に供給する。L / S 1 8 2 a ( j ) から X 側バッファ B / F 1 8 6 a ( j ) に転送される X 側駆動信号は、L / S 1 8 2 a ( j ) によって第 1 X 側電源 V H H X 及び第 3 X 側電源 V S S X の電位間の電圧へレベルシフトされている。なお、L / S 1 8 2 a ( j ) には、第 2 X 側電源 V D D X も供給される。第 2 X 側電源線 V D D X を L / S 1 8 2 a ( j ) に供給する電源線としては、例えば、S / R 1 8 1 a ( j ) に電源を供給する電源線が共用される。

【 0 1 1 3 】

第 1 X 側電源 V H H X を供給する第 3 X 側電源線 5 0 3 a と第 3 X 側電源線 V S S X を供給する第 4 X 側電源線 5 0 4 a との間には、ダイオード 1 8 7 a ( j ) が設けられている。ダイオード 1 8 7 a ( j ) のアノード側は第 4 X 側電源線 5 0 4 a と電気的に接続され、カソード側は第 3 X 側電源線 5 0 3 a と電気的に接続されている。したがって、ダイオード 1 8 7 a ( j ) は、第 3 X 側電源線 5 0 3 a と第 4 X 側電源線 5 0 4 a との間でこれら電源線に発生した静電気等を放出するための電流経路 1 8 5 a ( j ) を提供する。

【 0 1 1 4 】

10

20

30

40

50

ダイオード 187a (j) は、第4X側電源線 504a に第1X側電源 VHHX より高電位の静電気が印加された場合には、静電気を第4X側電源線 504a から第3X側電源線 503a に放出し、第3X側電源線 504a に第3X側電源 VSSX より低電位の静電気が印加された場合には、静電気を第3電源線 503a から第4X側電源線 504a に放出する。したがって、ダイオード 187a (j) は、X側レベルシフタを駆動するための電源を供給する電源線で発生した静電気によってX側レベルシフタが静電破壊されることを低減することができる。

## 【0115】

ダイオード 188a (j) は、第2X側電源 VDDX を供給する電源線と、第1X側電源 VHHX を供給する第3X側電源線 503a との間に電気的に接続されている。ダイオード 188a (j) も、ダイオード 187a (j) と同様にこれら2本の電源線で発生した静電気等を放出する電流経路 186a (j) を提供する。

10

## 【0116】

したがって、ダイオード 187a (j) 及び 188a (j) によれば、L/S182a (j) 駆動回路内の電源線で発生した静電気によって L/S182a (j) が破壊されることを抑制することができ、駆動回路全体が静電気によって破壊されることを抑制することが可能である。

## 【0117】

## [第5実施形態]

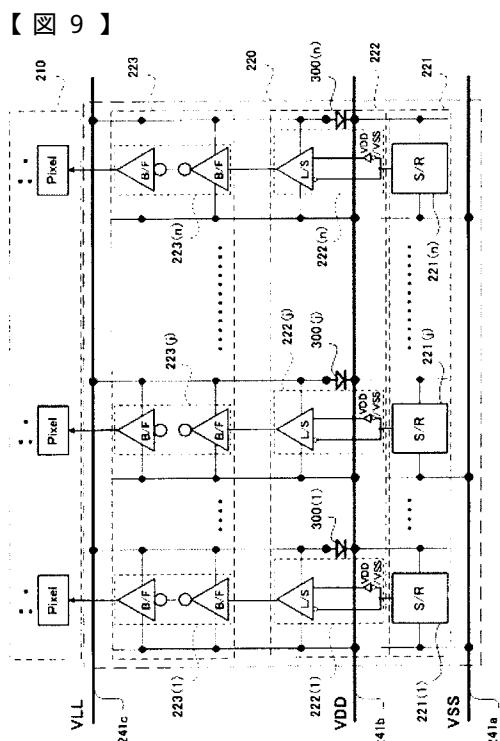

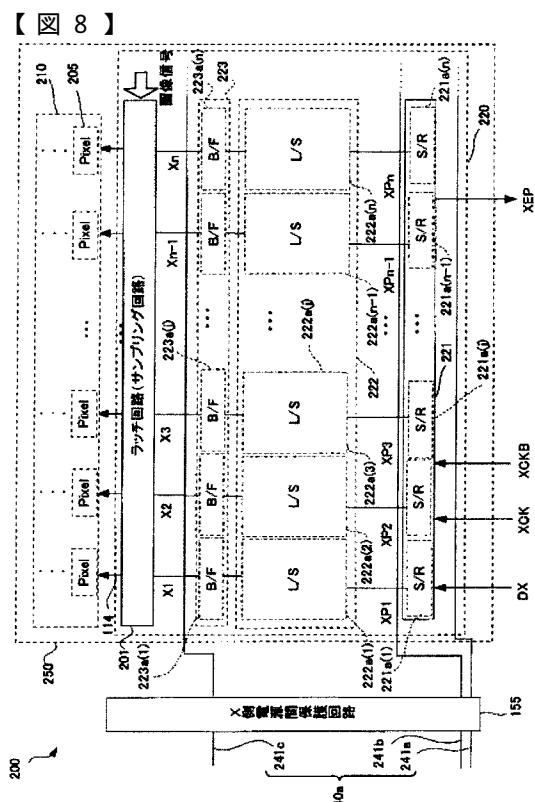

次に、本発明に係る駆動回路の実施形態について説明する。図8は、本実施形態に係る駆動回路を搭載した画像表示装置の構成の概略を示す図であり、図9乃至図11は、本実施形態に係る駆動回路に含まれる保護回路の配置をより詳細に示す図である。本実施形態に係る駆動回路も第1実施形態乃至第4実施形態で説明した電気光学パネルの駆動回路と同様に、駆動回路の含まれる各種回路を静電気から保護することができる。なお、図8乃至図11においては図4乃至図7に比べて配線の接続状態についてより詳細に示すと共に、共通部分については共通の符号を用いて説明を行う。

20

## 【0118】

図8において、有機EL表示装置 200 は、有機ELディスプレイパネル 250、有機ディスプレイパネル 250 上にマトリクス状が配列された複数の画素部 205 を含む画像表示領域 210、データ線駆動回路 220、及び電源線 241a、241b 及び 241c を含む電源線群 240a を備えて構成される。

30

## 【0119】

データ線駆動回路 220 は、本発明に係る「電子回路」の夫タ一例であるシフトレジスタ 221、レベルシフタ 222、及びバッファ 223 を含み、シフトレジスタ 221、レベルシフタ 222、及びバッファ 223 の各段 221(j)、222(j)、及び 223(j) が本発明に係る「単位回路」の夫タ一例である。電源線 241a、241b 及び 241c は夫々異なる電位の電源 VDD、VSS、VHH をデータ線駆動回路 220 に供給する。なお、有機EL表示装置は、図1を参照して説明した有機EL表示装置と同様の構成を備えていることから、詳細な構成についての説明は省略する。

40

## 【0120】

図9は、データ線駆動回路 220 に含まれる保護回路の一例を示す図であり、データ線駆動回路 220 は、電源入力線 280(j) (j = 1, 2, ..., n)、及び本発明に係る「保護回路」の一例である静電保護ダイオード 300(j) (j = 1, 2, ..., n) を含む。

## 【0121】

図9において、電源入力線 280(j) は、シフトレジスタ、バッファ、レベルシフタの各段及び電源線 241a、241b 及び 241c を電気的に接続し、電源線 241c から電源 VLL をシフトレジスタ 221、レベルシフタ 222、バッファ 223 の各段に夫々供給する。

## 【0122】

50

電源入力線 280 (j) は、電源線 241b 及び 241c 間に設けられており、電源線 241c から分岐するようにシフトレジスタ 221、レベルシフタ 222、バッファ 223 の各段の近傍に延設されている。

【0123】

静電保護ダイオード 300 (j) は、電源入力線 280 (j) の途中に設けられており、電源線 241b 及び 241c で発生、或いは電源線 241b 及び 241c に蓄積された静電気から、レベルシフタ 222 及びバッファ 223 の各段を保護する。静電保護ダイオード 300 (j) は、レベルシフタ 222 及びバッファ 223 の各段に電源を供給する電源入力線 280 (j) に設けられていることから、電源入力線 280 (j) の外部、例えば、電源線 241c 或いは 241b に設けられる保護回路に比べてレベルシフタ 222 及びバッファ 223 の各段の近傍に設けられている。したがって、レベルシフタ 222 及びバッファ 223 の各段を、電源線 241c 或いは 241b に蓄積された静電気からより確実に保護することが可能である。

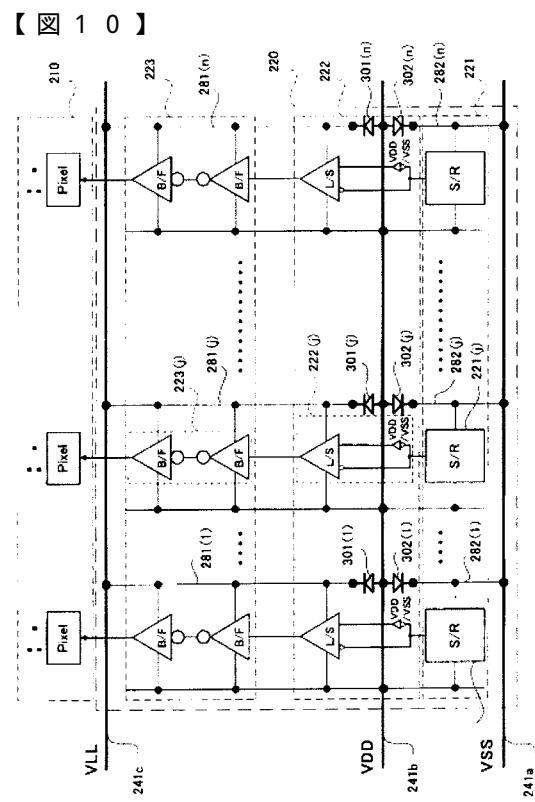

【0124】

図 10 は、保護回路の配置の他の例を示す図であり、データ線保護回路 220 は、電源入力線 281 (j) (j = 1, 2, ..., n) 及び 282 (j) (j = 1, 2, ..., n)、静電保護ダイオード 301 (j) (j = 1, 2, ..., n) 及び 302 (j) (j = 1, 2, ..., n) を含んで構成される。

【0125】

図 10において、電源入力線 281 (j) (j = 1, 2, ..., n) は、電源線 241c 及び 241b 間を電気的に接続するようにレベルシフタ 222 (j) 及びバッファ 223 (j) の各段毎に設けられており、レベルシフタ 222 (j) 及びバッファ 223 (j) の各段に夫々電源 VLL を供給する。

【0126】

静電保護ダイオード 301 (j) は、レベルシフタ 222 (j) 及びバッファ 223 (j) の各段毎に電源入力線 281 (j) の途中に設けられており、電源線 241c 及び 241b で発生した静電気、或いは電源線 241c 及び 241b に蓄積された静電気からレベルシフタ 222 (j) 及びバッファ 223 (j) の各段を保護する。

【0127】

電源入力線 282 (j) は、電源線 241a 及び 241b 間を電気的に接続するようにシフトレジスタ 221 (j) の各段毎に設けられており、シフトレジスタ 221 (j) の各段に夫々電源 VSS を供給する。

【0128】

静電保護ダイオード 302 (j) は、シフトレジスタ 221 (j) の各段毎に電源入力線 282 (j) の途中に設けられており、電源線 241a 及び 241b で発生した静電気、或いは電源線 241a 及び 241b に蓄積された静電気からシフトレジスタ 221 (j) の各段を保護する。

【0129】

静電保護ダイオード 301 (j) 及び 302 (j) は、シフトレジスタ 221 (j)、レベルシフタ 222 (j) 及びバッファ 223 (j) の各段に電源を供給する電源入力線 281 (j) 及び 282 (j) の外部、例えば、電源線 241a、241b 或いは 241b に設けられる保護回路に比べてシフトレジスタ 221 (j)、レベルシフタ 222 (j) 及びバッファ 223 (j) の各段の近傍に設けられている。したがって、静電保護ダイオード 301 (j) 及び 302 (j) は、シフトレジスタ 221 (j)、レベルシフタ 222 及びバッファ 223 の各段を、電源線 241a、241b 或いは 241c に蓄積された静電気からより確実に保護することが可能である。

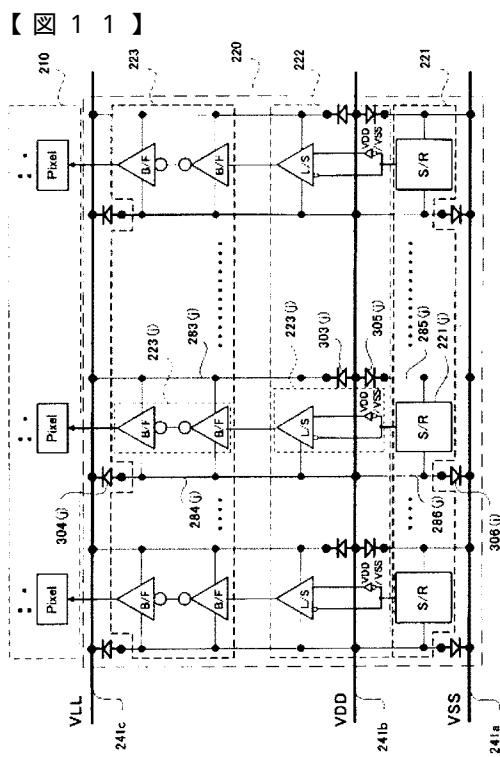

【0130】

図 11 は、保護回路の配置の他の例を示す図であり、データ線保護回路 220 は、電源入力線 283 (j) (j = 1, 2, ..., n)、284 (j) (j = 1, 2, ..., n)、285 (j) (j = 1, 2, ..., n)、286 (j) (j = 1, 2, ..., n) を含んで構成される。

n)、静電保護ダイオード303(j)(j=1、2、・・・、n)、304(j)(j=1、2、・・・、n)、305(j)(j=1、2、・・・、n)、306(j)(j=1、2、・・・、n)を含んで構成される。

【0131】

図11において、電源入力線283(j)は、電源線241c及び241b間を電気的に接続するようにレベルシフタ222(j)及びバッファ223(j)の各段毎に設けられており、レベルシフタ222(j)及びバッファ223(j)の各段に夫々電源VLLを供給する。

【0132】

静電保護ダイオード303(j)は、レベルシフタ222(j)及びバッファ223(j)の各段毎に電源入力線283(j)の途中に設けられており、電源線241c及び241bで発生した静電気、或いは電源線241c及び241bに蓄積された静電気からレベルシフタ222(j)及びバッファ223(j)の各段を保護する。 10

【0133】

電源入力線284(j)は、電源線241b及び241c間を電気的に接続するようにレベルシフタ222(j)及びバッファ223(j)の各段毎に設けられており、レベルシフタ222(j)及びバッファ223(j)の各段に夫々電源VSSを供給する。

【0134】

静電保護ダイオード304(j)は、レベルシフタ222(j)及びバッファ223(j)の各段毎に電源入力線284(j)の途中に設けられており、電源線241c及び241bで発生した静電気、或いは電源線241c及び241bに蓄積された静電気からレベルシフタ222(j)及びバッファ223(j)の各段を保護する。 20

【0135】

電源入力線285(j)は、電源線241a及び241b間を電気的に接続するようにシフトレジスタ221(j)の各段毎に設けられており、シフトレジスタ221(j)の各段に夫々電源VDDを供給する。

【0136】

静電保護ダイオード305(j)は、シフトレジスタ221(j)の各段毎に電源入力線285(j)の途中に設けられており、電源線241a及び241bで発生した静電気、或いは電源線241a及び241bに蓄積された静電気からシフトレジスタ221(j)の各段を保護する。 30

【0137】

電源入力線286(j)は、電源線241a及び241b間を電気的に接続するようにシフトレジスタ221(j)の各段毎に設けられており、シフトレジスタ221(j)の各段に夫々電源VSSを供給する。

【0138】

静電保護ダイオード306(j)は、シフトレジスタ221(j)の各段毎に電源入力線286(j)の途中に設けられており、電源線241a及び241bで発生した静電気、或いは電源線241a及び241bに蓄積された静電気からシフトレジスタ221(j)の各段を保護する。 40

【0139】

静電保護ダイオード303(j)、304(j)、305(j)、及び306(j)は、シフトレジスタ221(j)、レベルシフタ222(j)及びバッファ223(j)の各段に電源を供給する電源入力線283(j)、284(j)、285(j)、及び286(j)の外部、例えば、電源線241a、241b或いは241cに設けられる保護回路に比べてシフトレジスタ221(j)、レベルシフタ222(j)及びバッファ223(j)の各段の近傍に設けられている。したがって、静電保護ダイオード303(j)、304(j)、305(j)、及び306(j)は、シフトレジスタ221(j)、レベルシフタ222及びバッファ223の各段を、電源線241a、241b或いは241cに蓄積された静電気からより確実に保護することが可能である。 50

## 【0140】

(電子機器)

次に、上述した有機EL表示装置が搭載された各種電子機器について説明する。以下で説明する各種電子機器は、第1実施形態から第4実施形態に係る電気光学パネルの駆動回路のうち何れかの駆動回路を含む。また、以下で説明する各種電子機器は、第5実施形態に係る駆動回路を含んでいてもよい。

## 【0141】

<A：モバイル型コンピュータ>

モバイル型のパーソナルコンピュータに、上述した有機EL表示装置を適用した例について、図12を参照しながら説明する。ここに、図12は、コンピュータ1200の構成を示す斜視図である。

## 【0142】

図12において、コンピュータ1200は、キーボード1202を備えた本体部1204と、図示しない有機EL表示装置を用いて構成された表示部1005を有する表示ユニット1206とを備えている。表示部1005は、高品質の画像を表示することができるとともに、装置全体の信頼性も高められている。表示部1005が備える複数の有機ELディスプレイ基板に赤、緑、青の光の三原色の光を発光する有機EL素子を形成しておくことによって、該表示部1005はフルカラー表示で画像表示を行うことができる。

## 【0143】

<B：携帯型電話機>

更に、上述した有機EL表示装置を携帯型電話機に適用した例について、図13を参照して説明する。図13は、携帯型電話機1300の構成を示す斜視図である。図13において、携帯型電話機1300は、複数の操作ボタン1302と共に、本発明の一実施形態である有機EL表示装置を有する表示部1305を備えるものである。

## 【0144】

表示部1305は、上述の表示部1005と同様に高品質の画像を表示することができると共に信頼性が高められている。表示部1305が備える有機ELディスプレイパネルの歩留まりが向上していることから、携帯型電話機1300全体の価格が抑制できると共に、携帯型電話機1300の耐久性も高められている。また、表示部1305が備える複数の有機EL素子が夫々赤、緑、青の光の三原色の光を発光することによって、該表示部1305はフルカラー表示で画像表示を行うこともできる。

## 【0145】

尚、本発明は、上述した実施例に限られるものではなく、請求の範囲及び明細書全体から読み取れる発明の要旨或いは思想に反しない範囲で適宜変更可能であり、そのような変更を伴う電気光学パネルの駆動回路、その駆動方法、並びに電子機器もまた本発明の技術的範囲に含まれるものである。

## 【図面の簡単な説明】

## 【0146】

【図1】本発明の第1実施形態に係る有機EL表示装置の全体構成を示すブロック図である。

【図2】本発明の第1実施形態に係る有機EL表示装置に含まれる画素の構成を示すブロック図である。

【図3】本発明の第1実施形態に係る有機EL表示装置に含まれるデータ線駆動回路の構成を示すブロック図である。

【図4】本発明の第1実施形態に係る有機EL表示装置に含まれるデータ線駆動回路の一部を示すブロック図である。

【図5】本発明の第2実施形態に係る駆動回路の一部を示すブロック図である。

【図6】本発明の第3実施形態に係る駆動回路の一部を示すブロック図である。

【図7】本発明の第4実施形態に係る駆動回路の一部を示すブロック図である。

【図8】本発明の第5実施形態に係る駆動回路の一部を示すブロック図である。

10

20

30

40

50

【図9】本発明の第5実施形態に係る駆動回路の一部を示すブロック図である。

【図10】本発明の第5実施形態に係る駆動回路の一部を示すブロック図である。

【図11】本発明の第5実施形態に係る駆動回路の一部を示すブロック図である。

【図12】本発明の実施形態に係るコンピュータの斜視図である。

【図13】本発明の実施形態に係る携帯型電話機の斜視図である。

【符号の説明】

【0147】

有機EL表示装置 1、有機ELパネル 100、画素部 70、X側シフトレジスタ 114、112、110、120、Y側シフトレジスタ 117、114、112、110、120、150、151、152、レベルシフタ 114、117、110、120、150、151、152、

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図12】

【図13】

## フロントページの続き

(51)Int.Cl.

| F I           | テーマコード(参考) |

|---------------|------------|

| G 0 9 G 3/20  | 6 2 2 E    |

| G 0 9 G 3/20  | 6 2 2 G    |

| G 0 9 G 3/20  | 6 2 3 B    |

| G 0 9 G 3/20  | 6 2 3 G    |

| G 0 9 G 3/20  | 6 2 3 H    |

| G 0 9 G 3/20  | 6 2 3 L    |

| G 0 9 G 3/20  | 6 2 3 R    |

| G 0 9 G 3/20  | 6 7 0 M    |

| G 0 9 G 3/20  | 6 8 0 G    |

| G 0 9 G 3/36  |            |

| H 0 5 B 33/14 | A          |

F ターム(参考) 5C006 AA22 BB16 BC03 BC11 BC20 BF03 BF04 BF25 BF36 BF42

BF46 FA33

5C080 AA06 BB05 CC03 DD19 DD28 EE29 FF11 HH09 JJ02 JJ03

KK04 KK07

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于电光面板的驱动电路和驱动方法，电光装置和包括该电光面板的电子设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2006065292A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2006-03-09 |

| 申请号            | JP2005169174                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2005-06-09 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 青木幸司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 青木幸司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | G09G3/30 G09G3/20 G09G3/36 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G09G3/30.Z G09G3/20.612.A G09G3/20.621.J G09G3/20.621.L G09G3/20.622.B G09G3/20.622.E G09G3/20.622.G G09G3/20.623.B G09G3/20.623.G G09G3/20.623.H G09G3/20.623.L G09G3/20.623.R G09G3/20.670.M G09G3/20.680.G G09G3/36 H05B33/14.A G09G3/30.J G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| F-TERM分类号      | 3K007/AB18 3K007/BA06 3K007/DB03 3K007/GA03 3K007/GA04 5C006/AA22 5C006/BB16 5C006/BC03 5C006/BC11 5C006/BC20 5C006/BF03 5C006/BF04 5C006/BF25 5C006/BF36 5C006/BF42 5C006/BF46 5C006/FA33 5C080/AA06 5C080/BB05 5C080/CC03 5C080/DD19 5C080/DD28 5C080/EE29 5C080/FF11 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080/KK04 5C080/KK07 3K107/AA01 3K107/BB01 3K107/CC21 3K107/CC45 3K107/EE03 3K107/HH00 3K107/HH03 3K107/HH05 5C380/AA01 5C380/AB06 5C380/AB18 5C380/AB34 5C380/AB46 5C380/AC08 5C380/AC11 5C380/BA29 5C380/BB22 5C380/CA09 5C380/CA12 5C380/CA16 5C380/CA17 5C380/CA24 5C380/CA57 5C380/CB37 5C380/CC02 5C380/CC26 5C380/CC33 5C380/CC62 5C380/CD012 5C380/CE04 5C380/CE19 5C380/CF07 5C380/CF09 5C380/CF22 5C380/CF24 5C380/CF46 5C380/DA02 5C380/GA14 |         |            |

| 代理人(译)         | 须泽修                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 优先权            | 2004216891 2004-07-26 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 其他公开文献         | <a href="#">JP4111207B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

### 摘要(译)

解决的问题：减少用于驱动诸如有机EL面板之类的电光面板的驱动电路的静电击穿。在第三X侧电源线503a与第四X侧电源线504a之间，以及第三X侧电源线503a与第四X侧电源线504a之间的一条电源线之间设有二极管158a(j)。构成电流路径159(j)（其中j=1、2、…、N），该电流路径159使在1中产生的静电逸出。由于在第三X侧电源线503a和第四X侧电源线504a之一上产生的静电，电流路径159(j)包括放大电路152a(j)和包括在X侧电平移位器152中的缓冲器156a(j)。）被静电破坏。[选择图]图4