(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-219666

(P2004-219666A)

(43) 公開日 平成16年8月5日(2004.8.5)

(51) Int.Cl.<sup>7</sup>**G09G 3/30****G09G 3/20****H05B 33/14**

F 1

G09G 3/30

G09G 3/20

G09G 3/20 611A

G09G 3/20 611F

G09G 3/20 611H

テーマコード(参考)

3K007

5C080

審査請求 未請求 請求項の数 6 O L (全 18 頁) 最終頁に続く

(21) 出願番号

特願2003-6289 (P2003-6289)

(22) 出願日

平成15年1月14日 (2003.1.14)

(71) 出願人 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100080034

弁理士 原 謙三

(74) 代理人 100113701

弁理士 木島 隆一

(74) 代理人 100116241

弁理士 金子 一郎

(72) 発明者 岡本 成継

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

F ターム(参考) 3K007 AB02 AB03 AB11 AB17 DB03

GA04

最終頁に続く

(54) 【発明の名称】表示素子及び表示装置

## (57) 【要約】

【課題】より少ない個数の画素制御用素子構成によって、素子ばらつきを抑えた階調駆動精度の良い表示素子及び表示装置を提供する。

【解決手段】表示素子は、画素部11の選択を行うnch-TFT6a及び印加電流に応じた発光を行う有機EL素子OLED9aと、信号線12aに接続されかつ画素領域外部に設けられた、画素列に共有のpch-TFT10aと、有機EL素子OLED9aを駆動すべく保持容量C7a及びpch-TFT8aを有する駆動部とを備える。駆動部は、画素走査選択時に、信号線12aから印加された電流信号データに基いてpch-TFT10aにより変換され、かつnch-TFT6aを通して保持容量C7aにて保持された電圧値に応じて、pch-TFT8aにて電流供給線13aによる電流経路によって有機EL素子OLED9aに印加電流を流す。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

第 1 の電極と、

上記第 1 の電極と交差する第 2 の電極と、

第 3 の電極と、

上記第 1 の電極と第 2 の電極との各交差部に対応して設けられる各画素において、該画素の選択を行う選択画素回路、及び印加電流に応じた発光を行う電気光学素子と、

上記第 2 の電極に接続されかつ画素領域外部に設けられた、画素列に共有の電流電圧変換回路と、

上記電気光学素子を駆動すべく電圧保持部と能動素子とを有する駆動部とを備え、

上記駆動部は、上記第 1 の電極及び選択画素回路を介しての画素走査選択時に、上記第 2 の電極から印加された電流信号データに基いて上記電流電圧変換回路により変換され、かつ上記選択画素回路を通して電圧保持部にて保持された電圧値に応じて、上記能動素子にて第 3 の電極による電流経路によって上記電気光学素子に印加電流を流すことを特徴とする表示素子。

**【請求項 2】**

前記電流電圧変換回路の一方の端子が第 2 の電極である信号線に接続され、他方の端子が前記電気光学素子へ電流を供給する第 3 の電極に接続されていることを特徴とする請求項 1 記載の表示素子。

**【請求項 3】**

画素走査選択時には、

前記第 3 の電極から前記電気光学素子に至る電流経路における電流負荷と、前記第 2 の電極から前記電流電圧変換回路を経由して上記第 3 の電極に至る電流経路における電流負荷との比率が、所定値に設定されることを特徴とする請求項 2 記載の表示素子。

**【請求項 4】**

駆動信号発生部、画像信号出力部、選択信号出力部及び電流供給部からなるドライバ部と、表示部とを備え、

上記表示部には、

第 1 の電極と、

上記第 1 の電極と交差する第 2 の電極と、

第 3 の電極と、

上記第 1 の電極と第 2 の電極との各交差部に対応して設けられる各画素において、該画素の選択を行う選択画素回路、及び印加電流に応じた発光を行う電気光学素子と、

上記第 2 の電極に接続されかつ画素領域外部に設けられた、画素列に共有の電流電圧変換回路と、

上記電気光学素子を駆動すべく電圧保持部と能動素子とを有する駆動部とを備え、

上記駆動部は、上記第 1 の電極及び選択画素回路を介しての画素走査選択時に、上記第 2 の電極から印加された電流信号データに基いて上記電流電圧変換回路により変換され、かつ上記選択画素回路を通して電圧保持部にて保持された電圧値に応じて、上記能動素子にて第 3 の電極による電流経路によって上記電気光学素子に印加電流を流す表示素子を備えていることを特徴とする表示装置。

**【請求項 5】**

前記表示素子は、

前記電流電圧変換回路の一方の端子が第 2 の電極である信号線に接続され、他方の端子が前記電気光学素子へ電流を供給する第 3 の電極に接続されていることを特徴とする請求項 4 記載の表示装置。

**【請求項 6】**

前記表示素子では、

画素走査選択時には、

前記第 3 の電極から前記電気光学素子に至る電流経路における電流負荷と、前記第 2 の電

10

20

30

40

50

極から前記電流電圧変換回路を経由して上記第3の電極に至る電流経路における電流負荷との比率が、所定値に設定されることを特徴とする請求項5記載の表示装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、電流駆動型の電気光学素子を用いた表示素子及び表示装置に関するものであり、特に、画素構成及び同構成における階調駆動方法に関するものである。

【0002】

【従来の技術】

従来、エレクトロルミネッセンス(EL: Electro Luminescence) 10 素子として代表的な有機EL素子や無機EL素子を用いた表示装置、及び発光ダイオード等を発光素子として用いた表示装置においては、アナログ階調駆動とデジタル階調駆動との二通りの階調駆動方法が用いられている。

【0003】

前者のアナログ階調駆動による階調駆動方法は、電流ドライバによる電流信号データにより、所定の輝度出力となる電気光学素子電流を得るために電圧条件を画素記憶部に保持することによって階調表示を行う手法であり、この時の画素回路は3個ないし4個のTFT (Thin Film Transistor: 薄膜トランジスタ)回路から構成される。例えは、特許文献1にて開示される画素構成においては、隣接する行の2画素に共通の電流電圧変換回路を設け、平均的には1画素当たり3個のTFTで画素回路が構成されており、ばらつきを抑えたEL表示装置を提供している。 20

【0004】

一方、後者のデジタル階調駆動による階調駆動方法は、電圧ドライバによる電圧信号データにより、所定の輝度出力となる電気光学素子電流を得るために電圧条件を画素記憶部に保持することによって階調表示を行う手法であり、画素回路は2個ないし3個のTFT回路によって構成される。 30

【0005】

以上に掲げるよう、それぞれの階調駆動方法に応じた画素回路構成によるエレクトロルミネッセンス表示装置が提供されている。

【0006】

【特許文献1】

特開2002-215093号公報(平成14年7月31日公開)

【0007】

【発明が解決しようとする課題】

このように、素子を流れる電流に依存して発光する、例えは有機EL素子や無機EL素子及び発光ダイオード等の電気光学素子を発光源とする表示装置においては、電流データ信号の制御手法により、電流信号に比例した発光素子輝度を精度良く得ることができるため、画素をアナログ階調駆動することができる。

【0008】

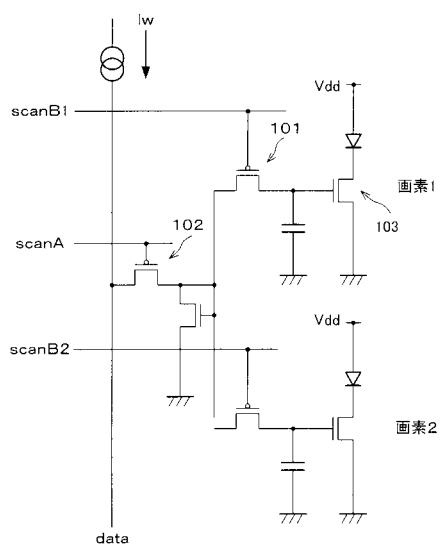

しかしながら、従来のアナログ階調駆動方式の階調駆動を行う際の画素構成としては、図13に示すように、行選択用TFT101、電流制御用TFT102、及び電気光学素子制御用TFT103のように、通常、3個以上のTFT素子が画素内に設けられている。 40

【0009】

一方、デジタル階調駆動において電圧データ信号により電気光学素子の点灯・非点灯を制御する方式においては、少なくとも画素内には行選択用TFTと電気光学素子制御用TFTとの2個のTFTで構成することができる。

【0010】

しかしながら、この画素構成では、素子の特性ばらつきのため精度の良いアナログ階調駆動が困難であることから、二値デジタル階調駆動が通常用いられる。

【0011】

10

20

30

40

50

また、画素開口率の面では、前述の電流制御型の階調駆動方式は、後述の電圧制御型の階調駆動方式よりも画素領域内でTFT素子領域を小さくすることができないため不利である。高画素開口率で画素を構成する程、同じ発光輝度を得る場合でも、より低電圧、高発光効率な電気的条件で素子を駆動することができるため、電力消費や素子寿命の面からも画素内のTFT回路をできるだけ少ない数で構成し、高い画素開口率である方が望まれる。

#### 【0012】

さらに、画素内により多くのTFT素子を設けた場合、各TFT素子相互間の特性ばらつきにより、動作マージンが狭くなったり、面内輝度ばらつきを抑えたりすることが困難になるため、少數のTFTで構成された画素回路でばらつきの影響をできるだけ小さくなるようにすることが望まれる。10

#### 【0013】

本発明は、上記従来の問題点に鑑みなされたものであって、その目的は、より少ない個数の画素制御用素子構成によって、素子ばらつきを抑えた階調駆動精度の良い表示素子及び表示装置を提供することにある。

#### 【0014】

##### 【課題を解決するための手段】

本発明の表示素子は、上記課題を解決するために、第1の電極と、上記第1の電極と交差する第2の電極と、第3の電極と、上記第1の電極と第2の電極との各交差部に対応して設けられる各画素において、該画素の選択を行う選択画素回路、及び印加電流に応じた発光を行う電気光学素子と、上記第2の電極に接続されかつ画素領域外部に設けられた、画素列に共有の電流電圧変換回路と、上記電気光学素子を駆動すべく電圧保持部と能動素子とを有する駆動部とを備え、上記駆動部は、上記第1の電極及び選択画素回路を介しての画素走査選択時に、上記第2の電極から印加された電流信号データに基いて上記電流電圧変換回路により変換され、かつ上記選択画素回路を通して電圧保持部にて保持された電圧値に応じて、上記能動素子にて第3の電極による電流経路によって上記電気光学素子に印加電流を流すことを特徴としている。20

#### 【0015】

また、本発明の表示装置は、上記課題を解決するために、駆動信号発生部、画像信号出力部、選択信号出力部及び電流供給部からなるドライバ部と、表示部とを備え、上記表示部には、第1の電極と、上記第1の電極と交差する第2の電極と、第3の電極と、上記第1の電極と第2の電極との各交差部に対応して設けられる各画素において、該画素の選択を行う選択画素回路、及び印加電流に応じた発光を行う電気光学素子と、上記第2の電極に接続されかつ画素領域外部に設けられた、画素列に共有の電流電圧変換回路と、上記電気光学素子を駆動すべく電圧保持部と能動素子とを有する駆動部とを備え、上記駆動部は、上記第1の電極及び選択画素回路を介しての画素走査選択時に、上記第2の電極から印加された電流信号データに基いて上記電流電圧変換回路により変換され、かつ上記選択画素回路を通して電圧保持部にて保持された電圧値に応じて、上記能動素子にて第3の電極による電流経路によって上記電気光学素子に印加電流を流す表示素子を備えていることを特徴としている。30

#### 【0016】

上記の発明によれば、表示装置は、駆動信号発生部、画像信号出力部、選択信号出力部及び電流供給部からなるドライバ部と、表示部とを備え、上記表示部は、表示素子を備えている。

#### 【0017】

そして、本発明の表示素子では、従来、画素内部に設けられていた電流電圧変換回路を画素領域外部に設け、第2の電極を共通とする画素列にて該電流電圧変換回路を共有化している。

#### 【0018】

したがって、従来、画素内部又は複数の画素内で共有化された電流電圧変換回路が、第240

10

20

30

40

50

の電極を共通とする画素列に対して1つで構成されるので、画素当たりの画素制御用素子の数を削減でき、素子ばらつきも抑えることができる。また、電流電圧変換回路を画素領域外部に設けることによって、画素開口率を大きくすることができ、かつ発光効率の良い駆動条件で駆動することが可能となり、さらには素子寿命の点からも利点がある。

【0019】

また、これにより、画素内の電気光学素子制御用の能動素子のサイズを大きくし、他画素間の特性ばらつきを抑えることが可能となる。

【0020】

この結果、より少ない個数の画素制御用素子構成によって、素子ばらつきを抑えた階調駆動精度の良い表示素子及び表示装置を提供することができる。

10

【0021】

また、本発明の表示素子及び表示装置は、上記記載の表示素子及び表示装置において、前記表示素子は、前記電流電圧変換回路の一方の端子が第2の電極である信号線に接続され、他方の端子が前記電気光学素子へ電流を供給する第3の電極に接続されていることを特徴としている。

【0022】

上記の発明によれば、電気光学素子へ電流を供給する第3の電極と電流電圧変換回路とが接続されている。

【0023】

これにより、画素選択時においては、画素に供給される電流データ信号電流は所定の変換電圧値に近づくと遮断されるので、余剰の電流データ信号電流を上記第3の電極に流すことによって、回路構成の電流・電圧を安定化することができ、かつ余分な配線を不要とし、配線を簡略化することができる。

20

【0024】

また、本発明の表示素子及び表示装置は、上記記載の表示素子及び表示装置において、前記表示素子では、画素走査選択時には、前記第3の電極から前記電気光学素子に至る電流経路における電流負荷と、前記第2の電極から前記電流電圧変換回路を経由して上記第3の電極に至る電流経路における電流負荷との比率が、所定値に設定されることを特徴としている。

30

【0025】

上記の発明によれば、画素走査選択時には、前記第3の電極から前記電気光学素子に至る電流経路における電流負荷と、前記第2の電極から前記電流電圧変換回路を経由して上記第3の電極に至る電流経路における電流負荷との比率が、所定値に設定される。

【0026】

したがって、画素の負荷と電流電圧変換回路の負荷とのバランスを所定の値に設定することにより、電流データ信号電流に対する電気光学素子を流れる電流の線形性つまりダイナミックレンジを調整することができ、信号ドライバの電流制御性が増すので、階調制御をより精度良く行うことができる。

【0027】

この結果、精度の良いアナログ階調駆動を実現する表示素子及び表示装置を提供することができる。

40

【0028】

【発明の実施の形態】

本発明の実施の一形態について、図2ないし図5に基づいて説明すれば、以下の通りである。なお、本実施の形態では、表示装置としての例えば有機エレクトロルミネッセンス(EL: Electro Luminescence) EL表示装置について説明するが、表示装置は必ずしもこれに限らず、例えば、無機EL素子を用いた表示装置、又は発光ダイオード等を発光素子として用いた表示装置についても適用が可能である。

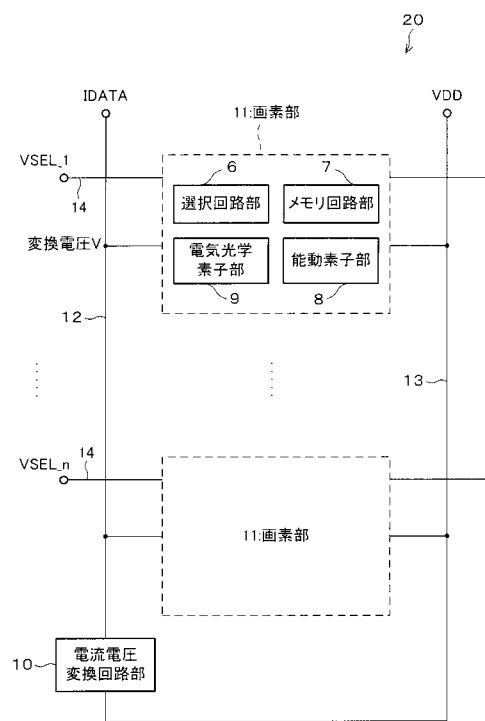

【0029】

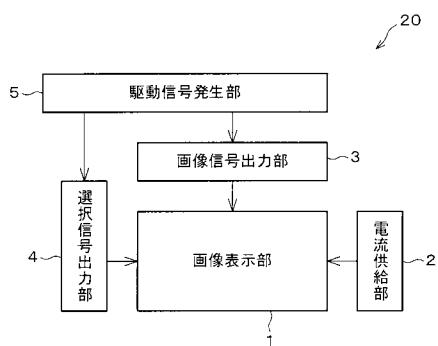

本実施の形態の表示装置としての例えば有機EL表示装置20は、図2に示すように、表

50

示部としての画像表示部1、電流供給部2、画像信号出力部3、選択信号出力部4、及び駆動信号発生部5から構成される。なお、上記駆動信号発生部5、画像信号出力部3及び選択信号出力部4と電流供給部2とは、本発明のドライバ部として機能するものとなっている。

#### 【0030】

上記画像表示部1は、複数の画素としての画素部11が格子状に形成されてなっている。ただし、格子は必ずしも直交するものに限らない。

#### 【0031】

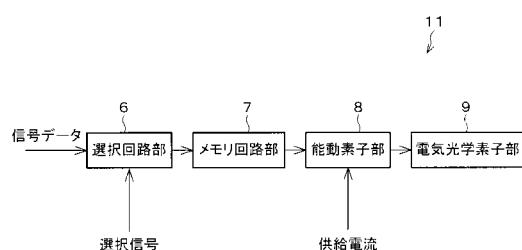

上記の各画素部11は、例えば図3に示すように、信号が入力される選択画素回路としての選択回路部6と、電圧保持部としてのメモリ回路部7と、能動素子としての能動素子部8と、この能動素子部8の素子電流の量に応じた発光を伴う電気光学素子としての電気光学素子部9とから構成される。なお、上記メモリ回路部7及び能動素子部8は、本発明の駆動部を構成する。

#### 【0032】

上記構成の有機EL表示装置20では、図4に示すように、上記画像信号出力部3から出力された電流信号は、第2の電極としての信号線電極12に接続される画素列に共通な電流電圧変換回路としての電流電圧変換回路部10によって変換され、第1の電極としての各走査線電極14によって選択された画素部11のメモリ回路部7に、変換電圧Vに基づく電圧が保持される。

#### 【0033】

上記変換電圧Vは、選択回路部6において電気光学素子部9に流れる電流が所定の値となるような能動素子部8の制御電圧を得る電圧であり、第3の電極としての電流供給電極13及び電流電圧変換回路部10を合わせた距離と、信号線電極12における画素入力に至るまで及び電流電圧変換回路部10に至るまでの距離とに応じた値となる。

#### 【0034】

ここで、上記の電流供給電極13及び電流電圧変換回路部10を合わせた距離については、信号線電極12に印加される電流値によって電気光学素子部9を点灯状態にする際には、電気光学素子部9の電流経路の距離も考慮される。

#### 【0035】

具体的には、距離とは電流負荷に関する値であり、信号線電極12に印加される電流値によって電気光学素子部9を点灯状態にする際には、電流供給電極13から画素部11内の能動素子部8及び電気光学素子部9を含めた選択画素位置までの電流経路における電流負荷と、信号線電極(選択画素位置までを含む)12から電流電圧変換回路部10を経由して電流供給電極13に至るまでの電流経路における電流負荷とのバランス(比率M)によって決定される変換電圧Vが設定される。

#### 【0036】

このようにして、選択期間中にメモリ回路部7によって該変換電圧Vによる情報が書き込まれ、非選択期間においてメモリ回路部7による保持電位に基いた能動素子部8の電流制御により、電気光学素子部9の点灯、非点灯、又はその中間状態の点灯状態を維持することができる。つまり、このような経緯により、入力信号電流値に応じて電気光学素子部9の素子電流を精度良く制御することができる。

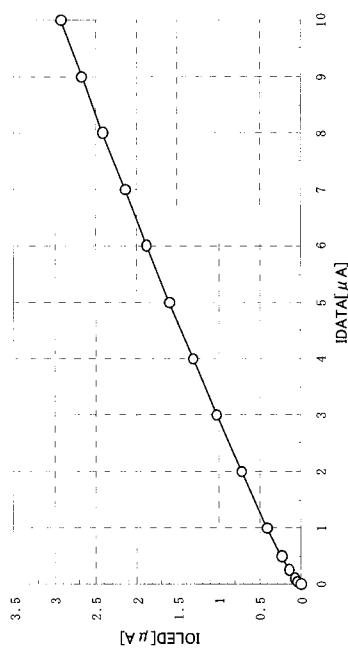

#### 【0037】

上記構成の有機EL表示装置20における入力信号電流DATAに対する電気光学素子電流IODEの出力例を、図5に示す。同図によれば、信号電流印加範囲は $10\mu A$ であり、それに対する出力は最大 $3\mu A$ である。したがって、入力信号電流DATAの量に対して電気光学素子電流IODEが略比例した値になっていることが分かる。

#### 【0038】

ここで、入力信号電流DATAと電気光学素子部9に流れる電気光学素子電流IODEとのバランスは、上記電流負荷のバランスによって決定される。このため、非選択時ににおける画素部11の点灯時における電流負荷を基準においたとき、選択時における電流電

10

20

30

40

50

圧変換回路部10における電流負荷の比率をMとすることにより、入力信号電流I DATAに対する出力画素電流である電気光学素子電流I OLEDの線形性を精度良く調整することができる。比率Mは、例えば、画素部11における能動素子部8を構成する TFT のゲートチャネル幅やゲートチャネル長さ、及び電流電圧変換回路部10を構成する TFT のゲートチャネル幅やゲートチャネル長さを、それぞれ調節することによって適当な値となるように設定すれば良い。

## 【0039】

このように、本実施の形態の有機EL表示装置20は、駆動信号発生部5、画像信号出力部3、選択信号出力部4及び電流供給部2からなるドライバ部と、画像表示部1とを備え、上記画像表示部1は、表示素子を備えている。すなわち、表示素子は、有機EL表示装置20からドライバ部を除いたものである。10

## 【0040】

そして、本実施の形態の表示素子では、従来、画素部11の内部に設けられていた電流電圧変換回路部10を画素領域外部に設け、信号線電極12を共通とする画素列にて該電流電圧変換回路部10を共有化している。

## 【0041】

したがって、従来、画素部11の内部又は複数の画素部11内で共有化された電流電圧変換回路部10が、信号線電極12を共通とする画素列に対して1つで構成されるので、画素当たりの画素制御用素子の数を削減でき、素子ばらつきも抑えることができる。また、電流電圧変換回路部10を画素領域外部に設けることによって、画素開口率を大きくすることができ、かつ発光効率の良い駆動条件で駆動することが可能となり、さらには素子寿命の点からも利点がある。20

## 【0042】

また、これにより、画素部11の内部における電気光学素子制御用の能動素子部8のサイズを大きくし、他画素間の特性ばらつきを抑えることが可能となる。

## 【0043】

この結果、より少ない個数の画素制御用素子構成によって、素子ばらつきを抑えた階調駆動精度の良い表示素子及び有機EL表示装置20を提供することができる。

## 【0044】

また、本実施の形態の表示素子及び有機EL表示装置20では、電気光学素子部9へ電流を供給する電流供給電極13と電流電圧変換回路部10とが接続されている。30

## 【0045】

これにより、画素選択時においては、画素部11に供給される入力信号電流I DATAは所定の変換電圧値に近づくと遮断されるので、余剰の入力信号電流I DATAを電流供給電極13に流すことによって、回路構成の電流・電圧を安定化することができ、かつ余分な配線を不要とし、配線を簡略化することができる。

## 【0046】

また、本実施の形態の表示素子及び有機EL表示装置20は、画素走査選択時には、電流供給電極13から電気光学素子部9に至る電流経路における電流負荷と、信号線電極12から電流電圧変換回路部10を経由して電流供給電極13に至る電流経路における電流負荷との比率が、所定値に設定される。40

## 【0047】

したがって、画素部11の負荷と電流電圧変換回路部10の負荷とのバランスを所定の値に設定することにより、入力信号電流I DATAに対する電気光学素子部9を流れる電流の線形性つまりダイナミックレンジを調整することができ、信号ドライバの電流制御性が増すので、階調制御をより精度良く行うことができる。

## 【0048】

この結果、精度の良いアナログ階調駆動を実現する表示素子及び有機EL表示装置20を提供することができる。

## 【0049】

**【実施例】**

以下、図1、及び図6～図12に基いて、前記実施の形態において説明した階調駆動方式を採用した前記有機EL表示装置20の具体的な構成について説明する。

**【0050】****【実施例1】**

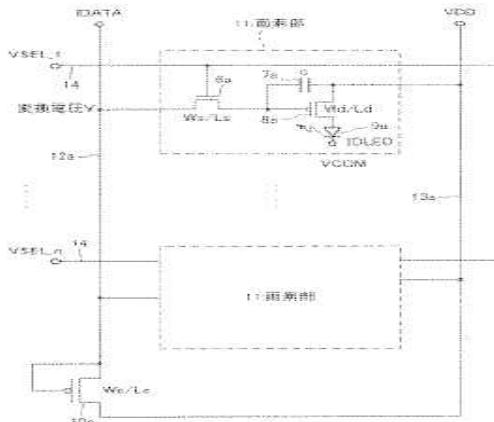

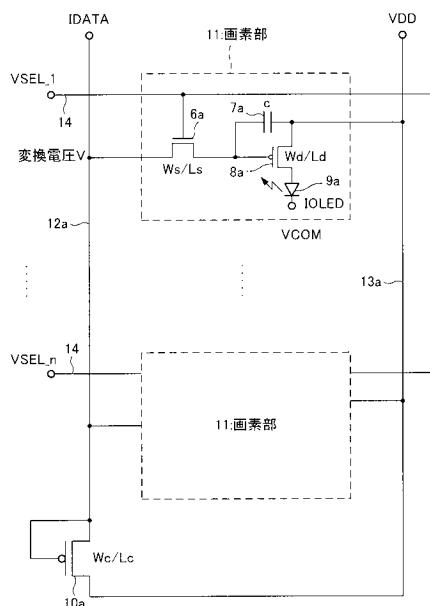

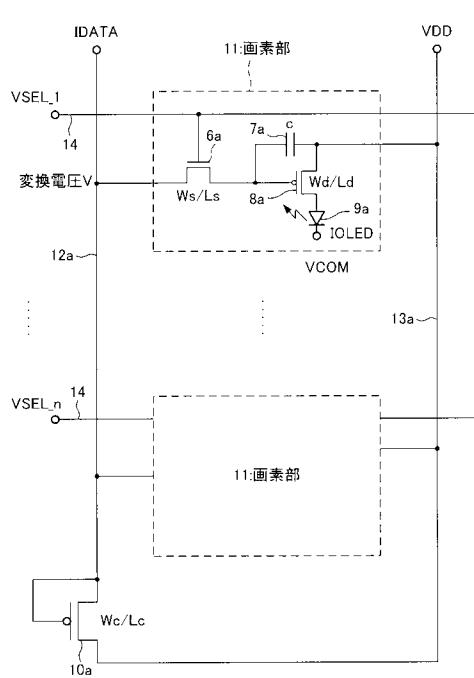

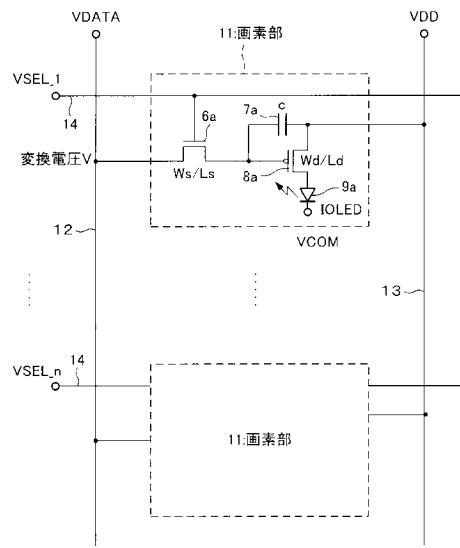

前記図4に示す構成を基本とし、画素部11には2個のTFT回路を設けるとともに、電流電圧変換回路部10に1個のTFTを設けた構成例を、図1に示す。

**【0051】**

図1に示すように、画素部11には、ゲート電極幅W<sub>s</sub>及びゲート電極長L<sub>s</sub>を有するnch-TFT6aが選択回路部6として設けられ、保持容量C<sub>7</sub>aがメモリ回路部7として設けられ、ゲート電極幅W<sub>d</sub>及びゲート電極長L<sub>d</sub>を有するpch-TFT8aが能動素子部8として設けられ、さらに、有機EL素子OLED(Organic Light Emitting Diode)9aが電気光学素子部9として設けられている。画素部11は、このように2個のnch-TFT6a及びpch-TFT8aにて構成されているため、大きな画素開口率を有している。

**【0052】**

一方、電流電圧変換回路部10には、ゲート電極幅W<sub>c</sub>及びゲート電極長L<sub>c</sub>を有するpch-TFT10aが設けられており、このpch-TFT10aのソース端子及びドレン端子は、一方が信号線電極12である信号線12aに接続されており、他方が電流供給電極13である電流供給線13aに接続されている。これによって、信号線12aに印加された入力信号電流IDATAの電流値が電圧に変換され、選択されている画素部11の保持容量C<sub>7</sub>aに、当該入力信号電流IDATAの電流値に対応する保持電圧が保持される。

**【0053】**

非選択期間において保持電圧は、直列に接続されたpch-TFT8aと有機EL素子OLED9aに流れる電気光学素子電流I<sub>OLED</sub>とを制御する。このようにして、能動素子部8の点灯の制御が行われる。つまり、選択画素には電気光学素子電流I<sub>OLED</sub>となるような入力信号電流IDATAが印加されることによって、階調の制御が行われる。

**【0054】**

上記の構成において、入力信号電流IDATAに対する電気光学素子電流I<sub>OLED</sub>の出力結果をシミュレーションによって求めた結果を、前記図5に示す。

**【0055】**

ここで、pch-TFT8a及びpch-TFT10aの各パラメータは、ゲート電極長についてL<sub>c</sub>=L<sub>d</sub>=5μm、ゲート電極幅についてW<sub>c</sub>=5W<sub>d</sub>=100μmである。また、保持容量C<sub>7</sub>aは、500fFである。

**【0056】**

さらに、同図においては、選択期間50μs間で入力信号電流IDATAを入力し、保持容量C<sub>7</sub>aに変換電圧を保持している。nch-TFT6aのゲート電極幅W<sub>s</sub>及びゲート電極長L<sub>s</sub>のパラメータは保持容量C<sub>7</sub>aの充放電時間に寄与するが、選択時間内に十分に充放電可能となるような値に設定する。ここでは、十分な選択時間を与えているため、nch-TFT6aのゲート電極幅W<sub>s</sub>及びゲート電極長L<sub>s</sub>の値は任意である。

**【0057】**

同図によれば、信号電流印加範囲は、0～10μAであり、それに対する出力は0～3μAであり、略比例した関係となっていることが分かる。

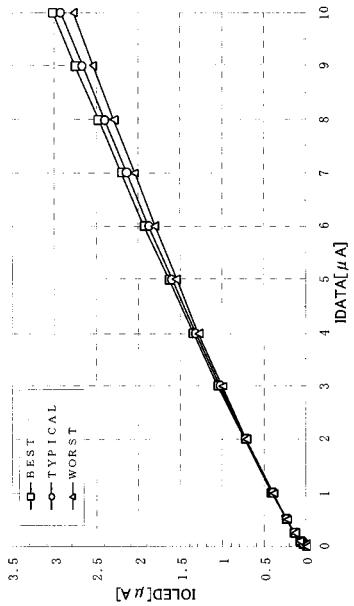

**【0058】**

次に、TFTの特性ばらつきに関する動作を検討した結果を、図6に示す。

**【0059】**

本実施例においては、各pch-TFT8a及びnch-TFT6aの移動度μと閾値電圧V<sub>th</sub>とを変化させて特性のばらつきを比較した。ゲート電極幅W<sub>d</sub>・W<sub>s</sub>やゲート電極長L<sub>d</sub>・L<sub>s</sub>の設定については、前記図5における設定値と同様である。設定されたそ

それぞれの TFT 特性値は、以下に示すとおりである。

【0060】

pch-TFT8a の移動度  $\mu$  と閾値電圧  $V_{th}$

| 条件      | $\mu$ [ cm <sup>2</sup> / Vs ] | $V_{th}$ [ V ] |

|---------|--------------------------------|----------------|

| BEST    | 250                            | -0.5           |

| Typical | 200                            | -1.5           |

| Worst   | 150                            | -2.5           |

nch-TFT の移動度  $\mu$  と閾値電圧  $V_{th}$

| 条件      | $\mu$ [ cm <sup>2</sup> / Vs ] | $V_{th}$ [ V ] |

|---------|--------------------------------|----------------|

| BEST    | 250                            | +1.0           |

| Typical | 200                            | +2.0           |

| Worst   | 150                            | +3.0           |

図6においては、それぞれの特性による結果は、入力信号電流 IDATA に概ね比例した電気光学素子電流 IOLED である有機EL素子電流 IOLED を出力していることが分かる。

【0061】

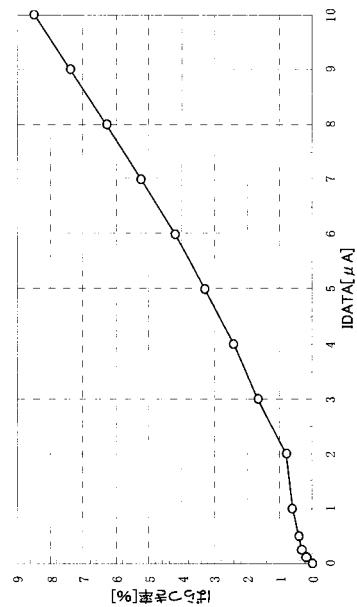

また、BEST 特性と Worst 特性との差を、入力信号電流 IDATA = 10 μA における Typical 値の有機 EL 素子電流 IOLED 出力を基準に置いたときの比率で示した場合を図7に示す。同図においては、入力信号値である入力信号電流 IDATA が低くなるに伴って、相対的なばらつき量が小さくなるため、低輝度領域でのばらつきは十分に小さいことが分かる。

【0062】

〔比較例1〕

図8は、定電圧制御型画素構成の一例であり、定電流制御型画素である図1と比較した場合、電流電圧変換回路部10がなく、信号線12aと電流供給線13aとは電気的に絶縁されており、信号線12aに印加される信号は電圧 VDATA である。

【0063】

同図においては、選択期間において選択された画素では、信号電圧 VDATA に対応する保持電圧が保持容量 C7a に保持され、非選択期間においては、上記の保持された電圧情報に対応する有機EL素子電流 IOLED が流れるように pch-TFT8a が制御される。

【0064】

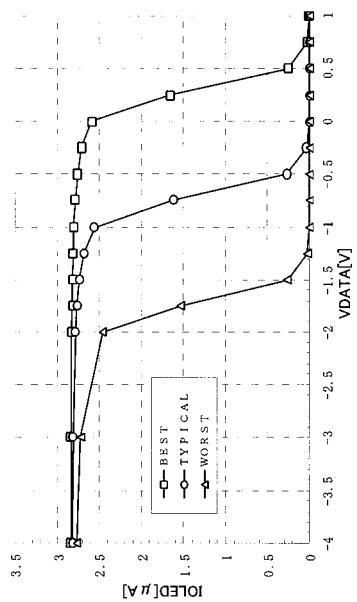

次に、図9は、上記実施例1に対応する電圧信号 VDATA に対する電気光学素子電流 IOLED の関係を図示したものである。また、図7に対応して電圧信号 VDATA に対する有機EL素子電流 IOLED のばらつき率を、図10に示す。ここで、図8～図10記載の信号電圧 VDATA は、pch-TFT8a の閾値電圧の Typical 条件と電流供給電源電圧 VDD との和を基準電圧としている。つまり、実際に印加されている電圧を VREAL とおくと、装置の基準電圧点からは、

$$V_{REAL} = V_{DD} + V_{th}(\text{Typical}) + V_{DATA}$$

が信号電圧として印加されることになる。

【0065】

図9によれば、入力電圧信号に対する出力信号の線形性は崩れており、アナログ階調制御を行う際は、例えば Typical 条件においては、-1.25 ~ +0.25 間の狭い入力電圧範囲内での電圧制御を必要とする。また、素子の特性ばらつきを考慮すると、上記電圧範囲内では、Worst 条件は非点灯状態であり、また、BEST 条件では点灯状態を示す。

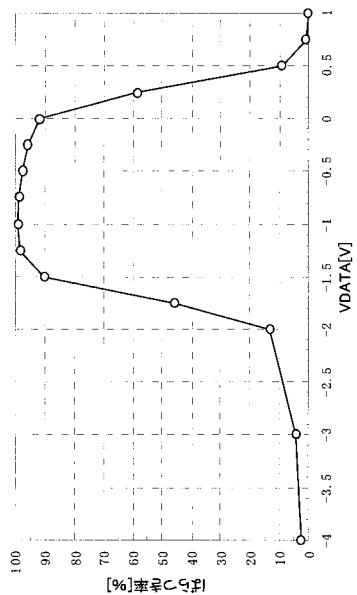

【0066】

このことを、図10を用いて説明すると、信号電圧 VDATA = 1V では有機EL素子電流 IOLED のばらつきは 2 ~ 3 % 程度であるが、信号電圧 VDATA = -1.5 ~ 0V 間では約 100 % のばらつきを持つ。つまり、この信号電圧範囲内では、完全点灯状態と

完全非点灯状態との差ほどの有機EL素子電流ILEDのばらつきが生じることを意味し、実際の表示においては、表示画面内で点灯個所と非点灯個所とが混在するような表示が観測されることになる。

以上のことから、図8における電圧制御型画素構成においては、アナログ階調駆動よりもむしろ、二値階調で駆動すること、つまりデジタル階調駆動を行う方が、有機EL素子電流ILEDの電流ばらつきを小さくできる。しかしながら、デジタル階調で多階調表示を行う際は、時分割階調駆動を行う必要があるため、ドライバ回路のクロックが高速化し、消費電流を増加させることになる。また、動き画像を表示した際に視覚の錯覚による偽輪郭妨害が発生することにもなるため、動画偽輪郭対策のために駆動回路規模が大きくなる。

10

#### 【0067】

##### 〔実施例2〕

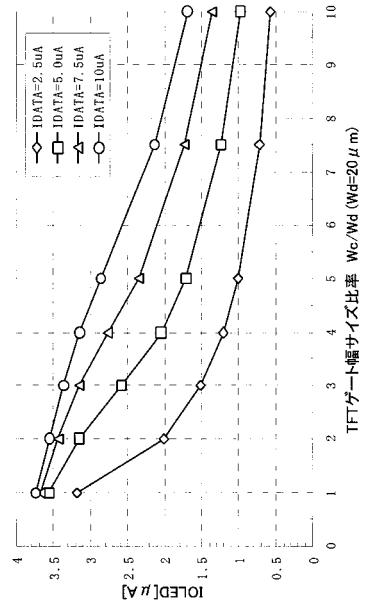

電流負荷の比率Mを変更するファクターとして、図1において画素部11内の能動素子部8に対応するpch-TFT8aにおけるTFTのゲート電極幅をWdとし、かつ電流電圧変換回路10に対応するpch-TFT10aにおけるTFTのゲート電極幅をWcとしたとき、入力信号電流IDATAが $2.5\mu A$ 、 $5.0\mu A$ 、 $7.5\mu A$ 及び $10\mu A$ であるときのゲート電極幅Wc/Wd比率に対する電気光学素子電流ILEDである有機EL素子電流ILEDの出力結果を図11示す。なお、TFT特性は、TYPICAL条件によるものを用いている。

#### 【0068】

同図によれば、ゲート電極幅Wc/Wd比率を1にすると、図示される入力信号電流IDATAの範囲に対して、有機EL素子電流ILEDは略飽和状態であり、線形性が大きく崩れている。ゲート電極幅Wc/Wd比率をより大きくなるようにしたとき、線形性が現れてくることが分かる。

20

#### 【0069】

このときの電流負荷について、pch-TFT8aのオン抵抗(数10k~数100k)、及び有機EL素子OLED9aのオン抵抗(数100k~数M)に比べると信号線12a及び電流供給線13aの配線抵抗は数100程度であるため、十分小さいと見なすことができれば配線抵抗成分は無視しても差し支えない。

30

#### 【0070】

つまり、pch-TFT10aにおける負荷と、画素部11のpch-TFT8a及び有機EL素子OLED9aの総負荷とのバランスによって、入力信号電流IDATAと有機EL素子電流ILEDとの線形性を調整することが可能である。

#### 【0071】

上記構成によれば、各nch-TFT6a及びpch-TFT8a・10aの負荷バランスは、ゲート電極幅Wやゲート電極長Lによってコントロールできるため、例えば、ゲート電極長Lを一定とする場合には、デジタル階調駆動を行う場合にはゲート電極幅Wc/Wd=1とし、また、アナログ階調駆動を行う場合にはゲート電極幅Wc/Wd>1となるように設定すればよい。

40

#### 【0072】

また、ゲート電極幅Wc/Wd比率が大きくなるにしたがって、入力信号電流IDATA= $10\mu A$ 時の有機EL素子電流ILEDのレベルが低下しているが、出力レベル自体を増加させるためには電流供給源電圧VDDを増加させれば良い。

#### 【0073】

このようにして、入力信号電流IDATAの制御性に対応させて負荷バランスを調整すれば、ダイナミックレンジや線形性の設定が行え、目的の駆動方法に合わせた画素構成を提供することができる。

#### 【0074】

また、上記電流負荷の設定手法により、信号ドライバの電流制御性を高めることができる。なぜなら、ドライバ回路の出力能力に応じた負荷設定値にすることによって信号電

50

流出力レベルの最小値を所定の設定値にすることができる、ドライバ回路の電流出力ばらつきを抑えた構成とすることが可能になるためである。

#### 【0075】

##### 〔実施例3〕

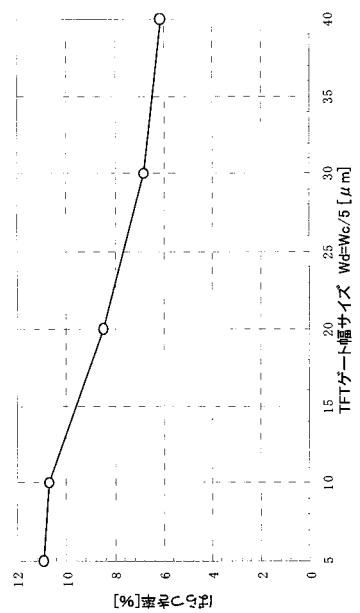

図12は、実施例1と同様のTFT特性条件と回路構成において、ゲート電極幅 $W_c$ ・ $W_d$ のサイズを変化させ、入力信号電流 $I_{DATA} = 10 \mu A$ における有機EL素子電流 $I_{OLED}$ のばらつき率を比較した結果である。

#### 【0076】

同図に示すように、入力信号電流 $I_{DATA}$ と出力電流である有機EL素子電流 $I_{OLED}$ との線形性を得るため、実施例2の結果からゲート電極幅 $W_c / W_d = 5$ とおいて、ゲート電極幅 $W_d = 5 \sim 40 \mu m$ の範囲でばらつき率の変化を見たとき、ゲート電極幅 $W_d = 5 \mu m$ では最もばらつき率が高く、ゲート電極幅 $W_d$ を大きくするに伴ってばらつき率を小さくできることが分かる。10

#### 【0077】

このことを画素開口率の面から考えると、図12で示される範囲の条件では、 $pch-TFT8a$ のゲート電極幅 $W_d = 5 \mu m$ の時が最も画素開口率を広く取ることが可能である。しかしながら、ばらつき率が大きいため、面内画素が全点灯状態であっても10%程度の輝度ばらつきが面内で発生することが予見できる。

#### 【0078】

ここで、ゲート電極幅 $W_d = 40 \mu m$ とすれば、ばらつきは6%以下にすることができる。この場合、電流電圧変換回路部10である $pch-TFT10a$ のゲート電極幅 $W_c$ は、 $W_c = 5 \times W_d = 200 \mu m$ とすればよい。20

#### 【0079】

$pch-TFT10a$ については、画素領域の外に設置されるため、画素部11の配置制約と比べて配置空間の制約が小さく、自由度の高い配置が可能である。

#### 【0080】

TFTの特性ばらつきをできるだけ減らすためには、通常、ゲート電極幅 $W$ を大きくすることによって、ポリシリコン結晶の不均一なばらつきを緩和することが可能となる。

#### 【0081】

しかしながら、従来の電流制御型画素では、通常、3個以上のTFTによって画素回路が構成されるため、大きなゲート電極幅 $W$ のTFTを配置することは物理的に困難であり、可能ではあっても画素開口率が小さくなるため不利である。30

#### 【0082】

本構成では、2個のTFTで画素回路が構成されているため、従来の3個のTFTを用いる構成よりも大きな画素開口率が望め、さらに、TFT特性ばらつきを抑えた画素構成を提供することが可能となる。

#### 【0083】

なお、上記に掲げた適用例は本発明による利点を説明するものであるため、本発明の主旨の範囲内で、種々の画素構成、及び駆動方式に適用が可能である。

#### 【0084】

##### 【発明の効果】

本発明の表示素子は、以上のように、第1の電極と、上記第1の電極と交差する第2の電極と、第3の電極と、上記第1の電極と第2の電極との各交差部に対応して設けられる各画素において、該画素の選択を行う選択画素回路、及び印加電流に応じた発光を行う電気光学素子と、上記第2の電極に接続されかつ画素領域外部に設けられた、画素列に共有の電流電圧変換回路と、上記電気光学素子を駆動すべく電圧保持部と能動素子とを有する駆動部とを備え、上記駆動部は、上記第1の電極及び選択画素回路を介しての画素走査選択時に、上記第2の電極から印加された電流信号データに基いて上記電流電圧変換回路により変換され、かつ上記選択画素回路を通して電圧保持部にて保持された電圧値に応じて、上記能動素子にて第3の電極による電流経路によって上記電気光学素子に印加電流を流す4050

ものである。

【0085】

また、本発明の表示装置は、以上のように、駆動信号発生部、画像信号出力部、選択信号出力部及び電流供給部からなるドライバ部と、表示部とを備え、上記表示部には、第1の電極と、上記第1の電極と交差する第2の電極と、第3の電極と、上記第1の電極と第2の電極との各交差部に対応して設けられる各画素において、該画素の選択を行う選択画素回路、及び印加電流に応じた発光を行う電気光学素子と、上記第2の電極に接続されかつ画素領域外部に設けられた、画素列に共有の電流電圧変換回路と、上記電気光学素子を駆動すべく電圧保持部と能動素子とを有する駆動部とを備え、上記駆動部は、上記第1の電極及び選択画素回路を介しての画素走査選択時に、上記第2の電極から印加された電流信号データに基いて上記電流電圧変換回路により変換され、かつ上記選択画素回路を通して電圧保持部にて保持された電圧値に応じて、上記能動素子にて第3の電極による電流経路によって上記電気光学素子に印加電流を流す表示素子を備えているものである。10

【0086】

それゆえ、表示装置は、駆動信号発生部、画像信号出力部、選択信号出力部及び電流供給部からなるドライバ部と、表示部とを備え、上記表示部は、表示素子を備えている。

【0087】

そして、本発明の表示素子では、従来、画素内部に設けられていた電流電圧変換回路を画素領域外部に設け、第2の電極を共通とする画素列にて該電流電圧変換回路を共有化している。20

【0088】

したがって、従来、画素内部又は複数の画素内で共有化された電流電圧変換回路が、第2の電極を共通とする画素列に対して1つで構成されるので、画素当たりの画素制御用素子の数を削減でき、素子ばらつきも抑えることができる。また、電流電圧変換回路を画素領域外部に設けることによって、画素開口率を大きくすることができ、かつ発光効率の良い駆動条件で駆動することが可能となり、さらには素子寿命の点からも利点がある。

【0089】

また、これにより、画素内の電気光学素子制御用の能動素子のサイズを大きくし、他画素間の特性ばらつきを抑えることが可能となる。

【0090】

この結果、より少ない個数の画素制御用素子構成によって、素子ばらつきを抑えた階調駆動精度の良い表示素子及び表示装置を提供することができるという効果を奏する。30

【0091】

また、本発明の表示素子及び表示装置は、上記記載の表示素子及び表示装置において、前記表示素子は、前記電流電圧変換回路の一方の端子が第2の電極である信号線に接続され、他方の端子が前記電気光学素子へ電流を供給する第3の電極に接続されているものである。

【0092】

それゆえ、画素選択時においては、画素に供給される電流データ信号電流は所定の変換電圧値に近づくと遮断されるので、余剰の電流データ信号電流を上記第3の電極に流すことによって、回路構成の電流・電圧を安定化することができ、かつ余分な配線を不要とし、配線を簡略化することができるという効果を奏する。40

【0093】

また、本発明の表示素子及び表示装置は、上記記載の表示素子及び表示装置において、前記表示素子では、画素走査選択時には、前記第3の電極から前記電気光学素子に至る電流経路における電流負荷と、前記第2の電極から前記電流電圧変換回路を経由して上記第3の電極に至る電流経路における電流負荷との比率が、所定値に設定されるものである。

【0094】

それゆえ、画素の負荷と電流電圧変換回路の負荷とのバランスを所定の値に設定することにより、電流データ信号電流に対する電気光学素子を流れる電流の線形性つまりダイナミ50

ックレンジを調整することができ、信号ドライバの電流制御性が増すので、階調制御をより精度良く行うことができる。

【0095】

この結果、精度の良いアナログ階調駆動を実現する表示素子及び表示装置を提供することができるという効果を奏する。

【図面の簡単な説明】

【図1】本発明における表示素子及び表示装置の実施の一形態を示すものであり、表示素子における電流制御型画素の具体的構成を示す回路図である。

【図2】上記表示装置としての有機EL表示装置の全体構成を示すブロック図である。

【図3】上記表示素子における画素部の構成を示すブロック図である。 10

【図4】上記表示素子における電流制御型画素の構成を示すブロック図である。

【図5】上記表示素子における入力信号電流に対する電気光学素子の電流特性を示すグラフである。

【図6】TFT特性条件による入力信号電流に対する電気光学素子の電流特性を示すグラフである。

【図7】入力信号電流に対する電気光学素子の電流特性のばらつき率を示すグラフである。

【図8】比較例を示すものであり、電圧制御型画素の構成を示す回路図である。

【図9】TFT特性条件による入力信号電圧に対する電気光学素子の電流特性を示すグラフである。 20

【図10】入力信号電圧に対する電気光学素子の電流特性のばらつき率を示すグラフである。

【図11】画素内のpch-TFTのゲート電極幅と電流電圧変換回路におけるpch-TFTaのゲート電極幅とのゲート電極幅比率に対する有機EL素子の出力電流特性の線形性を示すグラフである。

【図12】画素内のpch-TFTのゲート電極幅と電流電圧変換回路におけるpch-TFTのゲート電極幅とのゲート電極幅比率を固定した際の絶対サイズに対する有機EL素子の出力電流特性のばらつき率を示すグラフである。

【図13】従来の表示素子の構成を示す回路図である。

【符号の説明】

- 1 画像表示部（表示部）

- 2 電流供給部

- 3 画像信号出力部

- 4 選択信号出力部

- 5 駆動信号発生部

- 6 選択回路部（選択画素回路）

- 6 a nch-TFT（選択画素回路）

- 7 メモリ回路部（電圧保持部、駆動部）

- 7 a 保持容量C（電圧保持部）

- 8 能動素子部（能動素子、駆動部）

- 8 a pch-TFT（能動素子）

- 9 電気光学素子部（電気光学素子）

- 9 a 有機EL素子OLED（電気光学素子）

- 10 電流電圧変換回路部（電流電圧変換回路）

- 10 a pch-TFT（電流電圧変換回路）

- 11 画素部（画素）

- 12 信号線電極（第2の電極）

- 12 a 信号線

- 13 電流供給電極（第3の電極）

- 13 a 電流供給線

10

20

30

40

50

## 14 走査線電極（第1の電極）

I DATA 入力信号電流

I OLED 有機EL素子電流（電気光学素子電流）

Lc・Ld・Ls ゲート電極長

Wc・Wd・Ws ゲート電極幅

V 変換電圧

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き(51)Int.Cl.<sup>7</sup>

| F I          | テーマコード(参考) |

|--------------|------------|

| G 09 G 3/20  | 6 2 3 R    |

| G 09 G 3/20  | 6 2 4 B    |

| G 09 G 3/20  | 6 4 1 D    |

| G 09 G 3/20  | 6 4 2 A    |

| G 09 G 3/20  | 6 8 0 F    |

| H 05 B 33/14 | A          |

F ターム(参考) 5C080 AA06 BB05 DD02 DD05 DD22 DD26 DD28 DD29 EE19 EE29

FF11 HH09 JJ02 JJ03 JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示元件和显示设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2004219666A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 公开(公告)日 | 2004-08-05 |

| 申请号            | JP2003006289                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 申请日     | 2003-01-14 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| [标]发明人         | 岡本成継                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 岡本 成継                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| FI分类号          | G09G3/30.H G09G3/30.K G09G3/20.611.A G09G3/20.611.F G09G3/20.611.H G09G3/20.623.R G09G3/20.624.B G09G3/20.641.D G09G3/20.642.A G09G3/20.680.F H05B33/14.A G09G3/3225 G09G3/3266 G09G3/3275 G09G3/3283 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| F-TERM分类号      | 3K007/AB02 3K007/AB03 3K007/AB11 3K007/AB17 3K007/DB03 3K007/GA04 5C080/AA06 5C080/BB05 5C080/DD02 5C080/DD05 5C080/DD22 5C080/DD26 5C080/DD28 5C080/DD29 5C080/EE19 5C080/EE29 5C080/FF11 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080/JJ05 3K107/AA01 3K107/AA05 3K107/BB01 3K107/CC14 3K107/CC21 3K107/CC33 3K107/CC36 3K107/EE03 3K107/HH00 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB06 5C380/AB23 5C380/BA12 5C380/BA14 5C380/BA38 5C380/BB05 5C380/CA08 5C380/CA12 5C380/CA13 5C380/CB01 5C380/CC02 5C380/CC26 5C380/CC33 5C380/CC62 5C380/CC63 5C380/CD012 5C380/CD013 5C380/DA06 5C380/HA13 |         |            |

| 代理人(译)         | 木島隆一<br>金子一郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

### 摘要(译)

解决的问题：提供一种具有少量像素控制元件配置的显示元件和显示装置，该显示元件和显示装置抑制元件变化并且具有高灰度驱动精度。显示元件包括：用于选择像素部分11的nch-TFT 6a；用于根据施加的电流发光的有机EL元件OLED 9a；以及连接至信号线12a并设置在像素区域外部的像素列。另外，提供了共享的pch-TFT 10a以及具有存储电容器C7a和用于驱动有机EL元件OLED9a的pch-TFT 8a的驱动单元。当选择像素扫描时，驱动单元由pch-TFT 10a基于从信号线12a施加的电流信号数据，并根据保持电容器C7a通过nch-TFT 6a保持的电压值，由pch-TFT 10a转换。在TFT 8a中，施加的电流通过电流供应线13a的电流路径流过有机EL元件OLED9a。[选型图]图1