(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-122228

(P2009-122228A)

(43) 公開日 平成21年6月4日(2009.6.4)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | K 3K107     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/30 | J 5C080     |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 | 611H        |

|                             | G09G 3/20 | 641D        |

|                             | G09G 3/20 | 621A        |

審査請求 未請求 請求項の数 5 O L (全 22 頁) 最終頁に続く

|           |                              |            |                                                                                                 |

|-----------|------------------------------|------------|-------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2007-294100 (P2007-294100) | (71) 出願人   | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号                                                          |

| (22) 出願日  | 平成19年11月13日 (2007.11.13)     | (74) 代理人   | 100102185<br>弁理士 多田 繁範                                                                          |

|           |                              | (72) 発明者   | 豊村 直史<br>東京都港区港南1丁目7番1号 ソニー株式会社内                                                                |

|           |                              | (72) 発明者   | 内野 勝秀<br>東京都港区港南1丁目7番1号 ソニー株式会社内                                                                |

|           |                              | F ターム (参考) | 3K107 AA01 BB01 CC33 EE03 HH04<br>HH05<br>5C080 AA06 BB05 DD05 EE28 EE29<br>FF11 JJ02 JJ03 JJ04 |

(54) 【発明の名称】表示装置及び表示装置の駆動方法

(57) 【要約】 (修正有)

【課題】有機EL素子によるアクティブマトリックス型の表示装置に適用して正しく駆動トランジスタのしきい値電圧のばらつきを補正する。

【解決手段】信号レベル保持用コンデンサの端子間電圧( $V_g - V_s$ )を駆動トランジスタのしきい値電圧 $V_{th}$ 以上に設定した後、複数回の期間に分けて、この信号レベル保持用コンデンサの蓄積電荷を駆動トランジスタにより放電させて信号レベル保持用コンデンサの端子間電圧( $V_g - V_s$ )を駆動トランジスタのしきい値電圧 $V_{th}$ に設定する際に、始めの期間 $T_{th1}$ で発光素子のカソード電圧CATHを立ち上げて短時間で信号レベル保持用コンデンサの端子間電圧( $V_g - V_s$ )が駆動トランジスタのしきい値電圧 $V_{th}$ となるように設定した後、カソード電圧CATHを元の電圧に戻して最終的に信号レベル保持用コンデンサの端子間電圧( $V_g - V_s$ )を駆動トランジスタのしきい値電圧 $V_{th}$ に設定する。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

画素回路をマトリックス状に配置して形成された表示部に対して、前記表示部の信号線及び走査線を介して水平駆動回路及び垂直駆動回路により前記画素回路を駆動することにより、前記表示部で所望の画像を表示する表示装置において、

前記画素回路は、

少なくとも発光素子と、

信号レベル保持用コンデンサと、

前記信号レベル保持用コンデンサの両端をゲート及びソースに接続し、前記発光素子のアノードを前記ソースに接続し、前記ゲート及びソース間電圧に応じた駆動電流で前記発光素子を駆動する駆動トランジスタと、

前記垂直駆動回路から出力される書込信号によりオン動作し、前記駆動トランジスタのゲートを前記信号線に接続する書込トランジスタとを有し、

前記水平駆動回路は、

各画素の階調を示す階調電圧の連続による駆動信号を前記信号線毎に生成し、

前記駆動信号を対応する前記信号線に出力し、

前記垂直駆動回路は、

前記発光素子の発光を停止させる非発光期間において、

前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧以上の電圧に設定した後、

少なくとも所定の休止期間を間に挟んだ第1及び第2の期間で、それぞれ前記信号レベル保持用コンデンサの蓄積電荷を前記駆動トランジスタにより放電させて前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧に設定し、

続いて前記書込トランジスタをオン動作させて前記信号レベル保持用コンデンサのゲート側電圧を前記階調電圧に設定し、

前記垂直駆動回路は、

前記第1の期間の途中で前記有機EL素子のカソード電圧を立ち上げた後、遅くとも前記第2の期間の途中で発光期間の電圧に立ち下げるにより、前記第1の期間において、前記信号レベル保持用コンデンサの端子間電圧が前記駆動トランジスタのしきい値電圧となる速度を増大させる

ことを特徴とする表示装置。

## 【請求項 2】

前記水平駆動回路は、

所定の固定電圧をそれぞれ間に挟んで前記階調電圧の連続による駆動信号を生成し、

前記垂直駆動回路は、

前記駆動信号が前記固定電圧に設定されている期間で、前記書込トランジスタをオン状態に設定して前記駆動トランジスタのゲート電圧を前記固定電圧に設定することにより、前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧以上の電圧に設定する

ことを特徴とする請求項1に記載の表示装置。

## 【請求項 3】

前記休止期間が、

前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧以上の電圧に設定する期間に統いて、前記駆動信号が前記階調信号に設定される期間である

ことを特徴とする請求項2に記載の表示装置。

## 【請求項 4】

前記垂直駆動回路は、

前記第1の期間、前記休止期間及び前記第2の期間の間、前記駆動トランジスタに電源を供給し、

10

20

30

40

50

前記第1及び第2の期間の間、前記書込トランジスタをオン状態に設定することにより、前記第1及び第2の期間で前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧に設定し、

前記休止期間の間、前記書込トランジスタをオフ状態に設定することにより、前記駆動トランジスタをブートストラップ動作の状態に設定する

ことを特徴とする請求項3に記載の表示装置。

【請求項5】

画素回路をマトリックス状に配置して形成された表示部に対して、前記表示部の信号線及び走査線を介して水平駆動回路及び垂直駆動回路により前記画素回路を駆動することにより、前記表示部で所望の画像を表示する表示装置の駆動方法において、

10

前記画素回路は、

少なくとも発光素子と、

信号レベル保持用コンデンサと、

前記信号レベル保持用コンデンサの両端をゲート及びソースに接続し、前記発光素子のアノードを前記ソースに接続し、前記ゲート及びソース間電圧に応じた駆動電流で前記発光素子を駆動する駆動トランジスタと、

前記垂直駆動回路から出力される書込信号によりオン動作し、前記駆動トランジスタのゲートを前記信号線に接続する書込トランジスタとを有し、

前記駆動方法は、

各画素の階調を示す階調電圧の連続による駆動信号を前記信号線毎に生成し、前記駆動信号を対応する前記信号線に出力する駆動信号出力ステップと、

20

前記発光素子の発光を停止させる非発光期間において、

前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧以上の電圧に設定するしきい値電圧設定の前処理ステップと、

少なくとも所定の休止期間を間に挟んだ第1及び第2の期間で、それぞれ前記信号レベル保持用コンデンサの蓄積電荷を前記駆動トランジスタにより放電させて前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧に設定するしきい値電圧設定ステップと、

続いて前記書込トランジスタをオン動作させて前記信号レベル保持用コンデンサのゲート側電圧を前記階調電圧に設定する階調電圧設定ステップと、

30

前記第1の期間の途中で前記有機EL素子のカソード電圧を立ち上げた後、遅くとも前記第2の期間の途中で発光期間の電圧に立ち下がることにより、前記第1の期間において、前記信号レベル保持用コンデンサの端子間電圧が前記駆動トランジスタのしきい値電圧となる速度を増大させるカソード電圧制御のステップとを有する

ことを特徴とする表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置及び表示装置の駆動方法に関し、例えば有機EL(Electro Luminescence)素子によるアクティブマトリックス型の表示装置に適用することができる。本発明は、信号レベル保持用コンデンサの端子間電圧を駆動トランジスタのしきい値電圧以上に設定した後、複数回の期間に分けて、この信号レベル保持用コンデンサの蓄積電荷を駆動トランジスタにより放電させて信号レベル保持用コンデンサの端子間電圧を駆動トランジスタのしきい値電圧に設定する際に、始めの期間で発光素子のカソード電圧を立ち上げて短時間で信号レベル保持用コンデンサの端子間電圧が駆動トランジスタのしきい値電圧となるように設定した後、カソード電圧を元の電圧に戻して最終的に信号レベル保持用コンデンサの端子間電圧を駆動トランジスタのしきい値電圧に設定することにより、複数回に分けて駆動トランジスタのしきい値電圧のばらつきを補正する場合でも、正しく駆動ト

40

50

ランジスタのしきい値電圧のばらつきを補正することができるようとする。

【背景技術】

【0002】

従来、有機EL素子を用いたアクティブマトリックス型の表示装置は、有機EL素子による画素と有機EL素子を駆動する駆動回路とによる画素回路をマトリックス状に配置して表示部が形成され、この表示部の周囲に配置した水平駆動回路及び垂直駆動回路により各画素回路を駆動して所望の画像を表示している。

【0003】

この有機EL素子を用いた表示装置に関して、特開2005-345722号公報には、有機EL素子を駆動する駆動トランジスタのしきい値電圧のばらつきを補正して各画素の階調を設定することにより、このしきい値電圧のばらつきによる画質劣化を防止し、Nチャンネル型のトランジスタを使用する場合でも、高い画質を確保することが可能な構成が提案されている。また特開2007-133284号公報には、このしきい値電圧のばらつきを補正する処理を複数回に分けて実行する構成が提案されている。この特開2007-133284号公報には、さらに有機EL素子を駆動するトランジスタの移動度のばらつきによる画質劣化を防止する方法も開示されている。

10

【0004】

ここで図4は、この特開2005-345722号公報に開示の表示装置を示す接続図である。この表示装置1は、水平セレクタ(HSEL)2により水平駆動回路3が構成され、またドライブスキャナ(DSCN)4A、ライトスキャナ(WSCN)4B、第1及び第2のオートゼロスキャナ(AZCN1及びAZCN2)4C及び4Dにより垂直駆動回路5が構成される。

20

【0005】

ここで水平セレクタ2は、表示部6の信号線SIGにそれぞれ対応する複数のラッチ回路で入力画像データD1を順次ラッチすることにより、この画像データD1を各信号線SIGに振り分ける。また各信号線SIGに振り分けた画像データD1をそれぞれデジタルアナログ変換処理し、各信号線SIGに接続された各画素の階調を順次示す駆動信号SSigを信号線SIG毎に生成する。水平セレクタ2は、この駆動信号SSigを対応する信号線SIGに出力する。

30

【0006】

ライトスキャナ4A、ドライブスキャナ4B、第1及び第2のオートゼロスキャナ4C及び4Dは、それぞれ図示しない信号生成回路で生成された基準信号を順次転送することにより、各走査線の駆動信号DS、WS、AZ1、AZ2を生成し、この駆動信号DS、WS、AZ1、AZ2をそれぞれ対応する走査線に出力する。

【0007】

表示部6は、所定の画素回路7をマトリックス状に配置して形成される。ここで画素回路7は、信号レベル保持用コンデンサC1の両端をそれぞれゲート及びソースに接続したソースフォロワ回路構成のNMOSトランジスタTR1(以下、駆動トランジスタと呼ぶ)により、電流駆動型の発光素子である有機EL素子8を駆動する。なおここでCpは、有機EL素子8の容量成分である。またVcatは、有機EL素子8のカソード電圧である。

40

【0008】

この駆動トランジスタTR1は、ドライブスキャナ4Bから出力される駆動信号であるドライブ信号DSによりオンオフ動作するNMOSトランジスタTR2を介して、駆動用電源Vccにドレインが接続される。これにより画素回路7は、ドライブ信号DSによるトランジスタTR2のオンオフ制御により駆動トランジスタTR1への電源Vccの供給が制御され、発光、非発光が制御される。

【0009】

またこの駆動トランジスタTR1は、それぞれ第1及び第2のオートゼロスキャナ4C及び4Dから出力される駆動信号である第1及び第2のオートゼロ信号AZ1及びAZ2

50

によりオンオフ動作するN M O SトランジスタT R 3及びT R 4を介して、ゲート及びソースが第1及び第2の基準電源V i n i及びV s s 2に接続される。これにより画素回路7は、これら第1及び第2のオートゼロ信号A Z 1及びA Z 2によるトランジスタT R 3及びT R 4の制御により信号レベル保持用コンデンサC 1の両端電位をそれぞれ基準電圧V i n i及びV s s 2に設定する。

【0010】

また駆動トランジスタT R 1は、ライトスキャナ4 Aから出力される駆動信号である書込み信号W Sによりオンオフ動作するN M O SトランジスタT R 5を介して、ゲートが信号線S I Gに接続される。これにより画素回路7は、この書込み信号W SによるトランジスタT R 5の制御により信号線S I Gに出力される駆動信号S s i gの電圧が信号レベル保持用コンデンサC 1の一端に設定される。

10

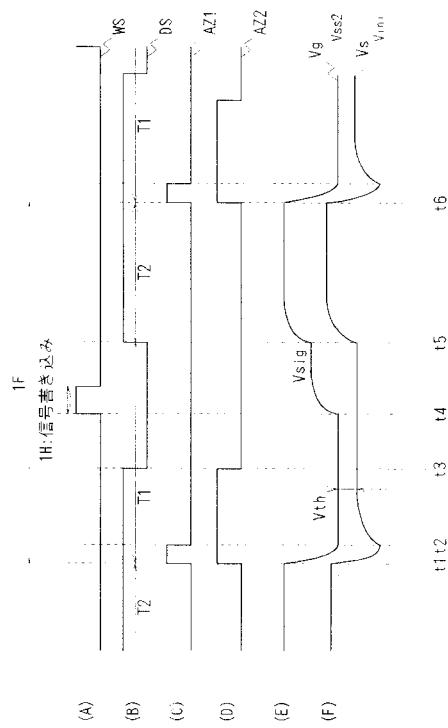

【0011】

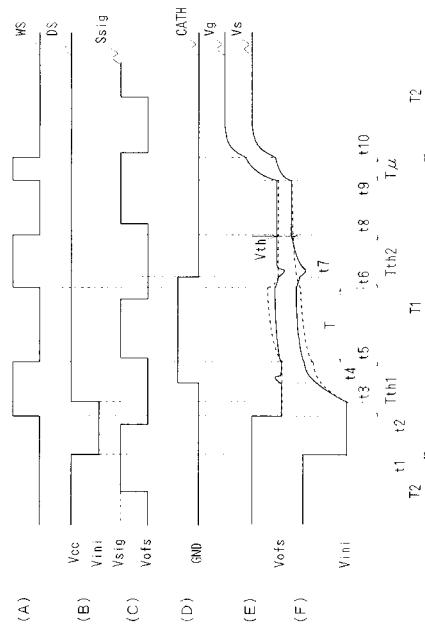

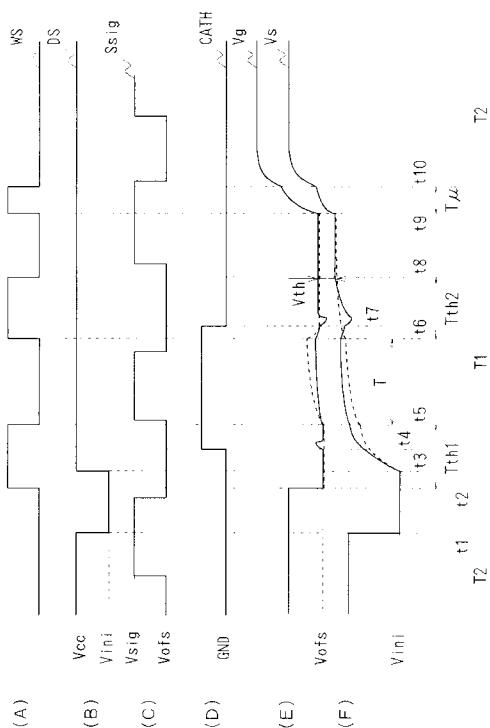

ここで図5は、この画素回路7の動作の説明に供するタイムチャートである。ここで表示部6は、図5(A)において信号書き込みにより駆動トランジスタT R 1への信号線S I Gの接続を示すように、フレーム単位のライン順次により各画素回路7の階調が設定される。各画素回路7は、この階調を設定する1水平走査期間(1 H)の前後、一定の期間が非発光期間T 1に設定され、残りが発光期間T 2に設定される(図5(B))。

【0012】

画素回路7は、非発光期間T 1が時点t 1により開始すると、第1及び第2のオートゼロ信号A Z 1及びA Z 2によりトランジスタT R 3及びT R 4がオン状態に設定され(図5(C)及び(D))、駆動トランジスタT R 1のゲート電圧V g及びソース電圧V s(図5(E)及び(F))がそれぞれ基準電圧V s s 2及びV i n iに設定される。ここで基準電圧V s s 2及びV i n iは、電位差V s s 2 - V i n iが駆動トランジスタT R 1のしきい値電圧V t hより十分に大きな電圧に設定される。これにより画素回路7は、信号レベル保持用コンデンサC 1の両端電位差が駆動トランジスタT R 1のしきい値電圧V t hより大きな電圧に設定される。

20

【0013】

続いて画素回路7は、時点t 2において、第1のオートゼロ信号A Z 1が立ち下げられ、駆動トランジスタT R 1のソース側トランジスタT R 3がオフ状態に設定される。これにより画素回路7は、駆動トランジスタT R 1のゲートソース間電圧V g sに応じた駆動電流が駆動トランジスタT R 1のソースから流出する。ここで駆動トランジスタT R 1のゲート側基準電圧V s s 2は、この駆動トランジスタT R 1による駆動電流が信号レベル保持用コンデンサC 1の有機E L素子8側端を充電するように、すなわち有機E L素子8のカソード電圧V c a tに比して有機E L素子8のアノード電圧を十分に低い電圧に保持する電圧に設定される。これにより画素回路7は、信号レベル保持用コンデンサC 1の蓄積電荷が駆動トランジスタT R 1により放電して信号レベル保持用コンデンサC 1の端子間電圧が徐々に低下し、この端子間電圧が駆動トランジスタT R 1のしきい値電圧V t hとなると、駆動トランジスタT R 1がオフ状態に動作を切り換え、信号レベル保持用コンデンサC 1の端子間電圧の低下が停止する。これにより画素回路7は、信号レベル保持用コンデンサC 1の両端電位差が駆動トランジスタT R 1のしきい値電圧V t hに設定される。

30

【0014】

画素回路7は、続く時点t 3において、第2のオートゼロ信号A Z 2が立ち下げられて、駆動トランジスタT R 1のゲート側トランジスタT R 4がオフ状態に設定され、またドライブ信号D Sが立ち下げられて、駆動トランジスタT R 1への電源V c cの供給が停止される。また続く時点t 4で、書き込み信号W Sが立ち上げられてトランジスタT R 5がオン状態に設定され、これにより駆動トランジスタT R 1のゲートが信号線S I Gに接続される。画素回路7は、所定のタイミングで書き込み信号W Sが立ち下げられてトランジスタT R 5がオフ状態に設定され、これにより信号線S I Gに出力される駆動信号S s i gの電圧V s i gが信号レベル保持用コンデンサC 1の一端にホールドされる。これにより画

40

50

素回路 7 は、信号レベル保持用コンデンサ C 1 に設定された駆動トランジスタ TR 1 のしきい値電圧 V th により補正して、信号レベル保持用コンデンサ C 1 の端子間電圧が駆動信号 Sig の電圧 V sig に応じた電圧に設定される。

【0015】

画素回路 7 は、発光期間 T 2 の開始時点 t 5 でトランジスタ TR 1 への電源 Vcc の供給が開始される。これにより画素回路 7 は、信号レベル保持用コンデンサ C 1 の端子間電圧によるゲートソース間電圧 Vgs により有機 EL 素子 8 を電流駆動し、有機 EL 素子 8 の容量 Cp によるブートストラップ動作により有機 EL 素子 8 を発光させる。なおここでこの駆動トランジスタ TR 1 による有機 EL 素子 8 の駆動電流 Ids は、次式により表される。ここで Vgs は、駆動トランジスタ TR 1 のゲートソース間電圧であり、信号レベル保持用コンデンサ C 1 の両端電圧差である。また  $\mu$  はトランジスタ TR 1 の移動度、W はトランジスタ TR 1 のチャンネル幅、L はトランジスタ TR 1 のチャンネル長、Cox はトランジスタ TR 1 の単位面積当たりのゲート絶縁膜の容量、Vth はトランジスタ TR 1 のしきい値電圧である。

10

【0016】

【数1】

$$I_{ds} = \frac{1}{2} \frac{W}{L} \mu C_{ox} (V_{gs} - V_{th})^2 \quad \dots \dots (1)$$

20

【0017】

この図 4 及び図 5 の構成によれば、駆動トランジスタ TR 1 のしきい値電圧 Vth で補正して信号線 SIG に出力される駆動信号 Sig の電圧 Vsig を信号レベル保持用コンデンサ C 1 に設定することにより、駆動トランジスタ TR 1 のしきい値電圧 Vth のばらつきによる画質の劣化を防止することができる。

【0018】

ところでこの図 4 に示す構成では、事前に、信号レベル保持用コンデンサ C 1 の両端電圧を基準電位 Vin 1 及び Vss 2 に設定して信号レベル保持用コンデンサ C 1 の両端電位差 Vss 2 - Vin 1 を駆動トランジスタ TR 1 のしきい値電圧 Vth より十分に大きな電圧に設定した後、信号レベル保持用コンデンサ C 1 の両端電位差を駆動トランジスタ TR 1 のしきい値電圧 Vth に設定する。

30

【0019】

この事前に、信号レベル保持用コンデンサ C 1 の両端電圧を基準電位 Vin 1 及び Vss 2 に設定する処理のうち、駆動トランジスタ TR 1 のゲート側電圧 Vss 2 の設定については、トランジスタ TR 5 を介して信号線 SIG により実行することもでき、この場合、トランジスタ TR 4 を省略して画素回路 7 の構成を簡略化することができる。また駆動トランジスタ TR 1 のソース側電圧 Vin 1 の設定については、電源電圧 Vcc の立ち下げにより設定できると考えられる。このようにすれば画素回路を構成するトランジスタ数を低減することができ、表示部を一段と高解像度化することができると考えられる。またこの場合に、特開 2007-133284 号公報に開示の手法を適用して、信号レベル保持用コンデンサ C 1 に駆動トランジスタ TR 1 のしきい値電圧 Vth を設定する処理を複数回に分けて実行すれば、高解像度化により動作周波数を高周波数化する場合でも、しきい値電圧 Vth を設定する時間を十分に確保することができ、駆動トランジスタ TR 1 のしきい値電圧 Vth のばらつきによる画質劣化を確実に防止できると考えられる。また併せて特開 2007-133284 号公報に開示の駆動トランジスタの移動度のばらつきによる画質の劣化を防止する手法を適用して、一段と画質を向上できると考えられる。

40

【0020】

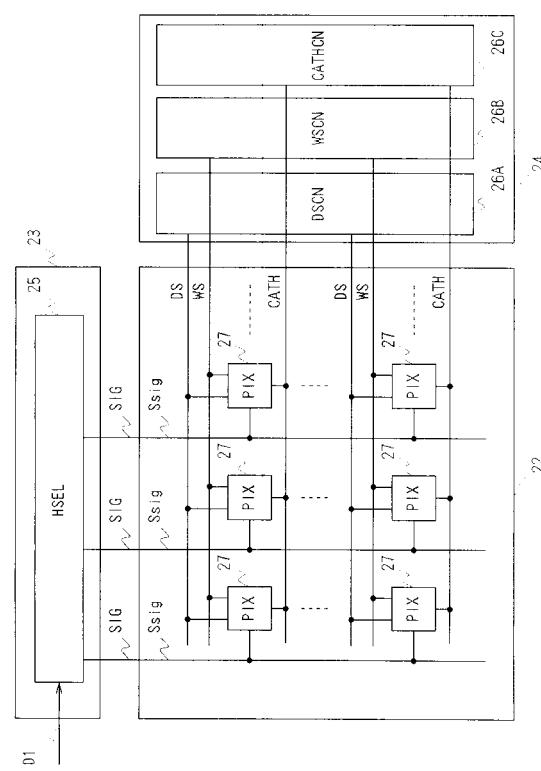

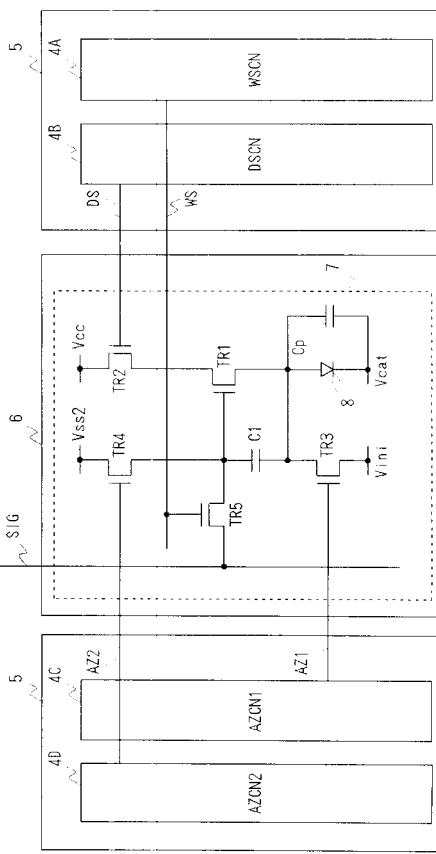

図 6 は、これらの点を考慮して考えられる表示装置を示すブロック図である。この表示

50

装置11は、所定の絶縁基板上に表示部12が作成され、この表示部12の周囲に水平駆動回路13及び垂直駆動回路14が設けられる。水平駆動回路13には、水平セレクタ(HSEL)15が設けられ、また垂直駆動回路14には、ライトスキャナ(WSCN)16A、ドライブスキャナ(DSCN)16Bが設けられる。

【0021】

水平セレクタ(HSEL)15は、水平セレクタ2と同様にして各信号線SIGに画像データD1を振り分けてデジタルアナログ変換処理する。水平セレクタ15は、所定の固定電圧Vofsとこのデジタルアナログ変換結果とを交互に出力することにより、固定電圧Vofsを間に挟んで、信号線SIGに接続された各画素の階調を示す階調電圧Vsigの連続による駆動信号SSigを各信号線SIGに出力する(図8(C)参照)。

10

【0022】

ライトスキャナ16A、ドライブスキャナ16Bは、それぞれ図示しない信号生成回路で生成された基準信号を順次転送することにより、各走査線の駆動信号DS、WSを生成し、この駆動信号DS、WSをそれぞれ対応する走査線に出力する。

【0023】

表示部12は、画素回路(PIX)17をマトリックス状に配置して作成される。ここで図7に示すように、画素回路17は、信号レベル保持用コンデンサC1への基準電圧の設定に係るトランジスタTR3及びTR4が省略された点、このトランジスタTR3及びTR4の省略に関連する構成が異なる点を除いて、図4の画素回路7と同一に構成される。

20

【0024】

図8に示すように、各画素回路17は、有機EL素子8の発光を停止させる非発光期間T1が時点t1で開始すると、ドライブ信号DSの電圧が発光期間T2の電圧Vccから基準電圧設定用電圧Viniに立ち下げられる(図8(B))。ここでこの基準電圧設定用電圧Viniは、有機EL素子8のしきい値電圧に有機EL素子8のカソード電圧Vcatを加算した電圧より低い電圧に設定される。これにより画素回路17は、駆動トランジスタTR1の駆動信号DS側がソースとして機能し、有機EL素子8のアノード電圧が立ち下がり、有機EL素子8が発光を停止する。また駆動トランジスタTR1を介して信号レベル保持用コンデンサC1の有機EL素子8側から蓄積電荷が放電し、これにより有機EL素子8のアノード電圧が立ち下がって信号レベル保持用コンデンサC1の有機EL素子8側端の電圧(駆動トランジスタTR1のソース電圧Vs)(図8(E))が電圧Viniに設定される。

30

【0025】

続いて画素回路17は、駆動信号SSigにより信号線SIGが所定電圧Vofsに立ち下がると、時点t2で書き込み信号WSによりトランジスタTR5がオン状態に切り換える(図8(A)及び(C))。これにより画素回路17は、駆動トランジスタTR1のゲート電圧Vgがこの信号線SIGの電圧Vofsに設定され、信号レベル保持用コンデンサC1の端子間電圧がVofs-Viniに設定される。ここで画素回路17では、この端子間電圧Vofs-Viniが駆動トランジスタTR1のしきい値電圧をVthより大きくなるように電圧Vofs、Viniが設定される。これにより画素回路17では、時点t1から時点t2までの期間で、信号レベル保持用コンデンサC1の端子間電圧が駆動トランジスタTR1のしきい値電圧Vthより大きな電圧に設定され、信号レベル保持用コンデンサC1に駆動トランジスタTR1のしきい値電圧Vthを設定するための準備処理が実行される。

40

【0026】

続いて画素回路17は、駆動信号SSigが固定電位Vofsに保持されている期間の時点t3で、トランジスタTR5をオン状態に保持したままの状態で、ドライブ信号DSが発光期間T2の電圧Vccに立ち上げられて駆動トランジスタTR1への電源の供給が開始される(図8(B))。また続いて信号線SIGの信号レベルが階調電圧Vsigに設定される直前の時点t4で、書き込み信号WSによりトランジスタTR5がオフ状態に切

50

り換えられる。

【0027】

これにより画素回路17は、信号レベル保持用コンデンサC1の端子間電圧が駆動トランジスタTR1のしきい値電圧V<sub>th</sub>より大きい場合であることを条件に、時点t3から時点t4までの期間T<sub>th1</sub>の間、駆動トランジスタTR1を介して電源V<sub>cc</sub>により信号レベル保持用コンデンサC1の有機EL素子8側端に充電電流が流れ、駆動トランジスタTR1のソース電圧V<sub>s</sub>が徐々に上昇する(図8(E))。その結果、画素回路17は、信号レベル保持用コンデンサC1の端子間電圧が徐々に駆動トランジスタTR1のしきい値電圧V<sub>th</sub>に接近する。なお画素回路17は、固定電位V<sub>ofs</sub>の設定によりこのように有機EL素子8側端の電圧V<sub>s</sub>が上昇しても有機EL素子8が発光しないように設定される。

10

【0028】

画素回路17は、時点t4で書き込み信号WSによりトランジスタTR5がオフ状態に切り換えられると、有機EL素子8の容量C<sub>p</sub>によるブートストラップ動作を開始し、駆動トランジスタTR1のゲート電圧V<sub>g</sub>及びソース電圧V<sub>s</sub>が徐々に上昇する(図8(D)及び(E))。

【0029】

画素回路17は、一定時間経過して再び信号線SIGの信号レベルが電圧V<sub>ofs</sub>に設定されると、時点t5で書き込み信号WSによりトランジスタTR5がオン状態に切り換えられて駆動トランジスタTR1のゲートが信号線SIGに接続される。また続いて信号線SIGの信号レベルが階調電圧V<sub>sig</sub>に設定される直前の時点t6で、書き込み信号WSによりトランジスタTR5がオフ状態に切り換えられる。

20

【0030】

これにより画素回路17は、時点t5から時点t6までの期間T<sub>th2</sub>の間、期間T<sub>th1</sub>の場合と同様にして、信号レベル保持用コンデンサC1の端子間電圧が徐々に駆動トランジスタTR1のしきい値電圧V<sub>th</sub>に接近し、信号レベル保持用コンデンサC1の端子間電圧が駆動トランジスタTR1のしきい値電圧V<sub>th</sub>となると、ソース電圧V<sub>s</sub>の上昇が停止する。これにより画素回路17は、信号レベル保持用コンデンサC1の端子間電圧が駆動トランジスタTR1のしきい値電圧V<sub>th</sub>に設定される。なおこれによりこの図8の例では、期間T<sub>th1</sub>と期間T<sub>th2</sub>との2回の処理で、信号レベル保持用コンデンサC1の端子間電圧が駆動トランジスタTR1のしきい値電圧V<sub>th</sub>に設定されるものの、この繰り返しの回数は、信号レベル保持用コンデンサC1の端子間電圧が駆動トランジスタTR1のしきい値電圧V<sub>th</sub>となるに十分な回数だけ繰り返すことができ、3回以上としてもよい。

30

【0031】

画素回路17は、続いて駆動信号SSIGが当該画素回路17の階調電圧V<sub>sig</sub>に設定されている時点t7で書き込み信号WSが立ち上げられてトランジスタTR5がオン状態に設定され、これにより駆動トランジスタTR1のゲートが信号線SIGに接続される。また一定期間T<sub>μ</sub>が経過した時点t8で、書き込み信号WSが立ち下げられ、これにより信号線SIGに出力されている駆動信号SSIGの階調電圧V<sub>sig</sub>が信号レベル保持用コンデンサC1の一端にホールドされる。これにより画素回路17は、信号レベル保持用コンデンサC1に設定された駆動トランジスタTR1のしきい値電圧V<sub>th</sub>により補正して、信号レベル保持用コンデンサC1の端子間電圧が階調電圧V<sub>sig</sub>に応じた電圧に設定される。これによりこの表示装置11では、駆動トランジスタTR1のしきい値電圧V<sub>th</sub>のばらつきによる画質劣化を防止することができる。

40

【0032】

ここでこの時点t7から時点t8までの期間T<sub>μ</sub>においては、駆動トランジスタTR1のゲート電圧V<sub>g</sub>を階調電圧V<sub>sig</sub>に設定した状態で駆動トランジスタTR1に電源V<sub>cc</sub>を供給していることから、駆動トランジスタTR1は、ゲートソース間電圧V<sub>gs</sub>に応じてソース電圧V<sub>s</sub>が徐々に上昇することになる。またここでこのソース電圧V<sub>s</sub>の上

50

昇速度は、(1)により駆動トランジスタTR1の移動度が大きい場合程、早くなる。またソース電圧Vsが上昇すると、ゲートソース間電圧Vgsが低下することにより、ソース電流が流れ難くなる。

#### 【0033】

これにより画素回路17は、この一定期間T<sub>μ</sub>により、移動度が大きい駆動トランジスタ程、信号レベル保持用コンデンサC1の端子間電圧が低下し、移動度のばらつきを補正して画質の劣化が防止される。

#### 【0034】

画素回路17は、時点t8で書き込み信号WSが立ち下げられると、発光期間T2が開始し、信号レベル保持用コンデンサC1の端子間電圧によるゲートソース間電圧Vgsにより有機EL素子8を電流駆動する。なおこの発光期間T2において、画素回路17は、有機EL素子8の容量Cpによる駆動トランジスタTR1のブートストラップ動作により、期間T<sub>μ</sub>で設定された駆動トランジスタTR1のゲート電圧Vg及びソース電圧Vsが徐々に上昇して有機EL素子8が発光を開始し、やがてこれらゲート電圧Vg及びソース電圧Vsの上昇が停止してこれらゲート電圧Vg及びソース電圧Vsが一定電圧に保持される。

10

#### 【0035】

ところで期間Tth1及びTth2間の時点t4から時点t5までの間、画素回路17では、駆動トランジスタTR1のブートストラップ動作により、駆動トランジスタTR1のソース電流で有機EL素子8の寄生容量Cpを充電し、その結果、駆動トランジスタTR1のソース電圧Vsが上昇する。ここで画素回路17では、このソース電圧Vsの上昇により駆動トランジスタTR1のゲート電圧Vgも上昇する。従って時点t4から時点t5までの間、駆動トランジスタTR1のゲートソース間電圧は一定電圧に保持されることになる。

20

#### 【0036】

しかしながら時点t4から時点t5までの期間の間の駆動トランジスタのソース電圧Vsの電圧上昇により、ソース電圧Vsが電圧Vof<sub>s</sub>-Vth以上に上昇してしまう場合も予測される。この場合には時点t5で続く2回目の期間Tth1を開始した時点で、信号レベル保持用コンデンサC1の端子間電圧が駆動トランジスタTR1のしきい値電圧Vth以下となり、その結果、画素回路17では、駆動トランジスタTR1のしきい値電圧のばらつきを正しく補正することができ困難になる問題があり、表示画像の画質が劣化することになる。

30

【特許文献1】特開2005-345722号公報

【特許文献2】特開2007-133284号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0037】

本発明は以上の点を考慮してなされたもので、信号レベル保持用コンデンサの端子間電圧を駆動トランジスタのしきい値電圧以上に設定した後、複数回に分けて駆動トランジスタのしきい値電圧のばらつきを補正する場合でも、正しく駆動トランジスタのしきい値電圧のばらつきを補正することができる表示装置及び表示装置の駆動方法を提案しようとするものである。

40

#### 【課題を解決するための手段】

#### 【0038】

上記の課題を解決するため請求項1の発明は、画素回路をマトリックス状に配置して形成された表示部に対して、前記表示部の信号線及び走査線を介して水平駆動回路及び垂直駆動回路により前記画素回路を駆動することにより、前記表示部で所望の画像を表示する表示装置に適用して、前記画素回路は、少なくとも発光素子と、信号レベル保持用コンデンサと、前記信号レベル保持用コンデンサの両端をゲート及びソースに接続し、前記発光素子のアノードを前記ソースに接続し、前記ゲート及びソース間電圧に応じた駆動電流で

50

前記発光素子を駆動する駆動トランジスタと、前記垂直駆動回路から出力される書込信号によりオン動作し、前記駆動トランジスタのゲートを前記信号線に接続する書込トランジスタとを有し、前記水平駆動回路は、各画素の階調を示す階調電圧の連続による駆動信号を前記信号線毎に生成し、前記駆動信号を対応する前記信号線に出力し、前記垂直駆動回路は、前記発光素子の発光を停止させる非発光期間において、前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧以上の電圧に設定した後、少なくとも所定の休止期間を間に挟んだ第1及び第2の期間で、それぞれ前記信号レベル保持用コンデンサの蓄積電荷を前記駆動トランジスタにより放電させて前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧に設定し、続いて前記書込トランジスタをオン動作させて前記信号レベル保持用コンデンサのゲート側電圧を前記階調電圧に設定し、前記垂直駆動回路は、前記第1の期間の途中で前記有機EL素子のカソード電圧を立ち上げた後、遅くとも前記第2の期間の途中で発光期間の電圧に立ち下げるにより、前記第1の期間において、前記信号レベル保持用コンデンサの端子間電圧が前記駆動トランジスタのしきい値電圧となる速度を増大させる。

#### 【0039】

また請求項5の発明は、画素回路をマトリックス状に配置して形成された表示部に対して、前記表示部の信号線及び走査線を介して水平駆動回路及び垂直駆動回路により前記画素回路を駆動することにより、前記表示部で所望の画像を表示する表示装置の駆動方法に適用して、前記画素回路は、少なくとも発光素子と、信号レベル保持用コンデンサと、前記信号レベル保持用コンデンサの両端をゲート及びソースに接続し、前記発光素子のアノードを前記ソースに接続し、前記ゲート及びソース間電圧に応じた駆動電流で前記発光素子を駆動する駆動トランジスタと、前記垂直駆動回路から出力される書込信号によりオン動作し、前記駆動トランジスタのゲートを前記信号線に接続する書込トランジスタとを有し、前記駆動方法は、各画素の階調を示す階調電圧の連続による駆動信号を前記信号線毎に生成し、前記駆動信号を対応する前記信号線に出力する駆動信号出力ステップと、前記発光素子の発光を停止させる非発光期間において、前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧以上の電圧に設定するしきい値電圧設定の前処理ステップと、少なくとも所定の休止期間を間に挟んだ第1及び第2の期間で、それぞれ前記信号レベル保持用コンデンサの蓄積電荷を前記駆動トランジスタにより放電させて前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧に設定するしきい値電圧設定ステップと、続いて前記書込トランジスタをオン動作させて前記信号レベル保持用コンデンサのゲート側電圧を前記階調電圧に設定する階調電圧設定ステップと、前記第1の期間の途中で前記有機EL素子のカソード電圧を立ち上げた後、遅くとも前記第2の期間の途中で発光期間の電圧に立ち下げるにより、前記第1の期間において、前記信号レベル保持用コンデンサの端子間電圧が前記駆動トランジスタのしきい値電圧となる速度を増大させるカソード電圧制御のステップとを有するようとする。

#### 【0040】

請求項1又は請求項5の構成によれば、カソード電圧の立ち上げにより従来に比して短い時間で信号レベル保持用コンデンサの端子間電圧を駆動トランジスタTR1のしきい値電圧に設定した後、続く第2の期間で、カソード電圧の立ち下げによる信号レベル保持用コンデンサの端子間電圧の変化等を補正して、最終的に、信号レベル保持用コンデンサの端子間電圧を駆動トランジスタTR1のしきい値電圧に設定することができる。従って信号レベル保持用コンデンサの端子間電圧を駆動トランジスタのしきい値電圧以上に設定した後、複数回に分けて駆動トランジスタのしきい値電圧のばらつきを補正する場合でも、正しく駆動トランジスタのしきい値電圧のばらつきを補正することができる。

#### 【発明の効果】

#### 【0041】

本発明によれば、信号レベル保持用コンデンサの端子間電圧を駆動トランジスタのしきい値電圧以上に設定した後、複数回に分けて駆動トランジスタのしきい値電圧のばらつき

10

20

30

40

50

を補正する場合でも、正しく駆動トランジスタのしきい値電圧のばらつきを補正することができる。

【発明を実施するための最良の形態】

【0042】

以下、適宜図面を参照しながら本発明の実施例を詳述する。

【実施例1】

【0043】

(1) 実施例の構成

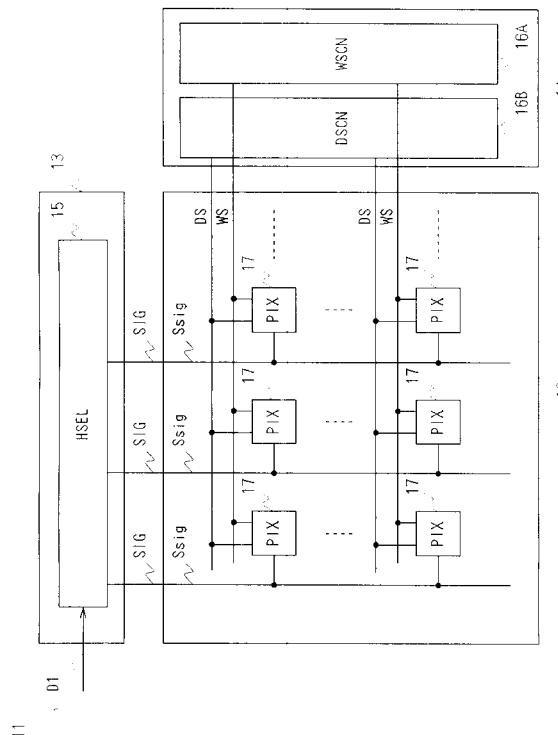

図2は、本発明の実施例1の表示装置を示すブロック図である。この表示装置21において、図6の表示装置と同一の構成は、対応する符号を付して示し、重複した説明は省略する。この表示装置21は、所定の絶縁基板上に表示部22が作成され、この表示部22の周囲に水平駆動回路23及び垂直駆動回路24が設けられる。

10

【0044】

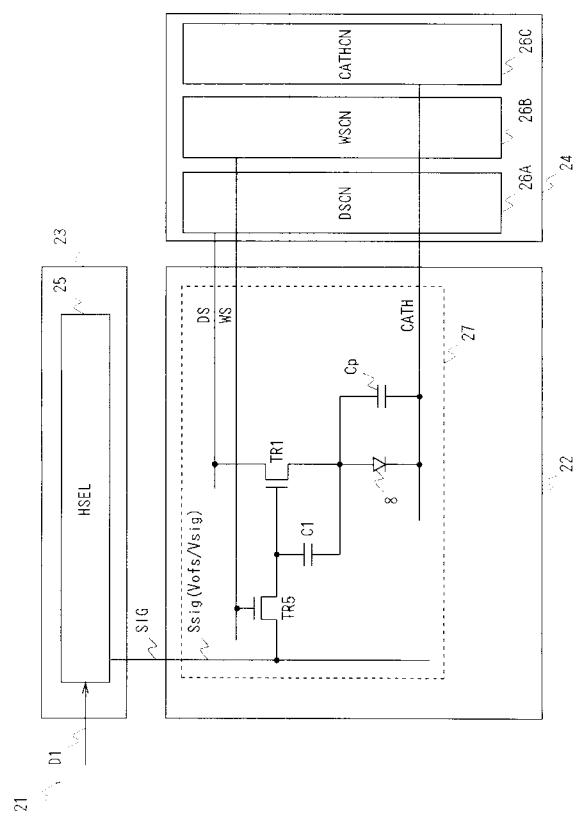

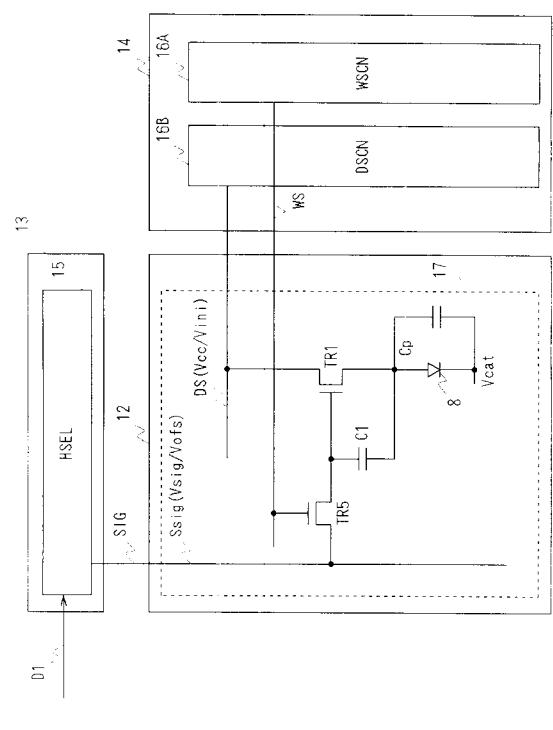

ここで水平駆動回路23は、水平セレクタ(HSEL)25を有し、水平セレクタ25は、水平セレクタ15と一緒に、階調電圧Vsigを間に挟んだ階調電圧Vsigの連続による駆動信号SSigを各信号線SIGに出力する(図1(D))。

【0045】

垂直駆動回路24は、ドライブスキャナ(DSCN)26A、ライトスキャナ(WSCN)26B、カソードスキャナ(CATHCN)26Cを有し、これらドライブスキャナ26A、ライトスキャナ26B、カソードスキャナ26Cは、それぞれ所定の基準信号を順次転送して各画素回路の駆動信号DS、WS、CATHを生成し、この駆動信号DS、WS、CATHを表示部22の走査線に出力する。

20

【0046】

表示部22は、画素回路27をマトリックス状に配置して形成される。ここで画素回路27は、図3に示すように、有機EL素子8のカソード端が走査線に接続されて、走査線毎にカソードスキャナ26Cにより制御される点を除いて、図7の画素回路17と一緒に構成される。

【0047】

これにより画素回路27は、図1に示すように、非発光期間T1が時点t1により開始すると、ドライブ信号DSが立ち下げられて駆動トランジスタTR1による駆動トランジスタTR1への電源Vccの供給が停止制御され(図1(A))、これにより有機EL素子8の発光が停止する(図1(E)及び(F))。また画素回路27は、駆動信号SSigにより信号線SIGが所定電圧Vofsに立ち下がると、時点t2で書き込み信号WSによりトランジスタTR5がオン状態に切り換えられ(図1(A)及び(C))、これにより信号レベル保持用コンデンサC1の端子間電圧が駆動トランジスタTR1のしきい値電圧Vthより大きい電圧に設定され、信号レベル保持用コンデンサC1の端子間電圧を駆動トランジスタTR1のしきい値電圧Vthに設定するための準備処理が実行される。

30

【0048】

続いて画素回路27は、駆動信号SSigが固定電位Vofsに保持されている期間の時点t3で、トランジスタTR5をオン状態に保持したままの状態で、ドライブ信号DSが発光期間T2の電圧Vccに立ち上げられて駆動トランジスタTR1への電源の供給が開始される(図1(B))。また続いて信号線SIGの信号レベルが階調電圧Vsigに設定される直前の時点t5で、書き込み信号WSによりトランジスタTR5がオフ状態に切り換えられ、これにより時点t3から時点t5までの期間Tth1で、1回目の信号レベル保持用コンデンサC1の端子間電圧を駆動トランジスタTR1のしきい値電圧Vthに設定する処理が実行される。

40

【0049】

また画素回路27は、再び信号線SIGの信号レベルが電圧Vofsに設定されると、時点t6で書き込み信号WSによりトランジスタTR5がオン状態に切り換えられて駆動トランジスタTR1のゲートが信号線SIGに接続される。また続いて信号線SIGの信号

50

レベルが階調電圧  $V_{sig}$  に設定される直前の時点  $t_8$  で、書き込み信号  $WS$  によりトランジスタ  $TR_5$  がオフ状態に切り換えられる。

【0050】

これにより画素回路 27 は、時点  $t_6$  から時点  $t_8$  までの期間  $T_{th2}$  の間、2回目の信号レベル保持用コンデンサ  $C_1$  の端子間電圧を駆動トランジスタ  $TR_1$  のしきい値電圧  $V_{th}$  に設定する処理が実行される。

【0051】

画素回路 27 は、続いて駆動信号  $S_{sig}$  が当該画素回路 27 の階調電圧  $V_{sig}$  に設定されている時点  $t_9$  で書き込み信号  $WS$  が立ち上げられてトランジスタ  $TR_5$  がオン状態に設定された後、一定期間  $T_{\mu}$  が経過した時点  $t_{10}$  で、書き込み信号  $WS$  が立ち下げられ、これにより信号レベル保持用コンデンサ  $C_1$  に設定された駆動トランジスタ  $TR_1$  のしきい値電圧  $V_{th}$  により補正して、さらには駆動トランジスタ  $TR_1$  の移動度のばらつきを補正して、信号レベル保持用コンデンサ  $C_1$  の端子間電圧が階調電圧  $V_{sig}$  に応じた電圧に設定される。

10

【0052】

画素回路 27 は、時点  $t_{10}$  で書き込み信号  $WS$  が立ち下げられると、発光期間  $T_2$  が開始し、信号レベル保持用コンデンサ  $C_1$  の端子間電圧によるゲートソース間電圧  $V_{gs}$  により有機 EL 素子 8 を電流駆動する。

20

【0053】

画素回路 27 は、このように期間  $T_{th1}$  と期間  $T_{th2}$  の2回に分けて信号レベル保持用コンデンサ  $C_1$  の端子間電圧を駆動トランジスタ  $TR_1$  のしきい値電圧  $V_{th}$  に設定するようにして、1回目の期間  $T_{th1}$  の途中で、カソードスキャナ  $26C$  により有機 EL 素子 8 のカソード電圧が立ち上げられる（図 1 (D)）。これにより画素回路 27 は、駆動トランジスタ  $TR_1$  のゲートソース間電圧  $V_{gs}$  が低減され、少なくともこの期間  $T_{th1}$  で信号レベル保持用コンデンサ  $C_1$  の端子間電圧がほぼ駆動トランジスタ  $TR_1$  のしきい値電圧  $V_{th}$  となるように設定される。

20

【0054】

その後、画素回路 27 は、続いて信号レベル保持用コンデンサ  $C_1$  への駆動トランジスタ  $TR_1$  のしきい値電圧  $V_{th}$  の設定処理を休止する期間である、駆動信号  $S_{sig}$  が階調電圧  $V_{sig}$  に設定される期間の間、有機 EL 素子 8 のカソード電圧が立ち上げられた状態に保持され、続いて駆動信号  $S_{sig}$  が固定電圧  $V_{off}$  に設定される期間の途中で、発光期間  $T_2$  の電圧に戻される。

30

【0055】

(2) 実施例の動作

以上の構成において、この表示装置 21 では（図 2）、水平駆動回路 23 及び垂直駆動回路 24 による表示部 22 の駆動により順次ライン単位で表示部 22 の画素回路 27 に信号線  $SIG$  の階調電圧  $V_{sig}$  が設定されると共に、この設定された階調電圧  $V_{sig}$  により各画素回路 27 の有機 EL 素子 8 が発光し、所望の画像が表示部 22 で表示される。

【0056】

すなわちこの表示装置 21 では、非発光期間  $T_1$  において（図 3）、各画素回路 27 に設けられた信号レベル保持用コンデンサ  $C_1$  の一端が信号線  $SIG$  の階調電圧  $V_{sig}$  に設定され、発光期間  $T_2$  において、この信号レベル保持用コンデンサ  $C_1$  の端子間電圧によるゲートソース間電圧  $V_{gs}$  により駆動トランジスタ  $TR_1$  で有機 EL 素子 8 が駆動される。これによりこの表示装置では、信号線  $SIG$  の階調電圧  $V_{sig}$  に応じた発光輝度で各画素回路 27 の有機 EL 素子 8 が発光する。

40

【0057】

表示装置 21 は、この階調電圧  $V_{sig}$  の設定に先立って、非発光期間  $T_1$  が開始すると、始めに信号レベル保持用コンデンサ  $C_1$  の両端電圧差が駆動トランジスタ  $TR_1$  のしきい値電圧  $V_{th}$  以上の電圧に設定された後、この信号レベル保持用コンデンサ  $C_1$  の蓄積電荷が駆動トランジスタ  $TR_1$  により放電されて信号レベル保持用コンデンサ  $C_1$  の端

50

子間電圧が駆動トランジスタTR1のしきい値電圧に設定される。表示装置21は、その後、駆動トランジスタTR1のゲートが信号線SIGに接続されて信号レベル保持用コンデンサC1の一端の電圧が階調電圧Vsigに設定されることにより、駆動トランジスタTR1のしきい値電圧Vthにより補正して信号レベル保持用コンデンサC1の端子間電圧が階調電圧Vsigに対応する電圧に設定される。これにより表示装置21では、駆動トランジスタTR1のしきい値電圧のばらつきによる画質劣化が有効に回避される。また階調電圧Vsigを設定する際に一定期間Tμの間、信号線SIGに接続されて駆動トランジスタTR1に電源が供給され、これにより信号レベル保持用コンデンサC1の端子間電圧が駆動トランジスタTR1の移動度により補正されて、駆動トランジスタTR1の移動度のばらつきによる画質劣化が防止される。

10

## 【0058】

またさらに画素回路27では、信号レベル保持用コンデンサC1の端子間電圧を駆動トランジスタTR1のしきい値電圧Vth以上の電圧に設定した後、2回の期間Tth1及びTth2に分けて、この信号レベル保持用コンデンサC1の端子間電圧が駆動トランジスタTR1により放電されて駆動トランジスタTR1のしきい値電圧に設定され、これにより高解像度化により動作周波数を高周波数化した場合でも、しきい値電圧Vthを設定する時間を十分に確保して、駆動トランジスタTR1のしきい値電圧Vthのばらつきによる画質劣化を確実に防止することができる。

20

## 【0059】

しかしながらこのように複数回の期間に分けて信号レベル保持用コンデンサC1の端子間電圧を駆動トランジスタTR1により放電して、信号レベル保持用コンデンサC1の端子間電圧を駆動トランジスタTR1のしきい値電圧に設定する場合、1回目の期間Tth1の期間で、信号レベル保持用コンデンサC1の端子間電圧を駆動トランジスタTR1のしきい値電圧Vthに十分に近づけることが困難な場合も発生する。この場合には、これら期間Tth1及びTth2の間の休止期間における駆動トランジスタTR1のブーストアップ動作により駆動トランジスタTR1のソース電圧Vsが電圧Vofs-Vth以上にまで上昇し、結局、信号レベル保持用コンデンサC1の端子間電圧を正しく駆動トランジスタTR1のしきい値電圧に設定することが困難になる場合も発生する恐れがある。

## 【0060】

そこでこの実施例では、1回目の期間Tth1の途中で、カソードスキャナ26Cにより有機EL素子8のカソード電圧が立ち上げられ、強制的に信号レベル保持用コンデンサC1の端子間電圧が低減され、この1回目の期間Tth1で信号レベル保持用コンデンサC1の端子間電圧がほぼ駆動トランジスタTR1のしきい値電圧Vthに設定される。

30

## 【0061】

すなわち有機EL素子8のカソード電圧をVcatだけ立ち上げると、駆動トランジスタTR1のゲートソース間電圧Vgsは、次式により示すように変化する。

## 【0062】

## 【数2】

40

$$V_{gs} = V_g - (V_s + \Delta V_{cat} \times C_p / (C_p + C_1))$$

$$= V_{ofs} - (V_s + \Delta V_{cat} \times C_p / (C_p + C_1)) \quad \dots \dots (2)$$

## 【0063】

なおゲート電圧Vgは、カソード電圧の上昇により瞬間的に上昇するものの、信号線SIGを介して固定電位Vofsに設定されていることにより、即座に元の固定電位Vofsに戻る。これに対して図6について上述した画素回路17では、駆動トランジスタTR

50

1のゲートソース間電圧  $V_{g_s}$  は、次式により表される。

【0064】

【数3】

$$V_{g_s} = V_g - V_s \quad \dots \dots (3)$$

【0065】

これによりこの実施例によれば、短時間で、信号レベル保持用コンデンサC1の端子間電圧を駆動トランジスタTR1のしきい値電圧  $V_{th}$  に設定できることが判る。なお図1においては、破線により図8の例によるゲート電圧  $V_g$ 、ソース電圧  $V_s$  を示す。

10

【0066】

さらに画素回路27は、休止期間の間もカソード電圧を立ち上げた状態に保持され、これにより休止期間におけるソース電圧  $V_s$  の上昇が抑制される。また続く2回目の期間  $T_{th2}$  で、カドード電圧が元の発光期間  $T_2$  の電圧に戻され、その結果この期間  $T_{th2}$  の間で最終的に信号レベル保持用コンデンサC1の端子間電圧が駆動トランジスタTR1のしきい値電圧  $V_{th}$  に設定される。これによりこの実施例では、信号レベル保持用コンデンサの端子間電圧を駆動トランジスタのしきい値電圧以上に設定した後、複数回に分けて駆動トランジスタのしきい値電圧のばらつきを補正する場合でも、正しく駆動トランジスタのしきい値電圧のばらつきを補正して画質劣化を防止することができる。

20

【0067】

なお非発光期間  $T_1$  の開始により事前に有機EL素子8のカソード電圧を立ち下げて信号レベル保持用コンデンサC1の端子間電圧を駆動トランジスタTR1のしきい値電圧  $V_{th}$  以上に設定した後、有機EL素子8のカソード電圧を立ち上げて信号レベル保持用コンデンサC1の端子間電圧を駆動トランジスタTR1のしきい値電圧  $V_{th}$  に設定する方法も考えられ、この場合には、1回目の期間の経過後、即座に階調電圧  $V_{sig}$  を信号レベル保持用コンデンサC1に設定できると考えられる。

30

【0068】

しかしながらこの方法の場合、この実施例に比してカソード電圧が高くなり、その分、有機EL素子のしきい値電圧が上昇し、発光期間  $T_2$  が開始した後のブートストラップ動作により駆動トランジスタTR1のソース電圧の上昇が大きくなる。その結果、この方法の場合、ブートストラップゲインの損失が増大し、駆動トランジスタTR1のゲートソース間電圧  $V_{gs}$  が減少して発光輝度が低下することになる。

30

【0069】

しかしながらこの実施例のように、2回目の期間  $T_{th2}$  で元の発光期間  $T_2$  のカソード電圧に戻すようにすれば、カソード電圧を低い電圧に保持することができ、ブートストラップゲインの損失の増大を防止して発光輝度の低下を防止することができる。

【0070】

なおこの2回目の期間  $T_{th2}$  で元の発光期間  $T_2$  のカソード電圧に戻す場合、信号レベル保持用コンデンサの端子間電圧は、駆動トランジスタTR1のしきい値電圧  $V_{th}$  から  $(V_{cat} \times C_p / (C_p + C_1))$  だけ増大することになり、この増大分も、この期間  $T_{th2}$  で補正されることになる。

40

【0071】

(3) 実施例の効果

以上の構成によれば、信号レベル保持用コンデンサの端子間電圧を駆動トランジスタのしきい値電圧以上に設定した後、複数回の期間に分けて、この信号レベル保持用コンデンサの蓄積電荷を駆動トランジスタにより放電させて信号レベル保持用コンデンサの端子間電圧を駆動トランジスタのしきい値電圧に設定する際に、始めの期間で発光素子のカソード電圧を立ち上げて短時間で信号レベル保持用コンデンサの端子間電圧が駆動トランジスタのしきい値電圧となるように設定した後、カソード電圧を元の電圧に戻して最終的に信

50

号レベル保持用コンデンサの端子間電圧を駆動トランジスタのしきい値電圧に設定することにより、複数回に分けて駆動トランジスタのしきい値電圧のばらつきを補正する場合でも、正しく駆動トランジスタのしきい値電圧のばらつきを補正することができる。

【0072】

また所定の固定電圧を間に挟んで各画素の階調を示す階調電圧に順次設定して信号線毎に駆動信号を生成するようにして、この駆動信号が固定電圧に設定されている期間で、書き込トランジスタをオン状態に設定して信号レベル保持用コンデンサの端子間電圧を駆動トランジスタのしきい値電圧以上の電圧に設定することにより、信号線を介して信号レベル保持用コンデンサの一端の電圧を固定電位に設定して信号レベル保持用コンデンサの端子間電圧を駆動トランジスタのしきい値電圧以上の電圧に設定する構成に適用して、正しく駆動トランジスタのしきい値電圧のばらつきを補正することができる。10

【0073】

またこの駆動信号が階調信号に設定される期間を、これら複数回の設定の間の休止期間に割り当てるにより、信号線を介して信号レベル保持用コンデンサの一端の電圧を固定電位に設定して信号レベル保持用コンデンサの端子間電圧を駆動トランジスタのしきい値電圧以上の電圧に設定する構成に適用して、正しく駆動トランジスタのしきい値電圧のばらつきを補正することができる。

【実施例2】

【0074】

なお上述の実施例においては、駆動トランジスタTR2の制御により駆動トランジスタTR1への電源の供給を制御する場合について述べたが、本発明はこれに限らず、駆動トランジスタTR2を省略して、直接、垂直駆動回路で電源ラインを制御することにより駆動トランジスタTR1への電源の供給を制御するようにしてもよい。20

【0075】

また上述の実施例においては、信号線を介して信号レベル保持用コンデンサの信号線側電圧を設定して信号レベル保持用コンデンサの端子間電圧を有機EL素子のしきい値電圧以上に設定する場合について述べたが、本発明はこれに限らず、図5について上述したように専用のトランジスタTR4を介して所定の基準電圧を接続して信号レベル保持用コンデンサの信号線側電圧を設定し、信号レベル保持用コンデンサの端子間電圧を有機EL素子のしきい値電圧以上に設定する場合にも広く適用することができる。30

【0076】

また上述の実施例においては、駆動トランジスタTR1の電源の制御により、信号レベル保持用コンデンサの有機EL素子側電圧を設定して信号レベル保持用コンデンサの端子間電圧を有機EL素子のしきい値電圧以上に設定する場合について述べたが、本発明はこれに限らず、図5について上述したように専用のトランジスタTR3を介して所定の基準電圧を接続して信号レベル保持用コンデンサの有機EL素子側電圧を設定し、信号レベル保持用コンデンサの端子間電圧を有機EL素子のしきい値電圧以上に設定する場合にも広く適用することができる。

【0077】

また上述の実施例では、発光素子に有機EL素子を使用する場合について述べたが、本発明はこれに限らず、電流駆動型の各種発光素子を使用する場合に広く適用することができる。40

【産業上の利用可能性】

【0078】

本発明は、例えば有機EL素子によるアクティブマトリックス型の表示装置に適用することができる。

【図面の簡単な説明】

【0079】

【図1】本発明の実施例1の動作の説明に供するタイムチャートである。

【図2】図1の表示装置を示すブロック図である。50

【図3】図2の表示装置を示す接続図である。

【図4】従来の表示装置を示す接続図である。

【図5】図4の表示装置の動作の説明に供するタイムチャートである。

【図6】信号線により信号レベル保持用コンデンサの一端の電圧を設定する場合等に考えられる表示装置を示すブロック図である。

【図7】図6の表示装置の接続図である。

【図8】図6の表示装置の動作の説明に供するタイムチャートである。

【符号の説明】

【0080】

1、11、21……表示装置、3、13、23……水平駆動回路、5、15、24……垂直駆動回路、6、16、22……表示部、7、17、27……画素回路、8……有機EL素子、26C……カソードスキャナ、C1……信号レベル保持用コンデンサ、TR1～TR5……トランジスタ

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

11

【図8】

## 【手続補正書】

【提出日】平成20年5月22日(2008.5.22)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】請求項1

【補正方法】変更

## 【補正の内容】

## 【請求項1】

画素回路をマトリックス状に配置して形成された表示部に対して、前記表示部の信号線及び走査線を介して水平駆動回路及び垂直駆動回路により前記画素回路を駆動することにより、前記表示部で所望の画像を表示する表示装置において、

前記画素回路は、

少なくとも発光素子と、

信号レベル保持用コンデンサと、

前記信号レベル保持用コンデンサの両端をゲート及びソースに接続し、前記発光素子のアノードを前記ソースに接続し、前記ゲート及びソース間電圧に応じた駆動電流で前記発光素子を駆動する駆動トランジスタと、

前記垂直駆動回路から出力される書き信号によりオン動作し、前記駆動トランジスタのゲートを前記信号線に接続する書きトランジスタとを有し、

前記水平駆動回路は、

各画素の階調を示す階調電圧の連続による駆動信号を前記信号線毎に生成し、

前記駆動信号を対応する前記信号線に出力し、

前記垂直駆動回路は、

前記発光素子の発光を停止させる非発光期間において、

前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧

以上の電圧に設定した後、

少なくとも所定の休止期間を間に挟んだ第1及び第2の期間で、それぞれ前記信号レベル保持用コンデンサの蓄積電荷を前記駆動トランジスタにより放電させて前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧に設定し、

続いて前記書込トランジスタをオン動作させて前記信号レベル保持用コンデンサのゲート側電圧を前記階調電圧に設定し、

前記垂直駆動回路は、

前記第1の期間の途中で前記発光素子のカソード電圧を立ち上げた後、遅くとも前記第2の期間の途中で発光期間の電圧に立ち下げることにより、前記第1の期間において、前記信号レベル保持用コンデンサの端子間電圧が前記駆動トランジスタのしきい値電圧となる速度を増大させる

ことを特徴とする表示装置。

【手続補正2】

【補正対象書類名】特許請求の範囲

【補正対象項目名】請求項3

【補正方法】変更

【補正の内容】

【請求項3】

前記休止期間が、

前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧以上の電圧に設定する期間に統いて、前記駆動信号が前記階調電圧に設定される期間である

ことを特徴とする請求項2に記載の表示装置。

【手続補正3】

【補正対象書類名】特許請求の範囲

【補正対象項目名】請求項5

【補正方法】変更

【補正の内容】

【請求項5】

画素回路をマトリックス状に配置して形成された表示部に対して、前記表示部の信号線及び走査線を介して水平駆動回路及び垂直駆動回路により前記画素回路を駆動することにより、前記表示部で所望の画像を表示する表示装置の駆動方法において、

前記画素回路は、

少なくとも発光素子と、

信号レベル保持用コンデンサと、

前記信号レベル保持用コンデンサの両端をゲート及びソースに接続し、前記発光素子のアノードを前記ソースに接続し、前記ゲート及びソース間電圧に応じた駆動電流で前記発光素子を駆動する駆動トランジスタと、

前記垂直駆動回路から出力される書込信号によりオン動作し、前記駆動トランジスタのゲートを前記信号線に接続する書込トランジスタとを有し、

前記駆動方法は、

各画素の階調を示す階調電圧の連続による駆動信号を前記信号線毎に生成し、前記駆動信号を対応する前記信号線に出力する駆動信号出力ステップと、

前記発光素子の発光を停止させる非発光期間において、

前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧以上の電圧に設定するしきい値電圧設定の前処理ステップと、

少なくとも所定の休止期間を間に挟んだ第1及び第2の期間で、それぞれ前記信号レベル保持用コンデンサの蓄積電荷を前記駆動トランジスタにより放電させて前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧に設定するしきい値電圧設定ステップと、

続いて前記書込トランジスタをオン動作させて前記信号レベル保持用コンデンサのゲート側電圧を前記階調電圧に設定する階調電圧設定ステップと、

前記第1の期間の途中で前記発光素子のカソード電圧を立ち上げた後、遅くとも前記第2の期間の途中で発光期間の電圧に立ち下げるにより、前記第1の期間において、前記信号レベル保持用コンデンサの端子間電圧が前記駆動トランジスタのしきい値電圧となる速度を増大させるカソード電圧制御のステップとを有する

ことを特徴とする表示装置の駆動方法。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0038

【補正方法】変更

【補正の内容】

【0038】

上記の課題を解決するため請求項1の発明は、画素回路をマトリックス状に配置して形成された表示部に対して、前記表示部の信号線及び走査線を介して水平駆動回路及び垂直駆動回路により前記画素回路を駆動することにより、前記表示部で所望の画像を表示する表示装置に適用して、前記画素回路は、少なくとも発光素子と、信号レベル保持用コンデンサと、前記信号レベル保持用コンデンサの両端をゲート及びソースに接続し、前記発光素子のアノードを前記ソースに接続し、前記ゲート及びソース間電圧に応じた駆動電流で前記発光素子を駆動する駆動トランジスタと、前記垂直駆動回路から出力される書込信号によりオン動作し、前記駆動トランジスタのゲートを前記信号線に接続する書込トランジスタとを有し、前記水平駆動回路は、各画素の階調を示す階調電圧の連続による駆動信号を前記信号線毎に生成し、前記駆動信号を対応する前記信号線に出力し、前記垂直駆動回路は、前記発光素子の発光を停止させる非発光期間において、前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧以上の電圧に設定した後、少なくとも所定の休止期間を間に挟んだ第1及び第2の期間で、それぞれ前記信号レベル保持用コンデンサの蓄積電荷を前記駆動トランジスタにより放電させて前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧に設定し、続いて前記書込トランジスタをオン動作させて前記信号レベル保持用コンデンサのゲート側電圧を前記階調電圧に設定し、前記垂直駆動回路は、前記第1の期間の途中で前記発光素子のカソード電圧を立ち上げた後、遅くとも前記第2の期間の途中で発光期間の電圧に立ち下げるにより、前記第1の期間において、前記信号レベル保持用コンデンサの端子間電圧が前記駆動トランジスタのしきい値電圧となる速度を増大させる。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0039

【補正方法】変更

【補正の内容】

【0039】

また請求項5の発明は、画素回路をマトリックス状に配置して形成された表示部に対して、前記表示部の信号線及び走査線を介して水平駆動回路及び垂直駆動回路により前記画素回路を駆動することにより、前記表示部で所望の画像を表示する表示装置の駆動方法に適用して、前記画素回路は、少なくとも発光素子と、信号レベル保持用コンデンサと、前記信号レベル保持用コンデンサの両端をゲート及びソースに接続し、前記発光素子のアノードを前記ソースに接続し、前記ゲート及びソース間電圧に応じた駆動電流で前記発光素子を駆動する駆動トランジスタと、前記垂直駆動回路から出力される書込信号によりオン動作し、前記駆動トランジスタのゲートを前記信号線に接続する書込トランジスタとを有し、前記駆動方法は、各画素の階調を示す階調電圧の連続による駆動信号を前記信号線毎に生成し、前記駆動信号を対応する前記信号線に出力する駆動信号出力ステップと、前記発光素子の発光を停止させる非発光期間において、前記信号レベル保持用コンデンサの端

子間電圧を前記駆動トランジスタのしきい値電圧以上の電圧に設定するしきい値電圧設定の前処理ステップと、少なくとも所定の休止期間を間に挟んだ第1及び第2の期間で、それぞれ前記信号レベル保持用コンデンサの蓄積電荷を前記駆動トランジスタにより放電させて前記信号レベル保持用コンデンサの端子間電圧を前記駆動トランジスタのしきい値電圧に設定するしきい値電圧設定ステップと、続いて前記書込トランジスタをオン動作させて前記信号レベル保持用コンデンサのゲート側電圧を前記階調電圧に設定する階調電圧設定ステップと、前記第1の期間の途中で前記発光素子のカソード電圧を立ち上げた後、遅くとも前記第2の期間の途中で発光期間の電圧に立ち下げるにより、前記第1の期間において、前記信号レベル保持用コンデンサの端子間電圧が前記駆動トランジスタのしきい値電圧となる速度を増大させるカソード電圧制御のステップとを有するようとする。

## フロントページの続き

| (51)Int.Cl. | F I          | テーマコード(参考) |

|-------------|--------------|------------|

|             | G 09 G 3/20  | 6 2 4 B    |

|             | G 09 G 3/20  | 6 2 2 D    |

|             | G 09 G 3/20  | 6 4 2 A    |

|             | G 09 G 3/20  | 6 4 1 P    |

|             | H 05 B 33/14 | A          |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置和显示装置的驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2009122228A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2009-06-04 |

| 申请号            | JP2007294100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2007-11-13 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| [标]发明人         | 豊村直史<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 豊村 直史<br>内野 勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| FI分类号          | G09G3/30.K G09G3/30.J G09G3/20.611.H G09G3/20.641.D G09G3/20.621.A G09G3/20.624.B G09G3/20.622.D G09G3/20.642.A G09G3/20.641.P H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD05 5C080/EE28 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/BA38 5C380/BA39 5C380/BB02 5C380/BC20 5C380/CA04 5C380/CA08 5C380/CA12 5C380/CA32 5C380/CA53 5C380/CA54 5C380/CB01 5C380/CB20 5C380/CB26 5C380/CB27 5C380/CB31 5C380/CC02 5C380/CC03 5C380/CC04 5C380/CC06 5C380/CC07 5C380/CC27 5C380/CC33 5C380/CC39 5C380/CC41 5C380/CC62 5C380/CC65 5C380/CC71 5C380/CD022 5C380/CD025 5C380/CE09 5C380/CF09 5C380/DA02 5C380/DA06 5C380/DA47 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

### 摘要(译)

解决的问题：通过将驱动晶体管应用于有机EL元件的有源矩阵型显示装置来校正阈值电压变化。解决方案：将信号电平保持电容器的端子之间的电压( $V_g-V_s$ )设置为驱动晶体管的阈值电压 $V_{th}$ 或更高，然后将该信号电平保持电容器的累积电荷分为多个周期。当通过利用驱动晶体管使电容器放电来设置驱动晶体管的阈值电压 $V_{th}$ 以将信号电平保持电容器电压( $V_g-V_s$ )设置为驱动晶体管的阈值电压 $V_{th}$ 时，发光元件的阴极电压CATH在第一时段 $T_{th1}$ 中升高。在短时间内将用于保持信号电平的电容器的端子之间的电压( $V_g-V_s$ )设置为驱动晶体管的阈值电压 $V_{th}$ 之后，阴极电压CATH返回到原始电压，最终达到信号电平。保持电容器的端子电压( $V_g-V_s$ )被设置为驱动晶体管的阈值电压 $V_{th}$ 。[选型图]图1