(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-287354

(P2007-287354A)

(43) 公開日 平成19年11月1日(2007.11.1)

| (51) Int.CI.                | F 1        |   | テーマコード (参考) |

|-----------------------------|------------|---|-------------|

| <b>H05B 33/26 (2006.01)</b> | H05B 33/26 | Z | 3 K 1 O 7   |

| <b>H01L 51/50 (2006.01)</b> | H05B 33/14 | A |             |

| <b>H05B 33/28 (2006.01)</b> | H05B 33/28 |   |             |

| <b>H05B 33/12 (2006.01)</b> | H05B 33/12 | B |             |

| <b>H05B 33/22 (2006.01)</b> | H05B 33/22 | Z |             |

審査請求 未請求 請求項の数 16 O L (全 26 頁)

|           |                              |          |                                               |

|-----------|------------------------------|----------|-----------------------------------------------|

| (21) 出願番号 | 特願2006-110141 (P2006-110141) | (71) 出願人 | 502356528<br>株式会社 日立ディスプレイズ<br>千葉県茂原市早野3300番地 |

| (22) 出願日  | 平成18年4月12日 (2006.4.12)       | (74) 代理人 | 100093506<br>弁理士 小野寺 洋二                       |

|           |                              | (72) 発明者 | 坂元 博次<br>千葉県茂原市早野3300番地 株式会社<br>日立ディスプレイズ内    |

|           |                              | (72) 発明者 | 加藤 真一<br>千葉県茂原市早野3300番地 株式会社<br>日立ディスプレイズ内    |

|           |                              | (72) 発明者 | 寺門 正倫<br>千葉県茂原市早野3300番地 株式会社<br>日立ディスプレイズ内    |

最終頁に続く

(54) 【発明の名称】有機EL表示装置

## (57) 【要約】

【課題】明るく、表示品位の高い有機EL表示装置を提供する。

【解決手段】基板上に、複数のアクティブ素子と、アクティブ素子によって制御されることにより発光する複数の有機EL素子とを有し、有機EL素子は基板側から、下部電極、有機層及び上部電極CDがこの順で積層されており、複数の有機EL素子の上部電極CDは全ての有機EL素子で共通の電極であり、上部電極CDと有機層との間に電極を備えさせ、その電極を挟む上部電極CD上の2点間のシート抵抗を、その金属電極を挟まない2点間のシート抵抗よりも低くなるようにする。

【選択図】図8

**【特許請求の範囲】****【請求項 1】**

基板上に、複数のアクティブ素子と、アクティブ素子によって制御されることにより多階調で発光する複数の有機EL素子と、を有する有機EL表示装置において、

前記有機EL素子は基板側から下部電極、有機層を含む機能層及び上部電極がこの順で積層されており、

該複数の有機EL素子の上部電極は全ての有機EL素子に対して共通の電極であり、

前記上部電極と前記機能層との間には、上部電極よりも導電率の高い材料で構成された補助電極が形成されていることを特徴とする有機EL表示装置。

**【請求項 2】**

基板上に、複数のアクティブ素子と、アクティブ素子によって制御されることにより発光する複数の有機EL素子と、を有する有機EL表示装置において、

前記有機EL素子は基板側から、下部電極、有機層を含む機能層及び上部電極がこの順で積層されており、

該複数の有機EL素子の上部電極は全ての有機EL素子で共通の電極であり、

前記上部電極と前記有機層との間に金属電極を備え、

その金属電極を挟む上部電極上の2点間のシート抵抗は、その金属電極を挟まない2点間のシート抵抗よりも低いことを特徴とする有機EL表示装置。

**【請求項 3】**

請求項1又は2において、

前記下部電極と前記有機層の間には、絶縁膜を備え、

前記絶縁膜と重畳する位置に、前記補助電極を備えていることを特徴とする有機EL表示装置。

**【請求項 4】**

請求項1又は2において、

前記補助電極は、前記複数の有機EL素子間に配置されることを特徴とする有機EL表示装置。

**【請求項 5】**

請求項1又は2において、

前記補助電極は、前記下部電極の間に配置されることを特徴とする有機EL表示装置。

**【請求項 6】**

請求項1又は2において、

前記複数の有機EL素子は、マトリクス状に配置され、

前記補助電極は、画面の行又は列方向に延在することを特徴とする有機EL表示装置。

**【請求項 7】**

請求項1又は2において、

前記補助電極が、有効表示領域の外側に形成されていることを特徴とする有機EL表示装置。

**【請求項 8】**

請求項7において、

前記補助電極の少なくとも一部が、有効表示領域の外側で前記有機層よりも下層の配線と接続されていることを特徴とする有機EL表示装置。

**【請求項 9】**

請求項8において、

前記接続部において、前記補助配線の上方には、前記上部電極を備えていることを特徴とする有機EL表示装置。

**【請求項 10】**

請求項8又は9において、

前記下層の配線は、前記下部電極と同層の電極が前記配線との間に介在することを特徴とする有機EL表示装置。

**【請求項 1 1】**

請求項 8 から 10 のいずれかにおいて、

前記補助電極の接続部の下方には、前記アクティブ素子のソース電極又はドレイン電極と同層の配線であることを特徴とする有機 E L 表示装置。

**【請求項 1 2】**

請求項 1、2、8 から 11 のいずれかにおいて、

前記上部電極は、透明導電膜であることを特徴とする有機 E L 表示装置。

**【請求項 1 3】**

請求項 1 2 において、

前記透明導電膜は、光透過性の金属薄膜、ITO、IZO 又はZnO を含むことを特徴とする有機 E L 表示装置。 10

**【請求項 1 4】**

請求項 1、2、8 から 13 のいずれかにおいて、

前記下部電極は、光不透過性の金属薄膜を含むことを特徴とする有機 E L 表示装置

**【請求項 1 5】**

請求項 1 4 において、

前記下部電極は、光不透過性の金属薄膜の上に透明導電膜を積層した構造を含むことを特徴とする有機 E L 表示装置

**【請求項 1 6】**

基板上に、有機 E L 素子と、垂直系駆動回路と、走査線と、該垂直系駆動回路と該走査線とにより各画素にデータ信号を取り込む第 1 アクティブ素子と、該第 1 アクティブ素子によって各画素に取り込まれたデータ信号によって有機 E L 素子に流す電流量を制御する第 2 アクティブ素子と、を有する有機 E L 表示装置において、 20

前記有機 E L 素子は基板側から金属電極を含む下部電極、有機層及び光透過性の上部電極がこの順で積層されており、

前記アクティブ素子と前記下部電極の間に、第 1 絶縁膜が形成され、

前記垂直系駆動回路と前記走査線の上方であって、前記下部電極の外縁及び前記第 1 絶縁膜との間の位置に、下部電極上に開口を備えた第 2 絶縁膜が形成され、

前記有機層は、前記開口及び第 2 絶縁膜上に形成され、

前記上部電極は、前記開口の上方に配置され、かつ、複数の画素に共通して形成され、 30

前記上部電極と有機層との間であって、前記第 2 絶縁膜と重畳する位置に、上部電極の上方より測定した 2 点間のシート抵抗を高める金属電極を有することを特徴とする有機 E L 表示装置。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、有機 E L 表示装置に係る。

**【背景技術】****【0 0 0 2】**

トップエミッション型（以下、「TE型」と称する。）のアクティブマトリクス型有機 E L 表示装置（以下、「AM-OLED」と称する。）は、先行開発品のボトムエミッション型（以下、「BE型」と称する。）の AM-OLED と大きく異なる部分が発光の取り出し方向である。 40

**【0 0 0 3】**

BE型 AM-OLED は、マトリクス状に配置された各画素 PXL をアクティブ素子で駆動するアクティブマトリクス基板（以下、「TFT 基板」と称する。）上に、TFT 基板側の下部電極、有機層で構成された発光層を含む機能層 OLF 、上部電極 C D の積層構造を備えた構造（以下、「有機EL素子」と称する。）を備え、その下部電極として透明導電膜である ITO を画素 PXL 每に形成し、この ITO 上に形成した発光層へ流れ込む 50

電流をアクティブ素子で制御することにより、表示を行う。発光層から生じた光は TFT 基板側に取り出されるため、発光層の上に形成される上部電極 CD は高い反射特性を備えた金属を有効表示領域 AR 前面に一括形成した構造となっている。この高い反射特性を備えた金属はシート抵抗が低いため、各画素 PXL の共通電極として十分に駆動回路へ電位を回帰できるようになっている。

#### 【0004】

一方、TE型のAM-OLEDでは、発光層の発光を TFT 基板側ではなく、上部電極 CD 側に取り出すので、下部電極を反射特性を備えた金属とし、上部電極 CD を透明導電膜とする必要がある。ここでいう、透明導電膜とは、一般的に透明導電膜と称される、IZO、ITO、ZnOといった、In、Zn、Sn系酸化膜だけでなく、薄膜Ag、薄膜Alも含めるものとする。これらの透明導電膜によって形成された電極は、シート抵抗が高いために、上部電極 CD として、有効表示領域 AR の全面に一括形成しただけでは、電位勾配を生じてしまい、画面内の輝度傾斜が発生する。

#### 【0005】

特許文献1と2には、発光取り出し側の透明導電膜の電気抵抗を見かけ上低減する為に、透明導電膜を金属補助電極によりある程度微小な領域に分割することが開示されている。特許文献1には、下部電極間の絶縁膜であるバンクの下であって、下部電極と同層、かつ分離された補助配線を設け、さらにその補助配線と上部電極 CD をコンタクトホールによって接続させた構造が開示されている。特許文献2には、有機EL素子の上部電極 CD の上層であって、バンクと重畳する領域に補助配線を設けることが開示されている。

【特許文献1】特開2001-230086号公報

【特許文献2】特開2002-318556号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0006】

特許文献1は、補助電極と有機EL素子の下部電極よりも下層の引き回し配線との間をコンタクトホールによって接続している。コンタクトホール内に発光層を含む有機EL素子の機能層OLFの一層が形成されると、電気的な接続ができなくなるため、コンタクトホールの近傍には機能層OLF形成ズレ分以上の非形成領域を設ける必要がある。つまり、特許文献1の技術によれば、開口率(1画素PXL当たりの発光面積(バンク開口面積)の1画素PXLの全面積に対する割合)を低くせざるを得なかった。

#### 【0007】

特許文献2は、補助電極が上部電極 CD の上、つまり、特許文献1よりも表示面に近い位置に補助電極が形成されるので、補助電極と下部電極との反射特性差により、画面上に補助電極の反射がはっきりとした模様となって見えててしまう。

#### 【0008】

本発明の目的は、明るく、まだ画面上の輝度ムラの少ないTE型AM-OLEDを提供することにある。

#### 【課題を解決するための手段】

#### 【0009】

本発明は、上記した目的を達成するため、例えば以下の手段を採用する。

有機EL素子がTFT基板側から、下部電極、有機発光層を含む機能層OLF、上部電極 CD の順で積層された構造を備えたTE型のAM-OLEDにおいて、上部電極 CD を全ての有機EL素子で共通の電極、つまり、ベタ電極とし、その上部電極 CD と機能層OLFとの間に、上部電極 CD よりも導電率の高い材料で構成された補助電極を形成するようとする。

#### 【0010】

また、別の表現をするならば、そのような構造を採用する場合に、ベタ電極である上部電極 CD と機能層OLFとの間に補助電極を形成し、その補助電極が挟まれる上部電極 CD 上の2点間のシート抵抗を、補助電極を挟まない上部電極 CD 上の2点間のシート抵

10

20

30

40

50

抗よりも低いようにする。

【0011】

このように、補助電極として上部電極CDよりも抵抗値の低い金属を用い、上部電極CDと合わせた機能層OLBFよりも上の電極全体のシート抵抗を下げるにより、面内における電圧降下を抑制できる。

【0012】

この補助電極を上部電極CDと機能層OLBFの間、具体的には、上部電極CDの直下で、上部電極CDに電気的に接続される構造を採用することにより、表示面までの間に上部電極CDが挟まるので、補助電極の反射光がぼやけることになるので、補助電極の反射による画面上の輝度ムラが減り、表示品位を向上する。

【0013】

この補助電極の形状、構造、形成位置等として好適な態様は次の通りである。

(1) 法線方向の構造：バンク上

下部電極と機能層OLBFの間に、通常、「バンク」と呼ばれる画素PXLを区画する絶縁膜を備えた構造を採用する場合、このバンクと重畳する位置に形成することが好ましい。このバンクは非発光領域であり、開口率(発光面積/画素PXLの全面積)を高いまま維持できる。また、補助電極が機能層OLBFに食い込んだ場合、その補助電極のエッジに電界が集中し、補助電極と下部電極との間にリーク電流が生じる可能性があるが、バンクの上であれば、バンクから露出している下部電極との距離が遠いので、リーク電流がほとんど生じない。

【0014】

この配置を言い換えると、下部電極、バンク、機能層OLBFの少なくとも一層、補助電極、上部電極CDの順に積層された構造Aと、下部電極の下層の絶縁膜、バンク、機能層OLBFの少なくとも一層、補助電極、上部電極CDの順に積層された構造Bとを備えた構造ともいいうことができる。ただ、この構造A、Bにおける積層体で、「機能層OLBFの少なくとも一層」としているのは、塗りわけ蒸着を行う場合に、蒸着ズレから、バンクの上に蒸着を行わない領域が生じる可能性が生じるがあるからである。ただし、逆に、通常、少なくともベタ蒸着を行う層が一層は存在するので、少なくとも一層の機能層OLBFは介在する。

【0015】

(2) 平面配置：発光領域間(画素PXL間)

補助電極の平面位置として好ましいのは、各画素PXLの発光領域の間である。この領域は非発光領域であるので、開口率(1画素PXL当たりの発光面積/1画素PXLの面積)を高いまま維持できる。別の表現をするならば、隣接する有機EL素子間の領域、下部電極の間の領域ともいえる。また、配線のレイアウトによっては、ソース電極層の配線(垂直系駆動回路VDRV、電流供給線、制御線)と重畳する領域、ゲート電極層の配線(走査線、電流供給線、制御線)と重畳する領域がこれらの領域に相当する。また、後述するようにこれらの領域はより高い平坦度がバンクの上に得られる可能性が高い。

【0016】

(3) 形状及び平面レイアウト

有機EL素子がマトリクス状に配置されている場合、画面の行又は列方向に延在するようにすれば、垂直系駆動回路VDRV、電流供給線といった列方向の配線や、走査線等の行方向の配線と重畳させることができる。有機物の平坦層を補助電極の下層の絶縁膜に用いた場合でも、緩和された凹凸があり、また、無機絶縁膜を用いた場合にあっては、補助配線の下層には大きな凹凸ができる。これらの配線は複数の画素PXLに跨って平坦な面が伸びているため、比較的凹凸が小さく、均一な厚みの電極が形成しやすい。

【0017】

(4) 有効表示領域AR外の配線レイアウト

補助電極を有効表示領域AR(発光画素PXLの全領域)の外側に形成すれば、上部電極CDを介さないでも、共通電圧VCOMを印加できるようになったり、また、開口率を

10

20

30

40

50

犠牲にしない補助電極の平面レイアウトが可能になるので、設計自由度を向上させることができ。また、有効表示領域 A R のいろいろな方向から共通電圧 V C O M を供給できるようになるので、電圧降下を効果的に抑制できる。具体的には、有効表示領域 A R の列方向（ドレインドライバと称される垂直系駆動回路 V D R V が存在する方向、いいかえると垂直系駆動回路 V D R V が延在する方向）、行方向（ゲートドライバと称される水平系駆動回路 H D R V が存在する方向、いいかえると走査線が延在する方向）の外側に配置することが好ましく。最も、電圧降下を抑制できるのは枠状にして全画素 P X L を囲む形状である。

#### 【 0 0 1 8 】

##### ( 5 ) 共通電圧 V C O M の供給構造

この補助電極を有効表示領域 A R の外側で機能層 O L B F よりも下層の配線と接続すると、高抵抗の上部電極 C D を介さずに、よりシート抵抗の低い補助電極で画面に共通電圧 V C O M を供給できるので、有効表示領域 A R での電圧降下を抑制できる。

#### 【 0 0 1 9 】

##### ( 6 ) 共通電圧 V C O M の安定供給構造 1

( 5 ) の接続部で、補助電極の上方にも上部電極 C D を備えさせれば、機能層 O L B F 全体を被うように配置できるので、保護層、封止層としても機能させることができる。また、補助電極及び補助電極に接続される配線の酸化抑制膜、保護層としても、機能させることができる。

#### 【 0 0 2 0 】

##### ( 7 ) 共通電圧 V C O M の安定供給構造 2

上部電極 C D に対して共通電圧 V C O M を印加する電極を配置する層としては、アクティブ素子のソース電極と同層とすることが好ましい。アクティブ素子のチャンネルを低温ポリシリコンで構成する場合、ゲート電極はエキシマレーザなどによりアニ - ルする。そのため、タングステン、チタン、モリブデンといった高融点金属をゲート電極層に用いる。これらの高融点金属は抵抗が高い。アクティブ素子のソース電極と同層、同材料の配線は、通常、アルミニウム合金などの抵抗の小さな材料を用いている。このソース電極層を形成した後ではレーザアニ - ル工程のようなアルミニウム合金を溶かす高温プロセスは存在しないため、採用できるのである。したがって、共通電圧 V C O M の低下を抑制するためには、配線抵抗の小さなソース電極層を用いることが好ましい。ただし、ゲート電極と同層の配線に接続することもできる。ただし、この場合、配線の抵抗は多少高くなるが、この層も用いれば、配線の引き回し自由度は向上する。

#### 【 0 0 2 1 】

##### ( 8 ) 共通電圧 V C O M の安定供給構造 3

ソース電極層と補助配線層との間には厚い絶縁膜が形成される。そのため、大きなコンタクトホールを形成しなければ、ソース電極との電気的な接続を安定的に得ることはできない。そこで、共通電圧 V C O M の安定供給の観点からは、上部電極 C D と下部電極よりも下の配線との間に、下部電極に含まれる電極層と同層で同材料の電極を介在させて、それら両電極と接続した構造が好ましい。

#### 【 0 0 2 2 】

##### ( 9 ) 発光タイプと電極の材質、厚さ

補助配線を用いて最も効果のある構造は、T E 型であり、本発明者らは上部電極 C D として、透明導電膜、つまり、銀やアルミニウムといった低抵抗金属を光が透過する程薄く形成した金属薄膜や、I T O 、I Z O 又はZ n O といった電極が好ましく、下部電極としては、光が実質的に透過しない程厚い金属電極を用いることが好ましいと考える。

#### 【 0 0 2 3 】

また、光透過性電極としては、I T O 、I Z O 、Z n O 、金属薄膜を採用することが好ましい。この構造によって、開口率を犠牲にしないで、面内の斑模様等の画面上の輝度ムラを抑制できる。

#### 【 発明の効果 】

10

20

30

40

50

**【0024】**

本発明によれば、高い開口率を維持しつつ、面内の輝度ムラ、反射特性の不均一性を緩和できる。

**【発明を実施するための最良の形態】****【0025】**

以下、本実施例を説明する。

**【実施例1】****【0026】**

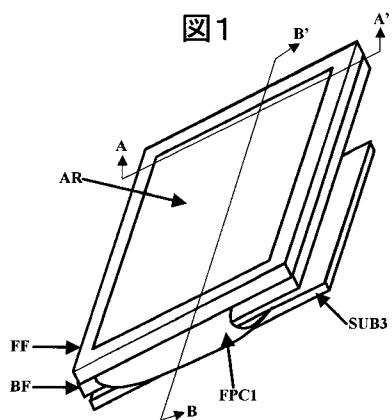

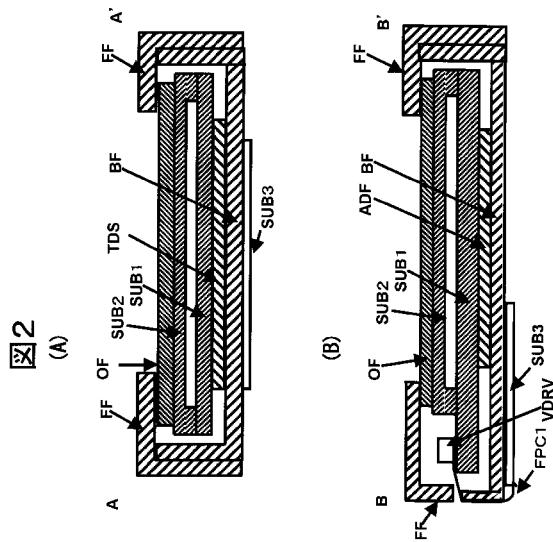

図1は、有機EL表示装置の外観斜視図である。図2は、本発明の有機EL表示装置の断面図である。図2(A)は、図1のA-A'における断面図である。図2(B)は、図1のB-B'における断面図である。有機EL素子やアクティブ素子が形成された TFT 基板であると、第1基板SUB1の有機EL素子上を封止する第2基板SUB2と、これら第1基板SUB1の封止構造体が搭載された前フレームFF及び裏フレームBFと、第1基板SUB1に接続されたフレキシブル回路基板FPC1と、フレキシブル回路基板FPC1に接続された第3基板SUB3とを備えた構造をしている。

**【0027】**

前フレームFFには、開口が設けられている。この開口は第1基板SUB1上の有機EL素子が形成された有効表示領域ARよりも一回り大きく、第2基板SUB2を介して有機EL素子の下部電極が見える(機能層OLBFは透明なので視認は不可能)ようになっている。また、材質はステンレスや鉄系合金により構成されている。ただし、プラスチックでも構わない。

裏フレームBFは、前フレームFFと同様に、ステンレスや鉄系合金により構成されている。これも、プラスチックでも構わない。前フレームFFと裏フレームBFとはスナップフィットを用いてはめ合わされて、一定の空間を保持している。この保持された空間に、第1基板SUB1、第2基板SUB2、光学フィルムOFが格納されている。

**【0028】**

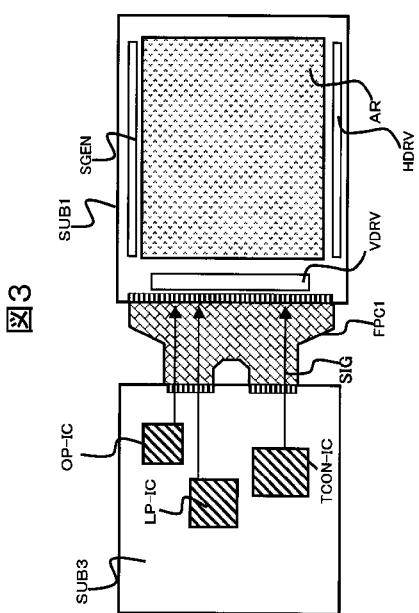

図3に第1~3基板SUB1~3のプロック図を示す。また、図4は、第1基板SUB1上のプロック構成図である。第1基板SUB1は、接着剤によって裏フレームBF(図2)に固定されている。第1基板SUB1上に、半導体ICで構成された垂直系駆動回路VDRVがCOGで搭載され、フレキシブル回路基板FPC1が端子PADに接続されている。第2基板SUB2は、第1基板SUB1にスペーサを混ぜたシール剤によって第1基板SUB1に固定されている。この第2基板SUB2は、表示面と第1基板SUB1との間に配置された基板であるので、光透過性の基板である。具体的には、ガラスで構成されている。この第2基板SUB2には凹部が形成され、その空間には光透過性の乾燥剤が塗布されている。ただし、乾燥剤が塗布されていない場合、樹脂で充填してもよい。

**【0029】**

第3基板SUB3は、第2基板SUB2の裏面に固定され、フレキシブル基板の逆側の端子がこの第3基板SUB3の端子に接続されている。また、この第3基板SUB3には、有機EL素子の駆動電源として機能するOLED電源回路と、低温ポリシリコンで構成された薄膜トランジスタを駆動するLTPS電源回路と、階調信号やタイミング信号を出力するタイミング制御回路とを有している。これらはフレキシブル基板FPC1を介して第1基板SUB1に供給されている。

**【0030】**

図2に示した光学フィルムOFは、前フレームFF側から、静電・反射防止層、直線偏光層、接着層、1/2位相板、接着層、1/4位相板、接着層、視角補償層、接着層、コレステリック液晶層、接着層、保護層の積層構造となっている。なお、視角補償層はコレステリック液晶層による透過光の視角依存性を補償する層である。この光学フィルムOFは、直線偏光板と2層の位相板により円偏光板を構成し、コレステリック液晶層によって偏光分離フィルムを構成し、この偏光分離フィルムによる視角依存性の補償を視角補償層によって行っている。光学フィルムOFは、第1基板SUB1に接着され、また、前フレ

10

20

30

40

50

ーム F F と裏フレーム F R との嵌め合わせによる力で固定されている。

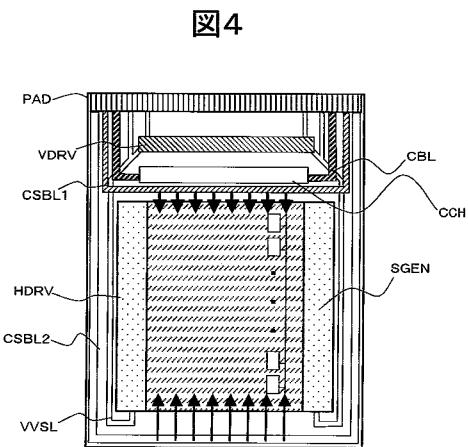

図 4において、第 1 基板 S U B 1 は、パッド P A D 、垂直系駆動回路 V D R V 、第 1 電流供給バスライン C S B L 1 、第 2 電流供給バスライン C S B L 2 、カソードバスライン C B L 、水平系駆動回路 H D R V 、水平系駆動回路 H D R V 用信号ライン、カソードコンタクト C C H 、有効表示領域 A R ( 図 3 ) が存在する。パッド P A D は、フレキシブル基板 F P C 1 と接続される。

#### 【 0 0 3 1 】

垂直系駆動回路 V D R V は、前述の通り、C O G 実装され、映像信号、電源、タイミング信号等の信号 S i g の供給をパッド P A D を介して受け取り、垂直方向に延在している垂直系駆動回路 V D R V を介して階調データを有効表示領域 A R にある画素 P X L ( 図 7 10 で後述 ) へ供給する。また、垂直系駆動回路 V D R V は、水平系駆動回路 H D R V と三角波発生回路 S G E N に対して。タイミング信号、L T P S 電源、信号電源、垂直系駆動回路 V D R V との同期を行う同期信号を供給する。

#### 【 0 0 3 2 】

カソードバスライン C B L は、後述する有機 E L 素子の上部電極 C D に供給する共通電圧 ( V C O M と称する ) が印加されている。そして、これはパッド P A D から垂直系駆動回路 V D R V の両脇を垂直方向に引き回され、垂直系駆動回路 V D R V と有効表示領域 A R の間で水平方向に引き回され、左右つながっている。また、このカソードバスライン C B L は水平系駆動回路 H D R V 及び三角波発生回路 S G E N のそれぞれと有効表示領域 A R の間、つまり、有効表示領域 A R の行方向の外側領域を垂直方向に引き回され、有効表示領域 A R の下側 ( 垂直系駆動回路 V D R V の対向する辺 ) でさらに水平方向に引き回されて左右つながっている。ただし、図 4 ではこの部分は省略してある。詳細は図 5 を用いて後述する。

#### 【 0 0 3 3 】

第 1 電流供給バスライン C S B L 1 は、パッド P A D から垂直系駆動回路 V D R V の両脇を垂直方向に引き回され、カソードバスライン C B L と有効表示領域 A R の間を水平方向に引き回されて左右つながっている。第 1 電流供給バスライン C S B L 1 は、図 4 の上下方向、つまり、垂直系駆動回路 V D R V が延在する方向に沿って形成され、その方向に沿って並んでいる画素 P X L に電流を供給する電流供給ライン C S L が接続されている。有効表示領域 A R の 4 辺に対してカソードコンタクト C H が形成され、このカソードコンタクト C H C D で上部電極 C D と接続され、上部電極 C D に対して共通電圧 V C O M を供給している。このカソードコンタクト C H における接続構造は後述する。

#### 【 0 0 3 4 】

第 2 電流供給バスライン C S B L 2 は、パッド P A D から垂直系駆動回路 V D R V の両脇を引き回され、さらに水平系駆動回路 H D R V 及び三角波発生回路 S G E N の外側を垂直方向に引き回され、さらに、有効表示領域 A R の下側へ水平方向に引き回され、左右つながっている。

#### 【 0 0 3 5 】

水平系駆動回路 H D R V は、一般にゲートドライバと呼ばれる回路で、本実施例では L T P S で基板上に内蔵されている。また、本実施例の場合、一画素 P X L 行当たり 3 本の走査線が水平系駆動回路 H D R V から水平方向 ( 行方向 ) に延在している。

#### 【 0 0 3 6 】

三角波発生回路は、本出願人が先に開発した画素 P X L 回路に必要な回路で、1 フレーム当たり 1 つの三角波を供給する回路である。

#### 【 0 0 3 7 】

これらの駆動回路や三角波発生回路は、本出願人が先に出願した特願 2 0 0 6 - 5 1 3 4 6 号、特に、該出願の図 2 3 乃至 2 5 に記載されたものと駆動波形を用いる。詳細な説明はその出願内容に記載されているので、ここに相互参照するものとし、敢えて本明細書では説明しない。

#### 【 0 0 3 8 】

10

20

30

40

50

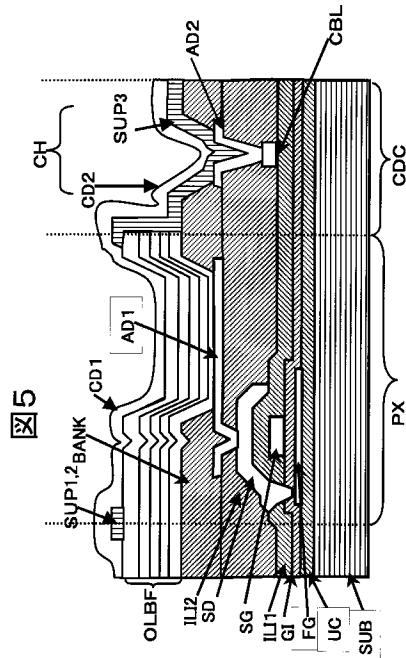

図5に、第1基板SUB1の層構造を示す。第1基板SUB1は、ガラス基板SUB、下地層UC、ポリシリコン層FG、第1絶縁層GI、第1電極層SG、第2絶縁層ILL1、第2電極層SD、第3絶縁層ILL2、第3電極層AD、第4絶縁層BANK、機能層OLBF、第4電極層SUP、第5電極層CDが順に形成された構造である。

#### 【0039】

下地層UCは、ガラス基板SUB上に形成され、SiOとSiNの積層膜である。この積層膜は、ガラスから拡散するNaをポリシリコン層FGに拡散させないようにする拡散防止膜であり、減圧化学気相成長法(LPCVD法)により形成する。

#### 【0040】

次に、ガラス基板SUB上に減圧化学気相成長法(LPCVD法)を用いて膜厚50nmのアモルファスシリコン層a-Siを形成する。次に、膜全面をエキシマレーザでレーザアニールすることによって、a-Siを結晶化し、多結晶シリコンp-Siで構成されたポリシリコン層FGを形成する。10

#### 【0041】

次に、ポリシリコン層FGを、ドライエッチングでパターン化し、トランジスタのチャネル(活性層)領域を形成する。次に、プラズマ増強化学気相成長法(PECVD法)を用い第1絶縁層GIを膜厚100nmのSiO<sub>2</sub>膜で形成した。この第1絶縁層GIは、ゲート絶縁膜として機能する。

#### 【0042】

次に、第1電極層SGとして膜厚50nmのTiW膜をスパッタリング法により作製し、バーニングする。このバーニングで薄膜トランジスタのゲート電極、前述した水平系駆動回路HDRVと三角波発生回路SGENから水平方向に延在する配線、その他の配線を形成する。なお、この配線はMOWでも構わない。20

#### 【0043】

次に、イオン注入法によりゲート絶縁膜の上部から、パターン化されたポリシリコン層にnイオンを注入する。上部にゲート電極がある領域にはnイオンが注入されず、活性層となる。

#### 【0044】

次に、第1基板SUB1を不活性N<sub>2</sub>雰囲気下で、加熱活性化処理を行い、ドーピングが有効に行われるようとする。その上に、第2絶縁層ILL1として窒化シリコン(SiNx)膜を成膜した。膜厚は200nmである。30

#### 【0045】

次に、活性層の両端上部の第1絶縁層GI及び第2絶縁層ILL1に、コンタクトホールを形成した。さらに、第2絶縁層ILL1にコンタクトホールを形成した。その上に、スパッタリング法にて膜厚500nmのAlで構成された第2電極層SDを形成する。ホトリソグラフィ工程によりバーニングすることにより、垂直系駆動回路VDRVや電流供給線CSLなど垂直に延びる配線や、カソードバスラインCBL、薄膜トランジスタのソースドレイン電極などを形成する。また、コンタクトホールを介して第1電極層SGやポリシリコン層FGと接続する。

#### 【0046】

次に、第3絶縁層ILL2としてSiNx膜を成膜した。膜厚は500nmである。薄膜トランジスタのソース電極上にコンタクトホールを設ける。その上にスパッタリング法を用いて、厚さ150nmのAlの上にITOが積層された第3電極層ADを形成する。さらに、ホトリソグラフィ法を用いてこの第3電極層をバーニングすることで有機EL素子の下部電極AD1、カソードバスラインCBL上のカソードコンタクトCHの中継電極(パッド)AD2を形成する。40

#### 【0047】

これらの駆動回路や三角波発生回路は、本出願人が先に出願した特願2006-51346号、特に、該出願の図12乃至22に記載されたものを用いる。詳細な説明はその出願内容に記載されているので、ここに相互参照するものとし、敢えて本明細書では説明し

10

20

30

40

50

ない。

#### 【 0 0 4 8 】

次に、第4絶縁層BANKとして、スピンドルコート法を用い、ポジ型感光性保護膜を形成し、ベーク処理を行った。第4絶縁層BANKの膜厚は1μmで、下部電極のエッジを3μm覆った。また、カソードコンタクトCHの周りも覆っている。この第4絶縁層BANKはバンクと称される層である。

#### 【 0 0 4 9 】

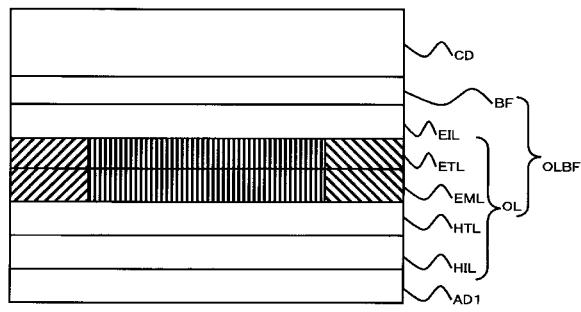

図6に、有機EL素子の概念図を示す。下部電極AD1の上に、ホール注入層HIL、ホール輸送層HTL、有機発光層OLE、電子輸送層ETL、電子注入層EIL、バッファ層BF、上部電極CDが積層された構造である。まず、下部電極AD1まで形成したガラス基板SUBをアセトン、純水の順に、それぞれ超音波洗浄を3分間行う。洗浄後、スピンドル乾燥させる。次に二元同時真空蒸着法にて、膜厚50nmのF4-TCNQと銅フタロシアニンの共蒸着膜を形成する。パターン形成はシャドウマスクを用いる。F4-TCNQと銅フタロシアニンのモル比は1:1とする。この共蒸着膜は正孔注入層HILとして機能する。

#### 【 0 0 5 0 】

次に、真空蒸着法により膜厚50nmの4,4'-ビス[N-(1-ナフチル)-N-フェニルアミノ]ビフェニル膜(以下、-NPD膜と略記)を形成する。パターン形成はシャドウマスクを用いる。蒸着領域は下部電極の各辺の1.2倍とする。この-NPD膜は正孔輸送層HTLとして機能する。その上に、二元同時真空蒸着法にて、膜厚20nmのトリス(8-キノリノール)アルミニウム(以下Alqと略記)とキナクリドン(以下Qcと略記)の共蒸着膜を形成した。蒸着速度を、40:1に制御して蒸着する。Alq+Qc共蒸着膜は、発光層EMLとして機能する。パターン形成はシャドウマスクを用いる。

#### 【 0 0 5 1 】

その上に、真空蒸着法により膜厚10nmのAlq膜を形成する。Alq膜は、電子輸送層ETLとして機能する。パターン形成はシャドウマスクを用いる。次に、電子注入層EILとして、二元同時真空蒸着法にてLiをドーピングしたAlq膜を10nm形成する。AlqとLiのモル比は1:1とする。パターン形成はシャドウマスクを用いる。バッファ層BFは、酸化バナジウムをEB蒸着により成膜する。膜厚は15nmとする。パターン形成は、シャドウマスクを用いる。蒸着後の酸化バナジウムの組成は、バナジウム1に対し酸素が2.2の比率であり、透過率は95%である。なお、このバッファ層は、ZnO, SnO<sub>2</sub>, WO<sub>3</sub>, MoO<sub>3</sub>, V<sub>2</sub>O<sub>5</sub>のいずれかを材料としてもよい。これらは上部電極CD材料よりも成膜時に分解生成する酸素が少ない酸化物を主成分とする層である。

#### 【 0 0 5 2 】

次に、スパッタリング法により、膜厚100nmのAlで第4電極層SUPを形成する。そして、パターンングすることにより、補助電極を形成する。このレイアウトは、後述する。また、この第4電極層SUPは、Alでなく、Cuや、これらの合金であってもかまわず、第5電極層CDよりも抵抗が小さく、このパターンングされた補助電極を挟んで第5電極上からシート抵抗を測定した場合、挟まない2点間シート抵抗よりも、挟んだ2点間の方が低いシート抵抗値を示すように形成されればよい。

#### 【 0 0 5 3 】

次に、スパッタリング法により、膜厚100nmのIn-Zn-O膜(以下、IZO膜と略記)を第4電極層SUPとして形成する。同膜は上部電極CD125として機能し、非晶酸化物膜である。ターゲットには、In/(In+Zn)=0.83であるターゲットを用いる。成膜条件は、Ar:O<sub>2</sub>混合ガスを雰囲気として真空度1Pa、スパッタリング出力を0.2W/cm<sup>2</sup>とする。In-ZnO膜からなる上部電極CDは陰極として機能し、その透過率は80%である。

#### 【 0 0 5 4 】

次に、スパッタリング法により、膜厚50nmのSiO<sub>x</sub>N<sub>y</sub>膜を形成した。同膜は保護層

10

20

30

40

50

として機能する。なお、この保護膜は図中省略してある。なお、ここで言う正孔注入層HILとは、陽極である下部電極ADと正孔輸送層HILの注入障壁を下げるため、適當なイオン化ポテンシャルを有する材料が望ましい。具体的には、鋼フタロシアニン、スターパーストアミン化合物、ポリアニリン、ポリチオフェン等が挙げられるが、これらに限定される訳ではない。また正孔注入層はホール供与性のドーパントがドーピングされていることが望ましい。ホール供与性のドーパントは具体的には2, 3, 5, 6-テトラフルオロ-テトラシアノキノジメタン(F4-TCNQ), 塩化鉄、ジシアノジグロロキノンが望ましい。また、もちろんこれらの材料に限られるわけではなく、また、これらの材料を2種以上併用しても差し支えない。

## 【0055】

ここで言う正孔輸送層HTLとは、正孔を輸送し、発光層へ注入する役割を有する。そのため、正孔移動度が高いことが望ましい。また、化学的に安定であることが望ましい。また、ガラス転移温度が高いことが望ましい。具体的には、N,N'-ビス(3-メチルフェニル)-N,N'-ジフェニル-[1,1'-ビフェニル]-4,4'-ジアミン(TPD)、4,4',4''-トリ(N-ナフチル)-N-フェニルアミノ]ビフェニル(-NPD)、4,4',4''-トリ(N-カルバゾリル)トリフェニルアミン(TCTA)、1,3,5-トリス[N-(4-ジフェニルアミノフェニル)フェニルアミノ]ベンゼン(p-DPA-TDAB)が望ましい。また、もちろんこれらの材料に限られるわけではなく、また、これらの材料を2種以上併用しても差し支えない。

## 【0056】

ここで言う発光層EMLとは、注入された正孔、電子が再結合し、材料固有の波長で発光する層をさす。発光層を形成するホスト材料自体が発光する場合とホストに微量添加したドーパント材料が発光する場合がある。異具体的なホスト材料としては、ジスチリルアリレン誘導体(DPVBi)，骨格にベンゼン環を有するシロール誘導体(2PSP)，トリフェニルアミン構造を両端に有するオキソジアゾール誘導体(EM2)，フェナンスレン基を有するベリノン誘導体(P1)，トリフェニルアミン構造を両端に有するオリゴチオフェン誘導体(BMA-3T)，ベリレン誘導体(tBu-PTC)，トリス(8-キノリノール)アルミニウム，ポリバラフェニレンビニレン誘導体，ポリチオフェン誘導体，ポリバラフェニレン誘導体，ポリシラン誘導体，ポリアセチレン誘導体が望ましい。また、もちろんこれらの材料に限られるわけではなく、また、これらの材料を2種以上併用しても差し支えない。

## 【0057】

次に、具体的なドーパント材料としては、キナクリドン、クマリン6、ナイルレッド、ルブレン、4-(ジシアノメチレン)-2-メチル-6-(パラ-ジメチルアミノスチリル)-4H-ピラン(DCM)，ジカルバゾール誘導体が望ましい。また、もちろんこれらの材料に限られるわけではなく、また、これらの材料を2種以上併用しても差し支えない。

## 【0058】

ここで言う電子輸送層ETLとは、電子を輸送し、発光層へ注入する役割を有する。そのため、電子移動度が高いことが望ましい。具体的には、トリス(8-キノリノール)アルミニウム，オキサジアゾール誘導体，シロール誘導体，亜鉛ベンゾチアゾール錯体が望ましい。また、もちろんこれらの材料に限られるわけではなく、また、これらの材料を2種以上併用しても差し支えない。

## 【0059】

ここで言う電子注入層EILとは、電子供与性ドーパントがドーピングされている有機化合物であり陰極から電子輸送層ETLへの電子注入効率を向上させるために用いる。電子供与性ドーパントは具体的には、リチウム、マグネシウム、カルシウム、ストロンチウム、バリウム、マグネシウム、アルミニウム、アルカリ金属化合物、アルカリ土類金属化合物、希土類金属化合物、アルカリ金属イオンを含有する有機金属錯体、アルカリ土類金属イオンを含有する有機金属錯体、希土類金属イオンを含有する有機金属錯体が望ましい。

10

20

30

40

50

。また、もちろんこれらの材料に限られるわけではなく、また、これらの材料を2種以上併用しても差し支えない。電子注入層EILのホスト材料としては具体的には、トリス(8-キノリノール)アルミニウム、オキサジアゾール誘導体、シロール誘導体、亜鉛ベンゾチアゾール錯体が望ましい。また、もちろんこれらの材料に限られるわけではなく、また、これらの材料を2種以上併用しても差し支えない。

#### 【0060】

上記構成において、電子注入層EIL、或いは正孔注入層HILを有さない構造も考えられる。また、電子輸送層ETL、或いは正孔輸送層HTLを有さない構造も考えられる。すなわちバッファ層は、有機発光層EMLと接する場合、電子輸送層ETLに接する場合、電子注入層EILに接する場合の3通りある。

10

#### 【0061】

下部電極AD1に用いられる陽極材料は、正孔の注入効率を高める仕事関数の大きな導電膜が望ましい。具体的には、モリブデン、ニッケル、クロム等の金属や、これら金属を用いた合金や、ポリシリコン、アモルファスシリコン、錫酸化物、酸化インジウム、インジウム・錫酸化物(ITO)等の無機材料が挙げられるが、これらの材料に限定されるわけではない。

#### 【0062】

In<sub>2</sub>O<sub>3</sub>-SnO<sub>2</sub>系導電膜では、スパッタ法において、基板温度を200度程度まで高めた条件で作製すると多結晶状態になる。多結晶状態では、結晶粒内と結晶粒界面において、エッチング速度が異なるため、下部電極AD1に用いる場合はアモルファス状態が望ましい。

20

#### 【0063】

また、下部電極AD1が陰極、上部電極CDが陽極の構成も考えられる。この場合、下部電極AD1、電子注入層EIL、電子輸送層ETL、発光層EML、正孔輸送層HTL、正孔注入層HIL、上部電極CDの順に積層される。上記構成において、電子注入層EIL、或いは正孔注入層HILを有さない構造も考えられる。また、電子輸送層ETL、或いは正孔輸送層HTLを有さない構造も考えられる。すなわちバッファ層は、有機発光層EMLと接する場合、正孔輸送層HTLに接する場合、正孔注入層EILに接する場合の3通りある。

30

#### 【0064】

下部電極AD1が陰極として用いられる場合、陰極材料は、電子の注入効率を高める仕事関数の小さな導電膜が望ましい。具体的には、アルミニウム、アルミニウム・ネオジウム合金、マグネシウム・銀合金、アルミニウム・リチウム合金、アルミニウム・カルシウム合金、アルミニウム・マグネシウム合金、金属カルシウム、セリウム化合物等が挙げられるが、これらの材料に限定されるわけではない。

#### 【0065】

上部電極CDが陽極として用いられる場合、陽極材料は、酸化インジウムを主原料とする酸化物が上げられる。特にIn<sub>2</sub>O<sub>3</sub>-SnO<sub>2</sub>系透明導電膜、In<sub>2</sub>O<sub>3</sub>-ZnO系透明導電膜が望ましい。透明導電膜の製造法は、スパッタ法、対向ターゲット式スパッタ法、EB蒸着法、イオンプレーティング法等が挙げられる。

40

#### 【0066】

上部電極CD成膜時に上部電極CDの構成材料である酸化物が一部分解し、生成された酸素ラジカルが有機膜を酸化し、発光電圧を上昇させる。詳細に検討した結果上部電極CDよりも酸素結合力が強い導電性酸化物を主成分としたバッファ層を有機膜と上部電極CDの間に設けることで、上部電極CD形成時における有機膜酸化による発光電圧上昇を低減できる。

#### 【0067】

上部電極CDよりも酸素結合力が強い導電性酸化物を主成分としたバッファ層BFは、例えば酸化インジウムを主成分とした上部電極CDを用いる場合、酸化バナジウム、酸化モリブデン、酸化タンゲステン、酸化タンタル、酸化チタニウム、酸化ニオブ、酸化クロ

50

ム等を主成分とした材料が挙げられる。一方、酸化ゲルマニウム、酸化銅、酸化ルテニウム等を主成分とした材料は酸化インジウムよりも酸素との結合力が弱く、バッファ層成膜時に上部電極CD成膜時よりも多く酸素ラジカルを生成してしまうため、発光電圧上昇を抑制できない。

#### 【0068】

また、バッファ層BFのことを言い換えると、有機層OLEと上部電極CDとの間に、融点近傍に置ける生成ギブズエネルギーが上部電極CDの構成材料よりも低い酸化物を主成分とする層と称することができる。融点付近での生成ギブズエネルギーが上部電極CD材料の主原料よりも低い材料をバッファ層用いることで、成膜前および成膜初期に分解生成される酸素ラジカル量も減らすことができ、有機層の酸化をより低減できる。

10

#### 【0069】

また、さらに言い換えると、有機層と上部電極CDとの間に形成された、融点近傍に置ける生成ギブズエネルギーが $-300\text{ kJ/mol}$ よりも低い酸化物を主成分とする層と称することもできる。生成ギブズエネルギーが $-300\text{ kJ/mol}$ 以下の材料を、バッファ層BFに用いることで電圧上昇は1V以下に抑えることができる。

#### 【0070】

また、バッファ層BFは比抵抗が $1 \times 10^7 \cdot \text{cm}$ 以下の酸化物を主成分とする材料からなり、膜厚は $5\text{ nm} \sim 50\text{ nm}$ が好ましい。バッファ層に比抵抗が $1 \times 10^7 \cdot \text{cm}$ 以上の材料を用いた場合、高輝度発光時のバッファ層での電圧降下は0.1V以上と大きくなり、酸化防止の効果が相殺されてしまい、また膜厚を $5\text{ nm}$ 以上にすることで、有機膜酸化を抑制できるが、 $50\text{ nm}$ 以上厚くすると透過率低下による効率低下が無視できなくなるため、このような構成としたものである。

20

#### 【0071】

また、上部電極CDを陽極とした場合、バッファ層はバナジウム酸化物を主成分とするものが好ましい。上部電極CDを陽極とし、バナジウム酸化物を、バッファ層を用いることで電圧上昇はほぼ0Vに抑えることができる。バナジウム酸化物の組成は、バナジウムに対し、酸素が2~5の割合であることが望ましい。また、上部電極CDを陽極とし、バッファ層に酸化バナジウムを用いた場合、酸化バナジウムは正孔輸送層の機能も有するため、正孔輸送層HTL、正孔注入層HILなしに、直接発光層EMLに正孔を供給することが可能となる。

30

#### 【0072】

また、上部電極CD上に保護層は、上部電極CD上に形成され、大気内 $\text{H}_2\text{O}$ 、 $\text{O}_2$ が上部電極CD、或いはその下の有機層に入りこむことを防ぐことを目的とするもので、 $\text{SiO}_2$ 、 $\text{SiN}_x$ 、 $\text{SiO}_x\text{N}_y$ 、 $\text{Al}_2\text{O}_3$ 等の無機材料やポリプロピレン、ポリエチレンテレフタレート、ポリオキシメチレン、ポリビニルクロライド、ポリフッ化ビニリデン、シアノエチルプルラン、ポリメチルメタクリレート、ポリサルファン、ポリカーボネート、ポリイミド等の有機材料が挙げられるが、これらの材料に限定されるわけではない。

#### 【0073】

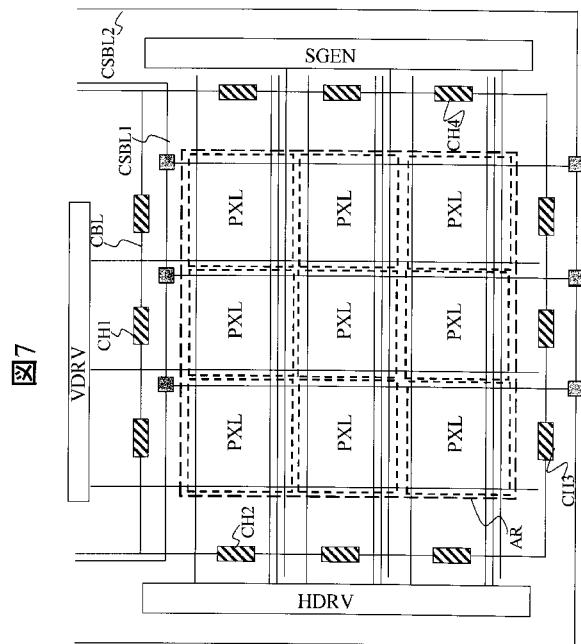

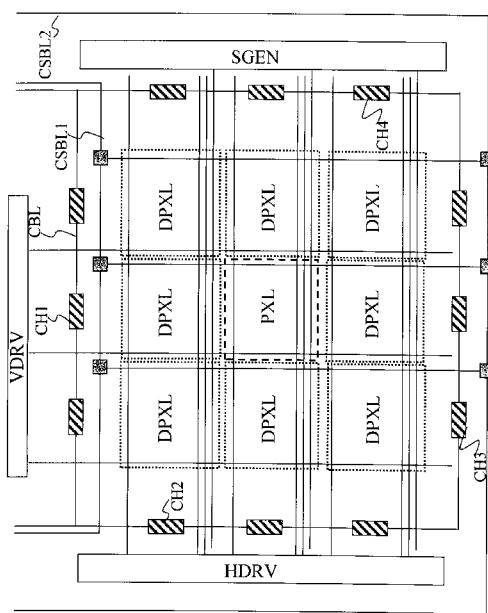

図7に、図4をさらに詳細に示した第1基板SUB1上のブロック構成図を示す。なお、説明を簡単にするために、 $3 \times 3$ の9画素PXLの場合を示しているが、本発明は、VGAやXGAといった高精細表示装置をも対象とするものであることは言うまでもない。

40

#### 【0074】

有効表示領域ARの上に配置された垂直系駆動回路VDRVからは、階調信号線DATAを含む複数の垂直系配線が延在している。この垂直系配線は第2電極層SDで構成されている。有効表示領域ARの上下に左右に延在している第1及び第2電流供給バスラインCSBL1、2からは縦方向、つまり垂直方向に第2電極層の電極で構成された電流供給線CSLが延在している。水平系駆動回路HDRVからは、3種類の信号を供給するために、1つの画素PXL行あたり3本の配線が延在している。この配線は第1電極層SGで構成されている。

#### 【0075】

50

電流供給バスライン C S B L は、概ね第 2 電極層 S D で構成されているが、垂直系駆動回路 V D R V との交差部だけ第 1 電極層 S G に迂回している。電流供給線 C S L は、垂直系駆動回路 V D R V に沿って形成され、第 2 電極層 S D で構成されている。

#### 【 0 0 7 6 】

カソードバスライン C B L は、垂直系駆動回路 V D R V の左右を通過し、有効表示領域 A R の外側の上（図 5 の場合、有効表示領域 A R から垂直系駆動回路 V D R V へ向かう方向）下左右に引き回されている。このカソードバスライン C B L には、垂直系駆動回路 V D R V や電流供給線 C S L の垂直方向に延在している配線グループの間や、水平系駆動回路 H D R V から延在している 3 本の配線と三角波発生回路 S G E N から延在している一本の配線の水平方向に延在している配線グループの間にコンタクトホール C H 1 ~ C H 4 を備えている。第 1 コンタクトホール C H 1 は、第 2 電流供給バスライン C S B L と有効表示領域 A R の間、第 2 コンタクトホール C H 2 は、水平系駆動回路 H D R V と有効表示領域 A R の間、第 3 コンタクトホール C H 3 は、第 2 電流供給バスライン C S B L 2 と有効表示領域 A R の間、第 4 コンタクトホール C H 4 は、三角波発生回路 S G E N と有効表示領域 A R との間に配置されている。

#### 【 0 0 7 7 】

このカソードバスライン C B L を第 2 電極層 S D で形成する場合、他の同層配線と交差する場合、第 1 電極層 S G や第 3 電極層に迂回させる。また、このカソードバスライン C B L を第 3 電極層で形成する場合、他の同層配線と交差する場合、第 2 電極層 S D や第 3 電極層に迂回させる。

#### 【 0 0 7 8 】

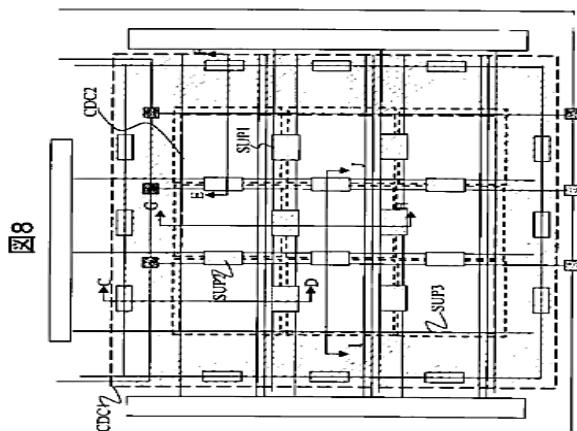

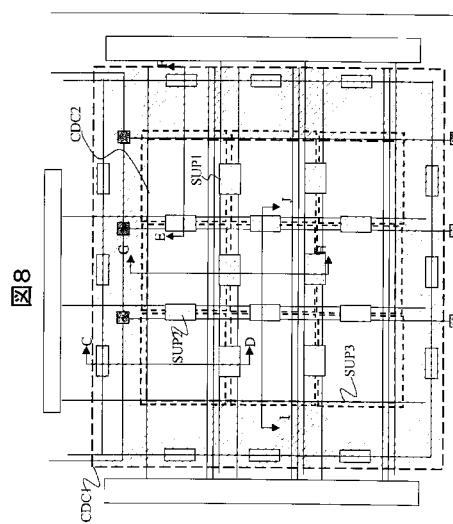

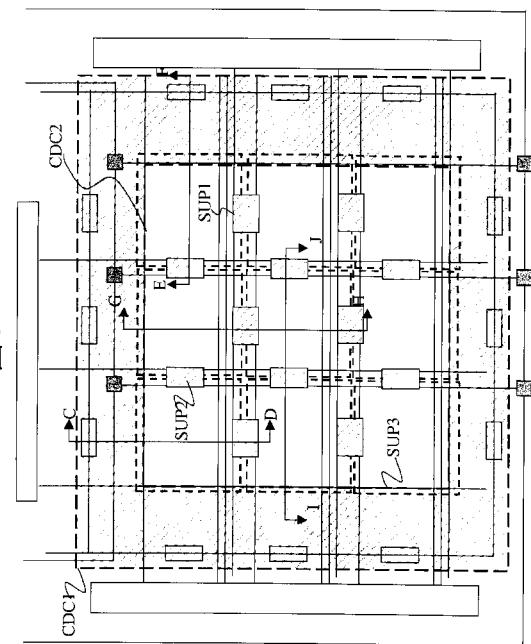

図 8 は、補助電極の配置を示した第 1 基板 S U B 1 のブロック図である。この図 8 では、表示画素 P X L の最も外縁を構成する画素 P X L の外側の全てにカソードコンタクト C H 1 ~ 4 を設けている。また、画素 P X L と画素 P X L の全ての間に第 1 、第 2 補助電極 S U P 1 、 S U P 2 が形成されている。水平方向に隣接した画素 P X L 間のバンクの上にある第 1 補助電極 S U P 1 は、垂直方向に延在した長方形をしている。そして、この第 1 補助電極 S U P 1 は、垂直方向に、破線状に複数列並んでいる。この実施例では、破線の実線部は発光領域の横と同じ長さ、破線の間隔は非発光領域の横と同じ長さである。垂直方向に隣接する画素 P X L 間のバンク上にある第 2 補助電極 S U P 2 は、水平方向に延在した長方形をしている。そして、この第 2 補助電極 S U P 2 は、垂直方向に、破線状に複数列並んでいる。この実施例では、破線の実線部は発光領域の縦の長さと同じ長さ、破線の間隔は非発光領域の縦の長さと同じ長さである。

#### 【 0 0 7 9 】

第 1 補助電極 S U P 1 及び第 2 補助電極 S U P 2 によって、それらの延在方向で生じる電圧降下を抑制できるので、それぞれの方向の輝度ムラを抑制できる。有効表示領域 A R の周囲にある第 3 補助電極 S U P 3 は、第 1 形成領域線 C D C 1 から、額縁、枠状に、有効表示領域 A R の外側から最外周の画素 P X L のバンク上の、第 2 形成領域 C D C 2 まで形成されている。この第 3 補助電極 S U P 3 は、各画素 P X L の外側にある第 1 ~ 第 4 カソードコンタクト C H 1 ~ 4 によって共通電圧 V C O M が供給されている。第 3 補助電極 S U P 3 を備えていることにより、水平及び垂直方向で生じる電圧降下を抑制できるので、水平及び垂直方向における輝度ムラを抑制できる。また、この水平及び垂直方向に延びる第 3 補助電極 S U P 3 に対して水平及び垂直方向にカソードコンタクト C H が点在しているので、電圧降下の抑制もさらに可能である。上部電極 C D は、各画素 P X L 共通で、第 1 形成領域線 C D C 1 を越えて第 2 形成領域線 C D C 2 まで延びている。

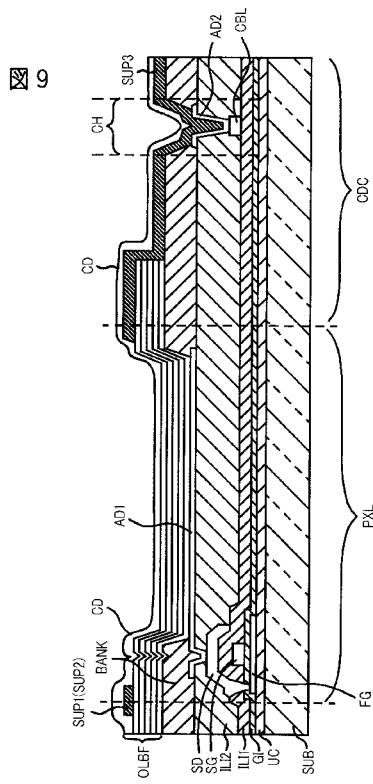

#### 【 0 0 8 0 】

図 9 、図 10 に、図 8 の C - D 、 E - F , G - H 、 I - J における第 1 基板 S U B 1 の断面構造を示す。図 9 は、図 8 の C - D 、 E - F における第 1 基板 S U B 1 の断面構造である。図 9 の左側に画素領域 P X L の断面構造、右側にカソードコンタクト C D C 領域の断面構造を示す。基本的な層構造は、図 5 と同じである。カソードコンタクト領域 C D C は、第 1 形成領域線 C D C 1 から第 2 形成領域線 C D C 2 までの領域から画素領域 P X L

10

20

30

40

50

に含まれる部分を除外した構造である。

#### 【0081】

画素領域 P X L には、ゲート電極が第 1 電極層 S G で構成され、ソースドレイン電極が第 2 電極層 S D で構成された薄膜トランジスタ上の第 3 絶縁層 I L I 2 、薄膜トランジスタのソースドレイン電極に接続された下部電極 A D 1 、下部電極 A D 1 間を区切るバンク B A N K 、下部電極 A D 1 上に形成された有機層 E M L とバッファ層を含む機能層 O L B F 、第 1 補助電極 S U P 1 、第 2 補助電極 ( S U P 2 ) 、全画素 P X L 共通の上部電極 C D 、第 3 補助電極 S U P 3 の一部が形成されており、バンクは、この下部電極 A D 上に開口があり、下部電極 A D の周囲及び第 3 絶縁層 I L I 2 の上を被い、カソードコンタクト領域のコンタクトホール C H の先まで延びている。

10

#### 【0082】

カソードコンタクト領域 C D C は、画素領域 P X L から伸びる機能層 O L B F 、第 3 補助電極 S U P 3 層、上部電極 C D 層が第 3 絶縁膜上に形成され、コンタクトホール部 C H では、下部電極 A D 1 と同層、つまり、第 3 電極層の中継電極 A D 2 が形成されている。したがって、コンタクトホール C H では、第 2 電極層 S D で構成されたカソードバスライン C B L 、カソードバスライン C B L のコンタクトパッド P A D の上に形成された第 3 電極層 A D で構成された中継電極 A D 2 、中継電極 A D 2 の上に形成した第 3 補助電極 S U P 3 を構成する第 4 電極層 S U P と、上部電極 C D を構成する第 5 電極層 C D の積層体となっている。

20

#### 【0083】

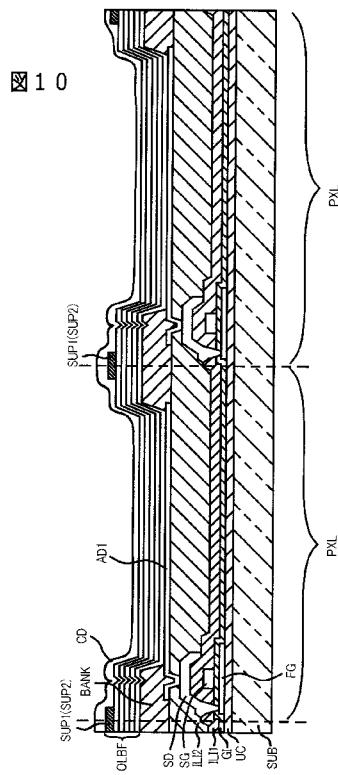

図 10 は、図 8 の G - H 、 I - J における第 1 基板 S U B 1 の断面構造である。画素 P X L 領域 P X L が二つ並んでいる構造の断面図である。

#### 【0084】

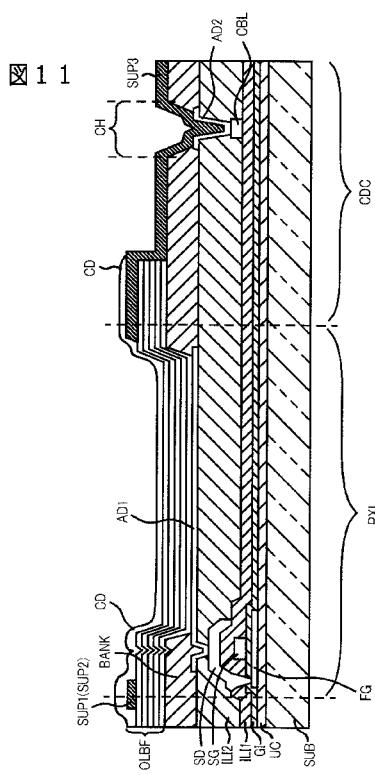

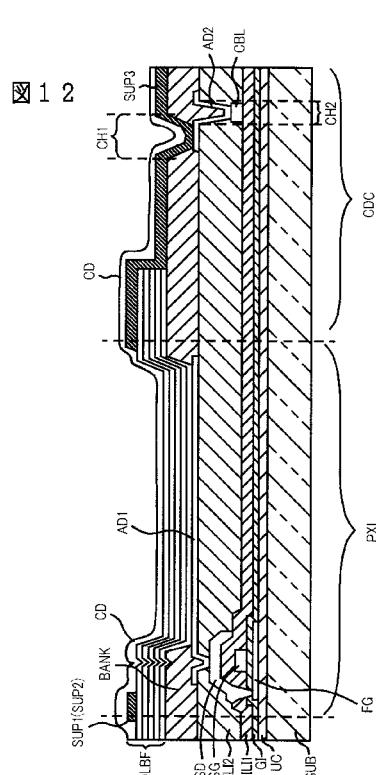

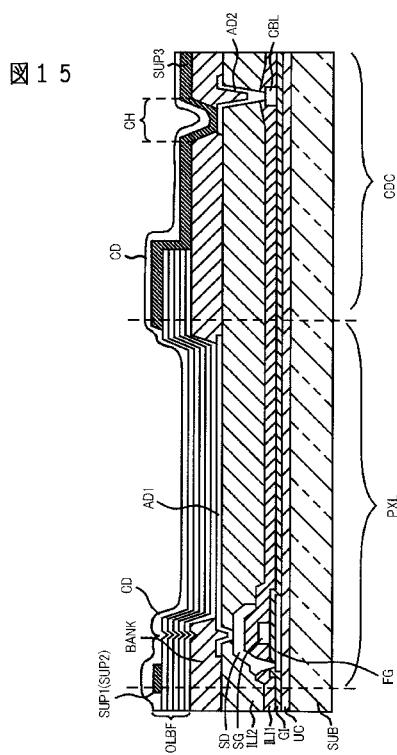

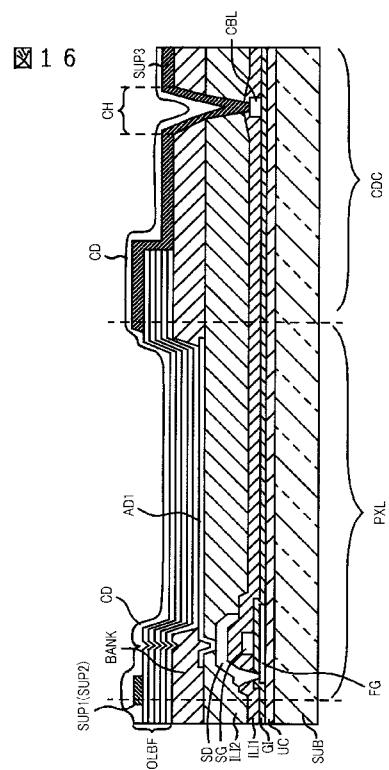

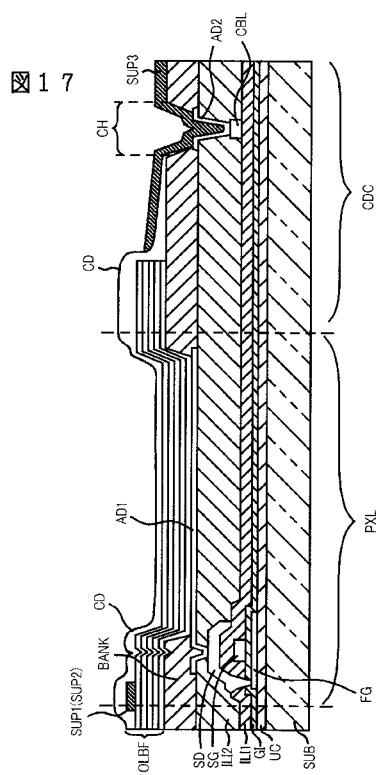

図 11 、図 12 、図 13 、図 14 、図 15 、図 16 、図 17 に、図 7 の C - D 、 E - F における第 1 基板 S U B 1 の断面構造例を示す。図 11 が図 9 と異なる点は、上部電極 C D を機能層 O L B F とほぼ同一パターンとしている点です。図 12 が図 9 と異なる点は、バンクの開口部であるバンク内の第 1 コンタクトホール C H 1 と、第 3 絶縁層 I L I 2 の開口部である第 2 コンタクトホール C H 2 を平面方向にずらしている点です。第 3 絶縁層 I L I 2 の厚みやバンク B A N K の厚みが厚い場合、コンタクトホールのテーパ角が急峻になったり、中継電極 A D 2 、第 3 補助電極 S U P 3 及び上部電極 C D で接続不良が生じたりする可能性があるが、このように平面方向にずらすことによって、接続信頼性を向上できる。

30

#### 【0085】

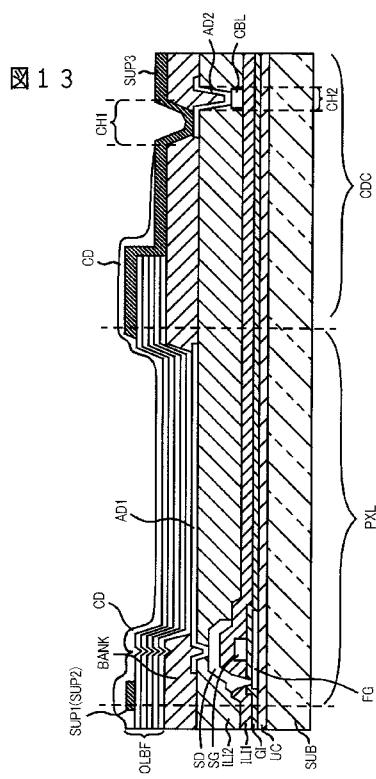

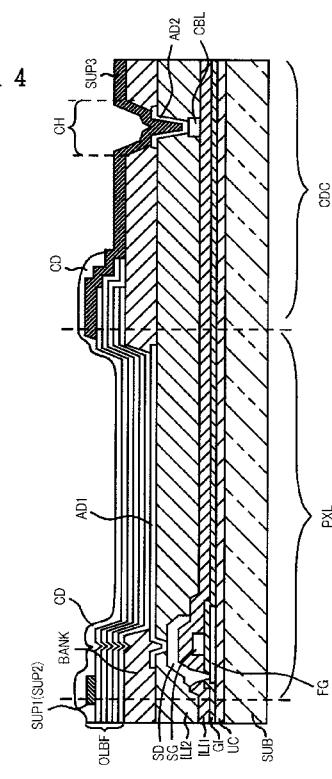

図 13 が図 12 と異なる点は、第 1 コンタクトホール C H 1 の直前まで上部電極 C D を形成している点です。図 14 が図 9 と異なる点は、機能層 O L B F のうち少なくとも 1 層をはみ出させた構造をしている点と、そのはみ出した位置まで上部電極 C D を覆っている点である。図 15 が図 12 と異なる点は、第 2 電極層 S D にカソードバスライン C B L を形成するのではなく、第 1 電極層 S G にカソードバスライン C B L を形成している点である。図 16 が図 9 と異なる点は、第 2 電極層 S D にカソードバスライン C B L を形成するのではなく、第 1 電極層 S G にカソードバスライン C B L を形成している点である。図 17 が図 9 と異なる点は、上部電極 C D をカソードコンタクト C H の手前まで形成し、その上に補助電極を形成している点である。

40

#### 【0086】

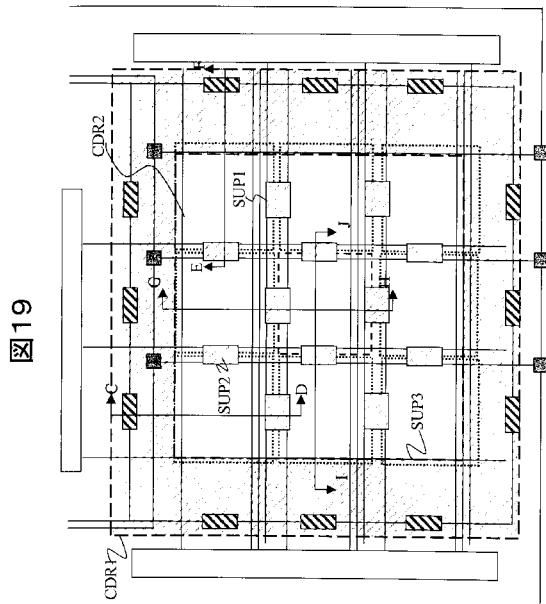

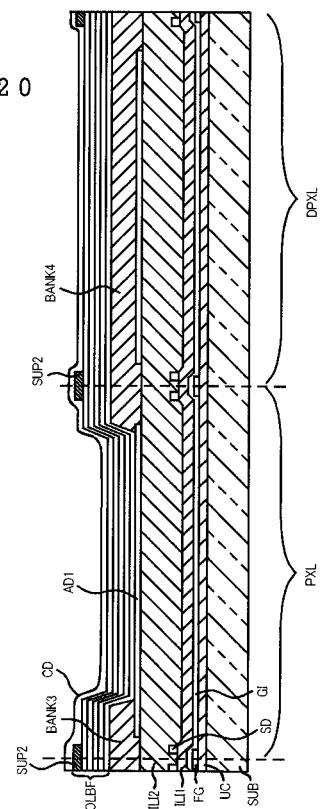

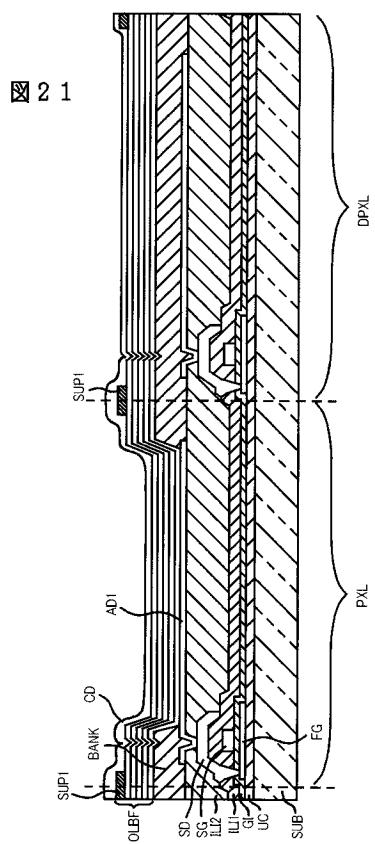

図 18 、図 19 に、ダミー画素 D P X L がある場合の第 1 基板 S U B 1 のブロック図を示す。図 18 が図 7 と異なる点は、最外周の画素がダミー画素 D P X L になっている点である。図 19 が図 8 と異なる点も、最外周の画素がダミー画素 D P X L になっている点である。両図とも、ダミー画素 D P X L には開口がありません。

#### 【0087】

図 20 に、図 19 の G - H における第 1 基板 S U B 1 の断面構造例を示す。図 20 は、水平方向に隣接したダミー画素 D P X L と表示画素 P X L の 2 画素 P X L 分の断面図であ

50

る。図21に、図19のI-Jにおける第1基板SUB1の断面構造例を示す。

#### 【0088】

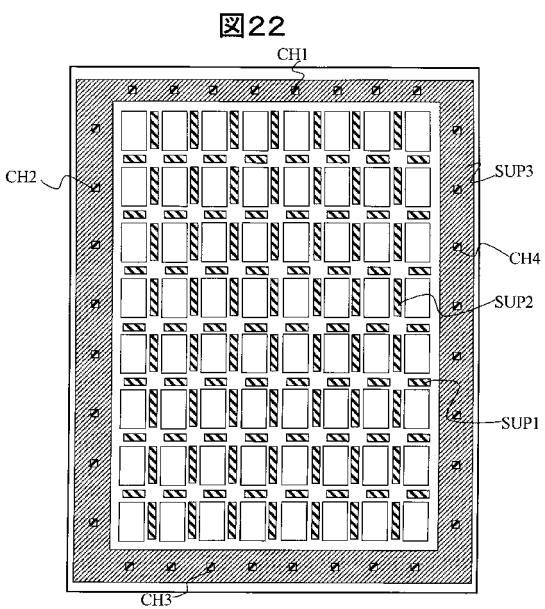

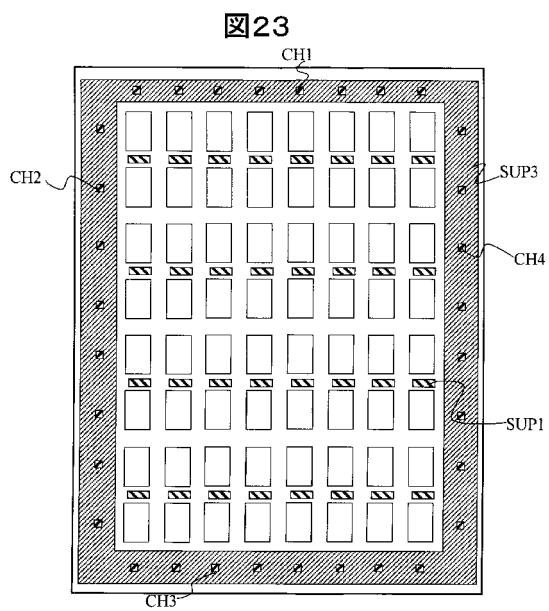

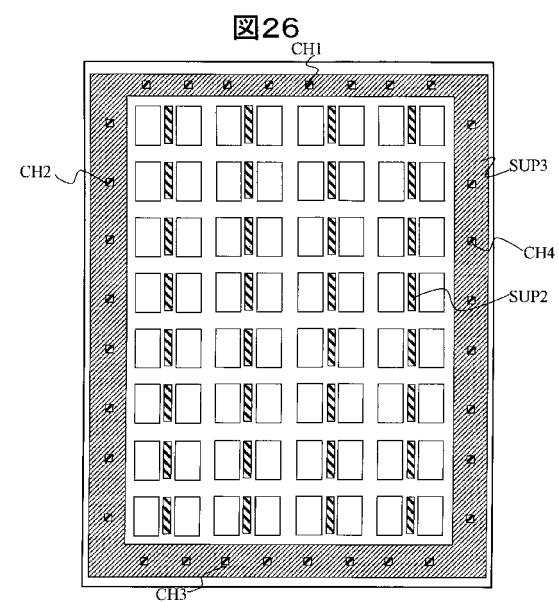

図22から図31は、補助電極の平面レイアウトを説明する平面図である。図22の構造は、有効表示領域(AR)の周囲に第3補助電極SUP3を枠状に形成してその垂直方向、水平方向の4辺にそれぞれコンタクトホール(カソードコンタクト)CH(CH1、CH2、CH3、CH4)でカソードバスラインCBL(例えば、図18参照)に接続されている。カソードコンタクトCHは有効表示領域(AR)に配列された矩形の画素PXL(図7参照)の行、列単位に形成されている。また、各画素PXLの間に第1補助電極SUP1と第2補助電極SUP2を形成している。第1補助電極SUP1は、垂直方向(図の上下方向)に隣接した画素PXLの間のバンク上に形成された補助電極で、水平方向に延在した矩形の電極である。各画素PXLの上下、および左右(水平方向)の位置で画素PXL単位に独立している。第2補助電極SUP2は、水平方向に隣接した画素PXLの間のバンク上に形成された補助電極で、垂直方向に延在した矩形の電極で、各画素PXLの上下左右の位置で画素PXL単位に独立している。ただし、全ての画素PXL間にある必要はなく、形成単位もバンク上であれば、発光領域間に必要はない。つまり、発光領域間に第1補助電極SUP1がない領域と、発光領域間に第1補助電極SUP1がある領域を並存させるレイアウトとしてもよい。

10

#### 【0089】

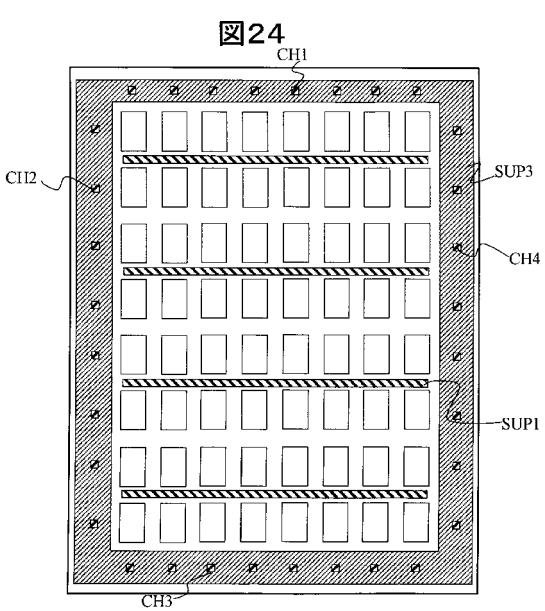

図23が図22と異なる点は、図22に示した第2補助電極SUP2を形成していない点である。図24が図23と異なる点は、全ての第1補助電極SUP1を接続している点である。なお、全て接続しなくとも、任意の第1補助電極SUP1を接続してもよい。つまり、垂直方向にx個の画素PXLがあり、垂直方向に第1補助電極SUP1がy個あるとすると、 $x > y$ の関係となるようにしてもよい。

20

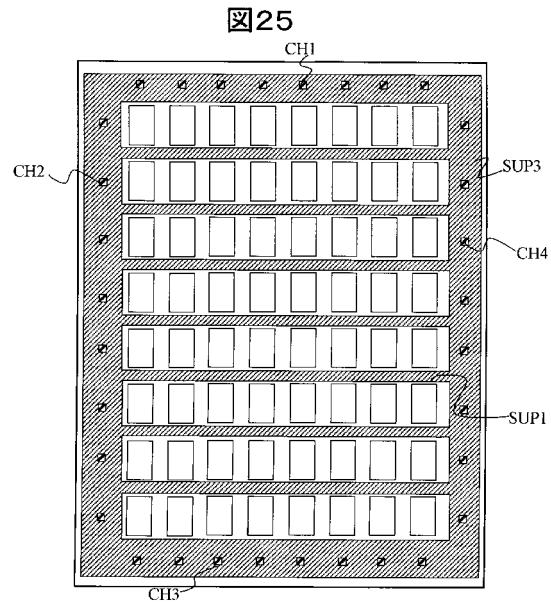

#### 【0090】

図25が図24と異なる点は、全ての第1補助電極SUP1と第3補助電極SUP3を接続している点である。図25では、全ての第1補助電極SUP1と第3補助電極SUP3を接続しているが、必ずしも全てである必要はなく、少なくとも一つの第1補助電極SUP1と第3補助電極SUP3が接続されればよい。

30

#### 【0091】

図26が図22と異なる点は、図22に示した第1補助電極SUP1を形成していない点である。

#### 【0092】

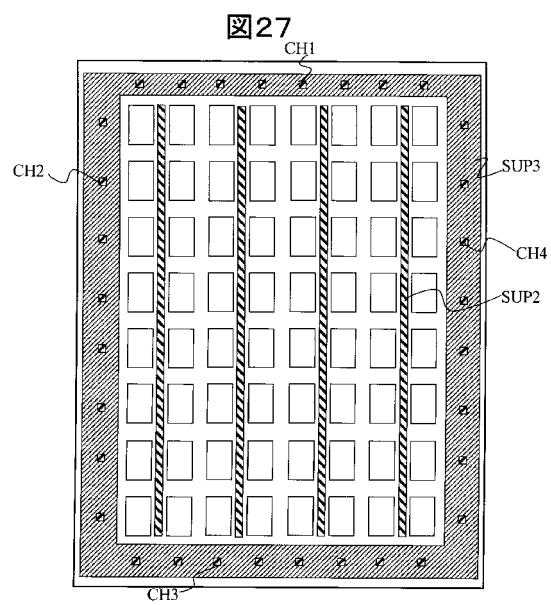

図27が図26と異なる点は、全ての第2補助電極SUP2を接続している点である。なお、全て接続しなくとも、任意の第2補助電極SUP2を接続してもよい。つまり、水平方向にv個の画素PXLがあり、水平方向に第2補助電極SUP2がw個あるとすると、 $v > w$ の関係となるようにしてもよい。

40

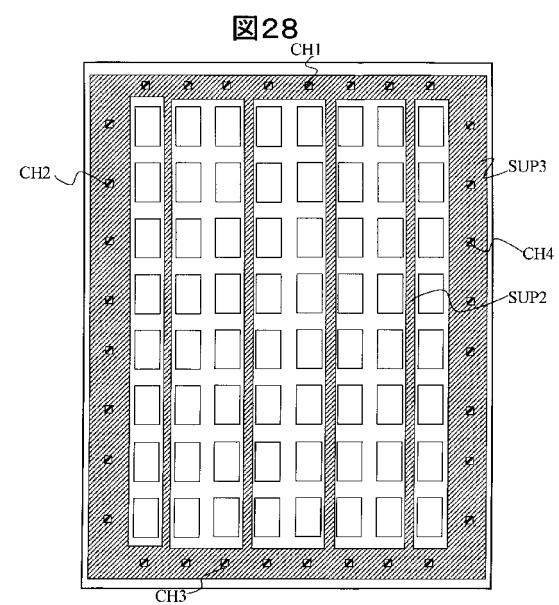

#### 【0093】

図28が図27と異なる点は、全ての第2補助電極SUP2と第3補助電極SUP3を接続している点である。この図28では、全ての第2補助電極SUP2と第3補助電極SUP3を接続しているが、必ずしも全てである必要はなく、少なくとも一つの第1補助電極SUP1と第3補助電極SUP3が接続されればよい。

#### 【0094】

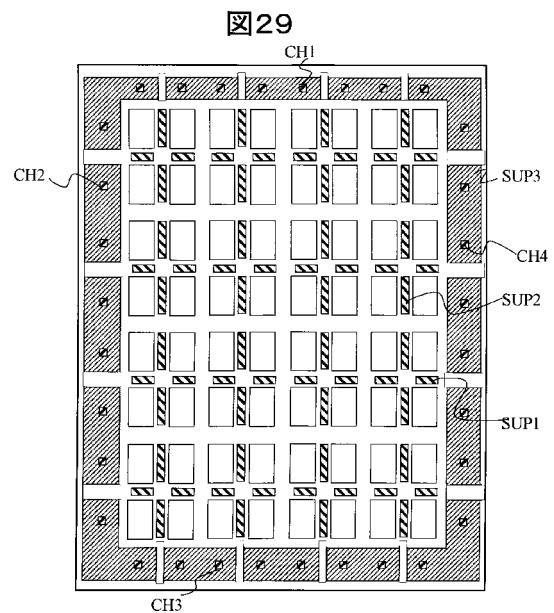

図29が図22と異なる点は、第3補助電極SUP3を分離している点である。この分離箇所は、図29の場合、4つの辺全てで分離しているが、いずれかの辺で分離されればよい。また、分離箇所も2画素PXLにつき1箇所としているが、必ずしもこれに限らず、1画素PXLにつき1箇所、複数画素PXLにつき1箇所の割合でも構わない。また、分離箇所も発光領域間の水平垂直方向の位置ではなく、発光領域の水平垂直方向の位置でもよい。

#### 【0095】

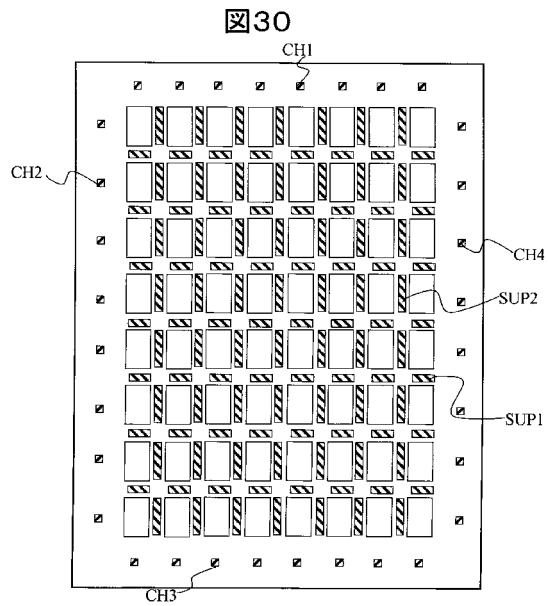

図30が図22と異なる点は、第3補助電極SUP3を形成していない点である。

50

## 【0096】

図31が図28と異なる点は、第3補助電極SUB3に設ける分離部を第2補助電極SUB2の延在方向、つまり、有効表示領域ARの垂直方向にのみ設けている点である。

## 【図面の簡単な説明】

## 【0097】

【図1】OLEDの外観斜視図である。

【図2】本発明の有機EL表示装置の断面図である。

【図3】第1基板SUB1と第2基板SUB2のブロック図を示す。

【図4】第1基板SUB1上のブロック構成図である。

【図5】第1基板SUB1の層構造図である。

【図6】有機EL素子の概念図である。

【図7】第1基板SUB1上のブロック構成図である。

【図8】補助電極を印した第1基板SUB1上のブロック構成図である。

【図9】図7のC-D、E-Fにおける第1基板SUB1の断面構造図である。

【図10】図7のG-H、I-Jにおける第1基板SUB1の断面構造図である。

【図11】図7のC-D、E-Fにおける第1基板SUB1の断面構造図である。

【図12】図7のC-D、E-Fにおける第1基板SUB1の断面構造図である。

【図13】図7のC-D、E-Fにおける第1基板SUB1の断面構造図である。

【図14】図7のC-D、E-Fにおける第1基板SUB1の断面構造図である。

【図15】図7のC-D、E-Fにおける第1基板SUB1の断面構造図である。

【図16】図7のC-D、E-Fにおける第1基板SUB1の断面構造図である。

【図17】図7のC-D、E-Fにおける第1基板SUB1の断面構造図である。

【図18】ダミー画素DPXLPIXLがある場合の第1基板SUB1のブロック図である。

。

【図19】補助電極を印した第1基板SUB1のブロック図である。

【図20】図19のG-H、I-Jにおける第1基板SUB1の断面構造例である。

【図21】図20のI-J C-D、E-Fにおける第1基板SUB1の断面構造例である。

。

【図22】補助電極の平面レイアウト図である。

【図23】補助電極の平面レイアウト図である。

【図24】補助電極の平面レイアウト図である。

【図25】補助電極の平面レイアウト図である。

【図26】補助電極の平面レイアウト図である。

【図27】補助電極の平面レイアウト図である。

【図28】補助電極の平面レイアウト図である。

【図29】補助電極の平面レイアウト図である。

【図30】補助電極の平面レイアウト図である。

【図31】補助電極の平面レイアウト図である。

## 【符号の説明】

## 【0098】

SUB1・・・第1基板、SUB2・・・第2基板と、FF・・・前フレーム、BF

・・・裏フレームBF、FPC1・・・フレキシブル回路基板、SUB3・・・第3基板

、OLBF・・・機能層。

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

图6

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

---

フロントページの続き

(72)発明者 松浦 利幸

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

F ターム(参考) 3K107 AA01 BB01 CC02 CC33 DD03 DD22 DD29 DD37 DD39 DD44X

DD46X DD46Y DD91 EE03 FF04

|                |                                                                                                                                                                         |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机EL表示装置                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2007287354A</a>                                                                                                                                           | 公开(公告)日 | 2007-11-01 |

| 申请号            | JP2006110141                                                                                                                                                            | 申请日     | 2006-04-12 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 日立显示器有限公司                                                                                                                                                               |         |            |

| [标]发明人         | 坂元博次<br>加藤真一<br>寺門正倫<br>松浦利幸                                                                                                                                            |         |            |

| 发明人            | 坂元 博次<br>加藤 真一<br>寺門 正倫<br>松浦 利幸                                                                                                                                        |         |            |

| IPC分类号         | H05B33/26 H01L51/50 H05B33/28 H05B33/12 H05B33/22                                                                                                                       |         |            |

| CPC分类号         | H01L27/3276 H01L27/3246 H01L51/5228                                                                                                                                     |         |            |

| FI分类号          | H05B33/26.Z H05B33/14.A H05B33/28 H05B33/12.B H05B33/22.Z H01L27/32                                                                                                     |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC02 3K107/CC33 3K107/DD03 3K107/DD22 3K107/DD29 3K107/DD37 3K107/DD39 3K107/DD44X 3K107/DD46X 3K107/DD46Y 3K107/DD91 3K107/EE03 3K107/FF04 |         |            |

| 代理人(译)         | 小野寺杨枝                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                               |         |            |

### 摘要(译)

要解决的问题：提供一种具有高显示质量的有机EL显示装置。解决方案：该有机EL显示装置具有多个有源元件和多个有机EL元件，这些有机EL元件通过由基板上的有源元件控制而发光。下部电极，有机层和上部电极CD从有机EL元件中的基板侧依次层叠，并且多个有机EL元件中的上部电极CD是所有有机EL元件中的公共电极。金属电极设置在上电极CD和有机层之间，并且使夹在金属电极上的上电极CD上的两点之间的薄层电阻小于不夹住金属电极的两点之间的薄层电阻。