(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-209074

(P2006-209074A)

(43) 公開日 平成18年8月10日(2006.8.10)

| (51) Int.C1.                 | F 1       | テーマコード (参考) |

|------------------------------|-----------|-------------|

| <b>G09G 3/30</b> (2006.01)   | G09G 3/30 | J 3K007     |

| <b>G09G 3/20</b> (2006.01)   | G09G 3/20 | 624B 5C080  |

| <b>H01L 51/50</b> (2006.01)  | G09G 3/20 | 641C 5F110  |

| <b>H01L 29/786</b> (2006.01) | G09G 3/20 | 611H        |

| <b>H01L 21/336</b> (2006.01) | G09G 3/30 | K           |

審査請求 未請求 請求項の数 17 O L (全 25 頁) 最終頁に続く

|              |                              |            |                                                                                         |

|--------------|------------------------------|------------|-----------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2005-245049 (P2005-245049) | (71) 出願人   | 000006633<br>京セラ株式会社<br>京都府京都市伏見区竹田鳥羽殿町6番地                                              |

| (22) 出願日     | 平成17年8月25日 (2005.8.25)       | (74) 代理人   | 100089118<br>弁理士 酒井 宏明                                                                  |

| (31) 優先権主張番号 | 特願2004-252753 (P2004-252753) | (72) 発明者   | 高杉 親知<br>神奈川県大和市下鶴間1623-14 株式会社京セラディスプレイ研究所内                                            |

| (32) 優先日     | 平成16年8月31日 (2004.8.31)       | (72) 発明者   | 草深 黒<br>神奈川県大和市下鶴間1623-14 株式会社京セラディスプレイ研究所内                                             |

| (33) 優先権主張国  | 日本国 (JP)                     | F ターム (参考) | 3K007 AB17 BA06 DB03 GA00<br>5C080 AA06 BB05 DD05 EE29 FF11<br>HH09 JJ03 JJ04 JJ05 JJ06 |

| (31) 優先権主張番号 | 特願2004-377348 (P2004-377348) |            |                                                                                         |

| (32) 優先日     | 平成16年12月27日 (2004.12.27)     |            |                                                                                         |

| (33) 優先権主張国  | 日本国 (JP)                     |            |                                                                                         |

最終頁に続く

(54) 【発明の名称】画像表示装置およびその駆動方法

## (57) 【要約】

【課題】寄生容量による輝度のバラツキを防止すること。

【解決手段】通電により発光する有機EL素子OLEDと、ゲート(第1端子)、ドレイン(第2端子)、ソースを備え、ゲートとドレインとの間に印加される所定の駆動閾値よりも高い電位差に応じて有機EL素子OLEDを制御する駆動トランジスタTdと、駆動トランジスタTdのゲートとドレインとの間に於ける駆動閾値に対応した閾値電圧を検出する閾値電圧検出用トランジスタTthと、駆動トランジスタTdに接続された可変容量Ccとを備えるように構成する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

通電により発光する発光手段と、

少なくとも第1端子、第2端子を備え、前記第1端子と前記第2端子との間に印加される所定の駆動閾値よりも高い電位差に応じて前記発光手段の発光を制御するドライバ手段と、

前記ドライバ手段の前記第1端子と前記第2端子との間ににおける前記駆動閾値に対応した閾値電圧を検出する閾値電圧検出手段と、

前記ドライバ手段に接続された容量可変手段と、

を備えたことを特徴とする画像表示装置。 10

**【請求項 2】**

前記容量可変手段の容量値は、前記ドライバ手段の端子間に存在する寄生容量、前記閾値電圧検出手段が有する端子間に存在する寄生容量の大きさに応じて、その値が決定されることを特徴とする請求項1に記載の画像表示装置。

**【請求項 3】**

前記閾値電圧検出手段に接続される選択信号線と該選択信号線に接続される制御信号線とが少なくとも一部共用されていることを特徴とする請求項1に記載の画像表示装置。

**【請求項 4】**

前記容量可変手段は、薄膜トランジスタと該薄膜トランジスタと接続された容量素子とを含んだ接続回路であり、該接続回路の一端が前記ドライバ手段に接続されることを特徴とする請求項1に記載の画像表示装置。 20

**【請求項 5】**

前記容量可変手段は、第1電極と、該第1電極よりも小面積である第2電極と、前記第1電極と前記第2電極との間に配置される絶縁層およびチャネル層と、を備えた可変容量素子であることを特徴とする請求項1に記載の画像表示装置。

**【請求項 6】**

前記チャネル層は、前記第2電極に接していることを特徴とする請求項5に記載の画像表示装置。

**【請求項 7】**

前記ドライバ手段および/または前記閾値電圧検出手段は薄膜トランジスタを含んで構成され、前記薄膜トランジスタのチャネル層と、前記可変容量素子のチャネル層とが同じ材料により略等しい厚みで形成されていることを特徴とする請求項5に記載の画像表示装置。 30

**【請求項 8】**

前記薄膜トランジスタのチャネル層および/または絶縁層と、前記可変容量素子のチャネル層および/または絶縁層とは同一工程で形成されることを特徴とする請求項7に記載の画像表示装置。

**【請求項 9】**

前記ドライバ手段および/または前記閾値電圧検出手段は薄膜トランジスタを含んで構成され、前記薄膜トランジスタの絶縁層と、前記可変容量素子の絶縁層とが同じ材料により略等しい厚みで形成されていることを特徴とする請求項5に記載の画像表示装置。 40

**【請求項 10】**

前記薄膜トランジスタの絶縁層と、前記可変容量素子の絶縁層とは同一工程で形成されることを特徴とする請求項9に記載の画像表示装置。

**【請求項 11】**

第1電極と、該第1電極上に配置される絶縁層と、該絶縁層上に配置されるチャネル層と、該チャネル層上に配置され、前記第1電極よりも小面積である第2電極と、を備えた可変容量素子を用いた画像表示装置。

**【請求項 12】**

前記チャネル層は、前記第1電極と前記第2電極との間の電位差に応じて導電性が変化 50

することを特徴とする請求項 1 1 に記載の画像表示装置。

【請求項 1 3】

通電により発光する発光素子と、

ゲート電極、ソース電極、ドレイン電極を有し、前記ソース電極および前記ドレイン電極のいずれか一方の電極が前記発光素子に電気的に接続される駆動トランジスタと、

走査信号に応じて前記駆動トランジスタの前記ゲート電極と前記駆動トランジスタの前記一方の電極とを短絡するスイッチングトランジスタと、

前記駆動トランジスタのゲート電極に接続される容量可変手段と、を備えた画像表示装置の駆動方法において、

前記駆動トランジスタ及び前記スイッチングトランジスタをオンに設定することにより、前記スイッチングトランジスタを介して前記駆動トランジスタのゲート電極と前記駆動トランジスタの前記ソース電極及び前記ドレイン電極のうちの他方の電極とを電気接続し、前記駆動トランジスタの前記他方の電極に対する前記ゲート電極の電位を駆動閾値とする第 1 の工程と、

前記駆動トランジスタをオフに設定するとともに前記スイッチングトランジスタをオンに設定することにより、前記発光素子の輝度電位を前記駆動トランジスタのゲート電極に供給する第 2 の工程と、

前記駆動トランジスタをオンに設定するとともに、前記スイッチングトランジスタをオフに設定することにより、前記発光素子に通電を行い、前記駆動トランジスタのゲート電極に供給された前記輝度電位に基づいて前記発光素子を発光させる第 3 の工程と、を含み

、前記駆動トランジスタの前記他方の電極に対する前記ゲート電極の電位を駆動閾値とする第 1 の工程における前記容量可変手段の容量値と、前記発光素子を発光させる第 3 の工程における前記容量可変手段の容量値とを異ならせることにより、前記発光素子の発光輝度に対する前記駆動トランジスタ及び前記スイッチングトランジスタの寄生容量の影響を抑制したことを特徴とする画像表示装置の駆動方法。

【請求項 1 4】

前記容量可変手段の容量値が、前記発光素子を発光させる第 3 の工程よりも前記駆動トランジスタの前記他方の電極に対する前記ゲート電極の電位を駆動閾値とする第 1 の工程の方が大きいことを特徴とする請求項 1 3 に記載の画像表示装置の駆動方法。

【請求項 1 5】

前記容量可変手段の容量値が、前記駆動トランジスタの前記他方の電極に対する前記ゲート電極の電位を駆動閾値とする第 1 の工程において、略一定であることを特徴とする請求項 1 3 に記載の画像表示装置の駆動方法。

【請求項 1 6】

前記容量可変手段の容量値が、前記発光素子を発光させる第 3 の工程において、略一定であることを特徴とする請求項 1 3 に記載の画像表示装置の駆動方法。

【請求項 1 7】

前記容量可変手段の容量値が、前記発光素子の輝度電位を前記駆動トランジスタのゲート電極に供給する第 2 の工程と、前記発光素子を発光させる第 3 の工程との間で変化することを特徴とする請求項 1 3 に記載の画像表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、画像表示装置およびその駆動方法に関するものであり、特に、寄生容量による輝度のバラツキを低減することができる画像表示装置およびその駆動方法に関するものである。

【背景技術】

【0 0 0 2】

従来から、発光層に注入された正孔と電子とが発光再結合することによって光を生じる

機能を有する電流制御型の有機 E L ( E l e c t r o n i c L u m i n e s c e n t ) 素子を用いた画像表示装置が提案されている。

【 0 0 0 3 】

この種の画像表示装置では、アモルファスシリコンや多結晶シリコン等で形成された T F T ( 薄膜トランジスタ ) や上述した有機 E L 素子等が各画素を構成しており、各画素に適切な電流値が設定されることにより、輝度が制御される。

【 0 0 0 4 】

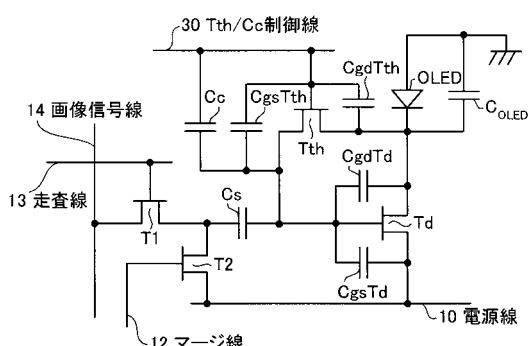

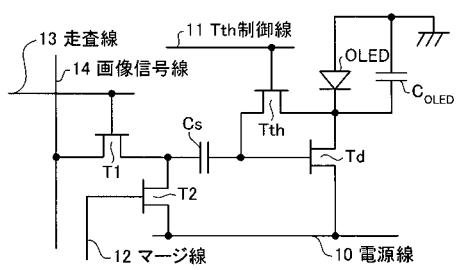

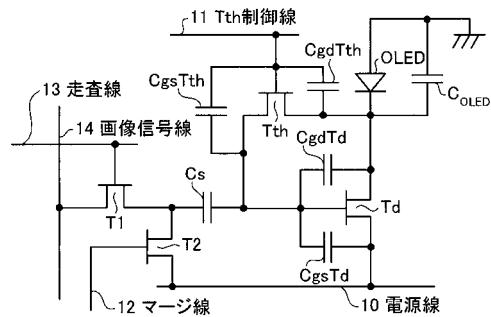

図 17 は、従来の画像表示装置における 1 画素に対応する画素回路の構成を示す図である。同図において、画素回路は、有機 E L 素子 O L E D 、有機 E L 素子容量 C <sub>OLED</sub> 、駆動トランジスタ T d 、閾値電圧検出用トランジスタ T t h 、補助容量 C s 、スイッチングトランジスタ T 1 およびスイッチングトランジスタ T 2 から構成されている。

【 0 0 0 5 】

駆動トランジスタ T d は、ゲート電極・ソース電極間に与えられる電位差に応じて有機 E L 素子 O L E D に流れる電流量を制御するためのものである。また閾値電圧検出用トランジスタ T t h は、オン状態となった時に、駆動トランジスタ T d のゲート電極とドレイン電極とを電気的に接続し、駆動トランジスタ T d のゲート電極・ソース電極間の電位差が駆動トランジスタ T d の閾値電圧 V <sub>t h</sub> となるまで駆動トランジスタ T d のゲート電極からドレイン電極に向かって電流を流すことにより、駆動トランジスタ T d の閾値電圧 V <sub>t h</sub> を検出する機能を有している。

【 0 0 0 6 】

有機 E L 素子 O L E D は、閾値電圧以上の電位差 ( アノード - カソード間電位差 ) が生じることにより、電流が流れ、発光する特性を有する素子である。具体的には、有機 E L 素子 O L E D は、A l 、C u 、I T O ( I n d i u m T i n O x i d e ) 等によって形成されたアノード層およびカソード層と、アノード層とカソード層との間にフタルシアニン、トリスアルミニウム錯体、ベンゾキノリノラト、ベリリウム錯体等の有機系の材料によって形成された発光層とを少なくとも備えた構造を有し、発光層に注入された正孔と電子とが発光再結合することによって光を生じる機能を有する。有機 E L 素子容量 C <sub>OLED</sub> は、有機 E L 素子 O L E D の容量を等価的に表したものである。

【 0 0 0 7 】

駆動トランジスタ T d 、閾値電圧検出用トランジスタ T t h 、スイッチングトランジスタ T 1 およびスイッチングトランジスタ T 2 は、例えば、薄膜トランジスタである。なお、以下で参照される各図面においては、各薄膜トランジスタについてチャネル ( n 型または p 型 ) を明示していないが、 n 型または p 型のいずれかであり、本明細書中の記載に従うものとする。

【 0 0 0 8 】

電源線 1 0 は、駆動トランジスタ T d およびスイッチングトランジスタ T 2 に電源を供給する。T t h 制御線 1 1 は、閾値電圧検出用トランジスタ T t h を制御するための信号を供給する。マージ線 1 2 は、スイッチングトランジスタ T 2 を制御するための信号を供給する。走査線 1 3 は、スイッチングトランジスタ T 1 を制御するための信号を供給する。画像信号線 1 4 は、画像信号を供給する。

【 0 0 0 9 】

上記構成において、画素回路は、準備期間、閾値電圧検出期間、書き込み期間および発光期間という 4 つの期間を経て動作する。すなわち、準備期間では、電源線 1 0 には所定の正電位 ( V <sub>p</sub> , V <sub>p</sub> > 0 ) が引加され、閾値電圧検出用トランジスタ T t h がオフ、スイッチングトランジスタ T 1 がオフ、駆動トランジスタ T d がオン、スイッチングトランジスタ T 2 がオンとなるように制御される。その結果、電源線 1 0 駆動トランジスタ T d 有機 E L 素子容量 C <sub>OLED</sub> という経路で電流が流れ、有機 E L 素子容量 C <sub>OLED</sub> に電荷が蓄積される。

【 0 0 1 0 】

つぎの閾値電圧検出期間では、電源線 1 0 にはゼロ電位が印加され、閾値電圧検出用ト

10

20

30

40

50

ランジスタ T<sub>t</sub>h がオンとなるように制御され、駆動トランジスタ T<sub>d</sub> のゲートとドレインとが接続される。これにより、補助容量 C<sub>s</sub> および有機 EL 素子容量 C<sub>OLED</sub> に蓄積された電荷が放電され、駆動トランジスタ T<sub>d</sub> 電源線 10 という経路で電流が流れる。そして、駆動トランジスタ T<sub>d</sub> のゲート - ドレイン間の電位差が、駆動トランジスタ T<sub>d</sub> の駆動閾値に対応する閾値電圧 V<sub>t</sub>h に達すると、駆動トランジスタ T<sub>d</sub> がオフとされる。

【0011】

つぎの書き込み期間では、電源線 10 の電位はゼロ電位を維持し、スイッチングトランジスタ T<sub>1</sub> がオン、スイッチングトランジスタ T<sub>2</sub> がオフとなり、有機 EL 素子容量 C<sub>OLED</sub> に蓄積された電荷が放電される。その結果、有機 EL 素子容量 C<sub>OLED</sub> 閾値電圧検出用トランジスタ T<sub>t</sub>h 補助容量 C<sub>s</sub> という経路で電流が流れ、補助容量 C<sub>s</sub> に電荷が蓄積される。すなわち、有機 EL 素子容量 C<sub>OLED</sub> に蓄積された電荷は、補助容量 C<sub>s</sub> に移動する。

10

【0012】

つぎの発光期間では、電源線 10 には所定の負電位 ( -V<sub>DD</sub> , V<sub>DD</sub> > 0 ) が印加され、駆動トランジスタ T<sub>d</sub> がオン、閾値電圧検出用トランジスタ T<sub>t</sub>h がオフ、スイッチングトランジスタ T<sub>1</sub> がオフとなるように制御される。その結果、有機 EL 素子 O<sub>LED</sub> 駆動トランジスタ T<sub>d</sub> 電源線 10 という経路で電流が流れ、有機 EL 素子 O<sub>LED</sub> が発光する。

【0013】

【非特許文献 1】 S. Ono et al. , Proceedings of IDW '03 , 255 (2003)

20

【発明の開示】

【発明が解決しようとする課題】

【0014】

ところで、従来の画像表示装置においては、図 18 に示したように、駆動トランジスタ T<sub>d</sub> のゲート付近に寄生容量 C<sub>g d T d</sub> および寄生容量 C<sub>g s T d</sub> が、さらに、閾値電圧検出用トランジスタ T<sub>t</sub>h のゲート付近にも寄生容量 C<sub>g d T t h</sub> および寄生容量 C<sub>g s T t h</sub> が存在している。

30

【0015】

これらの寄生容量は、有機 EL 素子 O<sub>LED</sub> の輝度のバラツキの要因となることが知られている。したがって、従来から、寄生容量による悪影響を効果的に小さくできる手法が切望されていた。

30

【0016】

本発明は、上記に鑑みてなされたものであって、寄生容量による輝度のバラツキを低減することができる画像表示装置およびその駆動方法を提供することを目的とする。

30

【課題を解決するための手段】

【0017】

上述した課題を解決し、目的を達成するために、本発明にかかる画像表示装置は、通電により発光する発光手段と、少なくとも第 1 端子、第 2 端子を備え、前記第 1 端子と前記第 2 端子との間に印加される所定の駆動閾値よりも高い電位差に応じて前記発光手段の発光を制御するドライバ手段と、前記ドライバ手段の前記第 1 端子と前記第 2 端子との間ににおける前記駆動閾値に対応した閾値電圧を検出する閾値電圧検出手段と、前記ドライバ手段に接続された容量可変手段と、備えたことを特徴とする。

40

【0018】

また、本発明にかかる画像表示装置は、第 1 電極と、該第 1 電極上に配置される絶縁層と、該絶縁層上に配置されるチャネル層と、該チャネル層上に配置され、前記第 1 電極よりも小面積である第 2 電極と、を備えた可変容量を用いたことを特徴とする。

【0019】

また、本発明にかかる画像表示装置の駆動方法は、通電により発光する発光素子と、ゲート電極、ソース電極、ドレイン電極を有し、前記ソース電極および前記ドレイン電極の

50

いずれか一方の電極が前記発光素子に電気的に接続される駆動トランジスタと、走査信号に応じて前記駆動トランジスタの前記ゲート電極と前記駆動トランジスタの前記一方の電極とを短絡するスイッチングトランジスタと、前記駆動トランジスタのゲート電極に接続される容量可変手段と、を備えた画像表示装置の駆動方法において、前記駆動トランジスタ及び前記スイッチングトランジスタをオンに設定することにより、前記スイッチングトランジスタを介して前記駆動トランジスタのゲート電極と前記駆動トランジスタの前記ソース電極及び前記ドレイン電極のうちの他方の電極とを電気接続し、前記駆動トランジスタの前記他方の電極に対する前記ゲート電極の電位を駆動閾値とする第1の工程と、前記駆動トランジスタをオフに設定するとともに前記スイッチングトランジスタをオンに設定することにより、前記発光素子の輝度電位を前記駆動トランジスタのゲート電極に供給する第2の工程と、前記駆動トランジスタをオンに設定するとともに、前記スイッチングトランジスタをオフに設定することにより、前記発光素子に通電を行い、前記駆動トランジスタのゲート電極に供給された前記輝度電位に基づいて前記発光素子を発光させる第3の工程と、を含み、前記駆動トランジスタの前記他方の電極に対する前記ゲート電極の電位を駆動閾値とする第1の工程における前記容量可変手段の容量値と、前記発光素子を発光させる第3の工程における前記容量可変手段の容量値とを異ならせることにより、前記発光素子の発光輝度に対する前記駆動トランジスタ及び前記スイッチングトランジスタの寄生容量の影響を抑制したことを特徴とする。

10

【発明の効果】

【0020】

本発明によれば、発光手段を駆動するドライバ手段に容量可変手段を接続した構成としたことから、容量可変手段の容量値を変化させることでドライバ手段や閾値検出手段等に存在する寄生容量の影響を小さくし、寄生容量による輝度のバラツキを低減することができる、画像表示装置の寿命を向上することができるという効果を奏する。また、製造工程や層構造の変更の手間を抑制できるので、本発明の適用が極めて容易であるという効果を奏する。

【発明を実施するための最良の形態】

【0021】

以下に、本発明にかかる画像表示装置の実施の形態を図面に基づいて詳細に説明する。なお、この実施の形態によりこの発明が限定されるものではない。

【0022】

(実施の形態1)

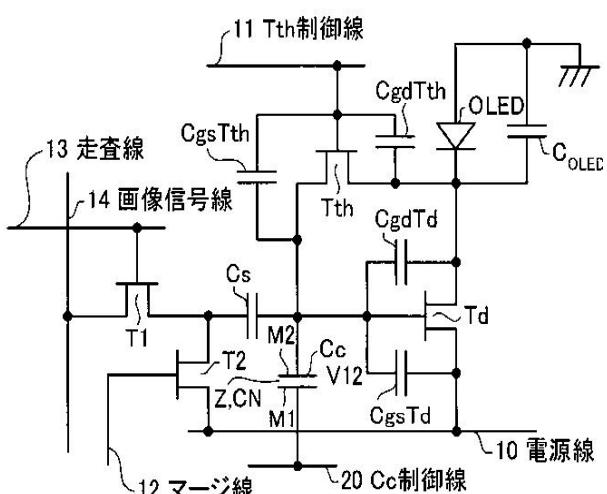

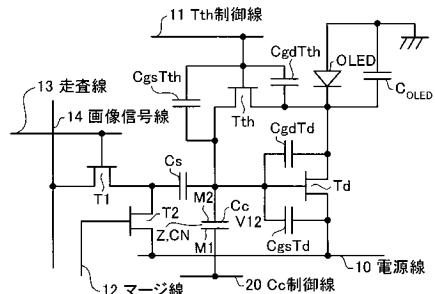

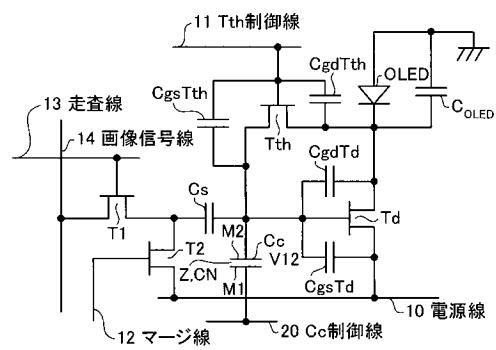

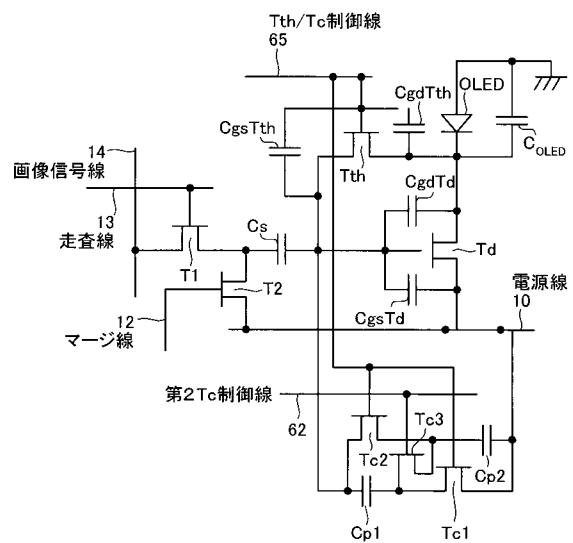

図1は、本発明の実施の形態1にかかる画像表示装置の1画素に対応する画素回路の構成を示す図である。同図においては、図18の各部に対応する部分には同一の符号を付ける。図1に示した画素回路においては、容量可変手段としての可変容量Ccと、この可変容量Ccを制御するためのCc制御線20と、が新たに設けられている。

【0023】

可変容量Ccは、前述した寄生容量による影響を小さくするための容量であり、第1電極M1と第2電極M2との間に挟まれた絶縁層Zおよびチャネル層CNを備えた構成とされており、薄膜トランジスタの層構成とほぼ同様である。第1電極M1は、Cc制御線20に接続されている。一方、第2電極M2は、駆動トランジスタTdのゲートに接続されている。

【0024】

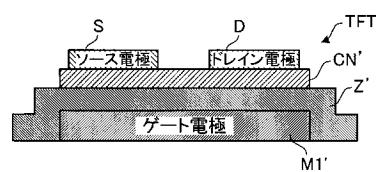

図2は、図1に示した薄膜トランジスタTFTの構成を示す断面図である。同図における薄膜トランジスタは、基板に近い層からゲート電極M1'、絶縁層Z'、チャネル層CN'、ソース電極S及びドレイン電極Dを積層した構造を有している。ゲート電極M1'、ソース電極S、ドレイン電極Dは、例えば、AlやAlNd、MoW等の金属材料により構成されている。絶縁層Z'は、例えばSiN系やSiO系の絶縁材料により形成されている。チャネル層CN'は、例えばアモルファスシリコンやポリシリコン等の半導体材料により形成されている。

20

30

40

50

## 【0025】

このような薄膜トランジスタにおいては、ゲート電極M1'・ソース電極S間の電圧によって形成される電界によって、チャネル層CN'の導電率が変化し、ドレイン電極D・ソース電極S間の抵抗値が変化するため、ドレイン電極Dとソース電極S間に流れる電流量を制御することができる。例えば、同図の薄膜トランジスタを駆動トランジスタTdとして使用した場合、ゲート電極・ソース電極間に与えられる電位差に応じて、有機EL素子OLEDに流れる電流量を制御することができる。

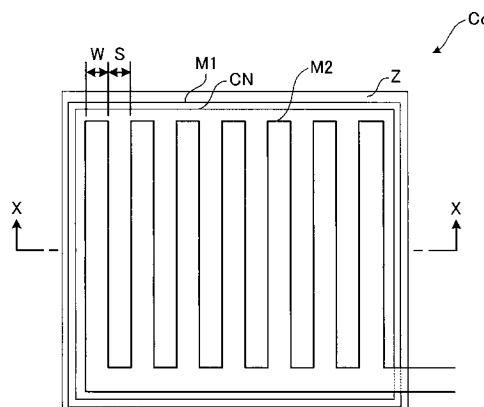

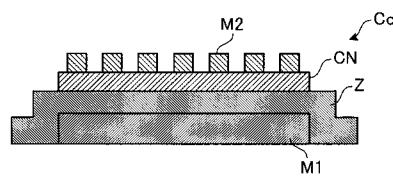

## 【0026】

また、図3-1は、図1に示した可変容量Ccの構成を示す概略平面図であり、図3-2は、同じく図1に示した可変容量Ccの構成を示すX-X線視断面図である。同図における可変容量Ccは、第1電極M1、絶縁層Z、チャネル層CNおよび第2電極M2の順番で積層されている。第1電極M1は、A1やA1NdやM0W等の金属材料により形成されており、例えば平面視形状が四角形状を有している。絶縁層Zは、第1電極M1上に配置されており、SiN系やSiO系等の絶縁材料により形成されている。チャネル層CNは、絶縁層Zと第2電極M2との間で、且つ第2電極M2に接するように配置されており、ポリシリコンやアモルファスシリコン等の半導体材料により形成されている。第2電極M2は、第1電極M1よりも小面積に形成されており、例えば、平面視形状が例えば複数の櫛歯状部を有する形状等、外周形状がクランク状となった形状となっている。

10

## 【0027】

ここで、チャネル層CNは、第1電極M1と第2電極M2との電位差V12(電位差V12とは、第1電極M1の電位をV1、第2電極M2の電位をV2とした場合、V1-V2をいう。以下同じ)が小さい場合に、絶縁体となるという特性を備えている。したがって、この場合、絶縁層Zおよびチャネル層CNが誘電体として作用し、可変容量Ccは、第1電極M1と第2電極M2との重なり面積に比例した容量となる。

20

## 【0028】

一方、第1電極M1と第2電極M2との電位差V12が大きい場合、チャネル層CNは、第2電極M2の直下および近傍の部分が導体となるという特性を備えている。したがって、この場合、第2電極M2の櫛部分の隙間が十分に小さいため、第2電極M2の表面全体が導体となり、絶縁層Zのみが誘電体として作用し、可変容量Ccは、第1電極M1とチャネル層CNとの重なり面積に比例した容量となる。

30

## 【0029】

また、可変容量Ccは、図2に示したゲート電極M1'、絶縁層Z'、チャネル層CN'、ソース電極Sおよびドレイン電極Dが積層された薄膜トランジスタTFTの構造と似ており、薄膜トランジスタTFTと同様の製造プロセスで作成が可能である。なお、図1に示した駆動トランジスタTd、閾値電圧検出用トランジスタTth、スイッチングトランジスタT1およびスイッチングトランジスタT2は、図2に示した薄膜トランジスタTFTと同様の構造とされている。

## 【0030】

なお、上述した薄膜トランジスタTFTと可変容量Ccは従来周知の薄膜形成技術を採用することにより形成される。具体的には、薄膜トランジスタTFTの場合、まず、ゲート電極に相当する金属材料をスパッタリング法等により所定厚み(例えば200~400nmの厚み)で成膜するとともに、これを従来周知のフォトリソグラフィーを行い、ドライエッティング等でパターニングしてゲート電極M1'を形成する。

40

## 【0031】

つぎに、絶縁層Z'に相当する絶縁材料とチャネル層CN'に相当する半導体材料をCVD法等で所定厚み(例えば、絶縁材料を300~400nmの厚みに、半導体材料を100~300nmの厚み)に積層し、該積層体に対してフォトリソグラフィーを行い、ドライエッティング等でパターニングして絶縁層Z'とチャネル層CN'をそれぞれ形成する。最後に、ソース電極Sおよびドレイン電極Dに相当する金属材料をスパッタリング法等で所定厚み(例えば200~400nmの厚み)に成膜し、これに対してフォトリソグラフィ

50

ーを行い、ドライエッティング等でパターニングしてソース電極Sおよびドレイン電極Dを形成する。

【0032】

また、可変容量Ccの場合、まず第1電極M1に相当する金属材料をスパッタリング法等で所定厚み(200~400nmの厚み)に成膜し、これに対してフォトリソグラフィーを行い、ドライエッティング等でパターニングして第1電極M1を形成する。つぎに、絶縁層Zに相当する絶縁材料とチャネル層CNに相当する半導体材料とをCVD法等で所定厚み(例えば、絶縁材料を300~400nmの厚みに、半導体材料を100~300nmの厚みに)積層し、該積層体に対してフォトリソグラフィーを行い、ドライエッティング等でパターニングして絶縁層Zとチャネル層CNの形成を行う。

10

【0033】

最後に、第2電極M2に相当する金属材料をスパッタリング法等で所定厚み(例えば200~400nmの厚み)に成膜し、これに対してフォトリソグラフィーを行い、ドライエッティング等でパターニングして第2電極M2を形成する。

【0034】

ここで、図2および図3-1、図3-2の場合、薄膜トランジスタTFTのチャネル層CN'、可変容量Ccのチャネル層CNとは、同じ材料により略等しい厚み(好ましくは両者の厚みの差が±80nm以内、さらに好ましくは±40nm以内)で形成されている。加えて、薄膜トランジスタTFTの絶縁層Z'、可変容量Ccの絶縁層Zとは、同じ材料により略等しい厚み(好ましくは両者の厚みの差が±80nm以内、さらに好ましくは±40nm以内)で形成されている。

20

【0035】

さらに、薄膜トランジスタTFTのゲート電極M1'、可変容量Ccの第1電極M1、並びに薄膜トランジスタTFTのソース電極Sおよびドレイン電極Dと可変容量Ccの第2電極M2のそれぞれが同じ材料によって略等しい厚み(好ましくは両者の厚みの差が±60nm以内、さらに好ましくは±30nm以内)で形成されている。

【0036】

このように、可変容量Ccを駆動トランジスタTd、閾値電圧検出用トランジスタTth等に用いられる薄膜トランジスタTFTと同様の層構成としたことから、両者を同じ材料で形成することができ、更には電極やチャネル層、絶縁層を同一工程で一括的に形成することもできる。したがって、可変容量の設置による生産性の低下を良好に防止することができる。

30

【0037】

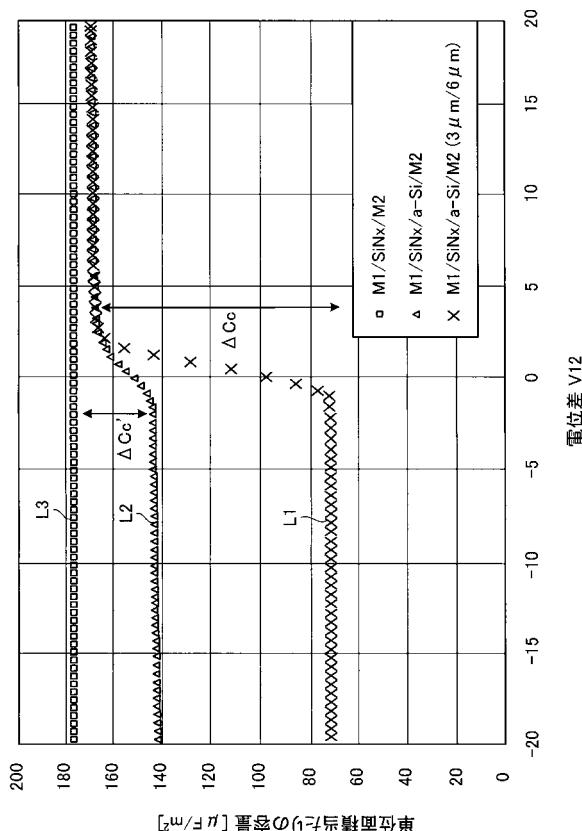

図4は、図1および図3-1および図3-2に示した可変容量Ccの単位面積当たりの容量の変化を示すグラフである。同図において、特性線L1~L3は、第1電極M1と第2電極M2(図1および図3参照)との電位差V12を-20Vから20Vに変化させた場合の、可変容量Ccの単位面積当たりの容量を表している。

【0038】

但し、特性線L1は、図3-1および図3-2に示した第2電極M2における柵部の幅Wを3μm、隙間Sを6μmとした場合を表す。この特性線L1からわかるように、電位差V12が第1閾値としての2.5V以上である場合、可変容量Ccの単位容量は、ほぼ一定の170μF/m<sup>2</sup>となる。一方、電位差V12が第2閾値としての-2.5V以下である場合、可変容量Ccの単位容量は、ほぼ一定の70μF/m<sup>2</sup>となる。ここで、可変容量Ccの単位容量の最大値と最小値との差分をCcとする。

40

【0039】

このように、特性線L1からわかるように、電位差V12を二値制御することにより、可変容量Ccの単位容量を最大値(同図では、170)または最小値(同図では、70)にすることができる。

【0040】

なお、特性線L2および特性線L3は、特性線L1との比較用にプロットされている。

50

特性線 L 2 は、第 2 電極 M 2 を櫛型形状に代えて、第 1 電極 M 1 と同形状同面積の略四角板形状とした場合を表す。ここで、特性線 L 1 と特性線 L 2 とを比較すると、特性線 L 1 に対応する差分  $C_{c'}$  は、可変容量  $C_c$  の単位容量の最大値と最小値との差分  $C_c'$  よりも大きくなることができる。

#### 【 0 0 4 1 】

これは、第 2 電極 M 2 の平面視形状を、複数の櫛歯状部を有する形状としたためであると推測される。第 2 電極 M 2 の平面視形状が複数の櫛歯状部を有すると  $C_{c'}$  を大きくすることができる理由は、第 2 電極 M 2 の外周形状がクランク状をなしているため、第 2 電極 M 2 に接するチャネル層 C N の面積が広くなり、第 1 電極 M 1 および第 2 電極 M 2 の電位差を大きくした場合に導体となるチャネル層 C N の面積を広く確保することができるからである。

#### 【 0 0 4 2 】

なお、複数の櫛歯状部を有する場合、隣接する櫛歯状部の間隔は  $4 \mu m \sim 8 \mu m$  に、櫛歯状部の線幅は  $1 \mu m \sim 5 \mu m$  にそれぞれ設定することが好ましい。また、特性線 L 3 は、可変容量  $C_c$  にチャネル層 C N を設けない場合を表し、可変容量  $C_c$  の単位容量は、電位差  $V_{12}$  に係わらず一定である。

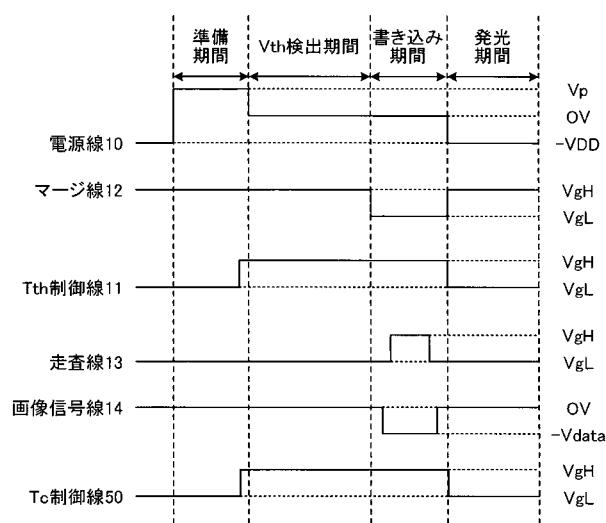

#### 【 0 0 4 3 】

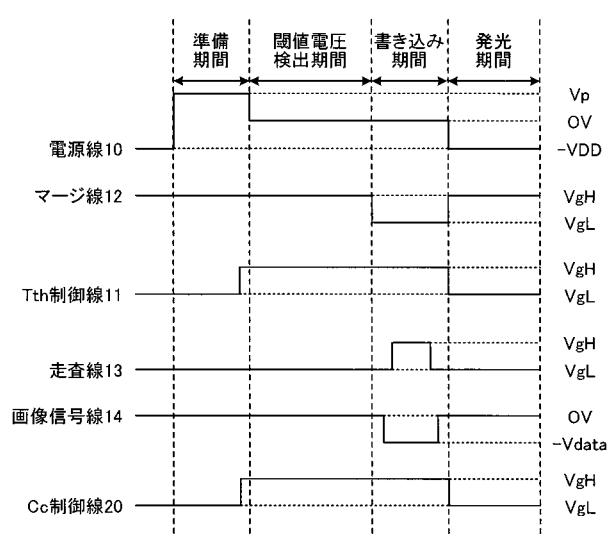

つぎに、実施の形態 1 の動作について、図 5 を参照しつつ説明する。以下では、準備期間、閾値電圧検出期間、書き込み期間および発光期間という都合 4 つの期間の動作について説明する。なお、以下に説明する動作は、制御部（図示略）の制御の下で行われる。

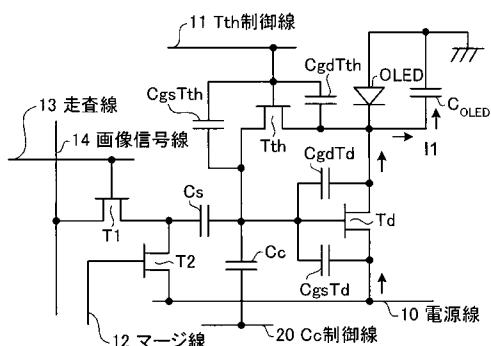

#### 【 0 0 4 4 】

##### （準備期間）

同図に示した準備期間では、電源線 1 0 が高電位（ $V_{pH}$ ）、マージ線 1 2 が高電位（ $V_{gH}$ ）、T t h 制御線 1 1 が低電位（ $V_{gL}$ ）、走査線 1 3 が低電位（ $V_{gL}$ ）、画像信号線 1 4 がゼロ電位、C c 制御線 2 0 が低電位（ $V_{gL}$ ）とされる。これにより、図 6 に示したように、閾値電圧検出用トランジスタ T t h がオフ、スイッチングトランジスタ T 1 がオフ、駆動トランジスタ T d がオン、スイッチングトランジスタ T 2 がオンとされ、電源線 1 0 駆動トランジスタ T d 有機 E L 素子容量  $C_{oLED}$  という経路で電流  $I_1$  が流れ、有機 E L 素子容量  $C_{oLED}$  に電荷が蓄積される。この準備期間で有機 E L 素子に電荷を蓄積する理由は、駆動閾値検出時に  $I_{ds} = 0$  となるまで電流を供給するためである。

#### 【 0 0 4 5 】

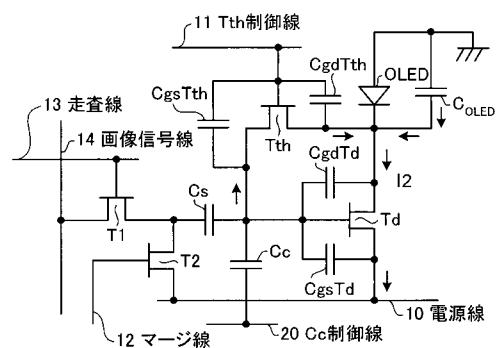

##### （閾値電圧検出期間）

つぎの閾値電圧検出期間では、電源線 1 0 がゼロ電位、マージ線 1 2 が高電位（ $V_{gH}$ ）、T t h 制御線 1 1 が高電位（ $V_{gH}$ ）、走査線 1 3 が低電位（ $V_{gL}$ ）、画像信号線 1 4 がゼロ電位、C c 制御線 2 0 が高電位（ $V_{gH}$ ）とされる。これにより、図 7 に示したように、閾値電圧検出用トランジスタ T t h がオンとなり、駆動トランジスタ T d のゲートとドレインとが接続される。

#### 【 0 0 4 6 】

また、補助容量  $C_s$  および有機 E L 素子容量  $C_{oLED}$  に蓄積された電荷が放電され、駆動トランジスタ T d 電源線 1 0 という経路で電流  $I_2$  が流れる。そして、駆動トランジスタ T d のゲート - ドレイン間の電位差が閾値電圧  $V_{th}$  に達すると、駆動トランジスタ T d がオフとされ、駆動トランジスタ T d の閾値電圧  $V_{th}$  が検出される。

#### 【 0 0 4 7 】

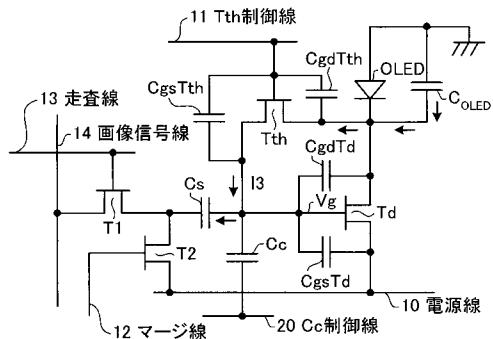

##### （書き込み期間）

つぎの書き込み期間では、データ電位（ $-V_{data}$ ）を  $C_s$  に供給することにより、駆動トランジスタ T d のゲート電位を所望する電位に可変させることが行われる。具体的には、電源線 1 0 がゼロ電位、マージ線 1 2 が低電位（ $V_{gL}$ ）、T t h 制御線 1 1 が高電位（ $V_{gH}$ ）、走査線 1 3 が高電位（ $V_{gH}$ ）、画像信号線 1 4 がデータ電位（ $-V_{data}$ ）、C c 制御線 2 0 が高電位（ $V_{gH}$ ）とされる。

#### 【 0 0 4 8 】

10

20

30

40

50

これにより、図8に示したように、スイッチングトランジスタT1がオン、スイッチングトランジスタT2がオフとなり、有機EL素子容量C<sub>OLED</sub>に蓄積された電荷が放電され、有機EL素子容量C<sub>OLED</sub> 閾値電圧検出用トランジスタTth 補助容量Csという経路で電流I3が流れ、補助容量Csに電荷が蓄積される。すなわち、有機EL素子容量C<sub>OLED</sub>に蓄積された電荷は、補助容量Csに移動する。

## 【0049】

ここで、可変容量CcおよびCc制御線20が存在しないと仮定した場合、駆動トランジスタTdのゲート電位Vgは、駆動トランジスタTdの閾値電圧をVthとすると、補助容量Csの容量値をCs、閾値電圧検出用トランジスタTthがオンの場合の全容量(駆動トランジスタTdのゲートに接続された静電容量および寄生容量)をCall1とすると、つぎの(1)式で表される(上記仮定は、(2)式~(11)式についても及ぶものとする)。

## 【0050】

$$Vg = Vth - (Cs/Call) \cdot Vdata \dots (1)$$

## 【0051】

また、補助容量Csの電位差VCsは、つぎの(2)式で表される。

## 【0052】

$$VCs = Vg - (-Vdata) = Vth + [(Call - Cs)/Call] \cdot Vdata \dots (2)$$

## 【0053】

なお、全容量Call1は、つぎの(3)式で表される。

## 【0054】

$$Call = C_{OLED} + Cs + CgsTth + CgdTth + CgsTd \dots (3)$$

## 【0055】

なお、駆動トランジスタTdのゲートとドレインとが接続されている場合、CgdTdは影響しない。その理由は、CgdTdの両端が略同電位となっているからである。また、補助容量Csと有機EL素子容量C<sub>OLED</sub>の関係は、Cs < C<sub>OLED</sub>とされている。

## 【0056】

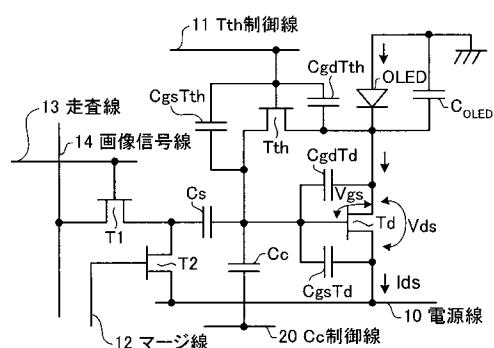

## (発光期間)

つぎの発光期間では、電源線10がマイナス電位(-VDD)、マージ線12が高電位(VgH)、Tth制御線11が低電位(VgL)、走査線13が低電位(VgL)、画像信号線14がゼロ電位、Cc制御線20が低電位(VgL)とされる。

## 【0057】

これにより、図9に示したように、駆動トランジスタTdがオン、閾値電圧検出用トランジスタTthがオフ、スイッチングトランジスタT1がオフとなり、有機EL素子OLED 駆動トランジスタTd 電源線10という経路で電流Idsが流れ、有機EL素子OLEDが発光する。

## 【0058】

駆動トランジスタTdのドレインからソースに流れる電流Idsは、駆動トランジスタTdの構造および材質から決定される定数を、駆動トランジスタTdのソースに対するゲートの電位をVgs、駆動トランジスタTdの閾値電圧をVthとすると、つぎの(4)式で表される。

## 【0059】

$$Ids = (-/2)(Vgs - Vth)^2 \dots (4)$$

## 【0060】

ここで、画素回路に寄生容量が存在しないと仮定した場合、駆動トランジスタのゲート・ソース間電位Vgsは、つぎの(5)式で表される。また、電流Idsは、つぎの(6)式で表される。

## 【0061】

$$Vgs = Vth + C_{OLED}/(Cs + C_{OLED}) \cdot Vdata \dots (5)$$

$$Ids = (-/2)(C_{OLED}/(Cs + C_{OLED}) \cdot Vdata)^2$$

10

20

40

50

$$= a \cdot V_{data}^2 \dots (6)$$

## 【0062】

(6)式からわかるように、寄生容量  $C_{gdTd}$ 、寄生容量  $C_{gsTd}$  が存在しないと仮定した場合には、閾値電圧  $V_{th}$  に依存しない電流  $I_{ds}$  を得ることができる。したがって、有機EL素子OLEDの光度は電流  $I_{ds}$  に比例するため、閾値電圧  $V_{th}$  に依存しない光度が得られる。

## 【0063】

しかしながら、実際には画素回路に寄生容量が存在しているため、閾値電圧  $V_{th}$  の影響を完全に消すことはできない。すなわち、寄生容量を考慮した場合、駆動トランジスタ  $Td$  のソースに対するドレインの電位を  $V_{ds}$  とすると、書き込み期間（図5参照）における電位  $V_{ds}$  は、つぎの(7)式で表される。

## 【0064】

$$V_{ds} = V_{gs} = V_{th} - (Cs/Call) \cdot V_{data} \dots (7)$$

## 【0065】

また、発光期間（図9参照）における電位  $V_{ds}$  は、有機EL素子OLEDの電圧降下を  $V_{tholed}$  とすると、つぎの(8)式で表される。

## 【0066】

$$V_{ds} = V_{DD} - V_{tholed} \dots (8)$$

## 【0067】

また、電位  $V_{ds}$  の変化量  $V_{ds}$  は、つぎの(9)式で表される。

## 【0068】

$$V_{ds} = V_{DD} - V_{tholed} - V_{th} + (Cs/Call) \cdot V_{data} \dots (9)$$

## 【0069】

また、寄生容量  $C_{gdTd}$  が存在しているため、電位  $V_{gs}$  も変化する。この電位  $V_{gs}$  の変化量  $V_{gs}$  は、つぎの(10)式で表される。

## 【0070】

$$\begin{aligned} V_{gs} &= (C_{gdTd}/Call') \cdot V_{ds} \\ &= (C_{gdTd}/Call') (V_{DD} - V_{tholed} - V_{th} + (Cs/Call) \cdot V_{data}) \end{aligned} \dots (10)$$

## 【0071】

(10)式において、 $Call'$  は、閾値電圧検出用トランジスタ  $Tth$  がオフの場合における全容量（駆動トランジスタ  $Td$  のゲートに接続された静電容量および寄生容量）であり、つぎの(11)式で表される。

## 【0072】

$$Call' = Cs + CgsTd + CgsTth + CgdTd \dots (11)$$

## 【0073】

(10)式において、 $(C_{gdTd}/Call') (V_{DD} - V_{tholed} + (Cs/Call) \cdot V_{data})$  の値は、全画素でほぼ同じであるために問題が発生しない。これに対して、 $(C_{gdTd}/Call') V_{th}$  が各画素の閾値電圧  $V_{th}$  によって異なるため、画素の輝度にバラツキが生じる原因とされる。ここで、現状では、いずれの構成の画素回路でも、発光時に  $V_{ds}$  が変化するため、寄生容量  $C_{gdTd}$  を介して  $V_{gs}$  が変化するのを回避することができない。このため、完全に均一な表示にはならず、ムラ、焼き付き、画面の輝度が低下するという問題が生じる。

## 【0074】

そこで、実施の形態1では、可変容量  $Cc$  を設けることにより、かかる問題を解決している。すなわち、可変容量  $Cc$  は、前述したように、電位差  $V_{12}$  が高い場合に、大きくなる一方、電位差  $V_{12}$  が小さい場合に小さくなるという特性を有している。

## 【0075】

ここで、電位差  $V_{12}$  が前述した第1閾値以上である場合の可変容量  $Cc$  の値を  $Ccon$ 、電位差  $V_{12}$  が第2閾値以下である場合の  $Ccoff$  ( $< Ccon$ ) とする。ここで、差分  $Cc$  はつぎの(12)式で表される。また、全容量  $Call$  および全容量  $Cal$

10

20

30

40

50

1'は、つぎの(13)式および(14)式で表される。

【0076】

$$\begin{aligned} Cc &= Ccon - Ccoff \dots (12) \\ Call &= C_{LED} + Cs + CgsTth + CgdTth + CgsTd + Ccon \dots (13) \\ Call' &= Cs + CgsTth + CgsTd + CgdTd + Ccon \dots (14) \end{aligned}$$

【0077】

そして、図5に示した閾値電圧検出期間および書き込み期間で、Cc制御線20を高電位(VgH)にし、電位差V12を第1閾値以上にすることにより、可変容量Ccの値は、Cconとなる。つぎに、発光期間でCc制御線20を低電位(VgL)にし、電位差V12を第2閾値以下にすることにより、可変容量Ccの値は、Ccoffとなる。ここで、発光期間においては、Vgsは変化し、つぎの(15)式で表される。

【0078】

$$\begin{aligned} Vgs &= Vth + [(Call - Cs)/Call] \cdot Vdata + (CgdTd/Call') [VDD - Vtholed \\ &\quad - Vth + (Cs/Call)Vdata] \\ &= [(Call' - CgdTd)/Call'] Vth + a \cdot Vdata + d \dots (15) \end{aligned}$$

【0079】

(15)式において、aおよびdは、定数である。

【0080】

また、可変容量Ccの値がCcoffになると、つぎの(16)式で表される電荷保存則より、Vgsは、つぎの(17)式で表されるVgs'となる。

【0081】

$$Q = Call' \cdot Vgs = (Call' - Cc)Vgs' \dots (16)$$

【0082】

$$\begin{aligned} Vgs' &= [Call'/(Call' - Cc)]Vgs \\ &= [Call'/(Call' - Cc)][[(Call' - CgdTd)/Call']Vth \\ &\quad + a \cdot Vdata + d] \\ &= [(Call' - CgdTd)/(Call' - Cc)]Vth + a' \cdot Vdata + d' \dots (17) \end{aligned}$$

【0083】

(17)式において、a'およびd'は、定数である。

【0084】

したがって、つぎの(18)式で表される差分Ccが成立するような可変容量Ccを設定することにより、(17)式の右辺第1項である閾値電圧Vthの係数が1となり、閾値電圧Vthへの依存度が理論的には0となる。

【0085】

$$Cc = CgdTdon \dots (18)$$

【0086】

また、(18)式が成立する場合、(17)式のVgs'は、つぎの(19)式のように簡略化することができる。

$$Vgs' = a' \cdot Vdata + d' + Vth \dots (19)$$

【0087】

(19)式のVgs'をVgsとして(4)式に代入すると、最終的なIdsは、つぎの(20)式で表される。

$$Ids = (1/2)(a' \cdot Vdata + d')^2 \dots (20)$$

【0088】

Ccが理論値に設定されていれば、(20)式に示されるIdsにVthの項が存在しないので、駆動トランジスタTdのドレインからソースに流れる電流Idsの値は駆動トランジスタTdの閾値電圧Vthに理論的には依存しない。つまり、発光期間における有機EL素子への通電量が駆動閾値Vthに理論的には依存しなくなる。

【0089】

また、Ccが理論値から外れる場合、Idsは、つぎの(21)式、

10

20

30

40

50

$$I_{ds} = ( /2) [ [ ( Cc - CgdTd) / (C_{all} - Cc) ] V_{th} + a' \cdot V_{data} + d' ]^2 \quad \dots \dots \quad (21)$$

となり、駆動閾値  $V_{th}$  が残存することになる。

#### 【0090】

しかしながら、 $Cc$  が (18) 式を満たすような理論値でなくとも、この理論値に対して、例えば  $\pm 10\%$  の範囲内に  $Cc$  の値が設定されていれば、寄生容量による輝度のバラツキ防止の効果に供することができる。この場合、駆動閾値  $V_{th}$  への依存度を小さくすることができ、有機 EL 素子への通電量を小さくすることが可能となる。

#### 【0091】

なお、本実施の形態においては、可変容量  $Cc$  は、その値が発光期間よりも閾値電圧検出期間の方で大きく変化するように  $Cc$  制御線への電位が制御されている。また可変容量  $Cc$  の値は閾値電圧検出期間および発光期間のそれぞれにおいて略一定となるように制御線  $Cc$  への電位を制御することが好ましい。

#### 【0092】

また可変容量は、発光期間終了から駆動閾値の検出終了前まで（好ましくは駆動閾値の検出終了時より 2 ms 以上前まで）の期間に小さな値から大きな値に変化し、データの書き込み期間終了から発光開始までの期間もしくは有機 EL 素子 OLED の発光開始時に大きな値から小さな値に変化するように制御線  $Cc$  への電位を制御することがそれ好ましい。

#### 【0093】

以上、説明したように、この実施の形態の画像表示装置によれば、上述したような容量可変手段としての可変容量  $Cc$  を設けるようにしているので、駆動トランジスタ  $Td$ （ドライバ手段）や閾値電圧検出用トランジスタ  $T_{th}$ （閾値検出手段）等に存在する寄生容量の影響を小さくし、寄生容量による輝度のバラツキを低減することができる。なお、実施の形態 1においては、閾値電圧検出手段および駆動トランジスタの素子としてアモルファスシリコン TFT を用いる場合について説明したが、これに代えて、ポリシリコン TFT 等、他の TFT を用いても良い。この場合、かかる TFT のチャネル層を構成する材料に対応させて可変容量のチャネル層の材料を選択することが好ましい。

#### 【0094】

##### （実施の形態 2）

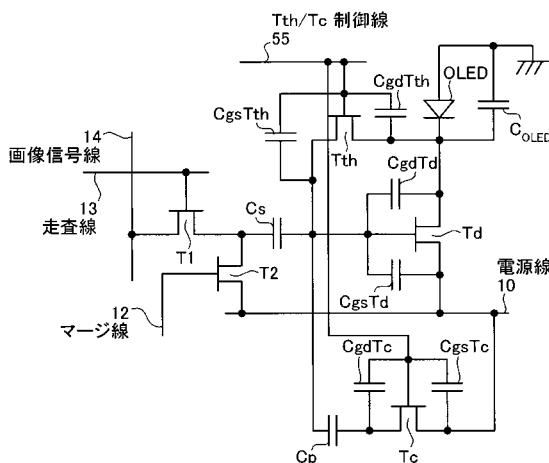

さて、前述した実施の形態 1においては、図 1 に示した  $T_{th}$  制御線 11 と  $Cc$  制御線 20 とをそれぞれ設けた構成例について説明したが、閾値電圧検出期間および書き込み期間に高電位、発光期間に低電位が可変容量  $Cc$  に供給されればよいため、実施の形態 2 として、図 10 に示したように、 $T_{th}$  制御線 11 と  $Cc$  制御線 20 と同じ  $T_{th} / Cc$  制御線 30 で共用する構成例としてもよい。この  $T_{th} / Cc$  制御線 30 の電位は、図 5 に示した  $T_{th}$  制御線 11（ $Cc$  制御線 20）の電位と同様に変化する。

#### 【0095】

##### （実施の形態 3）

また、前述した実施の形態 1においては、図 1 に示した構成の画素回路に可変容量  $Cc$  を適用した例について説明したが、駆動トランジスタと閾値電圧検出用トランジスタとを有する画素回路であれば、いかなる接続形態の画素回路にも適用可能である。要は、駆動トランジスタのゲートに実施の形態 1 で説明した要件を備える可変容量  $Cc$  を接続すればよい。

#### 【0096】

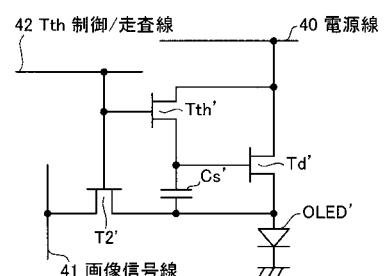

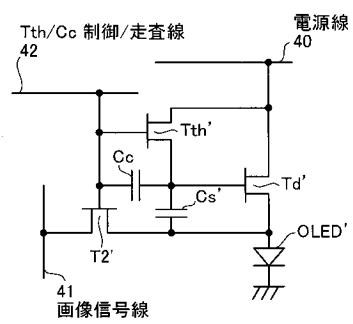

また、図 11 は、電流制御型の画像表示装置の 1 画素に対応する画素回路の構成を示す図である。同図に示した画素回路は、閾値電圧検出用トランジスタ  $T_{th}'$  と、有機 EL 素子 OLED' と、駆動トランジスタ  $Td'$  と、スイッチングトランジスタ  $T2'$  と、補助容量  $Cs'$  と、電源線 40 と、画像信号線 41 と、 $T_{th}$  制御 / 走査線 42 とを備えている。

#### 【0097】

10

20

30

40

50

このような図11に示した電流制御型の画素回路に可変容量C<sub>c</sub>を適用することもできる。この場合、駆動トランジスタT<sub>d'</sub>のゲートと閾値電圧検出用トランジスタT<sub>th'</sub>のゲートとの間に可変容量C<sub>c</sub>が接続される、図12に示すような画素回路を構成することができる。

【0098】

(実施の形態4)

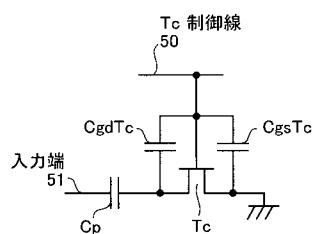

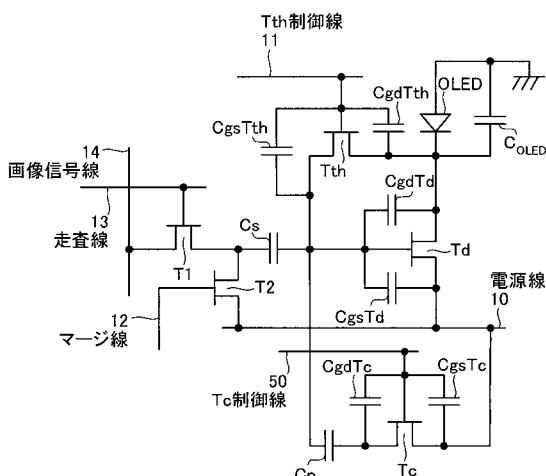

図13は、本発明の実施の形態4にかかる容量可変手段の構成を示す図である。同図に示す可変容量手段は、図3-1、図3-2に示した可変容量C<sub>c</sub>に代えて、容量素子とTFTとの直列接続回路を用いるものである。図13に示す回路では、固定容量C<sub>p</sub>に、例えば薄膜トランジスタであるスイッチングトランジスタT<sub>c</sub>が直列に接続されるとともに、このスイッチングトランジスタT<sub>c</sub>のゲート端にはT<sub>c</sub>制御線50が接続される。なお、スイッチングトランジスタT<sub>c</sub>のドレイン端-ゲート端およびソース端-ゲート端には、上述した他のスイッチングトランジスタと同様に寄生容量C<sub>gdTc</sub>および寄生容量C<sub>gstc</sub>がそれぞれ存在する。

【0099】

つぎに、この容量可変手段のスイッチングトランジスタT<sub>c</sub>の導通/非導通の前後における容量変化について説明する。図13において、スイッチングトランジスタT<sub>c</sub>が導通している場合、固定容量C<sub>p</sub>が直接ゼロ電位に接続されるため、入力端51に対する容量はC<sub>p</sub>となる。一方、スイッチングトランジスタT<sub>c</sub>が非導通の場合には、固定容量C<sub>p</sub>が寄生容量C<sub>gdTc</sub>および寄生容量C<sub>gstc</sub>を介してゼロ電位に接続されるため、入力端51に対する容量C<sub>p'</sub>は、次式で表される。

$$C_{p'} = 1/(1/C_p + 1/C_{gdTc}) \dots \dots \dots (22)$$

【0100】

したがって、スイッチングトランジスタT<sub>c</sub>の非導通、導通間での容量変化をC<sub>p</sub>とすると、このC<sub>p</sub>は次式で表される。

$$C_p = C_p - C_{p'} \dots \dots \dots (23)$$

【0101】

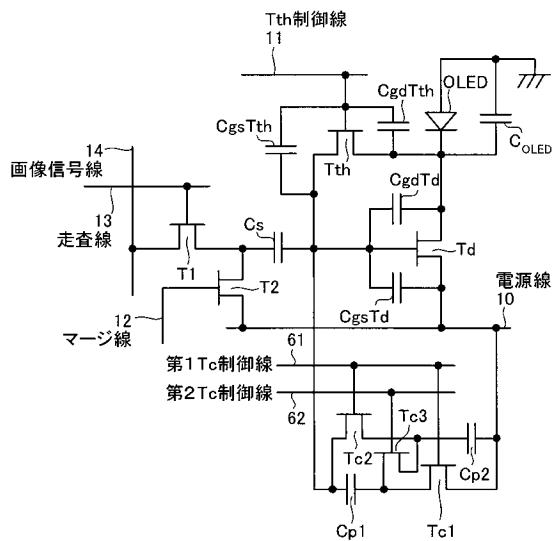

図14は、図13の容量可変手段を適用した実施の形態4にかかる画像表示装置の1画素に対応する画素回路の構成を示す図である。同図に示す画素回路では、図13の容量可変手段における入力端51が駆動トランジスタT<sub>d</sub>のゲート端に接続され、接地端が電源線に接続されるように構成される。なお、その他の構成は、図18に示す画素回路と同等である。

【0102】

つぎに、実施の形態4の画素回路の動作について説明する。図14において、まず、T<sub>c</sub>制御線50を高電位(V<sub>gH</sub>)にすることで追加容量をC<sub>p</sub>にし、V<sub>th</sub>検出および書き込みを行う。つぎに、T<sub>c</sub>制御線50を発光時の電位である低電位(V<sub>gL</sub>)にすると、実施の形態1の画素回路のようにV<sub>gs</sub>が変化する。このときのV<sub>gs</sub>の変化は、上述の(15)式で表すことができる。

$$\begin{aligned} V_{gs} &= V_{th} + [(C_{all} - C_s)/C_{all}] \cdot V_{data} + (C_{gdTd}/C_{all})[VDD - V_{tholed} \\ &\quad - V_{th} + (C_s/C_{all})V_{data}] \\ &= [(C_{all}' - C_{gdTd})/C_{all}']V_{th} + a \cdot V_{data} + d \dots \dots (15) \quad (\text{再掲}) \end{aligned}$$

【0103】

また、容量可変手段の容量値がC<sub>p</sub>からC<sub>p'</sub>に変化するとき、実施の形態1の場合と同様に、つぎの(24)式で表される電荷保存則が成立するので、上記(15)式で表されるV<sub>gs</sub>が、つぎの(25)式で表されるV<sub>gs'</sub>となる。

【0104】

$$Q = C_{all}' \cdot V_{gs} = (C_{all}' - C_p)V_{gs}' \dots \dots (24)$$

【0105】

$$\begin{aligned} V_{gs}' &= [C_{all}' / (C_{all}' - C_p)]V_{gs} \\ &= [C_{all}' / (C_{all}' - C_p)][[(C_{all}' - C_{gdTd})/C_{all}']V_{th} \end{aligned}$$

10

20

30

40

50

$$+ a \cdot V_{data} + d] \\ = [(Call' - CgdTd) / (Call' - Cp)] V_{th} + a' \cdot V_{data} + d' \dots \dots (25)$$

なお、これらの式に示される  $a$ 、 $a'$ 、 $d$ 、 $d'$  は、上記 (16)、(17) 式に示したものと同一である。

#### 【0106】

したがって、つぎの (26) 式で表される差分  $C_p$  が成立するような容量値  $C_p$  を設定することにより、(25) 式の右辺第 1 項である閾値電圧  $V_{th}$  の係数が 1 となり、閾値電圧  $V_{th}$  への依存度が理論的には 0 となる。

#### 【0107】

$$C_p = Cp - Cp' = Cp \cdot [1 - CgdTc / (Cp + CgdTc)] = CgdTd \dots \dots (26)$$

#### 【0108】

なお、(26) 式が成立する場合、(25) 式の  $V_{gs'}$  は、上述の (19) 式のように簡略化することができ、

$$V_{gs'} = a' \cdot V_{data} + d' + V_{th} \dots \dots (19) \text{ (再掲)}$$

また、最終的な  $I_{ds}$  は、上述の (20) 式のように表すことができる。

$$I_{ds} = (1/2)(a' \cdot V_{data} + d')^2 \dots \dots (20) \text{ (再掲)}$$

#### 【0109】

$C_c$  が理論値に設定されていれば、(20) 式に示される  $I_{ds}$  に  $V_{th}$  の項が存在しないので、駆動トランジスタ  $T_d$  のドレインからソースに流れる電流  $I_{ds}$  の値は駆動トランジスタ  $T_d$  の閾値電圧  $V_{th}$  には理論的には依存しない。つまり、発光期間における有機 EL 素子への通電量の駆動閾値  $V_{th}$  の影響を理論的には除去することができる。

#### 【0110】

また、 $C_p$  が理論値から外れる場合、 $I_{ds}$  はつぎの (27) 式、

$$I_{ds} = (1/2)[[(C_c - CgdTd) / (Call' - Cp)] V_{th} + a' \cdot V_{data} + d']^2 \dots \dots (27)$$

で表されるため、駆動閾値  $V_{th}$  が残存することになる。

#### 【0111】

しかしながら、 $C_c$  が (18) 式を満たすような理論値でなくとも、この理論値に対して、例えば  $\pm 10\%$  の範囲内に  $C_p$  の値が設定されていれば、寄生容量による輝度のバラツキ防止の効果に供することができる。また、この場合、駆動閾値  $V_{th}$  への依存度を小さくすることができるので、有機 EL 素子への通電量を小さくすることが可能となる。

#### 【0112】

また、図 15 は、 $T_c$  制御線の駆動波形を示すシーケンス図である。同図に示すように、 $T_c$  制御線は  $V_{th}$  検出時および書き込み時には高電位であり、逆に発光時には低電位であればよい。

#### 【0113】

また、図 15 から明らかなように、 $T_c$  制御線および  $T_{th}$  制御線は、高電位および低電位となるタイミングが一致している。したがって、 $T_c$  制御線と  $T_{th}$  制御線とを共用することができ、外部駆動装置を変更する必要がないという効果が得られる。なお、 $T_{th}$  制御線 11 と  $T_c$  制御線 50 とを共通の  $T_{th}$  /  $T_c$  制御線 55 で共用する画素回路の構成例を図 16 に示す。

#### 【0114】

以上、説明したように、この実施の形態の画像表示装置によれば、容量素子とスイッチングトランジスタとの直列接続回路による容量可変手段を設けるようにしているので、駆動トランジスタ  $T_d$  (ドライバ手段) や閾値電圧検出用トランジスタ  $T_{th}$  (閾値検出手段) 等に存在する寄生容量の影響を小さくし、寄生容量による輝度のバラツキを低減することができる。

#### 【0115】

なお、実施の形態 4 の画像表示装置においても、実施の形態 1 と同様に、閾値電圧検出

10

20

30

40

50

手段および駆動トランジスタの素子としてアモルファスシリコン TFT を用いる他、これに代えて、ポリシリコン TFT 等、他の TFT を用いてもよい。

【 0 1 1 6 】

また、図 14 に示した画素回路は、電圧制御型の画素回路に容量可変手段の構成を適用する例について示したが、電流制御型の画素回路に同様な容量可変手段の構成を適用することもできる。この場合、図 12 に示す実施の形態 3 の構成例のように、駆動トランジスタ Td' のゲートと閾値電圧検出用トランジスタ Tth' のゲートとの間に容量可変手段が接続されるように構成すればよい。

【 0 1 1 7 】

( 実施の形態 5 )

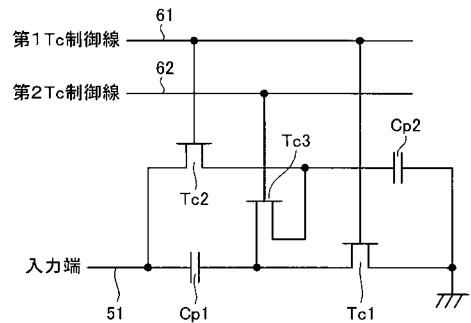

図 19 は、本発明の実施の形態 5 にかかる容量可変手段の構成を示す図である。同図に示す容量可変手段は、実施の形態 4 と同様に、容量素子と TFT とを組み合わせて直列接続回路を構成したものである。図 19 に示す回路では、固定容量 Cp1 に、例えば薄膜トランジスタであるスイッチングトランジスタ Tc1 が直列に接続され、固定容量 Cp2 に、例えば薄膜トランジスタであるスイッチングトランジスタ Tc2 が直列に接続される。これらのスイッチングトランジスタ Tc1 および Tc2 の各ゲート端には第 1 Tc 制御線 61 が接続される。さらに、図 19 に示す回路では、例えば薄膜トランジスタであるスイッチングトランジスタ Tc3 が設けられている。具体的には、スイッチングトランジスタ Tc3 のソースは固定容量 Cp1 とスイッチングトランジスタ Tc1 との間に接続され、そのドレインを固定容量 Cp2 とスイッチングトランジスタ Tc2 との間に接続される。また、スイッチングトランジスタ Tc3 のゲート端には第 2 Tc 制御線 62 が接続される。

【 0 1 1 8 】

つぎに、この容量可変手段のスイッチングトランジスタ Tc1 、 Tc2 、 Tc3 の導通 / 非導通の前後における容量変化について説明する。図 19 において、スイッチングトランジスタ Tc1 および Tc2 が導通し、且つスイッチングトランジスタ Tc3 が非導通の場合、入力端 51 に対する容量は  $Cp1 + Cp2$  となる。一方、スイッチングトランジスタ Tc1 および Tc2 が非導通であり、且つスイッチングトランジスタ Tc3 が導通している場合には、入力端 51 に対する容量は  $1 / (1/Cp1 + 1/Cp2)$  となる。

【 0 1 1 9 】

図 20 は、図 19 の容量可変手段を適用した実施の形態 5 にかかる画像表示装置の 1 画素に対応する画素回路の構成を示す図である。同図に示す画素回路では、図 19 の容量可変手段における入力端 51 が駆動トランジスタ Td のゲート端に接続され、接地端が電源線に接続されるように構成される。なお、その他の構成は、図 18 に示す画素回路と同等である。

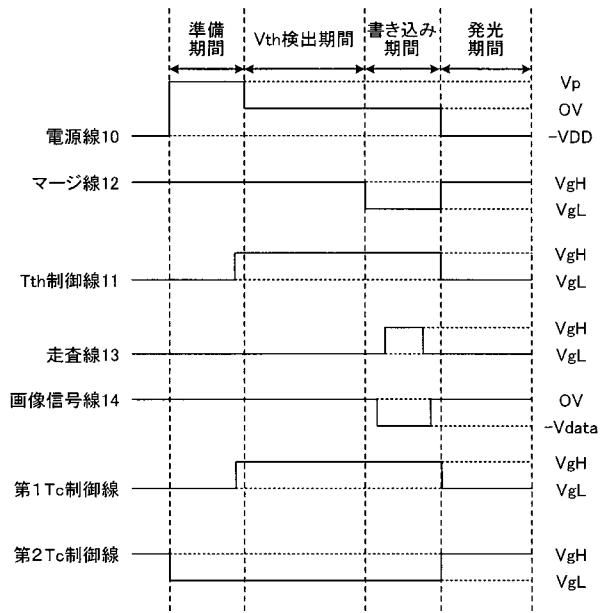

【 0 1 2 0 】

つぎに、この実施の形態 5 の画素回路の動作について説明する。図 20 において、まず、第 1 Tc 制御線 61 を高電位 ( VgH ) にすることで追加容量を  $Cp1 + Cp2$  にし、 Vth 検出および書き込みを行う。この際、 Vgs は、つぎの ( 28 ) 式で表される。

$$Vgs = Vth + [(Call + Cp1 + Cp2 - Cs) / (Call + Cp1 + Cp2)] \cdot Vdata \quad \dots \quad ( 28 )$$

【 0 1 2 1 】

書き込み期間終了後、第 1 制御線 61 を低電位 ( VgL ) にする。ここで、 Cp1 と Cp2 は、同じ容量値 Cpc であるとすると、それぞれ Cpc · Vgs の電荷がたまっている。つぎに、第 2 制御線 62 を高電位 ( VgH ) にすると、 Vgs は、つぎの ( 29 ) 式で表わされる  $Vgs'$  となる。

$$Vgs' = Vgs [(Call' + Cpc) / (Call' + Cpc/2)] \quad \dots \quad ( 29 )$$

【 0 1 2 2 】

つぎに、電源線 10 、マージ線 12 、 Tth 制御線 62 等の電位を図 21 における発光期間の電位に設定すると、実施の形態 1 の画素回路のように Vgs が変化する。このとき

10

20

30

40

50

の  $V_{gs}$  の変化は、つぎの(30)式の  $V_{gs}''$  で表すことができる。

$$\begin{aligned}

V_{gs}'' &= V_{gs}' + C_{gd}T_d/(C_{all}' + C_{pc}/2)[VDD - V_{tholed} \\

&\quad - V_{th} + C_s/(C_{all} + 2C_{pc})V_{data}] \\

&= [(C_{all}' + C_{pc})(C_{all}' + C_{pc}/2 - C_{gd}T_d)/(C_{all}' + C_{pc}/2)^2]V_{th} + a \cdot V_{data} + d \cdot \\

&\dots (30)

\end{aligned}$$

【0123】

なお、これらの式に示される  $a$ 、 $d$  は、上記(16)、(17)式に示したものと同一である。  $C_{all}' > C_{pc}$  且つ  $C_{all}' > C_{gd}T_d$  であるならば、つぎの(31)式が成立するような容量値  $C_{pc}$  を設定することにより、(30)式の右辺第1項である閾値電圧  $V_{th}$  の係数が 1 となり、閾値電圧  $V_{th}$  への依存度が理論的には 0 となる。

$$C_{pc}/2 = C_{gd}T_d \dots (31)$$

$$V_{gs}'' - V_{th} = a \cdot V_{data} + d \dots (32)$$

【0124】

つまり、駆動トランジスタ  $T_d$  のドレインからソースに流れる電流  $I_{ds}$  の値は駆動トランジスタ  $T_d$  の閾値電圧  $V_{th}$  には理論的には依存しない。これにより、発光期間における有機EL素子への通電量の駆動閾値  $V_{th}$  の影響を理論的には除去することができる。

【0125】

図21は、第1  $T_c$  制御線および第2  $T_c$  制御線の駆動波形を示すシーケンス図である。同図に示すように、第1  $T_c$  制御線 61 は  $V_{th}$  検出時および書き込み時には高電位であり、逆に発光時には低電位である。これに対して第2  $T_c$  制御線 62 は準備時、 $V_{th}$  検出時、および書き込み時に低電位であり、発光時に高電位である。

【0126】

また、図21から明らかなように、第1  $T_c$  制御線および  $T_{th}$  制御線は、高電位および低電位となるタイミングがほぼ一致している。したがって、第1  $T_c$  制御線と  $T_{th}$  制御線とを共用することができ、外部駆動装置と各画素を接続する制御線の本数を少なくすることができるという効果が得られる。なお、 $T_{th}$  制御線 11 と第1  $T_c$  制御線 61 を共通の  $T_{th}/T_c$  制御線 65 で共用する画素回路の構成例を図22に示す。

【0127】

以上、説明したように、この実施の形態の画像表示装置によっても、容量素子とスイッチングトランジスタとの直列接続回路による容量可変手段を設けるようにしているので、駆動トランジスタ  $T_d$  (ドライバ手段) や閾値電圧検出用トランジスタ  $T_{th}$  (閾値検出手段) 等に存在する寄生容量の影響を小さくし、寄生容量による輝度のバラツキを低減することができる。

【0128】

なお、実施の形態5の画像表示装置においても、実施の形態1と同様に、閾値電圧検出手段および駆動トランジスタの素子としてアモルファスシリコンTFTを用いる他、これに代えて、ポリシリコンTFT等、他のTFTを用いてもよい。

【0129】

また、図20および図22に示した画素回路は、電圧制御型の画素回路に容量可変手段の構成を適用する例について示したが、電流制御型の画素回路に同様な容量可変手段の構成を適用することもできる。この場合、図12に示す実施の形態3の構成例のように、駆動トランジスタ  $T_d'$  のゲートと閾値電圧検出用トランジスタ  $T_{th}'$  のゲートとの間に容量可変手段が接続されるように構成すればよい。

【産業上の利用可能性】

【0130】

以上のように、本発明にかかる画像表示装置は、寄生容量による輝度のバラツキの防止に対して有用である。

【図面の簡単な説明】

【0131】

【図1】本発明の実施の形態1にかかる画像表示装置の1画素に対応する画素回路の構成を示す図である。

【図2】図1に示した薄膜トランジスタTFTの構成を示す断面図である。

【図3-1】図1に示した可変容量Ccの構成を示す概略平面図である。

【図3-2】図1に示した可変容量Ccの構成を示すX-X線視断面図である。

【図4】図1および図3-1, 図3-2に示した可変容量Ccの単位面積当たりの容量の変化を示すグラフである。

【図5】実施の形態1の動作を説明するためのシーケンス図である。

【図6】図5に示した準備期間の動作を説明する図である。

【図7】図5に示した閾値電圧検出期間の動作を説明する図である。

10

【図8】図5に示した書き込み期間の動作を説明する図である。

【図9】図5に示した発光期間の動作を説明する図である。

【図10】本発明の実施の形態2にかかる画像表示装置の1画素に対応する画素回路の構成を示す図である。

【図11】電流制御型の画像表示装置の1画素に対応する画素回路の構成を示す図である。

【図12】本発明の実施の形態3にかかる画像表示装置の1画素に対応する画素回路の構成を示す図である。

【図13】本発明の実施の形態4にかかる容量可変手段の構成を示す図である。

【図14】図13の容量可変手段を適用した実施の形態4にかかる画像表示装置の1画素に対応する画素回路の構成を示す図である。

20

【図15】Tc制御線の駆動波形を示すシーケンス図である。

【図16】Tth制御線11とTc制御線50とを共通のTth/Tc制御線55で共用する画素回路の構成例を示す図である。

【図17】従来の画像表示装置の1画素に対応する画素回路の構成を示す図である。

【図18】図17に示した画素回路に発生する寄生容量等を示す図である。

【図19】本発明の実施の形態5にかかる容量可変手段の構成を示す図である。

【図20】図19の容量可変手段を適用した実施の形態5にかかる画像表示装置の1画素に対応する画素回路の構成を示す図である。

【図21】第1Tc制御線および第2Tc制御線の駆動波形を示すシーケンス図である。

30

【図22】第1Tth制御線61および第2Tth制御線62とTc制御線50とを共通のTth/Tc制御線65で共用する画素回路の構成例を示す図である。

【符号の説明】

【0132】

10, 40 電源線

11 Tth制御線

12 マージ線

13 走査線

14 画像信号線

20 Cc制御線

30 Tth/Cc制御線

41 画像信号線

42 Tth制御/走査線

50 Tc制御線

51 入力端

55, 65 Tth/Tc制御線

61 第1Tc制御線

62 第2Tc制御線

OLED 有機EL素子

Td, Td' 駆動トランジスタ

40

50

T<sub>th</sub>, T<sub>th'</sub> 閾値電圧検出用トランジスタ

T<sub>1</sub>, T<sub>2</sub>, T<sub>c</sub>, T<sub>c1</sub>, T<sub>c2</sub>, T<sub>c3</sub> スイッチングトランジスタ

C<sub>s</sub> 補助容量

C<sub>c</sub> 可変容量

C<sub>p</sub>, C<sub>p1</sub>, C<sub>p2</sub> 固定容量

【図1】

【図2】

【図3-1】

【図3-2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図19】

【図18】

【図20】

【図21】

【図22】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 4 2 A |

| H 0 5 B | 33/14 | A       |

| H 0 1 L | 29/78 | 6 1 4   |

| H 0 1 L | 29/78 | 6 1 2 Z |

F ターム(参考) 5F110 AA30 BB01 CC07 EE03 EE06 EE44 FF02 FF03 FF29 GG02

GG13 GG15 HK03 HK06 HK33 NN71 NN72 NN73

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 图像显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP2006209074A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2006-08-10 |

| 申请号            | JP2005245049                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2005-08-25 |

| [标]申请(专利权)人(译) | 京瓷株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 京瓷株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 高杉 親知<br>草深 薫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 高杉 親知<br>草深 薫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 H01L29/786 H01L21/336                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0819 G09G2300/0852 G09G2300/0866 G09G2320/0223 G09G2320/0233<br>G09G2320/043 H01L27/1296 H01L27/3244 H01L29/458                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.641.C G09G3/20.611.H G09G3/30.K G09G3/20.642.A<br>H05B33/14.A H01L29/78.614 H01L29/78.612.Z G09G3/3233 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 5C080/AA06 5C080/BB05 5C080/DD05 5C080<br>/EE29 5C080/FF11 5C080/HH09 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5F110/AA30 5F110<br>/BB01 5F110/CC07 5F110/EE03 5F110/EE06 5F110/EE44 5F110/FF02 5F110/FF03 5F110/FF29<br>5F110/GG02 5F110/GG13 5F110/GG15 5F110/HK03 5F110/HK06 5F110/HK33 5F110/NN71 5F110<br>/NN72 5F110/NN73 3K107/AA01 3K107/BB01 3K107/CC21 3K107/CC33 3K107/EE03 3K107/HH04<br>3K107/HH05 5C380/AA01 5C380/AB06 5C380/AB22 5C380/AB23 5C380/BA40 5C380/BB02 5C380<br>/CA12 5C380/CC04 5C380/CC07 5C380/CC26 5C380/CC33 5C380/CC34 5C380/CC42 5C380/CC48<br>5C380/CC51 5C380/CC61 5C380/CC62 5C380/CC64 5C380/CC65 5C380/CC71 5C380/CD013 5C380<br>/CD014 5C380/CD023 5C380/CD024 5C380/DA02 5C380/DA06 5C380/DA47 |         |            |

| 代理人(译)         | 酒井宏明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 优先权            | 2004252753 2004-08-31 JP<br>2004377348 2004-12-27 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 其他公开文献         | JP5137299B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

## 摘要(译)

要解决的问题：防止由于寄生电容引起的亮度变化。提供了在通电时发光的有机EL元件OLED，栅极(第一端子)，漏极(第二端子)和源极，并且其电位差高于施加在栅极和漏极之间的预定驱动阈值。连接至驱动晶体管Td，根据上述控制有机EL元件OLED的驱动晶体管Td，检测与驱动晶体管Td的栅极和漏极之间的驱动阈值相对应的阈值电压的阈值电压检测晶体管Tth和驱动晶体管Td。以及可变电容Cc。[选型图]图1