(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-148128

(P2007-148128A)

(43) 公開日 平成19年6月14日(2007.6.14)

|                  |                  |                  |

|------------------|------------------|------------------|

| (51) Int.C1.     | F 1              | テーマコード (参考)      |

| <b>G09G 3/30</b> | <b>GO9G 3/30</b> | <b>5 C 0 8 0</b> |

| <b>G09G 3/20</b> | <b>(2006.01)</b> | <b>GO9G 3/20</b> |

|                  |                  | <b>6 2 4 B</b>   |

|                  |                  | <b>GO9G 3/20</b> |

|                  |                  | <b>6 4 1 D</b>   |

|                  |                  | <b>GO9G 3/20</b> |

|                  |                  | <b>6 1 1 H</b>   |

|                  |                  | <b>GO9G 3/20</b> |

|                  |                  | <b>6 1 2 E</b>   |

審査請求 未請求 請求項の数 18 O L (全 36 頁) 最終頁に続く

|           |                              |          |                                         |

|-----------|------------------------------|----------|-----------------------------------------|

| (21) 出願番号 | 特願2005-344206 (P2005-344206) | (71) 出願人 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号  |

| (22) 出願日  | 平成17年11月29日 (2005.11.29)     | (74) 代理人 | 100092336<br>弁理士 鈴木 晴敏                  |

|           |                              | (72) 発明者 | 内野 勝秀<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内 |

|           |                              | (72) 発明者 | 山下 淳一<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内 |

|           |                              | (72) 発明者 | 山本 哲郎<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内 |

最終頁に続く

(54) 【発明の名称】 画素回路

## (57) 【要約】

【課題】ドライブトランジスタの閾電圧のばらつきをキャンセルする機能を備えた画素回路の簡素化及び合理化を図る。

【解決手段】ドライブトランジスタT 5のゲートGとソースS間に画素容量C 1が接続され、ソースSとカソード電位V<sub>c a t</sub>間に発光素子E Lが接続され、ゲートGと信号線S Lとの間にサンプリングトランジスタT 1が接続され、ドレインDと電源V<sub>c c</sub>との間にスイッチングトランジスタT 4が接続され、ソースSと信号線S Lとの間に別のスイッチングトランジスタT 2が接続されている。二つのスイッチングトランジスタT 2, T 4は、映像信号V<sub>s i g</sub>が画素容量C 1にサンプリングされる前に動作し、ドライブトランジスタT 5の閾電圧を検出して画素容量C 1に書き込み、以って出力電流の閾電圧に対する依存性を補正する。

【選択図】図14

**【特許請求の範囲】****【請求項 1】**

信号線と所要数の走査線が交差する部分に配され、発光素子とこれを駆動するドライブトランジスタとを含む画素回路であって、

該ドライブトランジスタのゲートとソース間に画素容量が接続され、該ドライブトランジスタのソースと所定のカソード電位間に該発光素子が接続され、該ドライブトランジスタのゲートと信号線との間にサンプリングトランジスタが接続され、該ドライブトランジスタのドレインと電源との間にスイッチングトランジスタが接続され、該ドライブトランジスタのソースと信号線との間に別のスイッチングトランジスタが接続されており、

前記サンプリングトランジスタは、水平走査期間に導通して該信号線から供給された映像信号を該画素容量にサンプリングし、10

前記画素容量は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートに入力電圧を印加し、

前記ドライブトランジスタは、該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタの閾電圧に対して依存性を有し、

前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光し、

前記二つのスイッチングトランジスタは、該映像信号が該画素容量にサンプリングされる前に動作し、該ドライブトランジスタの閾電圧を検出して該画素容量に書き込み、以って該出力電流の閾電圧に対する依存性を補正することを特徴とする画素回路。20

**【請求項 2】**

前記信号線は、映像信号を表す信号電圧と、第1のレベルに固定された第1固定電圧と、第2のレベルに固定された第2固定電圧とを切り替えて供給することを特徴とする請求項1記載の画素回路。

**【請求項 3】**

前記信号電圧は映像信号のサンプリング時に該ドライブトランジスタのゲートに与えられ、前記第1固定電圧は閾電圧を補正する時にドライブトランジスタのゲートに与えられ、前記第2固定電圧は閾電圧を補正する前の準備段階で、ドライブトランジスタのソースに与えられることを特徴とする請求項2記載の画素回路。30

**【請求項 4】**

前記二つのスイッチングトランジスタは該水平走査期間に動作し、該ドライブトランジスタの閾電圧を検出して該画素容量に書き込むことを特徴とする請求項1記載の画素回路。30

**【請求項 5】**

信号線と所要数の走査線が交差する部分に配され、発光素子とこれを駆動するドライブトランジスタとを含む画素回路であって、

該ドライブトランジスタのゲートとソース間に画素容量が接続され、該ドライブトランジスタのソースと所定のカソード電位間に該発光素子が接続され、該ドライブトランジスタのゲートと信号線との間にサンプリングトランジスタが接続され、該ドライブトランジスタのドレインと電源との間にスイッチングトランジスタが接続され、該ドライブトランジスタのソースとゲートとの間に別のスイッチングトランジスタが接続されており、40

前記サンプリングトランジスタは、水平走査期間に導通して該信号線から供給された映像信号を該画素容量にサンプリングし、

前記画素容量は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートに入力電圧を印加し、

前記ドライブトランジスタは、該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタの閾電圧に対して依存性を有し、

前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光し、

前記二つのスイッチングトランジスタは、該映像信号が該画素容量にサンプリングされ50

る前に動作し、該ドライブトランジスタの閾電圧を検出して該画素容量に書き込み、以って該出力電流の閾電圧に対する依存性を補正することを特徴とする画素回路。

【請求項 6】

前記信号線は、映像信号を表す信号電圧と、第1のレベルに固定された第1固定電圧と、第2のレベルに固定された第2固定電圧とを切り替えて供給することを特徴とする請求項5記載の画素回路。

【請求項 7】

前記信号電圧は映像信号のサンプリング時に該ドライブトランジスタのゲートに与えられ、前記第1固定電圧は閾電圧を補正する時にドライブトランジスタのゲートに与えられ、前記第2固定電圧は閾電圧を補正する前の準備段階で、該ドライブトランジスタのソースに与えられることを特徴とする請求項6記載の画素回路。

10

【請求項 8】

前記二つのスイッチングトランジスタは該水平走査期間に動作し、該ドライブトランジスタの閾電圧を検出して該画素容量に書き込むことを特徴とする請求項5記載の画素回路。

【請求項 9】

信号線と所要数の走査線が交差する部分に配され、発光素子とこれを駆動するドライブトランジスタとを含む画素回路であって、

該ドライブトランジスタのゲートとソース間に画素容量が接続され、該ドライブトランジスタのソースと所定のカソード電位間に該発光素子が接続され、該ドライブトランジスタのゲートと信号線との間にサンプリングトランジスタが接続され、該ドライブトランジスタのドレインと可変電源との間にスイッチングトランジスタが接続され、該ドライブトランジスタのゲートと固定電源との間に別のスイッチングトランジスタが接続されており、

20

前記サンプリングトランジスタは、水平走査期間に導通して該信号線から供給された映像信号を該画素容量にサンプリングし、

前記画素容量は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートに入力電圧を印加し、

前記ドライブトランジスタは、該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタの閾電圧に対して依存性を有し、

30

前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光し、

前記二つのスイッチングトランジスタは、該映像信号が該画素容量にサンプリングされる前に動作し、該ドライブトランジスタの閾電圧を検出して該画素容量に書き込み、以って該出力電流の閾電圧に対する依存性を補正することを特徴とする画素回路。

40

【請求項 10】

前記可変電源は高電圧と低電圧の二値をとることでドライブトランジスタのゲートとソース間の電圧をその閾電圧以上とし、該高電圧の印加で閾電圧の補正を開始し、ドライブトランジスタと該可変電源との間に接続されている前記スイッチングトランジスタのオフで閾電圧の補正を終了することを特徴とする請求項9記載の画素回路。

【請求項 11】

前記二つのスイッチングトランジスタは、一水平走査期間より長い時間幅で動作して該ドライブトランジスタの閾電圧を該画素容量に書き込むことができることを特徴とする請求項9記載の画素回路。

【請求項 12】

前記発光素子の発光を終了する際に、前記ドライブトランジスタのゲートと前記固定電源との間に接続されている一方のスイッチングトランジスタをオンし、且つ前記ドライブトランジスタのドレインと前記可変電源との間に接続されている他方のスイッチングトランジスタをオフすることで、前記ドライブトランジスタに負バイアスをかけることを特徴とする請求項9記載の画素回路。

50

## 【請求項 1 3】

前記ドライブトランジスタにかける負バイアスは、ドライブトランジスタの閾電圧の変動を抑制することを特徴とする請求項 1 2 記載の画素回路。

## 【請求項 1 4】

前記固定電源は、その電源電圧が該発光素子のカソードに印加されるカソード電圧と該発光素子の閾電圧の和よりも小さく設定されていることを特徴とする請求項 1 3 記載の画素回路。

## 【請求項 1 5】

信号線と所要数の走査線が交差する部分に配され、発光素子とこれを駆動するドライブトランジスタとを含む画素回路であって、

該ドライブトランジスタのゲートとソース間に画素容量が接続され、該ドライブトランジスタのソースと所定のカソード電位間に該発光素子が接続され、該ドライブトランジスタのゲートと信号線との間にサンプリングトランジスタが接続され、該ドライブトランジスタのドレインと固定電源との間に第 1 スイッチングトランジスタが接続され、該ドライブトランジスタのゲートと可変電源との間に第 2 スイッチングトランジスタが接続されており、

前記サンプリングトランジスタは、水平走査期間に導通して該信号線から供給された映像信号を該画素容量にサンプリングし、

前記画素容量は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートに入力電圧を印加し、

前記ドライブトランジスタは、該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタの閾電圧に対して依存性を有し、

前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光し、

前記第 1 スイッチングトランジスタ及び第 2 スイッチングトランジスタは、該映像信号が該画素容量にサンプリングされる前に、該ドライブトランジスタの閾電圧を検出して該画素容量に書き込む補正動作を行い、以って該出力電流の閾電圧に対する依存性を補正し、

前記可変電源は、該補正動作の前にその電源電圧を切り替え、前記第 2 スイッチングトランジスタを介して前記ドライブトランジスタのゲート電圧を高電圧から低電圧に変化させ、この電圧変化を前記ドライブトランジスタのソース電圧にカップリングさせる事で、該補正動作に入る前の準備動作を行うことを特徴とする画素回路。

## 【請求項 1 6】

該準備動作の結果、カップリング後は前記ドライブトランジスタのゲートとソース間の電圧が前記ドライブトランジスタの閾電圧よりも大きくなり、且つ前記ドライブトランジスタのソース電位が前記発光素子の動作点を下回るように設定されることを特徴とする請求項 1 5 記載の画素回路。

## 【請求項 1 7】

前記ドライブトランジスタは、その出力電流がチャネル領域の閾電圧に加えキャリア移動度に対しても依存性を有し、

前記第 1 スイッチングトランジスタは該出力電流のキャリア移動度に対する依存性を打ち消すために該水平走査期間の一部で動作し、該映像信号がサンプリングされている状態で該ドライブトランジスタから出力電流を取り出し、これを該画素容量に負帰還して該入力電圧を補正する移動度補正動作を行うことを特徴とする請求項 1 5 記載の画素回路。

## 【請求項 1 8】

該移動度補正動作を正確に行う為に、あらかじめ前記ドライブトランジスタのソース電位が前記発光素子の動作点を下回るように設定されることを特徴とする請求項 1 7 記載の画素回路。

## 【発明の詳細な説明】

## 【技術分野】

10

20

30

40

50

## 【0001】

本発明は、アクティブマトリクス型表示装置の画素を構成する発光素子を電流駆動する画素回路に関する。より詳しくは、各画素回路内に設けた絶縁ゲート型電界効果トランジスタによって、有機ELなどの発光素子に通電する電流量を制御する技術に関する。さらに詳しくは、発光素子を駆動する絶縁ゲート型電界効果トランジスタの閾電圧の補正技術に関する。

## 【背景技術】

## 【0002】

画像表示装置、例えば液晶ディスプレイなどでは、多数の液晶画素をマトリクス状に並べ、表示すべき画像情報に応じて画素毎に入射光の透過強度又は反射強度を制御することによって画像を表示する。これは、有機EL素子を画素に用いた有機ELディスプレイなどにおいても同様であるが、液晶画素と異なり有機EL素子は自発光素子である。その為、有機ELディスプレイは液晶ディスプレイに比べて画像の視認性が高く、バックライトが不要であり、応答速度が高いなどの利点を有する。又、各発光素子の輝度レベル（階調）はそれに流れる電流値によって制御可能であり、いわゆる電流制御型であるという点で液晶ディスプレイなどの電圧制御型とは大きく異なる。

## 【0003】

有機ELディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として単純マトリクス方式とアクティブマトリクス方式とがある。前者は構造が単純であるものの、大型且つ高精細のディスプレイの実現が難しいなどの問題がある為、現在はアクティブマトリクス方式の開発が盛んに行なわれている。この方式は、各画素回路内部の発光素子に流れる電流を、画素回路内部に設けた能動素子（一般には薄膜トランジスタ、TFT）によって制御するものであり、以下の特許文献に記載がある。

【特許文献1】特開2003-255856

【特許文献2】特開2003-271095

【特許文献3】特開2004-133240

【特許文献4】特開2004-029791

【特許文献5】特開2004-093682

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0004】

従来の画素回路は、制御信号を供給する行状の走査線と映像信号を供給する列状の信号線とが交差する部分に配され、少なくともサンプリングトランジスタと容量部とドライブトランジスタと発光素子とを含む。サンプリングトランジスタは、走査線から供給される制御信号に応じ導通して信号線から供給された映像信号をサンプリングする。容量部は、サンプリングされた映像信号に応じた入力電圧を保持する。ドライブトランジスタは、容量部に保持された入力電圧に応じて所定の発光期間に出力電流を供給する。尚一般に、出力電流はドライブトランジスタのチャネル領域のキャリア移動度及び閾電圧に対して依存性を有する。発光素子は、ドライブトランジスタから供給された出力電流により映像信号に応じた輝度で発光する。

## 【0005】

ドライブトランジスタは、容量部に保持された入力電圧をゲートに受けてソース／ドレン間に電流を流し、発光素子に通電する。一般に発光素子の発光輝度は通電量に比例している。更にドライブトランジスタの出力電流供給量はゲート電圧すなわち容量部に書き込まれた入力電圧によって制御される。従来の画素回路は、ドライブトランジスタのゲートに印加される入力電圧を入力映像信号に応じて変化させることで、発光素子に供給する電流量を制御している。

## 【0006】

ここでドライブトランジスタの動作特性は以下の式1で表わされる。

$$I_{ds} = (1/2) \mu (W/L) C_{ox} (V_{gs} - V_{th})^2 \dots \text{式1}$$

10

20

30

40

50

このトランジスタ特性式 1において、 $I_{ds}$ はソース／ドレイン間に流れるドレイン電流を表わしており、画素回路では発光素子に供給される出力電流である。 $V_{gs}$ はソースを基準としてゲートに印加されるゲート電圧を表わしており、画素回路では上述した入力電圧である。 $V_{th}$ はトランジスタの閾電圧である。又 $\mu$ はトランジスタのチャネルを構成する半導体薄膜の移動度を表わしている。その他 $W$ はチャネル幅を表わし、 $L$ はチャネル長を表わし、 $C_{ox}$ はゲート容量を表わしている。このトランジスタ特性式 1から明らかな様に、薄膜トランジスタは飽和領域で動作する時、ゲート電圧 $V_{gs}$ が閾電圧 $V_{th}$ を超えて大きくなると、オン状態となってドレイン電流 $I_{ds}$ が流れる。原理的に見ると上記のトランジスタ特性式 1が示す様に、ゲート電圧 $V_{gs}$ が一定であれば常に同じ量のドレイン電流 $I_{ds}$ が発光素子に供給される。従って、画面を構成する各画素に全て同一のレベルの映像信号を供給すれば、全画素が同一輝度で発光し、画面の一様性（ユニフォーミティ）が得られるはずである。

10

## 【0007】

しかしながら実際には、ポリシリコンなどの半導体薄膜で構成された薄膜トランジスタ（TFT）は、個々のデバイス特性にはらつきがある。特に、閾電圧 $V_{th}$ は一定ではなく、各画素毎にはらつきがある。前述のトランジスタ特性式 1から明らかな様に、各ドライブトランジスタの閾電圧 $V_{th}$ がばらつくと、ゲート電圧 $V_{gs}$ が一定であっても、ドレイン電流 $I_{ds}$ にはらつきが生じ、画素毎に輝度がばらついてしまう為、画面のユニフォーミティを損なう。従来からドライブトランジスタの閾電圧のばらつきをキャンセルする機能を組み込んだ画素回路が開発されており、例えば前記の特許文献 3に開示がある。

20

## 【0008】

しかしながら、ドライブトランジスタの閾電圧のばらつきをキャンセルする機能（閾電圧補正機能）を組み込んだ画素回路は、素子数が多くなり回路の複雑化を招いていた。画素回路を構成するトランジスタの個数が多くなると、これに伴って各トランジスタを制御する走査線（ゲートライン）や電源ラインの本数が増える。画素回路に対してゲートラインや電源ラインの占める割合が多くなり、パネルの高精細化を難しくしている。またゲートラインや電源ラインの本数が多いとその分配線間のクロスオーバーが増え、パネルの製造歩留りの悪化を招くという課題がある。

20

## 【課題を解決するための手段】

## 【0009】

30

上述した従来の技術の課題に鑑み、本発明はドライブトランジスタの閾電圧のばらつきをキャンセルする機能を備えた画素回路の簡素化及び合理化を図ることを目的とする。かかる目的を達成するために以下の手段を講じた。即ち本発明は、信号線と所要数の走査線が交差する部分に配され、発光素子とこれを駆動するドライブトランジスタとを含む画素回路であって、該ドライブトランジスタのゲートとソース間に画素容量が接続され、該ドライブトランジスタのソースと所定のカソード電位間に該発光素子が接続され、該ドライブトランジスタのゲートと信号線との間にサンプリングトランジスタが接続され、該ドライブトランジスタのドレインと電源との間にスイッチングトランジスタが接続され、該ドライブトランジスタのソースと信号線との間に別のスイッチングトランジスタが接続されており、前記サンプリングトランジスタは、水平走査期間に導通して該信号線から供給された映像信号を該画素容量にサンプリングし、前記画素容量は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートに入力電圧を印加し、前記ドライブトランジスタは、該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタの閾電圧に対して依存性を有し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光し、前記二つのスイッチングトランジスタは、該映像信号が該画素容量にサンプリングされる前に動作し、該ドライブトランジスタの閾電圧を検出して該画素容量に書き込み、以って該出力電流の閾電圧に対する依存性を補正することを特徴とする。

40

## 【0010】

具体的に前記信号線は、映像信号を表す信号電圧と、第 1 のレベルに固定された第 1 固

50

定電圧と、第2のレベルに固定された第2固定電圧とを切り替えて供給する。この場合前記信号電圧は映像信号のサンプリング時に該ドライブトランジスタのゲートに与えられ、前記第1固定電圧は閾電圧を補正する時にドライブトランジスタのゲートに与えられ、前記第2固定電圧は閾電圧を補正する前の準備段階で、ドライブトランジスタのソースに与えられる。又前記二つのスイッチングトランジスタは該水平走査期間に動作し、該ドライブトランジスタの閾電圧を検出して該画素容量に書き込む。

## 【0011】

又本発明は、信号線と所要数の走査線が交差する部分に配され、発光素子とこれを駆動するドライブトランジスタとを含む画素回路であって、該ドライブトランジスタのゲートとソース間に画素容量が接続され、該ドライブトランジスタのソースと所定のカソード電位間に該発光素子が接続され、該ドライブトランジスタのゲートと信号線との間にサンプリングトランジスタが接続され、該ドライブトランジスタのドレインと電源との間にスイッチングトランジスタが接続され、該ドライブトランジスタのソースとゲートとの間に別のスイッチングトランジスタが接続されており、前記サンプリングトランジスタは、水平走査期間に導通して該信号線から供給された映像信号を該画素容量にサンプリングし、前記画素容量は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートに入力電圧を印加し、前記ドライブトランジスタは、該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタの閾電圧に対して依存性を有し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光し、前記二つのスイッチングトランジスタは、該映像信号が該画素容量にサンプリングされる前に動作し、該ドライブトランジスタの閾電圧を検出して該画素容量に書き込み、以って該出力電流の閾電圧に対する依存性を補正することを特徴とする。

## 【0012】

具体的に前記信号線は、映像信号を表す信号電圧と、第1のレベルに固定された第1固定電圧と、第2のレベルに固定された第2固定電圧とを切り替えて供給する。この場合前記信号電圧は映像信号のサンプリング時に該ドライブトランジスタのゲートに与えられ、前記第1固定電圧は閾電圧を補正する時にドライブトランジスタのゲートに与えられ、前記第2固定電圧は閾電圧を補正する前の準備段階で、該ドライブトランジスタのソースに与えられる。又前記二つのスイッチングトランジスタは該水平走査期間に動作し、該ドライブトランジスタの閾電圧を検出して該画素容量に書き込む。

## 【0013】

更に本発明は、信号線と所要数の走査線が交差する部分に配され、発光素子とこれを駆動するドライブトランジスタとを含む画素回路であって、該ドライブトランジスタのゲートとソース間に画素容量が接続され、該ドライブトランジスタのソースと所定のカソード電位間に該発光素子が接続され、該ドライブトランジスタのゲートと信号線との間にサンプリングトランジスタが接続され、該ドライブトランジスタのドレインと可変電源との間にスイッチングトランジスタが接続され、該ドライブトランジスタのゲートと固定電源との間に別のスイッチングトランジスタが接続されており、前記サンプリングトランジスタは、水平走査期間に導通して該信号線から供給された映像信号を該画素容量にサンプリングし、前記画素容量は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートに入力電圧を印加し、前記ドライブトランジスタは、該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタの閾電圧に対して依存性を有し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光し、前記二つのスイッチングトランジスタは、該映像信号が該画素容量にサンプリングされる前に動作し、該ドライブトランジスタの閾電圧を検出して該画素容量に書き込み、以って該出力電流の閾電圧に対する依存性を補正することを特徴とする。

## 【0014】

具体的に前記可変電源は高電圧と低電圧の二値をとることでドライブトランジスタのゲートとソース間の電圧をその閾電圧以上とし、該高電圧の印加で閾電圧の補正を開始し、

10

20

30

40

50

ドライブトランジスタと該可変電源との間に接続されている前記スイッチングトランジスタのオフで閾電圧の補正を終了する。又前記二つのスイッチングトランジスタは、一水平走査期間より長い時間幅で動作して該ドライブトランジスタの閾電圧を該画素容量に書き込むことができる。又前記発光素子の発光を終了する際に、前記ドライブトランジスタのゲートと前記固定電源との間に接続されている一方のスイッチングトランジスタをオンし、且つ前記ドライブトランジスタのドレインと前記可変電源との間に接続されている他方のスイッチングトランジスタをオフすることで、前記ドライブトランジスタに負バイアスをかける。この場合、前記ドライブトランジスタにかける負バイアスは、ドライブトランジスタの閾電圧の変動を抑制する。又前記固定電源は、その電源電圧が該発光素子のカソードに印加されるカソード電圧と該発光素子の閾電圧の和よりも小さく設定されている。

10

## 【0015】

加えて本発明は、信号線と所要数の走査線が交差する部分に配され、発光素子とこれを駆動するドライブトランジスタとを含む画素回路であって、該ドライブトランジスタのゲートとソース間に画素容量が接続され、該ドライブトランジスタのソースと所定のカソード電位間に該発光素子が接続され、該ドライブトランジスタのゲートと信号線との間にサンプリングトランジスタが接続され、該ドライブトランジスタのドレインと固定電源との間に第1スイッチングトランジスタが接続され、該ドライブトランジスタのゲートと可変電源との間に第2スイッチングトランジスタが接続されており、前記サンプリングトランジスタは、水平走査期間に導通して該信号線から供給された映像信号を該画素容量にサンプリングし、前記画素容量は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートに入力電圧を印加し、前記ドライブトランジスタは、該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタの閾電圧に対して依存性を有し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光し、前記第1スイッチングトランジスタ及び第2スイッチングトランジスタは、該映像信号が該画素容量にサンプリングされる前に、該ドライブトランジスタの閾電圧を検出して該画素容量に書き込む補正動作を行い、以って該出力電流の閾電圧に対する依存性を補正し、前記可変電源は、該補正動作の前にその電源電圧を切り替え、前記第2スイッチングトランジスタを介して前記ドライブトランジスタのゲート電圧を高電圧から低電圧に変化させ、この電圧変化を前記ドライブトランジスタのソース電圧にカップリングさせる事で、該補正動作に入る前の準備動作を行うことを特徴とする画。

20

## 【0016】

具体的には該準備動作の結果、カップリング後は前記ドライブトランジスタのゲートとソース間の電圧が前記ドライブトランジスタの閾電圧よりも大きくなり、且つ前記ドライブトランジスタのソース電位が前記発光素子の動作点を下回るように設定される。又前記ドライブトランジスタは、その出力電流がチャネル領域の閾電圧に加えキャリア移動度に対しても依存性を有し、前記第1スイッチングトランジスタは該出力電流のキャリア移動度に対する依存性を打ち消すために該水平走査期間の一部で動作し、該映像信号がサンプリングされている状態で該ドライブトランジスタから出力電流を取り出し、これを該画素容量に負帰還して該入力電圧を補正する移動度補正動作を行う。この場合、該移動度補正動作を正確に行う為に、あらかじめ前記ドライブトランジスタのソース電位が前記発光素子の動作点を下回るように設定される。

30

## 【発明の効果】

## 【0017】

本発明によれば、画素回路は発光素子を駆動するドライブトランジスタと画素容量に映像信号をサンプリングするサンプリングトランジスタの他に、2個のスイッチングトランジスタを含んでいる。本発明では、映像信号を画素容量にサンプリングする前に、これら2個のスイッチングトランジスタをオンオフ制御してドライブトランジスタの閾電圧補正を行っている。即ちドライブトランジスタの閾電圧を検出して画素容量に書き込み、以って出力電流の閾電圧に対する依存性を補正している。閾電圧補正機能を備えた本発明の画

40

50

素回路は、ドライブトランジスタとサンプリングトランジスタの他に2個のスイッチングトランジスタを追加し、合計4個のトランジスタで構成されている。この様に画素回路の構成を簡素化及び合理化することで、各トランジスタを制御するゲートラインや電源ラインの本数を削減することが可能である。これら配線本数の削減によりパネルの高精細化及び高歩留り化を達成できる。

【発明を実施するための最良の形態】

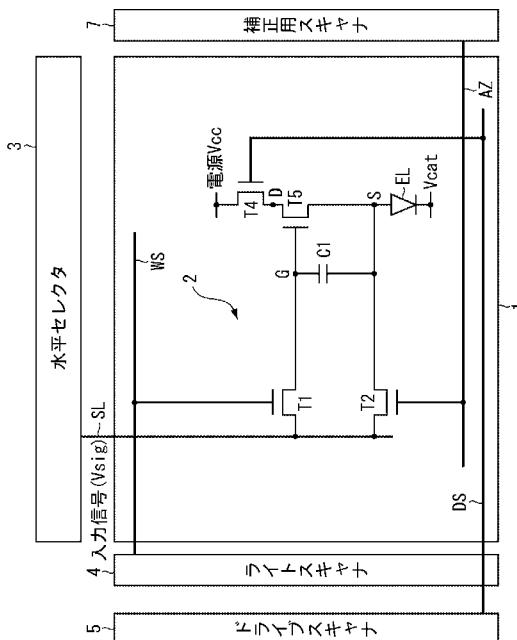

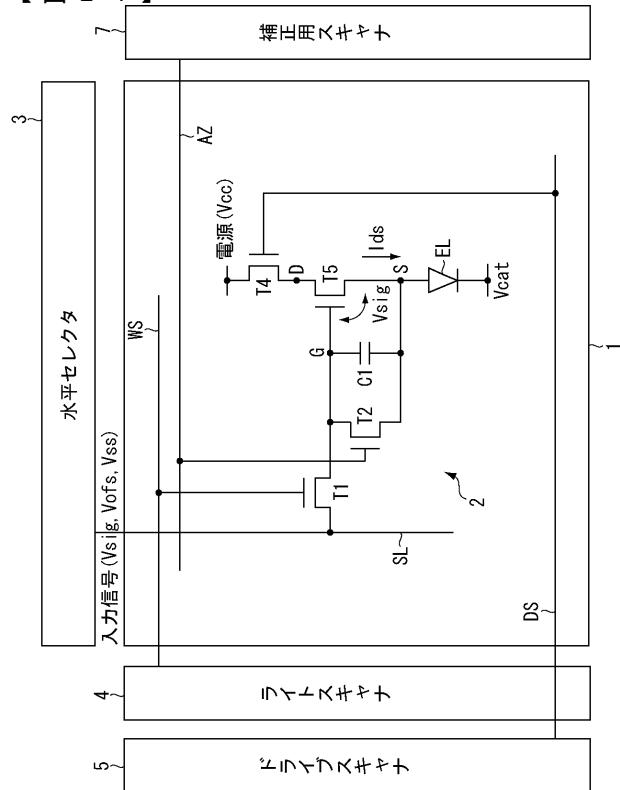

【0018】

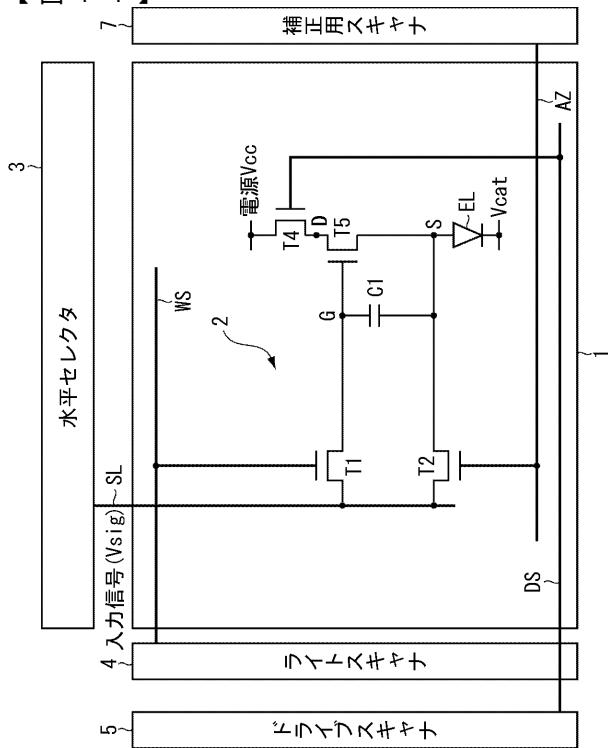

以下図面を参照して本発明の実施の形態を詳細に説明する。まず最初に本発明の背景を明らかにするため、図1を参照して基本的なアクティブマトリクス型表示装置の構成を説明する。図示する様にこの表示装置は、画素アレイ1と水平セレクタ3とライトスキャナ4とで構成されている。画素アレイ1は1枚のパネルに集積形成される。水平セレクタ3とライトスキャナ4はパネルに内蔵される場合と外付けされる場合とがある。画素アレイ1は行状に配列した走査線WSと列状に配列した信号線SLと両者の交差部に配された画素回路2とで構成されている。走査線WSはライトスキャナ4に接続されており、順次制御信号を出力して、画素回路2を行単位で順次選択する。水平セレクタ3は各信号線SLに接続されており、選択された画素回路2に映像信号を書き込む。

【0019】

図2は、図1に示した画素回路2の一例を示す回路図である。この画素回路2は最も単純な構成を有しており、2個のトランジスタT1, T5と1個の画素容量C1と1個の発光素子ELとで構成されている。サンプリングトランジスタT1はNチャネル型の薄膜トランジスタである。ドライブトランジスタT5はPチャネル型の薄膜トランジスタである。画素容量C1は薄膜容量である。発光素子ELは例えば有機EL薄膜を発光層とする2端子素子(ダイオード)である。これらの素子T1, T5, C1, ELはパネルを構成する絶縁基板の上に集積形成される。

【0020】

サンプリングトランジスタT1は信号線SLとドライブトランジスタT5のゲートとの間に接続されている。サンプリングトランジスタT1のゲートは走査線WSを介してライトスキャナ4に接続されている。ドライブトランジスタT5のゲートには、画素容量C1が接続されている。ドライブトランジスタT5のソースは電源Vccに接続されている。ドライブトランジスタT5のドレインは発光素子ELのアノードに接続されている。発光素子ELのカソードは接地されている。

【0021】

サンプリングトランジスタT1は水平走査期間になるとライトスキャナ4から制御信号が印加され、導通状態になる。これによりサンプリングトランジスタT1は水平セレクタ3から信号線SLに供給された映像信号をサンプリングし、画素容量C1に書き込む。ドライブトランジスタT5は画素容量C1に書き込まれた映像信号に応じてドレイン電流Idsを発光素子ELに供給する。これにより、発光素子ELは映像信号に応じた輝度で発光する。

【0022】

図2に示した方式では、ドライブトランジスタのゲート印加電圧Vgsを映像信号に応じて変化させることで、発光素子ELに流れる出力電流Idsをコントロールしている。本例ではPチャネル型のサンプリングトランジスタT5のソースは電源Vccに接続されており、常に飽和領域で動作するよう設計されているので、前述の式1にしたがって動作する定電流源となる。即ちこのPチャネル型のドライブトランジスタT5は、発光素子EL側に接続されたドレインの電位に依存することなく、常にゲートとソース間の電圧Vgsに従って一定の出力電流Idsを発光素子ELに供給できる。

【0023】

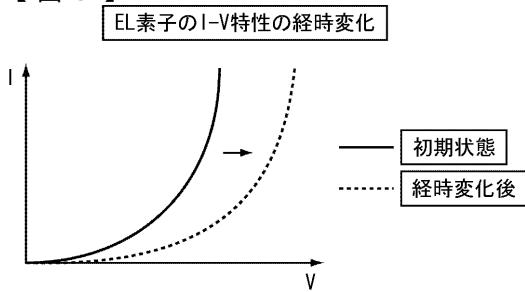

図3は、発光素子ELのI-V特性を示すグラフである。有機EL素子などによって代表される発光素子は、I-V特性が経時的に変化する傾向があり、実線が初期状態を表す一方点線が経時変化後のI-V特性を表している。グラフで電圧Vはアノード電圧である

10

20

30

40

50

。図2と対応させると、このアノード電圧VはドライブトランジスタT5のドレイン電圧となっている。一方電流Iは、ドライブトランジスタT5から供給される出力電流I<sub>ds</sub>である。前述したように、図2の画素回路2はドライブトランジスタT5がドレイン電圧に依存することなく、常に一定の出力電流I<sub>ds</sub>を発光素子ELに供給できる。したがって発光素子ELのI-V特性が経時に変化しても、この影響を受けることなく定電流を供給することが可能である。したがって、発光素子ELには輝度の変化が生じない。

## 【0024】

図4は、従来の画素回路2の他の例を示す回路図である。理解を容易にするため、図2に示した先の従来例と対応する部分には対応する参照番号を付してある。異なる点は、ドライブトランジスタT5がPチャネル型ではなくNチャネル型となっていることである。この場合、ドライブトランジスタT5のソース側が発光素子ELのアノード側と接続することになる。したがってソース電位が発光素子ELのI-V特性の経時変化に影響を受けて変動することになる。発光素子の経時変化と共にゲート/ソース間電圧V<sub>gs</sub>が変化してしまう。これにより発光素子ELに流れる出力電流I<sub>ds</sub>の量が変化し、発光輝度が変わってしまう。これに加え、ドライブトランジスタT5は個々の画素回路毎に閾電圧V<sub>th</sub>がばらついている。したがって、前述の式1に示すように、ドレイン電流I<sub>ds</sub>はV<sub>gs</sub>やV<sub>th</sub>の変動によってばらつきが生じ、発光輝度が画素毎に変化してしまう。

## 【0025】

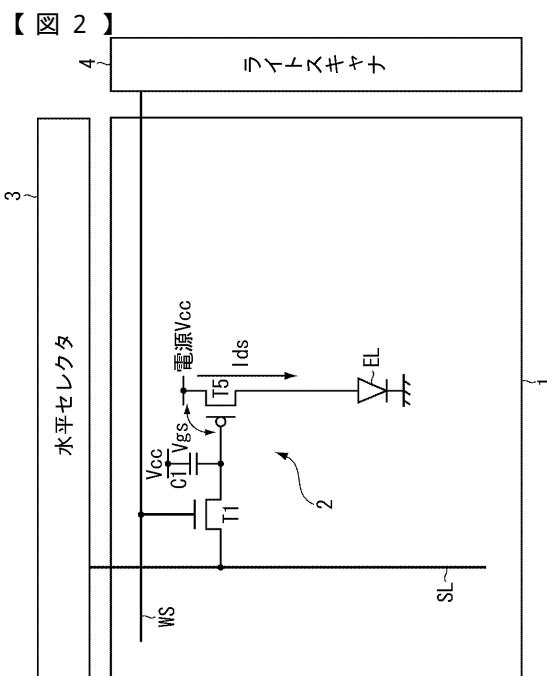

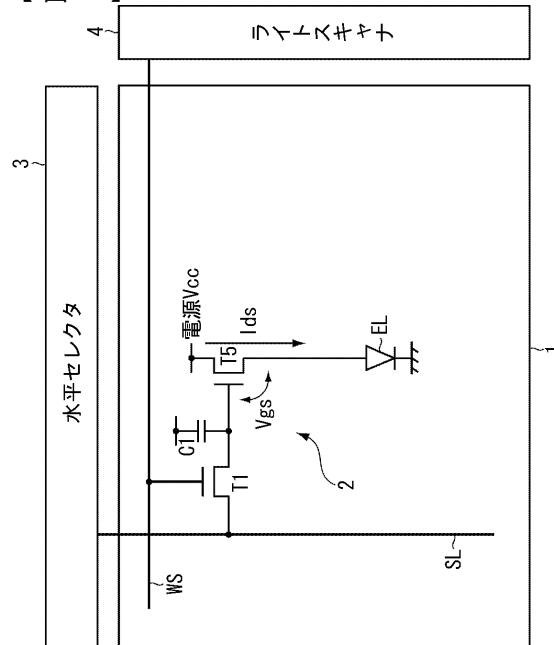

発光素子ELの経時劣化やドライブトランジスタT5の特性ばらつきに対処する画素回路として、例えば図5に示す参考例が先行開発されている。理解を容易にするため、図5に示した参考例は、図4に示した従来例と対応する参照番号を付してある。図示する様に本表示装置は、画素アレイ1と水平セレクタ3とライトスキャナ4とドライブスキャナ5と補正用スキャナ7と第2補正用スキャナ8とで構成されている。画素アレイ1はマトリクス状に配された画素回路2を含んでいる。図示を簡略化するため、1個の画素回路2を表してある。この画素回路2は5個のトランジスタT1ないしT5と1個の画素容量C1と1個の発光素子ELとで構成されており、比較的素子数が多い。またこの画素回路2を駆動するラインは、走査線がWS, DS, AZ, AZ2の4本、信号線SLが1本、電源ラインがVcc, Vss, Vofs, Vcatの4本で、比較的多い。制御ラインは計9本もあり、画素の占める面積を圧迫している。なお走査線WSはライトスキャナ4によって走査され、DSはドライブスキャナ5によって走査され、AZは補正用スキャナ7によって制御され、AZ2は第2補正用スキャナ8によって制御される。信号線SLには水平セレクタ3から入力信号(Vsig)が供給される。本例は全てのトランジスタT1ないしT5がNチャネル型である。中心となるドライブトランジスタT5のソースSは発光素子ELのアノードに接続されている。発光素子ELのカソードはVcatに接続されている。ドライブトランジスタT5のドレインはスイッチングトランジスタT4を介してVccに接続している。スイッチングトランジスタT4のゲートは走査線DSに接続している。ドライブトランジスタT5のゲートGはサンプリングトランジスタT1を介して信号線SLに接続している。サンプリングトランジスタT1のゲートは走査線WSに接続している。ドライブトランジスタT5のゲートGはスイッチングトランジスタT3を介してVofsに接続している。スイッチングトランジスタT3のゲートは走査線AZ2に接続している。ドライブトランジスタT5のゲートGとソースSの間には画素容量C1が接続されている。ドライブトランジスタT5のソースSはスイッチングトランジスタT2を介してVssに接続している。スイッチングトランジスタT2のゲートは走査線AZに接続している。

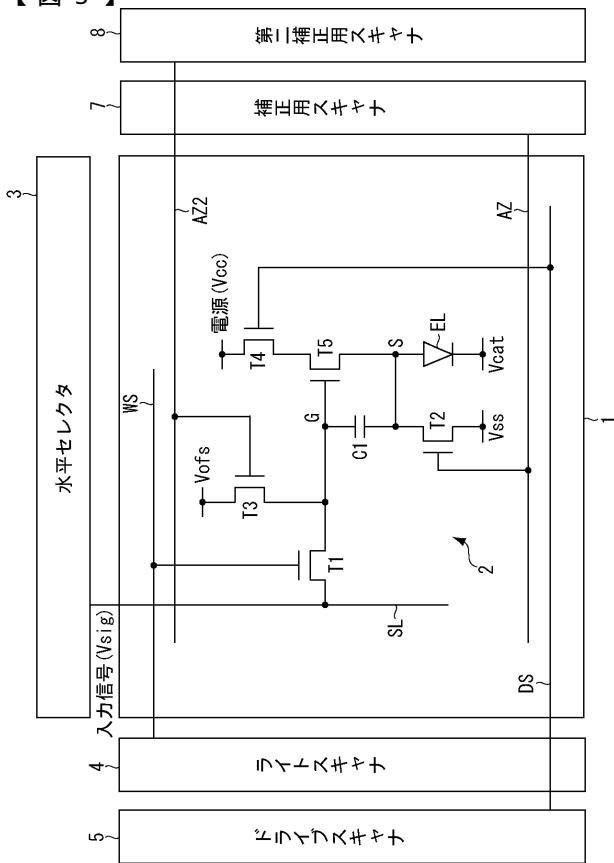

## 【0026】

図6は、図5に示した画素回路2の動作説明に供するタイミングチャートである。時間軸Jに沿ってトランジスタT1ないしT4のオン/オフの変化を表している。T1ないしT4のオン/オフ制御は、それぞれ対応する走査線を介して対応するスキャナによって行われる。このタイミングチャートはドライブトランジスタT5のゲートGとソースSの電位変化も合わせて表してある。タイミングJ1に入る前はトランジスタT4がオンしてい

10

20

30

40

50

るため、発光素子 E L にはドライブトランジスタ T 5 を介して出力電流が供給され発光状態にある。

【 0 0 2 7 】

タイミング J 1 になるとトランジスタ T 3 がオンし、ドライブトランジスタ T 5 のゲート G が  $V_{of}$  まで低下する。またスイッチングトランジスタ T 2 がオンするため、ドライブトランジスタ T 5 のソース S は  $V_{ss}$  まで低下する。 $V_{ss}$  は発光素子 E L の閾電圧  $V_{thel}$  よりも低いので、発光素子 E L には電流が流れず非発光期間に入る。また  $V_{of}$  と  $V_{ss}$  の電位差はドライブトランジスタ T 5 の閾電圧  $V_{th}$  よりも大きい。この様に画素容量 C 1 の両端の電位を設定することで、閾電圧補正動作の準備が行われる。

【 0 0 2 8 】

タイミング J 2 でスイッチングトランジスタ T 2 がオフする。これによりドライブトランジスタ T 5 のソース S が  $V_{ss}$  から切り離され、上昇を始める。ドライブトランジスタ T 5 から画素容量 C 1 に電流が流れ込み、両端の電圧  $V_{gs}$  が丁度ドライブトランジスタ T 5 の閾電圧  $V_{th}$  に等しくなったところでカットオフする。この結果画素容量 C 1 の両端にはドライブトランジスタ T 5 の閾電圧  $V_{th}$  に相当する電圧が書き込まれる。以上により閾値キャンセル動作が行われた。

【 0 0 2 9 】

タイミング J 3 でスイッチングトランジスタ T 4 をオフしさらにタイミング J 4 でスイッチングトランジスタ T 3 もオフする。この時点でトランジスタ T 1 ないし T 4 は全てオフとなる。

【 0 0 3 0 】

タイミング J 5 でサンプリングトランジスタ T 1 がオンし、信号線 S L から供給された映像信号  $V_{sig}$  がドライブトランジスタ T 5 のゲート G に書き込まれる。当該画素回路 2 に割り当てられた水平走査期間 ( 1 H ) が経過するタイミング J 6 でサンプリングトランジスタ T 1 はオフする。この期間 J 5 - J 6 で信号書き込みが行われた。

【 0 0 3 1 】

この後タイミング J 7 に進みスイッチングトランジスタ T 4 がオンする。これによりドライブトランジスタ T 5 は電源  $V_{cc}$  に接続されるので出力電流を供給する。この出力電流の値は画素容量 C 1 に保持された入力電圧  $V_{gs}$  によって一定に制御される。ドライブトランジスタ T 5 のソース S の電位が上昇し始め、発光素子 E L の閾電圧  $V_{thel}$  を超えた時点で発光が始まる。ブートストラップ効果で、ソース電位の上昇に伴いこれと連動してドライブトランジスタ T 5 のゲート電位も上昇する。ドライブトランジスタ T 5 のゲート / ソース間電圧  $V_{gs}$  は、常に画素容量 C 1 によって一定に保持されている。

【 0 0 3 2 】

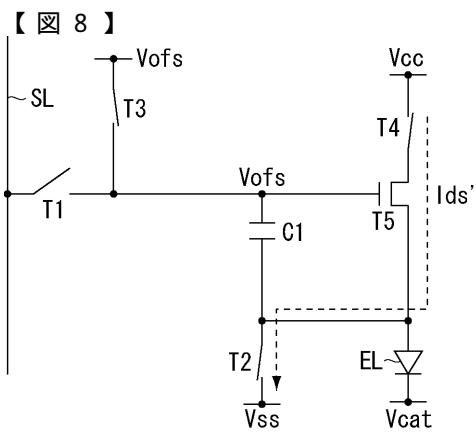

以下図 7 ないし図 13 を参照して、図 5 及び図 6 に示した先行開発にかかる画素回路の動作を詳細に説明する。まず、発光素子 E L の発光状態は図 7 のようにスイッチングトランジスタ T 4 のみがオンした状態である。この時ドライブトランジスタ T 5 は飽和領域で動作するように設定されているため、発光素子 E L に流れる電流  $I_{ds}$  はドライブトランジスタ T 5 のゲート / ソース間電圧  $V_{gs}$  に応じて特性式 1 に示される値をとる。

【 0 0 3 3 】

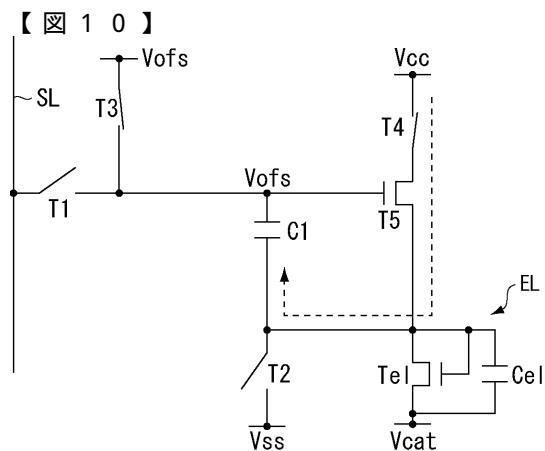

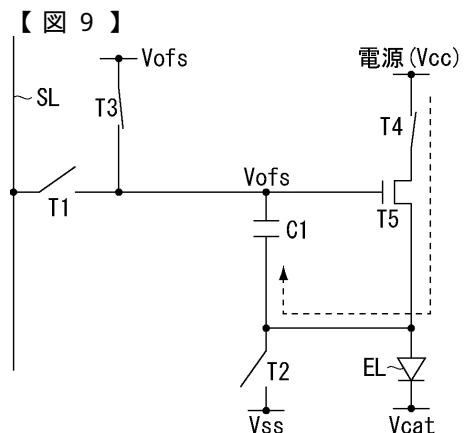

次に非発光期間においてスイッチングトランジスタ T 3 、スイッチングトランジスタ T 2 をオンする。この時、ドライブトランジスタ T 5 のゲート電圧は  $V_{of}$  、ソース電圧は  $V_{ss}$  という値に充電される。ドライブトランジスタ T 5 のゲート / ソース間電圧は  $V_{of} - V_{ss}$  という値をとり、それに応じた電流  $I_{ds'}$  が  $V_{cc}$  から  $V_{ss}$  に流れる。( 図 8 ) ここで、発光素子 E L を非発光とするために、発光素子 E L にかかる電圧  $V_e$  を発光素子 E L の閾電圧  $V_{thel}$  とカソード電圧  $V_{cat}$  の和よりも小さくなるように  $V_{of}$  と  $V_{ss}$  の電圧を設定する必要がある。また、スイッチングトランジスタ T 3 、スイッチングトランジスタ T 2 はどちらが先にオンしてもよい。

【 0 0 3 4 】

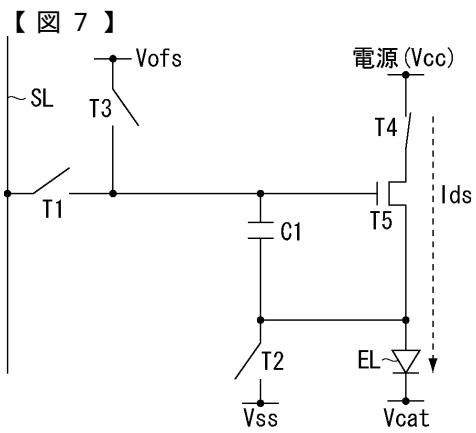

さらにスイッチングトランジスタ T 2 をオフ状態とする( 図 9 )。発光素子 E L の等価

10

20

30

40

50

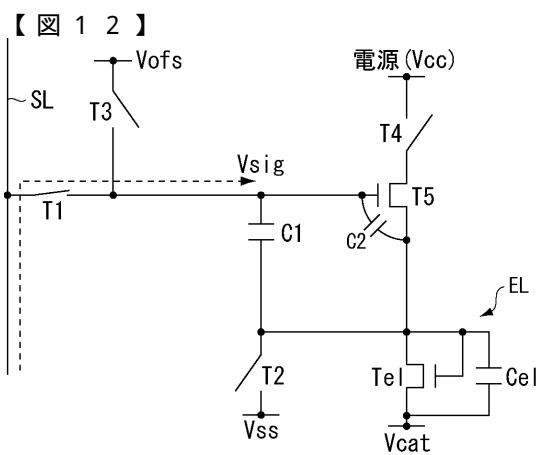

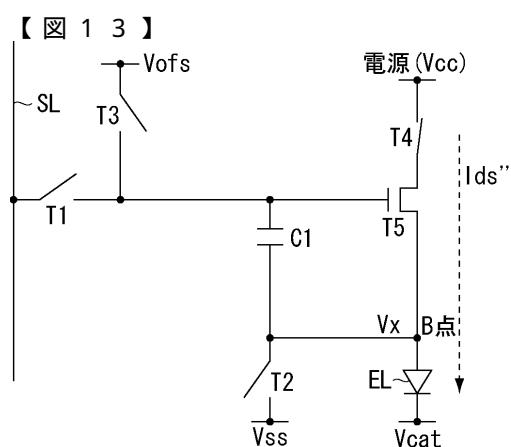

回路は図 10 に示されるようにダイオード T e 1 と容量 C e 1 で表されるため、 V e 1 = V c a t + V t h e 1 (発光素子 E L のリーク電流がドライブトランジスタ T 5 に流れる電流よりもかなり小さい) である限り、ドライブトランジスタ T 5 の電流は画素容量 C 1 と発光素子容量 C e 1 を充電するために使われる。この時発光素子のアノード電圧 V e 1 (即ちドライブトランジスタのソース電圧) は時間と共に図 11 のように上昇して行く。一定時間経過後、ドライブトランジスタ T 5 のゲート / ソース間電圧は V t h という値をとる。この時、 V e 1 = V o f s - V t h = V c a t + V t h e 1 となっている。

### 【 0 0 3 5 】

閾値キャンセル動作終了後スイッチングトランジスタ T 4、スイッチングトランジスタ T 3 をオフする。スイッチングトランジスタ T 4 をスイッチングトランジスタ T 3 よりも先にオフすることでドライブトランジスタ T 5 のゲート電圧の変動を抑えることが可能となる。次に、サンプリングトランジスタ T 1 をオンしてドライブトランジスタ T 5 のゲート電圧を信号電圧 V s i g とする(図 12)。この時、ドライブトランジスタ T 5 のゲート / ソース間電圧は画素容量 C 1 、発光素子 E L の寄生容量 C e 1 、ドライブトランジスタ T 5 の寄生容量 C 2 によって以下の式 2 のように決定される。しかし、発光素子容量 C e 1 は画素容量 C 1 及び寄生容量 C 2 に比べて大きいためにドライブトランジスタ T 5 のゲート / ソース間電圧 V g s はほぼ V s i g + V t h となる。但し簡便のため、 V o f s = 0 とした場合である。

### 【 数 1 】

$$V_{gs} = \frac{C_{el}}{C_{el} + C_1 + C_2} (V_{sig} - V_{ofs}) + V_{th} \quad \text{式 2}$$

### 【 0 0 3 6 】

書き込みが終了した後にスイッチングトランジスタ T 4 をオンしてドライブトランジスタ T 5 のドレイン電圧を電源電圧 V c c まで上昇させる。ドライブトランジスタ T 5 のゲート / ソース間電圧は一定であるのでドライブトランジスタ T 5 は一定電流 I d s ' ' を発光素子 E L に流し、 V e 1 は発光素子 E L に I d s ' ' という電流が流れる電圧 V x まで上昇し、発光素子 E L は発光する(図 13)。

### 【 0 0 3 7 】

本回路においても発光素子 E L は発光時間が長くなるとその I - V 特性は変化してしまう。そのため図中 B 点の電位も変化する。しかしながら、ドライブトランジスタ T 5 のゲート / ソース間電圧は一定値に保たれているので発光素子 E L に流れる電流は変化しない。よって発光素子 E L の I - V 特性が劣化しても、一定電流 I d s が常に流れ続け、発光素子 E L の輝度が変化することはない。

### 【 0 0 3 8 】

以上に説明した参考例の画素回路は、5 個のトランジスタ T 1 ないし T 5 を含んでいる。これらのトランジスタに接続される電源ラインや走査線(ゲートライン)はトランジスタ素子数に応じて増えている。図 5 の参考例にかかる画素回路は、RGB 3 画素当たり電源ラインが V c c 、 V o f s 、 V s s 、 V c a t の 12 本、ゲートラインは W S 、 A Z 、 A Z 2 、 D S の 4 本で構成されている。これでは、画素に対して電源ラインやゲートラインの占める割合が多くなり、パネルの高精細化や高歩留り化という点では難しいものがある。

### 【 0 0 3 9 】

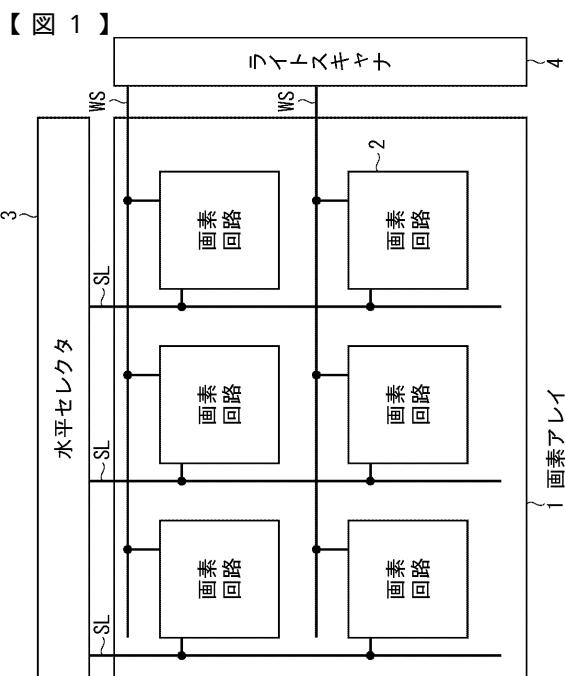

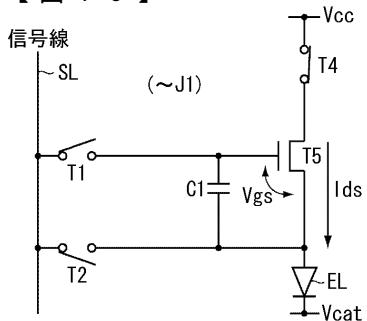

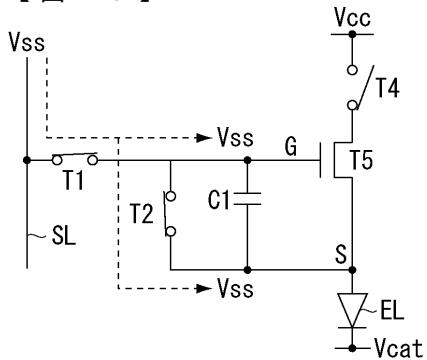

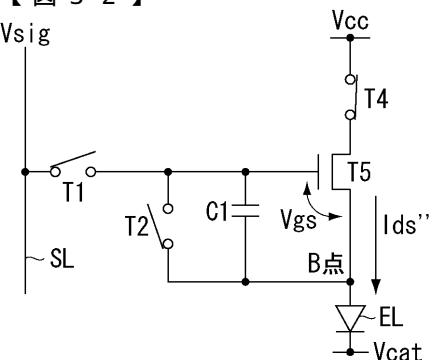

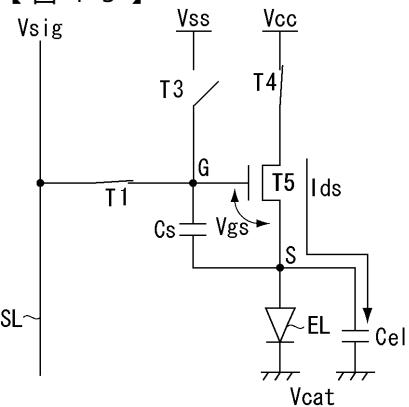

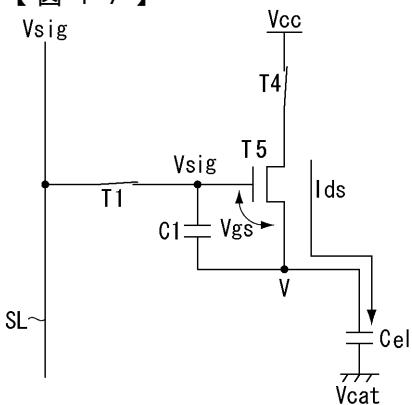

本発明は上記問題点に対処するため、画素回路の簡素化及び合理化を図るものである。図 14 は、本発明にかかる画素回路の第 1 実施形態を示す回路図である。図示する様に、本画素回路 2 は 1 個の発光素子 E L 当り、4 個のトランジスタ T 1 、 T 2 、 T 4 、 T 5 と

10

20

30

40

50

1 個の画素容量 C 1 で構成されており、図 5 に示した参考例に比べトランジスタ 1 個分が簡素化されている。さらに本画素回路 2 の駆動の合理化を図った結果、配線数は R G B 3 画素当たり、3 本のゲートラインと 6 本の電源ラインで構成できる。なお理解を容易にするため、図 14 に示した第 1 実施形態は、図 5 に示した参考例と対応する参照番号を付してある。

【 0 0 4 0 】

図 14 に示すように、本画素回路 2 は、サンプリングトランジスタ T 1 , ドライブトランジスタ T 5 , 画素容量 C 1 , 発光素子 E L に加えて、2 個のスイッチングトランジスタ T 2 , T 4 を含んでいる。全てのトランジスタ T 1 , T 2 , T 4 , T 5 が N チャネル型であり、例えばポリシリコン薄膜トランジスタあるいはアモルファスシリコン薄膜トランジスタでパネルに集積形成できる。

10

【 0 0 4 1 】

スイッチングトランジスタ T 4 は、電源 V c c とドライブトランジスタ T 5 のドレイン D との間に接続されている。スイッチングトランジスタ T 4 のゲートは走査線 D S を介してドライブスキャナ 5 に接続されている。このドライブスキャナ 5 はスイッチングトランジスタ T 4 を線順次でオンオフ制御するために設けてある。もう 1 つのスイッチングトランジスタ T 2 は信号線 S L とドライブトランジスタ T 5 のソース S との間に接続されている。このスイッチングトランジスタ T 2 のゲートは走査線 A Z を介して補正用スキャナ 7 に接続されている。補正用スキャナ 7 はスイッチングトランジスタ T 2 を線順次走査に合わせてオンオフ制御するためにある。画素容量 C 1 はドライブトランジスタ T 5 のゲート G とソース S との間に接続されている。発光素子 E L のアノードはドライブトランジスタ T 5 のソース S に接続し、カソードは所定のカソード電位 V c a t に接続されている。

20

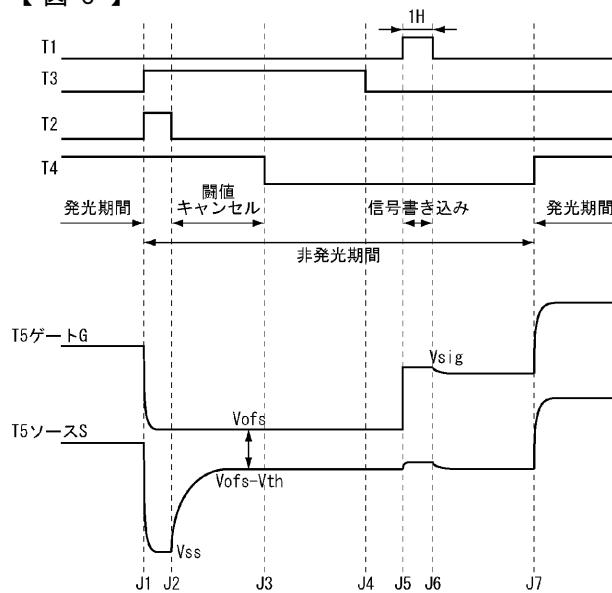

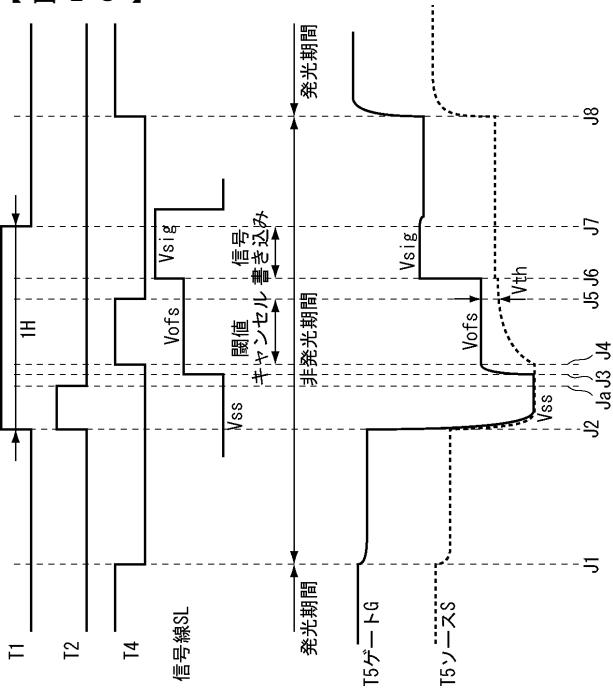

【 0 0 4 2 】

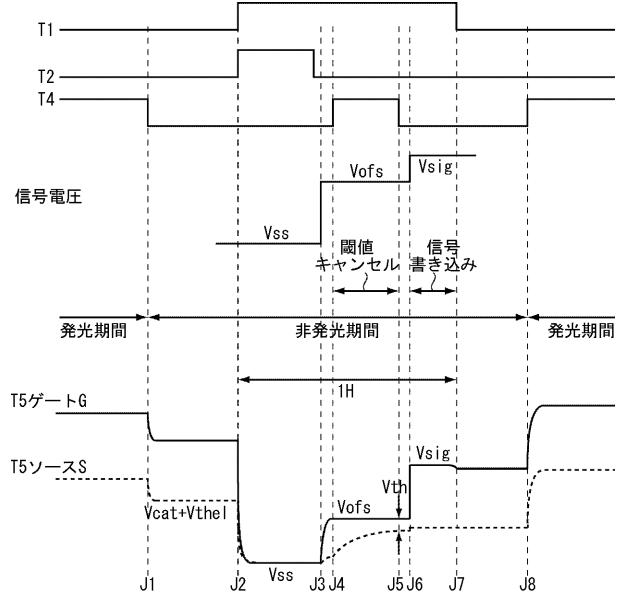

図 15 は、図 14 に示した本発明にかかる画素回路の動作説明に供するタイミングチャートである。このタイミングチャートは、時間軸 J に沿ってサンプリングトランジスタ T 1 , スイッチングトランジスタ T 2 , スイッチングトランジスタ T 4 オンオフ変化を表している。またこれに合わせて、信号線 S L に供給される信号電圧の変化も表してある。図示する様に、信号線は、映像信号を表す信号電圧 V s i g と、第 1 のレベルに固定された第 1 固定電圧 V o f s と、第 2 のレベルに固定された第 2 固定電圧 V s s とを切換えて供給している。加えてこのタイミングチャートは、ドライブトランジスタ T 5 のゲート G とソース S の電位変化も示してある。

30

【 0 0 4 3 】

時点 J 1 まではスイッチングトランジスタ T 4 がオンしている。この為ドライブトランジスタ T 5 は電源 V c c に接続されており、ゲート電圧 V g s に応じたドレイン電流 I d s を発光素子 E L に供給している。よって発光素子 E L は発光期間にある。

【 0 0 4 4 】

時点 J 1 になるとスイッチングトランジスタ T 4 がオフするため、ドレイン電流 I d s が流れなくなり、発光素子 E L は非発光期間に入る。発光素子 E L に電流が流れなくなる為、ドライブトランジスタ T 5 のソース電位は V c a t + V t h e 1 まで下がる。なお V t h e 1 は発光素子 E L の閾電圧である。これと連動してドライブトランジスタ T 5 のゲート電位も低下する。

40

【 0 0 4 5 】

時点 J 2 になるとサンプリングトランジスタ T 1 とスイッチングトランジスタ T 2 が共にオンする。このとき信号電圧は固定電位 V s s にある。ドライブトランジスタ T 5 のソース S が信号線につながることで、ソース電位は V s s まで下がる。またドライブトランジスタ T 5 のゲート G も信号線 S L につながる為、ゲート電位も V s s に下がる。

【 0 0 4 6 】

T 2 がオフした後時点 J 3 で信号電圧が V s s から V o f s に切換る。このときサンプリングトランジスタ T 1 は引き続きオン状態にあるので、ドライブトランジスタ T 5 のゲート電位は V o f s まで上昇する。

50

## 【0047】

この直後時点 J 4 になると、スイッチングトランジスタ T 4 がオンする。これによりドレイン電流  $I_{ds}$  が流れるが、発光素子 E L は逆バイアス状態となっているため、ソース S の電位が上昇する。ゲート G の電位とソース S の電位との差が閾電圧  $V_{th}$  となったところでドレイン電流  $I_{ds}$  は流れなくなる。

## 【0048】

ドライブトランジスタ T 5 がカットオフした後、時点 J 5 でスイッチングトランジスタ T 4 がオフになる。これにより、ドライブトランジスタ T 5 のゲート G とソース S との間に接続された画素容量 C 1 に閾電圧  $V_{th}$  が書き込まれる。この様に閾電圧  $V_{th}$  の検出及び書き込みが行われる時間 J 4 - J 5 を閾値キャンセル期間と呼んでいる。

10

## 【0049】

この後信号電圧は固定電位  $V_{off}$  から信号電位  $V_{sig}$  に変化する。このときサンプリングトランジスタ T 1 は引き続きオン状態にあるので、映像信号電位  $V_{sig}$  が画素容量 C 1 に書き込まれ、ドライブトランジスタ T 5 のゲート G の電位が  $V_{sig}$  となる。信号電位  $V_{sig}$  の書き込みは閾電圧  $V_{th}$  に足し込まれる形となるので、 $V_{gs}$  は  $V_{sig} + V_{th}$  である。時間 J 6 - J 7 を信号書き込み期間と呼んでいる。

## 【0050】

この後時点 J 7 でサンプリングトランジスタ T 1 がオフしさらに時点 T 8 でスイッチングトランジスタ T 4 が再びオンする。これにより出力電流  $I_{ds}$  が発光素子 E L に流れ込み、発光期間に入る。ドレイン電流  $I_{ds}$  が発光素子 E L に流れるとソース S の電位が上昇するが、これと連動してゲート G の電位も上昇する。ドライブトランジスタ T 5 に対する入力電圧  $V_{gs}$  は発光期間中一定に保たれる。

20

## 【0051】

図 15 のタイミングチャートから明らかなように、サンプリングトランジスタ T 1 がオンしている期間 J 2 - J 7 がほぼ 1 水平走査期間 (1H) に相当している。この間に信号電圧は  $V_{ss}$  から  $V_{off}$  に変わりさらに  $V_{sig}$  に変化する。またこの 1 水平走査期間 J 2 - J 7 の間に閾値キャンセル期間 J 4 - J 5 と信号書き込み期間 J 6 - J 7 が含まれる。換言すると、この発明は 1 水平走査期間という短い時間に、閾値キャンセル動作と信号書き込み動作を行っている。

30

## 【0052】

図 16 から図 23 を参照して、図 14 に示した本発明にかかる画素回路の動作を改めて説明する。図 16 は、時点 J 1 前の画素回路 2 の状態を表している。時点 J 1 の前は、スイッチングトランジスタ T 4 のみがオンしている。このときドライブトランジスタ T 5 は飽和領域で動作するように設計されている為、発光素子 E L に流れる電流  $I_{ds}$  は、ドライブトランジスタ T 5 のゲート / ソース間電圧  $V_{gs}$  に応じて、前述の式 1 に表される値を取る。

## 【0053】

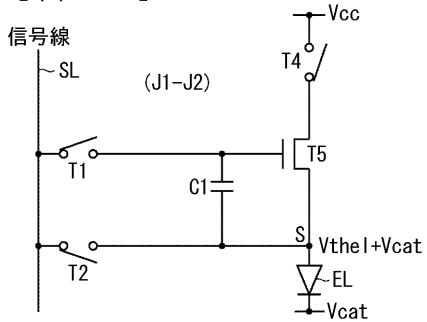

図 17 は、時間 J 1 - J 2 における画素回路 2 の状態を表している。ここではスイッチングトランジスタ T 4 がオフになる。スイッチングトランジスタ T 4 をオフにすることで、電源  $V_{cc}$  から発光素子 E L のカソードに電流が供給されなくなるので、発光素子 E L は消光する。そしてドライブトランジスタ T 5 のソース電圧はカソード電圧  $V_{cat}$  と発光素子 E L の閾電圧  $V_{the1}$  の和、つまり  $V_{cat} + V_{the1}$  という値になる。

40

## 【0054】

図 18 は、時間 J 2 - J 3 における画素回路 2 の状態を表している。ここではサンプリングトランジスタ T 1 とスイッチングトランジスタ T 2 がオンになる。サンプリングトランジスタ T 1 がオンすることでドライブトランジスタ T 5 のゲート G に固定電位  $V_{ss}$  が充電される。またスイッチングトランジスタ T 2 がオンすることで、ドライブトランジスタ T 5 のソース S にも信号線 S L から固定電位  $V_{ss}$  が充電される。ここで  $V_{ss}$  がカソード電圧  $V_{cat}$  と発光素子 E L の閾電圧  $V_{the1}$  の和  $V_{cat} + V_{the1}$  よりも小さく設定されている。つまり  $V_{ss} < V_{the1} + V_{cat}$  という逆バイアス状態にある

50

ので、発光素子 E L は発光する事がない。

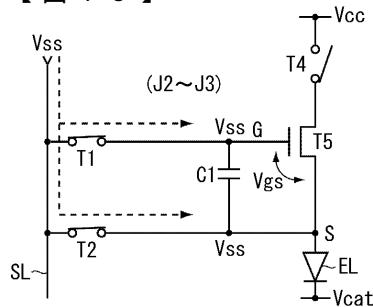

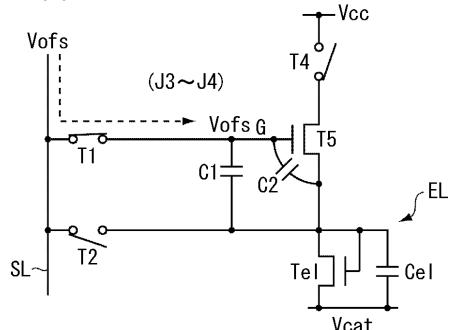

【 0 0 5 5 】

図 19 は、時間 J 3 - J 4 における画素回路 2 の状態を表している。ここではスイッチングトランジスタ T 2 がオフとなり、信号線 S L 上の信号電位が V ss から V o f s に切換る。これによりドライブトランジスタ T 5 のゲート G には V o f s が充電される。発光素子 E L の等価回路はダイオード接続されたトランジスタ T e 1 と容量 C e 1 で表されるため、ドライブトランジスタ T 5 のソース電圧は、画素容量 C 1 、発光素子 E L の寄生容量 C e 1 及びドライブトランジスタ T 5 の寄生容量 C 2 によって、以下の式 3 のように決定される。従って、ゲート / ソース間電圧 V g s は以下のようになる。

【 数 2 】

$$\text{ソース電圧} = \frac{C_1 + C_2}{C_{el} + C_1 + C_2} (V_{ofs} - V_{ss}) + V_{ss} \quad \text{式 3}$$

$$\text{ゲートソース間電圧} = \frac{C_{el}}{C_{el} + C_1 + C_2} (V_{ofs} - V_{ss})$$

【 0 0 5 6 】

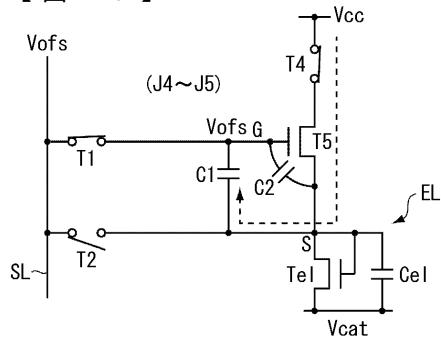

図 20 は、時間 J 4 - J 5 における画素回路 2 の状態を表している。この状態ではスイッチングトランジスタ T 4 をオンして閾電圧キャンセル動作（閾電圧補正動作）を開始する。前述の式 2 で示されるドライブトランジスタ T 5 のゲート / ソース間電圧 V g s が、ドライブトランジスタ T 5 の閾電圧 V t h よりも大きいので、電源 V c c からドライブトランジスタ T 5 を通って図示のように電流が流れ、画素容量 C 1 の充電を開始する。前述したように、発光素子 E L の等価回路はダイオード T e 1 と容量 C e 1 の並列接続で表される。発光素子 E L のアノード電圧 V e 1 が V c a t + V t h e 1 よりも小さい逆バイアス状態である限り、発光素子 E L に流れるリーク電流はほとんど無視可能であり、ドライブトランジスタ T 5 の電流はほぼ全て画素容量 C 1 と発光素子容量 C e 1 を充電するためで使われる。なお発光素子 E L のアノード電圧 V e 1 はドライブトランジスタ T 5 のソース電圧に等しい。この充電により、アノード電圧 V e 1 は時間と共に上昇していく。一定時間経過後、ドライブトランジスタ T 5 のゲート / ソース間電圧は V t h という値を取ってドライブトランジスタ T 5 がカットオフする。このとき、V e 1 = V o f s - V t h < V c a t + V t h e 1 となっている。

【 0 0 5 7 】

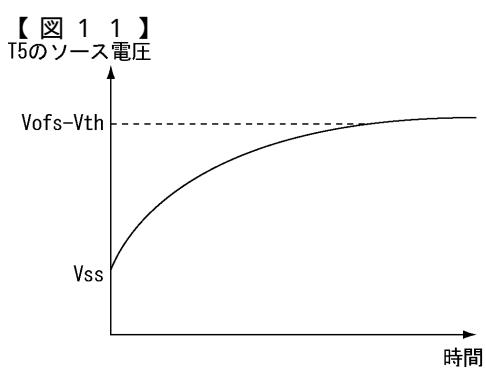

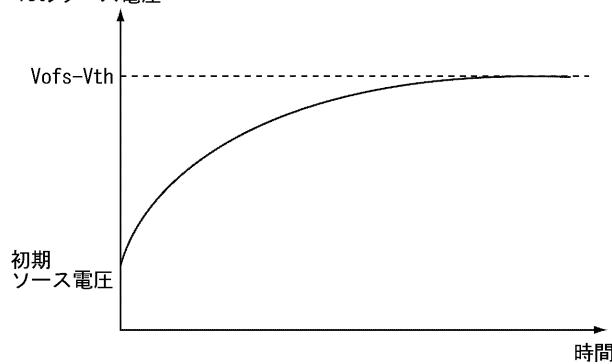

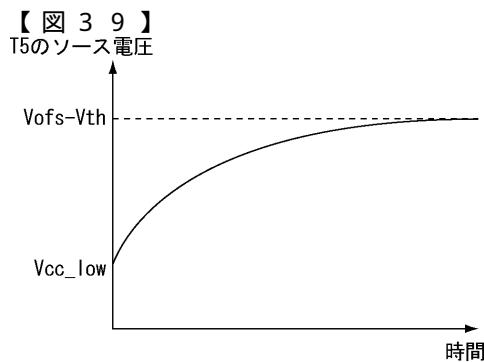

図 21 は、時間と共に上昇するアノード電圧 V e 1 の変化をグラフ化したものである。なおアノード電圧 V e 1 はドライブトランジスタ T 5 のソース電圧となっているので、図 12 のグラフは横軸に時間を取る一方、縦軸はアノード電圧 V e 1 に代えてドライブトランジスタ T 5 のソース電圧を取っている。図示する様にソース電圧は画素容量 C 1 の充電に伴って上昇し、V o f s - V t h となったところで停止する。換言するとドライブトランジスタ T 5 のゲート / ソース間電圧 V g s が丁度閾電圧 V t h となったところでドライブトランジスタ T 5 がカットオフする。この様にしてキャンセル期間 J 4 - J 5 では、ドライブトランジスタ T 5 の閾電圧 V t h の検出及び画素容量 C 1 に対する V t h の書き込みが行われる。

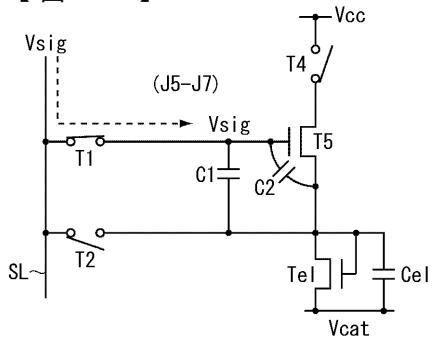

【 0 0 5 8 】

図 22 は、時間 J 5 - J 7 における画素回路 2 の状態を示している。この期間 J 5 - J 7 で映像信号電圧 V s i g の書き込みが行われる。即ち閾電圧キャンセル動作終了後スイッチングトランジスタ T 4 をオフし、信号線 S L 上の電圧を信号電圧 V s i g にして、ドライブトランジスタ T 5 のゲート G に所望の信号電圧 V s i g を書き込む。このとき、ドライブトランジスタ T 5 のゲート / ソース間電圧 V g s は、画素容量 C 1 、発光素子 E L

の寄生容量  $C_{e1}$  及びドライブトランジスタ T 5 の寄生容量  $C_2$  によって前述の式 2 のように決定される。しかし、 $C_{e1}$  は  $C_1$ 、 $C_2$  に比べて大きいため、ゲート / ソース間電圧  $V_{gs}$  はほぼ  $V_{sig} + V_{th}$  となる。

#### 【0059】

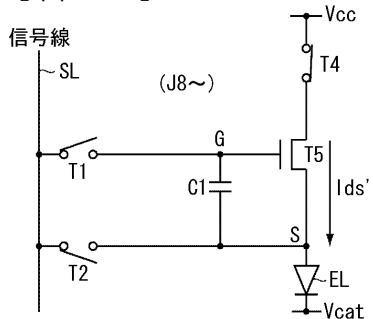

図 23 は、時点 J 8 以降の画素回路 2 の状態を表している。映像信号電位の書き込みが終了した後サンプリングトランジスタ T 1 をオフする一方、スイッチングトランジスタ T 4 をオンして、ドライブトランジスタ T 5 のドレイン電圧を電源電圧  $V_{cc}$  まで上昇させる。ドライブトランジスタ T 5 のゲート / ソース間電圧  $V_{gs}$  は  $V_{sig} + V_{th}$  と一定であるので、ドライブトランジスタ T 5 は一定電流  $I_{ds'}$  を発光素子 E L に流す。これによりアノード電圧  $V_{el}$  は発光素子 E L に  $I_{ds'}$  という電流が流れる電圧  $V_x$  まで上昇し、発光素子 E L が発光する。本参考例にかかる画素回路においても、発光素子 E L は発光時間が長くなるとその I - V 特性は変化してしまう。そのため図 23 中に示すドライブトランジスタ T 5 のソース電位も変化する。しかしながら、ドライブトランジスタ T 5 のゲート / ソース間電圧  $V_{gs}$  は一定に保たれているので、発光素子 E L に流れる電流は変化しない。よって発光素子 E L の I - V 特性が劣化しても、一定電流  $I_{ds}$  が常に流れ続け、発光素子 E L の輝度が変化することはない。またゲート / ソース間電圧  $V_{gs}$  は信号電圧  $V_{sig}$  に予め  $V_{th}$  が足し込まれているので、ドライブトランジスタ T 5 の閾電圧  $V_{th}$  の影響はキャンセルされる。

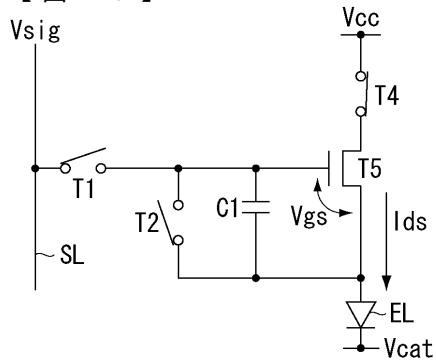

#### 【0060】

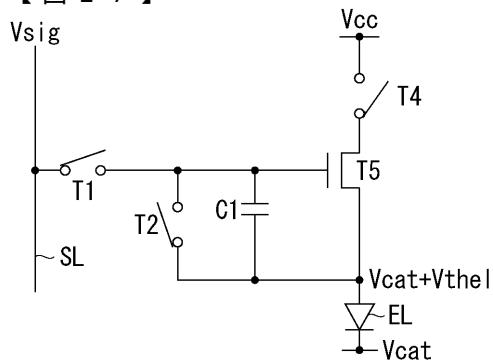

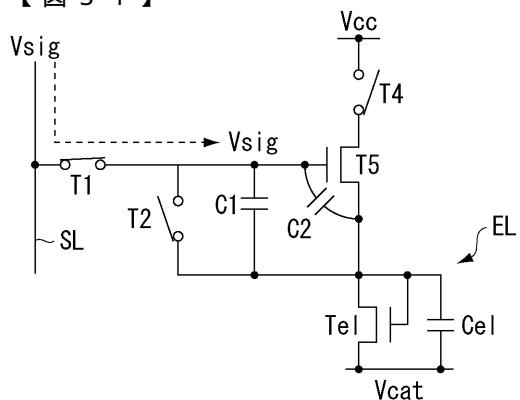

図 24 は、図 14 に示した第 1 実施形態にかかる画素回路の変形例を示す回路図である。理解を容易にするため、図 14 に示した画素回路と対応する部分には対応する参照番号を付してある。異なる点は、スイッチングトランジスタ T 2 の一端が信号線 S L ではなくドライブトランジスタ T 5 のゲート G に接続されていることである。以下、図 24 を参照して本変形例を詳細に説明する。

#### 【0061】

本画素回路 2 は、信号線 S L と所要数の走査線 W S, D S, A Z が交差する部分に配され、発光素子 E L とこれを駆動するドライブトランジスタ T 5 とを含む。ドライブトランジスタ T 5 のゲート G とソース S 間に画素容量  $C_1$  が接続されている。ドライブトランジスタ T 5 のソース S と所定のカソード電位  $V_{cat}$  間に発光素子 E L が接続されている。ドライブトランジスタ T 5 のゲート G と信号線 S L との間にサンプリングトランジスタ T 1 が接続されている。ドライブトランジスタ T 5 のドレイン D と電源  $V_{cc}$  との間にスイッチングトランジスタ T 4 が接続されている。ドライブトランジスタ T 5 のソース S とゲート G との間に別のスイッチングトランジスタ T 2 が接続されている。

#### 【0062】

サンプリングトランジスタ T 1 は、水平走査期間 (1 H) に導通して信号線 S L から供給された映像信号を画素容量  $C_1$  にサンプリングする。画素容量  $C_1$  は、サンプリングされた映像信号に応じてドライブトランジスタ T 5 のゲート G に入力電圧  $V_{sig}$  を印加する。ドライブトランジスタ T 5 は入力電圧  $V_{sig}$  に応じた出力電流  $I_{ds}$  を発光素子 E L に供給する。この出力電流  $I_{ds}$  はドライブトランジスタ T 5 の閾電圧  $V_{th}$  に対して依存性を有する。発光素子 E L はドライブトランジスタ T 5 から供給された出力電流  $I_{ds}$  により映像信号の信号電位  $V_{sig}$  に応じた輝度で発光する。本発明の特徴事項として、2 つのスイッチングトランジスタ T 2, T 4 は、映像信号が画素容量  $C_1$  にサンプリングされる前に動作し、ドライブトランジスタ T 5 の閾電圧  $V_{th}$  を検出して画素容量  $C_1$  に書き込み、以って出力電流  $I_{ds}$  の閾電圧  $V_{th}$  に対する依存性を補正する。

#### 【0063】

本実施形態では信号線 S L は、映像信号を表す信号電圧  $V_{sig}$  と、第 1 のレベルに固定された第 1 固定電圧  $V_{ofs}$  と、第 2 のレベルに固定された第 2 固定電圧  $V_{ss}$  とを切換えて供給する。信号電圧  $V_{sig}$  は映像信号のサンプリング時にドライブトランジスタ T 5 のゲート G に与えられ、第 1 固定電圧  $V_{ofs}$  は閾電圧  $V_{th}$  を補正する時にドライブトランジスタ T 5 のゲート G に与えられ、第 2 固定電圧  $V_{ss}$  は閾電圧  $V_{th}$  を補正す

10

20

30

40

50

る前の準備段階でドライブトランジスタ T 5 のソース S に与えられる。2つのスイッチングトランジスタ T 2 , T 4 は水平走査期間 (1 H) に動作し、ドライブトランジスタ T 5 の閾電圧  $V_{th}$  を検出して画素容量 C 1 に書き込む。

#### 【0064】

図 25 は、図 24 に示した画素回路の動作説明に供するタイミングチャートである。時間軸 J に沿って、トランジスタ T 1 , T 2 , T 4 のオンオフ変化を表している。また信号線 S L に現れる電位変化を表している。加えてドライブトランジスタ T 5 のゲート G 及びソース S の電位変化も表してある。図示する様に、タイミング J 1 までとタイミング J 8 以降が発光期間であり、その間の J 1 - J 8 まで非発光期間となっている。この非発光期間に水平走査期間 (1 H) が含まれ、ここで補正準備動作、閾値キャセル動作及び信号書き込み動作が行われる。タイミング J 1 でスイッチングトランジスタ T 4 がオフし、非発光期間に入る。ドライブトランジスタ T 5 のソース電位はカソード電圧  $V_{cat}$  に発光素子 E L の閾電圧  $V_{the1}$  を足したレベルまで低下する。続いてタイミング J 2 でサンプリングトランジスタ T 1 がオンすると共にスイッチングトランジスタ T 2 もオンする。スイッチングトランジスタ T 2 がオンすることでドライブトランジスタ T 5 のソース電位は  $V_{ss}$  まで低下する。なおこの電位  $V_{ss}$  は信号線 S L から供給される。これにより閾電圧補正準備動作が行われる。タイミング J a でトランジスタ T 2 がオフした後タイミング J 3 で信号線 S L の電位が  $V_{ss}$  から  $V_{ofs}$  に切換る。さらにタイミング J 4 でスイッチングトランジスタ T 4 がオンし、閾値キャセル動作が開始する。スイッチングトランジスタ T 4 のオンに伴い出力電流が流れ出しドライブトランジスタ T 5 のソース電位が丁度  $V_{th}$  に上昇したところでドライブトランジスタ T 5 がカットオフする。その後タイミング J 5 でスイッチングトランジスタ T 4 をオフする。以上のタイミング J 4 からタイミング J 5 までが閾値キャセル期間である。この後タイミング J 6 で信号線 S L の電位が固定電位  $V_{ofs}$  から信号電位  $V_{sig}$  に変化し信号書き込みが行われる。タイミング J 7 でサンプリングトランジスタ T 1 がオフし、この後タイミング J 8 でスイッチングトランジスタ T 4 が再びオンになって発光期間に入る。

#### 【0065】

以下図 26 から図 32 を参照して、図 24 に示した画素回路 24 の動作をさらに詳細に説明する。先ずタイミング J 1 の前の発光期間はスイッチングトランジスタ T 4 のみがオンした状態である (図 26)。

#### 【0066】

次に非発光期間に入ってスイッチングトランジスタ T 4 をオフする。スイッチングトランジスタ T 4 をオフすることで発光素子 E L には電流が流れなくなるため発光素子 E L は消光しそのアノード電圧は  $V_{cat} + V_{the1}$  となる (図 27)。

#### 【0067】

その後サンプリングトランジスタ T 1 及びスイッチングトランジスタ T 2 をオン、信号線電位を  $V_{ss}$  として、ドライブトランジスタ T 5 のゲート G の電圧及びソース S の電圧を  $V_{ss}$  とする (図 28)。ここで  $V_{ss}$  が発光素子 E L の閾電圧  $V_{the1}$  とカソード電圧  $V_{cat}$  の和よりも小さいので、つまり  $V_{ss} < V_{cat} + V_{the1}$  なので、発光素子 E L は発光しない。サンプリングトランジスタ T 1 、スイッチングトランジスタ T 2 のタイミングはどちらが先にオンしてもよい。

#### 【0068】

次にスイッチングトランジスタ T 2 をオフ、信号線電位を  $V_{ofs}$  として、ドライブトランジスタ T 5 のゲート電位に  $V_{ofs}$  という値を充電する (図 29)。この時、ドライブトランジスタ T 5 のゲート / ソース間電圧  $V_{gs}$  は以下の式で示す値となる。

$$V_{gs} = \{ (C_{el} / (C_{el} + C_1 + C_2)) \} \times (V_{ofs} - V_{ss})$$

#### 【0069】

$V_{ofs}$  の書き込みが終了した後スイッチングトランジスタ T 4 をオンし閾値補正動作を開始する (図 30)。スイッチングトランジスタ T 4 がオンとなるので電流は  $V_{cc}$  から画素容量 C 1 、発光素子容量 C e 1 を充電するために流れる。前述の通り一定時間経過

10

20

30

40

50

後ドライブトランジスタT5のソース電圧は $V_{ofs} - V_{th}$ となる。

【0070】

ドライブトランジスタT5のソース電圧が $V_{ofs} - V_{th}$ となった後スイッチングトランジスタT4をオフして閾値補正動作を終了する。その後信号線電位を $V_{sig}$ としてドライブトランジスタT5のゲート電圧を $V_{sig}$ とする(図31)。

【0071】

書き込みが終了した後にサンプリングトランジスタT1をオフ、スイッチングトランジスタT4をオンとして、ドライブトランジスタT5のドレイン電圧を電源電圧 $V_{cc}$ まで上昇させる(図32)。ドライブトランジスタT5のゲート/ソース間電圧 $V_{gs}$ は一定であるのでドライブトランジスタT5は一定電流 $I_{ds'}$ を発光素子ELに流し、発光素子ELのアノード電圧 $V_{el}$ は発光素子ELに $I_{ds'}$ という電流が流れる電圧 $V_x$ まで上昇し、発光素子ELは発光する。

【0072】

本画素回路においても発光素子ELは発光時間が長くなると、そのI-V特性は変化してしまうが、ドライブトランジスタT5のゲート/ソース間電圧 $V_{gs}$ は一定値に保たれているので発光素子ELに流れる電流は変化しない。よって発光素子ELのI-V特性が劣化しても、一定電流 $I_{ds}$ が常に流れ続け、発光素子ELの輝度が変化することはない。

【0073】

本発明により、ドライブトランジスタの閾値バラツキを抑えることができるため、ムラ、ザラツキのない均一な画質を得ることができる。本発明の画素回路は1RGBトリオあたり3本のゲートライン、6本の電源ラインから構成されているため、画素に対して電源及びゲートラインの占める割合を小さくすることができ、高精細化、高歩留まり化が期待できる。本発明により、電源をパルスにする必要がないため外部駆動回路、ドライバの個数を少なくすることができ、低コスト化が実現可能となる。本発明により、ドライブトランジスタのゲート/ソース間電圧は一定値に保たれているので発光素子ELに流れる電流は変化しない。よって発光素子ELのI-V特性が劣化しても、一定電流 $I_{ds}$ が常に流れ続け、発光素子ELの輝度が変化することはない。

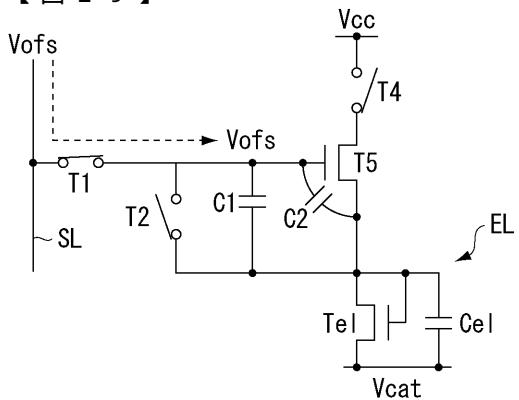

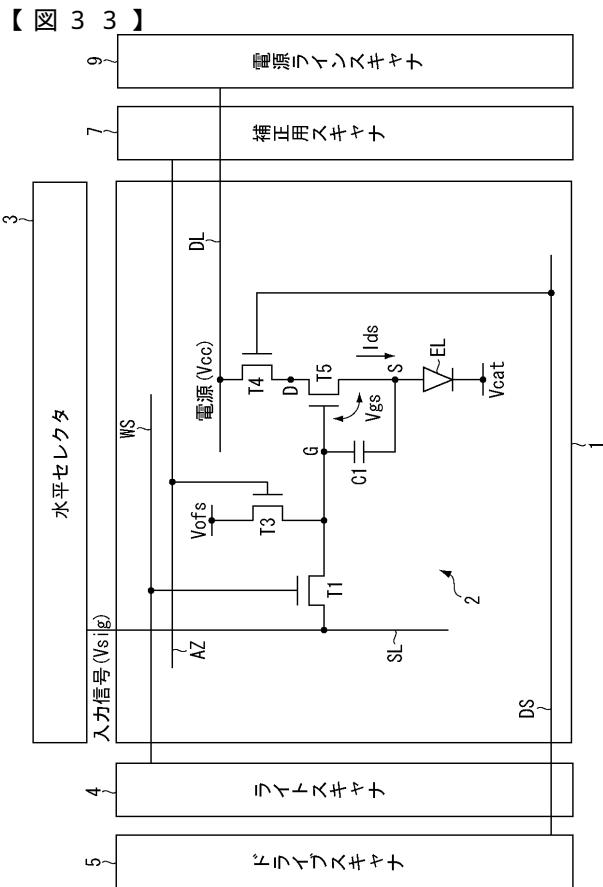

【0074】

図33は、本発明にかかる画素回路の第2実施形態を示す回路図である。本画素回路も1個の発光素子EL当たり、4個のトランジスタT1、T3、T4、T5と1個の画素容量C1とで構成されている。配線数は、RGB3画素当たり4本のゲートライン(走査線)と6本の電源ラインであり、配線の簡素化が図られている。

【0075】

図示する様に本画素回路2は、信号線SLと所要数の走査線WS、DS、AZが交差する部分に配され、発光素子ELとこれを駆動するドライブトランジスタT5とを含む。ドライブトランジスタT5のゲートGとソースS間に画素容量C1が接続されている。ドライブトランジスタT5のソースSと所定のカソード電位 $V_{cat}$ 間に発光素子ELが接続されている。ドライブトランジスタT5のゲートGと信号線SLとの間にサンプリングトランジスタT1が接続されている。ドライブトランジスタT5のドレインDと可変電源( $V_{cc}$ )との間にスイッチングトランジスタT4が接続されている。ドライブトランジスタT5のゲートGと固定電源( $V_{ofs}$ )との間に別のスイッチングトランジスタT3が接続されている。サンプリングトランジスタT1は水平走査期間(1H)に導通して信号線SLから供給された映像信号 $V_{sig}$ を画素容量C1にサンプリングする。画素容量C1は、サンプリングされた映像信号 $V_{sig}$ に応じてドライブトランジスタT5のゲートGに入力電圧 $V_{gs}$ を印加する。ドライブトランジスタT5は入力電圧 $V_{gs}$ に応じた出力電流 $I_{ds}$ を発光素子ELに供給する。この出力電流 $I_{ds}$ はドライブトランジスタT5の閾電圧 $V_{th}$ に対して依存性を有する。発光素子ELはドライブトランジスタT5から供給された出力電流 $I_{ds}$ により映像信号 $V_{sig}$ に応じた輝度で発光する。

【0076】

10

20

30

40

50

本発明の特徴事項として、2つのスイッチングトランジスタT3, T4は、映像信号V<sub>sig</sub>が画素容量C1にサンプリングされる前に動作し、ドライブトランジスタT5の閾電圧V<sub>th</sub>を検出して画素容量C1に書き込み、以って出力電流I<sub>ds</sub>の閾電圧V<sub>th</sub>に対する依存性を補正する。可変電源V<sub>cc</sub>は電源ラインDLから供給されており、高電圧V<sub>cc\_hig</sub>と低電圧V<sub>cc\_low</sub>の2値を取ることでドライブトランジスタT5のゲートGとソースS間の電圧V<sub>gs</sub>をその閾電圧V<sub>th</sub>以上とし、高電圧V<sub>cc\_hig</sub>の印加で閾電圧V<sub>th</sub>の補正を開始し、ドライブトランジスタT5と可変電源V<sub>cc</sub>との間に接続されているスイッチングトランジスタT4のオフで閾電圧V<sub>th</sub>の補正を終了する。なお電源ラインDLは走査タイミングと同期して電源V<sub>cc</sub>を高低に切換えるため、電源ラインスキャナ9に接続されている。この電源ラインスキャナ9はライトスキャナ4、ドライブスキャナ5、補正用スキャナ7と同じくシフトレジスタを内蔵したドライバICである。

10

## 【0077】

2つのスイッチングトランジスタT3, T4は、1水平走査期間(1H)より長い時間幅で動作してドライブトランジスタT5の閾電圧V<sub>th</sub>を画素容量C1に書き込むことができる。また発光素子ELの発光を終了する前に、ドライブトランジスタT5のゲートGと固定電源V<sub>ofs</sub>との間に接続されているスイッチングトランジスタT3をオンし、且つドライブトランジスタT5のドレインDと可変電源V<sub>cc</sub>との間に接続されているスイッチングトランジスタT4をオフすることで、ドライブトランジスタT5に負バイアスをかけている。ドライブトランジスタT5にかける負バイアスは、ドライブトランジスタT5の閾電圧V<sub>th</sub>の変動を抑制する効果がある。固定電源V<sub>ofs</sub>は、その電源電圧が発光素子ELのカソードに印加されるカソード電圧V<sub>cat</sub>と発光素子ELの閾電圧V<sub>the1</sub>の和よりも小さく設定されている。

20

## 【0078】

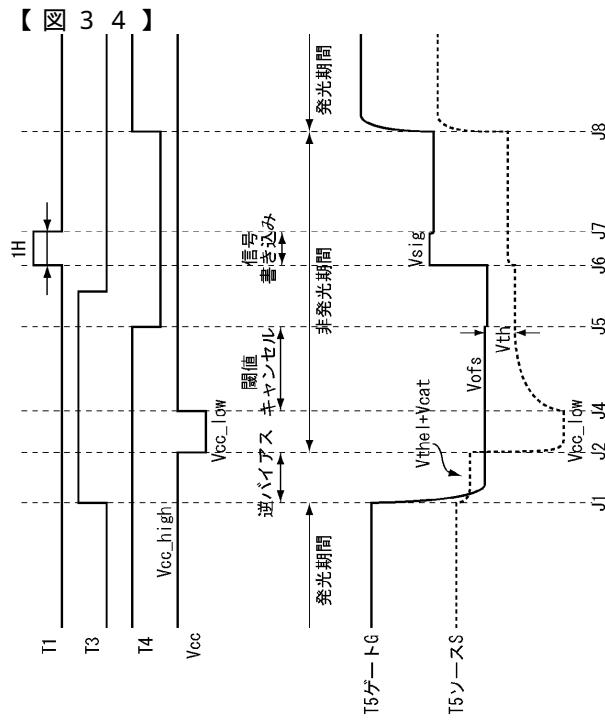

図34は、図33に示した画素回路2の動作説明に供するタイミングチャートである。時間軸Jに沿ってトランジスタT1, T3, T4のオンオフ変化と、可変電源V<sub>cc</sub>の電圧変化と、ドライブトランジスタT5のゲートG及びソースSの電位変化を表してある。タイミングJ1でトランジスタT3がオンしドライブトランジスタT5に逆バイアスがかかる。タイミングJ2-J4で可変電源V<sub>cc</sub>が低レベルV<sub>cc\_low</sub>に切換り、閾電圧補正準備が行われる。次にタイミングJ4-J5で可変電源V<sub>cc</sub>が高レベルV<sub>cc\_hig</sub>に切換り、閾値キャンセル動作が行われる。この後タイミングJ6-J7でサンプリングトランジスタT1がオンし、信号書き込みが行われる。さらにタイミングJ8でスイッチングトランジスタT4がオンし発光期間に入る。

30

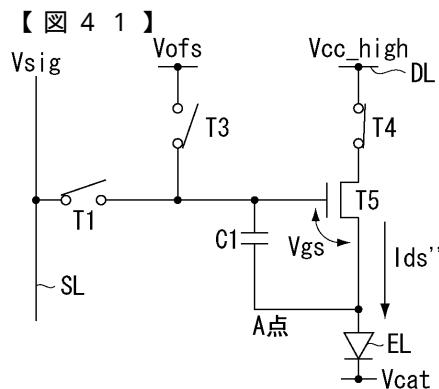

## 【0079】

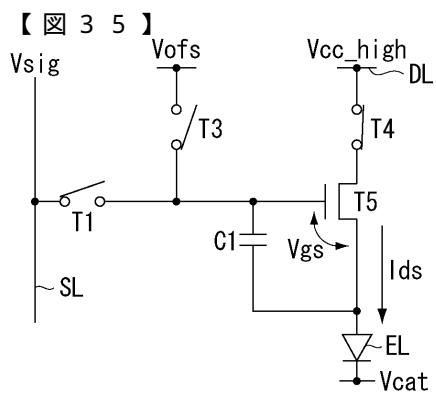

図35ないし図41を参照して、図33に示した画素回路2の動作をさらに詳細に説明する。まずタイミングJ1前では、発光素子ELの発光状態は図35に示すようにスイッチングトランジスタT4のみがオンした状態である。この時ドライブトランジスタT5は飽和領域で動作するように設計されているため、発光素子ELに流れる電流値はドライブトランジスタT5のゲート/ソース間電圧V<sub>gs</sub>に応じて特性式1に表される値をとる。

40

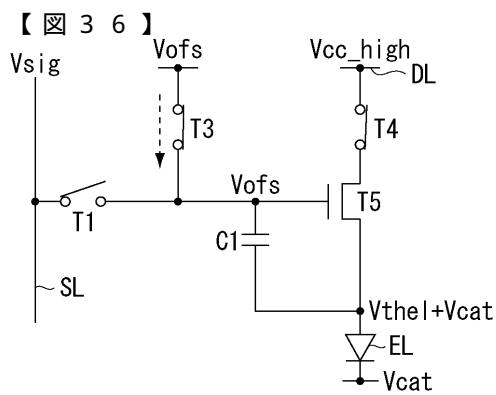

## 【0080】

次に非発光期間においてスイッチングトランジスタT3をオンする。スイッチングトランジスタT3をオンすることでドライブトランジスタT5のゲートはV<sub>ofs</sub>という値をとる。ここで、V<sub>ofs</sub>が発光素子ELの閾値電圧V<sub>the1</sub>とカソード電圧V<sub>cat</sub>とドライブトランジスタT5の閾値V<sub>th</sub>の和よりも小さいので、つまりV<sub>ofs</sub> V<sub>cat</sub> + V<sub>the1</sub> + V<sub>th</sub>なので、発光素子ELに電流は流れず消光する。さらに、V<sub>ofs</sub>がV<sub>the1</sub> + V<sub>cat</sub>よりも小さいので、ドライブトランジスタT5には逆バイアスがかかることとなり、ドライブトランジスタT5の閾値電圧の変動も小さく抑えることができる(図36)。

## 【0081】

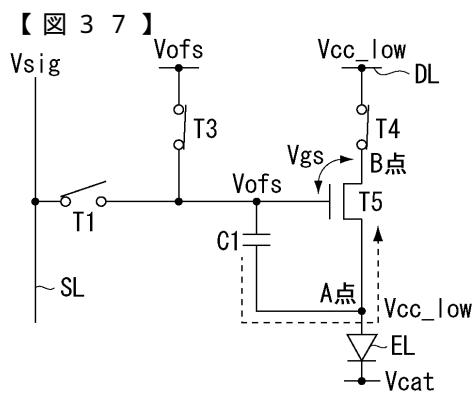

その後、電源電圧V<sub>cc</sub>を低レベル(V<sub>cc\_low</sub>)とする(図37)。この時、V

50

$V_{cc\_low}$  が図中 A 点の電位つまり  $V_{cat} + V_{thel}$  よりも小さく、かつ  $V_{ofs} - V_{cc\_low} > V_{th}$  ので、図中 B 点がドライブトランジスタ T5 のソースとなる。これにより、図中 A 点はドレインとなり、電流は図のように流れる。この動作により A 点の電位は  $V_{cc\_low}$  となる。スイッチングトランジスタ T3 のオンタイミングと電源電圧の切り替えタイミングはどちらが先でもよいが、スイッチングトランジスタ T3 を先にオンさせることで上述のようにドライブトランジスタ T5 に逆バイアスがかかり、高信頼性を実現することが可能である。

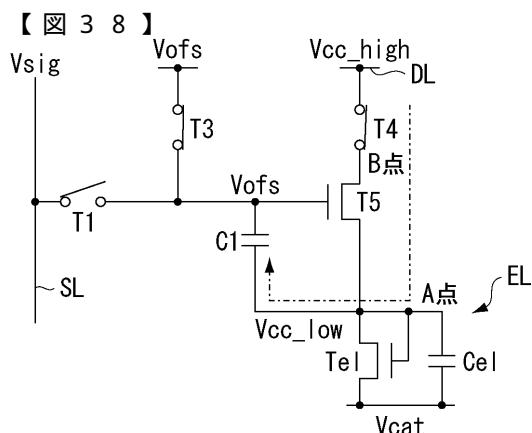

#### 【 0 0 8 2 】

A 点の電位が  $V_{cc\_low}$  となつた後再び電源電圧  $V_{cc}$  を  $V_{cc\_high}$  とする (図 38)。この動作により再び A 点がドライブトランジスタ T5 のソースとなり、ドライブトランジスタ T5 のゲート / ソース間電圧  $V_{gs}$  は  $V_{ofs} - V_{cc\_low}$  となつてドライブトランジスタ T5 の  $V_{th}$  よりも大きくなる。発光素子 EL の等価回路は図 38 に示されるようにダイオード  $T_{el}$  と容量  $C_{el}$  で表されるため、 $V_{el} = V_{cat} + V_{thel}$  (発光素子 EL のリーク電流がドライブトランジスタ T5 に流れる電流よりもかなり小さい) である限り、ドライブトランジスタ T5 の電流は画素容量  $C_1$  と発光素子容量  $C_{el}$  を充電するために使われる。この時発光素子のアノード電圧  $V_{el}$  即ちドライブトランジスタ T5 のソース電圧は時間と共に図 39 のように上昇して行く。一定時間経過後、ドライブトランジスタ T5 のゲート / ソース間電圧  $V_{gs}$  は  $V_{th}$  という値をとる。この時、 $V_{el} = V_{ofs} - V_{th} - V_{cat} - V_{thel}$  とすれば、発光素子 EL は発光することなしに  $V_{th}$  キャンセルの動作が行われる。

10

20

30

40

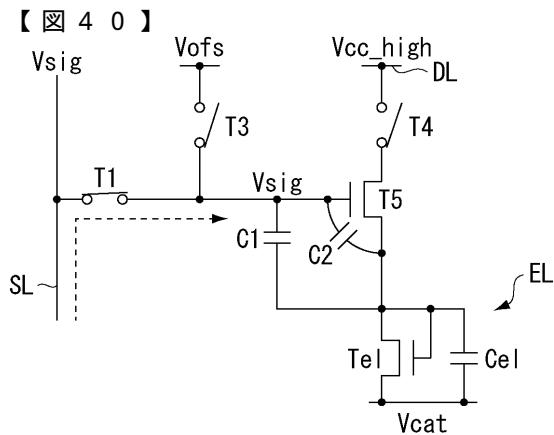

#### 【 0 0 8 3 】

閾値キャンセル動作終了後スイッチングトランジスタ T4 及び T3 をオフする。スイッチングトランジスタ T4 をスイッチングトランジスタ T3 よりも先にオフすることでドライブトランジスタ T5 のゲート電圧の変動を抑えることが可能となる。次に、サンプリングトランジスタ T1 をオンしてドライブトランジスタ T5 のゲート電圧を信号電圧  $V_{sig}$  とする (図 40)。この時、ドライブトランジスタ T5 のゲート / ソース間電圧は画素容量  $C_1$ 、発光素子 EL の寄生容量  $C_{el}$ 、ドライブトランジスタ T5 の寄生容量  $C_2$  によって前述の式 2 のように決定される。しかし、 $C_{el}$  は  $C_1$ 、 $C_2$  に比べて大きいために上記ドライブトランジスタ T5 のゲート / ソース間電圧  $V_{gs}$  はほぼ  $V_{sig} + V_{th}$  となる。

30

#### 【 0 0 8 4 】

信号電圧  $V_{sig}$  の書き込みが終了した後にスイッチングトランジスタ T4 をオンしてドライブトランジスタ T5 のドレイン電圧を電源電圧  $V_{cc\_high}$  まで上昇させる。ドライブトランジスタ T5 のゲート / ソース間電圧  $V_{gs}$  は一定であるのでドライブトランジスタ T5 は一定電流  $I_{ds'}$  を発光素子 EL に流し、 $V_{el}$  は発光素子 EL に  $I_{ds'}$  という電流が流れる電圧  $V_x$  まで上昇し、発光素子 EL は発光する (図 41)。本画素回路においても発光素子 EL は発光時間が長くなるとその I - V 特性は変化してしまう。そのため図中 A 点の電位も変化する。しかしながら、ドライブトランジスタ T5 のゲート / ソース間電圧  $V_{gs}$  は一定値に保たれているので発光素子 EL に流れる電流は変化しない。よって発光素子 EL の I - V 特性が劣化しても、一定電流  $I_{ds}$  が常に流れ続け、発光素子 EL の輝度が変化することはない。また本発明では、電源ラインは二値をもつパルスであるので、ゲートドライバの新規開発が必要なく、既存のものを使用することができるため低コスト化が実現可能となる。

40

#### 【 0 0 8 5 】

本発明により、ドライブトランジスタ T5 の閾値補正期間を 1H 以上と長く取ることができ、黒表示においてもムラのない均一な画質を得ることができる。本発明の画素回路は 1 画素あたり 4 トランジスタと 1 容量、RGB 画素 1 セットあたり 4 本のゲートライン、6 本の電源ラインから構成されているため、画素に対して電源及びゲートラインの占める割合を小さくすることができ、高精細化、高歩留まり化が期待できる。本発明により、ドライブトランジスタ T5 の閾値の変動を小さく抑えることができるため、画素の長寿命化

50

を図ることができる。本発明により、電源ラインは二値をもつパルスであるので、ゲートドライバの新規開発が必要なく、既存のものを使用することができるため低コスト化が実現可能となる。本発明により、ドライブトランジスタT5のゲート/ソース間電圧は一定値に保たれているので発光素子ELに流れる電流は変化しない。よって発光素子ELのI-V特性が劣化しても、一定電流Idsが常に流れ続け、発光素子ELの輝度が変化することはない。

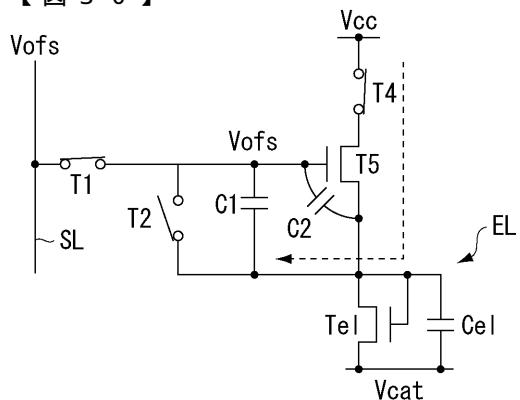

#### 【0086】

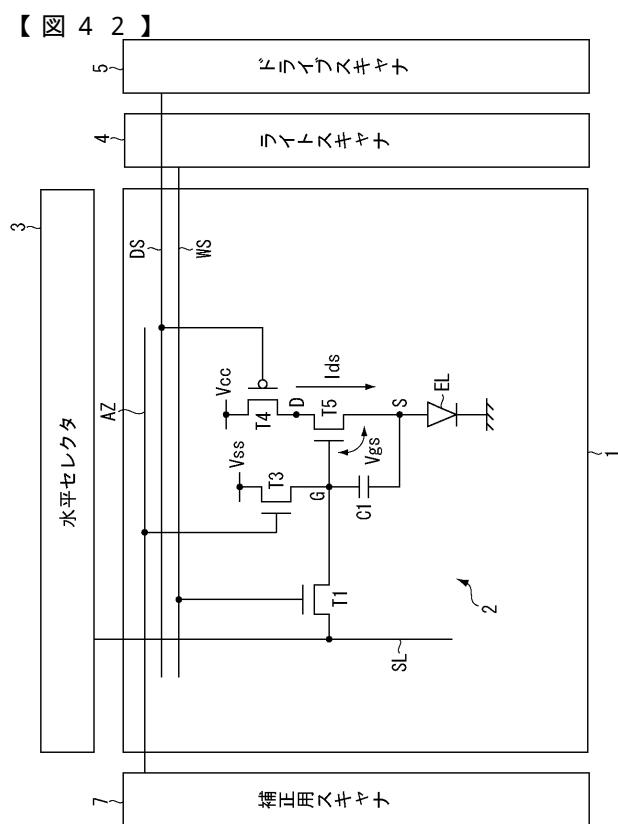

図42は、本発明にかかる画素回路の第3実施形態を示す回路図である。理解を容易にするため、先に説明した第1実施形態及び第2実施形態と対応する部分には対応する参照番号を付してある。本画素回路2も4個のトランジスタと1個の画素容量と1個の発光素子とで構成されている。本実施形態では特にVth補正を行う前に、ドライブトランジスタのゲート電位を一度高電圧にて書き込んだ後、低電圧(閾電圧補正時の電圧)まで下げる。この電圧変化により、ドライブトランジスタのソースSの電位を発光素子ELのカットオフ動作点までカップリングさせることができる。この一連の動作により、閾電圧補正動作の準備を行う。これによりトランジスタを削減することができる。さらに電源ラインやゲートラインの本数も削減することができ、パネルの歩留り改善につながった。

#### 【0087】

図42に示すように、本画素回路2は信号線SLと所要数の走査線WS, DS, AZが交差する部分に配され、発光素子ELとこれを駆動するドライブトランジスタT5とを含む。ドライブトランジスタT5のゲートGとソースS間に画素容量C1が接続され、ドライブトランジスタT5のソースSと所定のカソード電位間に発光素子ELが接続され、ドライブトランジスタT5のゲートGと信号線SLとの間にサンプリングトランジスタT1が接続され、ドライブトランジスタT5のドレインDと固定電源Vccとの間に第1スイッチングトランジスタT4が接続され、ドライブトランジスタT5のゲートGと可変電源Vssとの間に第2スイッチングトランジスタT3が接続されている。サンプリングトランジスタT1は水平走査期間(1H)に導通して信号線SLから供給された映像信号を画素容量C1にサンプリングする。画素容量C1はサンプリングされた映像信号に応じてドライブトランジスタT5のゲートGに入力電圧Vgsを印加する。ドライブトランジスタT5は入力電圧Vgsに応じた出力電流Idsを発光素子ELに供給する。この出力電流IdsはドライブトランジスタT5の閾電圧Vthに対し依存性を有する。発光素子ELはドライブトランジスタT5から供給された出力電流Idsにより映像信号に応じた輝度で発光する。

#### 【0088】

本発明の特徴事項として、第1スイッチングトランジスタT4及び第2スイッチングトランジスタT3は、映像信号が画素容量C1にサンプリングされる前に、ドライブトランジスタT5の閾電圧Vthを検出して画素容量C1に書き込む補正動作を行い、以って出力電流Idsの閾電圧Vthに対する依存性を補正している。その際可変電源Vssは、補正動作の前にその電源電圧を切換え、第2スイッチングトランジスタT3を介してドライブトランジスタT5のゲート電圧を高電圧VSSHから低電圧VSSLに変化させ、この電圧変化をドライブトランジスタT5のソース電圧にカップリングさせることで、補正動作に入る前の準備動作を行う。この準備動作の結果、カップリング後はドライブトランジスタT5のゲートGとソースS間の電圧がドライブトランジスタT5の閾電圧Vthよりも大きくなり、且つドライブトランジスタT5のソース電位が発光素子ELの動作点を下回るように設定される。

#### 【0089】

ドライブトランジスタT5は、その出力電流Idsがチャネル領域の閾電圧Vthに加えキャリア移動度に対しても依存性を有する。第1スイッチングトランジスタT4は出力電流Idsのキャリア移動度μに対する依存性を打ち消すために水平走査期間(1H)の一部で動作し、映像信号がサンプリングされている状態でドライブトランジスタT5から出力電流Idsを取り出し、これを画素容量C1に負帰還して入力電圧Vgsを補正する

10

20

30

40

50

移動度補正動作を行う。この移動度補正動作を正確に行うために、予めドライブトランジスタT5のソース電位が発光素子ELの動作点を下回るように設定される。

#### 【0090】

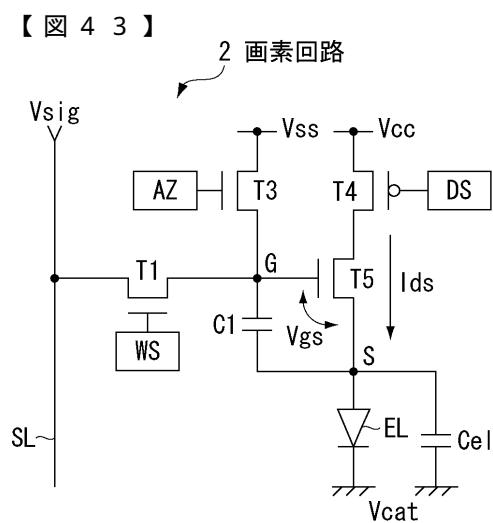

図43は、図42に示した画素アレイ1から画素回路2の部分を取り出した模式図である。理解を容易にするため、サンプリングトランジスタT1によってサンプリングされる映像信号V<sub>sig</sub>や、ドライブトランジスタT5の入力電圧V<sub>gs</sub>及び出力電流I<sub>ds</sub>、さらには発光素子ELが有する容量成分C<sub>e1</sub>などを書き加えてある。また各トランジスタのゲートに接続される走査線WS, DS, AZも書き込んである。図44は、図42及び図43に示した画素回路のタイミングチャートである。図44を参照して図42及び図43に示した画素回路の動作を具体的且つ詳細に説明する。

10

#### 【0091】

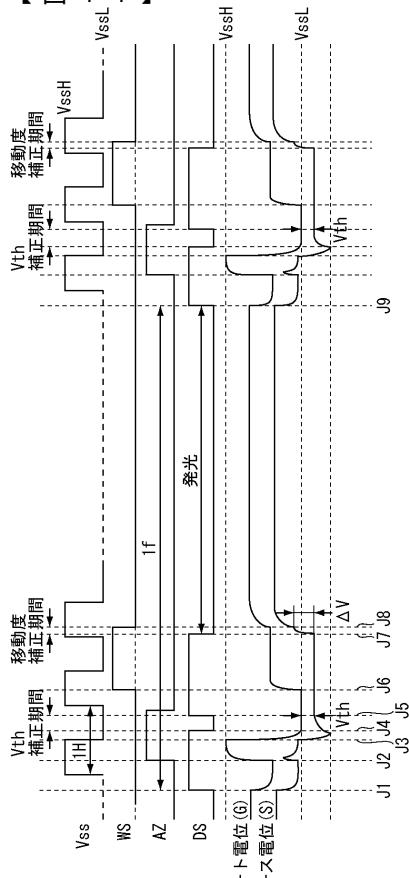

図44は、時間軸Jに沿って各走査線WS, AZ及びDSに印加される制御信号の波形を表してある。表記を簡略化するため、制御信号も対応する走査線の符号と同じ符号で示してある。合わせて可変電源V<sub>ss</sub>の電位変化も時間軸Jに沿って示してある。図示する様にこの可変電源V<sub>ss</sub>は各水平走査期間Hの前半で高電位V<sub>ssH</sub>となり後半で低電位V<sub>ssL</sub>となる。トランジスタT1及びT3はNチャネル型なので走査線WS, AZがそれぞれハイレベルの時オンし、ローレベルの時オフする。一方トランジスタT4はPチャネル型なので走査線DSがハイレベルの時オフし、ローレベルの時オンする。なおこのタイミングチャートは、各制御信号WS, AZ, DSの波形や可変電源V<sub>ss</sub>の波形と共に、ドライブトランジスタT5のゲートGの電位変化及びソースSの電位変化も表してある。

20

#### 【0092】

初めにタイミングJ1で、スイッチングトランジスタT4をオフして非発光とする。この時、ドライブトランジスタT5のソース電位はV<sub>cc</sub>からの電源供給が無いので、発光素子ELのカットオフ電圧V<sub>the1</sub>まで下げられる。次にタイミングJ2で、スイッチングトランジスタT3をオンする。この時、電源ラインV<sub>ss</sub>の電圧は高電圧V<sub>ssH</sub>にしておく。これにより、スイッチングトランジスタT3をオンする事でドライブトランジスタT5のゲート電位はV<sub>ssH</sub>が書き込まれる。この時、画素容量C1を介してソース電位にカップリングが入り、ソース電位は上昇する。ソースSは一度上昇するが、発光素子ELを介して放電されるので、再度ソース電圧はV<sub>the1</sub>になる。この時、ゲート電圧はV<sub>ssH</sub>のままである。

30

#### 【0093】

次に、スイッチングトランジスタT3をオンしたままで、タイミングJ3のときV<sub>ss</sub>ラインの電圧をV<sub>ssL</sub>に変化させる。この電位変化が画素容量C1を介してソース電位にカップリングされる。この時のカップリング量は、C1 / (C1 + C<sub>e1</sub>) × (V<sub>ssH</sub> - V<sub>ssL</sub>)にて求められる。この時、ゲート電位はV<sub>ssL</sub>、ソース電位はV<sub>the1</sub> - C1 / (C1 + C<sub>e1</sub>) × (V<sub>ssH</sub> - V<sub>ssL</sub>)で表される。ここでマイナスバイアスを入れた為に、ソース電圧はV<sub>the1</sub>よりも小さくなり、発光素子ELはカットオフする。ここで、ソース電位は、この後のV<sub>th</sub>補正や移動度補正終了後も発光素子ELがカットオフし続ける電位に設定することが望ましい。また、このV<sub>gs</sub> > V<sub>th</sub>となるようにカップリングを入れることで、V<sub>th</sub>補正の準備を行うことができる。以上により、トランジスタや電源ライン、ゲートラインを削減した画素回路においてもV<sub>th</sub>補正準備を行うことができる。

40

#### 【0094】

この後タイミングJ4で、スイッチングトランジスタT4をオンする事でドライブトランジスタT5に電流が流れて、V<sub>th</sub>補正が行われる。ドライブトランジスタT5がカットオフするまで電流が流れ、カットオフするとドライブトランジスタT5のソース電位はV<sub>ssL</sub> - V<sub>th</sub>となる。ここで、V<sub>ssL</sub> - V<sub>th</sub> < V<sub>the1</sub>とする必要がある。この後タイミングJ5で、スイッチングトランジスタT4をオフし、続いてスイッチングトランジスタT3をオフしてV<sub>th</sub>補正是終了する。

50

## 【0095】

この後、タイミングJ6でサンプリングトランジスタT1をオンし入力電圧Vgsを発光輝度に基づいた電圧に変化させゲートGに書き込む。最後にタイミングJ7でスイッチングトランジスタT4をオンして移動度補正を行った後、タイミングJ8でサンプリングトランジスタT1をオフし、発光期間に入る。なお移動度補正の詳細は後述する。

## 【0096】

以上の様に本発明ではゲート電圧を高電圧から低電圧に可変し、その電圧変化によるカップリングを用いてVth補正準備を行う。これにより、Vth補正用の電源やスイッチングトランジスタ、そのゲートラインを削減する事ができ、パネルの歩留まりを向上する事ができる。また、レイアウトを削減する事で高精細化も可能となる。また本実施形態では、サンプリングトランジスタT1をオンした状態でスイッチングトランジスタT4をオンして移動度補正をかけているが、サンプリングトランジスタT1とスイッチングトランジスタT4をノンオーバーラップにして移動度補正を行わない単純なVth補正動作においても、同様に配線やトランジスタの削減は可能である。本実施形態の画素回路では、スイッチングトランジスタT4以外のトランジスタはNチャネル型であるが、各トランジスタの特性はNチャネルでもPチャネルでも構わない。

## 【0097】

本発明により、閾電圧補正方式や移動度補正方式を採用した有機ELパネルにおいて、ゲート電位を高電圧から低電圧へと変化させ、ドライブトランジスタT5のソース電位にカップリング電圧を入れて発光素子ELをカットオフさせ、 $Vgs > Vth$ とする。これにより、Vth補正の準備を行う。この発明により、電源ラインやトランジスタ、ゲートライン数を削減し、配線クロスオーバーを減少させることで歩留まりを向上させる事ができる。同時にパネルの高精細化も可能となる。

## 【0098】

ここで移動度補正につき詳細に説明する。前述したように移動度 $\mu$ の補正是タイミングJ7～J8で行われる。サンプリング期間の終了するタイミングJ8より前のタイミングJ7で制御信号DSがローレベルとなりスイッチングトランジスタT4がオンする。これによりドライブトランジスタT5が電源Vccに接続されるので、画素回路は非発光期間から発光期間に進む。この様にサンプリングトランジスタT1がまだオン状態で且つスイッチングトランジスタT4がオン状態に入った期間J7～J8で、ドライブトランジスタT5の移動度補正を行う。即ち本実施形態では、サンプリング期間の後部分と発光期間の先頭部分とが重なる期間J7～J8で移動度補正を行っている。なお、この移動度補正を行う発光期間の先頭では、発光素子ELは実際には逆バイアス状態にあるので発光する事はない。この移動度補正期間J7～J8では、ドライブトランジスタT5のゲートGが映像信号Vsigのレベルに固定された状態で、ドライブトランジスタT5にドレイン電流Idsが流れる。ここで $VssL - Vth < Vhe1$ と設定しておく事で、発光素子ELは逆バイアス状態におかれる為、ダイオード特性ではなく単純な容量特性を示すようになる。よってドライブトランジスタT5に流れる電流Idsは画素容量C1と発光素子ELの等価容量Ce1の両者を結合した容量 $C = C1 + Ce1$ に書き込まれていく。これによりドライブトランジスタT5のソース電位(S)は上昇していく。図44のタイミングチャートではこの上昇分をVで表してある。この上昇分Vは結局画素容量C1に保持されたゲート/ソース間電圧Vgsから差し引かれる事になるので、負帰還をかけた事になる。この様にドライブトランジスタT5の出力電流Idsを同じくドライブトランジスタT5の入力電圧Vgsに負帰還する事で、移動度 $\mu$ を補正する事が可能である。なお負帰還量Vは移動度補正期間J7～J8の時間幅tを調整する事で最適化可能である。

## 【0099】

タイミングJ8では制御信号WSがローレベルとなりサンプリングトランジスタT1がオフする。この結果ドライブトランジスタT5のゲートGは信号線SLから切り離される。映像信号Vsigの印加が解除されるので、ドライブトランジスタT5のゲート電位(G)は上昇可能となり、ソース電位(S)と共に上昇していく。その間画素容量C1に保

持されたゲート／ソース間電圧  $V_{g s}$  は ( $V_{sig} - V + V_{th}$ ) の値を維持する。ソース電位 (S) の上昇に伴い、発光素子 EL の逆バイアス状態は解消されるので、出力電流  $I_{ds}$  の流入により発光素子 EL は実際に発光を開始する。この時のドレイン電流  $I_{ds}$  対ゲート電圧  $V_{g s}$  の関係は、先のトランジスタ特性式 1 の  $V_{g s}$  に  $V_{sig} - V + V_{th}$  を代入する事で、以下の式のように与えられる。

$$I_{ds} = k \mu (V_{gs} - V_{th})^2 = k \mu (V_{sig} - V)^2$$

上記式において、 $k = (1/2)(W/L)C_{ox}$  である。この特性式から  $V_{th}$  の項がキャンセルされており、発光素子 EL に供給される出力電流  $I_{ds}$  はドライブトランジスタ T 5 の閾電圧  $V_{th}$  に依存しない事が分かる。基本的にドレイン電流  $I_{ds}$  は映像信号の信号電圧  $V_{sig}$  によって決まる。換言すると、発光素子 EL は映像信号  $V_{sig}$  に応じた輝度で発光する事になる。その際  $V_{sig}$  は帰還量  $V$  で補正されている。この補正量  $V$  は丁度上記特性式の係数部に位置する移動度  $\mu$  の効果を打ち消すように働く。したがって、ドレイン電流  $I_{ds}$  は実質的に映像信号  $V_{sig}$  のみに依存する事になる。

#### 【0100】

図 45 は、移動度補正期間 J 7 - J 8 における画素回路 2 の状態を示す回路図である。図示する様に、移動度補正期間 J 7 - J 8 では、サンプリングトランジスタ T 1 及びスイッチングトランジスタ T 4 がオンしている一方、残りのスイッチングトランジスタ T 3 がオフしている。この状態でドライブトランジスタ T 5 のソース電位は  $V_{ssL} - V_{th}$  である。このソース電位は発光素子 EL のアノード電位でもある。ここで  $V_{ssL} - V_{th} < V_{thel}$  と設定しておくことで、発光素子 EL は逆バイアス状態に置かれ、ダイオード特性ではなく単純な容量特性を示すことになる。よってドライブトランジスタ T 5 に流れる電流  $I_{ds}$  は画素容量  $C_1$  と発光素子 EL の等価容量  $C_{el}$  との合成容量  $C = C_1 + C_{el}$  に流れ込むことになる。換言すると、ドレイン電流  $I_{ds}$  の一部が画素容量  $C_1$  に負帰還され、移動度の補正が行われる。

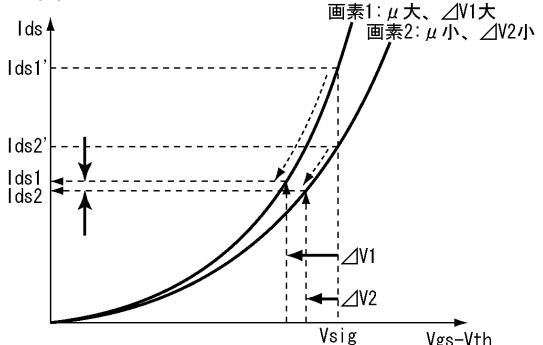

#### 【0101】

図 46 は上述したトランジスタ特性式をグラフ化したものであり、縦軸に  $I_{ds}$  を取り横軸に  $V_{sig}$  を取ってある。このグラフの下方にこの特性式も合わせて示してある。図 46 のグラフは、画素 1 と画素 2 を比較した状態で特性カーブを描いてある。画素 1 のドライブトランジスタの移動度  $\mu$  は相対的に大きい。逆に画素 2 に含まれるドライブトランジスタの移動度  $\mu$  は相対的に小さい。この様にドライブトランジスタをポリシリコン薄膜トランジスタなどで構成した場合、画素間で移動度  $\mu$  がばらつく事は避けられない。例えば両画素 1, 2 に同レベルの映像信号  $V_{sig}$  を書き込んだ場合、何ら移動度の補正を行わないと、移動度  $\mu$  の大きい画素 1 に流れる出力電流  $I_{ds1'}$  は、移動度  $\mu$  の小さい画素 2 に流れる出力電流  $I_{ds2'}$  に比べて大きな差が生じてしまう。この様に移動度  $\mu$  のばらつきに起因して出力電流  $I_{ds}$  の間に大きな差が生じるので、画面のユニフォーミティを損なう事になる。

#### 【0102】

そこで本発明では出力電流を入力電圧側に負帰還させる事で移動度のばらつきをキャンセルしている。トランジスタ特性式から明らかなように、移動度が大きいとドレイン電流  $I_{ds}$  が大きくなる。したがって負帰還量  $V$  は移動度が大きいほど大きくなる。図 46 のグラフに示すように、移動度  $\mu$  の大きな画素 1 の負帰還量  $V_1$  は移動度の小さな画素 2 の負帰還量  $V_2$  に比べて大きい。したがって、移動度  $\mu$  が大きいほど負帰還が大きくかかる事となって、ばらつきを抑制する事が可能である。図示するように、移動度  $\mu$  の大きな画素 1 で  $V_1$  の補正をかけると、出力電流は  $I_{ds1'}$  から  $I_{ds1}$  まで大きく下降する。一方移動度  $\mu$  の小さな画素 2 の補正量  $V_2$  は小さいので、出力電流  $I_{ds2'}$  は  $I_{ds2}$  までそれ程大きく下降しない。結果的に、 $I_{ds1}$  と  $I_{ds2}$  は略等しくなり、移動度のばらつきがキャンセルされる。この移動度のばらつきのキャンセルは黒レベルから白レベルまで  $V_{sig}$  の全範囲で行われるので、画面のユニフォーミティは極めて高くなる。以上をまとめると、移動度の異なる画素 1 と 2 があった場合、移動度の大きい画素 1 の補正量  $V_1$  は移動度の小さい画素 2 の補正量  $V_2$  に対して小さくなる。つまり

10

20

30

40

50

移動度が大きいほど  $V$  が大きく  $I_{ds}$  の減少値は大きくなる。これにより移動度の異なる画素電流値は均一化され、移動度のばらつきを補正する事ができる。

【0103】

以下参考の為図47を参照して、上述した移動度補正の数値解析を行う。図47に示すように、トランジスタT1及びT4がオンした状態で、ドライブトランジスタT5のソース電位を変数Vに取って解析を行う。ドライブトランジスタT5のソース電位(S)をVとすると、ドライブトランジスタT5を流れるドレイン電流  $I_{ds}$  は以下の式4に示す通りである。

【数3】

$$I_{ds} = k\mu(V_{gs} - V_{th})^2 = k\mu(V_{sig} - V - V_{th})^2 \quad \text{式4}$$

10

【0104】

またドレイン電流  $I_{ds}$  と容量  $C$  ( $= C_1 + C_{e1}$ ) の関係により、以下の式5に示す様に  $I_{ds} = dQ/dt = C dV/dt = C dV/dt$  が成り立つ。

【数4】

$$\begin{aligned} I_{ds} &= \frac{dQ}{dt} = C \frac{dV}{dt} \quad \text{より} \quad \int \frac{1}{C} dt = \int \frac{1}{I_{ds}} dV \quad \text{式5} \\ &\Leftrightarrow \int_0^t \frac{1}{C} dt = \int_{-V_{th}}^V \frac{1}{k\mu(V_{sig} - V_{th} - V)^2} dV \\ &\Leftrightarrow \frac{k\mu}{C} t = \left[ \frac{1}{V_{sig} - V_{th} - V} \right]_{-V_{th}}^V = \frac{1}{V_{sig} - V_{th} - V} - \frac{1}{V_{sig}} \\ &\Leftrightarrow V_{sig} - V_{th} - V = \frac{1}{\frac{1}{V_{sig}} + \frac{k\mu}{C} t} = \frac{V_{sig}}{1 + V_{sig} \frac{k\mu}{C} t} \end{aligned}$$

20

【0105】

式5に式4を代入して両辺積分する。ここで、ソース電圧V初期状態は  $-V_{th}$  であり、移動度ばらつき補正時間( J7 J8)をtとする。この微分方程式を解くと、移動度補正時間tに対する画素電流が以下の式6のように与えられる。

【数5】

$$I_{ds} = k\mu \left( \frac{V_{sig}}{1 + V_{sig} \frac{k\mu}{C} t} \right)^2 \quad \text{式6}$$

30

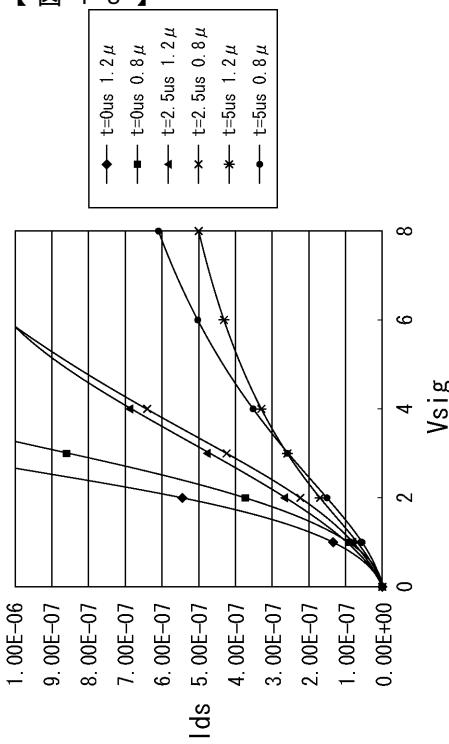

【0106】

図48は、式6をグラフ化した図であり、縦軸に出力電流  $I_{ds}$  を取り、横軸に映像信号  $V_{sig}$  を取ってある。パラメータとして移動度補正期間  $t = 0 \text{ us}$ 、 $2.5 \text{ us}$  及び  $5 \text{ us}$  の場合を設定している。さらに、移動度  $\mu$  もパラメータとして比較的大きい場合  $1.2 \mu$  と比較的小さい場合  $0.8 \mu$  をパラメータにとってある。  $t = 0 \text{ us}$  として実質的に移動度補正をかけない場合に比べ、  $t = 2.5 \text{ us}$  では移動度ばらつきに対する補正が十分にかかっていることがわかる。移動度補正なしでは  $I_{ds}$  に 40% のばらつきがあったものが、移動度補正をかけると 10% 以下に抑えられる。但し  $t = 5 \text{ us}$  として補正期間を長くすると逆に移動度  $\mu$  の違いによる出力電流  $I_{ds}$  のばらつきが大きくなってしまう。この様に、適切な移動度補正を掛けるために、  $t$  は最適な値に設定する必要がある。

40

50

図48に示したグラフの場合、最適値は  $t = 2.5 \text{ u s}$  の近辺である。

【図面の簡単な説明】

【0107】

【図1】アクティブマトリクス型の表示装置の一般的な構成を示すブロック図である。

【図2】図1に示した表示装置に組み込まれる画素回路の従来例を示す回路図である。

【図3】発光素子ELのI-V特性の経時変化を示すグラフである。

【図4】図1に示した表示装置に組み込まれる画素回路の他の従来例を示す回路図である。

【図5】本発明に先立って開発された画素回路の参考例を示す回路図である。

【図6】図5に示した画素回路の動作説明に供するタイミングチャートである。

【図7】参考例にかかる画素回路の動作説明に供する回路図である。

【図8】同じく動作説明に供する回路図である。

【図9】同じく動作説明に供する回路図である。

【図10】同じく動作説明に供する回路図である。

【図11】同じく動作説明に供するグラフである。

【図12】同じく動作説明に供する回路図である。

【図13】同じく動作説明に供する回路図である。

【図14】本発明にかかる画素回路の第1実施形態を示す回路図である。

【図15】第1実施形態の動作説明に供するタイミングチャートである。

【図16】第1実施形態の動作説明に供する回路図である。

【図17】同じく動作説明に供する回路図である。

【図18】同じく動作説明に供する回路図である。

【図19】同じく動作説明に供する回路図である。

【図20】同じく動作説明に供する回路図である。

【図21】同じく動作説明に供するグラフである。

【図22】同じく動作説明に供する回路図である。

【図23】同じく動作説明に供する回路図である。

【図24】本発明にかかる画素回路の第1実施形態の変形例を示す回路図である。

【図25】図24に示した変形例の動作説明に供するタイミングチャートである。

【図26】変形例の動作説明に供する回路図である。

【図27】同じく動作説明に供する回路図である。

【図28】同じく動作説明に供する回路図である。

【図29】同じく動作説明に供する回路図である。

【図30】同じく動作説明に供する回路図である。

【図31】同じく動作説明に供する回路図である。

【図32】同じく動作説明に供する回路図である。

【図33】本発明にかかる画素回路の第2実施形態を示す回路図である。

【図34】第2実施形態の動作説明に供するタイミングチャートである。

【図35】第2実施形態の動作説明に供する回路図である。

【図36】同じく動作説明に供する回路図である。

【図37】同じく動作説明に供する回路図である。

【図38】同じく動作説明に供する回路図である。

【図39】同じく動作説明に供するグラフである。

【図40】同じく動作説明に供する回路図である。

【図41】同じく動作説明に供する回路図である。

【図42】本発明にかかる画素回路の第3実施形態を示す回路図である。

【図43】第3実施形態の動作説明に供する模式図である。

【図44】第3実施形態の動作説明に供するタイミングチャートである。

【図45】第3実施形態の動作説明に供する回路図である。

【図46】同じく動作説明に供するグラフである。

10

20

30

40

50

【図47】同じく動作説明に供する回路図である。

【図48】同じく動作説明に供するグラフである。

【符号の説明】

【0108】

1・・・画素アレイ、2・・・画素回路、3・・・水平セレクタ、4・・・ライトスキャナ、5・・・ドライブスキャナ、7・・・補正用スキャナ、9・・・電源ラインスキャナ、T1・・・サンプリングトランジスタ、T2・・・スイッチングトランジスタ、T3・・・スイッチングトランジスタ、T4・・・スイッチングトランジスタ、T5・・・ドライブトランジスタ、C1・・・画素容量、EL・・・発光素子

【図3】

【 図 4 】

【図5】

〔 四 6 〕

### 【図14】

【 図 1 5 】

【図16】

【図17】

【図18】

【 図 1 9 】

【図20】

【図21】

T5のソース電圧

【図22】

【図23】

【図24】

【図25】

【図26】

【図28】

【図27】

【図29】

【図30】

【図32】

【図31】

【図4-4】

【 図 4 5 】

【図46】

$$I_{ds} = k \mu (V_{gs} - V_{th})^2 = k \mu (V_{sig} - \Delta V)^2$$

【 図 4 7 】

【 図 4 8 】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 4 2 A

G 0 9 G 3/20 6 2 1 J

F ターム(参考) 5C080 AA06 BB05 DD05 DD23 DD28 DD29 EE29 FF11 HH09 JJ02

JJ03 JJ04 JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 画素回路                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP2007148128A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2007-06-14 |

| 申请号            | JP2005344206                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2005-11-29 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| [标]发明人         | 内野勝秀<br>山下淳一<br>山本哲郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 内野 勝秀<br>山下 淳一<br>山本 哲郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09G3/30 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.641.D G09G3/20.611.H G09G3/20.612.E G09G3/20.642.A<br>G09G3/20.621.J G09G3/3233 G09G3/3266 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD23 5C080/DD28 5C080/DD29 5C080/EE29 5C080<br>/FF11 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C380/AA01 5C380/AB06<br>5C380/AB22 5C380/AB23 5C380/AB34 5C380/BA12 5C380/BA13 5C380/BA28 5C380/BA29 5C380<br>/BA37 5C380/BA38 5C380/BA39 5C380/BB02 5C380/BB21 5C380/BD02 5C380/BD08 5C380/BD10<br>5C380/CA12 5C380/CB01 5C380/CB16 5C380/CB20 5C380/CB26 5C380/CB31 5C380/CC02 5C380<br>/CC03 5C380/CC04 5C380/CC26 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC41<br>5C380/CC62 5C380/CC64 5C380/CC65 5C380/CD012 5C380/CD014 5C380/CD015 5C380/CD024<br>5C380/CD025 5C380/CE08 5C380/DA02 5C380/DA06 5C380/DA50 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

### 摘要(译)

要解决的问题：简化和合理化具有抵消驱动晶体管的阈值电压的变化的功能的像素电路。像素电容器C1连接在驱动晶体管T5的栅极G和源极S之间，发光元件EL连接在源极S和阴极电势Vcat之间，以及栅极G和信号线SL之间，采样晶体管T1开关晶体管T 4连接在漏极D和电源Vcc之间，另一个开关晶体管T 2连接在源极S和信号线SL之间。两个开关晶体管T 2和T 4在由像素电容器C 1对视频信号Vsig进行采样之前工作，检测驱动晶体管T 5的阈值电压，将其写入像素电容C 1，从而将其写入输出电流的阈值电压纠正依赖性。.The 14