(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-133284

(P2007-133284A)

(43) 公開日 平成19年5月31日(2007.5.31)

|                  |           |             |

|------------------|-----------|-------------|

| (51) Int.CI.     | F 1       | テーマコード (参考) |

| <b>G09G 3/30</b> | GO9G 3/30 | J 5C080     |

| <b>G09G 3/20</b> | GO9G 3/20 | 612L        |

|                  | GO9G 3/20 | 622B        |

|                  | GO9G 3/20 | 624B        |

|                  | GO9G 3/20 | 611H        |

審査請求 未請求 請求項の数 6 O L (全 22 頁)

|           |                              |            |                                                  |

|-----------|------------------------------|------------|--------------------------------------------------|

| (21) 出願番号 | 特願2005-328336 (P2005-328336) | (71) 出願人   | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号           |

| (22) 出願日  | 平成17年11月14日 (2005.11.14)     | (74) 代理人   | 100092336<br>弁理士 鈴木 晴敏                           |

|           |                              | (72) 発明者   | 内野 勝秀<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内          |

|           |                              | (72) 発明者   | 山下 淳一<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内          |

|           |                              | F ターム (参考) | 5C080 AA06 BB05 DD05 EE29 JJ02<br>JJ03 JJ04 JJ05 |

(54) 【発明の名称】表示装置及びその駆動方法

## (57) 【要約】

【課題】画素数の増加や動作速度の高周波数化に対応可能な閾電圧補正機能を備えた表示装置を提供する。

【解決手段】表示装置は、画素アレイ部1とスキャナ部4, 5と信号部3とを含む。各画素2は、サンプリングトランジスタTr1と、画素容量Csと、ドライブトランジスタTrdと、これに接続する発光素子ELと、ドライブトランジスタTrdを電源に接続するスイッチングトランジスタTr4を含む。ドライブトランジスタTrdは、入力電圧Vgsに応じた出力電流Idsを発光素子ELに供給する。出力電流IdsはドライブトランジスタTrdの閾電圧に対して依存性を有する。スキャナ部4, 5は、当該行の画素2に先行する行に割り当てられた複数の水平走査期間を利用して、ドライブトランジスタTrdの閾電圧をキャンセルする補正量を画素容量Csに充電する動作を時分割的に行う。

【選択図】図5

## 【特許請求の範囲】

## 【請求項 1】

画素アレイ部とスキャナ部と信号部とを含み、

前記画素アレイ部は、行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、

前記信号部は、該信号線に映像信号を供給し、

前記スキャナ部は、走査線に制御信号を供給して順次行ごとに画素を走査し、

各画素は、少なくともサンプリングトランジスタと、これに接続する画素容量と、これに接続するドライブトランジスタと、これに接続する発光素子とを含み、

前記サンプリングトランジスタは、走査線から供給される制御信号に応じ導通して信号線から供給された映像信号の信号電位を該画素容量にサンプリングし、

前記画素容量は、該サンプリングされた映像信号の信号電位に応じて該ドライブトランジスタのゲートに入力電圧を印加し、

前記ドライブトランジスタは、該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタの閾電圧に対して依存性を有し、

前記発光素子は、発光期間中該ドライブトランジスタから供給された出力電流により該映像信号の信号電位に応じた輝度で発光する表示装置であつて、

前記スキャナ部は、水平走査期間内で走査線に制御信号を出力して画素を制御し、該出力電流の該閾電圧に対する依存性を補正するため該画素容量に補正をかける動作と、補正された該画素容量に該映像信号の信号電位をサンプリングする動作とを実行し、

更に前記スキャナ部は、当該行の画素に先行する行に割り当てられた前の水平走査期間を利用して、該画素容量に補正をかける動作を各水平走査期間で時分割的に行うことを行つことを特徴とする表示装置。

## 【請求項 2】

各画素は、該ドライブトランジスタを電源に接続するスイッチングトランジスタを含み、

前記スイッチングトランジスタは、該サンプリングトランジスタに接続した第1の走査線とは別に第2の走査線から供給される制御信号に応じ導通して該発光期間中該ドライブトランジスタを電源に接続し、非発光期間では非導通状態になって該ドライブトランジスタを電源から切り離し、

前記スキャナ部は、水平走査期間に該第1走査線及び第2走査線に夫々制御信号を出力し、該サンプリングトランジスタ及び該スイッチングトランジスタをオンオフ制御して、該出力電流の該閾電圧に対する依存性を補正するため該画素容量に補正をかける動作として、該画素容量をリセットする準備動作とリセットされた該画素容量に該閾電圧をキャンセルするための電圧を書き込む補正動作とを行い、その後補正された該画素容量に該映像信号の信号電位をサンプリングするサンプリング動作を実行し、

更に前記スキャナ部は、当該行の画素に先行する行に割り当てられた前の水平走査期間を利用して、該準備動作と該補正動作の両方若しくは片方を各水平走査期間で時分割的に行ふことを特徴とする請求項1記載の表示装置。

## 【請求項 3】

前記信号部は、各水平走査期間に該映像信号を第1の固定電位と、第2の固定電位と、信号電位との間で切り替え、以って該準備動作、該補正動作及び該サンプリング動作に必要な電位を各画素に信号線を介して供給することを特徴とする請求項2記載の表示装置。

## 【請求項 4】

前記信号部は、該準備動作に合わせて高レベルの第1固定電位を供給し、該補正動作に合わせて低レベルの第2固定電位を供給し、該サンプリング動作に合わせて該信号電位を供給することを特徴とする請求項3記載の表示装置。

## 【請求項 5】

前記ドライブトランジスタは、その出力電流が閾電圧に加えチャネル領域のキャリア移動度に対しても依存性を有し、

10

20

30

40

50

前記スキャナ部は、水平走査期間に該第2走査線に制御信号を出力して更に該スイッチングトランジスタを制御し、該出力電流のキャリア移動度に対する依存性を打ち消すために、該信号電位がサンプリングされている状態で該ドライブトランジスタから出力電流を取り出し、これを該画素容量に負帰還して該入力電圧を補正する動作を実行することを特徴とする請求項2記載の表示装置。

#### 【請求項6】

画素アレイ部とスキャナ部と信号部とを含み、前記画素アレイ部は、行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、前記信号部は、該信号線に映像信号を供給し、前記スキャナ部は、走査線に制御信号を供給して順次行ごとに画素を走査し、各画素は、少なくともサンプリングトランジスタと、これに接続する画素容量と、これに接続するドライブトランジスタと、これに接続する発光素子とを含む表示装置の駆動方法であって、

前記サンプリングトランジスタが、走査線から供給される制御信号に応じ導通して信号線から供給された映像信号の信号電位を該画素容量にサンプリングし、

前記画素容量が、該サンプリングされた映像信号の信号電位に応じて該ドライブトランジスタのゲートに入力電圧を印加し、

前記ドライブトランジスタが、該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタの閾電圧に対して依存性を有し、

前記発光素子が、発光期間中該ドライブトランジスタから供給された出力電流により該映像信号の信号電位に応じた輝度で発光し、

前記スキャナ部が、水平走査期間内で走査線に制御信号を出力して画素を制御し、該出力電流の該閾電圧に対する依存性を補正するため該画素容量に補正をかける動作と、補正された該画素容量に該映像信号の信号電位をサンプリングする動作とを実行し、

更に前記スキャナ部が、当該行の画素に先行する行に割り当てられた前の水平走査期間を利用して、該画素容量に補正をかける動作を各水平走査期間で時分割的に行うことを行つことを特徴とする表示装置の駆動方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、画素毎に配した発光素子で画像を表示するフラットパネル型の表示装置に関する。より詳しくは、各画素内に設けた絶縁ゲート型電界効果トランジスタによって有機ELなどの発光素子に通電する電流量を制御する、いわゆるアクティブマトリクス型の表示装置及びその駆動方法に関する。

##### 【背景技術】

##### 【0002】

画像表示装置、例えば液晶ディスプレイなどでは、多数の液晶画素をマトリクス状に並べ、表示すべき画像情報に応じて画素毎に入射光の透過強度又は反射強度を制御することによって画像を表示する。これは、有機EL素子を画素に用いた有機ELディスプレイなどにおいても同様であるが、液晶画素と異なり有機EL素子は自発光素子である。その為、有機ELディスプレイは液晶ディスプレイに比べて画像の視認性が高く、バックライトが不要であり、応答速度が高いなどの利点を有する。又、各発光素子の輝度レベル（階調）はそれに流れる電流値によって制御可能であり、いわゆる電流制御型であるという点で液晶ディスプレイなどの電圧制御型とは大きく異なる。

##### 【0003】

有機ELディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として単純マトリクス方式とアクティブマトリクス方式とがある。前者は構造が単純であるものの、大型且つ高精細のディスプレイの実現が難しいなどの問題がある為、現在はアクティブマトリクス方式の開発が盛んに行なわれている。この方式は、各画素回路内部の発光素子に流れる電流を、画素回路内部に設けた能動素子（一般には薄膜トランジスタ、TFT）によって制御するものであり、以下の特許文献に記載がある。

10

20

30

40

50

【特許文献1】特開2003-255856

【特許文献2】特開2003-271095

【特許文献3】特開2004-133240

【特許文献4】特開2004-029791

【特許文献5】特開2004-093682

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0004】

従来の画素回路は、制御信号を供給する行状の走査線と映像信号を供給する列状の信号線とが交差する部分に配され、少なくともサンプリングトランジスタと容量部とドライブトランジスタと発光素子とを含む。サンプリングトランジスタは、走査線から供給される制御信号に応じ導通して信号線から供給された映像信号をサンプリングする。容量部は、サンプリングされた映像信号に応じた入力電圧を保持する。ドライブトランジスタは、容量部に保持された入力電圧に応じて所定の発光期間に出力電流を供給する。尚一般に、出力電流はドライブトランジスタのチャネル領域のキャリア移動度及び閾電圧に対して依存性を有する。発光素子は、ドライブトランジスタから供給された出力電流により映像信号に応じた輝度で発光する。

## 【0005】

ドライブトランジスタは、容量部に保持された入力電圧をゲートに受けてソース／ドレイン間に出力電流を流し、発光素子に通電する。一般に発光素子の発光輝度は通電量に比例している。更にドライブトランジスタの出力電流供給量はゲート電圧すなわち容量部に書き込まれた入力電圧によって制御される。従来の画素回路は、ドライブトランジスタのゲートに印加される入力電圧を入力映像信号に応じて変化させることで、発光素子に供給する電流量を制御している。

## 【0006】

ここでドライブトランジスタの動作特性は以下の式1で表わされる。

$$I_{ds} = (1/2) \mu (W/L) C_o x (V_{gs} - V_{th})^2 \dots \text{式1}$$

このトランジスタ特性式1において、 $I_{ds}$ はソース／ドレイン間に流れるドレン電流を表わしており、画素回路では発光素子に供給される出力電流である。 $V_{gs}$ はソースを基準としてゲートに印加されるゲート電圧を表わしており、画素回路では上述した入力電圧である。 $V_{th}$ はトランジスタの閾電圧である。又 $\mu$ はトランジスタのチャネルを構成する半導体薄膜の移動度を表わしている。その他 $W$ はチャネル幅を表わし、 $L$ はチャネル長を表わし、 $C_o x$ はゲート容量を表わしている。このトランジスタ特性式1から明らかな様に、薄膜トランジスタは飽和領域で動作する時、ゲート電圧 $V_{gs}$ が閾電圧 $V_{th}$ を超えて大きくなると、オン状態となってドレン電流 $I_{ds}$ が流れる。原理的に見ると上記のトランジスタ特性式1が示す様に、ゲート電圧 $V_{gs}$ が一定であれば常に同じ量のドレン電流 $I_{ds}$ が発光素子に供給される。従って、画面を構成する各画素に全て同一のレベルの映像信号を供給すれば、全画素が同一輝度で発光し、画面の一様性（ユニフォーミティ）が得られるはずである。

## 【0007】

しかしながら実際には、ポリシリコンなどの半導体薄膜で構成された薄膜トランジスタ（TFT）は、個々のデバイス特性にばらつきがある。特に、閾電圧 $V_{th}$ は一定ではなく、各画素毎にばらつきがある。前述のトランジスタ特性式1から明らかな様に、各ドライブトランジスタの閾電圧 $V_{th}$ がばらつくと、ゲート電圧 $V_{gs}$ が一定であっても、ドレン電流 $I_{ds}$ にばらつきが生じ、画素毎に輝度がばらついてしまう為、画面のユニフォーミティを損なう。従来からドライブトランジスタの閾電圧のばらつきをキャンセルする機能を組み込んだ画素回路が開発されており、例えば前記の特許文献3に開示がある。

## 【0008】

閾電圧のばらつきをキャンセルする機能（閾電圧補正機能）を組み込んだ画素回路は、一般に画素容量に映像信号をサンプリングする前に動作し、閾電圧 $V_{th}$ に相当する電圧

10

20

30

40

50

を画素容量に書き込んで、閾電圧  $V_{th}$  をキャンセルするようにしている。このため閾電圧補正動作は、画素容量を閾電圧に相当する電圧に充電するために、ある程度時間を要する。しかしながら、画素の高精細化やその結果としての画素数の増加に伴い、更にはパネルの動作速度の高周波数化により、各画素に割り当てられる閾電圧補正時間が短くなってしまっており、必ずしも十分な閾電圧補正機能を果たすことが出来ない。

【課題を解決するための手段】

【0009】

上述した従来の技術の課題に鑑み、本発明は画素数の増加や動作速度の高周波数化に対応可能な閾電圧補正機能を備えた表示装置及びその駆動方法を提供することを目的とする。かかる目的を達成するために以下の手段を講じた。即ち本発明は、画素アレイ部とスキヤナ部と信号部とを含み、前記画素アレイ部は、行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、前記信号部は、該信号線に映像信号を供給し、前記スキヤナ部は、走査線に制御信号を供給して順次行ごとに画素を走査し、各画素は、少なくともサンプリングトランジスタと、これに接続する画素容量と、これに接続するドライブトランジスタと、これに接続する発光素子とを含み、前記サンプリングトランジスタは、走査線から供給される制御信号に応じ導通して信号線から供給された映像信号の信号電位を該画素容量にサンプリングし、前記画素容量は、該サンプリングされた映像信号の信号電位に応じて該ドライブトランジスタのゲートに入力電圧を印加し、前記ドライブトランジスタは、該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタの閾電圧に対して依存性を有し、前記発光素子は、発光期間中該ドライブトランジスタから供給された出力電流により該映像信号の信号電位に応じた輝度で発光する表示装置であつて、前記スキヤナ部は、水平走査期間内で走査線に制御信号を出力して画素を制御し、該出力電流の該閾電圧に対する依存性を補正するため該画素容量に補正をかける動作と、補正された該画素容量に該映像信号の信号電位をサンプリングする動作とを実行し、更に前記スキヤナ部は、当該行の画素に先行する行に割り当てられた前の水平走査期間を利用して、該画素容量に補正をかける動作を各水平走査期間で時分割的に行うことの特徴とする。

【0010】

具体的に各画素は、該ドライブトランジスタを電源に接続するスイッチングトランジスタを含み、前記スイッチングトランジスタは、該サンプリングトランジスタに接続した第1の走査線とは別に第2の走査線から供給される制御信号に応じ導通して該発光期間中該ドライブトランジスタを電源に接続し、非発光期間では非導通状態になって該ドライブトランジスタを電源から切り離し、前記スキヤナ部は、水平走査期間に該第1走査線及び第2走査線に夫々制御信号を出力し、該サンプリングトランジスタ及び該スイッチングトランジスタをオンオフ制御して、該出力電流の該閾電圧に対する依存性を補正するため該画素容量に補正をかける動作として、該画素容量をリセットする準備動作とリセットされた該画素容量に該閾電圧をキャンセルするための電圧を書き込む補正動作とを行い、その後補正された該画素容量に該映像信号の信号電位をサンプリングするサンプリング動作を実行し、更に前記スキヤナ部は、当該行の画素に先行する行に割り当てられた前の水平走査期間を利用して、該準備動作と該補正動作の両方若しくは片方を各水平走査期間で時分割的に行う。この場合前記信号部は、各水平走査期間に該映像信号を第1の固定電位と、第2の固定電位と、信号電位との間で切り替え、以って該準備動作、該補正動作及び該サンプリング動作に必要な電位を各画素に信号線を介して供給する。又前記信号部は、該準備動作に合わせて高レベルの第1固定電位を供給し、該補正動作に合わせて低レベルの第2固定電位を供給し、該サンプリング動作に合わせて該信号電位を供給する。又前記ドライブトランジスタは、その出力電流が閾電圧に加えチャネル領域のキャリア移動度に対しても依存性を有し、前記スキヤナ部は、水平走査期間に該第2走査線に制御信号を出力して更に該スイッチングトランジスタを制御し、該出力電流のキャリア移動度に対する依存性を打ち消すために、該信号電位がサンプリングされている状態で該ドライブトランジスタから出力電流を取り出し、これを該画素容量に負帰還して該入力電圧を補正する動作を

10

20

30

40

50

実行する。

#### 【0011】

本発明は又、画素アレイ部とスキャナ部と信号部とを含み、前記画素アレイ部は、行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、前記信号部は、該信号線に映像信号を供給し、前記スキャナ部は、走査線に制御信号を供給して順次行ごとに画素を走査し、各画素は、少なくともサンプリングトランジスタと、これに接続する画素容量と、これに接続するドライブトランジスタと、これに接続する発光素子とを含む表示装置の駆動方法であって、前記サンプリングトランジスタが、走査線から供給される制御信号に応じ導通して信号線から供給された映像信号の信号電位を該画素容量にサンプリングし、前記画素容量が、該サンプリングされた映像信号の信号電位に応じて該ドライブトランジスタのゲートに入力電圧を印加し、前記ドライブトランジスタが、該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタの閾電圧に対して依存性を有し、前記発光素子が、発光期間中該ドライブトランジスタから供給された出力電流により該映像信号の信号電位に応じた輝度で発光し、前記スキャナ部が、水平走査期間内で走査線に制御信号を出力して画素を制御し、該出力電流の該閾電圧に対する依存性を補正するため該画素容量に補正をかける動作と、補正された該画素容量に該映像信号の信号電位をサンプリングする動作とを実行し、更に前記スキャナ部が、当該行の画素に先行する行に割り当てられた前の水平走査期間を利用して、該画素容量に補正をかける動作を各水平走査期間で時分割的に行うこととする。10

#### 【発明の効果】

#### 【0012】

本発明によれば、表示装置のスキャナ部は、水平走査期間内で走査線に制御信号を出力して画素を制御し、出力電流の閾電圧に対する依存性を補正するため画素容量に補正をかける動作と、補正された画素容量に映像信号の信号電位をサンプリングする動作とを実行している。その際スキャナ部は、当該行の画素に先行する行に割り当てられた前の水平走査期間を利用して、画素容量に補正をかける動作を時分割的に行っている。閾電圧補正動作を複数の水平走査期間に分割することで、トータルの補正時間を確保している。各水平走査期間で時分割的に行われた補正動作を蓄積して、最終的に当該水平走査期間で映像信号をサンプリングする際には、十分閾電圧に相当する電圧を画素容量に書き込んでおくことが出来る。このため、表示装置の駆動周波数が高周波数化して水平走査期間が短縮化されても、十分に閾電圧補正動作を行うことが可能になる。20

#### 【0013】

また本発明によれば、水平走査期間内で、閾電圧キャンセルのための準備動作と実際の補正動作を行い、さらに信号電位のサンプリング動作を行っている。この様に水平走査期間内で必要な動作を行うことで、信号線から画素に必要な制御電圧や信号電圧を供給することが出来るため、画素回路を構成する素子数は少なくてすむ。ちなみに本発明の画素回路は、3個のトランジスタと1個の画素容量と1個の発光素子で構成でき、従来の閾電圧補正機能付の画素回路に比べ、大幅に素子数を削減可能である。但し水平走査期間内で補正動作とサンプリング動作を行うため、高駆動周波数化に伴い水平走査期間が短くなると、必要な動作時間を確保できない。そこで本発明では、補正動作を複数の水平走査期間で時分割的に行い、その結果を蓄積することで、実質的に十分な動作時間を確保するようしている。30

#### 【発明を実施するための最良の形態】

#### 【0014】

以下図面を参照して本発明の実施の形態を詳細に説明する。まず最初に本発明の背景を明らかにする為、図1を参照して表示装置の参考例を説明する。この参考例は本発明にかかる表示装置を開発するにあたって、その元になったものであり本発明を理解する上で有用なため、ここに参考例として説明する。

#### 【0015】

10

20

30

40

50

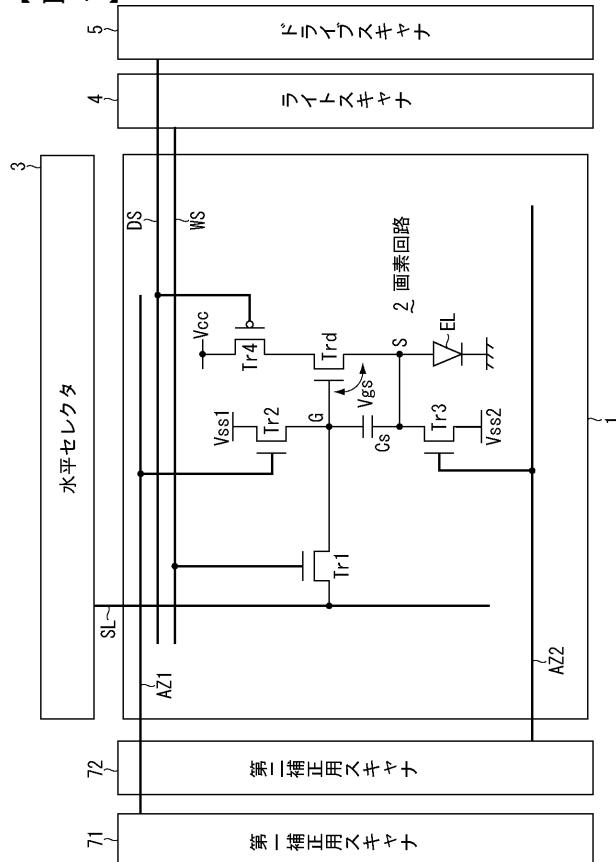

図示する様に、このアクティブマトリクス表示装置は主要部となる画素アレイ1と周辺の回路部とで構成されている。周辺の回路部は水平セレクタ3、ライトスキャナ4、ドライブスキャナ5、第一補正用スキャナ71、第二補正用スキャナ72などを含んでいる。画素アレイ1は行状の走査線WSと列状の信号線SLと両者の交差する部分にマトリクス状に配列した画素回路2とで構成されている。図では理解を容易にする為、1個の画素回路2のみを拡大表示してある。信号線SLは水平セレクタ3によって駆動される。水平セレクタ3は信号部を構成し、信号線SLに映像信号を供給する。走査線WSはライトスキャナ4によって走査される。なお、走査線WSと平行に別の走査線DS, AZ1及びAZ2も配線されている。走査線DSはドライブスキャナ5によって走査される。走査線AZ1は第一補正用スキャナ71によって走査される。走査線AZ2は第二補正用スキャナ72によって走査される。ライトスキャナ4、ドライブスキャナ5、第一補正用スキャナ71及び第二補正用スキャナ72はスキャナ部を構成しており、1水平走査期間ごと画素の行を順次走査する。各画素回路2は走査線WSによって選択されたとき信号線SLから映像信号をサンプリングする。さらに走査線DSによって選択されたとき、サンプリングされた映像信号に応じて画素回路2内に含まれている発光素子ELを駆動する。加えて画素回路2は走査線AZ1, AZ2によって走査された時、予め決められた補正動作を行う。

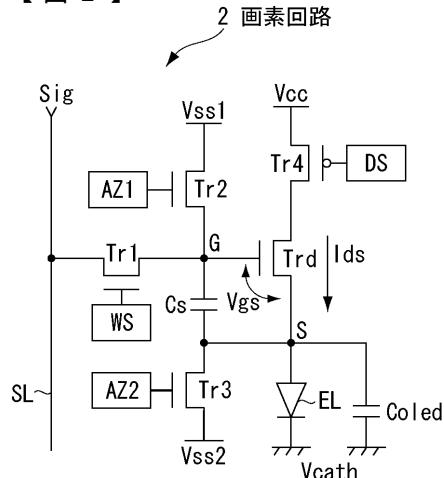

## 【0016】

画素回路2は、5個の薄膜トランジスタTr1～Tr4及びTrdと1個の容量素子(画素容量)Csと1個の発光素子ELとで構成されている。トランジスタTr1～Tr3とTrdはNチャネル型のポリシリコン TFTである。トランジスタTr4のみPチャネル型のポリシリコン TFTである。1個の容量素子Csは本画素回路2の容量部を構成している。発光素子ELは例えばアノード及びカソードを備えたダイオード型の有機EL素子である。但し本発明はこれに限られるものではなく、発光素子は一般的に電流駆動で発光する全てのデバイスを含む。

## 【0017】

画素回路2の中心となるドライブトランジスタTrdはそのゲートGが画素容量Csの一端に接続され、そのソースSと同じく画素容量Csの他端に接続されている。またドライブトランジスタTrdのゲートGはスイッチングトランジスタTr2を介して別の基準電位Vss1に接続されている。ドライブトランジスタTrdのドレインはスイッチングトランジスタTr4を介して電源Vccに接続されている。このスイッチングトランジスタTr2のゲートは走査線AZ1に接続されている。スイッチングトランジスタTr4のゲートは走査線DSに接続している。発光素子ELのアノードはドライブトランジスタTrdのソースSに接続し、カソードは接地されている。この接地電位はVcathで表される場合がある。また、ドライブトランジスタTrdのソースSと所定の基準電位Vss2との間にスイッチングトランジスタTr3が介在している。このトランジスタTr3のゲートは走査線AZ2に接続している。一方サンプリングトランジスタTr1は信号線SLとドライブトランジスタTrdのゲートGとの間に接続されている。サンプリングトランジスタTr1のゲートは走査線WSに接続している。

## 【0018】

かかる構成において、サンプリングトランジスタTr1は、所定のサンプリング期間に走査線WSから供給される制御信号WSに応じ導通して信号線SLから供給された映像信号Sigを容量部Csにサンプリングする。容量部Csは、サンプリングされた映像信号Sigに応じてドライブトランジスタのゲートGとソースS間に入力電圧Vgsを印加する。ドライブトランジスタTrdは、所定の発光期間中入力電圧Vgsに応じた出力電流Idsを発光素子ELに供給する。なおこの出力電流(ドレン電流)IdsはドライブトランジスタTrdのチャネル領域のキャリア移動度μ及び閾電圧Vthに対して依存性を有する。発光素子ELは、ドライブトランジスタTrdから供給された出力電流Idsにより映像信号Sigに応じた輝度で発光する。

## 【0019】

本参考例の特徴として、画素回路2はスイッチングトランジスタTr2～Tr4で構成

10

20

30

40

50

される補正手段を備えており、出力電流  $I_{ds}$  のキャリア移動度  $\mu$  に対する依存性を打ち消す為に、予め発光期間の先頭で容量部  $C_s$  に保持された入力電圧  $V_{gs}$  を補正する。具体的には、この補正手段 ( $T_{r2} \sim T_{r4}$ ) は、走査線  $WS$  及び  $DS$  から供給される制御信号  $WS$ ,  $DS$  に応じてサンプリング期間の一部で動作し、映像信号  $Sig$  がサンプリングされている状態でドライブトランジスタ  $T_{rd}$  から出力電流  $I_{ds}$  を取り出し、これを容量部  $C_s$  に負帰還して入力電圧  $V_{gs}$  を補正する。さらにこの補正手段 ( $T_{r2} \sim T_{r4}$ ) は、出力電流  $I_{ds}$  の閾電圧  $V_{th}$  に対する依存性を打ち消すために、予めサンプリング期間に先立ってドライブトランジスタ  $T_{rd}$  の閾電圧  $V_{th}$  を検出し、且つ検出された閾電圧  $V_{th}$  を入力電圧  $V_{gs}$  に足し込む様にしている。

## 【0020】

本参考例の場合、ドライブトランジスタ  $T_{rd}$  は N チャネル型トランジスタでドレインが電源  $V_{cc}$  側に接続する一方、ソース  $S$  が発光素子  $EL$  側に接続している。この場合、前述した補正手段は、サンプリング期間の後部分に重なる発光期間の先頭部分でドライブトランジスタ  $T_{rd}$  から出力電流  $I_{ds}$  を取り出して、容量部  $C_s$  側に負帰還する。その際本補正手段は、発光期間の先頭部分でドライブトランジスタ  $T_{rd}$  のソース  $S$  側から取り出した出力電流  $I_{ds}$  が、発光素子  $EL$  の有する容量に流れ込むようにしている。具体的には、発光素子  $EL$  はアノード及びカソードを備えたダイオード型の発光素子からなり、アノード側がドライブトランジスタ  $T_{rd}$  のソース  $S$  に接続する一方カソード側が接地されている。この構成で、本補正手段 ( $T_{r2} \sim T_{r4}$ ) は、予め発光素子  $EL$  のアノード / カソード間を逆バイアス状態にセットしておき、ドライブトランジスタ  $T_{rd}$  のソース  $S$  側から取り出した出力電流  $I_{ds}$  が発光素子  $EL$  に流れ込む時、このダイオード型の発光素子  $EL$  を容量性素子として機能させている。なお本補正手段は、サンプリング期間内でドライブトランジスタ  $T_{rd}$  から出力電流  $I_{ds}$  を取り出す時間幅  $t$  を調整可能であり、これにより容量部  $C_s$  に対する出力電流  $I_{ds}$  の負帰還量を最適化している。

## 【0021】

図 2 は、図 1 に示した表示装置から画素回路の部分を取り出した模式図である。理解を容易にするため、サンプリングトランジスタ  $T_{r1}$  によってサンプリングされる映像信号  $Sig$  や、ドライブトランジスタ  $T_{rd}$  の入力電圧  $V_{gs}$  及び出力電流  $I_{ds}$ 、さらには発光素子  $EL$  が有する容量成分  $C_{ole}$ などを書き加えてある。以下図 2 に基づいて、参考例にかかる画素回路 2 の動作を説明する。

## 【0022】

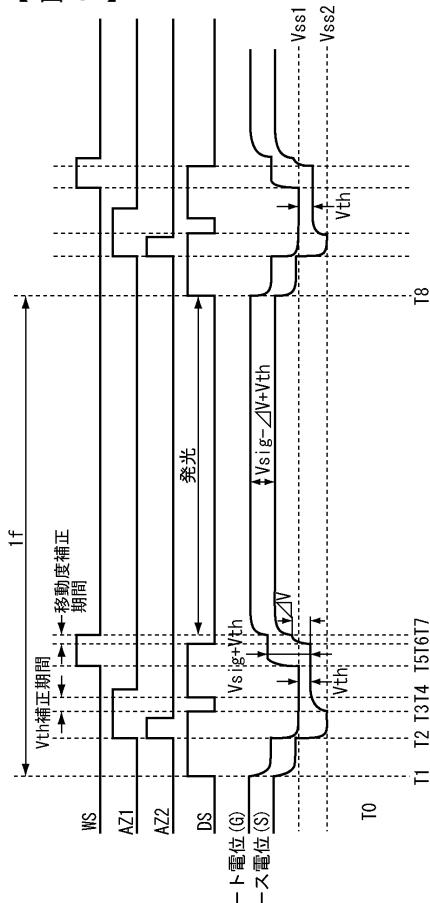

図 3 は、図 2 に示した画素回路のタイミングチャートである。図 3 を参照して、図 2 に示した参考例にかかる画素回路の動作をより具体的に説明する。図 3 は、時間軸  $T$  に沿って各走査線  $WS$ ,  $AZ1$ ,  $AZ2$  及び  $DS$  に印加される制御信号の波形を表してある。表記を簡略化する為、制御信号も対応する走査線の符号と同じ符号で表してある。トランジスタ  $T_{r1}$ ,  $T_{r2}$ ,  $T_{r3}$  は N チャネル型なので、走査線  $WS$ ,  $AZ1$ ,  $AZ2$  がそれぞれハイレベルの時オンし、ローレベルの時オフする。一方トランジスタ  $T_{r4}$  は P チャネル型なので、走査線  $DS$  がハイレベルの時オフし、ローレベルの時オンする。なおこのタイミングチャートは、各制御信号  $WS$ ,  $AZ1$ ,  $AZ2$ ,  $DS$  の波形と共に、ドライブトランジスタ  $T_{rd}$  のゲート  $G$  の電位変化及びソース  $S$  の電位変化も表してある。

## 【0023】

図 3 のタイミングチャートではタイミング  $T_1 \sim T_8$  までを 1 フィールド (1 f) としてある。1 フィールドの間に画素アレイの各行が一回順次走査される。タイミングチャートは、1 行分の画素に印加される各制御信号  $WS$ ,  $AZ1$ ,  $AZ2$ ,  $DS$  の波形を表してある。

## 【0024】

当該フィールドが始まる前のタイミング  $T_0$  で、全ての制御線号  $WS$ ,  $AZ1$ ,  $AZ2$ ,  $DS$  がローレベルにある。したがって N チャネル型のトランジスタ  $T_{r1}$ ,  $T_{r2}$ ,  $T_{r3}$  はオフ状態にある一方、P チャネル型のトランジスタ  $T_{r4}$  のみオン状態である。したがってドライブトランジスタ  $T_{rd}$  はオン状態のトランジスタ  $T_{r4}$  を介して電源  $V_c$

10

20

30

40

50

c に接続しているので、所定の入力電圧  $V_{g_s}$  に応じて出力電流  $I_{d_s}$  を発光素子 E\_L に供給している。したがってタイミング T\_0 で発光素子 E\_L は発光している。この時ドライブトランジスタ T\_r\_d に印加される入力電圧  $V_{g_s}$  は、ゲート電位 (G) とソース電位 (S) の差で表される。

## 【0025】

当該フィールドが始まるタイミング T\_1 で、制御信号 D\_S がローレベルからハイレベルに切り替わる。これによりトランジスタ T\_r\_4 がオフし、ドライブトランジスタ T\_r\_d は電源 V\_cc から切り離されるので、発光が停止し非発光期間に入る。したがってタイミング T\_1 に入ると、全てのトランジスタ T\_r\_1 ~ T\_r\_4 がオフ状態になる。

## 【0026】

続いてタイミング T\_2 に進むと、制御信号 A\_Z\_1 及び A\_Z\_2 がハイレベルになるので、スイッチングトランジスタ T\_r\_2 及び T\_r\_3 がオンする。この結果、ドライブトランジスタ T\_r\_d のゲート G が基準電位  $V_{ss1}$  に接続し、ソース S が基準電位  $V_{ss2}$  に接続される。ここで  $V_{ss1} - V_{ss2} > V_{th}$  を満たしており、 $V_{ss1} - V_{ss2} = V_{g_s} > V_{th}$  とする事で、その後タイミング T\_3 で行われる  $V_{th}$  補正の準備を行う。換言すると期間 T\_2 ~ T\_3 は、ドライブトランジスタ T\_r\_d のリセット期間に相当する。また、発光素子 E\_L の閾電圧を  $V_{th E_L}$  とすると、 $V_{th E_L} > V_{ss2}$  に設定されている。これにより、発光素子 E\_L にはマイナスバイアスが印加され、いわゆる逆バイアス状態となる。この逆バイアス状態は、後で行う  $V_{th}$  補正動作及び移動度補正動作を正常に行うために必要である。

## 【0027】

タイミング T\_3 では制御信号 A\_Z\_2 をローレベルにし且つ直後制御信号 D\_S もローレベルにしている。これによりトランジスタ T\_r\_3 がオフする一方トランジスタ T\_r\_4 がオンする。この結果ドレイン電流  $I_{d_s}$  が画素容量 C\_s に流れ込み、 $V_{th}$  補正動作を開始する。この時ドライブトランジスタ T\_r\_d のゲート G は  $V_{ss1}$  に保持されており、ドライブトランジスタ T\_r\_d がカットオフするまで電流  $I_{d_s}$  が流れる。カットオフするとドライブトランジスタ T\_r\_d のソース電位 (S) は  $V_{ss1} - V_{th}$  となる。ドレイン電流がカットオフした後のタイミング T\_4 で制御信号 D\_S を再びハイレベルに戻し、スイッチングトランジスタ T\_r\_4 をオフする。さらに制御信号 A\_Z\_1 もローレベルに戻し、スイッチングトランジスタ T\_r\_2 もオフする。この結果、画素容量 C\_s に  $V_{th}$  が保持固定される。この様にタイミング T\_3 ~ T\_4 はドライブトランジスタ T\_r\_d の閾電圧  $V_{th}$  を検出する期間である。ここでは、この検出期間 T\_3 ~ T\_4 を  $V_{th}$  補正期間と呼んでいる。

## 【0028】

この様に  $V_{th}$  補正を行った後タイミング T\_5 で制御信号 W\_S をハイレベルに切り替え、サンプリングトランジスタ T\_r\_1 をオンして映像信号 S\_ig の信号電位  $V_{sig}$  を画素容量 C\_s に書き込む。発光素子 E\_L の等価容量 C\_ole\_d に比べて画素容量 C\_s は充分に小さい。この結果、映像信号 S\_ig のほとんど大部分が画素容量 C\_s に書き込まれる。正確には、 $V_{ss1}$  に対する。信号電圧  $V_{sig}$  の差分  $V_{sig} - V_{ss1}$  が画素容量 C\_s に書き込まれる。したがってドライブトランジスタ T\_r\_d のゲート G とソース S 間の電圧  $V_{g_s}$  は、先に検出保持された  $V_{th}$  と今回サンプリングされた  $V_{sig} - V_{ss1}$  を加えたレベル ( $V_{sig} - V_{ss1} + V_{th}$ ) となる。以降説明簡易化の為  $V_{ss1} = 0V$  とすると、ゲート / ソース間電圧  $V_{g_s}$  は図 3 のタイミングチャートに示すように  $V_{sig} + V_{th}$  となる。かかる映像信号 S\_ig のサンプリングは制御信号 W\_S がローレベルに戻るタイミング T\_7 まで行われる。すなわちタイミング T\_5 ~ T\_7 がサンプリング期間に相当する。

## 【0029】

サンプリング期間の終了するタイミング T\_7 より前のタイミング T\_6 で制御信号 D\_S がローレベルとなりスイッチングトランジスタ T\_r\_4 がオンする。これによりドライブトランジスタ T\_r\_d が電源 V\_cc に接続されるので、画素回路は非発光期間から発光期間に進む。この様にサンプリングトランジスタ T\_r\_1 がまだオン状態で且つスイッチングトラン

10

20

30

40

50

ジスタ T r 4 がオン状態に入った期間 T 6 ~ T 7 で、ドライブトランジスタ T r d の移動度補正を行う。即ち本参考例では、サンプリング期間の後部分と発光期間の先頭部分とが重なる期間 T 6 ~ T 7 で移動度補正を行っている。なお、この移動度補正を行う発光期間の先頭では、発光素子 E L は実際には逆バイアス状態にあるので発光する事はない。この移動度補正期間 T 6 ~ T 7 では、ドライブトランジスタ T r d のゲート G が映像信号 S i g のレベル V s i g に固定された状態で、ドライブトランジスタ T r d にドレイン電流 I d s が流れる。ここで  $V_{ss1} - V_{th} < V_{th}$  E L と設定しておく事で、発光素子 E L は逆バイアス状態におかれる為、ダイオード特性ではなく単純な容量特性を示すようになる。よってドライブトランジスタ T r d に流れる電流 I d s は画素容量 C s と発光素子 E L の等価容量 C o l e d の両者を結合した容量  $C = C_s + C_{oled}$  に書き込まれていく。10 これによりドライブトランジスタ T r d のソース電位 ( S ) は上昇していく。図 3 のタイミングチャートではこの上昇分を  $\Delta V$  で表してある。この上昇分  $\Delta V$  は結局画素容量 C s に保持されたゲート / ソース間電圧 V g s から差し引かれる事になるので、負帰還をかけた事になる。この様にドライブトランジスタ T r d の出力電流 I d s を同じくドライブトランジスタ T r d の入力電圧 V g s に負帰還する事で、移動度  $\mu$  を補正する事が可能である。なお負帰還量  $\Delta V$  は移動度補正期間 T 6 ~ T 7 の時間幅 t を調整する事で最適化可能である。

#### 【 0 0 3 0 】

タイミング T 7 では制御信号 W S がロー レベルとなりサンプリングトランジスタ T r 1 がオフする。この結果ドライブトランジスタ T r d のゲート G は信号線 S L から切り離される。映像信号 S i g の印加が解除されるので、ドライブトランジスタ T r d のゲート電位 ( G ) は上昇可能となり、ソース電位 ( S ) と共に上昇していく。その間画素容量 C s に保持されたゲート / ソース間電圧 V g s は  $(V_{sig} - V + V_{th})$  の値を維持する。ソース電位 ( S ) の上昇に伴い、発光素子 E L の逆バイアス状態は解消されるので、出力電流 I d s の流入により発光素子 E L は実際に発光を開始する。この時のドレイン電流 I d s 対ゲート電圧 V g s の関係は、先のトランジスタ特性式 1 の  $V_{gs}$  に  $V_{sig} - V + V_{th}$  を代入する事で、以下の式 2 のように与えられる。20

$$I_{ds} = k \mu (V_{gs} - V_{th})^2 = k \mu (V_{sig} - V)^2 \dots \text{式 2}$$

上記式 2 において、 $k = (1/2)(W/L)C_{ox}$  である。この特性式 2 から  $V_{th}$  の項がキャンセルされており、発光素子 E L に供給される出力電流 I d s はドライブトランジスタ T r d の閾電圧  $V_{th}$  に依存しない事が分かる。基本的にドレイン電流 I d s は映像信号の信号電圧  $V_{sig}$  によって決まる。換言すると、発光素子 E L は映像信号 S i g の電位レベル  $V_{sig}$  に応じた輝度で発光する事になる。その際  $V_{sig}$  は帰還量  $\Delta V$  で補正されている。この補正量  $\Delta V$  は丁度特性式 2 の係数部に位置する移動度  $\mu$  の効果を打ち消すように働く。したがって、ドレイン電流 I d s は実質的に映像信号電位  $V_{sig}$  のみに依存する事になる。30

#### 【 0 0 3 1 】

最後にタイミング T 8 に至ると制御信号 D S がハイレベルとなってスイッチングトランジスタ T r 4 がオフし、発光が終了すると共に当該フィールドが終わる。この後次のフィールドに移って再び  $V_{th}$  補正動作、移動度補正動作及び発光動作が繰り返される事になる。40

#### 【 0 0 3 2 】

しかしながらこの参考例にかかる画素回路では、5種類のトランジスタ T r 1 , T r 2 , T r 3 , T r 4 , T r d と、3種類の電源ライン  $V_{ss1}$  ,  $V_{ss2}$  ,  $V_{cc}$  、4種類のゲートライン（走査線） W S , D S , A Z 1 , A Z 2 を形成する必要があり、電源ラインや信号線ラインとのクロスオーバーが増加してしまう。これは歩留りを低下させる原因になる。さらにレイアウト的に高精細化が困難になる。高精細パネルにおいては、歩留りを上げるために、素子数を削減する必要がある。

#### 【 0 0 3 3 】

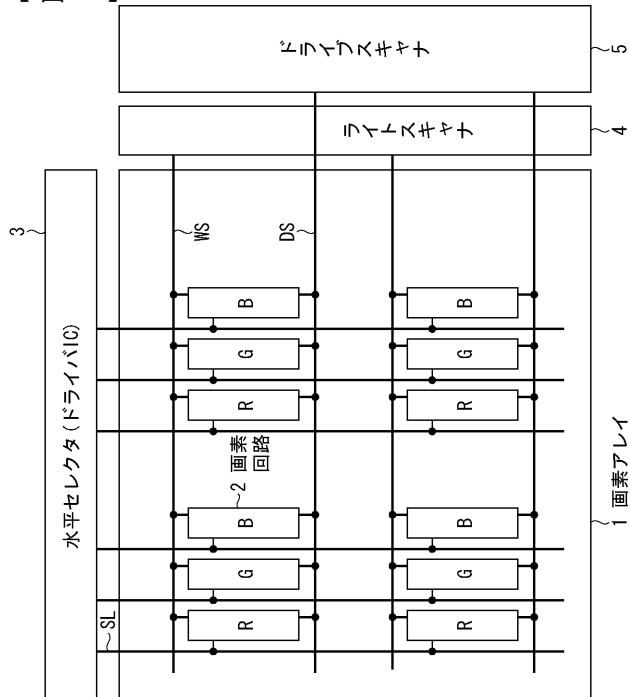

図 4 は、本発明にかかる表示装置の全体構成を示しており、閾電圧 ( $V_{th}$ ) 補正機能

10

20

30

40

50

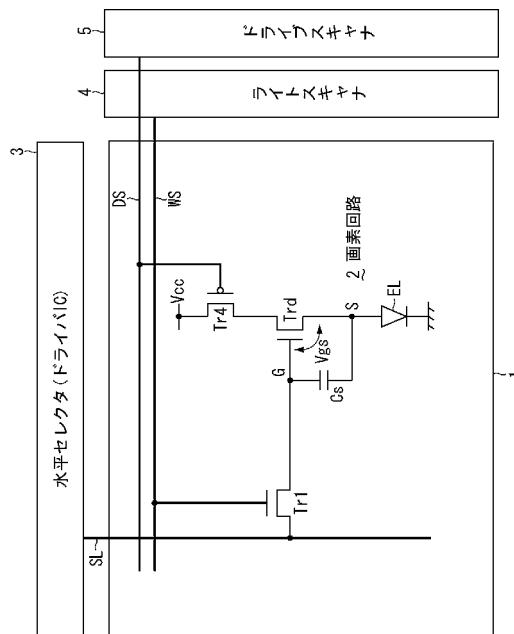

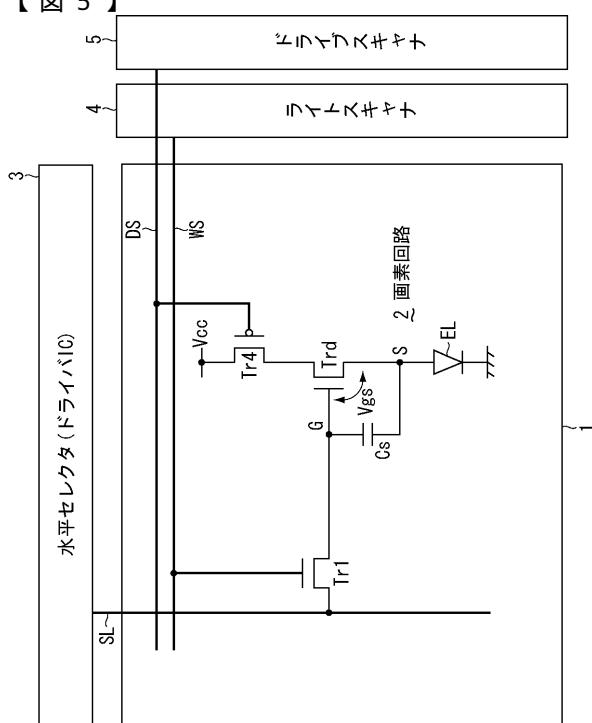

を備えたアクティブマトリクス型である。図示する様に、このアクティブマトリクス型表示装置は、主要部となる画素アレイ1と周辺の回路部とで構成されている。周辺の回路部は水平セレクタ3、ライトスキャナ4、ドライブスキャナ5などを含んでいる。画素アレイ1は行状の走査線WSと列状の信号線SLと両者の交差する部分にマトリクス状に配列した画素R,G,Bとで構成されている。カラー表示を可能とするため、RGBの三原色画素を用意しているが、本発明はこれに限られるものではない。各画素R,G,Bはそれぞれ画素回路2で構成されている。信号線SLは水平セレクタ3によって駆動される。水平セレクタ3は信号部を構成し、一般にドライバICが用いられ、信号線SLに映像信号を供給する。走査線WSはライトスキャナ4によって走査される。なお、第1の走査線WSと並行に第2の走査線DSも配線されている。走査線DSはドライブスキャナ5によって走査される。ライトスキャナ4とドライブスキャナ5はスキャナ部を構成しており、1水平走査期間ごと画素の行を順次走査する。各画素回路2は走査線WSによって選択されたとき信号線SLから映像信号をサンプリングする。さらに走査線DSによって選択されたとき、サンプリングされた映像信号に応じて画素回路2内に含まれている発光素子を駆動する。加えて画素回路2は水平走査期間内で走査線WS及びDSによって制御されたとき、予め決められた補正動作を行う。

#### 【0034】

上述した画素アレイ1は通常ガラスなどの絶縁基板上に形成されており、フラットパネルとなっている。各画素回路2はアモルファスシリコン薄膜トランジスタ(TFT)または低温ポリシリコンTFTで形成されている。アモルファスシリコンTFTの場合、スキャナ部はパネルとは別のTABなどで構成され、フレキシブルケーブルにてフラットパネルに接続される。同様に信号部も外付けのドライバICで構成され、フレキシブルケーブルにてフラットパネルに接続される。低温ポリシリコンTFTの場合、信号部及びスキャナ部も同じ低温ポリシリコンTFTで形成できるので、フラットパネル上に画素アレイ部と信号部とスキャナ部を一体的に形成できる。

#### 【0035】

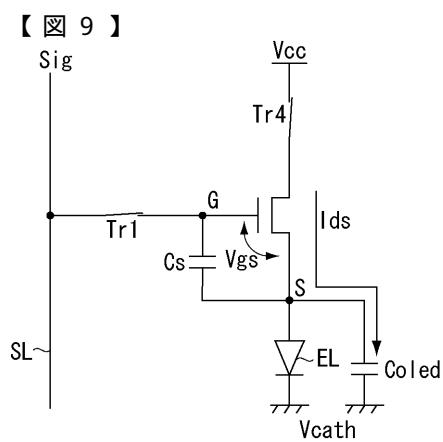

図5は、図4に示した表示装置に組み込まれる画素回路の実施形態を表している。この画素回路2は、サンプリングトランジスタTr1と、これに接続する画素容量Csと、これに接続するドライブトランジスタTrdと、これに接続する発光素子ELと、ドライブトランジスタTrdを電源Vccに接続するスイッチングトランジスタTr4とを含む。

#### 【0036】

サンプリングトランジスタTr1は、第1走査線WSから供給される制御信号WSに応じ導通して信号線SLから供給された映像信号の信号電位Vsigを画素容量Csにサンプリングする。画素容量Csは、サンプリングされた映像信号の信号電位Vsigに応じてドライブトランジスタTrdのゲートGに入力電圧Vgssを印加する。ドライブトランジスタTrdは、入力電圧Vgssに応じた出力電流Idsを発光素子ELに供給する。なおこの出力電流Idsは、ドライブトランジスタTrdの閾電圧Vthに対して依存性を有する。発光素子ELは、発光期間中ドライブトランジスタTrdから供給された出力電流Idsにより映像信号の信号電位Vsigに応じた輝度で発光する。スイッチングトランジスタTr4は、第2走査線DSから供給される制御信号DSに応じ導通して発光期間中ドライブトランジスタTrdを電源Vccに接続し、非発光期間では非導通状態になってドライブトランジスタTrdを電源Vccから切り離す。

#### 【0037】

特徴事項として、ライトスキャナ4及びドライブスキャナ5で構成されるスキャナ部は、水平走査期間(1H)に第1走査線WS及び第2走査線DSにそれぞれ制御信号WS,DSを出力し、サンプリングトランジスタTr1及びスイッチングトランジスタTr4をオンオフ制御して、出力電流Idsの閾電圧Vthに対する依存性を補正するために画素容量Csをリセットする準備動作、リセットされた画素容量Csに閾電圧Vthをキャセルするための電圧を書き込む補正動作、及び補正された画素容量Csに映像信号Sigの信号電位Vsigをサンプリングするサンプリング動作を実行する。一方水平セレクタ

(ドライバ I C) 3で構成された信号部は、水平走査期間(1H)に映像信号を第1の固定電位V<sub>ssH</sub>と、第2の固定電位V<sub>ssL</sub>と、信号電位V<sub>sig</sub>との間で切換え、以って上述した準備動作、補正動作及びサンプリング動作に必要な電位を各画素に信号線S<sub>L</sub>を介して供給する。

#### 【0038】

具体的には水平セレクタ3は、まず高レベルの第1固定電位V<sub>ssH</sub>を供給し続いて低レベルの第2固定電位V<sub>ssL</sub>に切換えて準備動作を可能とし、さらに低レベルの第2固定電位V<sub>ssL</sub>を維持した状態で補正動作を実行し、その後信号電位V<sub>sig</sub>に切換えてサンプリング動作を実行する。上述したように水平セレクタ3はドライバI Cで構成され、信号電位V<sub>sig</sub>を生成する信号生成回路と、信号生成回路から出力された信号電位V<sub>sig</sub>に第1固定電位V<sub>ssH</sub>及び第2固定電位V<sub>ssL</sub>を挿入し、以って第1固定電位V<sub>ssH</sub>と第2固定電位V<sub>ssL</sub>と信号電位V<sub>sig</sub>とが切換る映像信号を合成して各信号線S<sub>L</sub>に出力する出力回路とを含む。好ましくは水平セレクタ3を構成するドライバI Cは、通常の定格を超えない信号電位V<sub>sig</sub>と定格を超える第1固定電位V<sub>ssH</sub>とを合成した映像信号を出力する。この場合ドライバI Cに含まれる信号生成回路は定格を超えない信号電位V<sub>sig</sub>を生成するため通常の耐圧を有する一方、出力回路は定格を超える第1固定電位V<sub>ssH</sub>に対処するため高耐圧化されている。

#### 【0039】

ドライブトランジスタT<sub>rd</sub>は、その出力電流I<sub>ds</sub>が閾電圧V<sub>th</sub>に加えチャネル領域のキャリア移動度μに対しても依存性を有する。この場合ライトスキャナ4とドライブスキャナ5で構成されるスキャナ部は、水平走査期間(1H)に第2走査線D<sub>S</sub>に制御信号を出力してさらにスイッチングトランジスタT<sub>r4</sub>を制御し、出力電流I<sub>ds</sub>のキャリア移動度μに対する依存性を打ち消すために、信号電位V<sub>sig</sub>がサンプリングされている状態でドライブトランジスタT<sub>rd</sub>から出力電流を取り出し、これを画素容量C<sub>s</sub>に負帰還して入力電圧V<sub>gs</sub>を補正する動作を実行する。

#### 【0040】

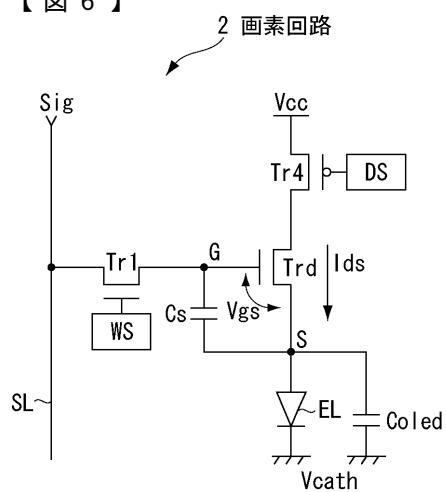

図6は、図5に示した表示装置から画素回路2の部分を取り出した模式図である。理解を容易にするため、サンプリングトランジスタT<sub>r1</sub>によってサンプリングされる映像信号S<sub>ig</sub>やドライブトランジスタT<sub>rd</sub>の入力電圧V<sub>gs</sub>及び出力電流I<sub>ds</sub>、さらには発光素子E<sub>L</sub>が有する容量成分C<sub>oled</sub>などを書き加えてある。また各トランジスタのゲートに接続される走査線W<sub>S</sub>、D<sub>S</sub>も書き込んである。この画素回路2は水平走査期間(1H)内にV<sub>th</sub>補正準備動作と、実際の補正動作と信号電位サンプリング動作を行う。これにより、画素回路2は3個のトランジスタT<sub>r1</sub>、T<sub>r4</sub>、T<sub>rd</sub>と1個の画素容量C<sub>s</sub>と1個の発光素子E<sub>L</sub>とで構成可能である。図1に示した参考例にかかるV<sub>th</sub>補正機能を組み込んだ画素回路に比べ、少なくともトランジスタを2個削減可能である。これにより電源ラインやゲートラインを削減することが出来、パネルの歩留りの改善につながる。また画素回路のレイアウトを簡素化することで高精細化も可能である。

#### 【0041】

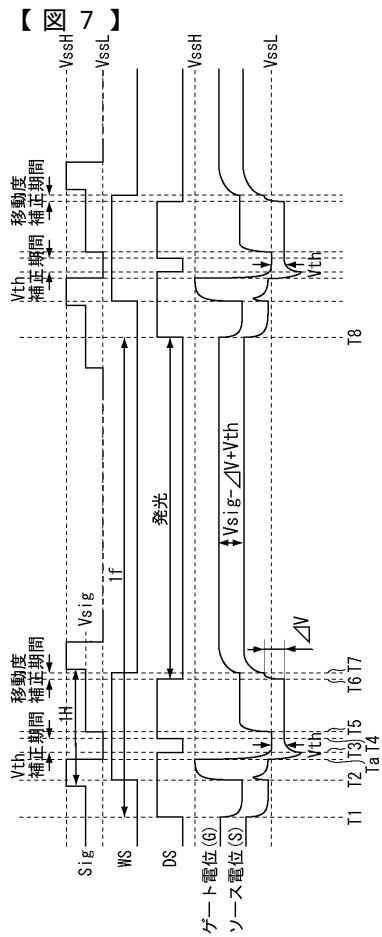

図7は、図5及び図6に示した画素回路のタイミングチャートである。図7を参照して、図5及び図6に示した画素回路の動作を具体的且つ詳細に説明する。図7は、時間軸Tに沿って各走査線W<sub>S</sub>、D<sub>S</sub>に印加される制御信号の波形を表してある。表記を簡略するため、制御信号も対応する走査線の符号と同じ符号で示してある。合わせて信号線に印加される映像信号S<sub>ig</sub>の波形も時間軸Tに沿って示してある。図示する様に、この映像信号は各水平走査期間(1H)内で、高電位V<sub>ssH</sub>、低電位V<sub>ssL</sub>、信号電位V<sub>sig</sub>と順に切換る。トランジスタT<sub>r1</sub>はNチャネル型なので、走査線W<sub>S</sub>がハイレベルのときオンし、ローレベルのときオフする。一方トランジスタT<sub>r4</sub>はPチャネル型なので、走査線D<sub>S</sub>がハイレベルのときオフし、ローレベルのときオンする。なおこのタイミングチャートは、各制御信号W<sub>S</sub>、D<sub>S</sub>の波形や映像信号の波形と共に、ドライブトランジスタT<sub>rd</sub>のゲートGの電位変化及びソースSの電位変化も表してある。

#### 【0042】

10

20

30

40

50

図7のタイミングチャートではタイミングT1～T8までを1フィールド(1f)としてある。1フィールドの間に画素アレイの各行が一回順次走査される。タイミングチャートは、1行分の画素に印加される各制御信号WS, DSの波形を表してある。

#### 【0043】

初めにタイミングT1で、スイッチングトランジスタTr4をオフして非発光とする。この時、ドライブトランジスタTrdのソース電位はVccからの電源供給が無いので、発光素子ELのカットオフ電圧VthELまで下げられる。

#### 【0044】

次にタイミングT2で、サンプリングトランジスタTr1をオンする。ただしこの前に、信号線電圧をVssHまで上げておく方が、書き込み時間を短くできるので好ましい。サンプリングトランジスタTr1をオンする事でドライブトランジスタTrdのゲート電位はVssHが書き込まれる。この時、画素容量Csを介してソース電位にカップリングが入り、ソース電位は上昇する。ソースSの電位は一度上昇するが、発光素子ELを介して放電されるので、再度ソース電圧はVthELになる。この時、ゲート電圧はVssHのままである。

#### 【0045】

次にタイミングTaで、サンプリングトランジスタTr1をオンしたまま、信号電圧をVssLに変化させる。この電位変化が画素容量Csを介してソース電位にカップリングされる。この時のカップリング量は、 $C_s / (C_s + C_{oled}) \times (VssH - VssL)$ にて求められる。この時、ゲート電位はVssL、ソース電位は $VthEL - C_s / (C_s + C_{oled}) \times (VssH - VssL)$ で表される。ここでマイナスバイアスを入れた為に、ソース電圧はVthELよりも小さくなり、発光素子ELはカットオフする。ここでソース電位は、この後のVth補正や移動度補正終了後も発光素子ELがカットオフし続ける電位に設定することが望ましい。また、この $Vgs > Vth$ となるようにカップリングを入れることで、Vth補正の準備を行うことができる。以上により、トランジスタや電源ライン、ゲートラインを削減した回路においてもVth補正準備を行うことができる。即ちタイミングT2～Taは補正準備期間に含まれる。

#### 【0046】

この後、タイミングT3でゲートGをVssLに保持した状態のままスイッチングトランジスタTr4をオンすると、ドライブトランジスタTrdに電流が流れ、参考例と同様にVth補正が行われる。ドライブトランジスタTrdがカットオフするまで電流が流れ、カットオフするとドライブトランジスタTrdのソース電位はVssL - Vthとなる。ここで、 $VssL - Vth < VthEL$ とする必要がある。

#### 【0047】

この後タイミングT4で、スイッチングトランジスタTr4をオフしてVth補正是終了する。即ち、タイミングT3～T4はVth補正期間である。

#### 【0048】

この様にタイミングT3～T4でVth補正を行った後、タイミングT5に至って信号線の電位がVssLからVsigに変化する。これにより映像信号の信号電位Vsigが画素容量Csに書き込まれる。発光素子ELの等価容量Coloredに比べて画素容量Csは十分に小さい。この結果、信号電位Vsigのほとんど大部分が画素容量Csに書き込まれる。したがってドライブトランジスタTrdのゲートGとソースS間の電圧Vgsは、先に検出保持されたVthと今回サンプリングされたVsigを加えたレベル( $Vsig + Vth$ )となる。即ちドライブトランジスタTrdに対する入力電圧VgsはVsig + Vthとなる。かかる信号電圧Vsigのサンプリングは制御信号WSがローレベルに戻るタイミングT7まで行われる。即ちタイミングT5～T7がサンプリング期間に相当する。

#### 【0049】

本発明にかかる画素回路は、上述した閾電圧Vthの補正に加え、移動度μの補正も行っている。移動度μの補正はタイミングT6～T7で行われる。この点については後で詳

10

20

30

40

50

細に説明する。結論としてタイミングチャートに示すように、補正量  $V$  が入力電圧  $V_{sig}$  から差し引かれる。

#### 【0050】

タイミング T7 になると、制御信号 WS がローレベルとなりサンプリングトランジスタ Tr1 がオフする。この結果ドライブトランジスタ Trd のゲート G は信号線 SL から切り離される。映像信号 Sig の印加が解除されるので、ドライブトランジスタ Trd のゲート電位 (G) は上昇可能となり、ソース電位 (S) と共に上昇していく。その間画素容量 Cs に保持されたゲート / ソース間電圧 Vgs は ( $V_{sig} - V + V_{th}$ ) の値を維持する。ソース電位 (S) の上昇に伴い、発光素子 EL の逆バイアス状態は解消されるので、出力電流 Ids の流入により発光素子 EL は実際に発光を開始する。この時のドレン電流 Ids 対ゲート電圧 Vgs の関係は、前述した式2 のように与えられる。この特性式2 から  $V_{th}$  の項がキャンセルされており、発光素子 EL に供給される出力電流 Ids はドライブトランジスタ Trd の閾電圧  $V_{th}$  に依存しない事が分かる。基本的にドレン電流 Ids は映像信号の信号電圧  $V_{sig}$  によって決まる。換言すると、発光素子 EL は映像信号 Sig に応じた輝度で発光する事になる。その際  $V_{sig}$  は帰還量  $V$  で補正されている。この補正量  $V$  は丁度特性式2 の係数部に位置する移動度  $\mu$  の効果を打ち消すように働く。したがって、ドレン電流 Ids は実質的に映像信号 Sig の信号電位  $V_{sig}$  のみに依存する事になる。

10

20

30

40

50

#### 【0051】

最後にタイミング T8 に至ると制御信号 DS がハイレベルとなってスイッチングトランジスタ Tr4 がオフし、発光が終了すると共に当該フィールドが終わる。この後次のフィールドに移って再び補正準備動作、 $V_{th}$  補正動作、移動度補正動作及び発光動作が繰り返される事になる。

#### 【0052】

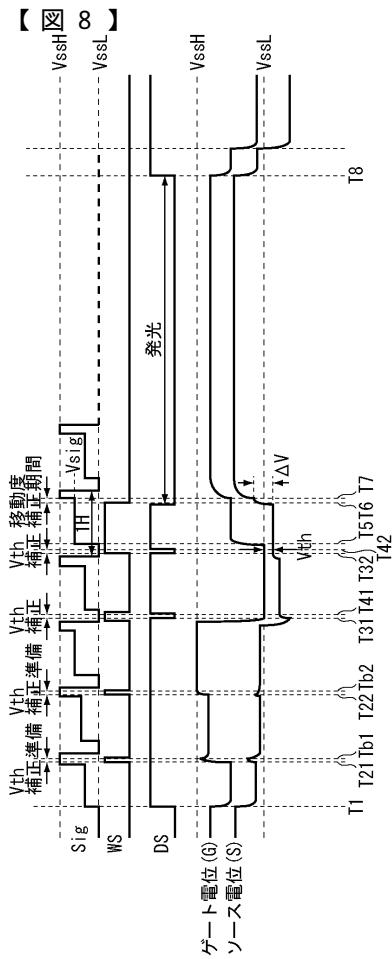

図7のタイミングチャートに示した様に、1水平走査期間 (1H) 内で閾電圧キャンセルのための準備動作、補正動作及びサンプリング動作を続けて行うことで、図5に示したように画素回路2を3個のトランジスタと1個の画素容量とで構成することが出来る。これにより、画素回路の構成素子数を参考例に比べ大幅に削減している。しかしながら、パネルが高精細化するにつれて画素数が増えるため、各画素行に割り当てる水平走査期間は短くなってしまう。また高画質化のために高周波数駆動方式が提案されているが、この高周波駆動においても同様に水平走査期間が短くなってしまう。この様に水平走査期間が短縮化されると、 $V_{th}$  補正準備動作や実際の  $V_{th}$  補正動作を1水平走査期間内で完了することが難しい場合がある。そのため、高精細パネルや高周波数駆動パネルに対応した表示装置駆動方式が求められており、以下に本発明の最良の実施形態として説明する。

#### 【0053】

本発明の最良の実施形態では、 $V_{th}$  補正機能付の画素回路で素子数を削減した上に、さらに高精細パネルや高周波数駆動パネルに対応可能な駆動方式を実現している。本実施形態では、1水平走査期間内で行っていた  $V_{th}$  補正準備や  $V_{th}$  補正動作を、複数の水平走査期間にわたって時分割的に実行することで、トータルの動作時間を図7に示したタイミングチャートの駆動方式と同程度に確保することが出来る。この時分割方式では1水平走査期間内に占める準備動作期間や補正動作期間を短縮化できるので、その分信号電位のサンプリング時間を十分に確保することが可能である。

#### 【0054】

図8は本発明の最良の実施形態を示すタイミングチャートである。理解を容易にするため、図7に示した先の例のタイミングチャートと対応する部分には対応する参照番号を付してある。

#### 【0055】

図示するようにタイミング T1 で、スイッチングトランジスタ Tr4 をオフして非発光とする。この時、ドライブトランジスタ Trd のソース電位は  $V_{cc}$  からの電源供給がないので、発光素子 EL のカットオフ電圧  $V_{th}$  EL まで下げられる。

## 【0056】

次に、映像信号  $S_{ig}$  が  $V_{th}$  補正準備に必要な高電圧  $V_{SSH}$  になる時間帯のタイミング  $T_{21} \sim T_{b1}$  にサンプリングトランジスタ  $T_{r1}$  をオンする。サンプリングトランジスタ  $T_{r1}$  をオンする事でドライブトランジスタ  $T_{rd}$  のゲート電位に  $V_{SSH}$  が書き込まれる。この時、画素容量  $C_s$  を介してソース電位にカップリングが入り、ソース電位は上昇する。ソース  $S$  は一度上昇するが、発光素子  $E_L$  を介して放電されるので、再度ソース電圧は  $V_{th} E_L$  になる。サンプリングトランジスタ  $T_{r1}$  をオンする制御信号  $WS$  は分割パルスであり、そのパルス幅 ( $T_{21} \sim T_{b1}$ ) は非常に短く、ゲート電圧は  $V_{SSH}$  まで書き込まれない。そこで、それ以降のタイミング  $T_{22} \sim T_{b2}$  において、再度映像信号  $S_{ig}$  が高電圧  $V_{SSH}$  になる時にサンプリングトランジスタ  $T_{r1}$  をオンする。必要に応じ同様のオペレーションをゲート電圧が  $V_{SSH}$  になるまで繰りかえす。

10

## 【0057】

次に映像信号  $S_{ig}$  が低電圧  $V_{SSL}$  に変化した状態で、サンプリングトランジスタ  $T_{r1}$  をオンする。この電位変化により  $V_{gs} > V_{th}$  とし、 $V_{th}$  補正の準備を完了することができる。サンプリングトランジスタ  $T_{r1}$  をオンした状態下、タイミング  $T_{31} \sim T_{41}$  でスイッチングトランジスタ  $T_{r4}$  を更にオンすることで、ドライブトランジスタ  $T_{rd}$  には電流が流れ、 $V_{th}$  補正動作が行われる。同様にこの  $V_{th}$  補正期間も分割されており各パルスの時間幅 (タイミング  $T_{31} \sim T_{41}$ ) は短くなっている為、 $V_{th}$  補正が完了するまで、サンプリングトランジスタ  $T_{r1}$  やスイッチングトランジスタ  $T_{r4}$  を繰り返しオン駆動する必要がある (タイミング  $T_{32} \sim T_{42}$ )。

20

## 【0058】

最後に、サンプリングトランジスタ  $T_{r1}$  がオンしているタイミング  $T_{5} \sim T_{7}$  で、画素容量  $C_s$  に信号電圧  $V_{sig}$  を書き込む。その間タイミング  $T_{6} \sim T_{7}$  で、移動度補正を行った後、発光状態に移行する。

## 【0059】

以上により、トランジスタや電源ライン、ゲートラインを削減した回路において、パネルの動作が高周波で且つ画素が高精細であっても、 $V_{th}$  補正準備と  $V_{th}$  補正を行うことができる。なお、上記の実施形態では、サンプリングトランジスタ  $T_{r1}$  をオンした状態でスイッチングトランジスタ  $T_{r4}$  をオンして移動度補正をかけているが、サンプリングトランジスタ  $T_{r1}$  とスイッチングトランジスタ  $T_{r4}$  をノンオーバーラップにして移動度補正を行わない単純な  $V_{th}$  補正動作においても、同様に配線やトランジスタの削減は可能である。又本実施形態の回路では、スイッチングトランジスタ  $T_{r4}$  は  $Nch$  型を用いたが、各トランジスタの特性は  $Nch$  でも  $Pch$  でも構わない。

30

## 【0060】

このように本発明のスキナ部は、水平走査期間内で走査線に制御信号を出力して画素回路  $2$  を制御し、ドライブトランジスタ  $T_{rd}$  の出力電流  $I_{ds}$  の閾電圧  $V_{th}$  に対する依存性を補正するため画素容量  $C_s$  に補正をかける動作と、補正された画素容量  $C_s$  に映像信号  $S_{ig}$  の信号電位  $V_{sig}$  をサンプリングする動作とを実行し、更にスキナ部は、当該行の画素回路に先行する行に割り当てられた前の水平走査期間を利用して、画素容量  $C_s$  に補正をかける動作を各水平走査期間で時分割的に行うことを特徴とする。具体的には、このスキナ部はライトスキナ  $4$  とドライブスキナ  $5$  とからなり、水平走査期間に第  $1$  走査線  $WS$  及び第  $2$  走査線  $DS$  に夫々制御信号を出力し、サンプリングトランジスタ  $T_{r1}$  及びスイッチングトランジスタ  $T_{r4}$  をオンオフ制御して、出力電流  $I_{ds}$  の閾電圧  $V_{th}$  に対する依存性を補正するため画素容量  $C_s$  に補正をかける動作として、画素容量  $C_s$  をリセットする準備動作とリセットされた画素容量  $C_s$  に閾電圧  $V_{th}$  をキヤンセルするための電圧を書き込む補正動作を行い、その後補正された画素容量  $C_s$  に映像信号  $S_{ig}$  の信号電位  $V_{sig}$  をサンプリングするサンプリング動作を実行し、更にスキナ部は、当該行の画素に先行する行に割り当てられた前の水平走査期間を利用して、準備動作と補正動作の両方若しくは片方を各水平走査期間で時分割的に行う。

40

## 【0061】

50

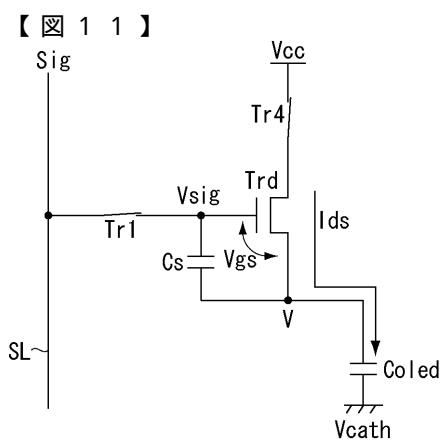

続いてタイミング T<sub>6</sub> T<sub>7</sub>で行われる移動度補正動作を詳細に説明する。図 9 は、移動度補正期間 T<sub>6</sub> T<sub>7</sub>における画素回路 2 の状態を示す回路図である。図示するように、移動度補正期間 T<sub>6</sub> T<sub>7</sub>では、サンプリングトランジスタ T<sub>r1</sub> 及びスイッチングトランジスタ T<sub>r4</sub> がオンしている一方、残りのスイッチングトランジスタ T<sub>r3</sub> がオフしている。この状態でドライブトランジスタ T<sub>r4</sub> のソース電位 (S) は V<sub>ssL</sub> - V<sub>th</sub> である。このソース電位 S は発光素子 E<sub>L</sub> のアノード電位でもある。前述したように V<sub>ssL</sub> - V<sub>th</sub> < V<sub>th</sub> E<sub>L</sub> と設定しておく事で、発光素子 E<sub>L</sub> は逆バイアス状態におかれ、ダイオード特性ではなく単純な容量特性を示す事になる。よってドライブトランジスタ T<sub>rd</sub> に流れる電流 I<sub>ds</sub> は画素容量 C<sub>s</sub> と発光素子 E<sub>L</sub> の等価容量 C<sub>olead</sub> との合成容量 C = C<sub>s</sub> + C<sub>olead</sub> に流れ込む事になる。換言すると、ドレン電流 I<sub>ds</sub> の一部が画素容量 C<sub>s</sub> に負帰還され、移動度の補正が行われる。

10

## 【0062】

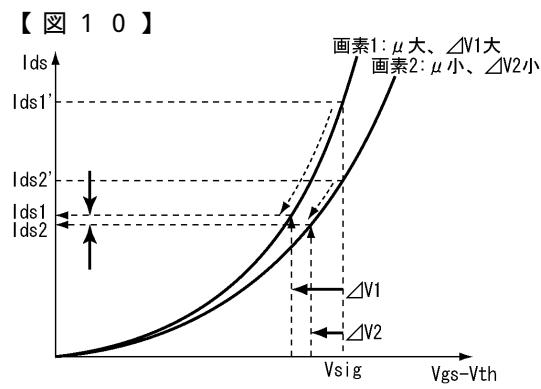

図 10 は上述したトランジスタ特性式 2 をグラフ化したものであり、縦軸に I<sub>ds</sub> を取り横軸に V<sub>sig</sub> を取ってある。このグラフの下方に特性式 2 も合わせて示してある。図 10 のグラフは、画素 1 と画素 2 を比較した状態で特性カーブを描いてある。画素 1 のドライブトランジスタの移動度 μ は相対的に大きい。逆に画素 2 に含まれるドライブトランジスタの移動度 μ は相対的に小さい。この様にドライブトランジスタをポリシリコン薄膜トランジスタなどで構成した場合、画素間で移動度 μ がばらつく事は避けられない。例えば両画素 1, 2 に同レベルの映像信号電位 V<sub>sig</sub> を書き込んだ場合、何ら移動度の補正を行わないと、移動度 μ の大きい画素 1 に流れる出力電流 I<sub>ds1'</sub> は、移動度 μ の小さい画素 2 に流れる出力電流 I<sub>ds2'</sub> に比べて大きな差が生じてしまう。この様に移動度 μ のばらつきに起因して出力電流 I<sub>ds</sub> の間に大きな差が生じるので、画面のユニフォーミティを損なう事になる。

20

## 【0063】

そこで本発明では出力電流を入力電圧側に負帰還させる事で移動度のばらつきをキャンセルしている。トランジスタ特性式から明らかなように、移動度が大きいとドレン電流 I<sub>ds</sub> が大きくなる。したがって負帰還量 V は移動度が大きいほど大きくなる。図 10 のグラフに示すように、移動度 μ の大きな画素 1 の負帰還量 V<sub>1</sub> は移動度の小さな画素 2 の負帰還量 V<sub>2</sub> に比べて大きい。したがって、移動度 μ が大きいほど負帰還が大きくかかる事となって、ばらつきを抑制する事が可能である。図示するように、移動度 μ の大きな画素 1 で V<sub>1</sub> の補正をかけると、出力電流は I<sub>ds1'</sub> から I<sub>ds1</sub> まで大きく下降する。一方移動度 μ の小さな画素 2 の補正量 V<sub>2</sub> は小さいので、出力電流 I<sub>ds2'</sub> は I<sub>ds2</sub> までそれ程大きく下降しない。結果的に、I<sub>ds1</sub> と I<sub>ds2</sub> は略等しくなり、移動度のばらつきがキャンセルされる。この移動度のばらつきのキャンセルは黒レベルから白レベルまで V<sub>sig</sub> の全範囲で行われるので、画面のユニフォーミティは極めて高くなる。以上をまとめると、移動度の異なる画素 1 と 2 があった場合、移動度の大きい画素 1 の補正量 V<sub>1</sub> は移動度の小さい画素 2 の補正量 V<sub>2</sub> に対して小さくなる。つまり移動度が大きいほど V が大きく I<sub>ds</sub> の減少値は大きくなる。これにより移動度の異なる画素電流値は均一化され、移動度のばらつきを補正する事ができる。

30

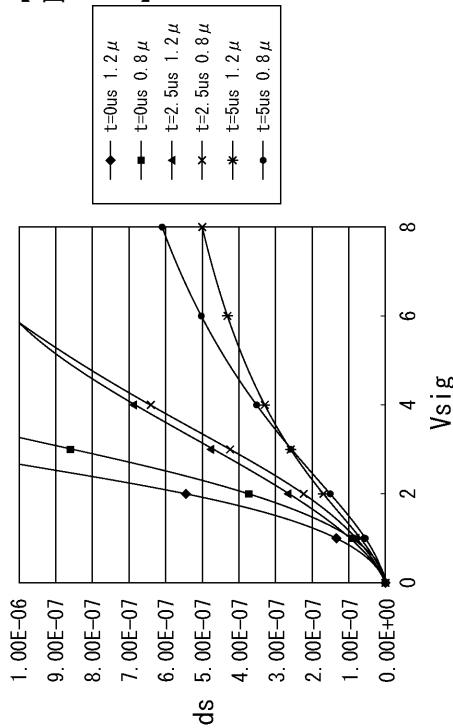

## 【0064】

以下参考の為図 11 を参照して、上述した移動度補正の数値解析を行う。図 11 に示すように、トランジスタ T<sub>r1</sub> 及び T<sub>r4</sub> がオンした状態で、ドライブトランジスタ T<sub>rd</sub> のソース電位を変数 V に取って解析を行う。ドライブトランジスタ T<sub>rd</sub> のソース電位 (S) を V とすると、ドライブトランジスタ T<sub>rd</sub> を流れるドレン電流 I<sub>ds</sub> は以下の式 3 に示す通りである。

40

## 【数 1】

$$I_{ds} = k \mu (V_{gs} - V_{th})^2 = k \mu (V_{sig} - V - V_{th})^2 \quad \text{式3}$$

50

## 【 0 0 6 5 】

またドレン電流  $I_{ds}$  と容量  $C$  ( $= C_s + C_{olead}$ ) の関係により、以下の式 4 に示す様に  $I_{ds} = dQ / dt = C dV / dt$  が成り立つ。

## 【 数 2 】

$$I_{ds} = \frac{dQ}{dt} = C \frac{dV}{dt} \quad \text{より} \quad \int \frac{1}{C} dt = \int \frac{1}{I_{ds}} dV \quad \text{式4}$$

$$\Leftrightarrow \int_0^t \frac{1}{C} dt = \int_{-V_{th}}^V \frac{1}{k \mu (V_{sig} - V_{th} - V)^2} dV$$

$$\Leftrightarrow \frac{k \mu}{C} t = \left[ \frac{1}{V_{sig} - V_{th} - V} \right]_{-V_{th}}^V = \frac{1}{V_{sig} - V_{th} - V} - \frac{1}{V_{sig}}$$

$$\Leftrightarrow V_{sig} - V_{th} - V = \frac{1}{\frac{1}{V_{sig}} + \frac{k \mu}{C} t} = \frac{V_{sig}}{1 + V_{sig} \frac{k \mu}{C} t}$$

10

## 【 0 0 6 6 】

式 4 に式 3 を代入して両辺積分する。ここで、ソース電圧  $V$  初期状態は  $-V_{th}$  あり、移動度ばらつき補正時間 ( $T_6 - T_7$ ) を  $t$  とする。この微分方程式を解くと、移動度補正時間  $t$  に対する画素電流が以下の数式 5 のように与えられる。

## 【 数 3 】

$$I_{ds} = k \mu \left( \frac{V_{sig}}{1 + V_{sig} \frac{k \mu}{C} t} \right)^2 \quad \text{式5}$$

20

## 【 0 0 6 7 】

図 12 は、式 5 をグラフ化した図であり、縦軸に出力電流  $I_{ds}$  を取り、横軸に映像信号  $Sig$  の信号電位  $V_{sig}$  を取ってある。パラメータとして移動度補正期間  $t = 0 \mu s$  、 $2.5 \mu s$  及び  $5 \mu s$  の場合を設定している。さらに、移動度  $\mu$  もパラメータとして比較的大きい場合  $1.2 \mu$  と比較的小さい場合  $0.8 \mu$  をパラメータにとってある。 $t = 0 \mu s$  として実質的に移動度補正をかけない場合に比べ、 $t = 2.5 \mu s$  では移動度ばらつきに対する補正が十分にかかっていることがわかる。移動度補正なしでは  $I_{ds}$  に 40 % のばらつきがあったものが、移動度補正をかけると 10 % 以下に抑えられる。但し  $t = 5 \mu s$  として補正期間を長くすると逆に移動度  $\mu$  の違いによる出力電流  $I_{ds}$  のばらつきが大きくなってしまう。この様に、適切な移動度補正を掛けるために、 $t$  は最適な値に設定する必要がある。図 12 に示したグラフの場合、最適値は  $t = 2.5 \mu s$  の近辺である。

30

## 【 0 0 6 8 】

以上のようにして、本発明ではゲート電圧を高電圧から低電圧に可変する事による  $V_{th}$  補正準備や、 $V_{th}$  補正動作を 1 H 以内に行い、その後同一水平走査期間内にて映像信号を書き込む。この動作により、従来必要であった 3 種類の電源を信号線に共有化することで電源ラインやスイッチングトランジスタ、そのゲートラインを削減する事ができ、3 トランジスタ 1 容量の画素回路を構成することができる。以上により、パネルの歩留まりを向上する事ができる。また、レイアウトを削減する事で高精細化も可能となる。なお本実施形態では、サンプリングトランジスタ  $T_r 1$  をオンした状態でスイッチングトランジスタ  $T_r 4$  をオンして移動度補正をかけているが、サンプリングトランジスタ  $T_r 1$  とスイッチングトランジスタ  $T_r 4$  をノンオーバーラップにして移動度補正を行わない単純な  $V_{th}$  補正動作においても、同様に配線やトランジスタの削減は可能である。

40

## 【 0 0 6 9 】

50

最後に、本発明にかかる表示装置の信号部（水平セレクタ）を構成するデータドライバにつき、その実施形態を説明する。本実施形態は、画像表示装置の列方向に配置され、画像データの表示に用いられるデータドライバにおいて、画像データを表す信号電位と画素回路制御用の固定電位を切り替えて出力する事を可能にし、且つこの画素回路制御用の固定電位が、一般的なデータドライバの最大定格電圧よりも高い電圧振幅を要求する場合、出力端子部分近くにある画像データ用信号電位と画素回路制御用固定電位を切り替えるスイッチ機能部分だけを高耐圧化する事で、ドライバの製造プロセスにおいて、高耐圧化プロセスへの変更、回路サイズの変更、端子の広ピッチ化等を必要としないまま、必要な機能を実現出来るものである。

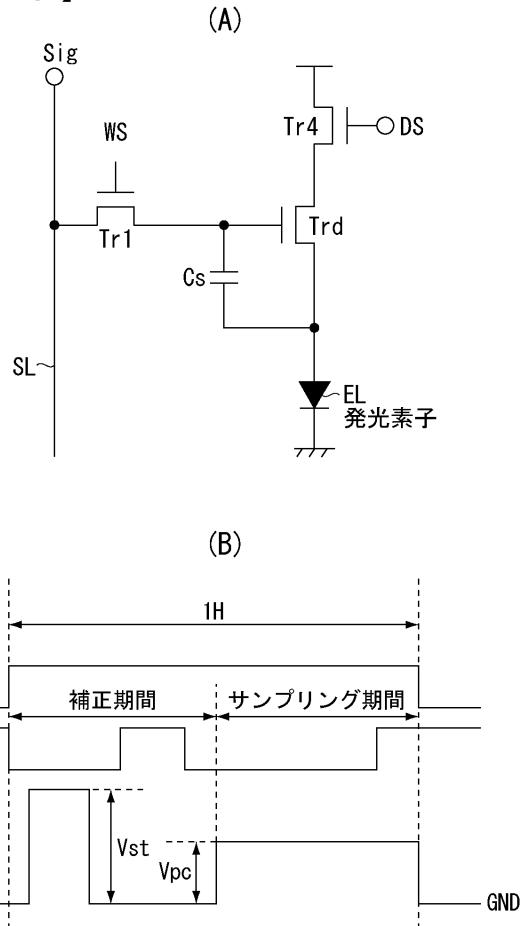

## 【0070】

10

図13にデータ信号線に画像データを表す信号電位と画素回路制御用の固定電位を混在させた画像表示装置の画素回路（A）と駆動波形（B）の例を示す。（A）に示した画素回路は、3個のトランジスタと1個の画素容量と、1個の発光素子ELとで構成されており、図5に示した本発明の実施形態にかかる画素回路を一般化したものである。映像信号Sigはデータ信号線SLから供給される。この映像信号の電圧値Vpcによって、ドライブトランジスタTrdを駆動し、所望の明るさで発光素子ELを発光させる。この画像表示装置においては、この際にドライブトランジスタTrdの特性ばらつきが直接画質に影響するため、画素容量Csを利用して、補正期間中にこのばらつきを補正する動作を行う。この補正動作を行う際に、走査パルスWAと走査パルスDSの駆動波形を利用してデータ信号線SLから制御用の固定電位Vstを画素回路に送り込む。通常の画像表示装置においては画像データ系の信号線と駆動制御系の信号線は分離されており、制御系の信号を入力する際には別な配線及び走査パルスを配置する。しかし、それによって画素回路内の素子数が増加すると、トランジスタ欠陥による歩留まり悪化や、一つの画素回路に必要とする面積が増える事から、物理的な解像度の低下等の悪影響が考えられるため、画素回路の素子数を極力少なくし、ドライブトランジスタTrdのばらつきを補正するためにはデータ信号線SLから、画像データに対応した信号電位Vpcと画素回路制御用の固定電位Vstをサンプリング時及び補正時に分けて送信する必要がある。

20

## 【0071】

この時、画素回路制御用の固定電圧Vstは必ずしも画像データの信号電圧Vpcと同一の範囲内にあるとは限らない。（B）の波形タイミングチャートの例のように、制御信号電圧Vstは画像信号電圧Vpcよりも高くなる場合が考えられ、且つVstはデータドライバICの定格電圧よりも高くなる場合もある。また、通常ドライバ出力は非表示期間には電圧不定（ハイインピーダンス）になるが、この画素回路の場合、VstとVpcはサンプリング期間と補正期間に分離され、その間の電圧はグランドレベルGNDに固定する事が必要となる場合がある。

30

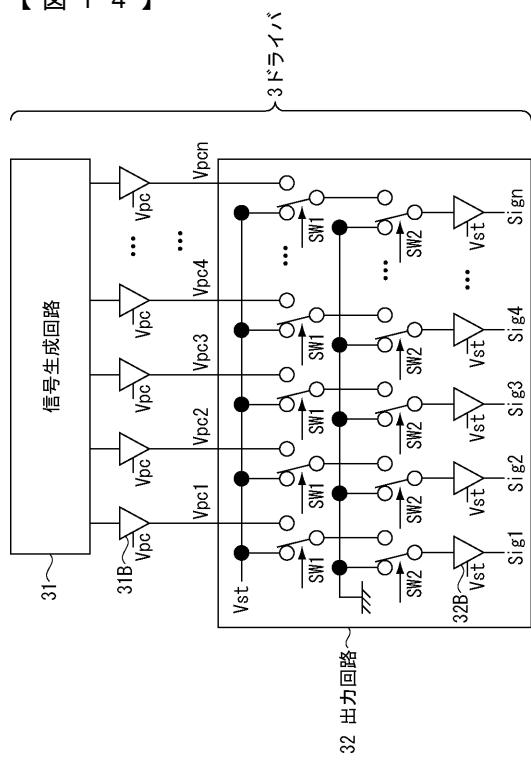

## 【0072】

このような駆動波形の条件を満たすデータドライバIC3のブロック構成を図14に示す。四角の実線で囲んだ部分が高耐圧の出力回路部32であり、この中の回路だけを配線膜厚を厚くする等して高耐圧化すれば、画像信号生成回路部31は通常通りの耐圧及びプロセスで作製可能である。出力回路部32は電圧切り替え用のスイッチSW1, SW2を含んでいる。但し、スイッチSW1の制御信号及びスイッチSW2の制御信号は、スイッチのON/OFFを制御するロジック信号であるため、高耐圧化の必要は無い。

40

## 【0073】

画像信号生成回路部31の出力端子31Bは、画像表示系電源電圧Vpcを最大電圧とする出力電圧Vpc1～Vpcnを出力する。この出力電圧は、スイッチSW1に送られ、画素回路制御用の固定電圧と切り替えられる。画素回路制御用の固定電圧は、制御系電源電圧Vstの振幅を持つロジックパルスである。またスイッチSW1の出力は、スイッチSW2に送られる。このスイッチSW2では、Vpc1～VpcnとVstの切り替え時に出力端をGNDレベルに固定するため、信号かGNDかの選択を行う。その結果、最終出力端32Bには最終出力信号Sigとして、制御系電源電圧を最大値とするVstま

50

たは画像表示系電源電圧を最大値とする  $V_{pc1} \sim V_{pcn}$ 、あるいは GND レベルの電圧が出力される。

## 【図面の簡単な説明】

【 0 0 7 4 】

【図1】表示装置の参考例を示すブロック図である。

【図2】図1に示した参考例の表示装置から1つの画素回路を切り取った模式図である。

【図3】図1及び図2に示した画素回路の動作説明に供するタイミングチャートである。

【図4】本発明にかかる表示装置の全体構成を示すブロック図である。

【図5】図4に示した表示装置に組み込まれる画素回路の構成例を示す回路図である。

【図6】図5に示した表示装置から1個の画素回路を切り取って示した模式図である。

【図7】図5及び図6に示した画素回路の動作説明に供するタイミングチャートである。

【図8】本発明にかかる表示装置の最も良の実施形態を示すタイミングチャートである。

【図9】本発明にかかる表示装置の動作説明に供する回路図である。

【図10】同じく動作説明に供するグラフである。

【図11】同じく動作説明に供する回路図である。

【図12】同じく動作説明に供するグラフである。

【図13】本発明にかかる表示装置に組み込まれるドライバICの動作説明に供する模式図である。

【図14】同じくドライバICの構成例を示す回路図である。

## 【 符号の説明 】

[ 0 0 7 5 ]

1 . . . 画素アレイ、2 . . . 画素回路、3 . . . 水平セレクタ（ドライバIC）、4 . . . ライトスキャナ、5 . . . ドライブスキャナ、Tr1 . . . サンプリングトランジスタ、Tr4 . . . スイッチングトランジスタ、Trd . . . ドライブトランジスタ、Cs . . . 画素容量、EL . . . 発光素子

( 1 )

( 义 2 )

10

【 図 3 】

【図5】

【 図 4 】

【图6】

$$I_{ds} = k \mu (V_{gs} - V_{th})^2 = k \mu (V_{sig} - \Delta V)^2$$

【図 1\_2】

【 図 1 3 】

【 図 1 4 】

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2007133284A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2007-05-31 |

| 申请号            | JP2005328336                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2005-11-14 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 内野勝秀<br>山下淳一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 内野 勝秀<br>山下 淳一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09G3/30 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| FI分类号          | G09G3/30.J G09G3/20.612.L G09G3/20.622.B G09G3/20.624.B G09G3/20.611.H G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/DD05 5C080/EE29 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C380/AA01 5C380/AB06 5C380/AB22 5C380/AB23 5C380/AB24 5C380/AB34 5C380/BA32 5C380/BA38 5C380/BA39 5C380/BB02 5C380/CA08 5C380/CA12 5C380/CA53 5C380/CB01 5C380/CB16 5C380/CB18 5C380/CB31 5C380/CC04 5C380/CC05 5C380/CC06 5C380/CC07 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC37 5C380/CC41 5C380/CC61 5C380/CC63 5C380/CC65 5C380/CD013 5C380/CD023 5C380/CE20 5C380/CF51 5C380/DA02 5C380/DA06 5C380/DA47 5C380/HA02 5C380/HA03 5C380/HA11 |         |            |

| 其他公开文献         | <a href="#">JP4923527B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

### 摘要(译)

要解决的问题：提供具有阈值电压校正功能的显示装置，其能够应对像素数量的增加和操作速率的更高频率。SOLUTION：显示装置包括像素阵列部分1，扫描仪部分4,5和信号部分3.每个像素2包含采样晶体管Tr1，像素电容器Cs，驱动晶体管Trd和连接的发光元件EL开关晶体管Tr4和将驱动晶体管Trd连接到电源的开关晶体管Tr4。驱动晶体管Trd根据输入电压Vgs将输出电流Ids提供给发光元件EL。输出电流Ids取决于驱动晶体管Trd的阈值电压Vth。扫描器部分4,5通过分时操作以利用校正量对像素电容器充电，以通过使用分配给相关像素2之前的行的多个水平扫描周期来消除驱动晶体管Trd的阈值电压。行。