(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-3744

(P2006-3744A)

(43) 公開日 平成18年1月5日(2006.1.5)

| (51) Int.CI.                | F 1                                              | テーマコード (参考) |

|-----------------------------|--------------------------------------------------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 J 3K007                                |             |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 621A 5C080                             |             |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 624B<br>G09G 3/20 641D<br>H05B 33/14 A |             |

審査請求 未請求 請求項の数 4 O L (全 22 頁)

|           |                              |          |                                                                       |

|-----------|------------------------------|----------|-----------------------------------------------------------------------|

| (21) 出願番号 | 特願2004-181655 (P2004-181655) | (71) 出願人 | 599142729<br>奇美電子股▲ふん▼有限公司<br>台湾台南県台南科学工業園区新市郷奇業路<br>1号               |

| (22) 出願日  | 平成16年6月18日 (2004.6.18)       | (71) 出願人 | 000006633<br>京セラ株式会社<br>京都府京都市伏見区竹田鳥羽殿町6番地                            |

|           |                              | (74) 代理人 | 100089118<br>弁理士 酒井 宏明                                                |

|           |                              | (72) 発明者 | 三和 宏一<br>神奈川県大和市下鶴間1623番地14<br>インターナショナル ディスプレイ テク<br>ノロジー株式会社 大和事業所内 |

最終頁に続く

(54) 【発明の名称】表示装置および表示装置の駆動方法

## (57) 【要約】

【課題】表示品位の低下を抑制しつつ画素回路と接続する配線構造の数を低減した表示装置を実現する。

【解決手段】画素回路1aは、有機EL素子3aと、有機EL素子3aに流れる電流を規定する薄膜トランジスタ4aと、コンデンサ5aと、薄膜トランジスタ4aの駆動状態を制御する第1スイッチング素子6aと、電荷蓄積工程および閾値電圧検出工程の際に機能する第2スイッチング素子7a、第3スイッチング素子8aとを備える。有機EL素子3aの陰極側と接続する陰極電位線17aは前段の画素回路1bと共に用する一方、第2スイッチング素子7a、第3スイッチング素子8aの駆動状態を制御する第1制御線18aおよび第2制御線19aは後段の画素回路1cと共に用する構成を有する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

行列状に複数配置され、それぞれが注入電流に応じた輝度で発光する発光素子と、該発光素子に流れる電流値を制御するトランジスタ素子とを備え、前記発光素子の発光に先立って、所定の静電容量に対して電荷を蓄積することによって前記トランジスタ素子のゲート・ソース間電圧の値を駆動閾値電圧よりも高い値に変化させる電荷蓄積動作と、ゲート・ソース間電圧を調整することによって前記トランジスタ素子のゲート・ソース間に駆動閾値電圧に対応した電圧の検出・供給動作とを行うよう形成された画素回路と、少なくとも該画素回路における電荷蓄積および駆動閾値電圧に対応した電圧の検出・供給のタイミングを制御するドライバ回路とを備えた表示装置であって、

前記ドライバ回路は、前記行列の第1行に対して一方の列方向に隣接した第2行に配置された画素回路に対して、前記電荷蓄積および前記電圧の検出・供給を前記第1行に配置された画素回路と同時に開始するよう制御し、前記第1行に対して他方の列方向に隣接した第3行に配置された画素回路に対して、前記電荷蓄積および前記電圧の検出・供給を前記第1行に配置された画素回路と同時に終了するよう制御することを特徴とする表示装置。

。

**【請求項 2】**

前記ドライバ回路は、前記第1行に配置された画素回路と前記第2行に配置された画素回路との間における前記電荷蓄積および前記電圧の検出・供給の終了タイミングの時間差と、前記第1行に配置された画素回路と前記第3行に配置された画素回路との間における前記電荷蓄積及び前記電圧の検出・供給の開始タイミングの時間差とが同一の値となるよう制御を行うことを特徴とする請求項1に記載の表示装置。

**【請求項 3】**

前記発光素子は、順方向に電圧を供給することによって電流が流れて発光し、逆方向に電圧を供給することによって供給電圧に応じた電荷を蓄積される特性を有し、前記電荷蓄積および前記電圧の検出・供給時に前記静電容量として機能することを特徴とする請求項1または2に記載の表示装置。

**【請求項 4】**

注入電流に応じた輝度で発光する発光素子と、該発光素子に流れる電流値を制御するトランジスタ素子とを備え、前記発光素子の発光に先立って、所定の静電容量に対して電荷を蓄積し、蓄積された電荷を用いて前記トランジスタ素子のゲート・ソース間に駆動閾値電圧に対応した電圧の検出・供給を行なうよう形成され、行列状に配置された複数の画素回路を備えた表示装置の駆動方法であって、

前記行列の第1行に対して一方の列方向に隣接した第2行に配置された画素回路に対して、前記電荷蓄積および前記電圧の検出・供給を前記第1行に配置された画素回路と同時に開始し、

前記第1行に対して他方の列方向に隣接した第3行に配置された画素回路に対して、前記電荷蓄積および前記電圧の検出・供給を前記第1行に配置された画素回路と同時に終了することを特徴とする表示装置の駆動方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、注入電流に応じた輝度で発光する発光素子と、該発光素子に流れる電流値を制御するトランジスタ素子とを備え、前記発光素子の発光に先立って、所定の静電容量に対して電荷を蓄積し、蓄積された電荷を用いて前記トランジスタ素子のゲート・ソース間に駆動閾値電圧に対応した電圧の検出および供給を行なうよう形成され、行列状に配置された複数の画素回路を備えた表示装置および表示装置の駆動方法に関するものである。

**【背景技術】****【0002】**

自ら発光する有機エレクトロルミネッセンス(EL)素子を用いた有機EL表示装置は

、液晶表示装置で必要なバックライトが不要で装置の薄型化に最適であるとともに、視野角にも制限がない。このため、液晶表示装置に替わる次世代の表示装置として実用化が期待されている。

### 【0003】

有機EL素子を用いた画像表示装置として、単純(パッシブ)マトリックス型とアクティブマトリックス型とが知られている。前者は構造が単純であるものの大型かつ高精細のディスプレイの実現が困難であるとの問題がある。このため、近年、画素内部の発光素子に流れる電流を、同時に画素内に設けた能動素子、たとえば、薄膜トランジスタ(Thin Film Transistor)からなるドライバ素子によって制御する、アクティブマトリックス型の表示装置の開発が盛んに行われている(例えば、特許文献1参照。)。

10

### 【0004】

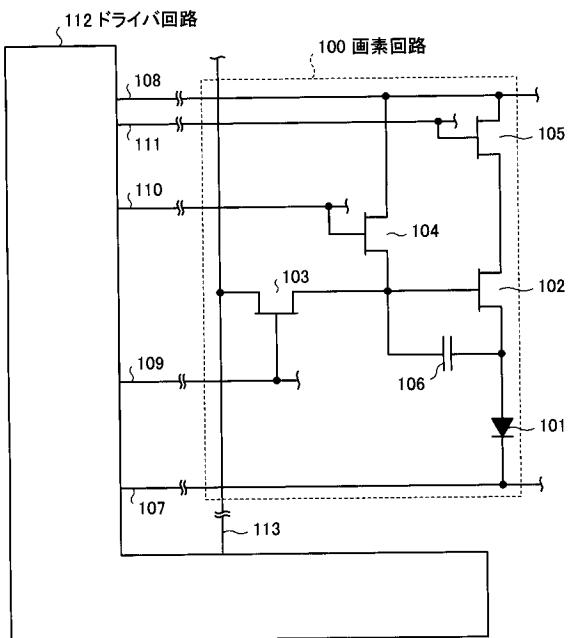

図7は、従来の画像表示装置における单一画素(カラー表示の場合には1画素中のR、G、Bのいずれかに対応した副画素、以下同様とする。)に対応した画素回路の構成を示す回路図である。図7に示すように、画素回路100は、発光素子として機能する有機EL素子101と、有機EL素子101に流れる電流値を規定するためのドライバ素子102と、ドライバ素子102の駆動状態を制御するための第1スイッチング素子103と、後述する閾値電圧検出の際に機能する第2スイッチング素子104および第3スイッチング素子105と、ドライバ素子102のゲート電極とソース電極との間に配置されたコンデンサ106とを備える。また、従来の表示装置は、これらの回路素子に対して、図7にも示すように低電位供給線107、高電位供給線108、走査線109および第1制御線110第2制御線111および信号線113を介してドライバ回路112から駆動制御用の電気信号が供給される構成を有する。

20

### 【0005】

ドライバ回路112は、画素回路100に備わる回路素子の駆動状態を制御する電気信号を供給するためのものである。具体的には、画素回路100に備わる各回路素子は、ドライバ素子102の駆動閾値電圧をあらかじめ供給する機能と、駆動閾値電圧の供給に先立ち有機EL素子101に対して所定の電荷を蓄積する機能と、ドライバ素子102に対して、有機EL素子101の表示階調に応じた電位を供給する機能と、有機EL素子101の陽極・陰極間に電圧を供給して有機EL素子101を表示階調に応じた輝度で発光させる機能とを有する。これらの機能を実現するにあたって、ドライバ回路112は、低電位供給線107等を介して所定の電気信号を供給している。

30

### 【0006】

【特許文献1】特開2002-196357号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

### 【0007】

しかしながら、従来の有機EL素子を用いた表示装置は、ドライバ回路112から延伸する配線構造の本数が多いために、各画素の開口率を向上させることが困難であるという問題を有する。以下、かかる問題点について詳細に説明する。

40

### 【0008】

従来の表示装置は、行列状に複数の画素回路100が配列された構成を有し、かかる複数の画素回路100のそれぞれにおいて、ドライバ素子102の駆動閾値電圧の供給等が行われることとなる。ここで、従来の表示装置は、同一列に配置された画素回路に対して同一の信号線113を介して順次データ電圧の供給を行う構成を有する関係上、同一行に配置された画素回路100に対しては同時に駆動閾値電圧の供給等を行つ一方で、異なる行に配置された画素回路100に対しては、データ電圧の供給に対応して互いに異なるタイミングで駆動閾値電圧の供給等を行う構成を有する。

### 【0009】

従つて、従来の表示装置では、異なる行に配置された画素回路100に対してそれぞれ別個独立に電気信号を供給する構造を採用する必要があり、具体的には、複数の画素回路

50

100によって構成される行列の行数に応じた本数の低電位供給線107～第2制御線111が必要となる。そして、低電位供給線107～第2制御線111のそれぞれは、同一列に配置されたすべての画素回路100に対して電気信号を供給するために、画素回路100が行列状に配置されるアレイ基板の一方の端部から他方の端部まで列方向に延伸した構成を有する。

#### 【0010】

このため、アレイ基板上におけるこれらの配線構造の占有面積は非常に大きなものとなり、配線構造の占有面積が増加するにつれて、各画素回路100が備える有機EL素子011の発光面の占有面積が相対的に減少することから、開口率を増加させることが困難となる。一方で、異なる列に配置された画素回路100に対して電気信号を供給する低電位供給線107等を単純に共通化した場合には開口率の向上が可能であるが、ドライバ素子102に供給される駆動閾値電圧の値がばらつく等により表示画像の画質が低下するという問題が新たに生じることとなる。

#### 【0011】

本発明は、上記に鑑みてなされたものであって、表示品位の低下を抑制しつつ画素回路と接続する配線構造の数を低減した表示装置を実現することを目的とする。

#### 【課題を解決するための手段】

#### 【0012】

上述した課題を解決し、目的を達成するために、請求項1にかかる表示装置は、行列状に複数配置され、それぞれが注入電流に応じた輝度で発光する発光素子と、該発光素子に流れる電流値を制御するトランジスタ素子とを備え、前記発光素子の発光に先立って、所定の静電容量に対して電荷を蓄積することによって前記トランジスタ素子のゲート・ソース間電圧の値を駆動閾値電圧よりも高い値に変化させる電荷蓄積動作と、蓄積された前記電荷の量を調整することによって前記トランジスタ素子のゲート・ソース間に駆動閾値電圧に対応した電圧の検出・供給動作を行うよう形成された画素回路と、少なくとも該画素回路における電荷蓄積および駆動閾値電圧に対応した電圧の検出・供給のタイミングを制御するドライバ回路とを備えた表示装置であって、前記ドライバ回路は、前記行列の第1行に対して一方の列方向に隣接した第2行に配置された画素回路に対して、前記電荷蓄積および前記電圧の検出・供給を前記第1行に配置された画素回路と同時に開始するよう制御し、前記第1行に対して他方の列方向に隣接した第3行に配置された画素回路に対して、前記電荷蓄積および前記電圧の検出・供給を前記第1行に配置された画素回路と同時に終了するよう制御することを特徴とする。

#### 【0013】

この請求項1の発明によれば、第1行に配置された画素回路と第2行に配置された画素回路との間で電荷蓄積の開始タイミングおよび閾値電圧に対応した電圧の検出・供給の開始タイミングを同時にし、第1行に配置された画素回路と第3行に配置された画素回路との間で電荷蓄積の終了タイミングおよび閾値電圧に対応した電圧の検出・供給の終了タイミングを同時にすることで、画素回路に対して各工程の開始、終了タイミングを規定する電気信号を伝送する配線構造を低減することが可能である。また、かかる態様でタイミングを規定することによって、隣接画素回路間で、一方の画素回路における電荷蓄積に要する時間長の増減と、電圧の検出・供給に要する時間長の増減が等しくなる。従って、例えば電荷蓄積に要する時間長の増加または減少に起因したトランジスタ素子のソース電位の変化量と、電圧の検出・供給に要する時間長の増加または減少に起因したトランジスタ素子のソース電位の変化量とが相殺されることとなり、全体としてゲート・ソース間電圧の変動幅を抑制することが可能である。

#### 【0014】

また、請求項2にかかる表示装置は、上記の発明において、前記ドライバ回路は、前記第1行に配置された画素回路と前記第2行に配置された画素回路との間における前記電荷蓄積および前記電圧の検出・供給の終了タイミングの時間差と、前記第1行に配置された画素回路と前記第3行に配置された画素回路との間における前記電荷蓄積及び前記電圧の

検出・供給の開始タイミングの時間差とが同一の値となるよう制御を行うことを特徴とする。

#### 【0015】

また、請求項3にかかる表示装置は、上記の発明において、前記発光素子は、順方向に電圧を供給することによって電流が流れて発光し、逆方向に電圧を供給することによって供給電圧に応じた電荷を蓄積される特性を有し、前記電荷蓄積および前記電圧の検出・供給時に前記静電容量として機能することを特徴とする。

#### 【0016】

また、請求項4にかかる表示装置の駆動方法は、注入電流に応じた輝度で発光する発光素子と、該発光素子に流れる電流値を制御するトランジスタ素子とを備え、前記発光素子の発光に先立って、所定の静電容量に対して電荷を蓄積し、蓄積された電荷を用いて前記トランジスタ素子のゲート・ソース間に駆動閾値電圧に対応した電圧の検出・供給を行うよう形成され、行列状に配置された複数の画素回路を備えた表示装置の駆動方法であって、前記行列の第1行に対して一方の列方向に隣接した第2行に配置された画素回路に対して、前記電荷蓄積および前記電圧の検出・供給を前記第1行に配置された画素回路と同時に開始し、前記第1行に対して他方の列方向に隣接した第3行に配置された画素回路に対して、前記電荷蓄積および前記電圧の検出・供給を前記第1行に配置された画素回路と同時に終了することを特徴とする。10

#### 【発明の効果】

#### 【0017】

本発明にかかる表示装置および表示装置の駆動方法は、第1行に配置された画素回路と第2行に配置された画素回路との間で電荷蓄積の開始タイミングおよび閾値電圧に対応した電圧の検出・供給の開始タイミングを同時にし、第1行に配置された画素回路と第3行に配置された画素回路との間で電荷蓄積の終了タイミングおよび閾値電圧に対応した電圧の検出・供給の終了タイミングを同時にすることで、画素回路に対して各工程の開始、終了タイミングを規定する電気信号を伝送する配線構造を低減することが可能である。また、かかる態様でタイミングを規定することによって、隣接画素回路間で、一方の画素回路における電荷蓄積に要する時間長の増減と、電圧の検出・供給に要する時間長の増減が等しくなる。従って、例えば電荷蓄積に要する時間長の増加または減少に起因したトランジスタ素子のソース電位の変化量と、電圧の検出・供給に要する時間長の増加または減少に起因したトランジスタ素子のソース電位の変化量とが相殺されることとなり、全体としてゲート・ソース間電圧の変動幅を抑制することが可能である。従って、請求項1の発明によれば、画素回路に対して電気信号を供給する配線構造の本数を低減したにもかかわらず、異なる行に配置された画素回路間におけるゲート・ソース間電圧の変動幅を抑制し、表示品位の低下を抑制できるという効果を奏する。20

#### 【発明を実施するための最良の形態】

#### 【0018】

以下に、本発明にかかる表示装置を実施するための最良の形態（以下、「実施の形態」と称する）について図面を参照しつつ説明を行う。なお、図面は模式的なものであって現実のものとは異なることに留意すべきであり、図面の相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。また、以下で言及する薄膜トランジスタは、nチャンネルのものとして説明するが、pチャンネルのものに本発明を適用可能なことは言うまでもない。さらに、以下の説明においては、薄膜トランジスタについて、ゲート電極以外の電極構造は、ソース電極およびドレイン電極のいずれとしても機能させることができある場合には、ソース／ドレイン電極と称することとする。40

#### 【0019】

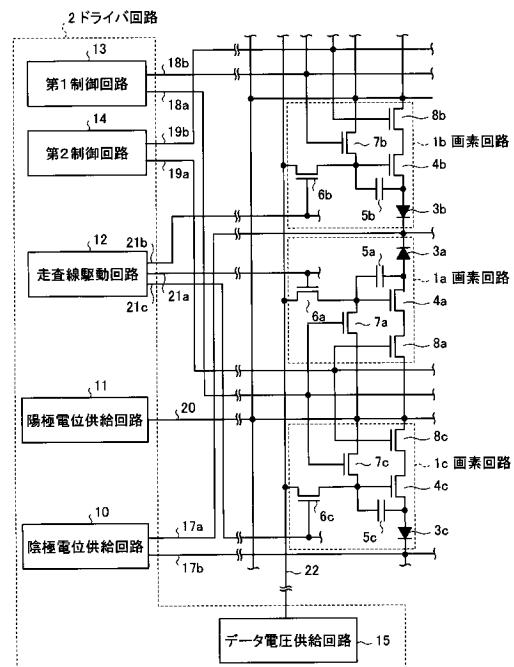

本実施の形態にかかる表示装置は、画素回路が行列状に配置された表示装置であって、異なる行に配置された画素回路に供給される電気信号を供給する配線構造のいくつかを共用した構成を有し、配線構造の共用態様等を工夫することによって、表示画像の品位の低下を視認不可能な程度に抑制しつつ、開口率を向上させた表示装置である。図1は、本実50

施の形態にかかる表示装置の構成を示す模式図である。なお、図1に示した画素回路は、表示画像の画素数に対応して行列状に多数配置されるものであって、画素回路の個数等について、図1に示すものに限定して解釈する必要はない。

#### 【0020】

本実施の形態にかかる表示装置は、図1に示すように、行列状に複数配置された画素回路1と、画素回路1に対して所定の電気信号を供給するドライバ回路2とを備える。なお、図1においては、M行N列（M，N：整数）の行列状に配置された多数の画素回路1のうち、m行n列（m：1 < n Mを満たす整数、n：N以下の整数）に位置する画素回路1aと、（m - 1）行n列に位置する画素回路1bと、（m + 1）行n列に位置する画素回路1cとについて示している。

10

#### 【0021】

次に、画素回路1の構造について説明する。本実施の形態において、画素回路1a～画素回路1cはそれぞれ同一の構造を有することから、以下では画素回路1aを例に説明する。画素回路1aは、注入電流に応じて発光する有機EL素子3aと、ソース電極が有機EL素子3aの陽極と接続され、有機EL素子3aに流れる電流量を制御するドライバ素子として機能する薄膜トランジスタ4aと、薄膜トランジスタ4aのゲート電極およびソース電極と接続されたコンデンサ5aとを備える。また、画素回路1aは、薄膜トランジスタ4aの駆動状態を制御する第1スイッチング素子6aと、後述する電荷蓄積工程および閾値電圧検出工程の際に機能する第2スイッチング素子7aおよび第2スイッチング素子8aとを備える。

20

#### 【0022】

有機EL素子3aは、特許請求の範囲における発光素子および静電容量として機能するものであり、順方向に電圧が印加されることによって電流が流れ発光するとともに、逆方向に電圧が印加された際にコンデンサとして機能するものである。有機EL素子3aは、具体的にはアノード層、発光層およびカソード層が順次積層された構造を有する。発光層は、カソード層側から注入された電子と、アノード層側から注入された正孔とが発光再結合するためのものであり、具体的にはフタルシアニン、トリスアルミニウム錯体、ベンゾキノリノラト、ベリリウム錯体等の有機系の材料によって形成され、必要に応じて所定の不純物が添加された構造を有する。なお、発光層に対してアノード側に正孔輸送層を設け、発光層に対してカソード側に電子輸送層を設けた構造としても良い。

30

#### 【0023】

薄膜トランジスタ4aは、ドライバ素子として機能するものであり、特許請求の範囲におけるトランジスタ素子として機能するものである。薄膜トランジスタ4aは、図1に示すようにソース電極が有機EL素子3aの陽極と接続されており、ゲート電極に印加される電圧に応じて有機EL素子3aに流れる電流値を制御することによって、有機EL素子3aの発光輝度を制御している。

40

#### 【0024】

第1スイッチング素子6aは、薄膜トランジスタ4aのゲート電極とデータ電圧供給回路15（後述）との間の電気的接続状態を制御するためのものである。具体的には、第1スイッチング素子6aは、後述するデータ電圧書き込み工程の際にデータ電圧供給回路15と薄膜トランジスタ4aのゲート電極とを電気的に接続し、データ電圧供給回路15から出力されるデータ電圧が薄膜トランジスタ4aのゲート電極に供給されるよう制御する。なお、第1スイッチング素子6aは、具体的には例えば薄膜トランジスタによって形成され、ゲート電極は、後述する走査線駆動回路12と電気的に接続されている。かかる構成を有することによって、第1スイッチング素子6aは、走査線駆動回路12から供給される電気信号によって導通状態を制御する構成を備えている。

40

#### 【0025】

第2スイッチング素子7aは、薄膜トランジスタ4aのゲート電極と陽極電位供給回路11（後述）との間の電気的接続状態を制御するためのものであり、第3スイッチング素子8aは、薄膜トランジスタ4aのドレイン電極と陽極電位供給回路11との間の電気的

50

接続状態を制御するためのものである。第2スイッチング素子7aおよび第2スイッチング素子8aは、具体的には、後述する電荷蓄積工程および閾値電圧工程において機能するものであり、それぞれ後述する第1制御回路13および第2制御回路14の制御によって動作する。なお、第2スイッチング素子7aおよび第3スイッチング素子8aは、第1スイッチング素子6aと同様に例えば薄膜トランジスタによって形成され、ゲート電極に対して第1制御回路13等からの電気信号を供給されることによって動作する構成を有する。

#### 【0026】

次に、ドライバ回路2について説明する。ドライバ回路2は、画素回路1に対して所定の電気信号を供給することによって、画素回路1に備わる有機EL素子3の発光状態等を制御するためのものである。ドライバ回路2は、複数の回路によって構成されており、具体的には、有機EL素子3の陰極側の電位を供給する陰極電位供給回路10と、有機EL素子3の陽極側の電位を供給する陽極電位供給回路11と、画素回路1に備わる第1スイッチング素子6の駆動状態を制御する走査線駆動回路12と、第2スイッチング素子7の駆動状態を制御する第1制御回路13と、第3スイッチング素子8の駆動状態を制御する第2制御回路14と、表示階調に応じたデータ電圧を供給するデータ電圧供給回路15とを備える。

#### 【0027】

陰極電位供給回路10は、有機EL素子3の陰極側の電位を制御するためのものである。陰極電位供給回路10は、陽極電位供給回路11から供給される電位よりも低い電位を有機EL素子3の陰極に供給することによって有機EL素子3に対して順方向の電圧を供給して発光させる機能を有する他に、後述する電荷蓄積工程および閾値電圧検出工程において供給電位を変化させることによって所定の役割を果たしている。電荷蓄積工程等の際における機能については後に説明する。

#### 【0028】

陽極電位供給回路11は、有機EL素子3の陽極側の電位を制御するためのものである。具体的には、陽極電位供給回路11は、薄膜トランジスタ4および第3スイッチング素子8を介して有機EL素子3の陽極と電気的に接続され、薄膜トランジスタ4および第3スイッチング素子8がオン状態の際に有機EL素子3の陽極に対して電位を供給している。なお、本実施の形態においては、陽極電位供給回路11は、ドライバ回路2に備わる他の回路と異なり、常に一定電位を供給するよう構成されている。

#### 【0029】

走査線駆動回路12は、画素回路1に備わる第1スイッチング素子6の駆動を制御するためのものである。具体的には、走査線駆動回路12は、画素回路1に備わる第1スイッチング素子6に対して、所定の走査用の電気信号を出力することによって、第1スイッチング素子6のオン・オフを制御している。

#### 【0030】

第1制御回路13は、画素回路1に備わる第2スイッチング素子7の駆動を制御するためのものであり、第2制御回路14は、第3スイッチング素子8の駆動を制御するためのものである。後述するように、第2スイッチング素子7および第3スイッチング素子8は、電荷蓄積工程および閾値電圧検出工程において所定の機能を果たすべく動作するものであり、第1制御回路13および第2制御回路14は、所定の電気信号を出力することによって、第2スイッチング素子7および第3スイッチング素子8のオン・オフのタイミングを制御する機能を有する。

#### 【0031】

データ電圧供給回路15は、画素回路1に備わる有機EL素子3の発光輝度に対応したデータ電圧を出力するためのものである。すなわち、有機EL素子3は、ドライバ素子として機能する薄膜トランジスタ4によって注入電流値が制御されるのであるが、薄膜トランジスタ4は、ゲート・ソース間電圧の値に応じてドレイン・ソース間に流れる電流値が決定される特性を有する。有機EL素子3には薄膜トランジスタ4のドレイン・ソース間

10

20

30

40

50

を通過した電流が供給されることから、薄膜トランジスタ4のゲート・ソース間電圧を制御することによって、有機EL素子3に流れる電流値を制御することが可能であり、電流値を制御することによって有機EL素子3の発光輝度を制御することが可能である。データ電圧供給回路15は、かかる薄膜トランジスタ4のゲート・ソース間電圧を規定するデータ電圧を出力する機能を有する。

#### 【0032】

次に、画素回路1に備わる構成要素と、ドライバ回路2との電気的な接続様について説明する。すなわち、ドライバ回路2に備わる各回路と、画素回路1に備わる各構成要素との関係は上述したとおりであって、例えば第1スイッチング素子6に関しては、画素回路1a～画素回路1cのそれぞれに備わる第2スイッチング素子7a～第2スイッチング素子7cのいずれに関しても、第1制御回路13から供給される電気信号によって駆動状態が制御され、画素回路1a～画素回路1cにおいてそれぞれ同様の機能を果たすべく動作するものである。

#### 【0033】

しかしながら、画素回路1に備わる各構成要素は、機能は同一であっても動作タイミングに関しては同一となるとは限らず、異なる画素回路1において同一の電気信号が供給される場合もあれば、異なる電気信号が供給される場合もある。具体的には、図1に示す態様によって画素回路1a～画素回路1cとドライバ回路2とを電気的に接続する構成とすることで、後述するように表示画像の品位の低下を視認不可能な程度に抑制しつつ、画素回路1と接続する配線構造の本数を低減することとしている。以下、ドライバ回路2に備わる各回路に関して、画素回路1a～画素回路1cとの接続態様を具体的に説明する。

#### 【0034】

陰極電位供給回路10は、画素回路1a、画素回路1bとは同一の配線構造を介して接続する一方で、画素回路1cに対しては異なる配線構造を介して電気的に接続している。すなわち、図1にも示すように、陰極電位供給回路10からは互いに異なる電気信号を伝送する陰極電位線17aおよび陰極電位線17bが延伸しており、陰極電位線17aは、画素回路1aに備わる有機EL素子3aの陰極と、画素回路1bに備わる有機EL素子3bの陰極と接続されている。これに対して、陰極電位線17bは、画素回路1cに備わる有機EL素子3cの陰極と接続されており、画素回路1a、画素回路1bに備わる有機EL素子3a、有機EL素子3bの陰極に供給される電気信号と、画素回路1cに備わる有機EL素子3cの陰極に供給される電気信号とは異なるものとなる。

#### 【0035】

一方で、第1制御回路13は、陰極電位供給回路10とは異なる接続態様を有する。具体的には、第1制御回路13は、画素回路1a、画素回路1cとは同一の配線構造を介して接続する一方で、画素回路1bに対しては異なる配線構造を介して電気的に接続している。すなわち、第1制御回路13からは、互いに異なる電気信号を伝送する第1制御線18aと第1制御線18bとが延伸しており、第1制御線18aは、画素回路1aに備わる第2スイッチング素子7aのゲート電極および画素回路1cに備わる第2スイッチング素子7cのゲート電極に接続されている。これに対して、第1制御線18bは、画素回路1bに備わる第2スイッチング素子7bのゲート電極に接続されており、画素回路1aおよび画素回路1cに備わる第2スイッチング素子7aおよび第2スイッチング素子7cのゲート電極に供給される電気信号と、画素回路1bに備わる第2スイッチング素子7bのゲート電極に供給される電気信号とは異なるものとなる。

#### 【0036】

第2制御回路14は、第1制御回路13と同様の接続態様を有し、陰極電位供給回路10と異なる接続態様を有する。すなわち、第2制御回路14からは第2制御線19aおよび第2制御線19bが延伸し、第2制御線19aは、画素回路1aに備わる第3スイッチング素子8aのゲート電極および画素回路1cに備わる第3スイッチング素子8cのゲート電極と接続し、第2制御線19bは、画素回路1bに備わる第3スイッチング素子8bのゲート電極と接続する。

10

20

30

40

50

## 【0037】

陽極電位供給回路11および走査線駆動回路12は、上記の回路と異なる接続様を有する。すなわち、陽極電位供給回路11は、単一の陽極電位線20を介して画素回路1a～画素回路1cにそれぞれ備わる第3スイッチング素子8a～第3スイッチング素子8cのドレイン電極と接続する。かかる接続様としたのは、陽極電位供給回路11が本実施の形態において電位変化のない一定電位を供給する構成を有するためである。また、走査線駆動回路12に関しては、画素回路1a～1cに対するデータ電圧の供給は、同一の信号線22を介して行う構成を有するため、画素回路1a～1cのそれぞれに対して異なるデータ電圧を供給するためには第1スイッチング素子6a～6cをそれぞれ異なるタイミングでオン状態にする必要があるためである。

10

## 【0038】

次に、本実施の形態にかかる表示装置の動作について説明する。以下では、まず画素回路1aを例にして、個々の画素回路1とドライバ回路2に備わる各回路との関係に注目した单一画素回路の動作について説明した後、ドライバ回路2との接続様の相違に基づく画素回路1a～画素回路1cの動作の相互の関係について説明する。

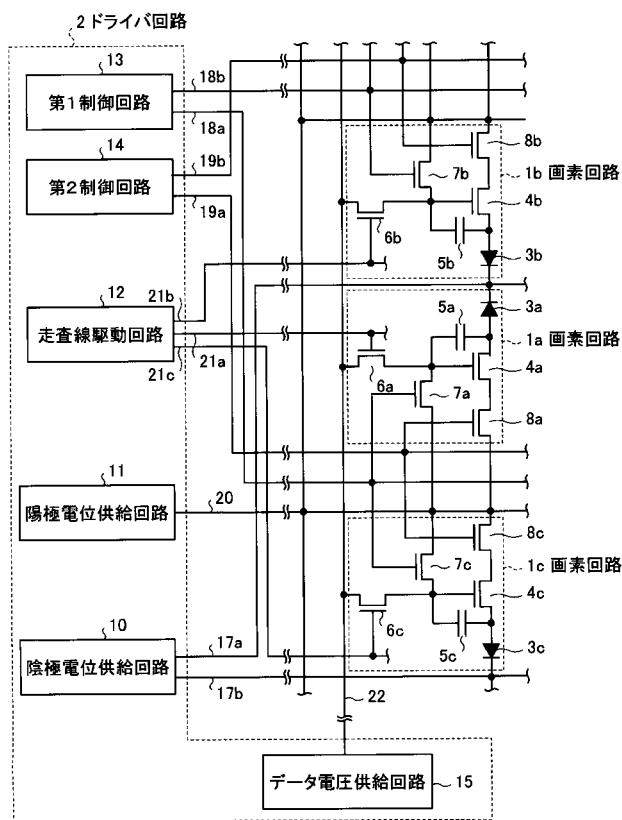

## 【0039】

まず、画素回路1の動作について、画素回路1aを例に説明する。図2は、画素回路1aに対してドライバ回路2に備わるから供給される電気信号の時間変化と、かかる電気信号の供給に基づく薄膜トランジスタ4aのソース電極（有機EL素子3aの陽極と接続する電極）の電位の時間変化を示すタイミングチャートである。以下、図2を参照しつつ画素回路1aの動作を説明する。

20

## 【0040】

画素回路1の動作は、具体的には有機EL素子3aに対して逆電圧を供給して電荷を蓄積させる電荷蓄積工程と、蓄積された電荷を用いて、薄膜トランジスタ4aのゲート・ソース間の駆動閾値電圧の検出・書きを行う閾値電圧検出工程と、薄膜トランジスタ4aのゲート・ソース間に表示輝度に対応したデータ電圧の書きを行うデータ電圧書き工程と、書き込まれたデータ電圧に応じた電流を有機EL素子3aに供給し、所定の輝度で発光させる発光工程とによって構成される。具体的は、図2に示すように、時間長t<sub>1</sub>に渡って電荷蓄積工程が行われ、時間長t<sub>2</sub>に渡って閾値電圧検出工程が行われ、時間長t<sub>3</sub>に渡ってデータ電圧書き工程が行われ、時間長t<sub>4</sub>に渡って発光工程が行われる。以下、各工程について簡単に説明する。

30

## 【0041】

電荷蓄積工程は、有機EL素子3aに対して逆電圧を供給することによって、有機EL素子3aをコンデンサとして機能させ、所定量の電荷を蓄積する工程である。具体的には、陰極電位線17aの電位が陽極電位線20の電位よりも高い値に変化することによって有機EL素子3aに対して逆電圧が供給され、電荷蓄積工程が開始される。また、本工程では第2制御線19aの電位がHighに変化することによって第3スイッチング素子8aがオン状態に変化し、第1制御線18aの電位がLowを維持することによって第2スイッチング素子7aがオフ状態を維持する。また、走査線21aの電位はLowを維持するため、第1スイッチング素子6aもオフ状態を維持する。

40

## 【0042】

かかる状態を維持することによって、有機EL素子3aの陰極側には正電荷が蓄積される一方、陽極側には負電荷が蓄積され、薄膜トランジスタ4aのソース電位は図2に示す通り徐々に低下する。

## 【0043】

電荷蓄積工程完了時においては、薄膜トランジスタ4aのゲート・ソース間電圧は、駆動閾値電圧よりも高い値となっており、薄膜トランジスタ4aはオン状態となっている。そして、第1制御線18aの電位がHighに変化することによって、電荷蓄積工程は完了することとなり、時間長t<sub>1</sub>に渡って行われた電荷の蓄積が終了する。

## 【0044】

50

そして、閾値電圧検出工程が行われる。閾値電圧検出工程は、薄膜トランジスタ4aのゲート・ソース間ににおける駆動閾値電圧の検出・供給を行う工程である。具体的には、図2に示すように、陰極電位線17aの電位が0電位に低下することによって、閾値電圧検出工程が開始される。また、本工程では、第1制御線18aおよび第2制御線19aの電位はHighに維持され、第2スイッチング素子7aおよび第3スイッチング素子8aはオン状態に維持されている。また、走査線21aの電位はLowに維持されていることから、第1スイッチング素子6aはオフ状態に維持されている。

#### 【0045】

従って、薄膜トランジスタ4aのゲート電極は、信号線22と電気的に絶縁される一方で、第2スイッチング素子7a、第3スイッチング素子8aを介して薄膜トランジスタ4aのドレイン電極と接続される。そして、薄膜トランジスタ4aはオン状態となっていることから、薄膜トランジスタ4aのドレイン・ソース間は形成されるチャンネルによって導通している。結果として、薄膜トランジスタ4aのゲート電極とソース電極との間が導通し、ゲート電極に蓄積された正電荷がソース電極(=有機EL素子3aの陽極)に対して徐々に供給され、電荷蓄積工程において蓄積された負電荷が相殺されることによって、ソース電極の電位が徐々に上昇する。従って、薄膜トランジスタ4aのゲート・ソース間電圧は徐々に低下し、駆動閾値電圧に徐々に近づくこととなり、具体的にはゲート・ソース間電圧は、 $V_2 (< 0)$ だけ変化する。

#### 【0046】

かかる閾値電圧検出工程は、第1制御線18aおよび第2制御線19aの電位がLowに変化することによって終了する。すなわち、第1制御線18aおよび第2制御線19aの電位がLowに変化することによって、第2スイッチング素子7aおよび第3スイッチング素子8aがオフ状態に変化し、薄膜トランジスタ4aのゲート電極と陽極電位線20との間が電気的に絶縁され、正電荷の供給が停止する。従って、ゲート・ソース間電圧の変化が停止され、かかる時点におけるゲート・ソース間電圧が駆動閾値電圧として薄膜トランジスタ4aのゲート・ソース間に保持される。

#### 【0047】

その後、データ電圧書込工程および発光工程が行われる。すなわち、第1制御線18aおよび第2制御線19aの電位がLowに維持された状態で、走査線21aの電位がHighに変化する。従って、薄膜トランジスタ4aのゲート電極は、第1スイッチング素子6aを介して信号線22と接続される一方、第2スイッチング素子7a等がオフ状態であることによって、信号線22以外とは絶縁された状態となる。このため、薄膜トランジスタ4aのゲート電極には、新たにデータ電圧供給回路15から出力されたデータ電圧が供給されることとなる。従って、薄膜トランジスタ4aのゲート・ソース間には、閾値電圧検出工程で供給された閾値電圧と、新たに加えられたデータ電圧との加算値に対応した電圧が書き込まれることとなる。そして、発光工程において、かかる電圧が書き込まれた薄膜トランジスタ4aによって制御された電流が有機EL素子3aに流れ、有機EL素子3aが所定の輝度で発光する。

#### 【0048】

以上のように、画素回路1aでは、陰極電位線17aの電位変化によって電荷蓄積工程および閾値電圧検出工程の開始タイミングが制御され、第1制御線18aおよび第2制御線19aの電位変化によって電荷蓄積工程および閾値電圧検出工程の終了タイミングが制御されている。かかる制御によって、時間長 $t_1$ に渡って電荷蓄積工程が行われ、時間長 $t_2$ に渡って閾値電圧検出工程が行われる。そして、電荷蓄積工程においては、薄膜トランジスタ4aのソース電位 $V_1$ は所定値だけ変化し、閾値電圧検出工程においては、薄膜トランジスタ4aのソース電位 $V_2$ も所定値だけ変化している。

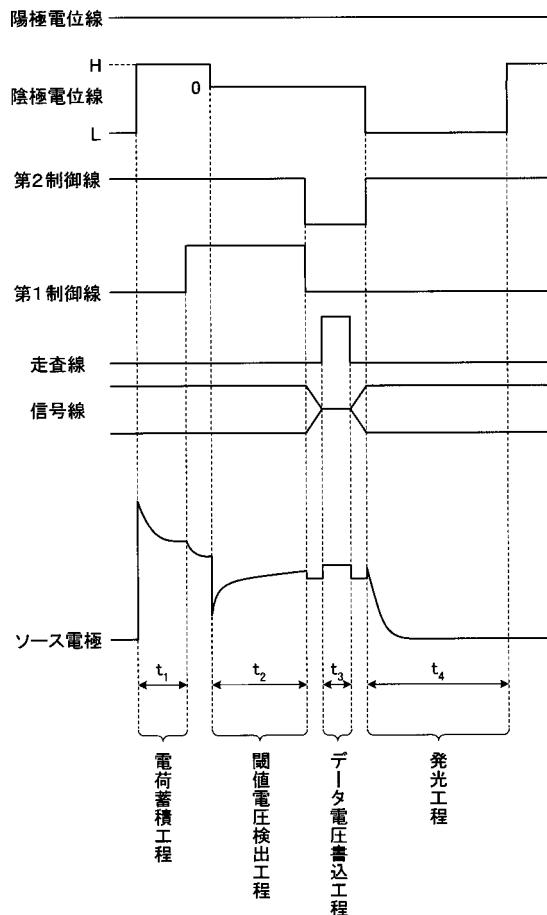

#### 【0049】

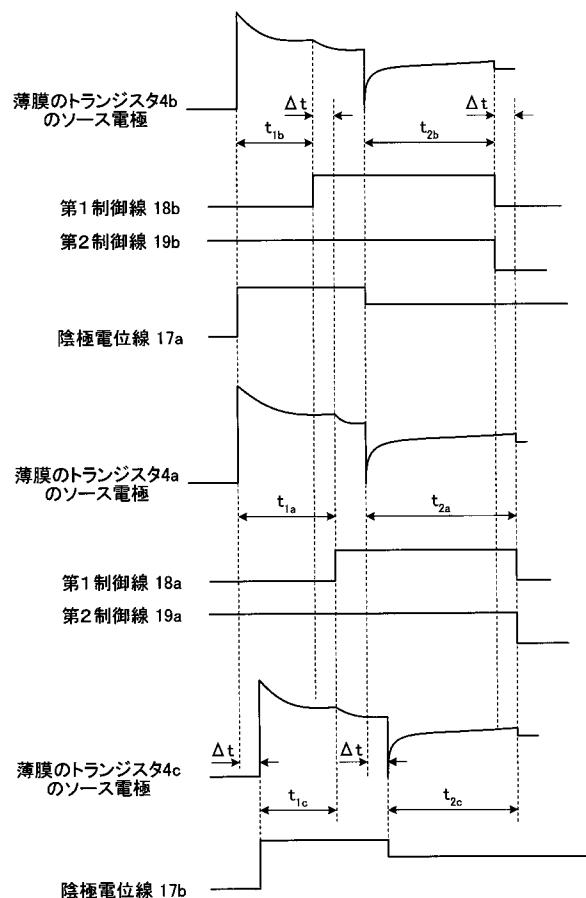

次に、電荷蓄積工程および閾値電圧検出工程に関する、画素回路1a～画素回路1cのそれぞれの関係について説明する。図3は、画素回路1a～画素回路1cに関する電荷蓄積工程および閾値電圧検出工程における電位変動を示すタイミングチャートであり、具体

10

20

30

40

50

的には、陰極電位線 17 a、17 b と、第1制御線 18 a、18 b と、第2制御線 19 a、19 b と、画素回路 1 a ~ 画素回路 1 c のそれぞれに備わる薄膜トランジスタ 4 a ~ 薄膜トランジスタ 4 c のソース電極との電位変化を示している。

#### 【0050】

画素回路 1 a と画素回路 1 b は、図 1 にも示したように共通の陰極電位線 17 a によって陰極電位供給回路 10 からの電気信号が供給される構成を有する。一方で、第1制御回路 13 および第2制御回路 14 からは、それぞれ異なる第1制御線 18 a、18 b および第2制御線 19 a、19 b からの異なる電気信号が供給される。

#### 【0051】

これに対して、画素回路 1 a と画素回路 1 c は、図 1 にも示したように共通の第1制御線 18 a および第2制御線 19 a によって第1制御回路 13 および第2制御回路 14 からの電気信号が供給される構成を有する。一方で、陰極電位供給回路 10 からは、それぞれ異なる陰極電位線 17 a、17 b によって異なる電気信号が供給される。

#### 【0052】

また、既に図 2 を参照しつつ説明したように、電荷蓄積工程および閾値電圧検出工程の開始タイミングは、陰極電位線 17 を介して供給される電気信号によって制御される一方で、電荷蓄積工程および閾値電圧検出工程の終了タイミングは、第1制御線 18 および第2制御線 19 を介して供給される電気信号によって制御されることとなる。

#### 【0053】

具体的には、図 3 にも示すように、画素回路 1 b は、画素回路 1 a と比較して、電荷蓄積工程および閾値電圧検出工程の開始タイミングが一致する一方で、電荷蓄積工程および閾値電圧検出工程の終了タイミングが  $t$  だけ早まることとなる。このため、画素回路 1 b は、電荷蓄積工程に要する時間長  $t_{1b}$  および閾値電圧検出工程に要する時間長  $t_{2b}$  に関して、画素回路 1 a における時間長  $t_{1a}$ 、 $t_{2a}$  と比較して、それ  $t$  だけ少ないこととなる。

#### 【0054】

画素回路 1 c についても同様である。すなわち、画素回路 1 c は、画素回路 1 a と比較して、電荷蓄積工程および閾値電圧検出工程の終了タイミングが一致する一方で、電荷蓄積工程および閾値電圧検出工程の開始タイミングが  $t$  だけ遅れることとなる。従って、画素回路 1 c は、電荷蓄積工程に要する時間長  $t_{1c}$  および閾値電圧検出工程に要する時間長  $t_{2c}$  に関して、画素回路 1 a における時間長  $t_{1a}$ 、 $t_{2a}$  と比較して、それ  $t$  だけ少ないこととなる。

#### 【0055】

ここで、電荷蓄積工程に要する時間長  $t_1$  および閾値電圧検出工程に要する時間長  $t_2$  と、各工程におけるソース電位  $V_1$  の変化量、 $V_2$  の変化量との関係について説明する。すなわち、既に説明したように電荷蓄積工程は、有機 EL 素子 3 に対して逆電圧を供給し、有機 EL 素子 3 を蓄電容量として機能させている。そして、図 2 における時間長  $t_1$  の期間におけるソース電位の変化からも明らかのように、電荷蓄積工程終了時における薄膜トランジスタ 4 のソース電位は、時間長  $t_1$  の値に依存することとなる。すなわち、電荷蓄積工程に要する時間長  $t_1$  が異なる場合にはソース電位  $V_1$  の変化量も異なることとなる。

#### 【0056】

このことは、閾値電圧検出工程の場合も同様である。すなわち、閾値電圧検出工程は、薄膜トランジスタ 4 のゲート・ソース間電圧が駆動閾値よりも高い状態で開始され、徐々にゲート・ソース間電圧を低下させて駆動閾値に近接させることを目的としている。そして、図 2 における時間長  $t_2$  におけるソース電位の変化からも明らかのように、閾値電圧検出工程では、薄膜トランジスタ 4 のゲート・ソース間電圧は、時間の経過と共に単調減少しており、閾値電圧検出工程終了時における薄膜トランジスタ 4 のゲート・ソース間電圧の値は、時間長  $t_2$  の値に依存することとなる。従って、閾値電圧検出工程に要する時間長  $t_2$  が異なる場合には、ソース電位  $V_2$  の変化量の値も異なることとなる。

#### 【0057】

10

20

30

40

50

また、各画素回路 1において、電荷蓄積工程開始時におけるゲート・ソース間電圧の絶対値および電荷蓄積工程終了から閾値検出工程開始までの期間におけるゲート・ソース間電圧の変化量がほぼ一定であるとみなすことが可能である。このため、時間長  $t_1$ 、 $t_2$  が互いに異なる場合には、閾値電圧検出工程を終了した時点における薄膜トランジスタ 4 のゲート・ソース間電圧が異なる値となり、具体的には、 $V_1$  の変化量と  $V_2$  の変化量に応じた異なる電圧が画素回路 1 a～画素回路 1 c に備わる薄膜トランジスタ 4 a～薄膜トランジスタ 4 c の間に生じることとなる。

#### 【0058】

そして、本実施の形態では、各画素回路 1 では、閾値電圧検出工程の完了時に与えられているゲート・ソース間電圧にデータ電圧を加算することによって画像表示を行うこととしている。従って、例えば画素回路 1 a～画素回路 1 c に対して同じ値のデータ電圧を供給して同一色を表示しようとした場合であっても、閾値電圧検出工程の完了時における電圧差が無視できないような場合には、それぞれ異なる色を表示することとなり、使用者に違和感を与えることとなる。

#### 【0059】

これに対して、本実施の形態のように陰極電位線 1 7、第 1 制御線 1 8 および第 2 制御線 1 9 について、隣接する画素回路 1 間で共用する構成とした場合には、電荷蓄積工程の時間長  $t_1$  とソース電位  $V_1$  の変化量および閾値電圧検出工程の時間長  $t_2$  とソース電位  $V_2$  の変化量の値を各画素回路 1 において同一とすることは困難である。従って、本実施の形態では、 $V_1$ 、 $V_2$  の変化量が異なる値になることを前提としつつ、異なる値をとることによる表示色の変化を、使用者が認識し得ない程度に低減することとしている。

#### 【0060】

まず、本実施の形態では、隣接する行に配置された画素回路 1 の一方の対（例えば、画素回路 1 a と画素回路 1 c）において陰極電位線 1 7、第 1 制御線 1 8 および第 2 制御線 1 9 のすべてを共用し、他方の対（例えば、画素回路 1 a と画素回路 1 c）とで陰極電位線 1 7 等のすべてを別個とする構成を採用していない。すなわち、図 1 にも示したように一方の対で一部の配線構造を共用し、他方の対で残りを共用した構成としている。

#### 【0061】

かかる構成によって、配線構造の本数を低減できると共に、列方向における表示色の変化を一様にすることが可能である。図 3 にも示したように、本実施の形態では、画素回路 1 a と画素回路 1 b、および画素回路 1 a と画素回路 1 c の間において、電荷蓄積工程の時間長の差は、隣接する画素回路間でいずれも一定の値  $t$  となる。このことは閾値電圧検出工程でも同様であって、隣接する画素回路の間、すなわち画素回路 1 b と画素回路 1 a の間および画素回路 1 a と画素回路 1 c の間における閾値電圧検出工程の時間長の差は、図 3 に示すように一定の値  $t$  となる。

#### 【0062】

このため、本実施の形態では、隣接行に属する画素回路間における各工程の時間長の差が一定となり、同一のデータ電圧を供給したにもかかわらず時間長差に起因して表示色が変動した場合であっても、各画素回路間において表示色の変動が一様に生じることとなる。すなわち、本実施の形態にかかる表示装置では、一部画素回路間において表示色が顕著に生じる、といったことがないため、使用者が違和感を生じる可能性を低減することが可能である。

#### 【0063】

また、本実施の形態では、画素回路 1 a と画素回路 1 b は、陰極電位線 1 7 a を共用し、画素回路 1 a と画素回路 1 c は、第 1 制御線 1 8 a および第 2 制御線 1 9 a を共用することとしている。かかる共用態様によって、本実施の形態では、画素回路 1 a と画素回路 1 b の間および画素回路 1 a と画素回路 1 c の間において生じる表示色の変動幅を抑制することを可能としている。

#### 【0064】

すなわち、電荷蓄積工程においては、薄膜トランジスタ 4 のソース電位は時間経過に対

10

20

30

40

50

して単調増加することから、電荷蓄積工程に要する時間長  $t_1$  が増加するにつれて、ソース電位の値が増加する。一方で、閾値電圧検出工程においては、ソース電位は時間経過に対して単調減少することから、閾値電圧検出工程に要する時間長  $t_2$  が増加するにつれて、薄膜トランジスタ 4 のソース電位の値は減少することとなる。

#### 【0065】

このような関係に鑑みて、本実施の形態では、一方の隣接画素回路間（例えば、画素回路 1 a と画素回路 1 b）とで陰極電位線を共用することによって電荷蓄積工程および閾値電圧検出工程の開始タイミングを同一とし、他方の隣接画素回路間（例えば、画素回路 1 a と画素回路 1 c）とで第 1 制御線および第 2 制御線を共用することによって電荷蓄積工程及び閾値電圧検出工程の終了タイミングを同一としている。10

#### 【0066】

かかる構成とした場合、基準とする画素回路に隣接する画素回路における各工程の時間長は、電荷蓄積工程の時間長が基準となる画素回路よりも増加すると、閾値電圧検出工程でも増加することとなる。すなわち、図 3 の例で言えば、例えば画素回路 1 b を基準とした場合、隣接する行に配置された画素回路 1 a の電荷蓄積工程の時間長は、画素回路 1 b の場合よりも増加するとともに、閾値電圧検出工程における時間長も増加している。上記したように、画素回路 1 は、電荷蓄積工程では時間長が増加するにつれてソース電位が増加する傾向を有し、閾値電圧検出工程では時間長が増加するにつれてソース電位が減少する特性を有する。このため、ある画素回路 1 において、隣接する画素回路 1 と比較して電荷蓄積工程および閾値電圧検出工程の双方の時間長が増加する構成では、電荷蓄積工程の長時間化によるソース電位の増加量を、閾値電圧検出工程の長時間化によるソース電位の減少量が相殺することとなり、全体としてソース電位の変動幅を低減することが可能である。そして、最終的な薄膜トランジスタ 4 のゲート・ソース間電圧の値は、全工程を通じたソース電位の変化量に対応することとなるため、異なる画素回路間におけるソース電位の変化量の差が減少することによって各画素回路に備わる薄膜トランジスタのゲート・ソース間電圧の差も減少し、異なる画素回路における表示色の違いを減少させることができるという利点を有することとなる。20

#### 【0067】

さらに、本実施の形態では、隣接する画素回路間における電荷蓄積工程の時間長の差と、当該画素回路間における閾値電圧検出工程の時間長の差が同一になるようにドライバ回路 2 および陰極電位線 17 等の配線構造が構成されている。かかる構成を採用することによって、電荷蓄積工程等における時間長の差が生じた場合であっても表示色の変動を抑制することが可能である。30

#### 【0068】

すなわち、図 2 のタイミングチャートにも示したように、電荷検出工程および閾値電圧検出工程における薄膜トランジスタ 4 a のソース電位は、工程が終了する近傍の時刻において、いずれの工程においても電位変化率が低くなると共に、両工程における変化率の絶対的な値がほぼ等しいものとなっている。従って、隣接画素回路間の電荷検出工程における時間長の差と、閾値電圧検出工程における時間長の差が等しい場合には、各工程におけるソース電位の変動値の絶対値もほぼ等しいものとなり、隣接する行に配置された画素回路間における電荷蓄積工程および閾値電圧検出工程を通じたゲート・ソース間電圧の差を減少させることができあり、この結果、表示色の変動を抑制することが可能である。40

#### 【0069】

さらに、本実施の形態では、隣接画素回路間における  $V_1$ 、 $V_2$  の変化量の差の許容範囲を定め、 $V_1$ 、 $V_2$  の変化量によって定まる薄膜トランジスタ 4 のゲート・ソース間電圧の差が許容範囲内に抑制される構成を採用することによって、表示色の変化を、使用者が認識し得ない程度にまで抑制している。以下、隣接画素回路間における  $V_1$ 、 $V_2$  の具体的な値の違いによって生ずる薄膜トランジスタ 4 のゲート・ソース間電圧差の許容範囲について詳細に説明する。なお、以下では隣接画素回路間において同一色を表示する場合を例に説明を行うこととし、閾値電圧検出工程完了時におけるゲート・ソース間電圧の違いのみ50

によって表示色の変動が生じるものとする。また、以下の議論では表示装置はモノトーン表示を行うこととし、表示色の違いは各画素回路1における有機EL素子3の発光輝度の違いを意味することとする。さらに、有機EL素子3の発光輝度の違いの指標として、有機EL素子3に流れる電流値を用いることとする。

## 【0070】

隣接する一方の画素回路1(例えば、画素回路1b)を基準とし、基準となる画素回路に備わる有機EL素子3(例えば、有機EL素子3b)に流れる電流Iと、比較対象となる画素回路(例えば画素回路1a)に備わる有機EL素子3(例えば、有機EL素子3a)に流れる電流と電流Iとの差分値をΔIとする。これらの文字を用いて許容範囲を表現すると、

10

## 【数1】

$$\left| \frac{\Delta I}{I} \right| < k$$

・・・(1)

と表される。ここで、kは使用者の表示色変化の認識限界に対応した値であり、例えば、(k=0.01)で与えられる。

## 【0071】

ここで、発光工程時に有機EL素子3に流れる電流Iは、薄膜トランジスタ4の駆動閾値電圧V<sub>th</sub>に依存して変化し、具体的には、隣接行に位置する画素回路に備わる薄膜トランジスタ4で検出される駆動閾値電圧の差分値ΔV<sub>th</sub>を用いて、

20

## 【数2】

$$\Delta I = \frac{\partial I}{\partial V_{th}} \Delta V_{th} = -\beta (V_{gs} - V_{th}) \cdot \Delta V_{th}$$

・・・(2)

の関係が成立する。なお、(2)式の導出において、一般の薄膜トランジスタにおいて電流値I、駆動閾値V<sub>th</sub>およびゲート・ソース間電圧V<sub>gs</sub>の間で成立する、

## 【数3】

$$I = \frac{\beta}{2} (V_{gs} - V_{th})^2$$

30

・・・(3)

## 【数4】

$$\beta = \frac{\mu C_{ox} W}{L}$$

・・・(4)

の2式を用いている。(4)式において、μは薄膜トランジスタに形成されるチャンネル領域における電子の移動度であり、C<sub>ox</sub>は薄膜トランジスタの単位面積あたりの静電容量であり、Wは薄膜トランジスタに形成されるチャンネルの幅であり、Lはチャンネル長である。(2)式を用いることによって、(1)式は、

40

## 【数5】

$$\left| \frac{\Delta I}{I} \right| = \frac{2}{V_{gs} - V_{th}} |\Delta V_{th}| = \frac{2}{V_{data}} |\Delta V_{th}| < k$$

・・・(5)

と変形することが可能である。従って、許容しうる表示色の変動範囲を導出するにあたっては、電荷蓄積工程および閾値電圧検出工程によって導出される駆動閾値電圧V<sub>th</sub>の値の変化量が(5)式を満たせば良いことになる。

50

## 【0072】

ところで、電荷蓄積工程においては薄膜トランジスタ4のドレイン電位は0電位に維持され、ゲート・ソース間電圧は、コンデンサ5の作用により前フレーム表示の際に供給されたデータ電圧 $V_{data}'$ と駆動閾値 $V_{th}$ の和に維持されている。このため、電荷蓄積工程においては、薄膜トランジスタ4はいわゆる線形領域にて動作することとなり、電荷蓄積工程の際に薄膜トランジスタ4のソース・ドレイン間に流れる電流 $I_{charge}$ に関して、

## 【数6】

$$I_{charge} \approx \beta(V_{gd}(t) - V_{th}) \cdot V_{sd}(t) = \beta(V_g(t) - V_{th}) \cdot V_1(t) = \beta(V_{data}' + V_1(t)) \cdot V_1(t)$$

· · · (6)

10

という一般式が成立する。そして、かかる電流 $I_{charge}$ は、容量値 $C_{OLED}$ の静電容量として機能する有機EL素子3によって供給されることから、

## 【数7】

$$I_{charge} = \frac{\partial V_1(t)}{\partial t}$$

· · · (7)

が成立し、(6)式および(7)式に基づいて、時間長 $t_1$ だけ電荷蓄積工程が行われた場合の薄膜トランジスタ4のソース電位 $V_1(t_1)$ は、

## 【数8】

$$V_1(t_1) = \frac{V_{data}'}{\exp\left(-\frac{\beta \cdot V_{data}'}{C_{OLED}} t_1 + \ln\left(1 + \frac{V_{data}'}{V_1(0)}\right)\right) - 1}$$

· · · (8)

20

と表されることになる。

## 【0073】

次に、閾値電圧検出工程の終了時における薄膜トランジスタ4のソース電位 $V_2$ について説明する。閾値電圧検出工程においては、薄膜トランジスタ4のゲート電位およびドレイン電位は0電位に維持されることから、薄膜トランジスタ4は飽和領域で動作することになり、閾値電圧検出工程の際に薄膜トランジスタ4のドレイン・ソース間に流れる電流 $I_{Vth}$ は、コンデンサ5の静電容量値 $C_s$ を用いた、

30

## 【数9】

$$I_{Vth} = \frac{\beta}{2}(-V_2(t) - V_{th})^2 = (C_s + C_{OLED}) \frac{\partial V_2(t)}{\partial t}$$

· · · (9)

の関係を満たすこととなり、(9)式に示す微分方程式を解くことによって、ソース電位 $V_2$ は、

## 【数10】

$$V_2(t) = -V_{th} + \frac{1}{\frac{1}{V_2(0) + V_{th}} - \frac{\beta}{2(C_s + C_{OLED})} t}$$

· · · (10)

40

と表されることになる。そして、本実施の形態にかかる表示装置において、閾値電圧検出工程によって実際に検出される駆動閾値電圧の値は $V_2(t_2)$ であることから、(5)式等における隣接行に配置された画素回路間における駆動閾値電圧 $V_{th}$ の差分値 $\Delta V_{th}$ の値は、(10)式に基づき閾値電圧検出工程に要する時間長 $t_2$ およびソース電位 $V_2$ の初期値 $V_2(0)$ を用いて、

50

【数11】

$$\Delta V_{th} = \frac{\partial V_2(t_2)}{\partial t_2} \Delta t_2 + \frac{\partial V_2(t_2)}{\partial V_2(0)} \Delta V_2(0)$$

・・・(11)

と表される。ここで、初期値  $V_2(0)$  は、閾値電圧検出工程開始時における陰極電位線 17 の電位変動に起因したソース電位の変化量(定数)  $V_{pow}$  を用いて、

【数12】

$$V_2(0) = V_1(t_1) + \Delta V_{pow}$$

10

・・・(12)

と表されることから、(12)式を(11)式に代入して所定の式変形を行うことによって、

【数13】

$$\Delta V_{th} = \frac{\partial V_2(t_2)}{\partial t_2} \Delta t_2 + \frac{\partial V_2(t_2)}{\partial V_2(0)} \frac{\partial V_1(t_1)}{\partial t_1} \Delta t_1$$

・・・(13)

が成立する。そして、(13)式に(8)式および(10)式を代入することによって、

【数14】

$$\begin{aligned} \Delta V_{th} &= \frac{\beta}{2(C_s + C_{OLED})} \Delta t_2 \\ &- \frac{1}{(V_2(0) + V_{th})^2 \left( \frac{1}{V_2 + V_{th}} - \frac{\beta}{2(C_s + C_{OLED})} t_2 \right)^2} \\ &\times \frac{\frac{\beta \cdot V_{data}'}{C_{OLED}} \cdot \exp\left(-\frac{\beta \cdot V_{data}'}{C_{OLED}} t_1 + \ln\left(1 + \frac{V_{data}'}{V_1(0)}\right)\right)}{\left(\exp\left(-\frac{\beta \cdot V_{data}'}{C_{OLED}} t_1 + \ln\left(1 + \frac{V_{data}'}{V_1(0)}\right)\right) - 1\right)^2} \Delta t_1 \end{aligned}$$

・・・(14)

という関係が導出される。本実施の形態にかかる表示装置において、(14)式に示す  $V_{th}$  の値が任意の  $V_{data}'$  の値に関して(5)式を満たすようコンデンサ 5 の容量値や薄膜トランジスタ 4 の具体的構造等を定めることによって、陰極電位線 17、第 1 制御線 18 および第 2 制御線 19 を隣接行の画素回路同士で共用した場合であっても、例えば画面全体で同一色を表示した場合に、互いに隣接した行に配置された画素回路 1 間における表示色の変動が視認不可能な程度にまで抑制することが可能である。

【0074】

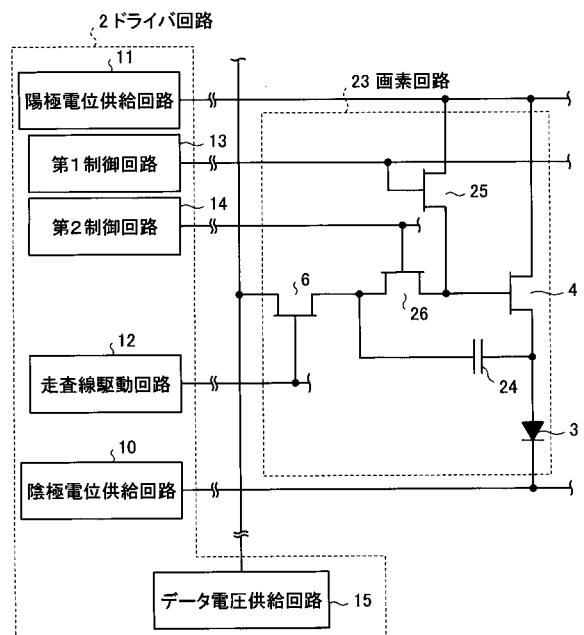

(変形例 1)

なお、異なる行に配置された複数の画素回路が陰極電位線等の配線構造を共用する表示装置において、画素回路の具体的な構成としては図 1 に示すものに限定されないことは言うまでもない。例えば、図 4 に示す画素回路 23 を用いて表示装置を構成した場合であっても、図 1 と同様の態様で配線構造を共用しつつ、表示色の変動を視認不可能な程度にまで抑制することが可能である。

20

30

40

50

## 【0075】

すなわち、図4に示す画素回路23は、画素回路1と異なり、薄膜トランジスタ4のゲート・ドレイン間に配置された第2スイッチング素子25と、薄膜トランジスタ4と第1スイッチング素子6との間に配置された第3スイッチング素子26と、第1スイッチング素子6の一方のソース／ドレイン電極（データ電圧供給回路15と電気的に接続していない側のソース／ドレイン電極）と、有機EL素子3の陽極との間に配置されたコンデンサ24とを備えた構成を有する。かかる画素回路23に関しても、具体的な条件として、図1の回路におけるコンデンサ5をコンデンサ24に置き換えた上で（10）式を満たすよう設計することによって、配線構造を共用しつつ表示色の変動を視認不可能な程度に抑制することが可能である。

10

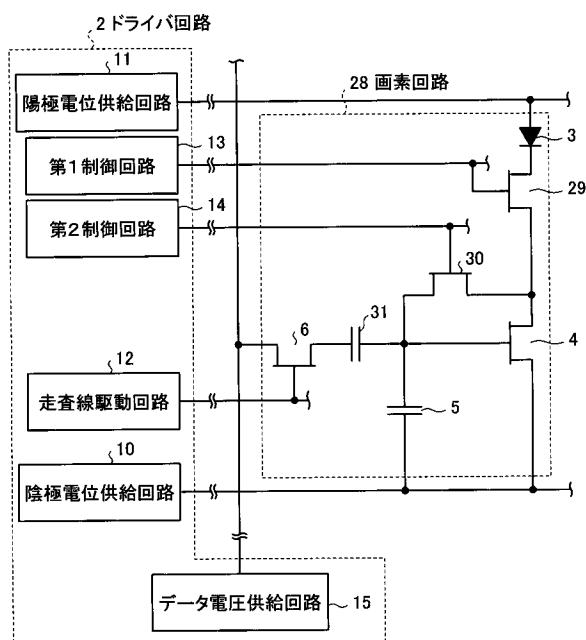

## 【0076】

## （変形例2）

また、図5に示す画素回路28においても、配線構造を共用しつつ表示色の変動を視認不可能な程度に抑制することが可能である。具体的には、図5に示す画素回路28においては、有機EL素子3の陽極側が薄膜トランジスタ4を介さずに陽極電位供給回路11と電気的に接続されると共に、有機EL素子3の陰極側と薄膜トランジスタ4のドレイン電極との間に配置された第2スイッチング素子29と、薄膜トランジスタ4のゲート・ドレイン間に配置された第3スイッチング素子30と、薄膜トランジスタ4のゲート電極と第1スイッチング素子6の一方のソース／ドレイン電極（データ電圧供給回路15と接続するソース／ドレイン電極と反対側のソース／ドレイン電極）との間に配置されたコンデンサ31とを備える。かかる画素回路28では、（10）式において $(C_s + C_{OLED})$ の部分が、コンデンサ31の静電容量値 $C_1$ と $C_s$ の和に置き換わることになる。そして、駆動閾値検出工程の際に薄膜トランジスタ4に流れる電流値 $I_{V_{th}}$ に関して、陽極電位線から供給される電位 $V_{DD}$ および所定の比例係数 $\alpha$ を用いて、

20

## 【数15】

$$I \approx \alpha(V_{DD} - V_1 - V_{th})^2$$

・・・(15)

と近似すると、

## 【数16】

$$\alpha(V_{DD} - V_1 - V_{th,OLED})^2 = \frac{\beta}{2}(V_1 - V_{th})^2 + (C_1 + C_{OLED}) \frac{dV_1}{dt}$$

・・・(16)

30

が成立する。（16）式に示す微分方程式の解を用いて、実施の形態1と同様に表示色の変動が視認不可能な程度にまで抑制された表示装置を実現することが可能である。

40

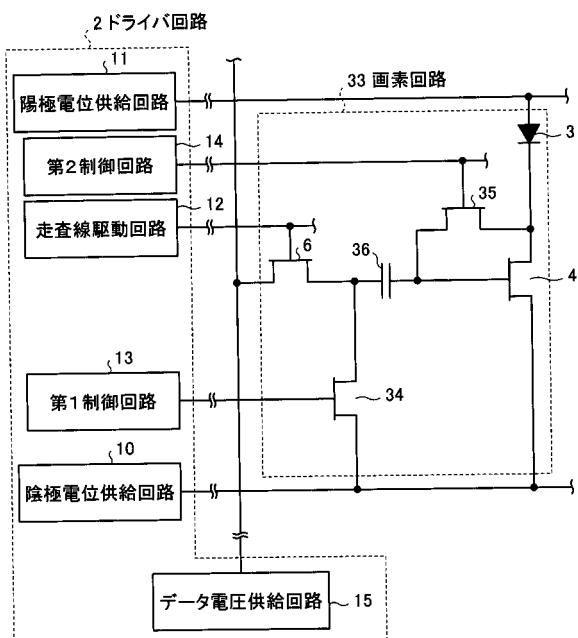

## 【0077】

## （変形例3）

さらに、図6に示す画素回路33についても同様である。すなわち、画素回路33は、第1スイッチング素子の一方のソース／ドレイン電極（データ電圧供給回路15と接続したソース／ドレイン電極と反対側のソース／ドレイン電極）と陰極電位供給回路10との間の電気的接続を制御する第2スイッチング素子34と、薄膜トランジスタ4のゲート・ドレイン間に配置された第3スイッチング素子35と、薄膜トランジスタ4と第1スイッチング素子6との間に配置されたコンデンサ36とを新たに備えた構成を有する。かかる画素回路33を備えた表示装置では、ドレイン電位に関して実施の形態1および変形例1と同様の計算を行うことによって、表示色の変動が視認不可能な程度まで抑制された表示装置を実現することが可能である。

## 【0078】

以上、本発明について実施の形態および変形例を用いて説明したが、本発明は上記の例に限定して解釈するべきではなく、当業者であれば、様々な実施例、変形例等に想到する

50

ことが可能である。例えば、実施の形態等においては、特許請求の範囲におけるトランジスタ素子の例としてnチャンネルの薄膜トランジスタ4を用いることとしたが、トランジスタの構成としてはかかるものに限定して解釈する必要はなく、p型の薄膜トランジスタ等を用いることが可能である。

#### 【0079】

また、発光素子に関しても、有機EL素子以外に無機EL素子等を用いることが可能である。さらに、発光素子が特許請求の範囲における静電容量としての機能をも併せ持つことは必然のことではなく、コンデンサとしての機能を有さない発光素子と、電荷蓄積工程において電荷を蓄積するための静電容量とを別個独立に形成することとしても良い。

#### 【図面の簡単な説明】

10

#### 【0080】

【図1】実施の形態にかかる表示装置の全体構成を示す模式図である。

【図2】単一の画素回路に備わる薄膜トランジスタのソース電位および画素回路に対して供給される電気信号の時間変動を示すタイミングチャートである。

【図3】複数の画素回路におけるソース電位の時間変動および供給される電気信号の供給タイミングの関係を示すタイミングチャートである。

#### 【図4】実施の形態の変形例における画素回路の構成を示す回路図である。

#### 【図5】実施の形態の他の変形例における画素回路の構成を示す回路図である。

#### 【図6】実施の形態の他の変形例における画素回路の構成を示す回路図である。

#### 【図7】従来の表示装置の構成を示す模式図である。

20

#### 【符号の説明】

#### 【0081】

1 a ~ 1 c 画素回路

2 ドライバ回路

3 a ~ 3 c 有機EL素子

4 a ~ 4 c 薄膜トランジスタ

5 a ~ 5 c コンデンサ

6 a ~ 6 c 第1スイッチング素子

7 a ~ 7 c 第2スイッチング素子

8 a ~ 8 c 第3スイッチング素子

30

10 陰極電位供給回路

11 陽極電位供給回路

12 走査線駆動回路

13 第1制御回路

14 第2制御回路

15 データ電圧供給回路

17 a、17 b 陰極電位線

18 a、18 b 第1制御線

19 a、19 b 第2制御線

20 陽極電位線

40

21 a ~ 21 c 走査線

22 信号線

23 画素回路

24 コンデンサ

25 第2スイッチング素子

26 第3スイッチング素子

28 画素回路

29 第2スイッチング素子

30 第3スイッチング素子

31 コンデンサ

50

- 3 3 画素回路

3 4 第2スイッチング素子

3 5 第3スイッチング素子

3 6 コンデンサ

1 0 0 画素回路

1 0 1 素子

1 0 2 ドライバ素子

1 0 3 第1スイッチング素子

1 0 4 第2スイッチング素子

1 0 5 第3スイッチング素子

1 0 6 コンデンサ

1 0 7 低電位供給線

1 0 8 高電位供給線

1 0 9 走査線

1 1 0 制御線

1 1 1 制御線

1 1 2 ドライバ回路

1 1 3 信号線

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 小野 晋也

神奈川県大和市下鶴間1623番地14 インターナショナル ディスプレイ テクノロジー株式

会社 大和事業所内

(72)発明者 小林 芳直

神奈川県大和市下鶴間1623番地14 インターナショナル ディスプレイ テクノロジー株式

会社 大和事業所内

F ターム(参考) 3K007 AB17 BA06 DB03 GA00

5C080 AA06 BB05 DD23 FF11 JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置和显示装置的驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP2006003744A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2006-01-05 |

| 申请号            | JP2004181655                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2004-06-18 |

| [标]申请(专利权)人(译) | 群创光电股份有限公司<br>京瓷株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 奇美电子股▲ふん▼有限公司<br>京瓷株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 三和宏一<br>小野晋也<br>小林芳直                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 三和 宏一<br>小野 晋也<br>小林 芳直                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| CPC分类号         | G09G3/3233 G09G3/3291 G09G2300/0426 G09G2300/0465 G09G2300/0819 G09G2300/0842<br>G09G2310/0256 G09G2310/0262 G09G2310/08 G09G2330/02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G09G3/30.J G09G3/20.621.A G09G3/20.624.B G09G3/20.641.D H05B33/14.A G09G3/20.611.F<br>G09G3/20.622.D G09G3/20.622.G G09G3/20.680.G G09G3/3233 G09G3/3266 G09G3/3275 G09G3<br>/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 5C080/AA06 5C080/BB05 5C080/DD23 5C080<br>/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 3K107/AA01 3K107/BB01 3K107/CC11 3K107/CC33<br>3K107/CC36 3K107/EE03 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AA02 5C380/AB06 5C380<br>/AB32 5C380/AB45 5C380/BA12 5C380/BA31 5C380/BA38 5C380/BA39 5C380/CA08 5C380/CA12<br>5C380/CA53 5C380/CB01 5C380/CB09 5C380/CB16 5C380/CB17 5C380/CB20 5C380/CB31 5C380<br>/CB32 5C380/CB37 5C380/CC04 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC41<br>5C380/CC54 5C380/CC65 5C380/CC77 5C380/CD014 5C380/CD024 5C380/DA02 5C380/DA06<br>5C380/DA32 5C380/HA03 5C380/HA08 5C380/HA13 |         |            |

| 代理人(译)         | 酒井宏明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | <a href="#">JP4737587B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

**摘要(译)**

解决的问题：实现一种显示装置，其中减少了与像素电路连接的布线结构的数量，同时抑制了显示质量的下降。像素电路（1a）包括有机EL元件（3a），调节流过有机EL元件（3a）的电流的薄膜晶体管（4a），电容器（5a），控制薄膜晶体管（4a）的驱动状态的第一开关元件（6a）和电荷累积。提供了在该步骤和阈值电压检测步骤中起作用的第二开关元件7a和第三开关元件8a。在前一级，与有机EL元件3a的阴极侧连接的阴极电位线17a与像素电路1b共用，但第二开关元件7a，第一控制线18a和第二控制线18a用于控制第三开关元件8a的驱动状态。控制线19a具有在后一级与像素电路1c共享的配置。[选型图]图1