(19)日本国特許庁( J P )

(12) 公開特許公報 ( A ) (11)特許出願公開番号

特開2003 - 323133

(P2003 - 323133A)

(43)公開日 平成15年11月14日(2003.11.14)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I           | テ-マコード <sup>*</sup> (参考) |

|--------------------------|------|---------------|--------------------------|

| G 0 9 F 9/30             | 338  | G 0 9 F 9/30  | 3 K 0 0 7                |

|                          | 336  |               | 5 C 0 9 4                |

|                          | 365  |               | 365 Z                    |

| H 0 5 B 33/14            |      | H 0 5 B 33/14 | A                        |

審査請求 未請求 請求項の数 140 L (全 6 数)

(21)出願番号 特願2002 - 128008(P2002 - 128008)

(71)出願人 000001889

三洋電機株式会社

(22)出願日 平成14年4月30日(2002.4.30)

大阪府守口市京阪本通2丁目5番5号

(72)発明者 安齋 勝矢

大阪府守口市京阪本通2丁目5番5号 三洋電

機株式会社内

(74)代理人 100107906

弁理士 須藤 克彦 (外1名)

F ターム (参考) 3K007 AB02 AB03 AB11 AB17 DB03

GA00

5C094 AA07 AA31 BA03 BA27 CA19

DA13 DA15 DB04 FA02 FB02

FB15 FB19 HA08

(54)【発明の名称】エレクトロルミネッセンス表示装置

(57)【要約】

【課題】EL表示装置において、駆動用トランジスタのゲートに供給されるビデオ信号を保持するための保持容量の形成面積を縮小し、表示品位の向上と有機EL素子の寿命延長を図る。

【解決手段】第1の容量電極層55と兼用されたTFT30のソース33s上には、ゲート絶縁膜12を介して第2の容量電極層54が設けられている。第2の容量電極層54は、ゲート電極31と同一の層で、同一工程で形成されている。第2の容量電極層54上には、層間絶縁膜15を介して、第3の容量電極層70が延設されている。第3の容量電極層70は、ドレイン電極36、ドレイン信号線52と同一の層で形成されている。第3の容量電極層70はTFT30のソース33sと接続されている。

## 【特許請求の範囲】

【請求項1】 複数の画素部を有し、各画素部は、エレクトロルミネッセンス素子と、前記エレクトロルミネッセンス素子を駆動する駆動用トランジスタと、ドレイン信号線と、ゲート信号に応じてスイッチングし、前記駆動用トランジスタのゲートに前記ドレイン信号線からのビデオ信号を供給する画素選択用トランジスタと、前記駆動用トランジスタのゲートに供給されるビデオ信号を保持するための保持容量と、を具備するエレクトロルミネッセンス表示装置であって、

前記保持容量は、第1の容量電極層を兼ねた前記画素選択用トランジスタのソース上に、第1の絶縁膜を介して形成された第2の容量電極層と、前記ソースに接続され、前記第2の容量電極層上に第2の絶縁膜を介して延設された第3の容量電極層と、を有することを特徴とするエレクトロルミネッセンス表示装置。

【請求項2】 前記第2の容量電極層は、前記画素選択用トランジスタのゲートと同一の層で形成されていることを特徴とする請求項1記載のエレクトロルミネッセンス表示装置。

【請求項3】 前記第1の絶縁膜は、前記画素選択用トランジスタのゲート絶縁膜と同一の膜で形成されていることを特徴とする請求項1記載のエレクトロルミネッセンス表示装置。

【請求項4】 前記第3の容量電極層は、前記ドレイン信号線と同一の層で形成されていることを特徴とする請求項1記載のエレクトロルミネッセンス表示装置。

【請求項5】 前記第2の絶縁膜は、前記画素選択用トランジスタのゲートと前記ドレイン信号線間の層間絶縁膜と同一の膜で形成されていることを特徴とする請求項1記載のエレクトロルミネッセンス表示装置。

【請求項6】 複数の画素部を有し、各画素部は、陽極層、発光層及び陰極層を有するエレクトロルミネッセンス素子と、前記エレクトロルミネッセンス素子を駆動する駆動用トランジスタと、ドレイン信号線と、ゲート信号に応じてスイッチングし、前記駆動用トランジスタのゲートに前記ドレイン信号線からのビデオ信号を供給する画素選択用トランジスタと、前記駆動用トランジスタのゲートに供給されるビデオ信号を保持するための保持容量と、を備えたエレクトロルミネッセンス表示装置であって、

前記保持容量は、第1の容量電極層を兼ねた前記画素選択用トランジスタのソース上に、第1の絶縁膜を介して形成された第2の容量電極層と、前記ソースに接続され前記第2の容量電極層上に第2の絶縁膜を介して延設された第3の容量電極層と、前記第3の容量電極層に接続され該第3の容量電極層上に第3の絶縁膜を介して延設された第4の容量電極層と、前記第4の容量電極層上に第4の絶縁膜を介して延設された第5の容量電極層と、を具備することを特徴とするエレクトロルミネッセンス\*

\*表示装置。

【請求項7】 前記第2の容量電極層は、前記画素選択用トランジスタのゲートと同一の層で形成されていることを特徴とする請求項5記載のエレクトロルミネッセンス表示装置。

【請求項8】 前記第1の絶縁膜は、前記画素選択用トランジスタのゲート絶縁膜と同一の膜で形成されていることを特徴とする請求項6記載のエレクトロルミネッセンス表示装置。

10 【請求項9】 前記第3の容量電極層は、前記ドレイン信号線と同一の層で形成されていることを特徴とする請求項6記載のエレクトロルミネッセンス表示装置。

【請求項10】 前記第2の絶縁膜は、前記画素選択用トランジスタのゲートと前記ドレイン信号線間の層間絶縁膜と同一の膜で形成されていることを特徴とする請求項6記載のエレクトロルミネッセンス表示装置。

【請求項11】 前記第4の容量電極層は、前記陽極層と同一の層で形成されていることを特徴とする請求項6記載のエレクトロルミネッセンス表示装置。

20 【請求項12】 前記第3の絶縁膜は、第1平坦化絶縁膜と同一の膜で形成されていることを特徴とする請求項6記載のエレクトロルミネッセンス表示装置。

【請求項13】 前記第5の容量電極層は、前記陰極層と同一の層で形成されていることを特徴とする請求項6記載のエレクトロルミネッセンス表示装置。

【請求項14】 前記第4の絶縁膜は、第2平坦化絶縁膜と同一の膜で形成されていることを特徴とする請求項6記載のエレクトロルミネッセンス表示装置。

## 【発明の詳細な説明】

## 【0001】

【発明の属する技術分野】本発明は、エレクトロルミネッセンス表示装置に関し、特に、駆動用トランジスタのゲートに供給されるビデオ信号を保持するための保持容量を有するエレクトロルミネッセンス表示装置に関する。

## 【0002】

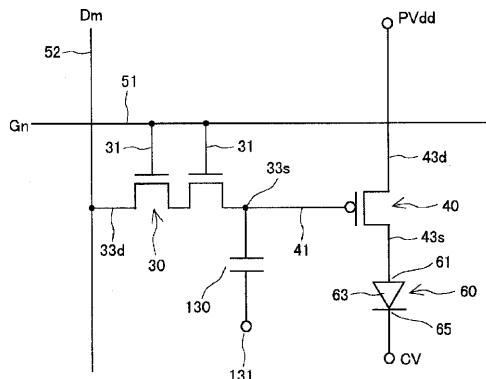

【従来の技術】近年、エレクトロルミネッセンス(Electro Luminescence:以下、「EL」と称する。)素子を用いたEL表示装置が、CRTやLCDに代わる表示装置として注目されており、例えば、そのEL素子を駆動させるスイッチング素子として薄膜トランジスタ(Thin Film Transistor:以下、「TFT」と称する。)を備えたEL表示装置の研究開発も進められている。図4に有機EL表示装置の一画素の等価回路図を示す。ゲート信号Gnを供給するゲート信号線51と、ドレイン信号、すなわち、ビデオ信号Dmを供給するドレイン信号線52とが互いに交差している。

【0003】それらの両信号線の交差点付近には、有機EL素子60及びこの有機EL素子60を駆動するTFT40、画素を選択するためのTFT30が配置されて

いる。

【0004】有機EL素子駆動用の TFT40 のドライエン43dには、正電源電圧 P Vdd が供給されている。また、ソース43sは有機EL素子60のアノード61に接続されている。

【0005】また、画素選択用のTFT30のゲート31にはゲート信号線51が接続されることによりゲート信号Gnが供給され、ドレイン33dにはドレイン信号線52が接続されることにより、ビデオ信号Dmが供給される。TFT30のソース33sは上記TFT40のゲート41に接続されている。ここで、ゲート信号Gnは不図示のゲートドライバ回路から出力される。ビデオ信号Dmは不図示のドレインドライバ回路から出力される。

【0006】また、有機EL素子60は、アノード61、カソード65、このアノード61とカソード65の間に形成された発光素子層63から成る。カソード65には、負電源電圧CVが供給されている。

【0007】また、TFT40のゲート41には保持容量130が接続されている。すなわち、保持容量130の一方の電極はゲート41に接続され、他方の電極は保持容量電極131に接続されている。保持容量130はビデオ信号Dmに応じた電荷を保持することにより、1フィールド期間、表示画素のビデオ信号を保持するため設けられている。

【0008】上述した構成のEL表示装置の動作を説明すると以下の通りである。ゲート信号Gnが一水平期間、ハイレベルになると、TFT30がオンする。すると、ドレイン信号線52からビデオ信号DmがTFT30を通して、TFT40のゲート41に印加される。そして、ゲート41に供給されたビデオ信号Dmに応じて、TFT40のコンダクタンスが変化し、それに応じた駆動電流がTFT40を通して、有機EL素子60に供給され、有機EL素子60が点灯する。

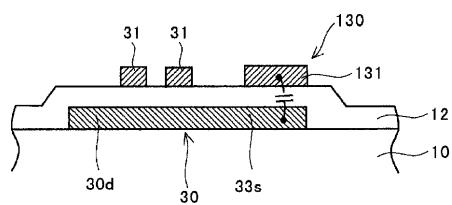

【0009】図5に、上述の保持容量130の断面構造を示す。絶縁性基板10上に、TFT30が形成されている。TFT30は、ソース33s、ドレイン33d及びゲート絶縁膜上12上に形成されたゲート31とを有している。そして、TFT30のソース33s上にはゲート絶縁膜12を介して保持容量電極131が形成され40している。保持容量電極131には一定電圧が印加されている。

【0010】このように、従来、有機EL素子60の輝度を決定する電流量を制御する駆動用トランジスタ40のゲートの電位を固定するために、各画素毎に保持容量130を形成していた。

[0011]

【発明が解決しようとする課題】画素に供給されるビデオ信号 Dm のドロップ電圧量が大きいと表示品位に影響が出てしまう。そこで、このドロップ電圧量を抑えるた

めには、保持容量 130 の容量値をある程度大きくする必要がある。すなわち、保持容量 30 の面積を大きくする必要がある。

【0012】ところで、有機EL表示装置には、トップエミッション型とボトムエミッション型がある。トップエミッション型では、有機EL素子60から発光された光は、絶縁性基板10とは反対側の有機EL素子60の側、すなわちパネル上面側から射出される。一方、ボトムエミッション型では、有機EL素子60から発光された光は、絶縁性基板10の側から射出される。

【0013】保持容量130の面積を大きくしても、トップエミッション型の有機EL表示装置では問題ないが、ボトムエミッション型では保持容量の形成部分はブラインドとして働き、開口率が減少してしまう。このため、必要な輝度を得るために、開口率に余裕がある場合に比べて有機EL素子に供給する電流を増加させる必要があり、結果として有機EL素子の寿命が短くなってしまうという問題があった。

【0014】

【課題を解決するための手段】そこで、本発明は、複数の画素部を有し、各画素部は、エレクトロルミネッセンス素子と、前記エレクトロルミネッセンス素子を駆動する駆動用トランジスタと、ドレイン信号線と、ゲート信号に応じてスイッチングし、前記駆動用トランジスタのゲートに前記ドレイン信号線からのビデオ信号を供給する画素選択用トランジスタと、前記駆動用トランジスタのゲートに供給されるビデオ信号を保持するための保持容量と、を具備するエレクトロルミネッセンス表示装置であって、前記保持容量は、第1の容量電極層を兼ねた前記画素選択用トランジスタのソース上に、第1の絶縁膜を介して形成された第2の容量電極層と、前記ソースに接続され、前記第2の容量電極層上に第2の絶縁膜を介して延設された第3の容量電極層と、を有することを特徴とするものである。

【0015】本発明によれば、保持容量を多層構造の容量電極層で形成しているので、保持容量の形成面積を縮小することができる。また、開口率の低下を招くことなく、保持容量が有する容量値を大きくすることができる。

【 0 0 1 6 】

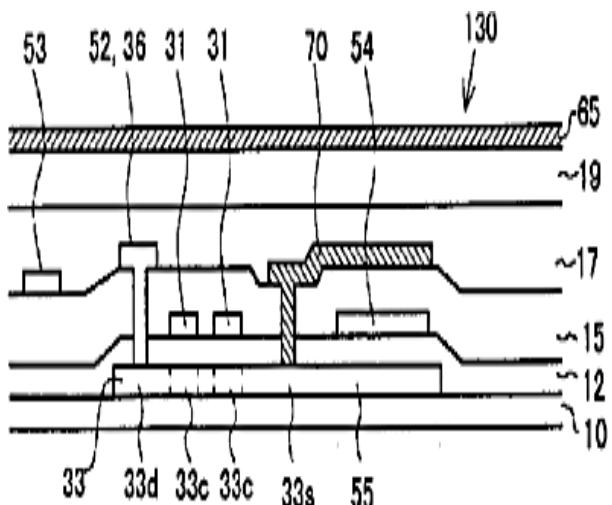

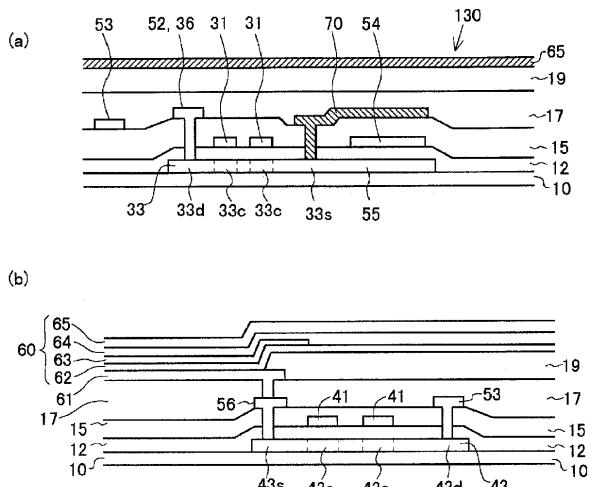

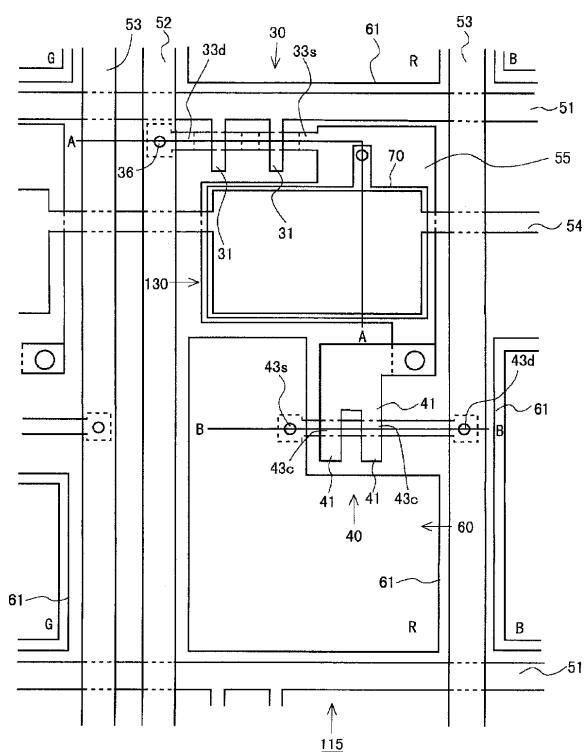

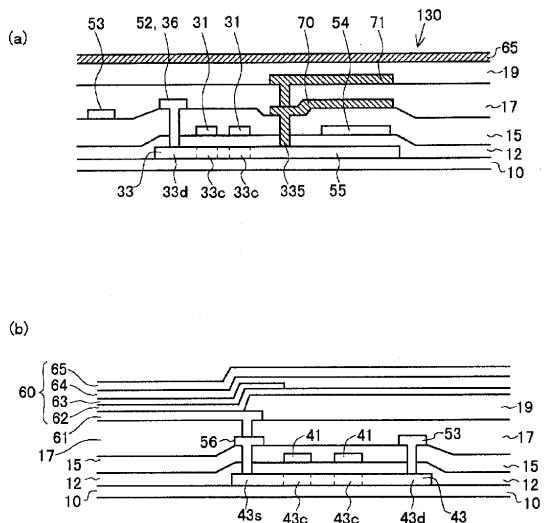

【発明の実施の形態】次に、本発明の第1の実施形態について説明する。図1に有機EL表示装置の画素部を示す平面図を示し、図2(a)に図1中のA-A線に沿った断面図を示し、図2(b)に図1中のB-B線に沿った断面図を示す。なお、当該画素部の等価回路は図4に示した中のと同じである。

【0017】図1及び図2に示すように、ゲート信号線51とドレイン信号線52とに囲まれた領域に画素部115が形成されている。そして、複数の画素部115がマトリクス状に配置され、表示領域を構成している。

【0018】この画素部115には、自発光素子である有機EL素子60と、この有機EL素子60に電流を供給するタイミングを制御する画素選択用TFT30と、有機EL素子60に電流を供給する有機EL素子駆動用TFT40と、保持容量130とが配置されている。なお、有機EL素子60は、アノード(陽極)層61と発光材料からなる発光素子層と、カソード(陰極)層65とから成っている。

【0019】即ち、両信号線51、52の交点付近には画素選択用TFT30が設けられている。TFT30のソース33sは第1の容量電極層55を兼ねるとともに、有機EL素子駆動用TFT40のゲート41に接続されている。TFT30のソース33s上には、ゲート絶縁膜12を介して第2の容量電極層54が設けられている。第2の容量電極層54は、クロムやモリブデン等から成っており、ゲート信号線51と並行して配置されている。さらに、第2の容量電極層54上には、層間絶縁膜15を介して、第3の容量電極層70が形成されている。

【0020】また、有機EL素子駆動用のTFT40のソース43sは有機EL素子60のアノード層61に接続され、他方のドレイン43dは有機EL素子60に供給される電流源である駆動電源線53に接続されている。

【0021】図2に示すように、有機EL表示装置は、ガラスや合成樹脂などから成る基板又は導電性を有する基板あるいは半導体基板等の基板10上に、TFT及び有機EL素子を順に積層形成して成る。ただし、基板10として導電性を有する基板及び半導体基板を用いる場合には、これらの基板10上にSiO<sub>2</sub>やSiNなどの絶縁膜を形成した上にTFT30、40及び有機EL素子を形成する。いずれのTFTとともに、ゲート電極がゲート絶縁膜を介して能動層の上方にあるいわゆるトップゲート構造である。

【0022】次に、画素選択用TFT30、及び保持容量139の構造について詳細に説明する。図2(a)に示すように、石英ガラス、無アルカリガラス等からなる絶縁性基板10上に、非晶質シリコン膜(以下、「a-Si膜」と称する。)をCVD法等にて成膜し、そのa-Si膜にレーザ光を照射して溶融再結晶化させて多結晶シリコン膜(以下、「p-Si膜」と称する。)とし、これを能動層33とする。その上に、SiO<sub>2</sub>膜、SiN膜の単層あるいは積層体をゲート絶縁膜12として形成する。

【0023】更にその上に、Cr、Moなどの高融点金属からなるゲート電極31を兼ねたゲート信号線51、及びA1から成るドレイン信号線52を備えており、有機EL素子の駆動電源でありA1から成る駆動電源線53が配置されている。

【0024】そして、ゲート絶縁膜12及び能動層33

上の全面には、SiO<sub>2</sub>膜、SiN膜及びSiO<sub>2</sub>膜の順に積層された層間絶縁膜15が形成されており、ドレン33dに対応して設けたコンタクトホールにA1等の金属を充填したドレイン電極36が設けられ、更に全面に有機樹脂から成り表面を平坦にする第1平坦化絶縁膜17が形成されている。

【0025】次に保持容量130の構造について説明する。TFT30のソース33sは第1の容量電極層55を兼ねている。第1の容量電極層55と兼用されたTFT30のソース33s上には、ゲート絶縁膜12を介して第2の容量電極層54が設けられている。第2の容量電極層54は、Cr、Moなどの高融点金属から成り、ゲート電極31と同一の層で、同一工程で形成されている。第2の容量電極層54上には、層間絶縁膜15を介して、第3の容量電極層70が延設されている。第3の容量電極層70は、ドレイン電極36、ドレイン信号線52と同一の層で、同一工程で形成されている。また、第3の容量電極層70はコンタクトホールを介してTFT30のソース33sと接続されている。

【0026】即ち、保持容量139は、第2の容量電極層54を、絶縁膜を介して、第1の容量電極層55、第3の容量電極層70によって挟んだ多層構造となっているため、少ない占有面積で大きな容量を形成することができる。

【0027】また、第3の容量電極層70上に、第1平坦化絶縁膜17、第2平坦化絶縁膜19を介して、カソード層65を延設することにより、更に大きな容量を得ることが可能である。

【0028】次に、有機EL素子駆動用TFT40について説明する。図2(b)に示すように、石英ガラス、無アルカリガラス等からなる絶縁性基板10上に、a-Si膜にレーザ光を照射して多結晶化してなる能動層43、ゲート絶縁膜12、及びCr、Moなどの高融点金属からなるゲート電極41が順に形成されており、その能動層43には、チャネル43cと、このチャネル43cの両側にソース43s及びドレイン43dが設けられている。そして、ゲート絶縁膜12及び能動層43上の全面に、SiO<sub>2</sub>膜、SiN膜及びSiO<sub>2</sub>膜の順に積層された層間絶縁膜15を形成し、ドレン43dに対応して設けたコンタクトホールにA1等の金属を充填して駆動電源に接続された駆動電源線53が設けられている。また、ソース43sに対応して設けたコンタクトホールにA1等の金属を充填してソース電極56が設けられている。

【0029】更に全面に例えれば有機樹脂から成り表面を平坦にする第1平坦化絶縁膜17を備えている。そして、その第1平坦化絶縁膜17のソース電極56に対応した位置にコンタクトホールを形成し、このコンタクトホールを介してソース電極56と接続されたITOから成る透明電極、即ち有機EL素子のアノード層61が第

1平坦化絶縁膜17上に設けられている。このアノード層61は各画素部ごとに島状に分離形成されている。第1平坦化絶縁膜17上には、更に第2平坦化絶縁膜19が設けられているが、アノード層61上については、第2平坦化絶縁膜19は除去されている。

【0030】有機EL素子60は、ITO(Indium Tin Oxide)等の透明電極から成るアノード層61、MTD A T A (4,4-bis(3-methylphenylphenylamino)biphenyl)から成る第1ホール輸送層、TPD (4,4,4-tris(3-methylphenylphenylamino)triphenylamine)からなる第2ホール輸送層から成るホール輸送層62、キナクリドン(Quinacridone)誘導体を含むBebq2(10-ベンゾ[*h*]キノリノール-ベリリウム錯体)から成る発光層63、及びBebq2から成る電子輸送層64、マグネシウム・インジウム合金もしくはアルミニウム、もしくはアルミニウム合金から成るカソード層65が、この順番で積層形成された構造である。

【0031】有機EL素子60は、アノード層61から注入されたホールと、カソード層65から注入された電子とが発光層の内部で再結合し、発光層を形成する有機分子を励起して励起子が生じる。この励起子が放射失活する過程で発光層から光が放たれ、この光が透明なアノード層61から透明絶縁基板を介して外部へ放出されて発光する。

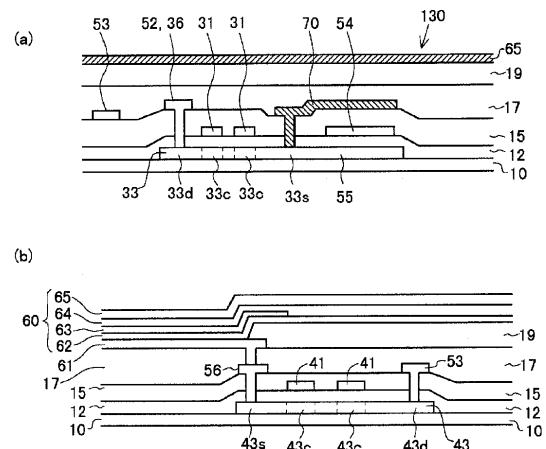

【0032】次に、本発明の第2の実施形態について説明する。図3は、画素部の断面図を示しており、図3(a)は、図1中のA-A線に沿った断面図、図3(b)は、図1中のB-B線に沿った断面図に対応している。なお、本実施形態についても当該画素部の等価回路は図3に示したものと同じである。

【0033】第1の実施形態では、保持容量139は、第2の容量電極層54を、絶縁膜を介して、第1の容量電極層55、第3の容量電極層70によって挟んだ多層構造であるが、本実施形態では更なる多層化を図り、単位面積当たりの容量値の増加を図ったものである。

【0034】本実施形態では、上記構成に加えて、第3の容量電極層70上に、更に第1平坦化絶縁膜17を介して第4の容量電極層71が延設されている。第4の容量電極層71は、アノード層61と同一の層で、同一工程で形成されている。

【0035】また、第4の容量電極層71上に、更に第2平坦化絶縁膜19を介して、カソード層65が延設されている。このカソード層65は、第5の容量電極層として機能するものである。

【0036】第1の実施形態では、第3の容量電極層70とカソード層65との間に容量が形成されているが、\*

\*その容量絶縁膜は、第1平坦化絶縁膜17及び第2平坦化絶縁膜19である。これに対して、本実施形態では、第4の容量電極層71とカソード層65との間に容量が形成される。その容量絶縁膜は第2平坦化絶縁膜19のみであるから、対向する容量電極間の容量絶縁膜が第1の実施形態に比して薄くなり、その分容量値を増加させることができる。

### 【0037】

【発明の効果】本発明のエレクトロルミネセンス表示装置によれば、駆動用トランジスタのゲートに供給されるビデオ信号を保持するための保持容量を多層構造の容量電極層で形成しているので、保持容量の形成面積を縮小することができる。また、開口率の低下を招くことなく、大きな保持容量を確保し、表示品位の向上を図ることができる。

【0038】また、開口率の低下を招くことがないで、有機EL素子に供給する電流を増加させる必要がなく、その結果として有機EL素子の寿命化を図ることができる。

### 【図面の簡単な説明】

【図1】本発明の実施形態に係る有機EL表示装置の画素部を示す平面図である。

【図2】本発明の実施形態に係る有機EL表示装置の画素部を示す断面図である。

【図3】本発明の実施形態に係る有機EL表示装置の画素部を示す断面図である。

【図4】有機EL表示装置の一画素の等価回路図である。

【図5】保持容量の構造を示す断面図である。

### 【符号の説明】

|     |          |     |              |    |          |

|-----|----------|-----|--------------|----|----------|

| 10  | 絶縁性基板    | 12  | ゲート絶縁膜       | 15 | 層間絶縁膜    |

| 17  | 第1平坦化絶縁膜 | 19  | 第2平坦化絶縁膜     |    |          |

| 30  | 画素選択用TFT | 31  | ゲート電極        | 33 | s ソース    |

| 33d | ドレイン     | 40  | 有機EL素子駆動用TFT |    |          |

| 41  | ゲート電極    | 43s | ソース          | 51 | ゲート信号線   |

| 52  | ドレイン信号線  | 54  | 第2の容量電極層     |    |          |

| 60  | 有機EL素子   |     |              |    |          |

| 61  | アノード     | 62  | ホール輸送層       | 63 | 発光素子層    |

| 64  | 電子輸送層    | 65  | カソード層        | 70 | 第3の容量電極層 |

| 71  | 第4の容量電極層 |     |              |    |          |

【図1】

【図2】

【図5】

【図3】

【図4】

|                |                                                                                                                                                                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 电致发光显示装置                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2003323133A</a>                                                                                                                                                                                                                                                        | 公开(公告)日 | 2003-11-14 |

| 申请号            | JP2002128008                                                                                                                                                                                                                                                                         | 申请日     | 2002-04-30 |

| [标]申请(专利权)人(译) | 三洋电机株式会社                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 三洋电机株式会社                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 安齋勝矢                                                                                                                                                                                                                                                                                 |         |            |

| 发明人            | 安齋 勝矢                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | H01L51/50 G09F9/30 G09G3/00 G09G3/30 H01L27/32 H05B33/14                                                                                                                                                                                                                             |         |            |

| CPC分类号         | H01L27/1255 H01L27/1214 H01L27/3265                                                                                                                                                                                                                                                  |         |            |

| FI分类号          | G09F9/30.338 G09F9/30.336 G09F9/30.365.Z H05B33/14.A G09F9/30.365 H01L27/32                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 3K007/AB02 3K007/AB03 3K007/AB11 3K007/AB17 3K007/DB03 3K007/GA00 5C094/AA07 5C094 /AA31 5C094/BA03 5C094/BA27 5C094/CA19 5C094/DA13 5C094/DA15 5C094/DB04 5C094/FA02 5C094/FB02 5C094/FB15 5C094/FB19 5C094/HA08 3K107/AA01 3K107/BB01 3K107/CC21 3K107 /CC36 3K107/EE03 3K107/HH05 |         |            |

| 其他公开文献         | JP4027149B2<br>JP2003323133A5                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                            |         |            |

## 摘要(译)

要解决的问题：通过减小用于保持提供给EL显示装置中的驱动晶体管的栅极的视频信号的保持电容形成区域来改善显示质量并延长有机EL元件的寿命。

ŽSOLUTION：在作为第一电容电极层55的TFT30的源极33s上，经由栅极绝缘膜12形成第二电容电极层54。第二电容电极层54是与栅电极31相同的层。并通过相同的过程形成。在第二电容电极层54上，经由层间绝缘电极膜15延伸地布置第三电容层70。第三电容电极层70形成在与漏电极36和漏极信号线52相同的层中。电容层70连接到TFT 30的源极33s。