(19) 日本国特許庁 (JP)

## 再公表特許(A1)

(11) 国際公開番号

WO2005/013249

発行日 平成18年9月28日(2006.9.28)

(43) 国際公開日 平成17年2月10日(2005.2.10)

| (51) Int.Cl.                | F I       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/30 (2006.01)</b>  | G09G 3/30 | K 3KO07     |

| <b>G09G 3/20 (2006.01)</b>  | G09G 3/20 | 612U 5CO80  |

| <b>H01L 51/50 (2006.01)</b> | G09G 3/20 | 623C        |

|                             | G09G 3/20 | 641D        |

|                             | G09G 3/20 | 642E        |

審査請求 未請求 予備審査請求 未請求 (全 88 頁) 最終頁に続く

|              |                              |            |                                                   |

|--------------|------------------------------|------------|---------------------------------------------------|

| 出願番号         | 特願2005-512611 (P2005-512611) | (71) 出願人   | 302020207<br>東芝松下ディスプレイテクノロジー株式会社<br>東京都港区港南4-1-8 |

| (21) 國際出願番号  | PCT/JP2004/011416            | (74) 代理人   | 100092794<br>弁理士 松田 正道                            |

| (22) 國際出願日   | 平成16年8月3日 (2004.8.3)         | (72) 発明者   | 前田 智之<br>東京都港区港南四丁目1番8号 東芝松下<br>ディスプレイテクノロジー株式会社内 |

| (31) 優先権主張番号 | 特願2003-287214 (P2003-287214) | F ターム (参考) | 3K007 AB11 BA06 DB03 GA00                         |

| (32) 優先日     | 平成15年8月5日 (2003.8.5)         |            |                                                   |

| (33) 優先権主張国  | 日本国 (JP)                     |            |                                                   |

| (31) 優先権主張番号 | 特願2004-17653 (P2004-17653)   |            |                                                   |

| (32) 優先日     | 平成16年1月26日 (2004.1.26)       |            |                                                   |

| (33) 優先権主張国  | 日本国 (JP)                     |            |                                                   |

最終頁に続く

(54) 【発明の名称】自己発光表示装置の駆動回路、およびその駆動方法

(57) 【要約】

有機ELには素子寿命と言う問題がある。素子寿命の原因には温度、電流量などがある。また、有機EL素子を用いたディスプレイは電流を用いて発光させるため、画面の発光量とデバイスに流れる電流量が比例するため、発光量の大きい画像ではデバイスに大きな電流が流れ、素子劣化が起きると言う問題や、最大の電流量を流すために大容量の電源を持たなくてはならないなどの問題があった。有機EL素子を用いたディスプレイは画面の発光量とデバイスに流れる電流量が比例の関係にあるため、素子の最大発光量をあげればあげるほど、画面の全ての素子が最大発光したときの電流が大きくなる。また、素子の最大発光量を抑えると画面全体が暗くなる。そのため、画面の表示状態によって素子の発光量を制御する駆動を行う。

**【特許請求の範囲】****【請求項 1】**

各画素を構成する複数の自己発光素子が画素列方向と画素行方向にマトリクス状に配置され、前記各自己発光素子のアノード電極とカソード電極の間に電流を流すことにより前記各画素を発光させることで表示部を駆動するための自己発光表示装置の駆動方法であって、

外部から入力される映像データに対応して、前記アノード電極と前記カソード電極の間に流れるべき第1の電流量を取得し、かつ前記第1の電流量は前記映像データ周辺の映像データ値分布状況によらず、予め定められた単一の値を取得する処理を行う第1の処理と、

外部から入力される前記映像データに対応して、前記アノード電極と前記カソード電極の間に流れるべき第2の電流量を取得し、かつ前記第2の電流量は前記映像データ周辺の前記映像データ値分布状況によって、前記第1の電流量が所定の割合で抑制された値が1つ準備され、かつ前記抑制割合は前記映像データ値分布状況に応じて可変である処理を行う第2の処理と、

前記第1または前記第2の処理手段の結果に基づき、前記画素行毎に流れる電流量を制御することで、前記表示部を発光させる自己発光表示装置の駆動方法。

**【請求項 2】**

外部から入力される前記映像データの階調値が、第1の所定の階調値よりも、黒表示を行う為の低階調側のときに、前記第1の処理により対応する前記各自己発光素子の前記アノード電極と前記カソード電極の間に印加される前記第1の電流量が決定される請求の範囲第1項記載の、自己発光表示装置の駆動方法。

**【請求項 3】**

外部から入力される前記映像データの階調値が、第1の所定の階調値よりも、白表示を行う為の高階調側のときに、前記第2の処理により対応する前記各自己発光素子の前記アノード電極と前記カソード電極の間に印加される前記第2の電流量 $x$ が決定され、このとき前記階調値に対し前記第1の処理を行った場合の前記第1の電流量を $y$ としたとき、前記第1の電流量 $y$ と前記第2の電流量 $x$ の間に、

$$0.20y \times 0.60y$$

の関係が成立する請求の範囲第1項記載の、自己発光表示装置の駆動方法。

**【請求項 4】**

前記印加電流量は、第1の期間に外部から入力される前記映像データの最大値である電流値 $i_1$ を取得し、第2の期間に入力される前記映像データから適正な電流値 $i_2$ を演算により求め、前記第2の期間に入力される所定の前記映像データに基づき表示される前記各画素に印加する電流量を比率 $i_2 / i_1$ に基づき順次算出する処理により決定される請求の範囲第1項から第3項の何れかに記載の、自己発光表示装置の駆動方法。

**【請求項 5】**

前記印加電流量は、入力される前記映像データの最大値である第3の電流値 $i_3$ を取得し、前記各自己発光素子の前記アノード電極と前記カソード電極の間に実際に電流を印加し、最適値をもとめその値を前記第2の電流値 $i_4$ とし、比率 $i_4 / i_3$ を入力される前記映像データに乗算することにより、所定の前記映像データに基づき表示される前記各画素に印可する電流量を順次算出することで決定される請求の範囲第1項から第3項の何れかに記載の、表示装置の駆動方法。

**【請求項 6】**

外部から入力される前記映像データの階調値が、第1の所定の階調値よりも、白表示を行う為の高階調側で、前記各自己発光素子の前記アノード電極と前記カソード電極の間に印加される電流量は黒挿入率で制御される請求の範囲第1項から第3項の何れかに記載の、自己発光表示装置の駆動方法。

**【請求項 7】**

前記黒挿入は1行目から順に終端行まで行われ、1フレーム内で黒領域は一括して挿入さ

れる請求の範囲第 6 項記載の、自己発光表示装置の駆動方法。

【請求項 8】

前記黒挿入は前記 1 行目から順に前記終端行まで行われ、前記 1 フレーム内で前記黒領域は複数の領域に分割して挿入される請求の範囲第 7 項記載の、自己発光表示装置の駆動方法。

【請求項 9】

前記黒挿入は、1 フレーム内で黒領域は複数の領域に分割して挿入され、1 行目から終端行まで順番に行われるのではなく、順番を入れ替えながら挿入される請求の範囲第 6 項記載の、自己発光表示装置の駆動方法。

【請求項 10】

外部から入力される前記映像データの階調値が、第 1 の所定の階調値よりも、白表示を行う為の高階調側で、前記各自己発光素子の前記アノード電極と前記カソード電極の間に印加される電流量はソース線群に流れる電流量を調整することで制御される請求の範囲第 1 項から第 3 項の何れかに記載の、自己発光表示装置の駆動方法。

10

【請求項 11】

前記ソース線群に流れる前記電流量の前記調整が、基準電流値を増減することにより行われる請求の範囲第 10 項記載の、自己発光表示装置の駆動方法。

【請求項 12】

前記ソース線群に流れる前記電流量の前記調整が、階調数を増減することにより行われる請求の範囲第 10 項記載の、自己発光表示装置の駆動方法。

20

【請求項 13】

第 1 のフレーム期間に前記各自己発光素子の前記アノード電極と前記カソード電極の間に流れる第 1 の電流と、前記第 1 のフレーム期間の次の第 2 のフレーム期間に流れる前記第 2 の電流との差分を取得し、差分値を  $1 / n$  ( $n$  は 1 以上の数) にした  $n$  差分電流値を演算し、前記  $n$  差分電流値より画素行の選択値を決定する請求の範囲第 1 項から第 3 項の何れかに記載の、自己発光表示装置の駆動方法。

【請求項 14】

前記  $n$  値は、 $4 \leq n \leq 6$  である請求の範囲第 13 項記載の、自己発光表示装置の駆動方法。

30

【請求項 15】

前記各自己発光素子の前記アノード電極と前記カソード電極の間に流れる電流量によって、定数が最適になるよう補正される請求の範囲第 1 項から第 3 項の何れかに記載の、自己発光表示装置の駆動方法。

【請求項 16】

前記 定数は複数の 曲線の中間値を順次組み合わせて構成される曲線上の点の集合である請求の範囲第 15 項記載の、自己発光表示装置の駆動方法。

【請求項 17】

前記 定数の増減は前記自己発光素子の発光期間の長短により調整される請求の範囲第 15 項記載の、自己発光表示装置の駆動方法。

【請求項 18】

前記第 2 の処理手段に対するスイッチング手段を配設し前記第 2 の処理の入切を制御することで、入にしたときには前記第 1 の処理と前記第 2 の処理の組み合わせで前記各自己発光素子の前記アノード電極と前記カソード電極の間に流れる電流量を決定し、切にしたときには前記第 1 の処理のみで前記各自己発光素子の前記アノード電極と前記カソード電極の間に流れる電流量を決定する請求の範囲第 1 項から第 3 項の何れかに記載の、自己発光表示装置の駆動方法。

40

【発明の詳細な説明】

【技術分野】

本発明は、有機または無機エレクトロルミネッセンス (EL) 素子を用いた EL 表示パネルなどの自発光表示パネルに関するものである。また、これらの表示パネルなどの駆動

50

回路( I C )に関するものである。 E L 表示パネルなどの駆動方法と駆動回路およびそれらを用いた情報表示装置などに関するものである。

#### 【背景技術】

一般に、アクティブマトリクス型表示装置では、多数の画素をマトリクス状に並べ、与えられた映像信号に応じて画素毎に光強度を制御することによって画像を表示する。たとえば、電気光学物質として液晶を用いた場合は、各画素に書き込まれる電圧に応じて画素の透過率が変化する。電気光学変換物質として有機エレクトロルミネッセンス( E L )材料を用いたアクティブマトリクス型の画像表示装置は画素に書き込まれる電流に応じて発光輝度が変化する。

液晶表示パネルは、各画素はシャッタとして動作し、バックライトからの光を画素であるシャッタでオンオフさせることにより画像を表示する。有機 E L 表示パネルは各画素に発光素子を有する自発光型である。そのため、有機 E L 表示パネルは、液晶表示パネルに比べて画像の視認性が高い、バックライトが不要、応答速度が速い等の利点を有する。10

有機 E L 表示パネルは各発光素子(画素)の輝度は電流量によって制御される。つまり、発光素子が電流駆動型あるいは電流制御型であるという点で液晶表示パネルとは大きく異なる。

有機 E L 表示パネルも単純マトリクス方式とアクティブマトリクス方式の構成が可能である。前者は構造が単純であるものの大型かつ高精細の表示パネルの実現が困難である。しかし、安価である。後者は大型、高精細表示パネルを実現できる。しかし、制御方法が技術的に難しい、比較的高価であるという課題がある。現在では、アクティブマトリクス方式の開発が盛んに行われている。アクティブマトリクス方式は、各画素に設けた発光素子に流れる電流を画素内部に設けた薄膜トランジスタ(トランジスタ)によって制御する。20

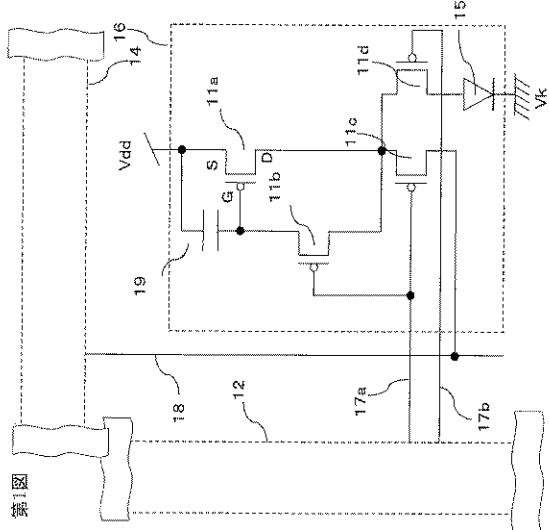

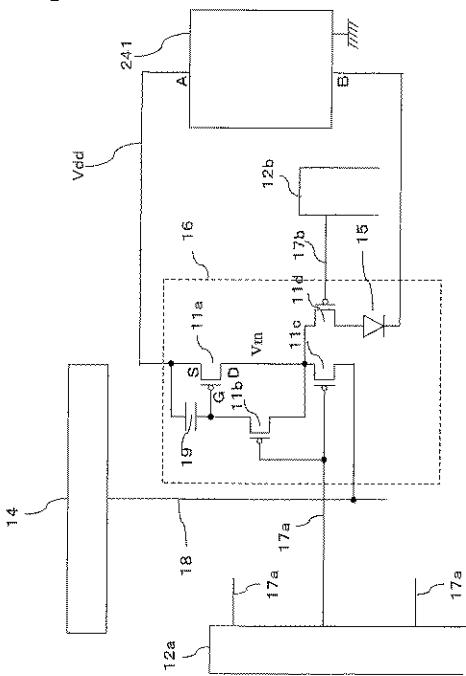

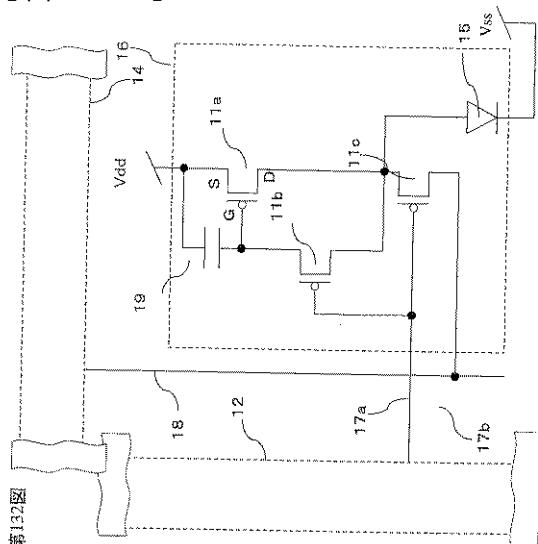

このアクティブマトリクス方式の有機 E L 表示パネルは、画素 1 6 は発光素子である E L 素子 1 5 、第 1 のトランジスタ 1 1 a 、第 2 のトランジスタ 1 1 b および蓄積容量 1 9 からなる。発光素子 1 5 は有機エレクトロルミネッセンス( E L )素子である。本発明では、 E L 素子 1 5 に電流を供給(制御)するトランジスタ 1 1 a を駆動用トランジスタ 1 1 と呼ぶ。

有機 E L 素子 1 5 は多くの場合、整流性があるため、 O L E D (有機発光ダイオード)と呼ばれることがある。図 1 などでは発光素子 1 5 としてダイオードの記号を用いている。30

ただし、本発明における発光素子 1 5 は O L E D に限るものではなく、素子 1 5 に流れる電流量によって輝度が制御されるものであればよい。たとえば、無機 E L 素子が例示される。その他、半導体で構成される白色発光ダイオードが例示される。また、一般的な発光ダイオードが例示される。その他、発光トランジスタでもよい。また、発光素子 1 5 は必ずしも整流性が要求されるものではない。双方向性ダイオードであってもよい。本発明の E L 素子 1 5 はこのいずれでもよい。

有機 E L には素子寿命と言う問題がある。素子寿命の原因には温度、電流量などがある。また、有機 E L 素子を用いたディスプレイは電流を用いて発光させるため、画面の発光量とデバイスに流れる電流量が比例するため、発光量の大きい画像ではデバイスに大きな電流が流れ、素子劣化が起きると言う問題や、最大の電流量を流すために大容量の電源を持たなくてはならないなどの問題があった。40

#### 【発明の開示】

有機 E L 素子を用いたディスプレイは画面の発光量とデバイスに流れる電流量が比例の関係にあるため、素子の最大発光量をあげればあげるほど、画面の全ての素子が最大発光したときの電流が大きくなる。また、素子の最大発光量を抑えると画面全体が暗くなる。そのため、画面の表示状態によって素子の発光量を制御する駆動を行う。

第 1 の本発明は、各画素を構成する複数の自己発光素子が画素列方向と画素行方向にマトリクス状に配置され、前記各自己発光素子のアノード電極とカソード電極の間に電流を流すことにより前記各画素を発光させることで表示部を駆動するための自己発光表示装置の駆動方法であって、50

外部から入力される映像データに対応して、前記アノード電極と前記カソード電極の間に流れるべき第1の電流量を取得し、かつ前記第1の電流量は前記映像データ周辺の映像データ値分布状況によらず、予め定められた単一の値を取得する処理を行う第1の処理と、

外部から入力される前記映像データに対応して、前記アノード電極と前記カソード電極の間に流れるべき第2の電流量を取得し、かつ前記第2の電流量は前記映像データ周辺の前記映像データ値分布状況によって、前記第1の電流量が所定の割合で抑制された値が1つ準備され、かつ前記抑制割合は前記映像データ値分布状況に応じて可変である処理を行う第2の処理と、

前記第1または前記第2の処理手段の結果に基づき、前記画素行毎に流れる電流量を制御することで、前記表示部を発光させる自己発光表示装置の駆動方法である。 10

第2の本発明は、外部から入力される前記映像データの階調値が、第1の所定の階調値よりも、黒表示を行う為の低階調側のときに、前記第1の処理により対応する前記各自己発光素子の前記アノード電極と前記カソード電極の間に印加される前記第1の電流量が決定される第1の本発明の、自己発光表示装置の駆動方法である。

第3の本発明は、外部から入力される前記映像データの階調値が、第1の所定の階調値よりも、白表示を行う為の高階調側のときに、前記第2の処理により対応する前記各自己発光素子の前記アノード電極と前記カソード電極の間に印加される前記第2の電流量 $x$ が決定され、このとき前記階調値に対し前記第1の処理を行った場合の前記第1の電流量を $y$ としたとき、前記第1の電流量 $y$ と前記第2の電流量 $x$ の間に、 20

$$0.20y \times 0.60y$$

の関係が成立する第1の本発明の、自己発光表示装置の駆動方法である。

第4の本発明は、前記印加電流量は、第1の期間に外部から入力される前記映像データの最大値である電流値 $i_1$ を取得し、第2の期間に入力される前記映像データから適正な電流値 $i_2$ を演算により求め、前記第2の期間に入力される所定の前記映像データに基づき表示される前記各画素に印加する電流量を比率 $i_2 / i_1$ に基づき順次算出する処理により決定される第1から第3の何れかの本発明の、自己発光表示装置の駆動方法である。

第5の本発明は、前記印加電流量は、入力される前記映像データの最大値である第3の電流値 $i_3$ を取得し、前記各自己発光素子の前記アノード電極と前記カソード電極の間に実際に電流を印加し、最適値をもとめその値を前記第2の電流値 $i_4$ とし、比率 $i_4 / i_3$ を入力される前記映像データに乗算することにより、所定の前記映像データに基づき表示される前記各画素に印可する電流量を順次算出することで決定される第1から第3の何れかの本発明の、表示装置の駆動方法である。 30

第6の本発明は、外部から入力される前記映像データの階調値が、第1の所定の階調値よりも、白表示を行う為の高階調側で、前記各自己発光素子の前記アノード電極と前記カソード電極の間に印加される電流量は黒挿入率で制御される第1から第3の何れかの本発明の、自己発光表示装置の駆動方法である。

第7の本発明は、前記黒挿入は1行目から順に終端行まで行われ、1フレーム内で黒領域は一括して挿入される第6の本発明の、自己発光表示装置の駆動方法である。 40

第8の本発明は、前記黒挿入は前記1行目から順に前記終端行まで行われ、前記1フレーム内で前記黒領域は複数の領域に分割して挿入される第7の本発明の、自己発光表示装置の駆動方法である。

第9の本発明は、前記黒挿入は、1フレーム内で黒領域は複数の領域に分割して挿入され、1行目から終端行まで順番に行われるのではなく、順番を入れ替えながら挿入される第6の本発明の、自己発光表示装置の駆動方法である。

第10の本発明は、外部から入力される前記映像データの階調値が、第1の所定の階調値よりも、白表示を行う為の高階調側で、前記各自己発光素子の前記アノード電極と前記カソード電極の間に印加される電流量はソース線群に流れる電流量を調整することで制御される第1項から第3の何れかの本発明の、自己発光表示装置の駆動方法である。

第11の本発明は、前記ソース線群に流れる前記電流量の前記調整が、基準電流値を増

減することにより行われる第10の本発明の、自己発光表示装置の駆動方法である。

第12の本発明は、前記ソース線群に流れる前記電流量の前記調整が、階調数を増減することにより行われる第10の本発明の、自己発光表示装置の駆動方法である。

第13の本発明は、第1のフレーム期間に前記各自己発光素子の前記アノード電極と前記カソード電極の間に流れる第1の電流と、前記第1のフレーム期間の次の第2のフレーム期間に流れる前記第2の電流との差分を取得し、差分値を $1/n$ (nは1以上の数)にしたn差分電流値を演算し、前記n差分電流値より画素行の選択値を決定する第1から第3の何れかの本発明の、自己発光表示装置の駆動方法である。

第14の本発明は、前記n値は、 $4 \leq n \leq 256$ である第13の本発明の、自己発光表示装置の駆動方法である。

10

第15の本発明は、前記各自己発光素子の前記アノード電極と前記カソード電極の間に流れる電流量によって、定数が最適になるよう補正される第1から第3の何れかの本発明の、自己発光表示装置の駆動方法である。

第16の本発明は、前記定数は複数の曲線の中間値を順次組み合わせて構成される曲線上の点の集合である第15の本発明の、自己発光表示装置の駆動方法である。

第17の本発明は、前記定数の増減は前記自己発光素子の発光期間の長短により調整される第15の本発明の、自己発光表示装置の駆動方法である。

第18の本発明は、前記第2の処理手段に対するスイッチング手段を配設し前記第2の処理の入切を制御することで、入にしたときには前記第1の処理と前記第2の処理の組み合わせで前記各自己発光素子の前記アノード電極と前記カソード電極の間に流れる電流量を決定し、切にしたときには前記第1の処理のみで前記各自己発光素子の前記アノード電極と前記カソード電極の間に流れる電流量を決定する第1から第3の何れかの本発明の、自己発光表示装置の駆動方法である。

20

第19の本発明は、各画素を構成する複数の自己発光素子が画素列方向と画素行方向にマトリクス状に配置され、前記各自己発光素子のアノード電極とカソード電極の間に電流を流すことにより前記各画素を発光させることで表示部を駆動するための自己発光表示装置の駆動回路であって、

前記各自己発光素子を、外部から入力される映像データに対応して予め設定された第1の輝度で発光させる第1の発光手段と、

前記各自己発光素子を周囲の前記各画素の発光輝度分布に併せて、外部から入力される前記映像データに対応して予め設定された前記第1の輝度を抑制するよう調整した第2の輝度で発光させる第2の発光手段とを備えた自己発光表示装置の駆動回路である。

30

第20の本発明は、各画素を構成する複数の自己発光素子が画素列方向と画素行方向にマトリクス状に配置され、前記各自己発光素子のアノード電極とカソード電極の間に電流を流すことにより前記各画素を発光させることで表示部を駆動するための自己発光表示装置の駆動回路であって、

外部から入力される映像データに対応して、前記アノード電極と前記カソード電極の間に流れるべき第1の電流量を設定し、かつ前記第1の電流量は前記映像データ周辺の映像データ値分布状況によらず、予め定められた単一の値を設定する処理を行う第1の処理手段と、

40

外部から入力される前記映像データに対応して、前記アノード電極と前記カソード電極の間に流れるべき第2の電流量を設定し、かつ前記第2の電流量は前記映像データ周辺の前記映像データ値分布状況によって、前記第1の電流量が所定の割合で抑制された値が1つ準備され、かつ前記抑制割合は前記映像データ値分布状況に応じて可変である処理を行う第2の処理手段と、

前記第1及び前記第2の処理手段の結果に基づき、前記画素行毎に流れる電流量を制御する制御手段とを備えた自己発光表示装置の駆動回路である。

第21の本発明は、前記第2の処理回路は、外部から入力される前記映像データを基に演算処理により画素行毎の前記第2の電流量を決定する処理を行う第20の本発明の、自己発光表示装置の駆動回路である。

50

第22の本発明は、前記演算処理は、第1の期間に外部から入力される前記映像データの最大値である電流値*i*1を取得し、第2の期間に入力される前記映像データから適正な電流値*i*2を演算により求め、前記第2の期間に入力される所定の前記映像データに基づき表示される前記各画素に印加する電流量を比率*i*2/*i*1に基づき順次算出する処理である第21の本発明の、自己発光表示装置の駆動回路である。

第23の本発明は、前記第2の処理回路は、外部から入力される前記映像データを測定する手段を有し、前記測定結果を基に画素行毎の前記第2の電流量を決定する演算処理を行う第20の本発明の、自己発光表示装置の駆動回路である。

第24の本発明は、前記演算処理は、外部から入力される前記映像データの最大値である第3の電流値*i*3を取得し、前記各自己発光素子の前記アノード電極と前記カソード電極の間に実際に電流を印加し、最適値をもとめその値を第2の電流値*i*4とし、比率*i*4/*i*3を入力される前記映像データに乗算することにより、所定の前記映像データに基づき表示される前記各画素に印可する電流量を順次算出する処理である第23の本発明の、自己発光表示装置の駆動回路である。

第25の本発明は、前記第1の処理手段のみで動作させるための、前記第2の処理手段に対するスイッチング手段を備えた第19から第24の何れかの本発明の、自己発光表示装置の駆動回路である。

第26の本発明は、第19から第24の何れかの本発明の、駆動回路を有する自己発光表示装置のコントローラである。

第27の本発明は、第19から第24の何れかの本発明の、駆動回路を備えた、前記自己発光素子が前記画素列方向と前記画素行方向にマトリクス状に形成または配置された自己発光表示装置である。

#### 【図面の簡単な説明】

図1は、本発明における表示パネルの画素構成図である。

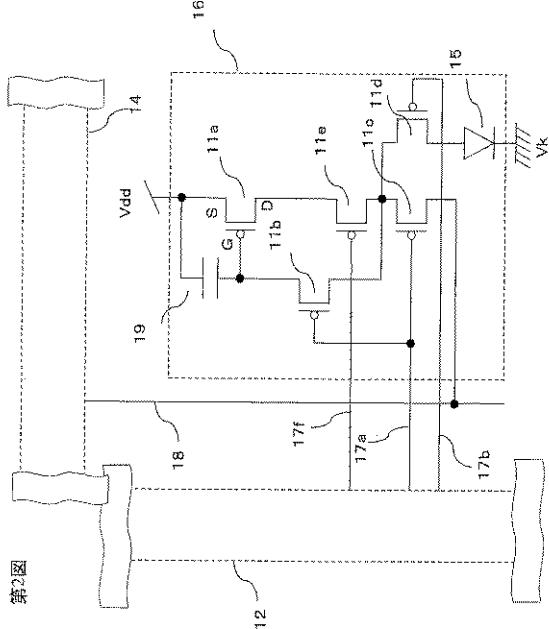

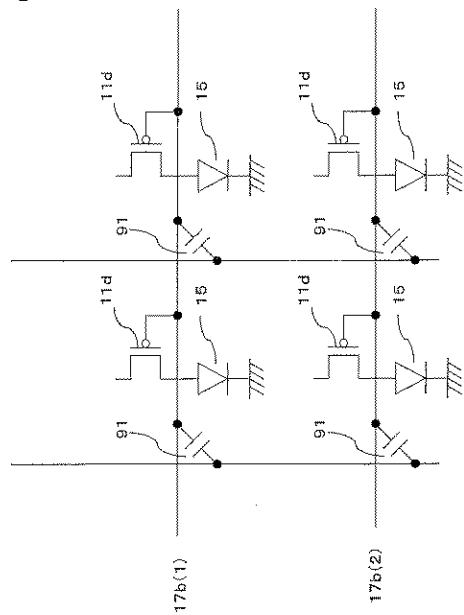

図2は、本発明における表示パネルの画素構成図である。

図3は、本発明の駆動時の流れを示した図である。

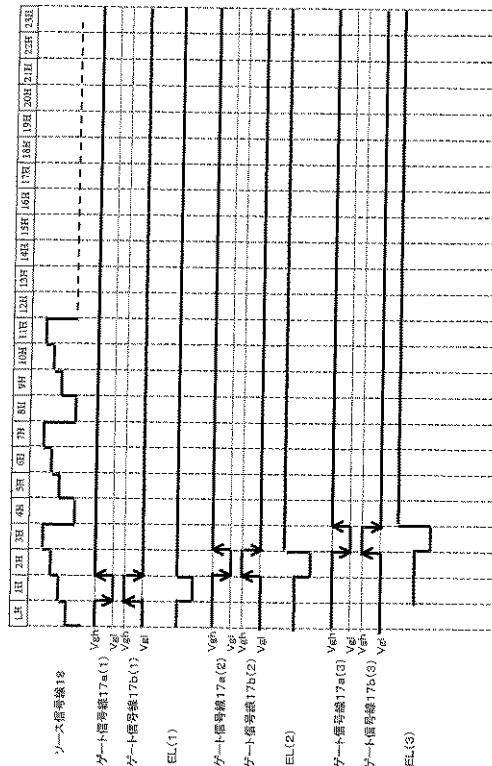

図4は、本発明の駆動波形を示した図である。

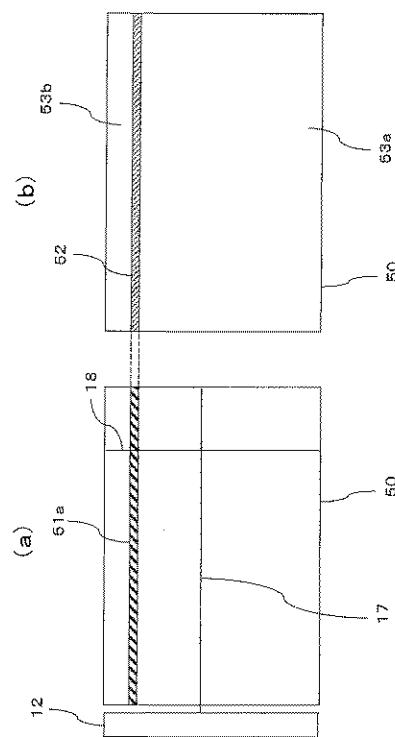

図5は、本発明の表示パネルの表示領域の説明である。

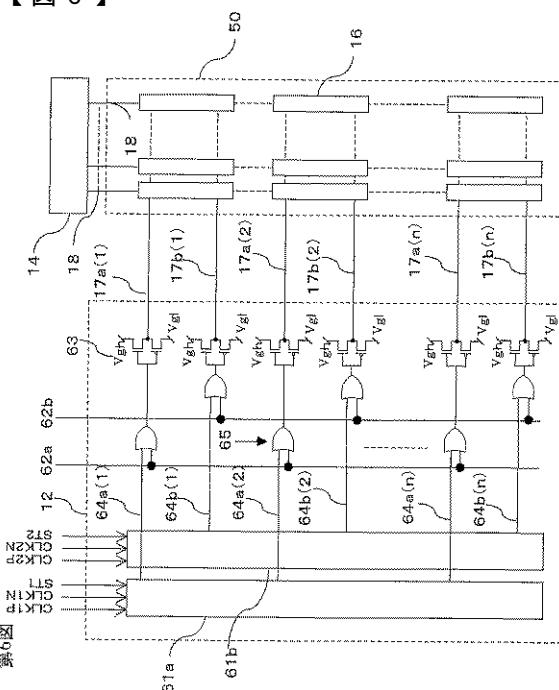

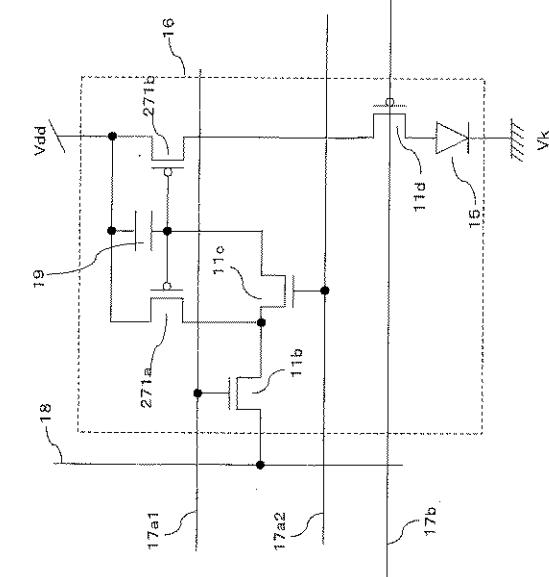

図6は、本発明における表示パネルの画素構成図である。

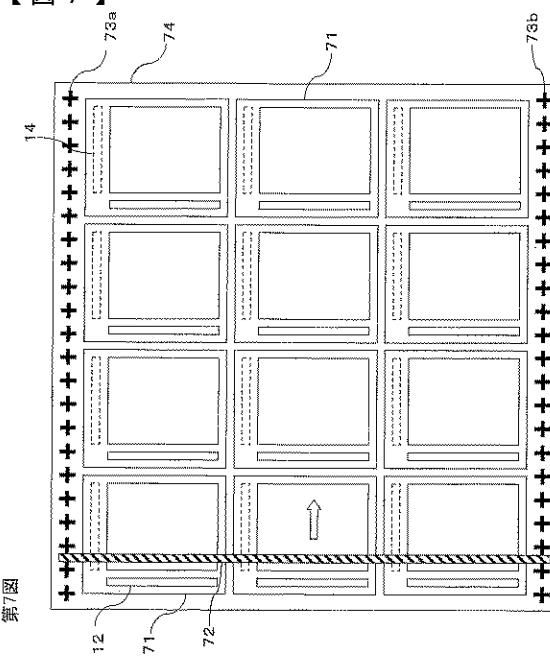

図7は、本発明の表示パネルの製造方法の説明図である。

30

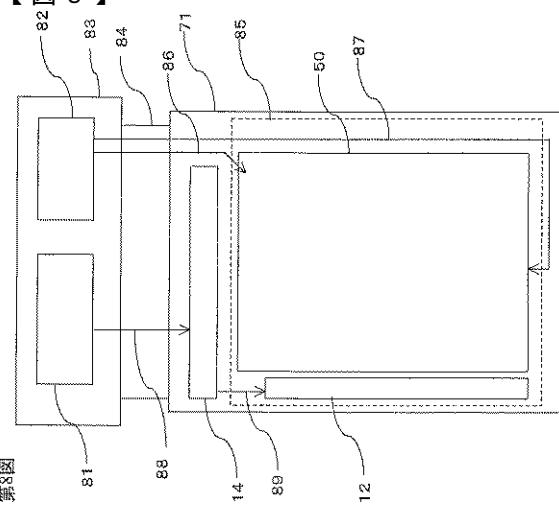

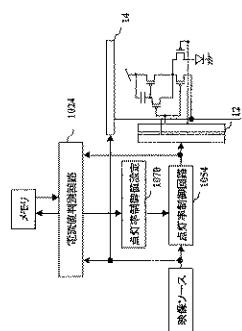

図8は、本発明のパネルの構成図である。

図9は、ソース信号線とゲート信号線の間の浮遊容量について説明した図である。

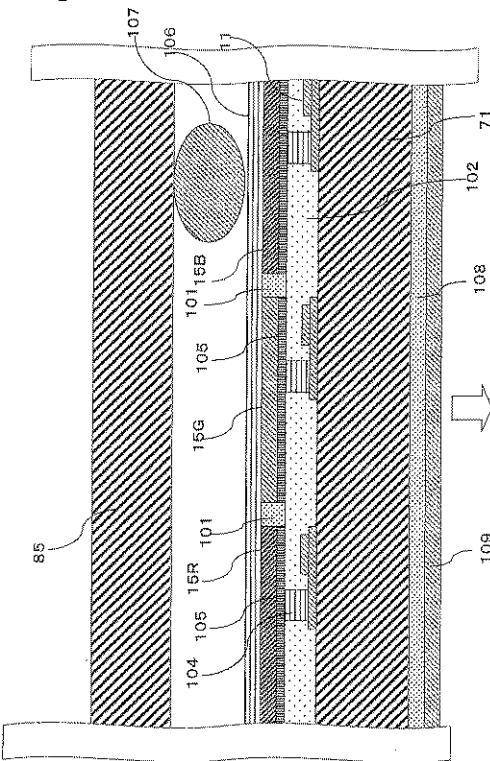

図10は、本発明の表示パネルの断面図である。

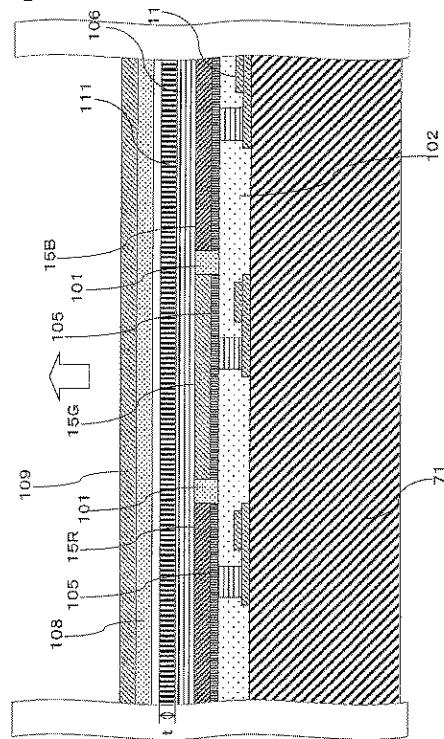

図11は、本発明の表示パネルの断面図である。

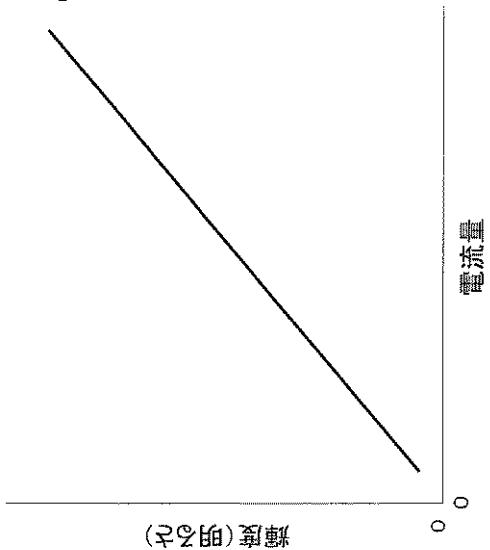

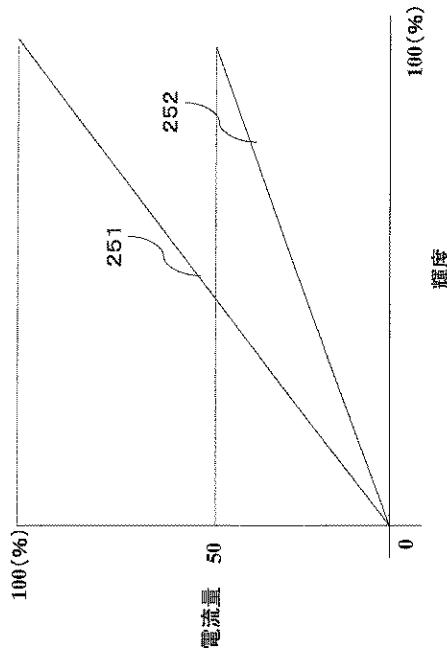

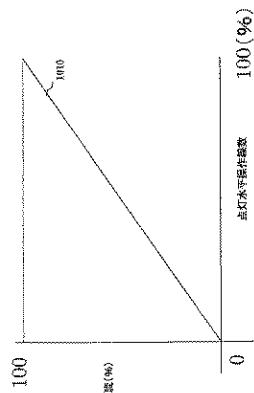

図12は、ソースラインの電流量とパネルの明るさの関係図である。

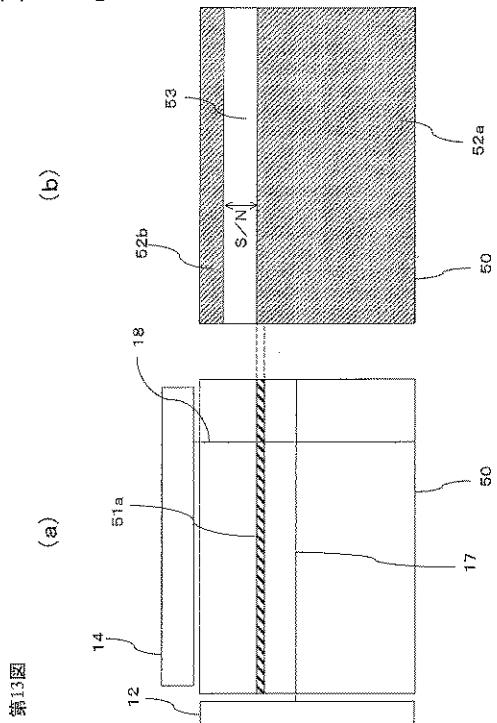

図13は、表示パネルの表示状態の説明図である。

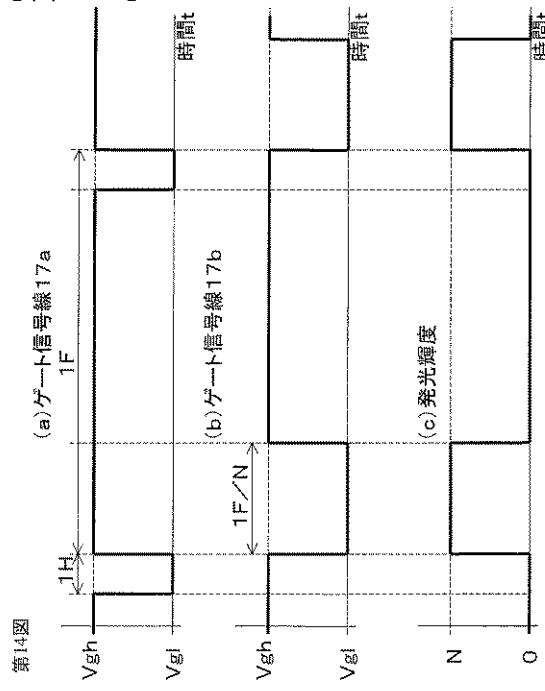

図14は、本発明の駆動波形を示した図である。

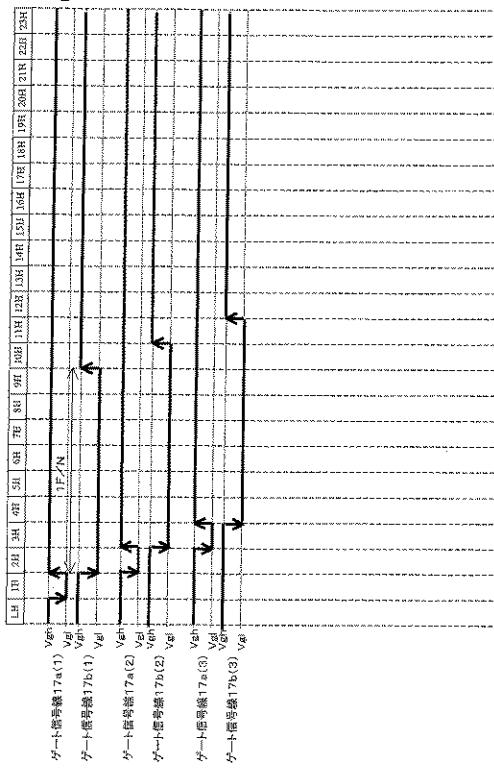

図15は、本発明の駆動波形を示した図である。

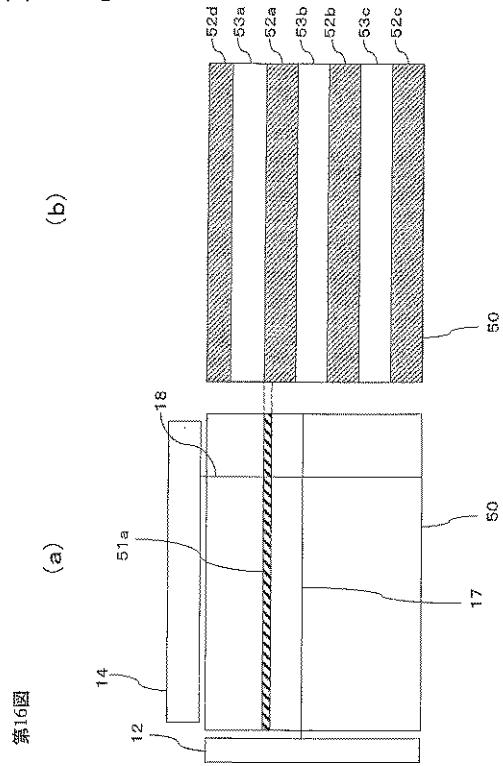

図16は、表示パネルの表示状態の説明図である。

40

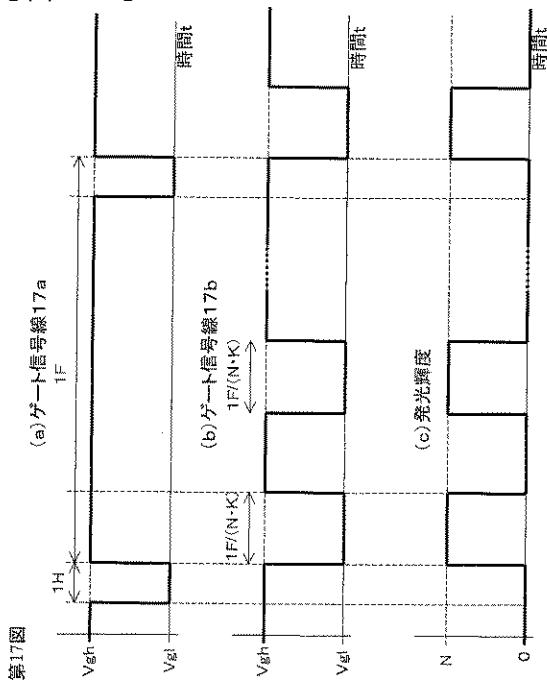

図17は、本発明の駆動波形を示した図である。

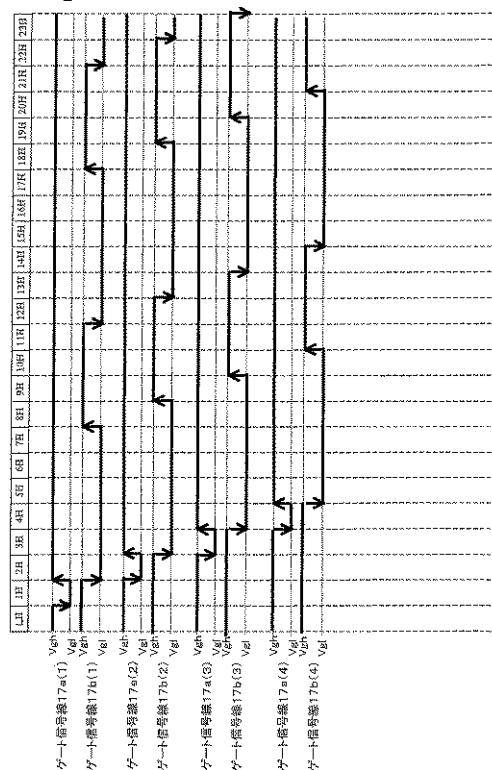

図18は、本発明の駆動波形を示した図である。

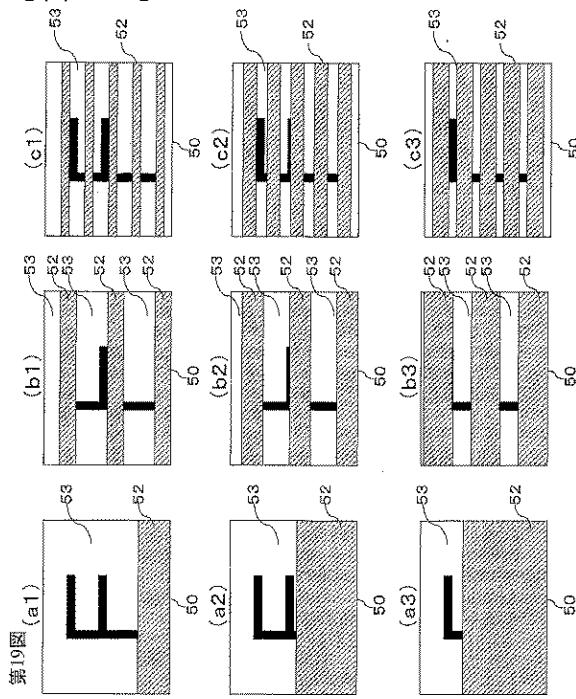

図19は、表示パネルの表示状態の説明図である。

図20は、表示パネルの表示状態の説明図である。

図21は、本発明の駆動波形を示した図である。

図22は、表示パネルの表示状態の説明図である。

図23は、本発明の駆動波形を示した図である。

図24は、画素構成とバッテリーの関係図である。

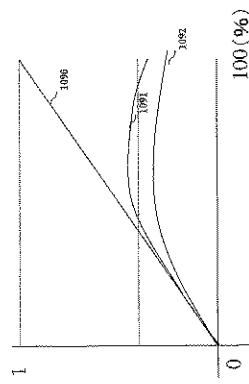

図25は、表示領域の輝度と電流量の関係図である。

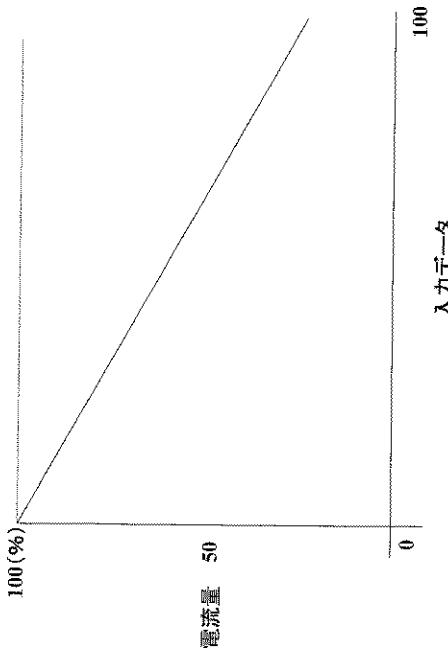

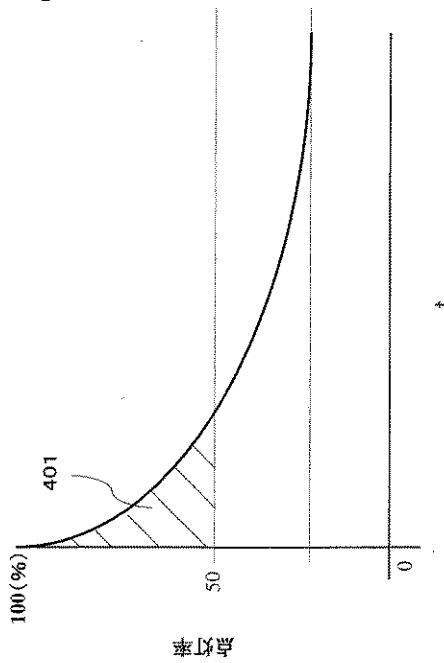

図26は、本発明における入力データと電流量の関係図である。

50

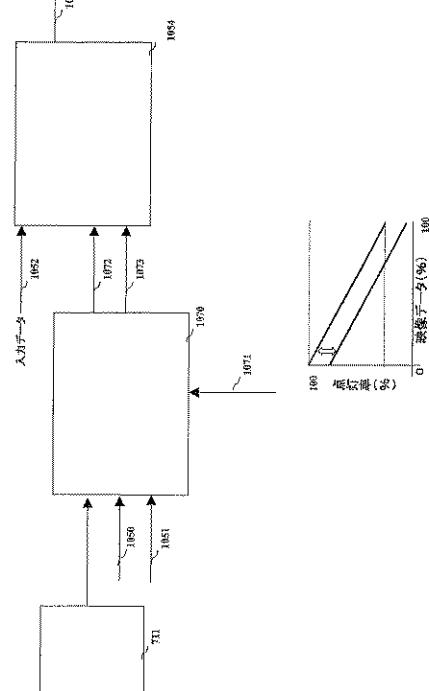

図27は、本発明の回路構成図である。

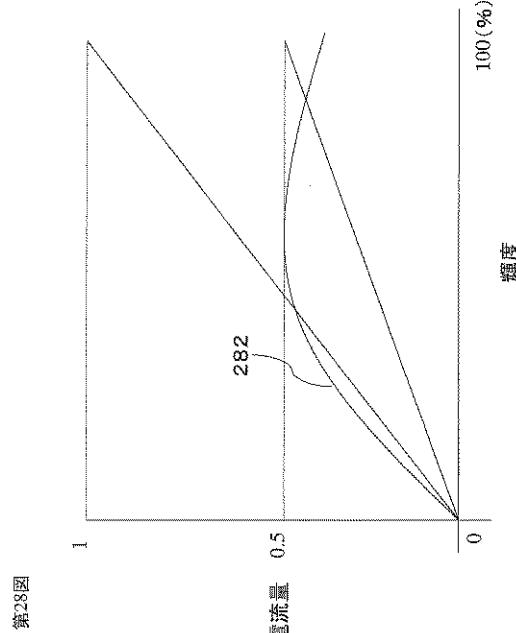

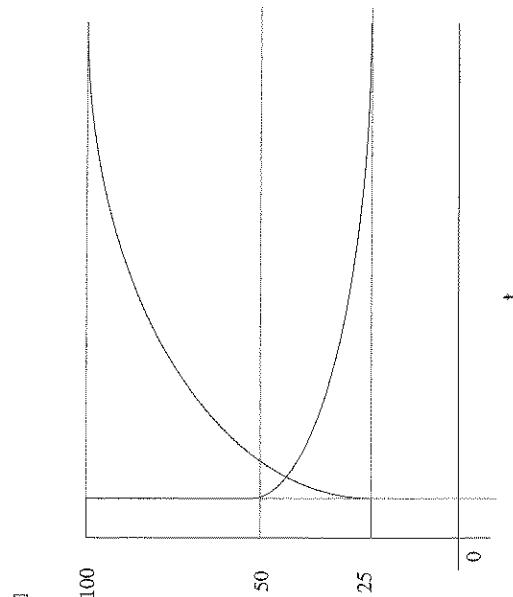

図 2 8 は、点灯率制御駆動適用時の表示領域の輝度と電流量の関係図である。

図 2 9 は、点灯率制御駆動の制御方法の図である。

図 3 0 は、点灯率制御駆動の制御方法の図である。

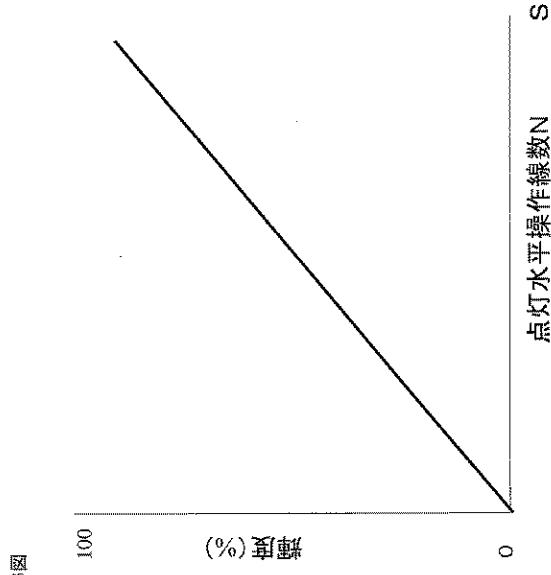

図 3 1 は、点灯率と明るさの関係図である。

図 3 2 は、本発明の駆動波形を示した図である。

図 3 3 は、本発明により修正された点灯率と明るさの関係図である。

図 3 4 は、本発明のピューファインダの説明図である。

図 3 5 は、本発明の表示状態の説明図である。

図 3 6 は、ソース信号線とのカップリングについて説明した図である。

図 3 7 は、点灯率とカップリングの関係図である。

10

図 3 8 は、入力データが大きく振られた時の点灯率の移動図である。

図 3 9 は、本発明によるちらつき対策の方法の説明図である。

図 4 0 は、特殊な画像パターン時の電流の変移図である。

図 4 1 は、本発明によるバッテリー保護の駆動図である。

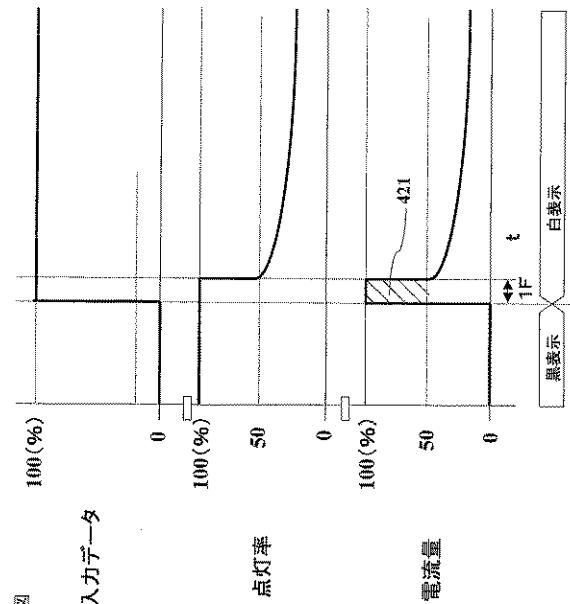

図 4 2 は、黒表示から白表示に変わった時の電流量の関係図である。

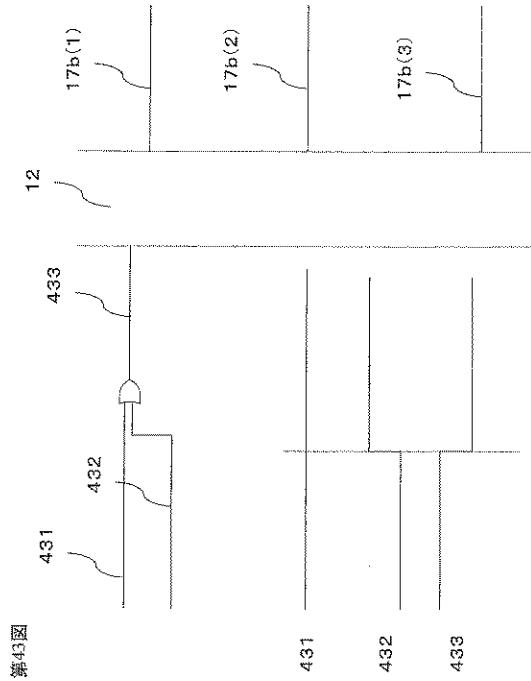

図 4 3 は、本発明の回路構成図である。

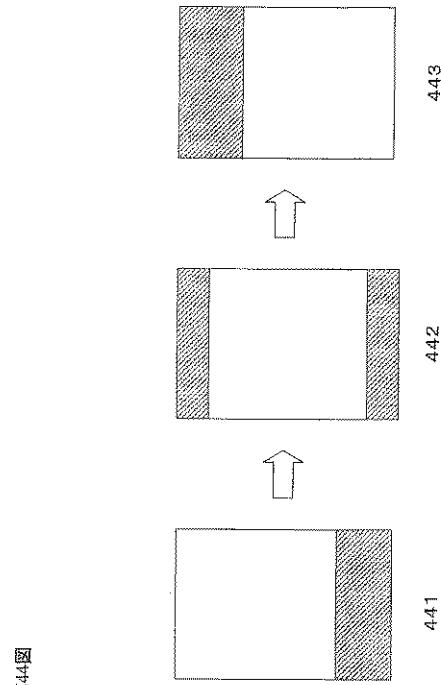

図 4 4 は、本発明の表示状態の説明図である。

図 4 5 は、本発明の回路構成図である。

図 4 6 は、本発明の回路構成図である。

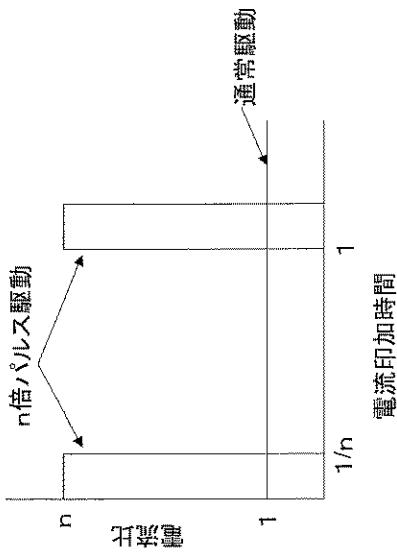

図 4 7 は、N倍パルス駆動の駆動波形図である。

20

図 4 8 は、N倍パルス駆動の駆動波形図である。

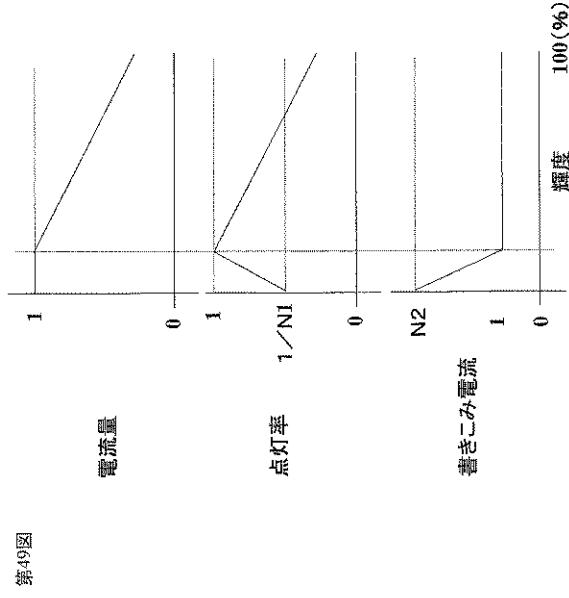

図 4 9 は、低輝度部N倍パルス駆動の説明図である。

図 5 0 は、本発明の駆動の説明図である。

図 5 1 は、低輝度部N倍パルス駆動の説明図である。

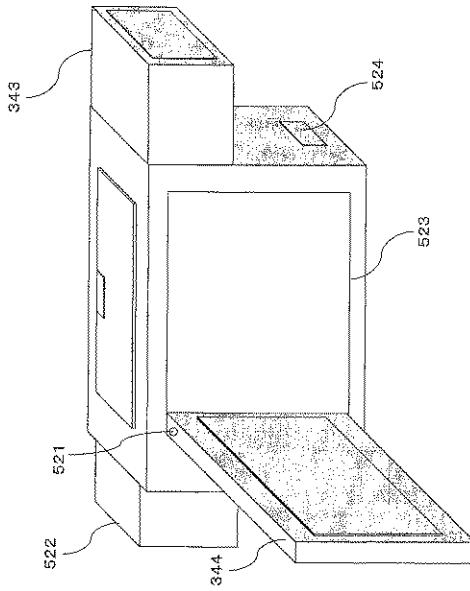

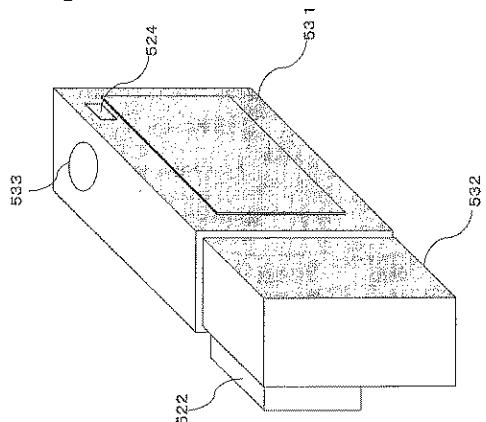

図 5 2 は、本発明のビデオカメラの説明図である。

図 5 3 は、本発明のデジタルカメラの説明図である。

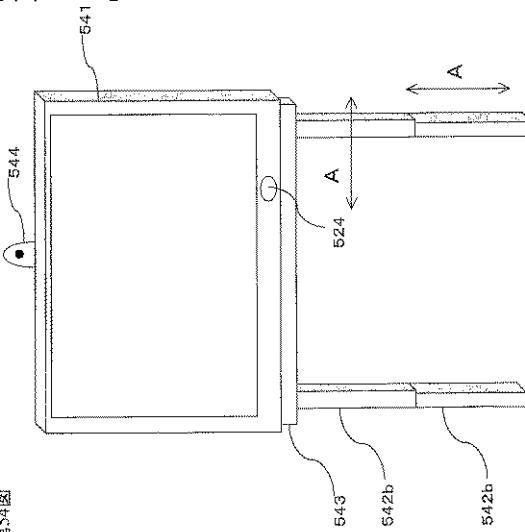

図 5 4 は、本発明のテレビ（モニター）の説明図である。

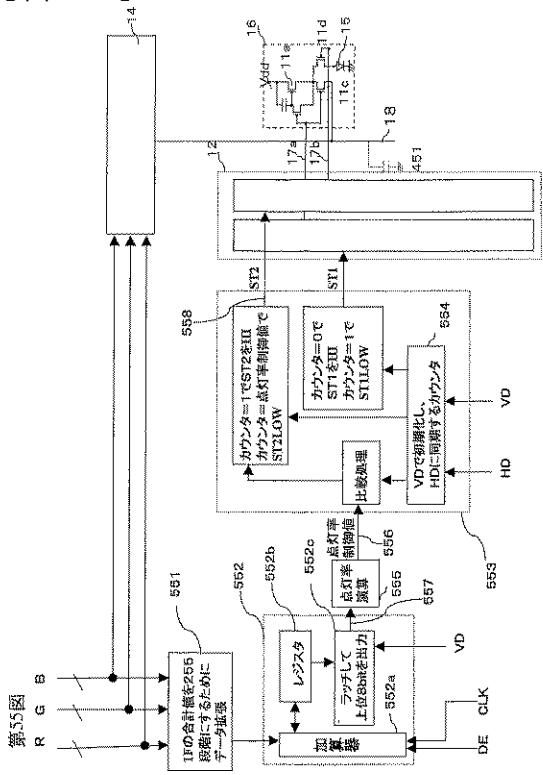

図 5 5 は、点灯率制御駆動の回路構成図である。

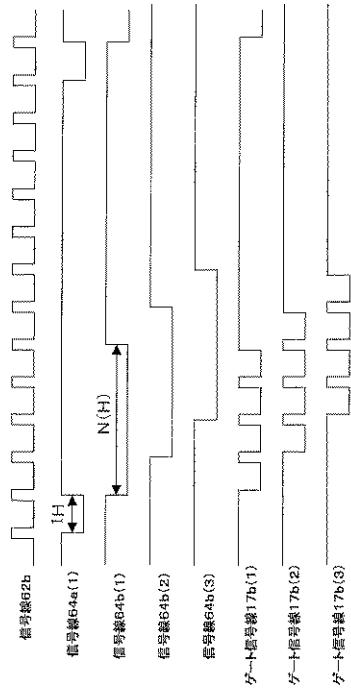

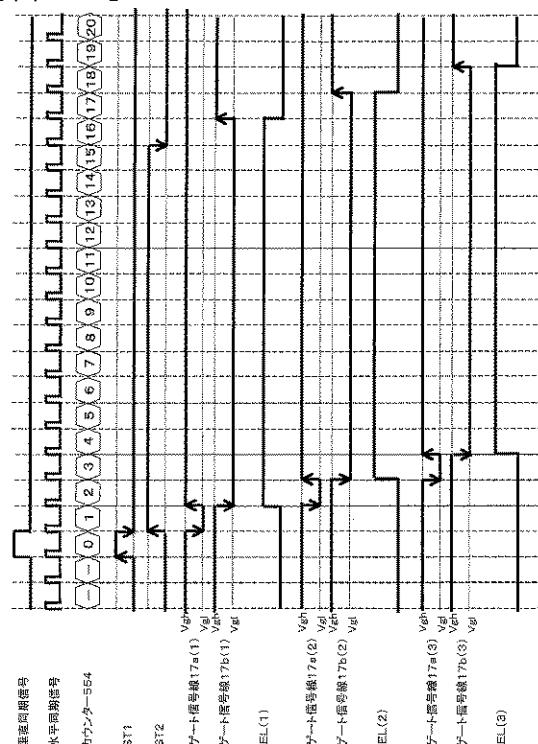

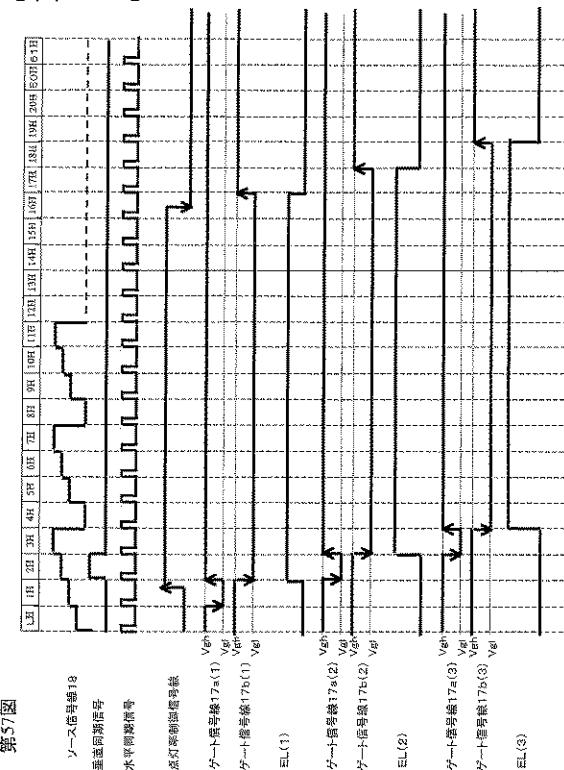

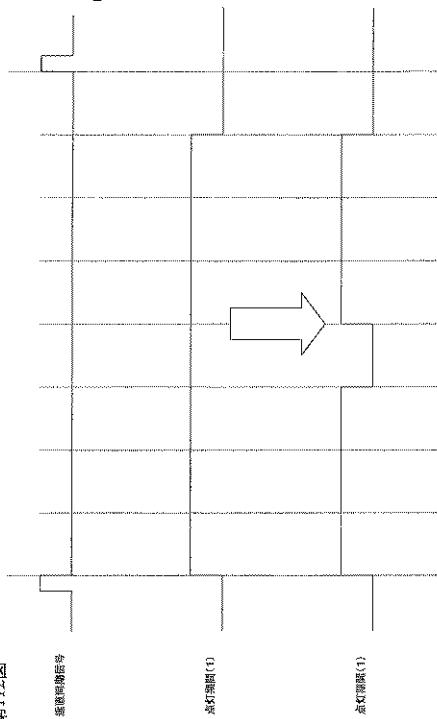

図 5 6 は、点灯率制御駆動のタイミングチャートである。

図 5 7 は、点灯率制御駆動のタイミングチャートである。

30

図 5 8 は、点灯率遅延加算回路の回路構成図である。

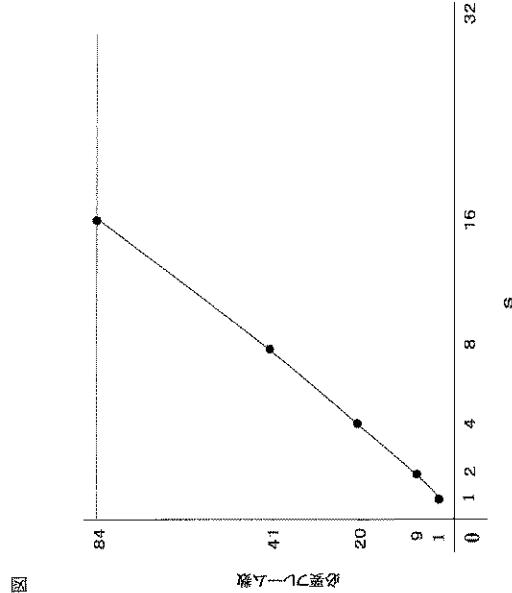

図 5 9 は、遅延率と必要フレーム数のグラフである。

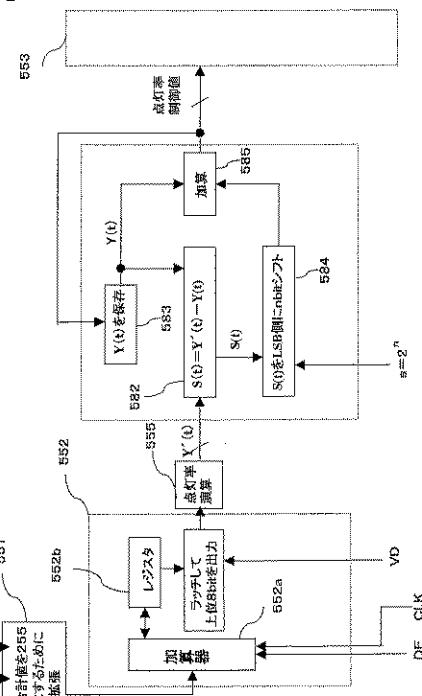

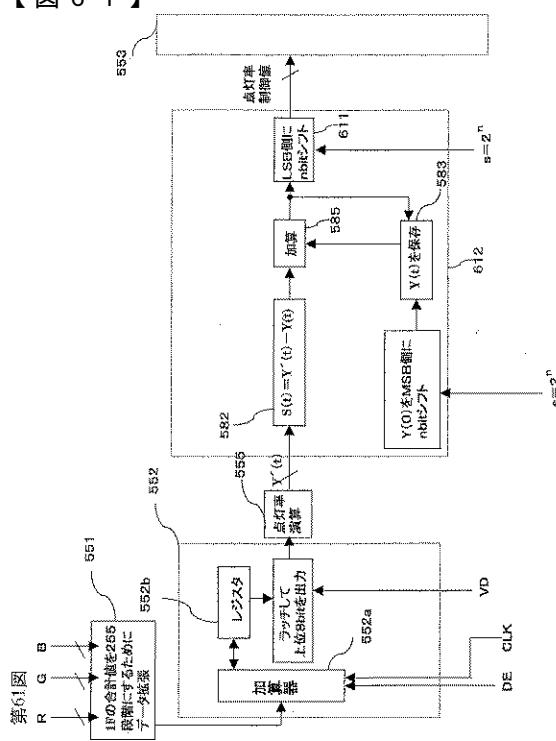

図 6 0 は、点灯率微小制御駆動の回路構成図である。

図 6 1 は、点灯率遅延加算回路の回路構成図である。

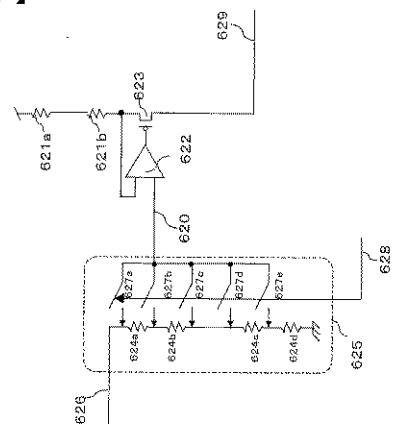

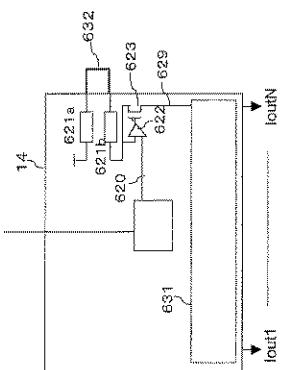

図 6 2 は、ソースドライバーの構成図である。

図 6 3 は、ソースドライバーの構成図である。

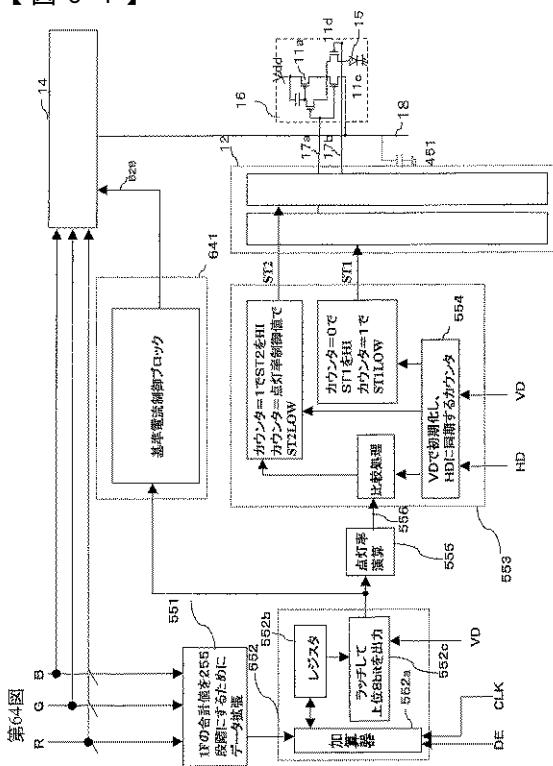

図 6 4 は、低輝度部でN倍パルス駆動を行う駆動方法の回路構成図である。

図 6 5 は、低輝度部でN倍パルス駆動を行う駆動方法の回路構成図である。

図 6 6 は、ガンマカーブの説明である。

図 6 7 は、ガンマカーブの説明である。

40

図 6 8 は、ガンマカーブの回路構成図である。

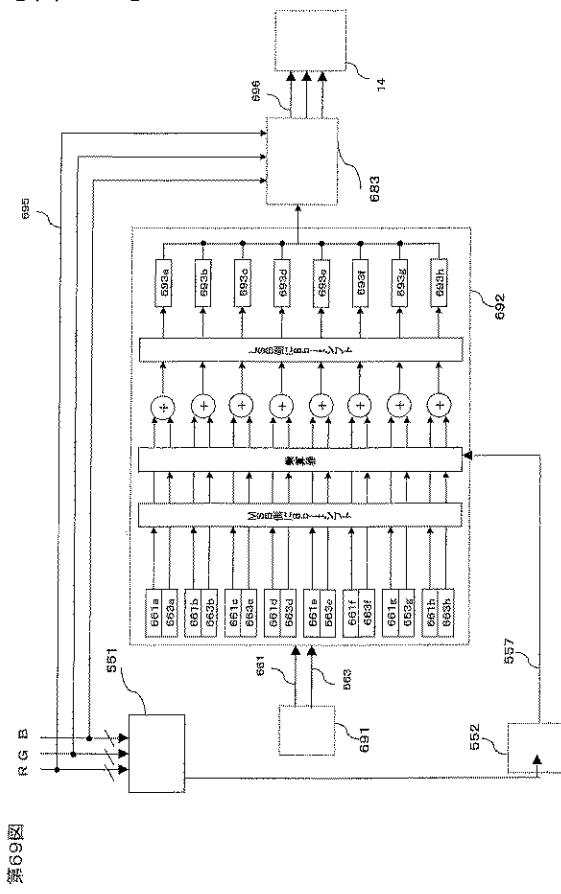

図 6 9 は、発明の回路構成図である。

図 7 0 は、本発明に利用するレジスタの構成図である。

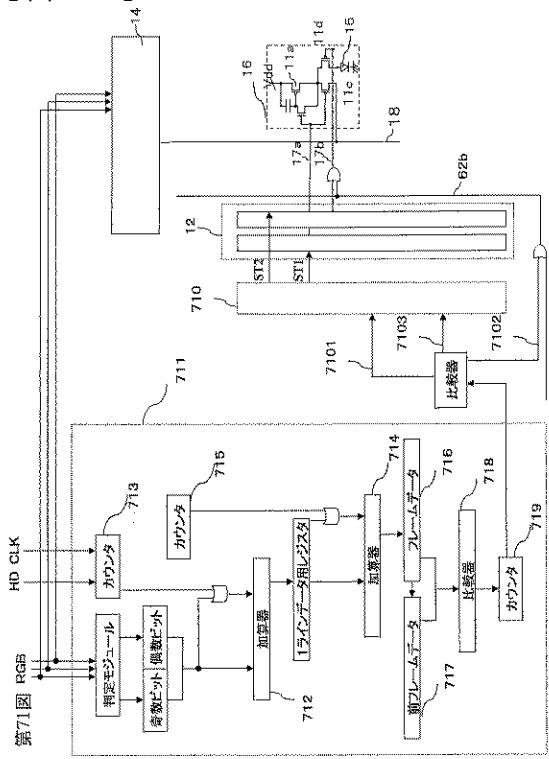

図 7 1 は、本発明の回路構成図である。

図 7 2 は、表示状態を示した図である。

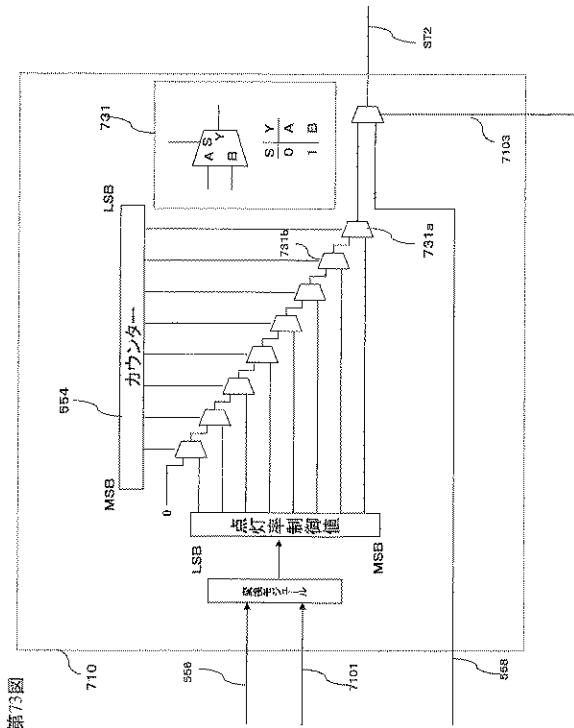

図 7 3 は、本発明の回路構成図である。

図 7 4 は、本発明に利用するレジスタの構成図である。

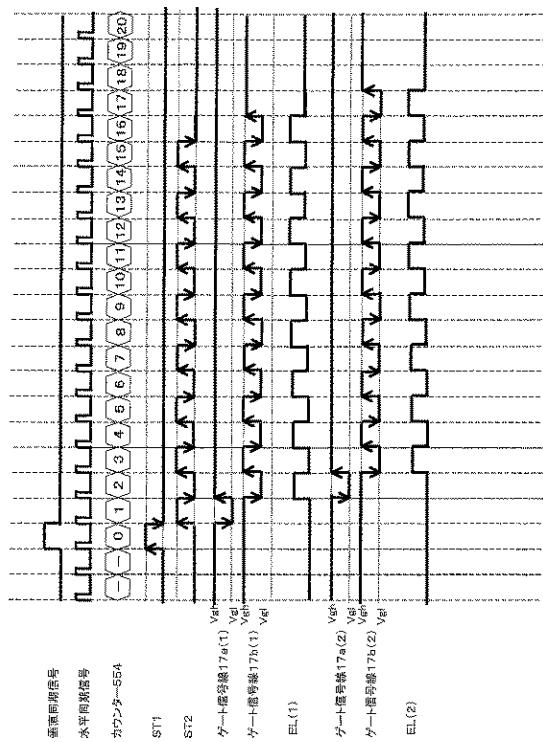

図 7 5 は、本発明のタイミングチャートである。

図 7 6 は、本発明の画素構成図である。

図 7 7 は、本発明の回路構成図である。

50

図 7 8 は、本発明のタイムチャートである。

図 7 9 は、本発明搭載パネルの表示状態の説明図である。

図 8 0 は、本発明搭載パネルの表示状態の説明図である。

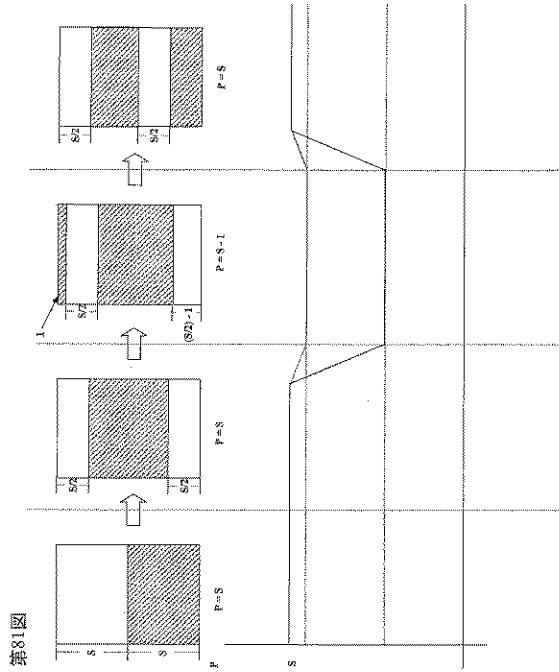

図 8 1 は、本発明搭載パネルの表示状態の説明図である。

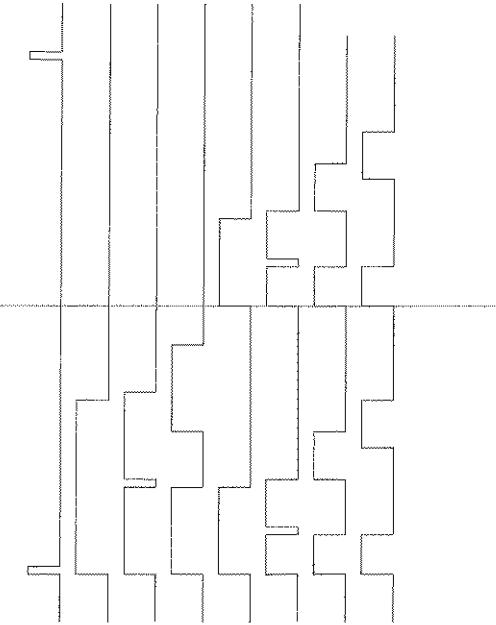

図 8 2 は、本発明のタイムチャートである。

図 8 3 は、本発明のタイムチャートである。

図 8 4 は、本発明のタイムチャートである。

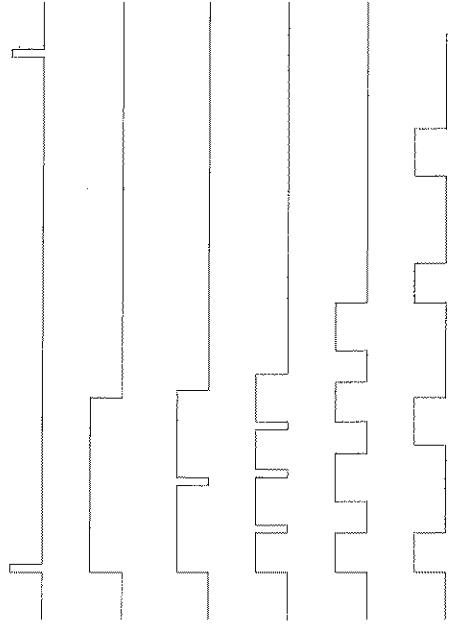

図 8 5 は、本発明の回路構成図である。

図 8 6 は、本発明のタイムチャートである。

図 8 7 は、本発明のタイムチャートである。

図 8 8 は、本発明のタイムチャートである。

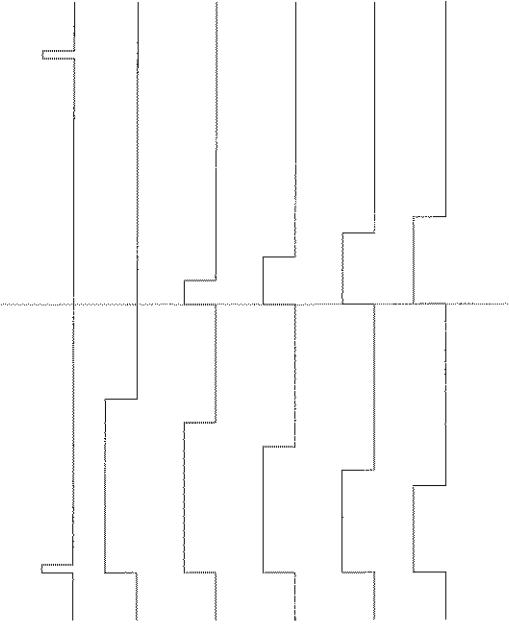

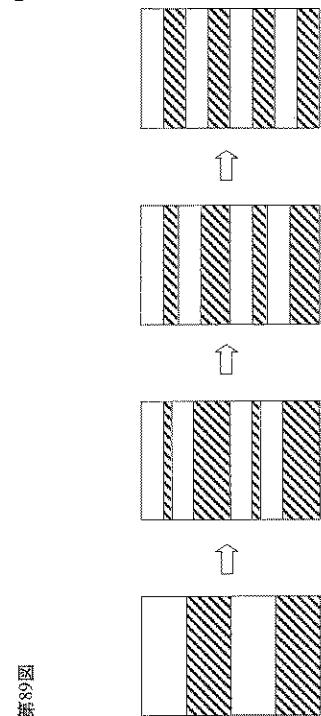

図 8 9 は、本発明搭載パネルの表示状態の説明図である。

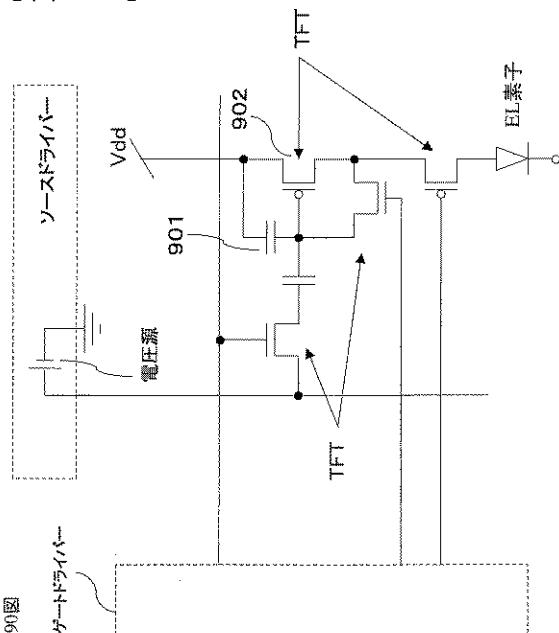

図 9 0 は、画素構成の説明図である。

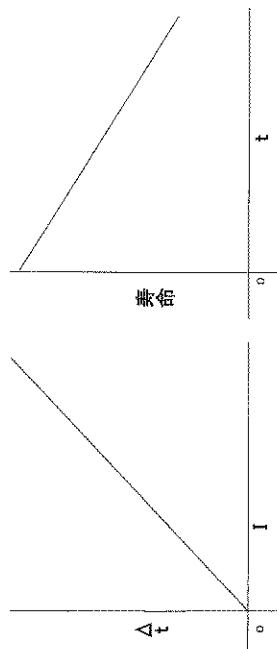

図 9 1 は、有機 E L 素子の温度と寿命の関係図である

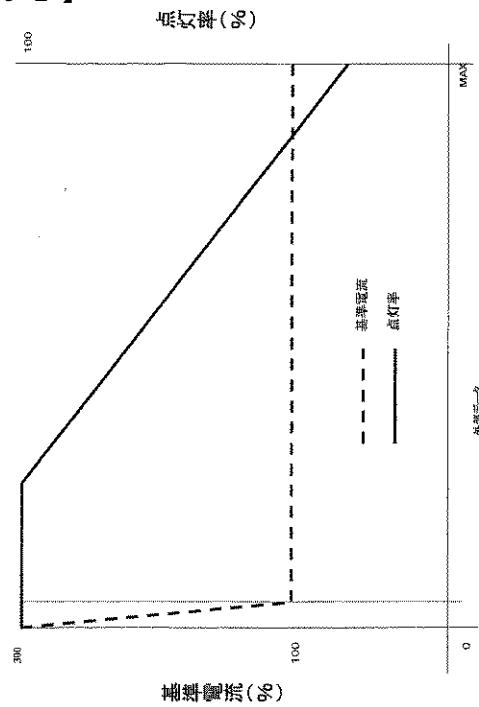

図 9 2 は、本発明使用時のデバイス状態を判断するデータとデバイスの点灯率、信号線に流れる電流の基準電流値の関係図である。

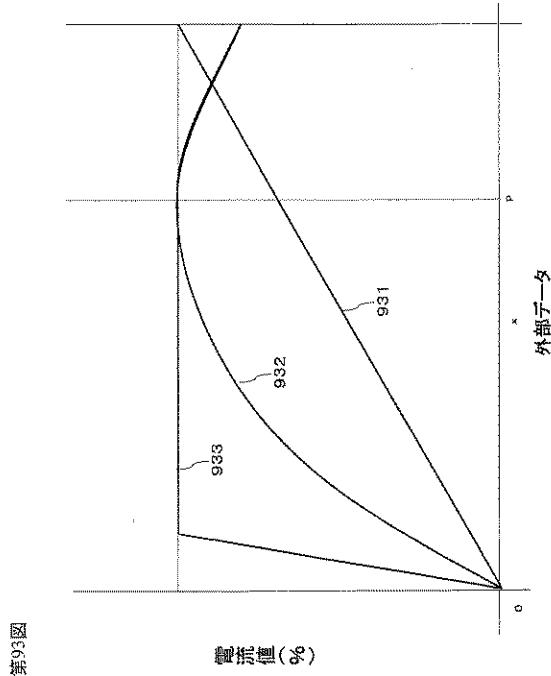

図 9 3 は、本発明使用時のデバイス状態を判断するデータとデバイスに流れる電流量の関係図である。

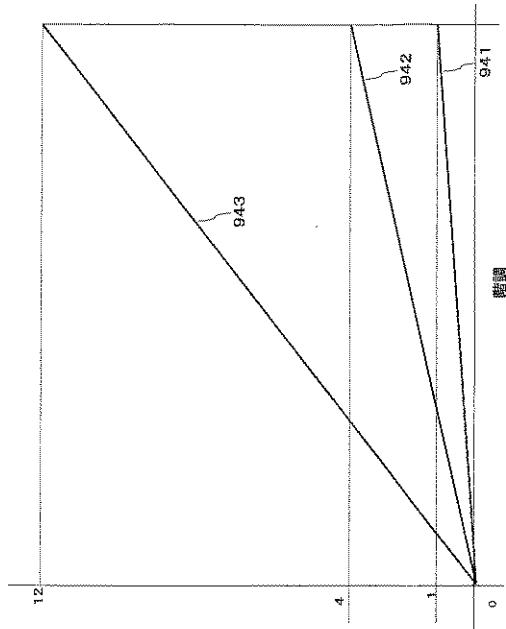

図 9 4 は、本発明使用時の画素の発光量の関係図である

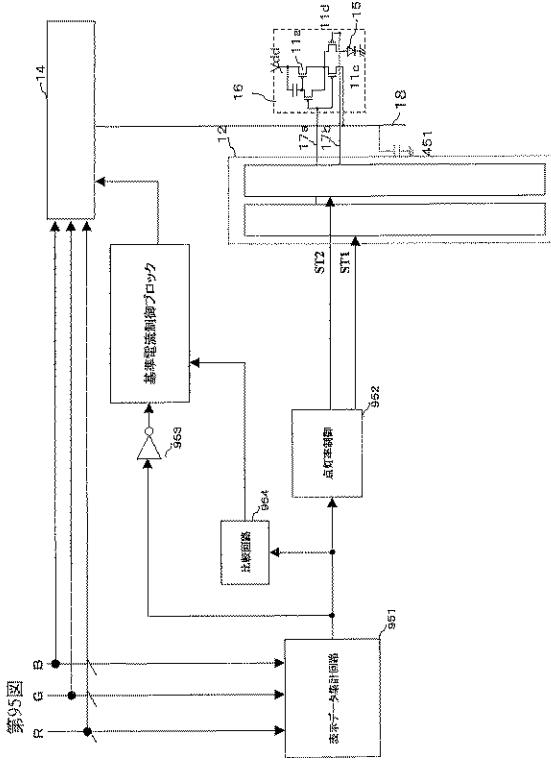

図 9 5 は、本発明の回路構成図である。

20

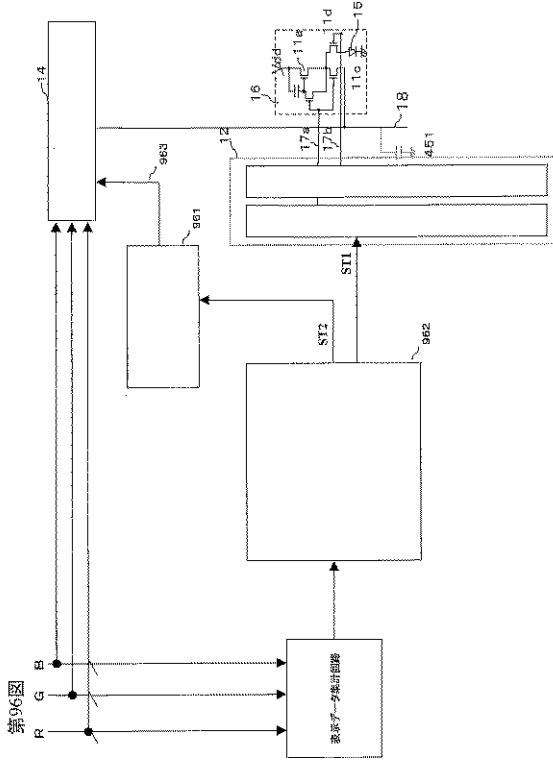

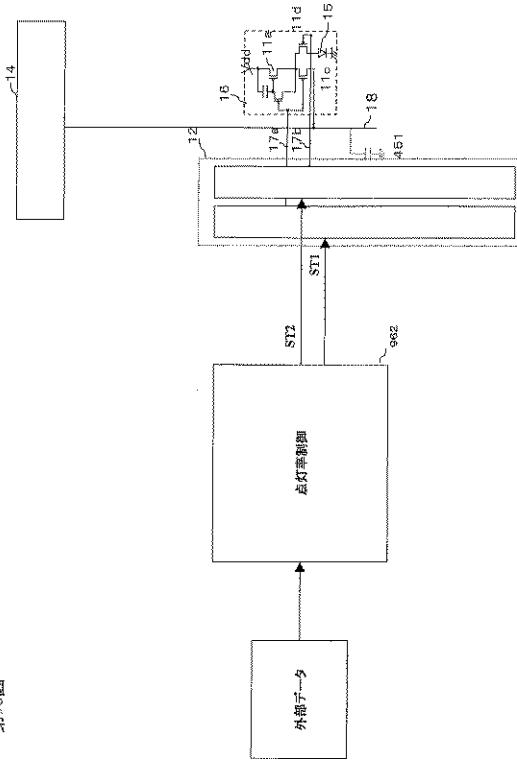

図 9 6 は、本発明の回路構成図である。

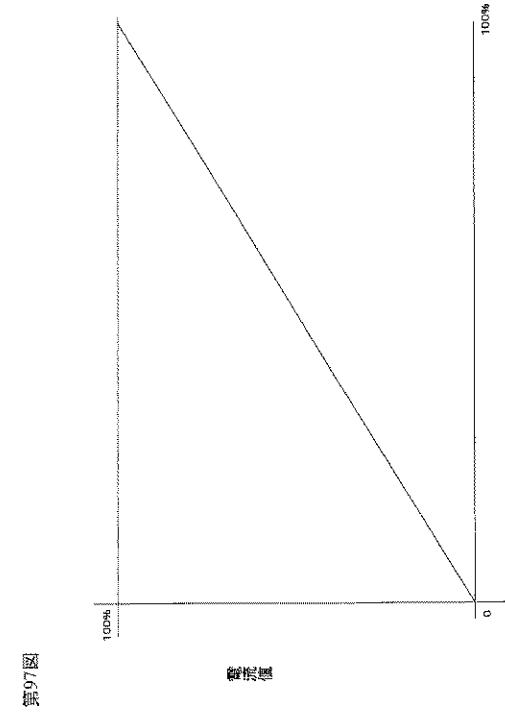

図 9 7 は、点灯率と電流値の関係図である。

図 9 8 は、本発明の回路構成図である。

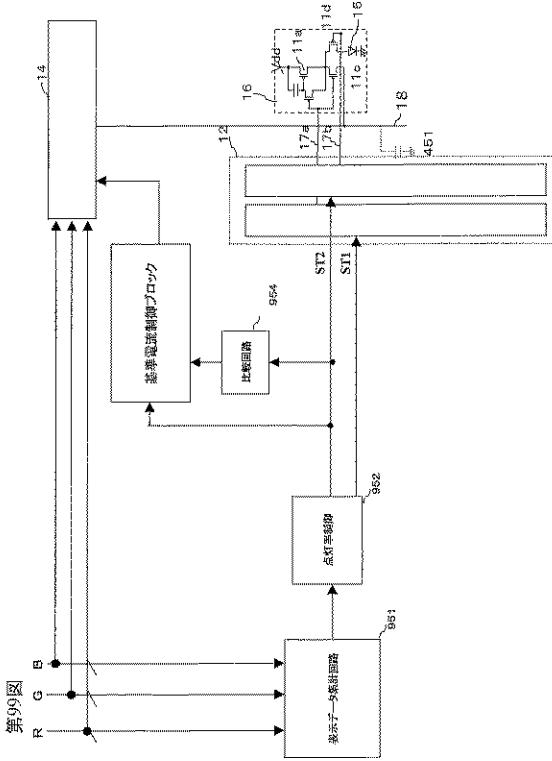

図 9 9 は、本発明の回路構成図である。

図 1 0 0 は、本発明搭載パネルの表示状態の説明図である。

図 1 0 1 は、本発明搭載パネルの表示状態の説明図である。

図 1 0 2 は、本発明の回路構成図である。

図 1 0 3 は、本発明の回路構成図である。

図 1 0 4 は、デバイスの温度上昇率の関係図である。

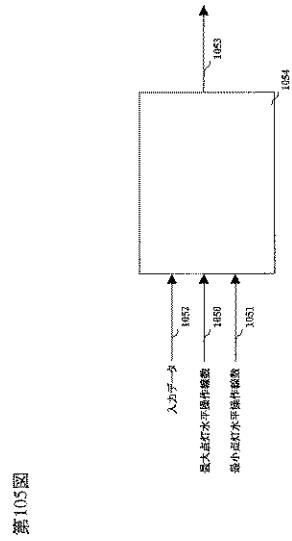

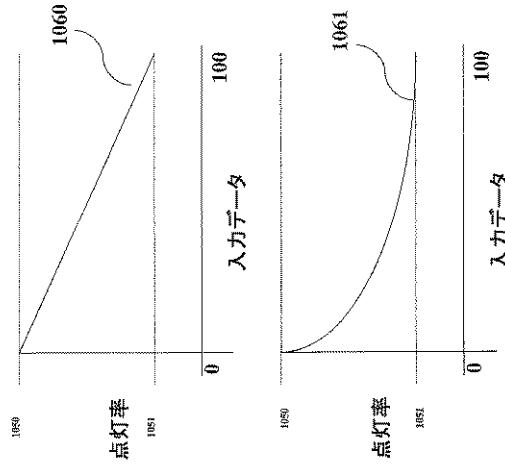

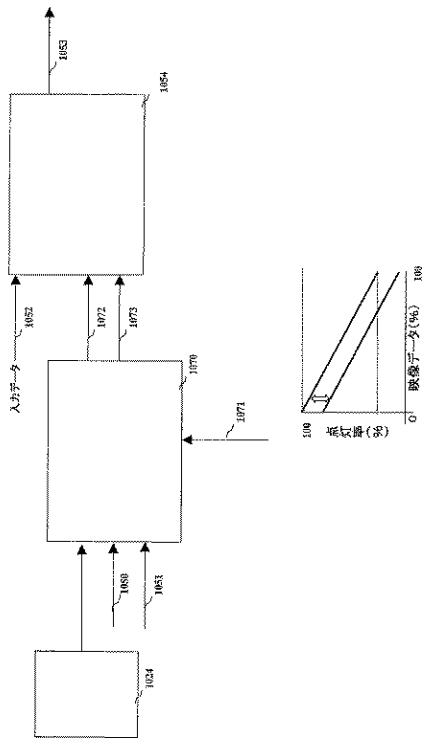

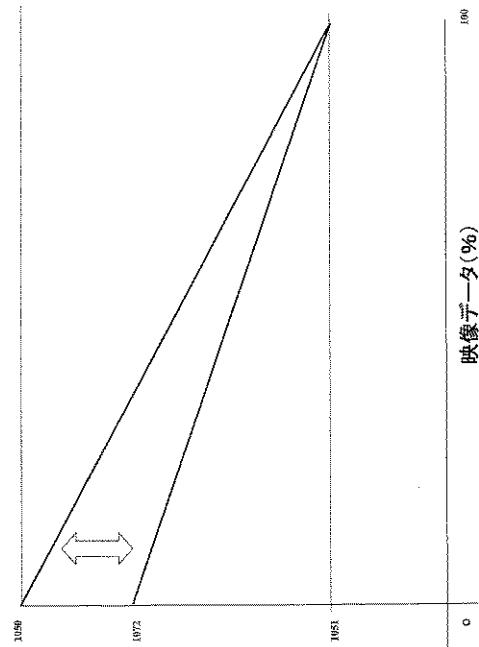

図 1 0 5 は、本発明の回路構成図である。

30

図 1 0 6 は、入力データと点灯水平操作線数との関係図である。

図 1 0 7 は、本発明の回路構成図である。

図 1 0 8 は、入力データと点灯水平操作線数との関係図である。

図 1 0 7 は、入力データに対する温度上昇の関係図である。

図 1 1 0 は、本発明の回路構成図である。

図 1 1 1 は、本発明の回路構成図である。

図 1 1 2 は、本発明のタイムチャートである。

図 1 1 3 は、本発明のタイムチャートである。

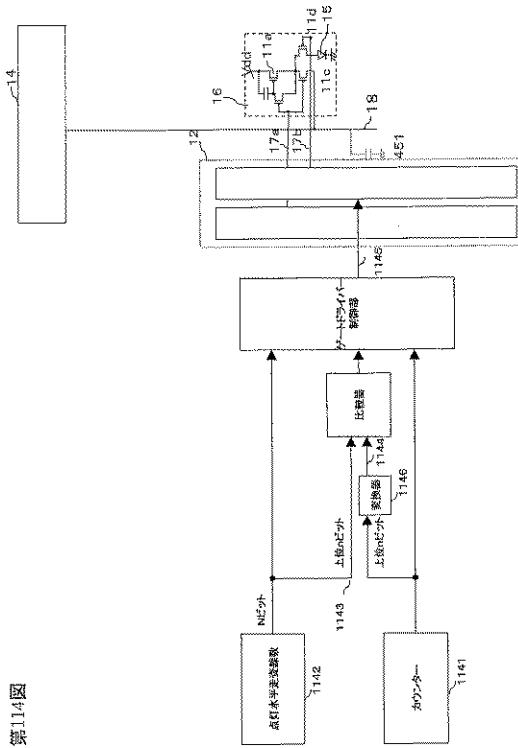

図 1 1 4 は、本発明の回路構成図である。

図 1 1 5 は、本発明のタイムチャートである。

40

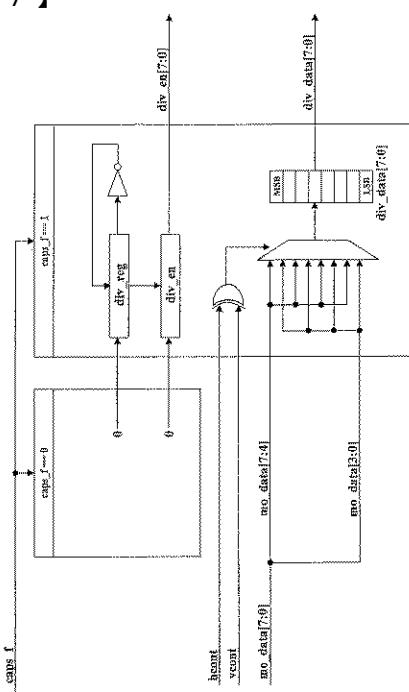

図 1 1 6 は、本発明の回路構成図である。

図 1 1 7 は、本発明の回路構成図である。

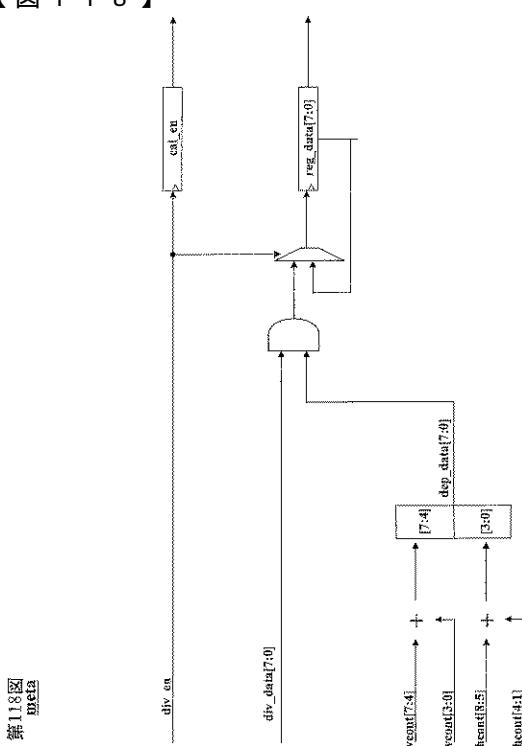

図 1 1 8 は、本発明の回路構成図である。

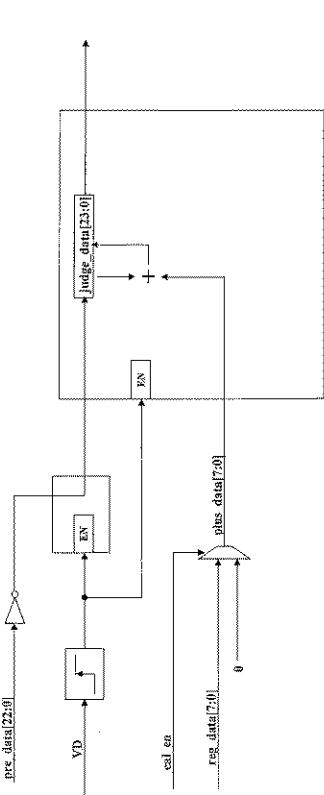

図 1 1 9 は、本発明の回路構成図である。

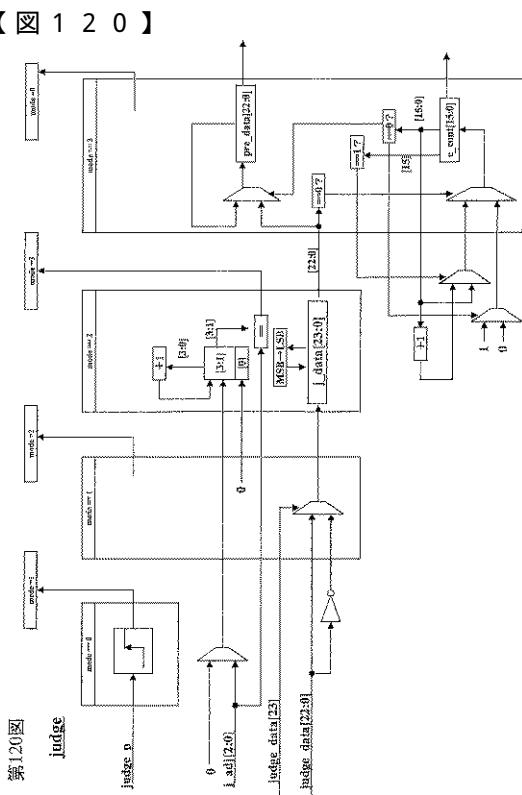

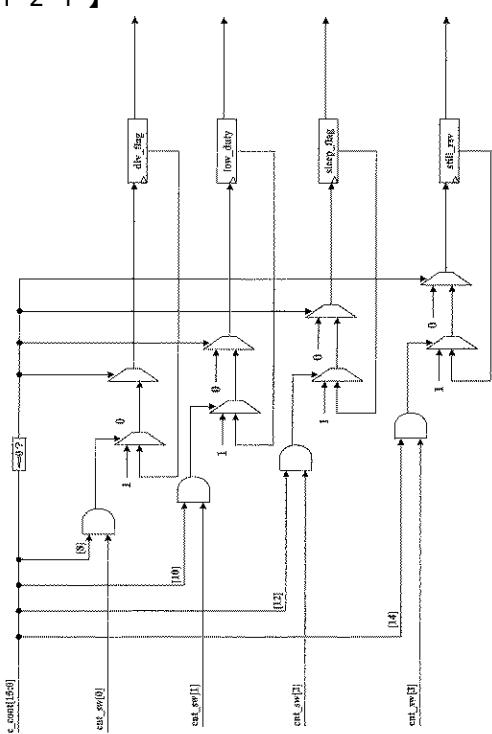

図 1 2 0 は、本発明の回路構成図である。

図 1 2 1 は、本発明の回路構成図である。

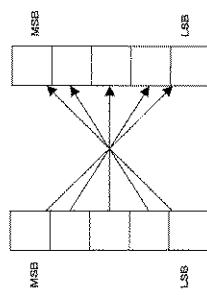

図 1 2 2 は、データの変換器の変換方法を示した図である。

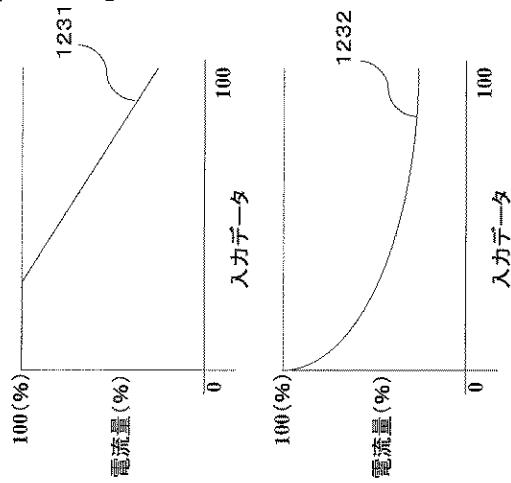

図 1 2 3 は、入力データと電流量の関係図である。

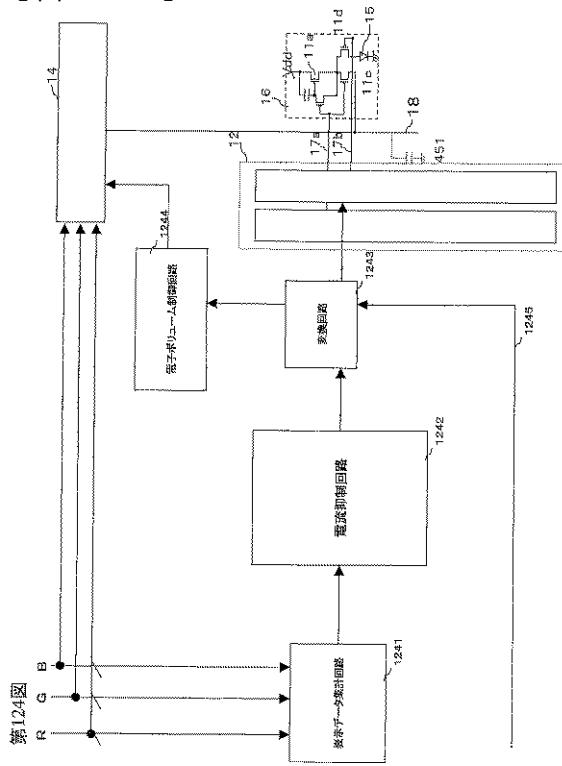

図 1 2 4 は、本発明の回路構成図である。

図 1 2 5 は、入力データと最大階調数の関係図である。

50

図126は、ガンマカーブの変換を示したものである。

図127は、電流量の抑制を最大階調数の制御と、点灯率の制御を合わせて行った際の関係図である。

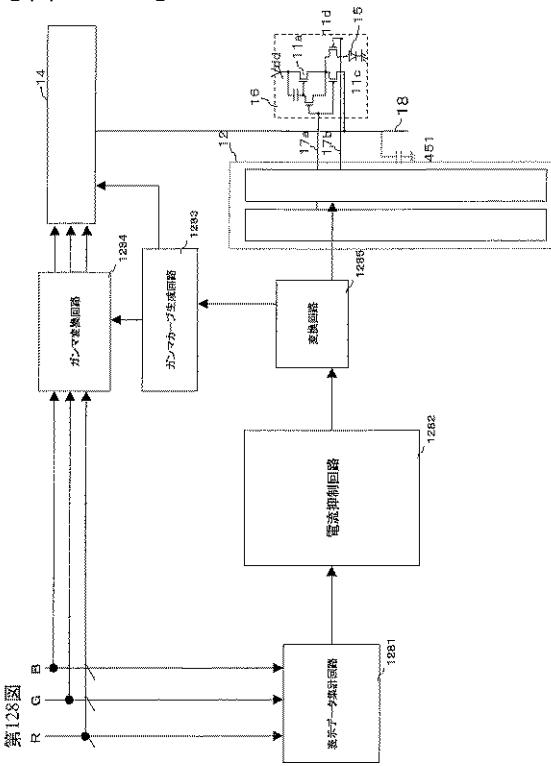

図128は、本発明の回路構成図である。

図129は、本発明のデータの変換方法を示した図である。

図130は、入力データと表示点灯率、またそれを分類した図である。

図131は、本発明の回路構成図である。

図132は、本発明における表示パネルの画素構成図である。

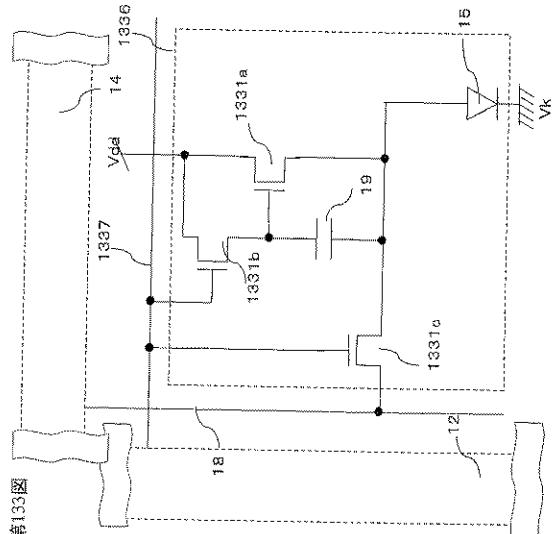

図133は、本発明における表示パネルの画素構成図である。

図134は、点灯率の変化の遅延を示した図である。

10

#### 【符号の説明】

1 1、1 3 3 1 トランジスタ（薄膜トランジスタ、TFT）

1 2 ゲートドライバ（ゲートドライバIC回路）

1 4 ソースドライバ（ソースドライバIC回路）

1 5 E L 素子（発光素子）

1 6、1 3 3 6 画素

1 7、1 3 3 7 ゲート信号線

1 8 ソース信号線

1 9 蓄積容量（附加コンデンサ、附加容量）

5 0 表示画面

20

5 1 書き込み画素（書き込み画素行）

5 2 非表示画素（非表示領域、非点灯領域）

5 3 表示画素（表示領域、点灯領域）

6 1 シフトレジスタ

6 2 インバータ（OEV信号線）

6 3 出力バッファ

6 5 OR回路

7 1 アレイ基板（表示パネル）

7 2 レーザー照射範囲（エキシマレーザースポット）

7 3 位置決めマーカー

30

7 4 ガラス基板（アレイ基板）

8 1 コントロールIC（コントロールIC回路）

8 2 電源IC（電源IC回路）

8 3 プリント基板

8 4 フレキシブル基板

8 5 封止フタ

8 6 カソード配線

8 7 アノード配線（Vdd）

8 8 データ信号線

8 9 ゲート制御信号線

40

9 1、4 5 1 浮遊容量

1 0 1 土手（リブ）

1 0 2 層間絶縁膜

1 0 4 コンタクト接続部

1 0 5 画素電極

1 0 6 カソード電極

1 0 7 乾燥剤

1 0 8 / 4 板

1 0 9 偏光板

1 1 1 薄膜封止膜

50

2 7 1 ダミー画素（ダミー画素行）

3 4 1 接眼リング

3 4 2 拡大レンズ

3 4 3 凸レンズ

4 5 2 電流原

4 8 1 a 水平同期信号 H D

4 8 2 a 4 8 3 a ゲート制御信号

5 2 1 支点（回転部）

5 2 2 撮影レンズ

5 2 3 格納部

5 2 4 スイッチ 10

5 3 1 本体

5 3 2 撮影部

5 3 3 シャッタスイッチ

5 4 1 取り付け枠

5 4 2 脚

5 4 3 取り付け台

5 4 4 固定部

6 2 1 抵抗

6 2 2 演算増幅器 20

6 2 3 トランジスタ

6 2 4 抵抗

6 2 5 電圧調節部

6 2 6 電源線

6 2 7 切り替え手段（スイッチ）

6 2 8 制御データ

6 2 9 基準電流線

#### 【発明を実施するための最良の形態】

本明細書において各図面は理解を容易にまたは／および作図を容易にするため、省略または／および拡大縮小した箇所がある。たとえば、図11に図示する表示パネルの断面図では封止膜111などを十分厚く図示している。一方、図10において、封止フタ85は薄く図示している。また、省略した箇所もある。たとえば、本発明の表示パネルなどでは、不要光の反射防止のための位相フィルムなどを省略していくが、適時付加することが望ましい。以上のこととは以下の図面に対しても同様である。また、同一番号または、記号等を付した箇所は同一もしくは類似の形態もしくは材料あるいは機能もしくは動作を有する。

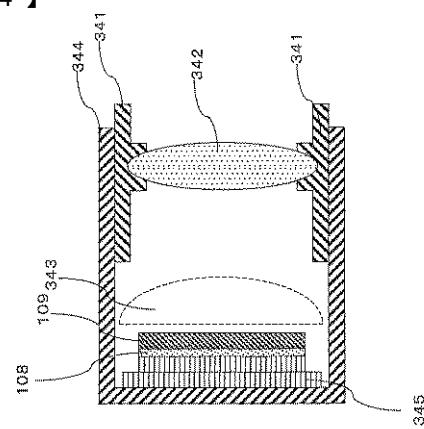

なお、各図面等で説明した内容は特に断りがなくとも、他の実施例等と組み合わせることができる。たとえば、図8の表示パネルにタッチパネルなどを付加し、図34、図52から図54に図示する情報表示装置とすることができます。また、拡大レンズ342を取り付けビデオカメラ（図52など参照のこと）などに用いるビューファインダ（図34を参照のこと）を構成することもできる。また、図4、図15、図18、図21、図23などで説明した本発明の駆動方法は、いずれの本発明の表示装置または表示パネルに適用することができる。つまり、本明細書で記載された駆動方法は本発明の表示パネルに適用することができる。また、本発明は各画素にトランジスタが形成されたアクティブマトリックス型表示パネルを主に説明するがこれに限定するものではなく、単純マトリックス型にも適用することができることはいうまでもない。

このように特に明細書中に例示されていなくとも、明細書、図面中で記載あるいは説明した事項、内容、仕様は、互いに組み合させて請求項に記載することができる。すべての組み合わせについて明細書などで記述することは不可能であるからである。

近年、低消費電力でかつ高表示品質であり、更に薄型化が可能な表示パネルとして、有機エレクトロルミネッセンス（E L）素子の複数をマトリックス状に配列して構成される有

機 E L 表示パネルが注目されている。

有機 E L 表示パネルは、図 10 に示すように、画素電極としての透明電極 105 が形成されたガラス板 71 (アレイ基板) 上に、電子輸送層、発光層、正孔輸送層などからなる少なくとも 1 層の有機機能層 (E L 層) 15、及び金属電極 (反射膜) (カソード) 106 が積層されたものである。

透明電極 (画素電極) 105 である陽極 (アノード) にプラス、金属電極 (反射電極) 106 の陰極 (カソード) にマイナスの電圧を加え、すなわち、透明電極 105 及び金属電極 106 間に直流を印加することにより、有機機能層 (E L 層) 15 が発光する。良好な発光特性を期待することのできる有機化合物を有機機能層に使用することによって、E L 表示パネルが実用に耐えうるものになっている。なお、本発明は有機 E L 表示パネルを例にして説明をするが、これに限定するものではない。無機 E L を使用したディスプレイや、FED、もしくは SED のような自発光素子を利用したディスプレイに適応することが可能である。また、構造、回路などは TN 液晶表示パネル、STN 液晶表示パネルなど、他の表示パネルにも適用できる事項がある。

以下、本発明の E L 表示パネルの製造方法および構造について詳しく説明をする。まず、アレイ基板 71 に画素を駆動するトランジスタ 11 を形成する。1つの画素は 2 個以上、好ましくは 4 個または 5 個のトランジスタで構成される。また、画素は電流プログラムされ、プログラムされた電流が E L 素子 15 に供給される。通常、電流プログラムされた値は電圧値として蓄積容量 19 に保持される。このトランジスタ 11 の組み合わせなど画素構成については後に説明をする。次にトランジスタ 11 に正孔注入電極としての画素電極を形成する。画素電極 105 はフォトリソグラフィーによりパターン化する。なお、トランジスタ 11 の下層、あるいは上層にはトランジスタ 11 に光入射することにより発生するホトコンダクタ現象 (以後、ホトコンと呼ぶ) による画質劣化を防止するために、遮光膜を形成または配置する。

なお、電流プログラムとは、ソースドライバ回路 14 からプログラム電流を画素に印加し (もしくは画素からソースドライバ回路 14 に吸収し)、この電流に相当する信号値を画素に保持させるものである。この保持された信号値に対応する電流を E L 素子 15 に流す (もしくは、E L 素子 15 から流し込む)。つまり、電流でプログラムし、プログラムされた電流に相当 (対応) する電流を E L 素子 15 に流すようにするものである。

一方、電圧プログラムとは、ソースドライバ回路 14 からプログラム電圧を画素に印加し、この電圧に相当する信号値を画素に保持させるものである。この保持された電圧に対応する電流を E L 素子 15 に流す。つまり、電圧でプログラムし、画素内で電圧を電流値に変換し、プログラムされた電圧に相当 (対応) する電流を E L 素子 15 に流すようにするものである。

まず、有機 E L 表示パネルに用いられるアクティブマトリックス方式は、1. 特定の画素を選択し、必要な表示情報を与えられること。2. 1 フレーム期間を通じて E L 素子に電流を流すことができることという 2 つの条件を満足させなければならない。

この 2 つの条件を満足させるため、図 76 に図示する従来の有機 E L の画素構成では、第 1 のトランジスタ 11b は画素を選択するためのスイッチング用トランジスタ、第 2 のトランジスタ 11a は E L 素子 (E L 膜) 15 に電流を供給するための駆動用トランジスタとする。

ここで液晶に用いられるアクティブマトリックス方式と比較すると、スイッチング用トランジスタ 11b は液晶用にも必要であるが、駆動用トランジスタ 11a は E L 素子 15 を点灯させるために必要である。この理由は液晶の場合は、電圧を印加することでオン状態を保持することができるが、E L 素子 15 の場合は、電流を流しつづけなければ画素 16 の点灯状態を維持できないからである。

したがって、E L 表示パネルでは電流を流し続けるためにトランジスタ 11a をオンさせ続けなければならない。まず、走査線、データ線が両方ともオンになると、スイッチング用トランジスタ 11b を通してキャパシタ 19 に電荷が蓄積される。このキャパシタ 19 が駆動用トランジスタ 11a のゲートに電圧を加え続けるため、スイッチング用トラン

10

20

30

40

50

ジスタ 11 b がオフになっても、電流供給線 (Vdd) から電流が流れつづけ、1 フレーム期間にわたり画素 16 をオンできる。

この構成を用いて階調を表示させる場合、駆動用トランジスタ 11 a のゲート電圧として階調に応じた電圧を印加する必要がある。したがって、駆動用トランジスタ 11 a のオン電流のばらつきがそのまま表示に現れる。

トランジスタのオン電流は単結晶で形成されたトランジスタであれば、きわめて均一であるが、安価なガラス基板に形成することのできる形成温度が 450 度以下の低温ポリシリコン技術で形成した低温多結晶トランジスタでは、そのしきい値のばらつきが ±0.2 V ~ 0.5 V の範囲でばらつきがある。そのため、駆動用トランジスタ 11 a を流れるオン電流がこれに対応してばらつき、表示にムラが発生する。これらのムラは、しきい値電圧のばらつきのみならず、トランジスタの移動度、ゲート絶縁膜の厚みなどでも発生する。また、トランジスタ 11 の劣化によっても特性は変化する。10

なお、低温ポリシリコン技術に限定されるものではなく、プロセス温度が 450 度（摂氏）以上の高温ポリシリコン技術を用いて構成してもよく、また、固相（CGS）成長させた半導体膜を用いて TFTなどを形成したものをもちいてもよい。その他、有機 TFT を用いたものであっても良い。

また、アモルファスシリコン技術で形成した TFT アレイを用いてパネルを構成する。なお、本明細書では低温ポリシリコン技術で形成した TFT を主として説明する。しかし、TFT のバラツキが発生するなどの課題は他の方式でも同一である。

したがって、アナログ的に階調を表示させる方法では、均一な表示を得るために、デバイスの特性を厳密に制御する必要があり、現状の低温多結晶ポリシリコントランジスタではこのバラツキを所定範囲以内の抑えるというスペックを満足できない。この問題を解決するため、1 画素内に 4 つ以上のトランジスタをもうけて、しきい値電圧のばらつきをコンデンサにより補償させて均一な電流を得る方法、定電流回路を 1 画素ごとに形成し電流の均一化を図る方法などが考えられる。20

しかしながら、これらの方法は、プログラムされる電流が EL 素子 15 を通じてプログラムされるため電流経路が変化した場合に電源ラインに接続されるスイッチングトランジスタに対し駆動電流を制御するトランジスタがソースフォロワとなり駆動マージンが狭くなる。したがって、駆動電圧が高くなるという課題を有する。

また、電源に接続するスイッチングトランジスタをインピーダンスの低い領域で使用する必要があり、この動作範囲が EL 素子 15 の特性変動により影響を受けるという課題もある。その上、飽和領域における電圧電流特性に、キンク電流が発生する場合、トランジスタのしきい値電圧の変動が発生した場合、記憶された電流値が変動するという課題もある。30

本発明の EL 素子構造は、上記課題に対して、EL 素子 15 に流れる電流を制御するトランジスタ 11 が、ソースフォロワ構成とならず、かつそのトランジスタにキンク電流があっても、キンク電流の影響を最小に抑えることが出来て記憶される電流値の変動を小さくすることが出来る構成である。

本発明の EL 表示装置の画素構造は、具体的には図 1 に示すように単位画素が最低 4 つからなる複数のトランジスタ 11 ならびに EL 素子により形成される。なお、画素電極はソース信号線と重なるように構成する。つまり、ソース信号線 18 上に絶縁膜あるいはアクリル材料からなる平坦化膜を形成して絶縁し、この絶縁膜上に画素電極 105 を形成する。このようにソース信号線 18 上に画素電極を重ねる構成をハイアパー・チャ（H.A.）構造と呼ぶ。40

ゲート信号線（第 1 の走査線）17 a をアクティブ（ON 電圧を印加）とすることにより EL 素子 15 駆動用のトランジスタ（トランジスタあるいはスイッチング素子）11 a およびトランジスタ（トランジスタあるいはスイッチング素子）11 c を通して、前記 EL 素子 15 に流すべき電流値をソースドライバ回路 14 から流す。また、トランジスタ 11 a のゲートとドレイン間を短絡するようにトランジスタ 11 b がゲート信号線 17 a アクティブ（ON 電圧を印加）となることにより開くと共に、トランジスタ 11 a のゲート50

とソース間に接続されたコンデンサ（キャパシタ、蓄積容量、付加容量）19に、前記電流値を流すようにトランジスタ11aのゲート電圧（あるいはドレイン電圧）を記憶する（図3（a）を参照のこと）。

なお、トランジスタ11aのソース（S）-ゲート（G）間容量（コンデンサ）19は0.2pF以上の容量とすることが好ましい。他の構成として、別途、コンデンサ19を形成する構成も例示される。つまり、コンデンサ電極レイヤーとゲート絶縁膜およびゲートメタルから蓄積容量を形成する構成である。トランジスタ11cのリークによる輝度低下を防止する観点、表示動作を安定化させるための観点からはこのように別途コンデンサを構成するほうが好ましい。なお、コンデンサ（蓄積容量）19の大きさは、0.2pF以上2pF以下とすることがよく、中でもコンデンサ（蓄積容量）19の大きさは、0.4pF以上1.2pF以下とすることがよい。10

なお、コンデンサ19は隣接する画素間の非表示領域におおむね形成することがこのましい。一般的に、フルカラー有機EL15を作成する場合、有機EL層15をメタルマスクによるマスク蒸着で形成するためマスク位置ずれによるEL層の形成位置が発生する。位置ずれが発生すると各色の有機EL層15（15R、15G、15B）が重なる危険性がある。そのため、各色の隣接する画素間の非表示領域は10μ以上離れなければならぬ。この部分は発光に寄与しない部分となる。したがって、蓄積容量19をこの領域に形成することは開口率向上のために有効な手段となる。

なお、メタルマスクは磁性体で作製し、基板71の裏面から磁石でメタルマスクを磁力で吸着する。磁力により、メタルマスクは基板と隙間なく密着する。以上の製造方法に関する事項は、本発明の他の製造方法にも適用される。20

次に、ゲート信号線17aを非アクティブ（OFF電圧を印加）、ゲート信号線17bをアクティブとして、電流の流れる経路を前記第1のトランジスタ11a並びにEL素子15に接続されたトランジスタ11dならびに前記EL素子15を含む経路に切り替えて、記憶した電流を前記EL素子15に流すように動作する（図3（b）を参照のこと）。

この回路は1画素内に4つのトランジスタ11を有しており、トランジスタ11aのゲートはトランジスタ11bのソースに接続されている。また、トランジスタ11bおよびトランジスタ11cのゲートはゲート信号線17aに接続されている。トランジスタ11bのドレインはトランジスタ11cのソースならびにトランジスタ11dのソースに接続され、トランジスタ11cのドレインはソース信号線18に接続されている。トランジスタ11dのゲートはゲート信号線17bに接続され、トランジスタ11dのドレインはEL素子15のアノード電極に接続されている。30

なお、図1ではすべてのトランジスタはPチャンネルで構成している。Pチャンネルは多少Nチャンネルのトランジスタに比較してモビリティが低いが、耐圧が大きくまた劣化も発生しにくいので好ましい。しかし、本発明はEL素子構成をPチャンネルで構成することのみに限定するものではない。Nチャンネルのみで構成してもよい。また、NチャンネルとPチャンネルの両方を用いて構成してもよい。

なお、図1においてトランジスタ11c、11bは同一の極性で構成し、かつNチャンネルで構成し、トランジスタ11a、11dはPチャンネルで構成することが好ましい。一般的にPチャンネルトランジスタはNチャンネルトランジスタに比較して、信頼性が高い、キンク電流が少ないなどの特長があり、電流を制御することによって目的とする発光強度を得るEL素子15に対しては、トランジスタ11aをPチャンネルにする効果が大きい。最適には画素を構成するTFT11をすべてPチャンネルで形成し、内蔵ゲートドライバ12もPチャンネルで形成することが好ましい。このようにアレイをPチャンネルのみのTFTで形成することにより、マスク枚数が5枚となり、低コスト化、高歩留まりを実現できる。40

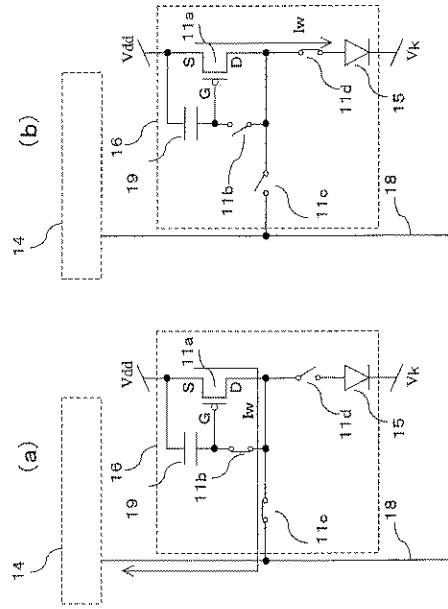

以下、さらに本発明の理解を容易にするために、本発明のEL素子構成について図3を用いて説明する。本発明のEL素子構成は2つのタイミングにより制御される。第1のタイミングは必要な電流値を記憶させるタイミングである。このタイミングでトランジスタ11bならびにトランジスタ11cがONすることにより、等価回路として図3（a）と

なる。ここで、信号線より所定の電流  $I_w$  が書き込まれる。これによりトランジスタ 11 a はゲートとドレインが接続された状態となり、このトランジスタ 11 a とトランジスタ 11 c を通じて電流  $I_w$  が流れる。従って、トランジスタ 11 a のゲート-ソースの電圧は  $I_1$  が流れるような電圧  $V_1$  となる。

第 2 のタイミングはトランジスタ 11 a とトランジスタ 11 c が閉じ、トランジスタ 11 d が開くタイミングであり、そのときの等価回路は図 3 ( b ) となる。トランジスタ 11 a のソース - ゲート間の電圧は保持されたままとなる。この場合、トランジスタ 11 a は常に飽和領域で動作するため、 $I_w$  の電流は一定となる。

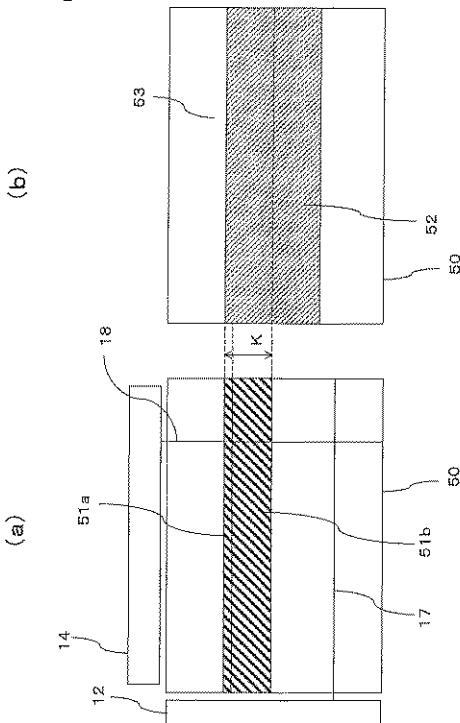

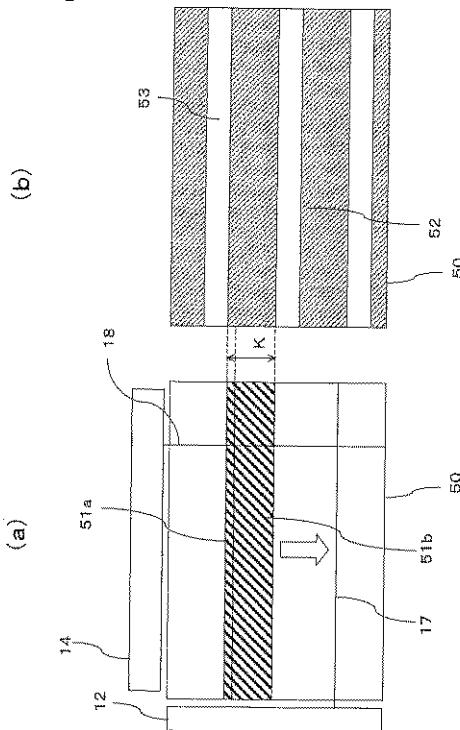

このように動作させると、図 5 に図示するようになる。つまり、図 5 ( a ) の 51a は表示画面 50 における、ある時刻での電流プログラムされている画素 ( 行 ) ( 書き込み画素行 ) を示している。この画素 ( 行 ) 51a は、図 5 ( b ) に図示するように非点灯 ( 非表示画素 ( 行 ) ) とする。他の、画素 ( 行 ) は表示画素 ( 行 ) 53 とする ( 非画素 53 の EL 素子 15 には電流が流れ、EL 素子 15 が発光している )。

図 1 の画素構成の場合、図 3 ( a ) に示すように、電流プログラム時は、プログラム電流  $I_w$  がソース信号線 18 に流れる。この電流  $I_w$  がトランジスタ 11 a を流れ、 $I_w$  を流す電流が保持されるように、コンデンサ 19 に電圧設定 ( プログラム ) される。このとき、トランジスタ 11 d はオーブン状態 ( オフ状態 ) である。

次に、EL 素子 15 に電流を流す期間は図 3 ( b ) のように、トランジスタ 11 c 、 11 b がオフし、トランジスタ 11 d が動作する。つまり、ゲート信号線 17a にオフ電圧 ( $V_{gh}$ ) が印加され、トランジスタ 11 b 、 11 c がオフする。一方、ゲート信号線 17b にオン電圧 ( $V_{g1}$ ) が印加され、トランジスタ 11 d がオンする。

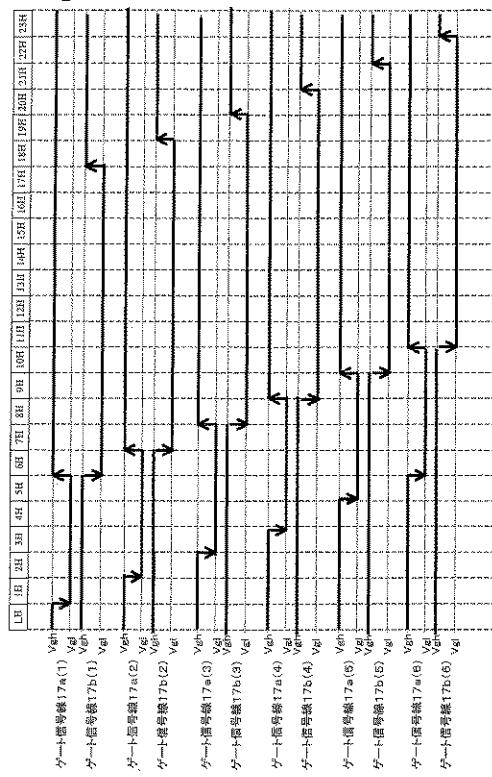

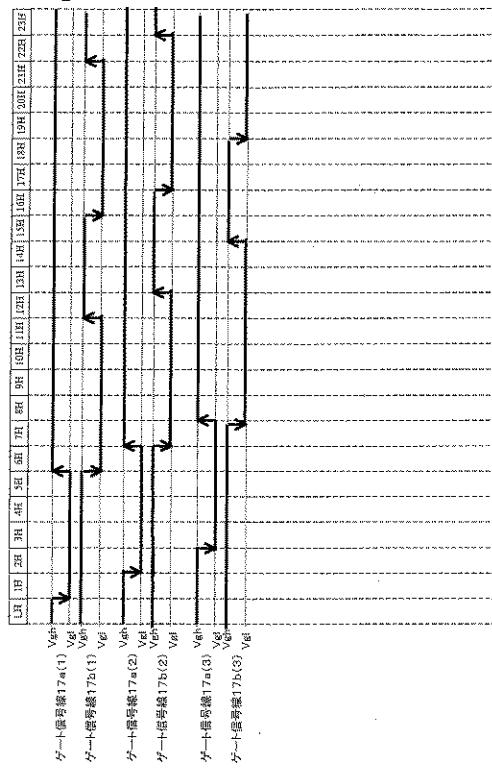

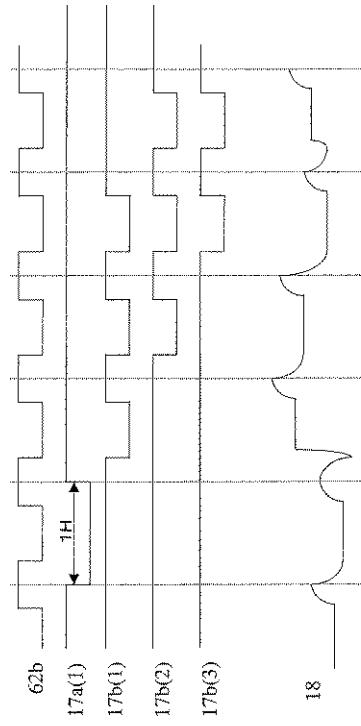

このタイミングチャートを図 4 に図示する。なお、図 4 などにおいて、括弧内の添え字 ( たとえば、( 1 ) など ) は画素行の番号を示している。つまり、ゲート信号線 17a ( 1 ) とは、画素行 ( 1 ) のゲート信号線 17a を示している。また、図 4 の上段の \*H とは、水平走査期間を示している。つまり、1H とは第 1 番目の水平走査期間である。なお、以上の事項は、説明を容易にするためであって、限定 ( 1H の番号、1H 周期、画素行番号の順番など ) するものではない。

図 4 でわかるように、各選択された画素行 ( 選択期間は、1H としている ) において、ゲート信号線 17a にオン電圧が印加されている時には、ゲート信号線 17b にはオフ電圧が印加されている。また、この期間は、EL 素子 15 には電流が流れていない ( 非点灯状態 )。選択されていない画素行において、ゲート信号線 17a にオフ電圧が印加され、ゲート信号線 17b にはオン電圧が印加されている。また、この期間は、EL 素子 15 に電流が流れている ( 点灯状態 )。

なお、トランジスタ 11 b のゲートとトランジスタ 11 c のゲートは同一のゲート信号線 17a に接続している。しかし、トランジスタ 11 b のゲートとトランジスタ 11 c のゲートとを異なるゲート信号線 17 に接続してもよい。1 画素のゲート信号線は 3 本となる ( 図 1 の構成は 2 本である )。トランジスタ 11 b のゲートの ON / OFF タイミングとトランジスタ 11 c のゲートの ON / OFF タイミングを個別に制御することにより、トランジスタ 11 a のばらつきによる EL 素子 15 の電流値バラツキをさらに低減することができる。

ゲート信号線 17a とゲート信号線 17b とを共通にし、トランジスタ 11 c と 11 d が異なった導電型 ( N チャンネルと P チャンネル ) とすると、駆動回路の簡略化、ならびに画素の開口率を向上させることが出来る。

このように構成すれば本発明の動作タイミングとしては信号線からの書き込み経路がオフになる。すなわち所定の電流が記憶される際に、電流の流れる経路に分岐があると正確な電流値がトランジスタ 11 a のソース ( S ) - ゲート ( G ) 間容量 ( コンデンサ ) に記憶されない。トランジスタ 11 c とトランジスタ 11 d を異なった導電形にすることにより、お互いの閾値を制御することによって走査線の切り替わりのタイミングで必ずトランジスタ 11 c がオフしたのちに、トランジスタ 11 d がオンすることが可能になる。

本特許の発明の目的は、トランジスタ特性のばらつきが表示に影響を与えない回路構成

を提案するものであり、そのために4トランジスタ以上が必要である。これらのトランジスタ特性により、回路定数を決定する場合、4つのトランジスタの特性がそろわなければ、適切な回路定数を求めることが困難である。レーザー照射の長軸方向に対して、チャンネル方向が水平の場合と垂直の場合では、トランジスタ特性の閾値と移動度が異なって形成される。なお、どちらの場合もばらつきの程度は同じである。水平方向と、垂直方向では移動度、閾値のあたいの平均値が異なる。したがって、画素を構成するすべてのトランジスタのチャンネル方向は同一であるほうが望ましい。

図27においてEL素子15に流す電流を設定する時、トランジスタ271aに流す信号電流を $I_w$ 、その結果トランジスタ271aに生ずるゲート-ソース間電圧を $V_{gs}$ とする。書き込み時はトランジスタ11cによってトランジスタ271aのゲート・ドレイン間が短絡されているので、トランジスタ271aは飽和領域で動作する。よって、 $I_w$ は、以下の式で与えられる。

(数1)

$$I_w = \mu_1 \cdot C_{ox} \cdot \{W_1 / (2 \cdot L_1)\} \cdot (V_{gs} - V_{th1})^2$$

ここで、 $C_{ox}$ は単位面積当たりのゲート容量であり、 $C_{ox} = \epsilon_0 \cdot r / d$ で与えられる。 $V_{th}$ はトランジスタの閾値、 $\mu$ はキャリアの移動度、 $W$ はチャンネル幅、 $L$ はチャンネル長、 $\epsilon_0$ は真空の移動度、 $r$ はゲート絶縁膜の比誘電率を示し、 $d$ はゲート絶縁膜の厚みである。EL素子15に流れる電流を $I_{dd}$ とすると、 $I_{dd}$ は、EL素子15と直列に接続されるトランジスタ271bによって電流レベルが制御される。本発明では、そのゲート-ソース間電圧が(数1)の $V_{gs}$ に一致するので、トランジスタ1bが飽和領域で動作すると仮定すれば、以下の式が成り立つ。

(数2)

$$I_{drv} = \mu_2 \cdot C_{ox} \cdot \{W_2 / (2 \cdot L_2)\} \cdot (V_{gs} - V_{th2})^2$$

絶縁ゲート電界効果型の薄膜トランジスタ(トランジスタ)が飽和領域で動作するための条件は、 $V_{ds}$ をドレイン・ソース間電圧として、一般に以下の式で与えられる。

(数3)

$$|V_{ds}| > |V_{gs} - V_{th}|$$

ここで、トランジスタ271aとトランジスタ271bは、小さな画素内部に近接して形成されるため、大略 $\mu_1 = \mu_2$ 及び $C_{ox1} = C_{ox2}$ であり、特に工夫を凝らさない限り、 $V_{th1} = V_{th2}$ と考えられる。すると、このとき(数1)及び(数2)から容易に以下の式が導かれる。

(数4)

$$I_{drv} / I_w = (W_2 / L_2) / (W_1 / L_1)$$

ここで注意すべき点は、(数1)及び(数2)において、 $\mu$ 、 $C_{ox}$ 、 $V_{th}$ の値自体は、画素毎、製品毎、あるいは製造ロット毎にばらつくのが普通であるが、(数4)はこれらのパラメータを含まないので、 $I_{drv} / I_w$ の値はこれらのばらつきに依存しないということである。

仮に $W_1 = W_2$ 、 $L_1 = L_2$ と設計すれば、 $I_{drv} / I_w = 1$ 、すなわち $I_w$ と $I_{drv}$ が同一の値となる。すなわちトランジスタの特性ばらつきによらず、EL素子15に流れる駆動電流 $I_{dd}$ は、正確に信号電流 $I_w$ と同じになるので、結果としてEL素子15の発光輝度を正確に制御できる。

以上の様に、駆動用トランジスタ271aの $V_{th1}$ と駆動用トランジスタ271bの

$V_{th2}$  は基本的に同一である為、両トランジスタお互いにの共通電位にあるゲートに対してカットオフレベルの信号電圧が印加されると、トランジスタ 271a 及びトランジスタ 271b 共に非導通状態になるはずである。ところが、実際には画素内でもパラメータのばらつきなどの要因により、 $V_{th1}$  よりも  $V_{th2}$  が低くなってしまうことがある。この時には、駆動用トランジスタ 271b にサブスレッショルドレベルのリーク電流が流れる為、EL 素子 15 は微発光を呈する。この微発光により画面のコントラストが低下し表示特性が損なわれる。

本発明では特に、駆動用トランジスタ 271b の閾電圧  $V_{th2}$  が画素内で対応する駆動用トランジスタ 271a の閾電圧  $V_{th1}$  より低くならない様に設定している。例えば、トランジスタ 271b のゲート長  $L_2$  をトランジスタ 271a のゲート長  $L_1$  よりも長くして、これらの薄膜トランジスタのプロセスパラメータが変動しても、 $V_{th2}$  が  $V_{th1}$  よりも低くならない様にする。これにより、微少な電流リークを抑制することが可能である。以上の事項は図 1 のトランジスタ 271a とトランジスタ 11c の関係にも適用される。

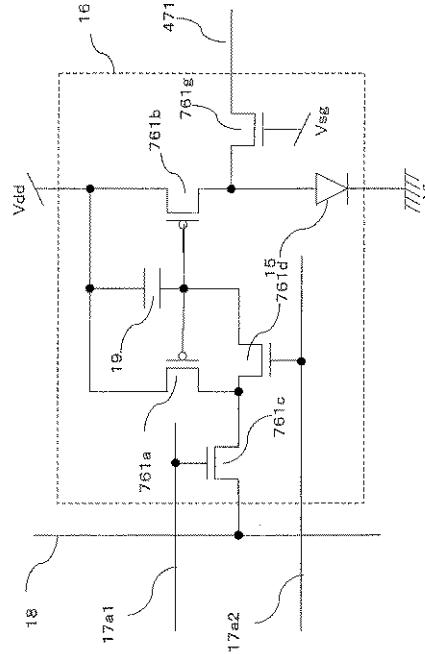

図 27 に示すように、信号電流が流れる駆動用トランジスタ 271a、EL 素子 15 等からなる発光素子に流れる駆動電流を制御する駆動用トランジスタ 271b の他、ゲート信号線 17a1 の制御によって画素回路とデータ線 data とを接続もしくは遮断する取込用トランジスタ 11b、ゲート信号線 17a2 の制御によって書き込み期間中にトランジスタ 271a のゲート・ドレインを短絡するスイッチ用トランジスタ 11c、トランジスタ 271a のゲート - ソース間電圧を書き込み終了後も保持するための容量 C19 および発光素子としての EL 素子 15 などから構成される。

図 27 でトランジスタ 11b、11c は N チャンネル MOS (NMOS)、その他のトランジスタは P チャンネル MOS (PMOS) で構成しているが、これは一例であって、必ずしもこの通りである必要はない。容量 C は、その一方の端子をトランジスタ 271a のゲートに接続され、他方の端子は Vdd (電源電位) に接続されているが、Vdd に限らず任意の一定電位でも良い。EL 素子 15 のカソード (陰極) は接地電位に接続されている。したがって、以上の事項は図 1 などにも適用されることはあるまでもない。

なお、図 1 などの Vdd 電圧はトランジスタ 271b のオフ電圧 (トランジスタが P チャンネル時) よりも低くすることが好ましい。具体的には、 $V_{gh}$  (ゲートのオフ電圧) は少なくとも  $V_{dd} - 0.5$  (V) よりの高くするべきである。これよりも低いとトランジスタのオフリークが発生し、レーザーニールのショットムラが目立つようになる。また、 $V_{dd} + 4$  (V) よりも低くすべきである。あまりにも高いと逆にオフリーク量が増加する。

したがって、ゲートのオフ電圧 (図 1 では  $V_{gh}$ 、つまり、電源電圧に近い電圧側) は、電源電圧 (図 1 では  $V_{dd}$ ) は、よりも -0.5 (V) 以上 +4 (V) 以下とすべきである。さらに好ましくは、電源電圧 (図 1 では  $V_{dd}$ ) は、よりも 0 (V) 以上 +2 (V) 以下とすべきである。つまり、ゲート信号線に印加するトランジスタのオフ電圧は、十分オフになるようにする。トランジスタが N チャンネルの場合は、 $V_{g1}$  がオフ電圧となる。したがって、 $V_{g1}$  は GND 電圧に対して -4 (V) 以上 0.5 (V) 以下の範囲となるようにする。さらに好ましくは -2 (V) 以上 0 (V) 以下の範囲することが好ましい。

以上の事項は、図 1 の電流プログラムの画素構成について述べたが、これに限定するものではなく、電圧プログラムの画素構成にも適用できることは言うまでもない。なお、電圧プログラムの  $V_t$  オフセットキャンセルは、R、G、B ごとに個別に補償することが好ましい。

駆動用トランジスタ 271b は、コンデンサ 19 に保持された電圧レベルをゲートに受け入れそれに応じた電流レベルを有する駆動電流はチャネルを介して EL 素子 15 に流す。トランジスタトランジスタ 271a のゲートとトランジスタトランジスタ 271b のゲートとが直接に接続されてカレントミラー回路を構成し、信号電流  $I_w$  の電流レベルと駆動電流の電流レベルとが比例関係となる様にしている。

トランジスタ 271b は飽和領域で動作し、そのゲートに印加された電圧レベルと閾電圧との差に応じた駆動電流を EL 素子 15 に流す。

トランジスタ 271b は、その閾電圧が画素内で対応するトランジスタ 271a の閾電圧より低くならない様に設定されている。具体的には、トランジスタ 271b は、そのゲート長がトランジスタ 271a のゲート長より短くならない様に設定されている。あるいは、トランジスタ 271b は、そのゲート絶縁膜が画素内で対応するトランジスタ 271a のゲート絶縁膜より薄くならないように設定しても良い。

あるいは、トランジスタ 271b は、そのチャネルに注入される不純物濃度を調整して、閾電圧が画素内で対応するトランジスタ 271a の閾電圧より低くならない様に設定してもよい。仮に、トランジスタ 271a とトランジスタ 271b の閾電圧が同一となる様に設定した場合、共通接続されたトランジスタのゲートにカットオフレベルの信号電圧が印加されると、トランジスタ 271a 及びトランジスタ 271b は両方共オフ状態になるはずである。ところが、実際には画素内にも僅かながらプロセスパラメータのばらつきがあり、トランジスタ 271a の閾電圧よりトランジスタ 271b の閾電圧が低くなる場合がある。

この時には、カットオフレベル以下の信号電圧でもサブレッショルドレベルの微弱電流が駆動用トランジスタ 271b に流れる為、EL 素子 15 は微発光し画面のコントラスト低下が現れる。そこで、トランジスタ 271b のゲート長をトランジスタ 271a のゲート長よりも長くしている。これにより、トランジスタ 11 のプロセスパラメータが画素内で変動しても、トランジスタ 271b の閾電圧がトランジスタ 271a の閾電圧よりも低くならない様にする。

ゲート長 L が比較的短い短チャネル効果領域 A では、ゲート長 L の増加に伴い  $V_{th}$  が上昇する。一方、ゲート長 L が比較的大きな抑制領域 B ではゲート長 L に関わらず  $V_{th}$  はほぼ一定である。この特性を利用して、トランジスタ 271b のゲート長をトランジスタ 271a のゲート長よりも長くしている。例えば、トランジスタ 271a のゲート長が 7  $\mu m$  の場合、トランジスタ 271b のゲート長を 10  $\mu m$  程度にする。

トランジスタ 271a のゲート長が短チャネル効果領域 A に属する一方、トランジスタ 271b のゲート長が抑制領域 B に属する様にしても良い。これにより、トランジスタ 271b における短チャネル効果を抑制することができるとともに、プロセスパラメータの変動による閾電圧低減を抑制可能である。以上により、トランジスタ 271b に流れるサブレッショルドレベルのリーク電流を抑制して EL 素子 15 の微発光を抑え、コントラスト改善に寄与可能である。

このようにして作製した図 1、図 2、図 27 などで説明した EL 表示素子 15 に直流電圧を印加し、10 mA / cm<sup>2</sup> の一定電流密度で連続駆動させた。EL 構造体は、7.0 V、200 cd / cm<sup>2</sup> の緑色（発光極大波長  $\lambda_{max} = 460 nm$ ）の発光が確認できた。青色発光部は、輝度 100 cd / cm<sup>2</sup> で、色座標が x = 0.129、y = 0.105、緑色発光部は、輝度 200 cd / cm<sup>2</sup> で、色座標が x = 0.340、y = 0.625、赤色発光部は、輝度 100 cd / cm<sup>2</sup> で、色座標が x = 0.649、y = 0.338 の発光色が得られた。

フルカラー有機 EL 表示パネルでは、開口率の向上が重要な開発課題になる。開口率を高めると光の利用効率が上がり、高輝度化や長寿命化につながるためである。開口率を高めるためには、有機 EL 層からの光を遮るトランジスタの面積を小さくすればよい。低温多結晶 Si - トランジスタはアモルファスシリコンに比較して 10 - 100 倍の性能を持ち、電流の供給能力が高いため、トランジスタの大きさを非常に小さくできる。したがって、有機 EL 表示パネルでは、画素トランジスタ、周辺駆動回路を低温ポリシリコン技術、高温ポリシリコン技術で作製することが好ましい。もちろん、アモルファスシリコン技術で形成してもよいが画素開口率はかなり小さくなってしまう。

ゲートドライバ回路 12 あるいはソースドライバ回路 14 などの駆動回路をガラス基板 71 上に形成することにより、電流駆動の有機 EL 表示パネルで特に問題になる抵抗を下げることができる。TCP の接続抵抗がなくなるうえに、TCP 接続の場合に比べて電極

からの引き出し線が2~3mm短くなり配線抵抗が小さくなる。さらに、TCP接続のための工程がなくなる、材料コストが下がるという利点があるとする。

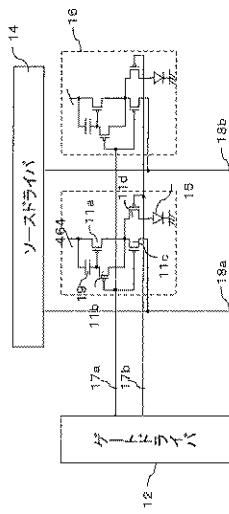

次に、本発明のEL表示パネルあるいはEL表示装置について説明をする。図6はEL表示装置の回路を中心とした説明図である。画素16がマトリックス状に配置または形成されている。各画素16には各画素の電流プログラムを行う電流を出力するソースドライバ回路14が接続されている。ソースドライバ回路14の出力段は映像信号のビット数に対応したカレントミラー回路が形成されている（後に説明する）。たとえば、64階調であれば、63個のカレントミラー回路が各ソース信号線に形成され、これらのカレントミラー回路の個数を選択することにより所望の電流をソース信号線18に印加できるように構成されている。10

なお、1つのカレントミラー回路の1つの単位トランジスタの最小出力電流は10nA以上50nA以下にしている。特にカレントミラー回路の最小出力電流は15nA以上35nA以下にすることがよい。ソースドライバIC14内のカレントミラー回路を構成するトランジスタの精度を確保するためである。

また、ソース信号線18の電荷を強制的に放出または充電するプリチャージあるいはディスチャージ回路を内蔵する。ソース信号線18の電荷を強制的に放出または充電するプリチャージあるいはディスチャージ回路の電圧（電流）出力値は、R、G、Bで独立に設定できるように構成することが好ましい。EL素子15の閾値がRGBでことなるからである。

以上に説明した画素構成、アレイ構成、パネル構成などは、以下に説明する構成、方法、装置に適用されることはあるまでもない。また、以下に説明する構成、方法、装置は、すでに説明した画素構成、アレイ構成、パネル構成などが適用されることはあるまでもない。20

ゲートドライバ12はゲート信号線17a用のシフトレジスタ回路61aと、ゲート信号線17b用のシフトレジスタ回路61bとを内蔵する。各シフトレジスタ回路61は正相と負相のクロック信号（CLKxP、CLKxN）、スタートパルス（STx）で制御される。その他、ゲート信号線の出力、非出力を制御するイネーブル（ENABLE）信号、シフト方向を上下逆転するアップダウン（UPDOWN）信号を付加することが好ましい。他に、スタートパルスがシフトレジスタにシフトされ、そして出力されていることを確認する出力端子などを設けることが好ましい。30

なお、シフトレジスタのシフトタイミングはコントロールIC81からの制御信号で制御される。また、外部データのレベルシフトを行うレベルシフト回路を内蔵する。また、検査回路を内蔵する。

図8は本発明の表示装置の信号、電圧の供給の構成図あるいは表示装置の構成図である。コンピュータIC81からソースドライバ回路14aに供給する信号（電源配線、データ配線など）はフレキシブル基板84を介して供給する。

図8ではゲートドライバ12の制御信号はコントロールICで発生させ、ソースドライバ14でいったん、レベルシフトを行った後、ゲートドライバ12に印加している。ソースドライバ14の駆動電圧は4~8(V)であるから、コントロールIC81から出力された3.3(V)振幅の制御信号を、ゲートドライバ12が受け取れる5(V)振幅に変換することができる。40

以下、本発明の駆動方法について説明する。本発明は有機ELパネルの駆動に特化した輝度調整駆動である。有機EL素子は蓄積容量19に蓄積された電荷とVddに応じて駆動トランジスタ11aが流す電流量に比例して発光する。そのため、図12に示すようにパネルに流れる総電流とパネルの明るさの関係はリニアになる。有機EL素子に電流を流すための電圧Vddは図24に示すようにバッテリー241によって供給される。

このバッテリー241には容量の制限があり、特に小型モジュールに使用する場合流すことの出来る電流量は少なくなる。仮に、図25に示すようにバッテリー241が有機ELパネルの消費する電力の50%までしか流すことができないとすると。ここで251に示すような直線で有機ELが発する明るさ（全面白表示を100%とする）と電力の関係を50

決めると明るさの高い領域ではバッテリーの流せる最大の電流量を超えてしまうため、バッテリーを破壊してしまう恐れがある。

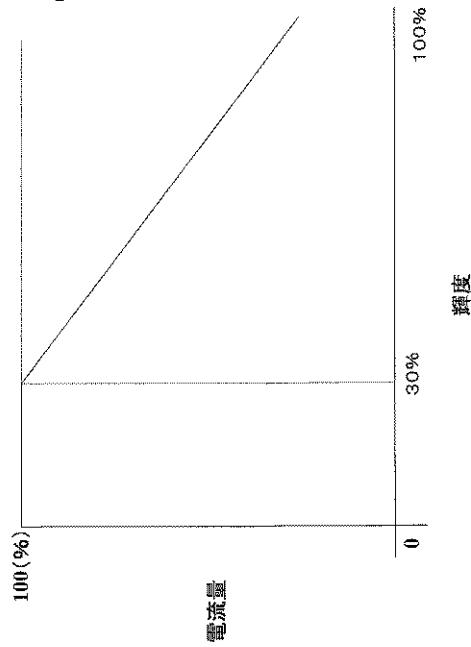

反対に 252 に示すように有機ELパネルの最大発光時に流れる電流量と、バッテリー 241 が流すことが出来る最大電流量を同じ値にして明るさと電力の関係を決めると低輝度部において電流を流すことが出来なくなる。一般に映像データは全面白表示状態を 100 % とすると、30 % 辺りが多いと言われている。252 に示すような明るさと電流量の関係にすると、映像データの多い領域で電流を流すことが出来なくなり、見栄えのしない画像になってしまう。

そこで本発明では図 26 に示すように特定の入力データを設定し、そのデータに応じて、有機ELパネルに流れる電流量を調整する駆動を提案する。バッテリーの限界値を超える可能性がある領域では電流値を抑制し、電流があまり流れない領域では電流量を増やす駆動方法である。この駆動方法を実現すると有機ELパネルの明るさと電流量の関係は 282 のようになり、バッテリーの容量制限があっても映像データの多い領域で電流を流すことが可能となり、見栄えの良い画像を作ることができる。本発明の内容は 2 種類の駆動方法を組み合わせたもので、以下その駆動方法と適用される回路構成を説明する。第 1 の駆動方法は、従来の一般的な駆動方法と同様に外部からの入力映像データと自己発光素子を用いた表示装置の画面の輝度、もしくは自己発光素子のアノード電極とカソード電極の間に流れる電流量の関係が 1 : 1 に対応、すなわち 1 つの入力映像データに対して取り得る電流量の値は 1 つであり予め定められた値であり、外部からの入力映像信号に応じた第 1 の輝度で各表示画素を発光させる。またそれらは比例の関係にあり、理想的には線形的に比例する。本発明では特に低階調側（黒表示側）の駆動に適用した場合を説明する。

一方第 2 の駆動方法は、外部からの入力映像データと自己発光素子を用いた表示装置の画面の輝度、もしくは自己発光素子のアノード電極とカソード電極の間に流れる電流量の関係を 1 対 1 に対応させるのではなく、周辺の入力映像データの分布状況を考慮した電流量を決定、すなわち可変値の中から定められたある値に決定される。従って先程の第 1 の駆動と異なり、線形的な比例関係になるとは限らず、非線形な関係になることが多い。このとき外部からの入力映像信号に応じた第 1 の輝度を所定の割合で抑制した第 2 の輝度で各表示画素を発光させる。従って先程の第 1 の駆動と異なり、線形的な比例関係になるとは限らず、非線形な関係になることが多い。

第 2 の駆動方法では電流量の値は、まず外部から入力される映像データに対して第 1 の駆動方法を施したと仮定したときの電流量を 1 としたときに、ある所定の定数（1 以下の数）を乗して抑制された電流量として得ることができる。定数の値については周辺の入力映像データの分布状況により都度決定される。また、前に述べたように映像データが多い領域では電流を多く流したいため、抑制処理を行わない場合の最大入力データに対する電力、もしくは電流量を 1 とすると、第 2 の駆動を適用する領域において、電力値  $x$  が  $0.2 \times 0.6$  になるように電力、もしくは電流量を調整することを特徴とする駆動方法である。

尚、第 2 の駆動を行う回路にスイッチング手段を設け、第 2 の駆動手段の入切を制御することで、

第 2 の駆動手段を入れた場合は本発明の駆動方法を行い、また第 2 の駆動手段を切った場合には従来の駆動方法と互換性を持たせることができる。

電流値を調整する方法として二つの方法を提案する。一つはソース信号線 18 に流す電流量を減らし、有機EL素子に流れる電流量自体を調整する方法である。しかし、この方法は電流量を抑制する際にはソース信号線 18 に流れる電流量を少なくしなくてはならない。前に示したように有機EL素子は蓄積容量 19 に蓄積された電荷に応じて発光する。入力されたデータを正しく発光させるためには蓄積容量 19 に正しい電流値を流せるような電荷を蓄積する必要がある。

しかし、実際ソース信号線 18 には浮遊容量 451 が存在する。V2 から V1 までソース信号線電圧を変化させるにはこの浮遊容量の電荷を引き抜く必要がある。この引き抜きにかかる時間 T は、 $Q$  (浮遊容量の電荷) =  $I$  (ソース信号線に流れる電流) ×  $T$

10

20

30

40

50

= C (浮遊容量値) × V となる。このため、電流値 I を減少させると蓄積容量 19 に正しい電荷を蓄積させることができなくなる。また、電流値を減少させると、階調表現が困難になる。階調を 1024 階調で表現させようとすると黒を表示させるための電流値と白を表現させる電流値の差を 1024 等分する必要がある。そのため、白を表現させる電流値をへらすと 1 階調あたりの電流変化量が小さくなり、階調表現をするための精度が高くなり、実現が難しくなる。

まず、映像を判断するための表示データについて説明をする。表示データは、画像データあるいはパネルの消費電流（アノード電極とカソード電極の間に流れる電流）から導出する。本発明中では表示データを % で示している。100% は表示データの最大値、つまり全ての画素が最高階調で発光する状態であり、0% は全ての画素が最低階調で発光する状態である。

10

1 画面の画像データが全体的に大きいときは画像データの総和は大きくなる。たとえば、白ラスターは 64 階調表示の場合は画像データとしては 63 であるから、画面 50 の画素数 × 63 が画像データの総和である。1 / 100 の白ウインドウ表示で、白表示部が最大輝度の白表示では、画面 50 の画素数 × (1 / 100) × 63 が画像データの総和である（データ和の最大値である）。

本発明では画像データの総和あるいは画面の消費電流量を予測できる値を求め、この総和あるいは値により、自己発光素子のアノード電極とカソード電極の間に流れる電流量を抑制する駆動を行う。

なお、画像データの総和を求めるとしたが、これに限定するものではない。たとえば、画像データの 1 フレームの平均レベルを求めてこれを用いてもよい。アナログ信号であれば、アナログ画像信号をコンデンサによりフィルタリングすることにより平均レベルを得ることができる。アナログの映像信号に対しフィルタを介して直流レベルを抽出し、この直流レベルを A/D 変換して画像データの総和としてもよい。この場合は、画像データは APL レベルとも言うことができる。

20

本発明中には表示データを入力データと書いている場合があるが、これは同義語である。

。

また、画面を構成する画像のすべてのデータを加算する必要はなく、画面の 1/W (W は 1 より大きい値) をピックアップして抽出し、ピックアップしたデータの総和を求めてよい。

30

データ和 / 最大値は表示データ（入力データ）の比率と同義である。データ和 / 最大値が 1 であれば、入力データが 100% である（基本的に最大の白ラスター表示）。データ和 / 最大値が 0 であれば、入力データが 0% である（基本的に完全黒ラスター表示である）。

データ和 / 最大値は、映像データの和から求める。入力映像信号が Y、U、V の場合は、Y (輝度) 信号から求めても良い。しかし、EL パネルの場合は、R、G、B で発光効率が異なるため、Y 信号から求めた値が消費電力にならない。したがって、Y、U、V 信号の場合も、一度 R、G、B 信号に変換し、R、G、B に応じて電流に換算する係数をかけて、消費電流（消費電力）を求めることが好ましい。しかし、簡易的に Y 信号から消費電流を求ることは回路処理が容易になることも考慮してもよい。

40

表示データの比率を精度良く求めるためには演算を行うと良い。演算とは加算、減算、乗算、除算をふくむものである。

また、有機 EL パネルに流れる電流値を外部回路により測定し、フィードバックすることにより判断する方法も可能である。同様に有機 EL パネル内にサーミスタもしくは熱電対などの温度センサーやフォトセンサーを内蔵することにより得られるデータを利用するこども可能である。

表示データは、パネルに流れる電流、つまり自己発光素子のアノード電極とカソード電極の間に流れる電流量で換算されているものであるとする。なぜなら、EL 表示パネルでは B の発光効率が悪いため、海の表示などが表示されると、消費電力が一気に増加するからである。したがって、最大値は、電源容量の最大値である。また、データ和とは単純な

50

映像データの加算値ではなく、映像データを消費電流に換算したものとしている。したがって、点灯率も最大電流に対する各画像の使用電流から求められたものである。

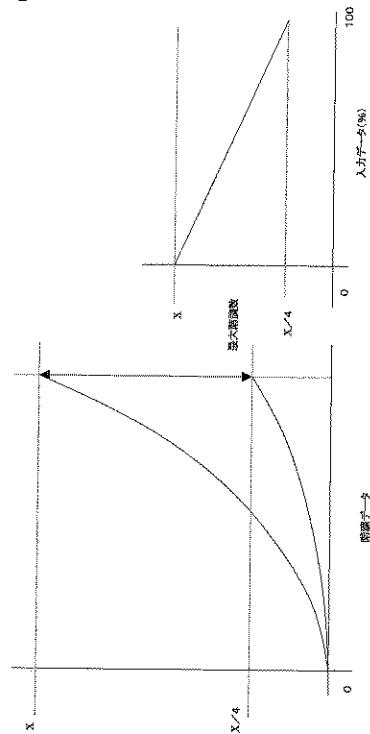

二つ目はソース信号線に流す電流値  $I$  はそのままに 1 画面に点灯している水平走査線数（点灯率）を変えることで明るさを制御する。有機 EL パネルはトランジスタ 11d の ON 時間を制御することで水平走査線の 1 フレーム内の点灯時間を制御することができる。図 14 に示すようにゲートドライバー 12 を制御して 1 フレーム内の 1/N 期間しか点灯させないような駆動をすると、明るさは全ての水平走査線が常に点灯している場合の明るさに対して 1/N になる。この方法により明るさを調整することが可能である。この方法では発光している期間で明るさを制御するため、発光量を制御しても階調表現を実現するためのソース信号線に流れる電流値に求められる精度は変わらないので階調表現を容易に実現できる。そのため、本発明では点灯率を制御することにより有機 EL パネルに流れる電流量を抑制する駆動方法を提案する。10

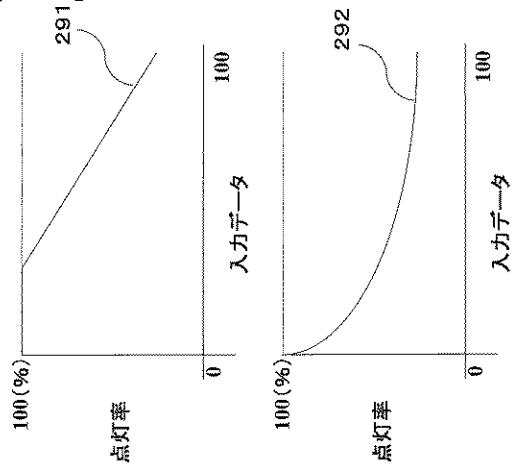

点灯率と入力データの関係は比例関係だけとは限らない。図 29 に示すように曲線や、折れ線にすることも可能である。291 のように一定期間点灯率の高い状況を持続し、その後データに応じて点灯率を低くして行く形は一般的に映像データの明るさが 30%（全面白表示が 100%）のあたりが多い点を考えると有効であると言える。仮にバッテリー 241 の容量が有機 EL パネルに流すことが出来る最大電流量の 50%まで流すことが可能だとすると、入力データが最大の 50% の領域まで点灯率を最大にしておいてもバッテリーを破壊することはない。

また、明るさを制御するのに必ずしもトランジスタ 11d を完全に OFF する必要はない。トランジスタ 11d に少量の電流が流れ、有機 EL 素子 15 が微発光している状態でも明るさを抑制することは可能である。20

また、非発光、もしくは微発光期間は有機 EL 素子 15 を非発光、または微発光にするものであってトランジスタ 11d の ON と OFF で生成するのにかぎるものではない。例えば、図 132、もしくは図 133 に示すようにトランジスタ 11d が無い構成でもアノード電圧、もしくはカソード電圧を上下させることにより非発光、もしくは微発光期間を生成することが可能である。

また、有機 EL 素子 15 に印加される電流を制御することが本発明であるので、図 76 に示すような回路構成でも 761g を制御するのと同じことである。

また、明るさを制御するための非発光部は水平走査線、つまり画素行方向に限るものではない。ソースドライバー 14 を制御して、画素列方向に非発光、もしくは微発光の期間を作り出すことで明るさの制御を行うことが可能である。30

微発光、もしくは非発光の期間をつくることにより、表示映像の中に画素列方向、もしくは画素行方向に微発光、もしくは非発光の表示ができる。この微発光、もしくは非発光の表示を表示映像の中に入れることを黒挿入と呼ぶ。

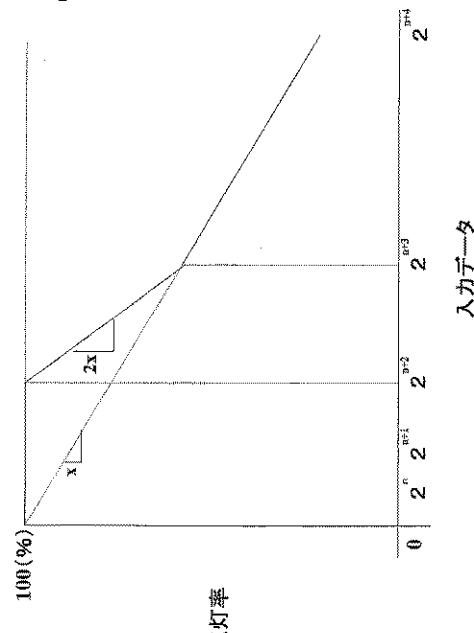

また、入力データは最小と最大の間を 2 の  $n$  乗で刻むことが望ましい。例えば、全面黒点灯を 0 とすると、全面白点灯は 256 (2 の 8 乗) とすると言ったやり方である。点灯率の変化を演算する際に変化量を求めるには最大点灯率と最小点灯率を入力データで割る必要がある。半導体設計において除算回路を組み込むことは回路構成において非常に大きい負荷である。その際に全面白表示時を 2 の  $n$  乗としておくと傾きは最大点灯率と最小点灯率の差を 2 進数にして 8 ビット分シフトするだけで求められるので半導体設計の観点から考えると除算回路を組み込む必要が無くなり、回路設計が非常に容易になる 6291 のような、一定期間最大点灯率を保った後、点灯率を徐々に下げるような波形を実現する際も、図 30 に示すように入力データの最小から 2 の  $n'$  乗までの間点灯率が最大になるような波形では、( ) のような直線型のグラフにおいて傾きを  $x$  とすると 2 の  $n'$  乗から 2 の (  $n'$  + 1 ) 乗までの期間だけ傾きを  $2x$  とすることで直線型のグラフと交わる。この構造を用いることにより、直線型の傾きを求めるだけで、折れ線型のグラフにした際に傾きを求めなおす必要が無くなり、回路規模を大きくせずに様々な折れ線型のグラフを作成することが可能になる。これは回路設計において回路規模を小さく構成するというメリットがある。4050

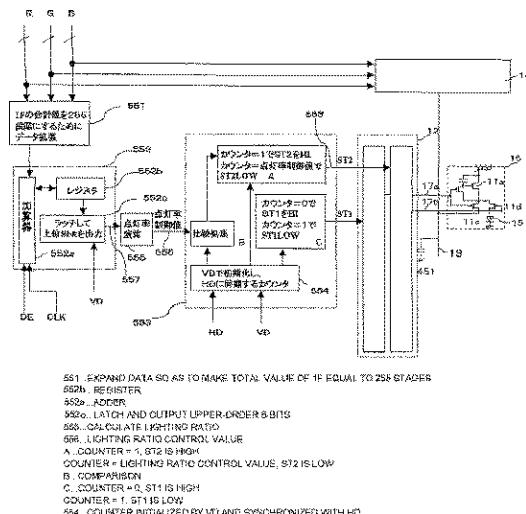

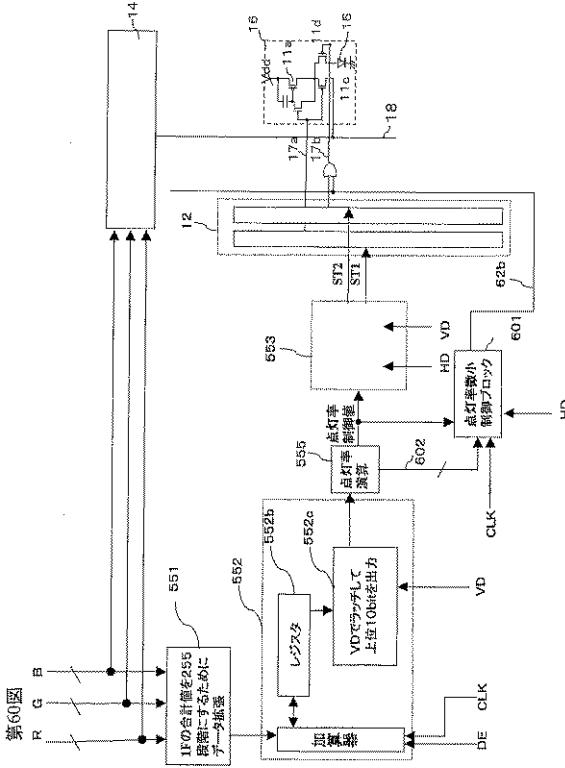

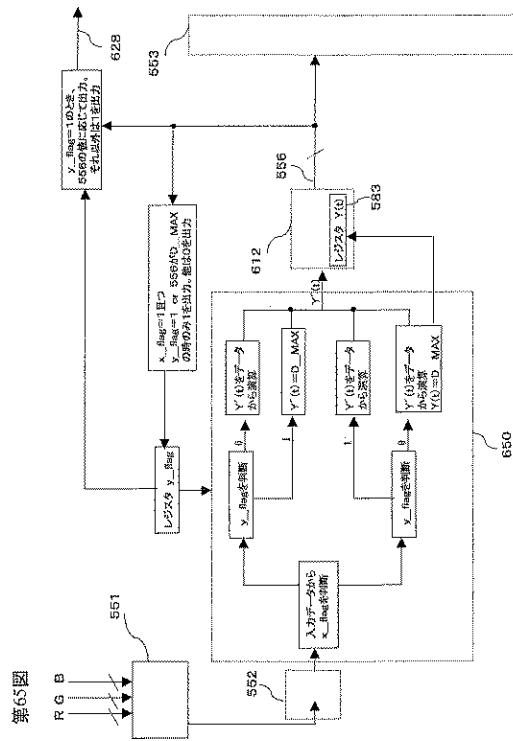

続いて図 5 5 にて本駆動を実現するための回路構成について説明する。まず最初に映像ソースより、RGB の色データが 551 に入力される。同じデータは 处理などの画像処理を経てソースドライバー 14 に入力される。図では RGB の色データを書いているが、RGB に限るものではない。YUV の信号であることも考えられるし、前述のサーミスター やフォトセンサーから得られる温度データや輝度データでも良い。551 でデータを拡張した後、データを収集するモジュール 552 にデータを入力する。551 のデータの拡張に関しては後述で説明する。552 でははじめにデータが加算器 552a に入力される。ただし、常にデータが来ているわけではなく場合によっては画像データ以外の不定なデータが来ている可能性もある。そのため、加算器 552a はデータが来ているかどうかのイネーブル信号 (DE) と、クロック (CLK) により加算するかどうかを決定する。ただし、あらかじめ画像データ以外が入力しないような回路構成を行っている場合はイネーブル信号は必要がない。加算したデータはレジスタ 552b に格納される。そして 552c にて垂直同期信号 (VD) でラッチしてレジスタのデータ (2 進数) の上位 8bit を出力する。レジスタのサイズは規定しない。レジスタのサイズを大きくすれば大きくするほど回路規模は大きくなるが加算データの精度が高まる。また、出力されるデータは 8bit に固定するものではない。点灯率の制御をより細かい範囲で行いたい場合、出力するデータを 9bit 以上にすればよいし、精度が必要としない場合 7bit 以下でもかまわない。出力された値の最大値がすなわち入力されたデータの刻みとなる。出力した 8bit の最大値が 100 の場合、入力データは 100 分割で判断されることになる。前述の様に回路規模を小さくする為にも入力データは 2 の n 乗で刻むことが望ましい。そこで 551 では 1F 間に得られるデータを 255 等分しやすくするために、データの拡張を行う。仮にそのままデータを 552 に入力した場合、出力された値が最大 100 になるとすると 551 で入力データ自体を 2.55 倍して入力することにより出力された値の最大を 255 (0 を含めると 256 (2 の 8 乗) 通り) にすることができる。

次に出力された 8bit の値は点灯率を演算するモジュール 555 に入力される。555 で入力された値は点灯率制御値 556 として演算され、出力される。

点灯率制御値 556 はゲート制御ブロック 553 に入力される。ゲート制御ブロック 553 は VD に同期して初期化され、水平同期信号 (HD) によってカウントアップするカウンター 554 を有している。

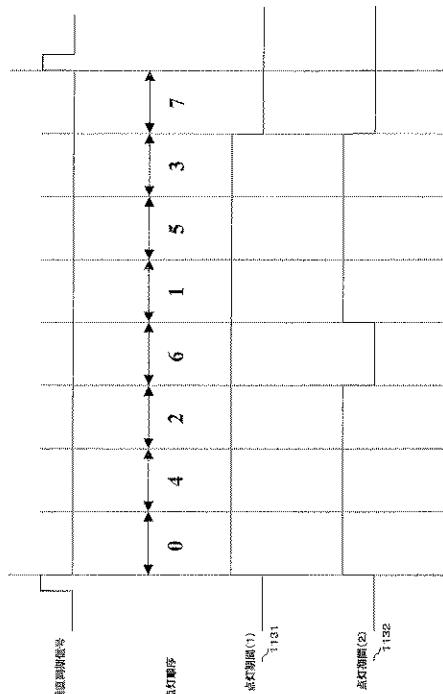

図 56 にて点灯率制御値 556 が 15 のときのゲート制御ブロック 553 のタイムチャートを示す。カウンター 554 が 0 のとき ST1 が HI (スイッチングトランジスタ 11b, 11c を ON にする) になる。ST1 はゲート信号線 17a を制御するためのスタートパルスであり、17a により、スイッチングトランジスタ 11b, 11c が ON / OFF する。また、カウンター 554 が 1 のとき ST1 が LOW になり、ST2 が HI になる。ST2 はゲート信号線 17d を制御するためのスタートパルスであり、17b によりスイッチングトランジスタ 11d が ON / OFF する。すなわち、ST2 の HI 期間の長さが直接、有機 EL 素子 15 の発光時間に関わることになる。そこで点灯率制御信号の値とカウンター 554 が同値のとき、ST2 が LOW になると点灯率制御信号の値により、有機 EL 素子 15 の発光量を調整することが可能となる。仮に点灯率制御値 556 が 255 のときと 1 のときでは点灯率が 1/255 になるため、発光量が 1/255 になる。これにより明るさの制御が可能となる。ST1, 2 を HI にするカウンター値は 0, 1 に固定されるものではない。画像データの遅延などを考慮してもっと大きな値にすることもある。図 55 では点灯率制御信号は 8bit の値を持っている。点灯率制御信号は図 57 にしめすように 552 内部で点灯率の時間分 HI 期間を有する 1bit の信号線でも良い。図 57 の場合は ST2 の信号線と点灯率制御信号線を論理演算することで点灯時間を制御することが可能である。また、画素構成のスイッチングトランジスタ 11b, 11c, 11d によってはゲート信号線の論理が反転する場合もある。

続いて、本発明の駆動を行う際に点灯率の変化を遅延させる方法を提案する。図 38 に示すように時間軸 t (t = 0, 1, 2, ...) に対して入力データが大きく変化すると、点灯率が大きく変化する。このような状況になると、画面内の明るさが頻繁に変化しち

らつきが起きてしまう。そこで図39に示すように現在の点灯率と次フレームで移る予定の点灯率との差分をとり、その差分の数%分だけ変化させることで、変化の割合を緩やかにする。式にすると時間tでの点灯率をY(t)とし、時間tでの入力データから算出する点灯率をY'(t)とすると $Y(t+1) = Y(t) + (Y'(t) - Y(t)) / s$

( $s > 0$ ) $\cdots$ (5)となる。この式で点灯率を変化させる場合、点灯率の差が大きいと変化量も大きくなり、差が小さいと変化量は小さくなる。そのため、sが大きくなりすぎると点灯率が変化するのに必要な時間が長くなってしまう。

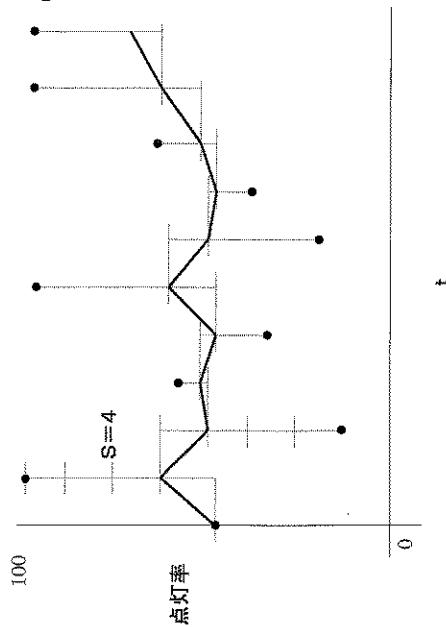

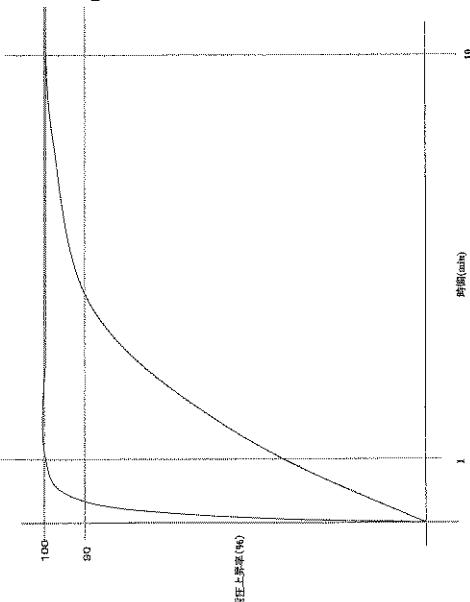

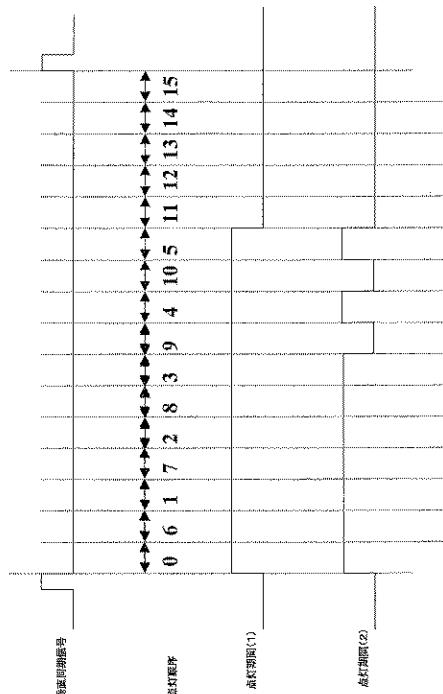

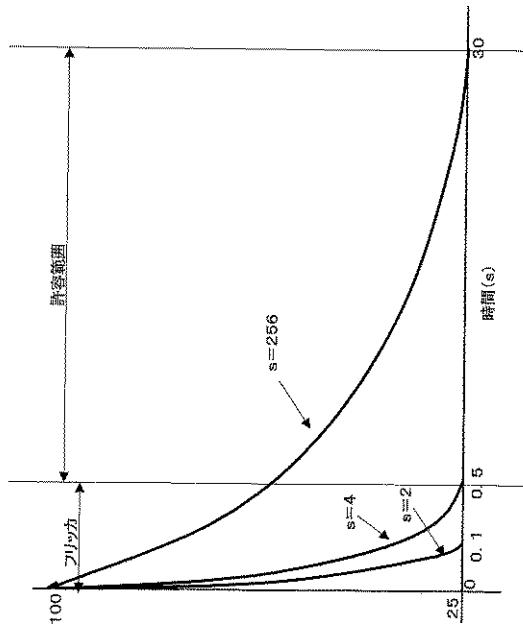

図59に点灯率が0から100まで移動する時に必要なフレーム数とsの関係を示す。60Hzの周波数で映像が映る場合、点灯率が0%から100%に移動するまでにs=32で約200フレーム必要なことから約3秒かかる。これ以上変化に時間がかかると逆に明るさの変化がスムーズに見えなくなる。また、sが小さいとちらつきの改善にならない。回路設計ではデータは2進数で表記されるため除算回路は多くのロジックを必要とし、実現は現実的ではない。しかし、2のn乗で除算を行う場合2進数で表記されたデータの左端を最上位ビット、右端を最下位ビットとするとnビット右にシフトするだけで除算と同じ効果が得られるので回路構成が非常に容易となる。前述の観点からsは2のn乗であるべきである。図134に前面黒表示状態から前面白表示にした際の点灯率の変化を示す。検討の結果、s=2では改善効果が小さいが、s=4ではちらつきが改善する。また、s=256を超えると変化に時間がかかりすぎるため、抑制機能として働くなくなる。以上のことから本発明ではsの範囲を4~s=256とする。さらに好ましくは、4~s=32が好ましい。これにより、ちらつきのない良好な表示を得ることができた。なお、回路設計以外では、sは2のn乗に限定されない。また(5)式の $(Y'(t) - Y(t)) / s$ の分子 $(Y'(t) - Y(t))$ をr倍する際にはsの範囲もr倍されるものとする。

sは常に一定でなくても良い。点灯率の高い領域ではちらつきが少ないのでsを4よりも小さくすると言う方法もある。したがって、点灯率が高い領域と低い領域でsを変化させてもよい。たとえば、点灯率50%以上の時、2~s=16で制御することが好ましく、点灯率50%以下の時、4~s=32で制御することが好ましい。

また、点灯率を下げる場合と、上げる場合で速度を変えたい場合はY'(t)とY(t)の大小関係でsの値を変えるのも有効である。

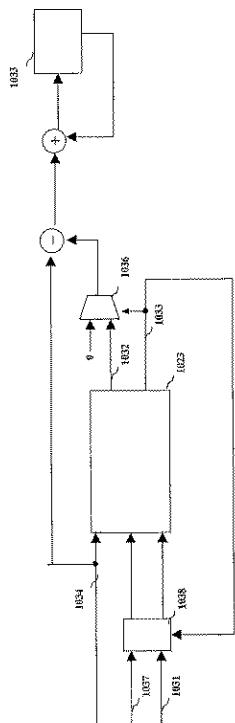

図58にて点灯率の変化を遅延させる駆動方法の回路構成を示す。前述の通り551から出力されたデータを加算器552aにて加算し、レジスタ552bに収納する。VDに同期して出力された8bitの値を演算モジュールにて演算し、点灯率制御値Y'(t)を導く。Y'(t)は減算モジュール582に入力される。減算モジュール582内では現在の点灯率制御値を保持するレジスタ583から得た点灯率制御値Y(t)と現在の入力データから導かれる点灯率制御値Y'(t)の減算を行い、二つの差分S(t)を求める。次にS(t)は入力されるsの値により584内で除算処理を行う。前述の用に除算処理は複雑なロジックを必要とするため、入力されるsの値を2のn乗にすることにより、S(t)は最下位ビット(LSB)側にnbitシフトさせることにより除算を行うことが可能となる。

除算を行ったS(t)はレジスタ583に保持された現在の点灯率制御値Y(t)と加算モジュール585にて加算される。585にて加算された値が点灯率制御値556となりゲート制御ブロック553に入力されることになる。また、この点灯率制御値556はレジスタ583に入力されることにより、次フレームへと反映されることになる。

ただし、図58の方法の場合S(t)をnbitシフトさせた際にシフトさせただけデータを捨ててしまうため、精度に問題が出る。具体的にはs=8の場合n=3になるので3ビットシフトさせることになるがS(t)が7以下の数値の場合3ビットLSB側にシフトさせると0になってしまう。回避法としてはS(t)、Y(t)ともに予めnbit分最上位ビット(MSB)側にシフトさせておいて出力する時に出力データをLSB側にnbit分シフトさせて出力させる。もしくは図61に示す用に初期値Y(0)をnbit MSB側にさせてレジスタ583に収める。そしてS(t)を加えた時点のデータをレ

ジスタ 5 8 3 に収納し、出力するデータは n b i t L S B 側にシフトしてから出力する。初期値が M S B 側に n b i t シフトしていることから加えられる S ( t ) は L S B 側に n b i t シフトしているのと同じ効果が得られ、さらにレジスタ 5 8 3 に収められるデータはシフトによって捨てられるデータが存在しないため、精度が高まる。

図 4 0 に入力データが最小から最大に移った時の点灯率の変化を示す。前に述べた方式で点灯率を変化させると点灯率は曲線を描いて変化する。しかし、このとき 4 0 1 に示す領域では電源容量の限界値を超えていたため、電源を破壊する恐れがある。そこで、図 4 1 に示すように点灯率が増える時と減る時で変化を変える方法を提案する。点灯率が低い領域で点灯率を大きく変化させるとちらついて見えるが点灯率の高い領域では点灯率を大きく変えてちらつきはみえない。

これは点灯率の低い領域では画面内を締める黒表示（非表示部）の割合が大きいからである。もともと黒表示部の割合が少ない点灯率の高い領域では点灯率を大きく落としても画質に影響はない。そこで点灯率が 50 % 以上の時に入力データから算出される Y' が 50 % 未満の領域である時は前述の変化の速度を緩やかにする駆動方法を用いずに点灯率を 50 % まで減少させる。

しかし、電源の容量の限界値が 50 % より大きい場合、50 % まで下げずにその限界容量に応じた点灯率でおさえるべきである。好ましくは 75 % がよい。電源の限界容量が 50 % 未満の場合は点灯率を 50 % まで減少させてもまだ電源の限界容量を越える可能性があるが、一度に 50 % 未満の点灯率まで減少させることはちらつきの観点から好ましくない。

この方法を用いても、点灯率は入力データを判断してから変化するものなので 1 フレーム間は電源の容量の限界値を超える場合がある。例えば、図 4 2 に示すように入力データ = 有機 E L パネルの映像の輝度データとすると、しばらくの間黒表示が続くと入力データが小さいことから点灯率は最大になる。そこで突然全面白表示になるとそのフレーム間は最大点灯率のまま全面白表示になることになる。このとき、有機 E L パネルに流れる電流量は 4 2 1 に示す領域にあり、電源の限界容量を越えている。

この現象を回避するには二通りの方法がある。一つは回路内にフレームメモリを有することである。フレームメモリ内に一旦画像データを収め、その後表示すると言う構成にすると白表示をする前に点灯率を落とすことができる。しかし、回路内にフレームメモリを有すると回路規模はかなり大きくなると言うデメリットがある。

そこでフレームメモリを使わずにこの現象を回避する方法を提案する。図 4 3 に示すようにゲートドライバ 1 2 に入力するゲート信号線 4 3 1 に信号線 4 3 2 を加え、二つの信号線を A N D で論理演算する。これにより信号線 4 3 2 が H I のときはゲート信号線 4 3 1 に応じて有機 E L パネルのトランジスタ 1 1 d が O N / O F F し、信号線 4 3 2 が L O W のときはゲート信号線 4 3 1 にかかる有機 E L パネルのトランジスタ 1 1 d が O F F する。

もちろん、A N D 以外で論理演算を行い、二つの信号線の組み合わせを変えて問題はない。ここでは A N D で論理演算を行い、ゲート信号線 1 7 が L O W のとき、有機 E L パネルのトランジスタ 1 1 d が O F F する場合について説明する。まず、点灯率から入力データの限界値を計算する。仮に点灯率が 100 % の状況で電源の容量の限界値が 50 % の場合、入力データが 50 % の時点で限界となる。点灯率が 70 % の状況で電源の限界容量が 50 % のときは入力データが 71 % の時点で限界になる。入力データがその限界値に達した時点で信号線 4 3 2 を L O W に落とす。

すると、ゲート信号線 1 7 は L O W となり有機 E L パネルのトランジスタ 1 1 d が O F F する。この場合、表示領域の変化について図 4 4 に示す。4 4 1 の時点で限界値に達したとすると信号線 4 3 2 が L O W になり、1 ライン目のトランジスタ 1 1 d を操作しているゲート信号線 1 7 a ( 1 ) が L O W になる。これにより 1 ライン目が非点灯状態になり、このラインは次に 1 7 a ( 1 ) が H I になるまで非点灯状態が続く。1 ライン目が非点灯状態になった後 1 H 每に 1 7 b ( 2 )、1 7 b ( 3 ) …… と順番に L O W になっていく、2 ライン目、3 ライン目…… と順番に非点灯状態になって行く。この様子を図で示す。

すと 441, 442, 443 の順番になり、ラインごとの点灯時間は変わらない。よって 1 フレームの途中でこのような処理を行っても画像には影響がでない。この方法によりフレームメモリを使わずに電源の限界容量を超えないように電流量を抑制することができた。

本発明搭載のディスプレイは図 19 に示すように 1 フレーム間に点灯させる表示領域によって明るさを調整することが出来る。図 13 に示すように画像表示領域の水平走査線数を S とし、1 フレーム間に点灯する表示領域を N とすると表示領域の明るさは  $N / S$  となる。この方法による表示領域の明るさの調整は先にも記載したようにゲートドライバ回路 12 のシフトレジスタ回路 61 などの制御により、容易に実現できる。

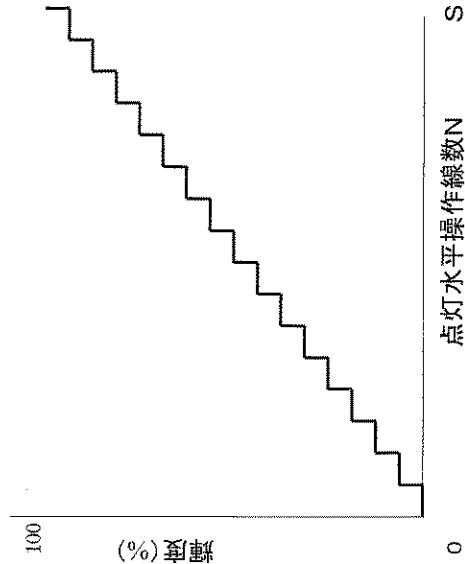

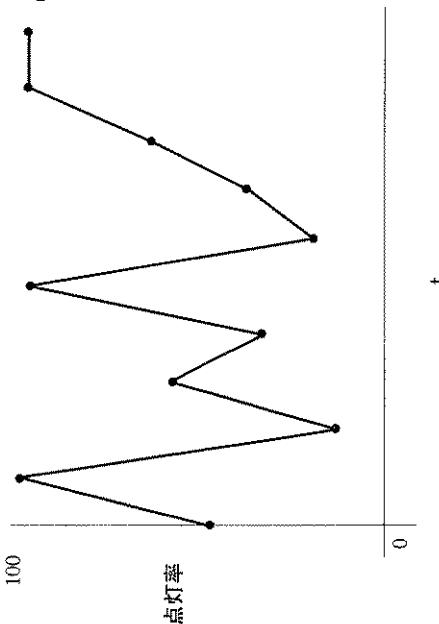

しかし、この方法では表示領域の明るさの調整は S 段階でしか調整できない。点灯する表示領域の N を変化させた際の表示領域の明るさの変化を図 31 に示す。点灯走査線数 N の変化で明るさを調整するため、明るさの変化は図のように階段状になる。明るさの調整幅が小さい場合は問題が無いが、明るさの調整の幅が大きい場合、この調整方法では N を変化させた際の明るさの変化が大きくなり、滑らかに明るさを変化させると言うことが難しくなる。

そこで図 6 に示すようにゲートドライバ 12 内に二本の信号線 62a、62b を配置する。この二本の信号線 62a、62b はシフトレジスタに接続されているゲート制御用信号線 64 と OR 回路 65 に接続される。OR 回路 65 の出力は出力バッファ 63 に接続された後、ゲート信号線 17 に出力される。図 28 に示すようにゲート信号線 17 は信号線 62 と 64 がともに LOW のときのみ、LOW を出力し、どちらかが HI の場合は HI を出力する。

これによりトランジスタ 11b、11d が ON 状態（ゲート信号線 17 が LOW 出力）の時に信号線 62 を HI 出力にすることによりゲート信号線 17 を HI 出力にすることができる、トランジスタ 11b、11d を OFF にすることができる。尚、本発明は信号線と OR 回路の組み合わせに限定するものではない。信号線 62 を変化させることによりゲート信号線 17 を変化させるもので、OR 回路の代わりに AND 回路、NAND 回路、NOT 回路を用いることも可能である。

そして、図 32 に示すように信号線 62b の HI 出力期間を調整することにより EL 素子 15 の発光時間を調整する。一つの EL 素子 15 に注目した場合、点灯走査線数が N のとき、1 フレーム間に N 水平走査期間 (H) 点灯する。この時 1 水平期間 (1H) 内の信号線 62b の HI 出力期間を M ( $\mu$ ) とすると、1 フレーム間の点灯時間は  $M \times N$  ( $\mu$ ) 減少する。図 33 にこの時の明るさの変化について示す。 $N = N'$  と  $N = N' - 1$  ( $1 - N'$  / S) の間の輝度は傾きが  $-M \times N'$  で表現される。これにより、図 31 の階段状の明るさの変化はリニアな変化をすることが可能となる。

この図では信号線 62b は 1H に一回 HI 出力になるように書いてあるが、本発明はこれに限るものではない。数 H 期間に一度信号線 62b が HI になるような処理方法も考えられ、また HI 出力の期間は 1H 内のいかなる場所に配置しても問題はない。また、数フレーム間で明るさを調整することも可能である。例を挙げると 2 フレームに一回信号線 62b を HI 出力にすると HI 出力の期間 M は見た目的には 1 / 2 になる。ただし、このような処理を行うとき特定の表示期間にのみ信号線 62b を HI 出力にすると画像表示領域に明るさのムラが出る可能性がある。

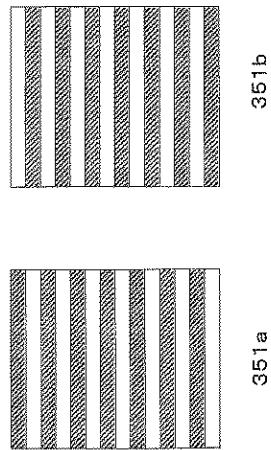

このような場合、数フレーム間にわたって処理を行うことによって明るさのムラをなくすことができる。例えば図 35 に示すように奇数ラインの点灯時に信号線 62b を HI にする表示方法 351a と偶数ラインの点灯時に信号線 62b を HI にする表示方法 351b を 1 フレームごとに切り替える方法がある。これにより見た目には表示領域の明るさのムラは無くなる。本発明では表示領域の水平走査線数が S 本あり、うち N 本が転倒している場合、 $N / S = 1 / 4$  の場合にのみ信号線 62 を操作して明るさを調整する。最初に  $N / S$  が 1 / 4 以下の時に信号線 62 を操作する利点について説明する。

先に書いたように点灯水平走査線数 N の変化で明るさを調整すると明るさの変化は階段状になるため N が変化する境目で明るさが大きく変化することになる。表示領域の明るさ

が大きい場合、人間の視覚には変化の大きさに気づくにくいが、表示領域の明るさが小さい場合気づきやすくなる。そこで本発明では表示領域の明るさが小さい場合に信号線 62 を調整することにより明るさの変化量を微調整することが可能になる。

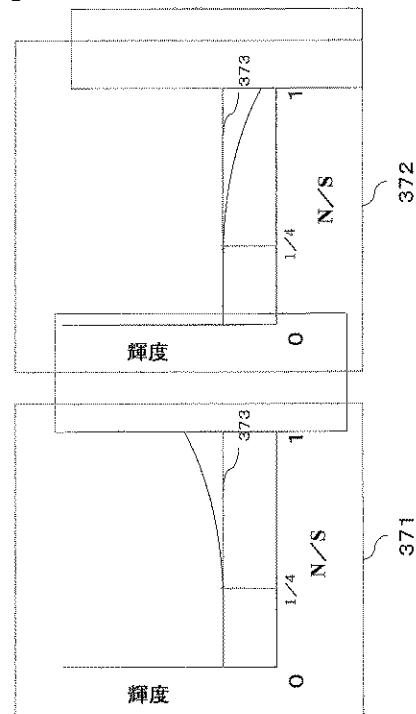

次に  $N/S$  が 1/4 以上の時の問題点について説明する。図 9 に示すようにソース信号線 18 とゲート信号線 17b の間には浮遊容量 91 が存在する。信号線 62b を H I 出力にすると  $N$  本のゲート信号線 17b が一斉に H I 出力となるため、図 36 に示すようにソース信号線 18 とゲート信号線 17b のカップリングによりソース信号線 18 が変化する。このカップリングにより蓄積容量 19 に正しい電圧を書き込むことができなくなる。特に図 37 に示すように低電流により書き込む低階調部においてはカップリングによる書き込み電圧の変化を補正することができず 371 のように書き込み電圧が高くなる場合は低階調部が目的の明るさ 373 より高くなり、372 のように書き込み電圧が低くなる場合は低階調部が目的の明るさ 373 より低くなる。

以上により、明るさの変化を微調整できる利点を持ち、且つカップリングによる書き込み電圧の変化の影響が少ない期間として  $N/S = 1/4$  が適当である。

上記の駆動方法について図 60 に回路構成を示す。上記の駆動は 601 にて行う。上記駆動法はより細かい点灯率制御値を求めるため、552c より 10bit のデータを出力し、点灯率制御値 556 を作成する。10bit のデータから点灯率制御値 556 を作成すると 1024 段階のデータが作成可能であり、8bit で点灯率制御値 556 を作成した場合の 4 倍の細かさで制御することが可能となる。しかし、点灯率は水平走査線数 S 段階でしか調整することができない。そこで S が 8bit の値とすると生成された 10bit の制御データの下位 2bit を点灯率の微調整に使用する。もしくは前述図 61 のような駆動を行う場合、出力の際に LSB 側にシフトされる nbit 分のデータを点灯率の微調整に使用しても良い。

本駆動は点灯率が  $N/S = 1/4$  の期間において行うことから 555 から 601 に点灯率制御値 556 を入力する。601 は点灯率が  $N/S = 1/4$  において駆動を行う。先に示したとおり 601 から出力される信号線 62b はゲートドライバ 12 から出力される信号線 64b と論理演算を行い、その出力がゲート信号線 17b となっている。そのため、信号線 62b の出力状況で全画素のトランジスタ 11d を操作することが可能である。駆動を行わない  $N/S = 1/4$  の区間においては信号線 64b の出力波形が 17b に反映される用に信号線 62b に出力する。

$N/S = 1/4$  の場合、601 は HD に同期して駆動する。同期するのは HD だけとは限らない。601 を駆動させるための専用の信号を設けても良い。601 は入力される微調整用信号 602 とクロック (CLK) により、指定期間トランジスタ 11d が OFF になるように信号線 62b を操作する。先に示した用に N ライン点灯している状況で 1 水平期間 (1H) 内の信号線 62b の H I 出力期間を M ( $\mu$ ) とすると、1 フレーム間の点灯時間は  $M \times N$  ( $\mu$ ) 減少する。そのため、1H の時間と 602 のデータを計算して M を算出し、62b の操作による点灯時間の減少を操作することにより、点灯率を滑らかに変化させることができる。

図 60 は図 55 に 601 を加えた形となっているが当然図 58 や図 61 などの本文に記載されたあらゆる回路構成に適用が可能である。

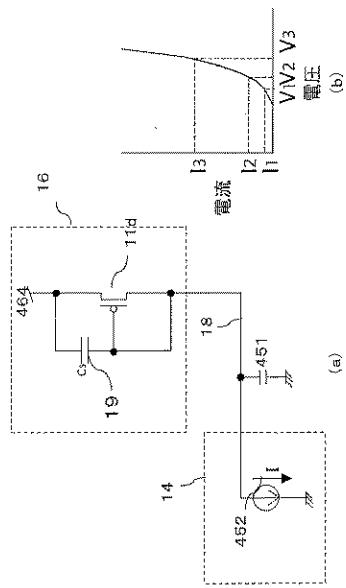

次に図 46 に示す画素構成のアクティブマトリクス型表示装置において、ソース信号線からある画素に所定電流値を書き込む場合について考える。ソースドライバ IC14 の出力段から画素までの電流経路に関係する回路を抜き出した回路は図 45(a) のようになる。

階調に応じた電流 I がソースドライバ IC14 内から、電流源 452 という形で引き込み電流として流れる。この電流はソース信号線 18 を通じて、画素 16 内部に取り込まれる。取り込まれた電流は駆動トランジスタ 11a を流れる。つまり、選択された画素 16 において EL 電源線 464 から駆動トランジスタ 11a、ソース信号線 18 を介して、ソースドライバ IC36 に電流 I が流れる。

映像信号が変化して電流源 452 の電流値が変化すると、駆動トランジスタ 11a 及び

ソース信号線 18 に流れる電流も変化する。そのときソース信号線の電圧は駆動トランジスタ 11a の電流 - 電圧特性に応じて変化する。駆動トランジスタ 11a の電流電圧特性が図 45 (b) である場合、例えば電流源 452 が流す電流値が I2 から I1 に変化したとすると、ソース信号線の電圧は V2 から V1 に変化することになる。この電圧の変化は電流源 452 の電流によっておこる。

ソース信号線 18 には浮遊容量 451 が存在する。V2 から V1 までソース信号線電圧を変化させるにはこの浮遊容量の電荷を引き抜く必要がある。この引き抜きにかかる時間

T は、 $Q$  (浮遊容量の電荷) =  $I$  (ソース信号線に流れる電流) ×  $T$  =  $C$  (浮遊容量値) ×  $V$  となる。ここで  $V$  (白表示時から黒表示時間の信号線振幅) は 5 [V]、 $C = 10 \text{ pF}$ 、 $I = 10 \text{ nA}$  とすると、 $T = 50 \text{ ミリ秒}$  必要となる。これは  $QCIF +$  サイズ (画素数  $176 \times 220$ ) を  $60 \text{ Hz}$  のフレーム周波数で駆動させるとの、1 水平走査期間 ( $75 \mu\text{s}$ ) よりもながくなるため、仮に、白表示画素の下の画素に黒表示を行おうとすると、ソース信号線電流が変化途中に画素に電流を書き込むためのスイッチトランジスタ 11a、11b が閉じてしまうため、中間調が画素にメモリーされることにより白と黒の中間の輝度で画素が光ってしまうことを意味する。

10

階調が低くなるほど I の値が小さくなるため、浮遊容量 451 の電荷を引き抜きにくくなるため、所定輝度に変化する前の信号が画素内部に書き込まれてしまうという問題は、低階調表示ほど顕著に現れる。極端にいうと黒表示時は電流源 452 の電流は 0 であり、電流を流さずに浮遊容量 451 の電荷を引き抜くことは不可能である。

そこでこの問題を解決するために、図 47 に示すようなソース信号線 18 に通常の n 倍の電流を通常の  $1/n$  時間印加する n 倍パルス駆動を使用する。この駆動法により通常よりも高い電流を書けることによりコンデンサへの書きこみ時間を短縮できる。ソース信号線に n 倍の電流を流すと有機 EL 素子にも n 倍の電流が流れるため、ゲート制御信号を 483a となるように出力し TFT11d の導通時間を  $1/n$  にすることにより、有機 EL 素子 15 に  $1/n$  の期間だけ電流を印加し平均印加電流は変化しないようとする。

20

ソース信号線 18 の電流値変化に要する時間 t は浮遊容量 451 の大きさを C、ソース信号線 18 の電圧を V、ソース信号線 18 に流れる電流を I とすると  $t = C \cdot V / I$  であるため電流値を 10 倍大きくできることは電流値変化に要する時間が 10 分の 1 近くまで短くできる。またはソース線の浮遊容量 451 が 10 倍になっても所定の電流値に変化できるということを示す。従って、短い水平走査期間内に所定の電流値を書きこむためには電流値を増加させることができることが有効である。

30

入力電流を 10 倍にすると出力電流も 10 倍となり、EL の輝度が 10 倍となるため所定の輝度を得るために、図 1 の TFT11d の導通期間を従来の 10 分の 1 とし、点灯率を 10 分の 1 とすることで、所定輝度を表示するようにした。

つまり、ソース信号線 18 の浮遊容量 (寄生容量) 451 の充放電を十分に行い、所定の電流値を画素の TFT11a にプログラムを行うためには、ソース信号線 18 から比較的大きな電流を出力する必要がある。しかし、このように大きな電流をソース信号線 18 に流すとこの電流値が画素にプログラムされてしまい、所定の電流に対し大きな電流が EL 素子 15 に流れる。たとえば、10 倍の電流でプログラムすれば、当然、10 倍の電流が EL 素子 15 に流れ、EL 素子 15 は 10 倍の輝度で発光する。所定の発光輝度にするためには、EL 素子 15 に流れる時間を  $1/10$  にすればよい。このように駆動することにより、ソース信号線 18 の寄生容量を十分に充放電できるし、所定の発光輝度を得ることができる。

40

なお、10 倍の電流値を画素の TFT11a (正確にはコンデンサ 19 の端子電圧を設定している) に書き込み、EL 素子 15 のオン時間を  $1/10$  にするとしたがこれは一例である。場合によっては、10 倍の電流値を画素の TFT11a に書き込み、EL 素子 15 のオン時間を  $1/5$  にしてもよい。逆に 10 倍の電流値を画素の TFT11a に書き込み、EL 素子 15 のオン時間を 2 倍にする場合もある。

この N 倍駆動を使用するとソース信号線に流れる電流量を増やすことができるため、所定輝度に変化する前の信号が画素内部に書き込まれてしまうという問題を解決することができる

50

できる。たとえば、ゲート信号線 17 b は従来導通期間が 1 F (電流プログラム時間を 0 とした時、通常プログラム時間は 1 H であり、EL 表示装置の画素行数は少なくとも 100 行以上であるので、1 F としても誤差は 1 % 以下である) とし、N = 10 とするとすれば、最も変化に時間がかかる階調 0 から階調 1 へもソース容量が 20 pF 程度であれば 7.5 μs 程度で変化できる。これは、2 型程度の EL 表示装置であればフレーム周波数が 60 Hz で駆動できることを示している。

更に大型の表示装置で浮遊容量 (ソース容量) 451 が大きくなる場合はソース電流を 10 倍以上にしてやればよい。一般にソース電流値を N 倍にした場合、ゲート信号線 17 b (TFT 11d) の導通期間を 1 F / N とすればよい。これによりテレビ、モニター用の表示装置などにも適用が可能である。

しかし、N 倍駆動は、同じ明るさで表示しても画素に瞬間に流れる電流が N 倍になるため、有機 EL 素子に大きな負担がかかる。

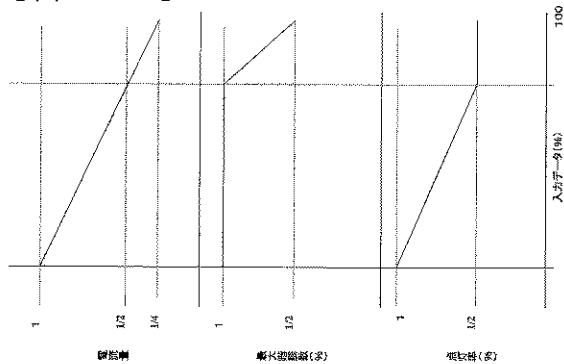

そこで、本発明の入力データに応じて点灯率を制御する駆動方法を用いて表示画像の低輝度部において点灯率とともにソース信号線 18 に流す電流量を制御して図 49 に示すような低輝度部でのみ N 倍パルス駆動をすることを提案する。この駆動方法のメリットは前述の電流量不足の問題は高輝度部では起こり難い。そのため、有機 EL 素子に負担のかかる N 倍パルス駆動は高輝度部では行わず、全体的に画素に流れる電流が少ない低輝度部においてのみ N 倍パルス駆動を行うことにより、有機 EL 素子の負担を軽くしつつ、前述のソース信号線の浮遊容量 451 のために所定輝度に変化する前の信号が画素内部に書き込まれてしまうという問題を解決できることにある。

具体的には低輝度部では点灯率を 1 / N1 にして、それに応じて総電流量が目的の値になるように ソース信号線に流す電流 N2 倍に増やす。この際、N1 = N2 である必要はない。N1 = N2 の場合もあるし、N1 > N2 の場合ももちろんある。ただし、本駆動の目的はソース信号線 18 に流す電流量を増やすことにあるので N2 > 1 である。そして点灯率は必ずしも下げなければいけないと言う訳ではない。求める入力データに対する有機 EL パネルに流れる電流量の関係によっては点灯率を変えないことや、点灯率の上昇を抑えると言う処理をすることもある。

仮に入力データと点灯率の関係を図 50 のように入力データが 30 % 未満の領域では点灯率を最大にし、30 % 以上の領域では有機 EL パネルに流れる電流量がバッテリー 241 の限界容量を超えないように点灯率を下げて行くような駆動を考える。そして前述の駆動時ににおいて入力データが 30 % 未満の領域において N 倍パルス駆動を行うとする。ただし、この N 倍パルスと、通常駆動の切り替え点は 30 % に固定するものではない。しかし、寿命を考えると 30 % 以下の領域に N 倍パルスとの切り替え点を持つことが好ましい。

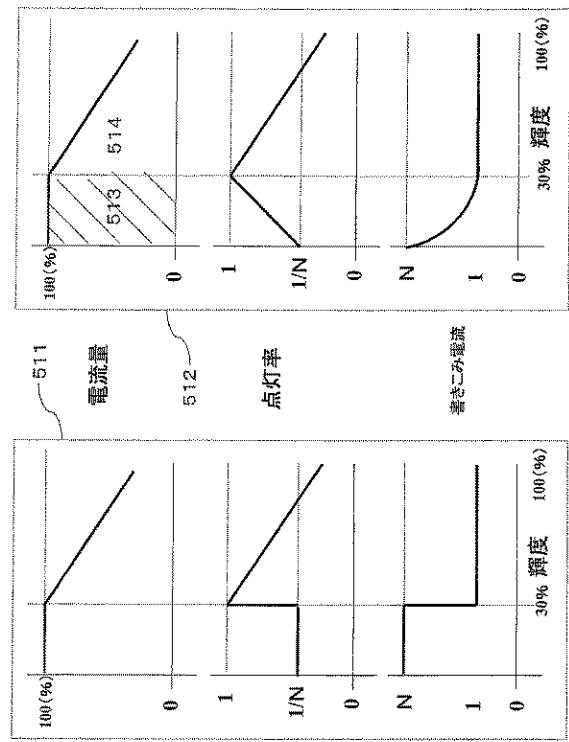

ここで N 倍パルス駆動のやり方について 2 通り提案する。一つ目に 511 のように入力データが 30 % 未満の領域では点灯率を 1 / N にし、ソース信号線に流す電流量を N 倍にする方法がある。二つ目は 512 のように入力データが 30 % の状態から 0 % にかけて徐々に点灯率を下げ、逆にソース信号線に流す電流量を徐々に上げて行く方法がある。ともに有機 EL パネルが流す電流量は図 50 の関係になるが一つ目の方法は入力データが 30 % 未満の状況では点灯率も電流値も固定で良いため、回路作成が非常に容易であると言うメリットがある。しかし、入力データが 30 % の境目で点灯率と電流値が同時に大きく変わるので変わる瞬間にちらつきが見えてしまうと言う問題も有している。

二つ目の方法は入力データが 30 % 未満の状況では点灯率と電流値を同時に操作しなければならないので回路作成が複雑になると言うデメリットがある。しかし、この方法だと点灯率と電流値は緩やかに変化させることが可能であるのでちらつき等の問題点がない。さらに前に示したように所定輝度に変化する前の信号が画素内部に書き込まれてしまうという問題はソース信号線に流す電流量が少なければ少ないと顕著に出るものなので入力データが減少に応じてソース信号線に流す電流量をふやすと言う方法は理にかなっているし、有機 EL 素子に対する負担も小さくなる。この方法により、極力有機 EL 素子への負担を小さくし、かつ所定輝度に変化する前の信号が画素内部に書き込まれてしまうという問題を解決する駆動方法を実現した。

図 6 4 にて本駆動の回路構成について説明する。552で加算された映像データは基準電流制御モジュール 641 に入力される。641 では入力されたデータに応じて、ソース信号線 18 に流れる電流量を増減させるようにソースドライバー 14 を制御する。

図 6 2・図 6 3 にてソースドライバー 14 について説明する。図 6 3 に示す用にソースドライバー 14 は基準電流 629 に応じてソース信号線 18 に電流を流す。さらに基準電流 629 について説明すると図 6 2 において基準電流 629 は節点 620 の電位と、抵抗素子 621 の抵抗値により決まる。さらに節点 620 の電位は電圧調節部 625 により、制御データ信号線 628 により変化させることが可能である。つまり制御データ信号線 628 を 641 により制御すれば、抵抗素子 621 の抵抗値によって決められた範囲内で変化させることが可能となる。

上記の駆動法の適用例として図 6 5 にて図 6 1 の回路構成に上記の駆動法を付加した回路構成を示す。入力データと点灯率、基準電流値の関係が 512 のようになる場合、基準電流を変化させる領域を 513 と変化させない領域 514 で区別する。入力データが 513 の領域にある場合図 6 5 の  $x\_f1ag$  が 1 になり、514 の領域の場合、0 になるように構成する。また、同じようにそのフレームでの点灯率  $Y(t)$  が 513 にある場合は  $y\_f1ag$  が 1 になり、514 の場合は 0 になる。すなわち、 $y\_f1ag$  が 1 の場合は基準電流を変化させている領域となり、651 にて  $y\_f1ag$  が 1 のときは 556 のデータに応じて基準電流の制御データ信号線 628 を変化させる。650 内は  $y\_f1ag$  と  $x\_f1ag$  の組み合わせで構成されている。 $y\_f1ag$  と  $x\_f1ag$  がともに 0 のときはともに 514 の領域にいるため、 $Y'(t)$  は 555 と同様のシーケンスで設計すれば良い。同じ用に  $y\_f1ag$  と  $x\_f1ag$  がともに 1 のときは 513 の領域内で動くため、基準電流は変化するが点灯率の計算に関しては 555 と同様のシーケンスでよい。 $y\_f1ag$  と  $x\_f1ag$  が (0, 1) もしくは (1, 0) のときは 513 の領域から 514 の領域に移ろうとしている状態（もしくは逆）である。513 の領域では点灯率と基準電流値がともに変化するが、かけあわせると常に一定になる用に動いている。つまりは 514 における点灯率を最大の状況（D\_MAX と定義する）と同じものと言って良い。そこで  $y\_f1ag$  が 0 でと  $x\_f1ag$  が 1 の状態、すなわち 514 の領域から 513 の領域に移動する時は  $Y'(t)$  を D\_MAX とする。逆に  $y\_f1ag$  が 1 でと  $x\_f1ag$  が 0 の状態、すなわち 513 の領域から 514 の領域に移動する時は D\_MAX から 555 で導かれる  $Y'(t)$  に向けて移動すると考えると  $Y(t)$  を保持しているレジスタ 583 に D\_MAX を入力し、 $Y'(t)$  を 555 と同様のシーケンスで設計することにより違和感のない点灯率の変化を実現することができる。

また、図 30 のような点灯率のカーブを描く方法と併用する回路構成について説明する。この駆動方法は図 30 のような点灯率のカーブを描く方法と併用することにより、回路規模を小さくすることが可能になる。

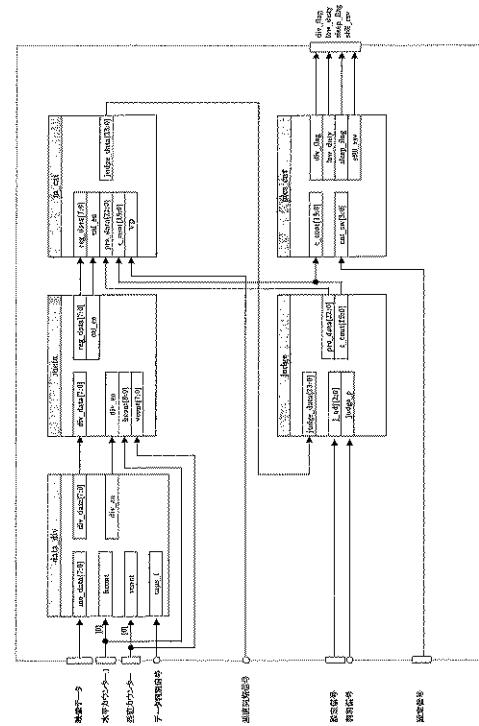

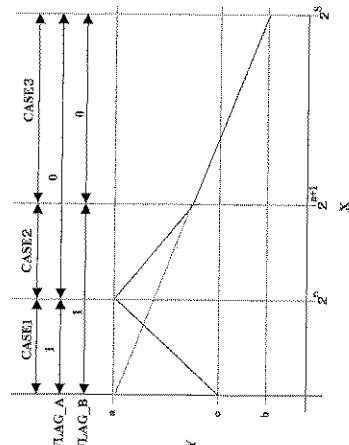

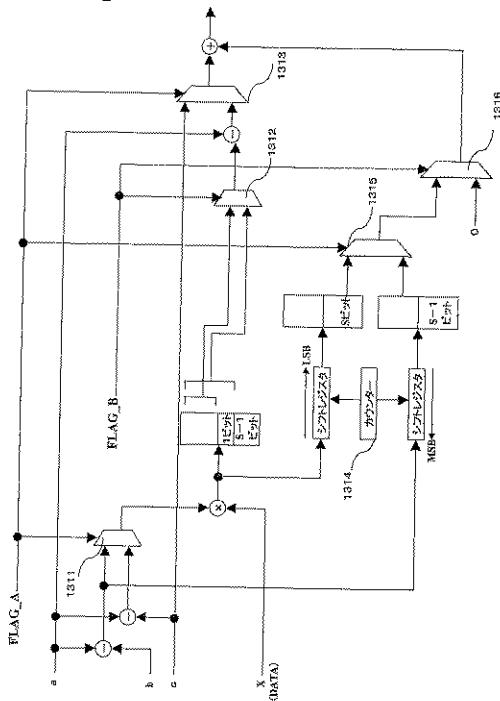

図 130 に示すように、入力データを 2 の S 乗で分割し、2 の n 乗の入力データまで N 倍電流値、1 / N 点灯率駆動を行うとする。最大の点灯率の値を a、通常の点灯率抑制駆動の最小点灯値を b、N 倍電流値、1 / N 点灯率駆動の最小点灯率の値を c とし、また入力データが 0、つまり最小値から 2 の n 乗までを CASE 1、2 の n 乗から 2 の (n + 1) 乗までを CASE 2、2 の (n + 1) 乗から 2 の S 乗、つまり最大値までを CASE 3 とする。また、CASE 1 のときだけ 1 になる FLAG\_A と CASE 3 のときだけ 0 になる FLAG\_B を用意する。これにより CASE 1 は (FLAG\_A, FLAG\_B) = (1, 1)、CASE 2 は (FLAG\_A, FLAG\_B) = (0, 1)、CASE 3 は (FLAG\_A, FLAG\_B) = (0, 0) と表すことができる。続いて、図 131 にてこの駆動を実現する回路構成を示す。FLAG\_A と FLAG\_B の値の判別は入力データをシフトレジスタによりシフトさせて比較器に入力すればわかる。n ビットシフトさせたデータが 0 だったら FLAG\_A は 1、それ以外は 0、さらに 1 ビット（計 n + 1 ビット）シフトさせて 0 だった場合、FLAG\_B は 1、それ以外は 0 である。尚、FLAG\_A と FLAG\_B の 0 と 1 は逆でもかまわない。この二つのフラグを利用して、CASE 1 から 3 を満たす回路を作成する。

3つの式は点灯率をY、データをX（最大2のS乗）とすると次のように表される。

$$\text{CASE 1} \cdots Y = ((a - c) / 2^n) \cdot X + c$$

$$\text{CASE 2} \cdots Y = a - 2 \cdot ((a - b) / 2^s) \cdot X + 2^n \cdot ((a - b) / 2^{(s-1)})$$

$$\text{CASE 3} \cdots Y = a - ((a - b) / 2^s) \cdot X$$

この3つを実現するにはそれぞれの場合において演算を行えばよいが、回路構成において演算処理は回路規模が大きくなるため、できるだけ演算を行う回数を減らすことが好ましい。特に乗算処理は回路規模に大きな負担をかける。そのため、セレクター回路とシフトレジスタを多用することにより負荷の少ない回路構成を実現する。

まずa - b、a - cをそれぞれ行う。その値をセレクター1311にかける。上の式からCASE 1の場合のみa - cを行うのでFLAG\_Aが1のときa - cを出力し、0のときはa - bを出力する。セレクター1311の出力値と入力データXの演算を行う。これにより、(a - b) · Xの値と(a - c) · Xの値が完成する。CASE 2とCASE 3では傾きが2倍であるため、セレクター1311の出力値をそのままのものと2倍したものをFLAG\_Bの値によりセレクター13212で選択する。この際に2倍する方法としてはセレクター1311の出力値をMSB側に1ビットシフトする方法と、シフトレジスタを使用しなくても二つとも $2^s$ で割っているのでセレクター1311の出力値の下位Sビットを削ったものとS - 1ビット削ったものをセレクター1312にかけねばよい。aとセレクター1312の出力の減算結果はCASE 3のYの値と一致する。CASE 2はこの演算結果に $2^n \cdot ((a - b) / 2^{(s-1)})$ を加えたものである。また、CASE 1はcに((a - c) / 2^n) · Xを加えたものと考えることができるのでこの出力値とcの値をFLAG\_Aで選択されるセレクター1313にかけることにより、あとはセレクター1313に加える値をセレクトすることで点灯率を求めることができる。 $2^n \cdot ((a - b) / 2^{(s-1)})$ は((a - b) / 2<sup>(s-1)</sup>)をnビットMSB側にシフトさせたものである。また((a - c) / 2^n) · Xは(a - c) · X、即ちセレクター1311の出力と入力データXとの演算値をnビットLSB側にシフトさせたものである。ともにnビットシフトさせるのでカウンター1314一つでシフトを完了させることができる。 $2^n \cdot ((a - b) / 2^{(s-1)})$ はa - bの値をnビットMSB側にシフトさせた後下位S - 1ビットをけずって出力する。この二つの出力をセレクター1315にかける。このセレクターはCASE 1とCASE 2のセレクターであるのでFLAG\_Aを使用する。CASE 3の場合はこの出力を足す必要がないため、FLAG\_Bでセレクター1316にかけ、CASE 3の場合は0を出力するようにする。これにより、最小限の演算とセレクターによりすべてのCASEの点灯率の算出が可能になる。

この方式はCASE 1から3を別々に演算するのに比べると回路規模は半分以下になり、この仕組みを実現するのに非常に効果が高い。

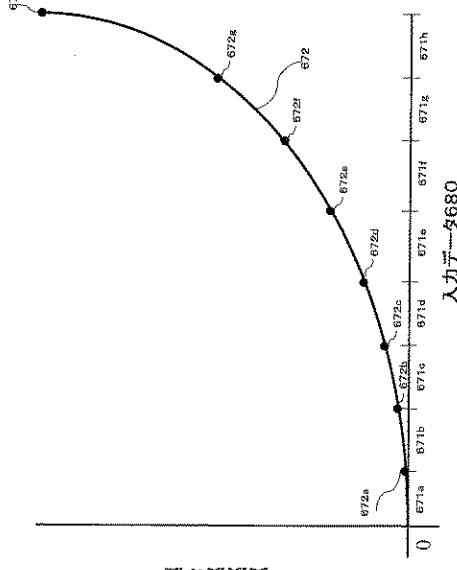

一般に画像はガンマカーブを用いている。ガンマカーブとは低階調部を抑えることにより、全体的にコントラスト感がでるような画像処理である。しかし、ガンマカーブにより低階調部が抑えられると、低階調部が多い画像では黒く潰れてしまい奥行き感のない画像になってしまふ。とは言え、ガンマカーブを使用しないと高階調部が多い画像ではコントラスト感が出ない画像になってしまふ。

本発明の点灯率制御駆動を行う場合、表示領域に低階調表示が多い場合は点灯率を上げることにより、全体が明るくなる。この時、ガンマカーブにより低階調部をつぶしていると表示される画素と表示されない画素の明るさの差が大きくなるため、より奥行きのない画像になる可能性がある。また、表示領域に高階調表示が多い場合は点灯率を下げるため、表示画素と非表示画素の明るさの差が小さくなる。そのため、ガンマカーブで画像をつぶさないとコントラスト感のない画像になってしまふ。

そこで本発明の電流量制御駆動と連動させて表示領域の変化により、ガンマカーブを制御する駆動方法を提案する。

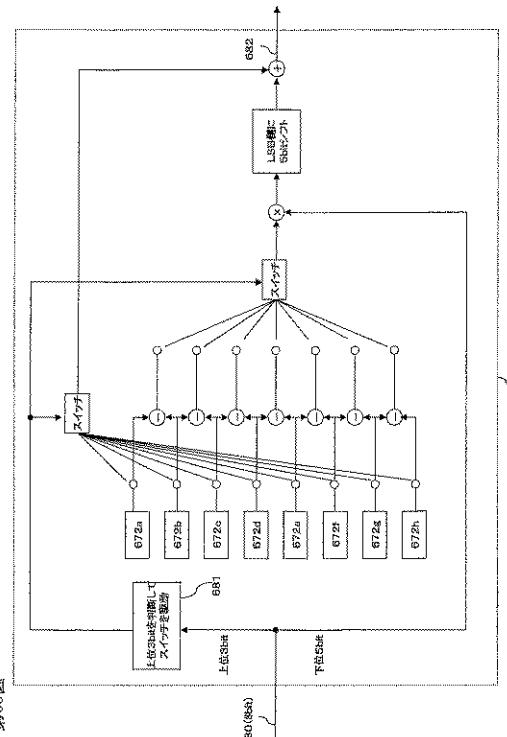

図67・図68にて カーブを実現する回路構成について説明する。入力される色データをグラフの横軸にとり2のn乗で分割する。図67では8分割し、それぞれを671a

10

20

30

40

50

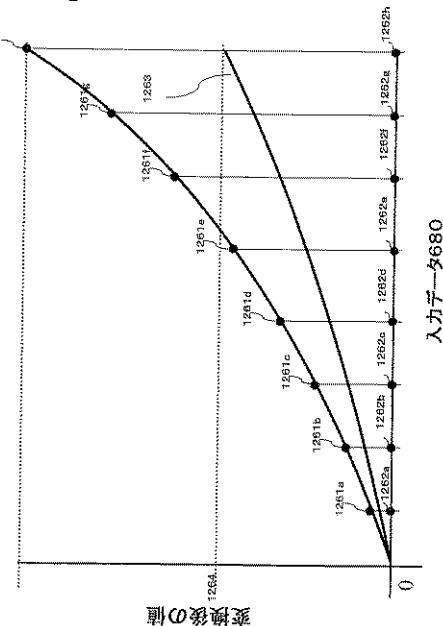

、 6 7 1 b . . . 6 7 1 f としている。そして、 6 7 1 a ~ f の境目に対応する カーブの値 6 7 2 a ~ f を入力する。図 6 8 では入力される色データは 8 b i t と仮定して処理を行っている。最初に 6 8 1 にて入力データ 6 8 0 の上位 3 b i t を判定する。ガンマカーブは 8 分割 (2 の 3 乗分割) されているので 6 8 0 の上位 3 b i t の値により、入力データ 6 8 0 は 6 7 1 a ~ f のどの領域にいるか判断することができる。仮に 6 7 1 c の領域に 6 8 0 がいるとする。6 7 1 c の領域はガンマカーブの値が最低が 6 7 2 b 、最高が 6 7 2 c であり、 2 5 6 段階の入力データを 8 分割しているので 1 区間は 3 2 段階に分けられる。よって 6 7 1 c のグラフの傾きは ( 6 7 2 b - 6 7 2 c ) / 3 2 となる。入力データが 6 7 1 c の領域のどの場所にいるかは 6 8 0 の下位 5 b i t の値と等しいので ( 6 8 0 の下位 5 b i t ) × ( 6 7 2 b - 6 7 2 c ) の値を L S B 側に 5 b i t シフト ( 3 2 での除算) したものが 6 7 1 c 内での増加分となる。すなわち、上記に 6 7 2 b の値を加えたものが入力データ 6 8 0 がガンマカーブにより変換された出力値 6 8 2 となる。

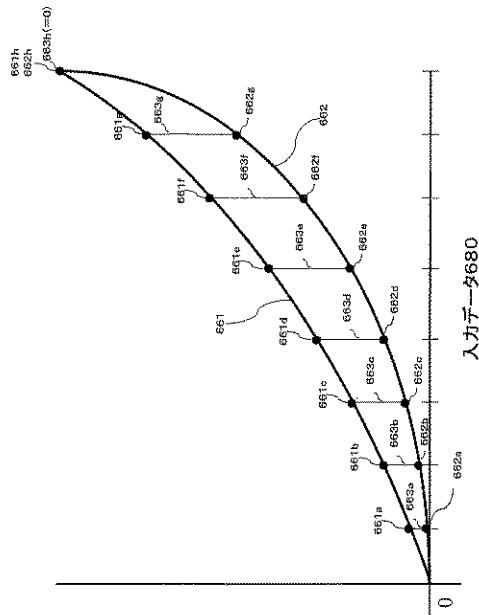

続いて図 6 6 ・ 図 6 9 にて 5 5 2 内で作られた有機 E L パネルの表示状態などを示したデータ 5 5 7 を用いて、表示状態により カーブを調整する回路構成について説明する。まず 6 9 1 にて 2 種類の カーブを作成するため、 6 6 1 a ~ 6 6 1 h 、 6 6 2 a ~ 6 6 2 h の値を決める。ここでは 6 6 1 6 6 2 が成り立っているものとする。 カーブは使用するデバイスによっても違うのでこの値は外部から設定できるようにするべきである。そして 6 6 1 a ~ f と 6 6 2 a ~ f の各差 6 6 3 a ~ f をとる。その後、 6 9 1 から 6 9 2 に対して 6 6 1 a ~ f と 6 6 3 a ~ f を出力する。 6 9 2 には 5 5 2 から出力された表示状態のデータである 5 5 7 も入力される。 6 9 2 では 5 5 7 に応じて カーブの値を決める。 5 5 7 が大きいほど、画像は高階調が多く、ガンマカーブをきつくして画像にメリハリをつける必要があり、 5 5 7 が小さいほど画像は低階調部が多く、ガンマカーブを緩くして奥行きのある映像を作る必要がある。 5 5 7 は 0 ~ 2 5 5 のデータであることから ( 6 6 1 a ~ f のデータ ) - { ( 6 6 3 a ~ f のデータ ) × ( 5 5 7 のデータ / 2 5 5 ) } と言う演算により 5 5 7 に応じたガンマデータ 6 9 3 a ~ f が作成される。このガンマデータ 6 9 3 a ~ f を 6 8 3 に入力する。 6 8 3 は図 6 8 で説明したように、入力される色データ 6 8 0 から 6 7 2 a ~ f のデータに基づいて作られたガンマカーブにより変換されたデータが出力されるモジュールである。 6 7 2 a ~ f に 6 9 3 a ~ f が入力され、入力される R G B のデータ 6 9 5 が 6 9 3 a ~ f によって作られるガンマカーブにより変換され出力 6 9 6 としてソースドライバー 1 4 に入力される。

上記の説明では緩やかなガンマカーブ 6 6 1 から 5 5 7 に対応したデータを減算すると言う方式をとっているが、当然のことながらきついガンマカーブ 6 6 2 から 5 5 7 に対応したデータを加算すると言う方法をとっても良い。

また、ガンマカーブは 2 種類からつくるのに限るものではない。複数のガンマカーブから表示映像に合わせたガンマカーブを作る構造を用いてもよい。

ガンマカーブの変化も点灯率の変化と同様、頻繁に変化させるとちらつきが見えると言う問題を有している。そこで点灯率の変化を 6 1 2 により遅延させたのと同様に 5 5 7 も 6 1 2 により変化の速度を遅延させてやることは非常に有効である。

図では R G B を 6 9 4 で同様に処理しているが、 R G B を別別にやることにより、 R G B 個別のガンマカーブを作ることも可能である。

以上の駆動により、表示領域に低階調部が多い場合はガンマカーブを緩くすることにより奥行き感を出し、高階調部が多い場合はガンマカーブをきつくすることにより、コントラスト感をだすような駆動を行うことができる。

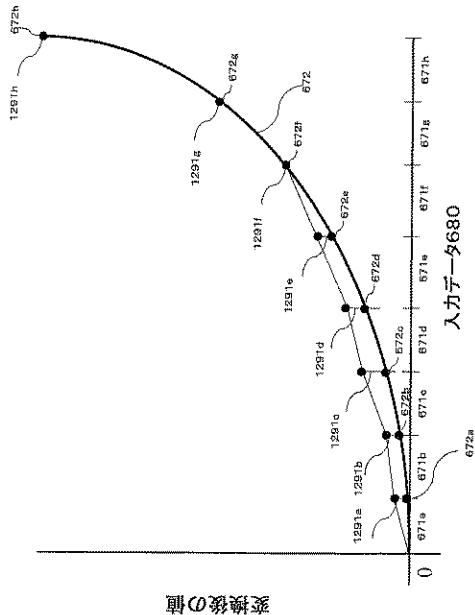

また、 R G B を独立してガンマカーブを作成する手段として図 1 2 9 に示すように作成されたガンマカーブ 6 7 2 に R G B それぞれに補正值 1 2 9 1 a ~ 1 2 9 1 f を加えることによって R G B を別々にガンマカーブを作ることが可能となる。この方式は複雑なガンマカーブの演算は 1 種類で済むため、回路規模を大きくせずに実現が可能となる。

有機 E L 素子 1 5 は劣化するため、固定パターンを表示し続けると一部の画素の有機 E L 素子 1 5 のみが劣化して、表示していたパターンが焼きつく場合がある。焼きつきを防ぐためには表示している映像が静止画かどうか判別してやる必要がある。

10

20

30

40

50

静止画を判別する方法としてはまず、フレームメモリを内蔵し、1F期間のデータを全てフレームメモリに記憶させることで次フレームとの映像データの正否を判断し、静止画かどうか判断させる方法がある。この方法は確実に映像データの違いを認識できると言う利点を有しているがフレームメモリを内蔵しなくてはならないため、回路規模が非常に大きくなってしまう。

そこで図71に示すようにフレームメモリを使わずに静止画かどうか判断する方法について提案する。判断する方法として、1F期間の全画素のデータを加算した合計値で判断する方法がある。映像がかわらない場合、映像データも変わらないのでデータの総和量はかわらない。そのため、1F内の全データを加算し、比較することで静止画かどうか検出することができる。この方法だと全映像データをそのまま記憶させるよりも非常に少ない回路規模で実現できる。しかし、データの総和量をとる方法は特定のパターンにおいて効果をなさない場合がある。例えば、黒い画面の中を白いブロックが飛びまわるような画像の場合、白いブロックの位置は違ってもデータの総和量としては同じのため、静止画として誤認識してしまうことになる。そこで本発明では数個の画素を組み合わせてデータを作ることにより、他の画素のデータとの相関関係を持たせる方法を提案する。

まず、711はデータイネーブル(DE)とクロック(CLK)によって動作する。これは常にデータが来ているわけではなく、必要なデータでのみ判定を行うためのものである。

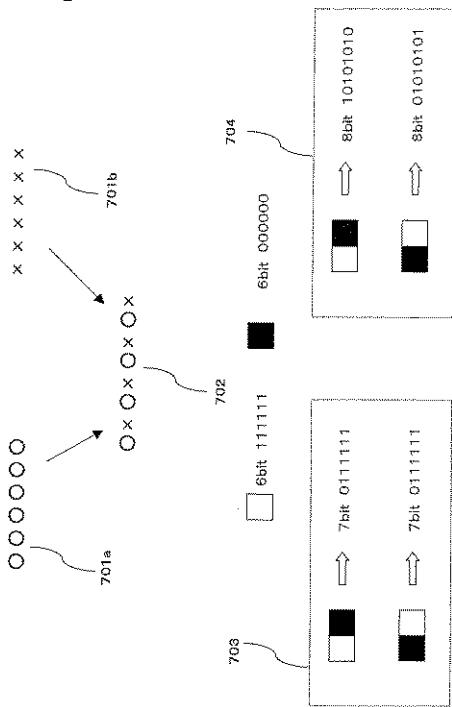

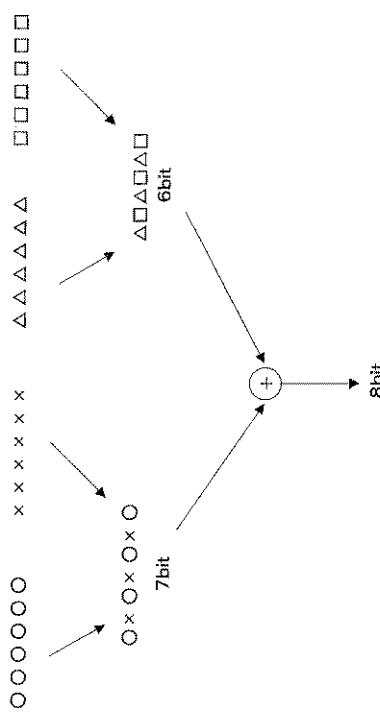

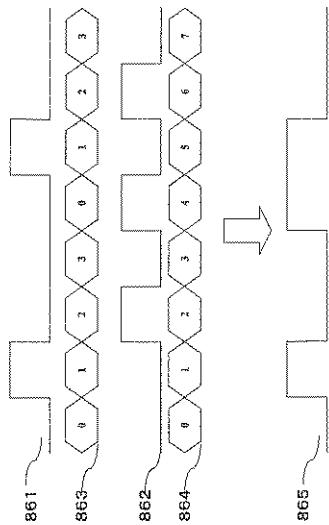

図70に示すように6bitの映像データ701a, 701bが入力される場合、8bitのレジスタ702を用意し、奇数bitと偶数bitにそれぞれの映像データの上位4bitを入力し、一つのレジスタを構成する。この時、レジスタ702は8bitである必要はない。回路規模は大きくなるが12bitのレジスタを持っても良いし、精度が落ちて良いならば8bit未満のレジスタ構成にしても良い。また、2つ映像データの比率を変えても良い。8bitのレジスタに入力する場合、701aから5bit、701bから3bitと言う割合にしても良い。更にレジスタに入力するデータは必ずしも上位から取る必要はない。下位4bitを選択して入力しても良いし、カウンター713の値に応じて取る場所を変えることも有効な手段である。図70に示すように2画素で見た場合、703の場合はどちらのパターンもデータは同じになるが、704の場合はデータが違うようになるため、静止画として誤認識しない。図70と図71は駆動方法を簡略化して説明するために2画素間で相関関係を持たしているが、これは3画素以上でも構わない。多くの画素で図70の方式を行うと、より静止画検出の精度が上がるメリットを有しているがレジスタ702のbit数が大きくなるため、回路規模が大きくなるデメリットも有している。そのため、図74に示すようにbit数の違う数種類のレジスタを用意し、複数の画素で相関関係を持たせる方法もある。

712ではレジスタのデータとカウンタ713の値で論理演算を行った値を加算している。カウンタ713は水平同期信号(HD)によってリセットされ、クロックによってカウントアップするモジュールである。そのため、表示領域の水平方向の座標を示しているのと同じであり、このカウンタとデータを論理演算することにより、データに水平方向の座標の重みをつけることが可能である。

714では1水平期間分のデータとカウンタ715の値で論理演算を行った値を加算している。カウンタ715は垂直同期信号(VD)によってリセットされ、HDによってカウントアップするモジュールである。そのため、表示領域の垂直方向の座標を示しているのと同じであり、このカウンタとデータを論理演算することにより、データに垂直方向の座標の重みをつけることが可能である。

以上の方を利用することにより、静止画検出の精度を高めることが可能である。しかし、必ずしも上記の方法を全て使用する必要はない。上記の方法はより精度を高める手法であり、上記の方法を全て使用しないと静止画を検出できないわけではない。

上記の方法を組み合わせた形により、フレームデータ716が出来る。フレームデータは前フレームのデータ717と718にて比較を行う。718で行う比較の方法としては二つのデータが必ずしも同じである必要はない。映像データには少なからずノイズが乗る

ものである。そのため、ノイズが全く無いデータでない限り二つのデータが同じであることは無い。718では必要精度により、二つのデータの誤差範囲を決めてやるのがよい。比較方法として、二つのデータを減算して演算結果から静止画かどうか判断する方法がある他、フレームのはじめに前フレームのデータ717を反転させてフレームデータ（レジスタ）716に入力させて、1F間に加算されたフレームデータ716がいかに0に近づくかにより静止画を判断する方法もある。712、714は加算器を使用しているが前フレームのデータ717から減算器を用いていかに0に近づくかで静止画かどうか判断する方法もある。

図71では表示領域全てのデータを加算することにより、静止画かどうか判断している。しかし、表示画像によっては50%が静止画で残り50%が動画と言う場合もありえる。そのため、カウンタ713とカウンタ715により、画面を複数に分割して画面内のどの範囲が静止画かどうか判断して様々な処理を行う方法も有効である。

10

比較器718が静止画と判断した場合、カウンタ719をカウントアップする。逆に動画と判断した場合はカウンタ719をリセットする。つまりカウンタ719の値が静止画が続いている期間と言うことになる。

まず、このカウンタ719を利用して、EL素子15の劣化速度を落とすために点灯率を落とす方法を提案する。

カウンタ719がある値になった時点で信号線7101を操作する。この信号線7101はH Iのときに点灯率を強制的に制御する信号線である。710内で点灯率制御値556と信号線7101がつながるモジュールを用意し、信号線7101がH Iの場合、強制的に点灯率を現在の1/2に落とすように回路構成する。このとき強制的に点灯率を落とす値は1/2に固定する必要は無く、必要に応じて点灯率を減少させるようにする。点灯率が減少するため、有機EL素子15は発光量が減少し、寿命劣化の速度を落とすことが可能である。もちろん、7101がLOWのときに点灯率を落とすように制御しても構わない。

しかし、劣化速度を上記の方法で落としても長時間流していれば焼きつきは起きてしまう。そのため、長時間静止画状況が続いた場合、有機EL素子15に流す電流を完全に止めてやる必要がある。そのために信号線7102を用いて信号線62bを強制的に操作して、強制的に有機EL素子に電流を流す期間を制御するスイッチング素子をOFFにして有機EL素子に電流が流れるのを阻止する。信号線62bは先に示したとおり、スイッチング素子11dを操作するゲート信号線17bを強制的にH I, LOWどちらかに固定することができる信号線であり、これを信号線7102で制御することにより、長時間静止画が続いた場合に有機EL素子の発光を止めることができると想定されるため有機EL素子の焼きつきを防ぐことが可能となる。

30

更に有機EL素子を利用した表示装置では静止画を検出できることにメリットがある。左記に示したように有機EL素子は間欠駆動を行うことが可能であり、本発明でも点灯率制御値を制御することにより、点灯率を制御している。先に示したように間欠駆動において、黒を一括で挿入することにより、映像の輪郭をはっきりさせることができると想定されるが、映像が非常に良好となる。しかし、黒を一括で挿入することはデメリットも有している。挿入する黒領域が大きくなれば大きくなるほど、人間の目が黒挿入に追いつくことが可能となり、黒挿入がちらつきとして見えてしまうと言う問題がある。これは主に静止画でよく見られる問題であり、動画の場合、映像の変化により、黒挿入のちらつきは見えない。黒を分割して挿入するとこの現象は改善されるが、同時に黒一括挿入によって輪郭をはっきり表示させると想定される効果は使えないことになる。

40

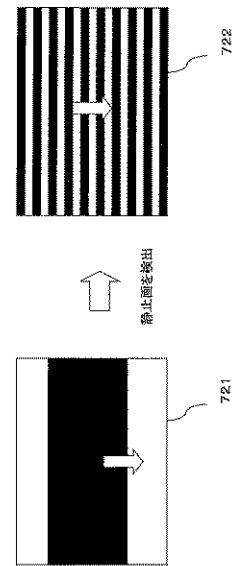

そこで図72に示すように動画表示の場合、黒を一括で挿入する駆動方法を行い、静止を検出すると黒を分割して挿入することにより、静止画時のちらつきを防止する駆動方法について提案する。

図73にてカウンター554と点灯率制御値を利用して黒を分割して挿入するための回路構成について説明する。先に示したようにスイッチングトランジスタ11dはゲート信号線17bによって制御され、ゲート信号線17bはゲートドライバ12に入力されるS

50

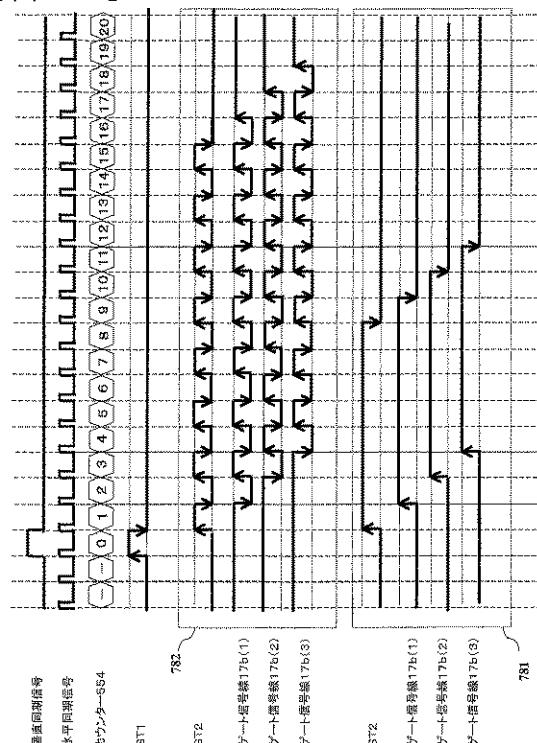

T 2 によって決まる。図 7 5 に示すように S T 2 が 1 H 単位で ON / OFF を繰り返すと、スイッチングトランジスタ 1 1 d は 1 H ごとに ON / OFF を繰り返し、7 2 2 のように黒が分割されて挿入されるような画像となる。そこで、7 3 1 のようなセレクタを多数使用して黒の分割挿入を実現する。

7 1 0 の回路構成はまず最初にカウンタ 5 5 4 の L S B に注目する。セレクタ 7 3 1 は入力値 S が 1 のときに B の値を、0 のときは A の値を出力する。すなわち 7 3 1 a で考えるとカウンタ 5 5 4 の L S B の値が 1 のときは点灯率制御値の M S B の値を出力する。カウンタ 5 5 4 の L S B が 0 のときは 7 3 1 b の出力値が反映される。7 3 1 b はカウンタ 5 5 4 の下位から 2 b i t 目が 1 のときに点灯率制御値の値が 8 b i t の場合、7 b i t 目の値が出力される。これを 3 b i t 目、4 b i t 目・・・と繰り返して行く回路構成になっている。カウンタ 5 5 4 の L S B は 1 H 毎に H I , L O W を繰り返す。点灯率制御値が 8 b i t の場合、8 b i t 目が 1 のときは 1 2 8 以上であるため、2 H に一回は必ず H I になる。すなわち、カウンタ 5 5 4 の L S B をセレクタのスイッチにして L S B が 1 のときに点灯率制御値の M S B の値を出力すると、2 H に一回 S T 2 が H I になる。L S B が 0 の場合は一つ左のセレクタから出る信号の値が S T 2 に出力される。そしてカウンタ 5 5 4 の L S B が 0 でカウンタ 5 5 4 の下位から 2 b i t 目が 1 のときに点灯率制御値の 7 b i t 目が出力されることになる。つまり点灯率制御値の 7 b i t 目が出力されるのは 4 H に 1 回と言うことになる。同様に続けて行くと点灯率制御値の 6 b i t 目の値が出力されるのは 8 H に 1 回・・・と言う形になり。これをくみあわせることにより、黒一括挿入から黒分割挿入に変換させることができるとなる。

上記の黒分割挿入の回路構成と、先に示したフレームメモリを使用する方法を含めて、静止画を検出する回路方法を組み合わせることにより、動画では黒を一括挿入して輪郭をはっきりさせる駆動方法を行い、静止画では黒を分割して挿入することにより一括挿入によるちらつきを防止する駆動を実現することができる。

先に示したソース信号線 1 8 の浮遊容量 4 5 1 を引きぬく手段としてインピーダンスの低い電圧源 7 7 3 を用意しソース信号線 1 8 に電圧を印加する方法がある。上記の手法をプリチャージ駆動と呼ぶものとする。

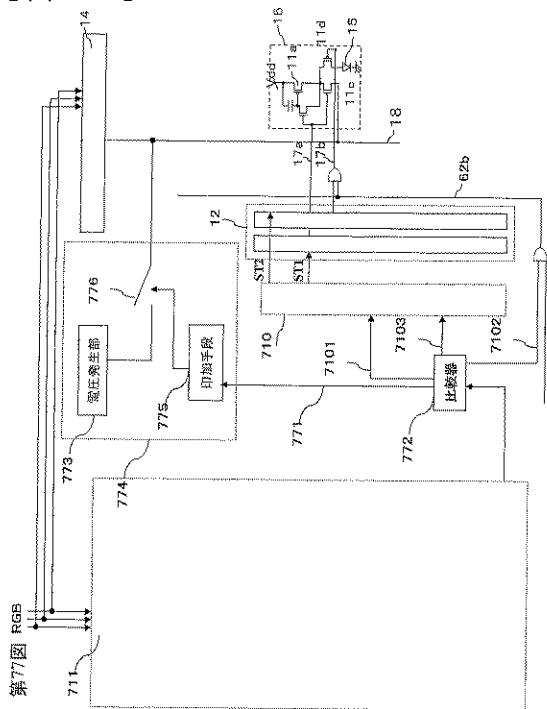

プリチャージ駆動の回路構成を図 7 7 に示す。回路内に電圧源 7 7 3 と電圧印加手段 7 7 5 を設ける。電圧印加手段 7 7 5 がスイッチ 7 7 6 を ON にすると電圧源 7 7 3 がソース信号線 1 8 の浮遊容量 4 5 1 を充放電する。図面の都合上 7 7 4 はソースドライバー 1 4 とは別に書いているが、7 7 4 はソースドライバー 1 4 に内蔵しても良い。また、電圧印加手段 7 7 5 によってプリチャージを行うソース信号線 1 8 を選択することを可能にする回路構成にすると、画素単位でプリチャージの ON / OFF を調整できるので細かい設定が可能となる。

本発明では上記の回路構成に静止画検出手段 7 1 1 を使用する。これは 7 1 1 の変わりにフレームメモリなどを用いても構わない。動画に比べて静止画の方が先に示した浮遊容量 4 5 1 による画像劣化が目立つ。よって 7 1 1 により静止画を検出し、比較器 7 7 2 により電圧印加手段 7 7 5 を操作し、プリチャージを行うことにより、静止画時の画像劣化を防ぐことができる。

前記の用に動画を表示する場合に輪郭をはっきりさせる為に黒を一括挿入するのが好ましいのに加えて、有機 E L 表示装置を駆動させるゲートドライバー回路の電力面からしても黒は一括で挿入する方が好ましい。

また、E L 表示パネルを駆動させるゲートドライバー 1 2 はスタートパルス S T 2 をクロック C L K 2 で動作するシフトレジスタ 6 1 b により、各ゲート信号線 1 7 b を動作させる。7 8 1 に示す用に黒を一括で挿入する場合、1 フレーム間に各ゲート信号線 1 7 は 1 回ずつ ON と OFF をするだけで良い。しかし 7 8 2 の用に黒を分割して挿入する場合、ゲート信号線 1 7 は繰り返し ON と OFF をすることとなる。このため、複数の信号線を同時に ON ・ OFF することになりゲートドライバー 1 2 の消費電力が大きくなると言う問題点がある。

以上の観点から、有機 E L 表示装置は通常は黒を一括で挿入する方が好ましい。しかし

、黒を一括で挿入する場合静止画において黒を一括で挿入することによるちらつきが見える。そのために静止画、もしくは動きの少ない映像を表示している 本発明搭載パネルの表示状態の説明図である。 本発明搭載パネルの表示状態の説明図である。場合、黒を一括挿入から分割挿入に変化させる仕組みが必要となる。しかし、黒を一括挿入から分割挿入に変えると切り替わりの瞬間にちらつきが見える。これには二つの理由が考えられる。

一つ目の理由は分割挿入への切り替え時の一時的な輝度の劣化が考えられる。

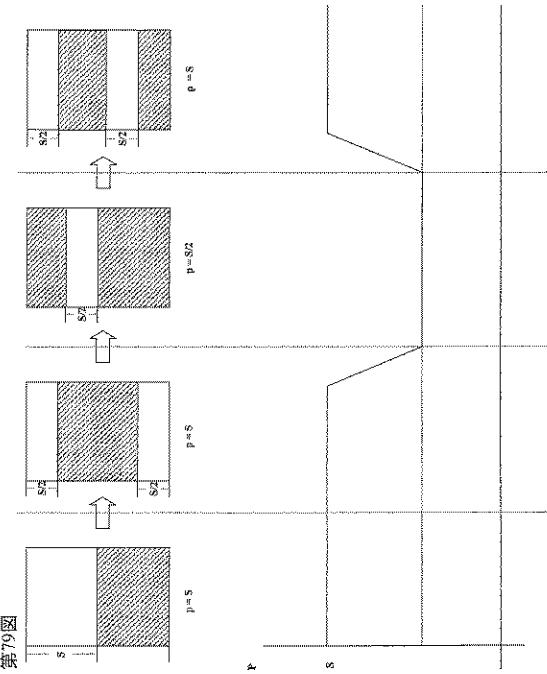

図 7 9 に示すように P 本の水平走査線の内、S 本の水平走査線が点灯している状況を考える。この時の点灯していない、つまり黒の走査線数は P - S (本) である。これを 2 分割させる場合、点灯していない走査線数は (P - S) / 2 (本) ずつになる。切り替わる前は常に S 本の走査線が点灯している状況だが、切り替わりの瞬間のみ S / 2 (本) 点灯してから (P - S) / 2 (本) の間、点灯走査線数が S / 2 になる。この間、表示領域の輝度は S / 2 になるため、わずか 1 フレーム内ではあるが輝度減少が発生し、それが画像劣化になっていると考えられる。

10

二つ目の理由は黒の間隔の急激な変化が考えられる。

黒を一括で挿入すると画像劣化する原因の一つとして、人間の目が無意識に挿入される黒を追っていることが考えられる。そこで黒を一括で挿入している状態から黒を分割して挿入することで、急激に画像が変わったような間隔を覚え、画像劣化のように感じると考えられる。

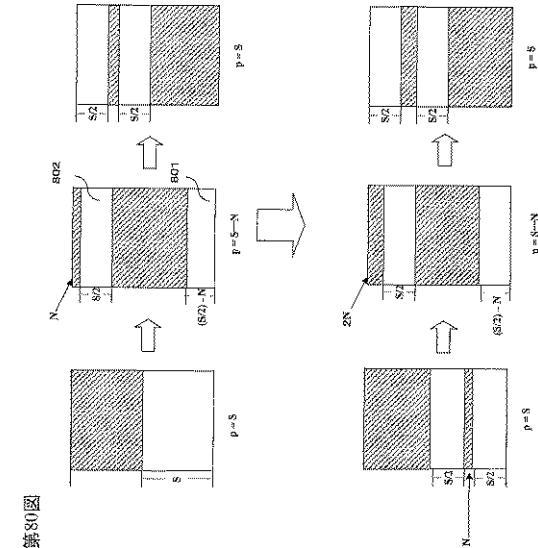

本発明では以上の二つの問題点を解決し、画像の劣化無く、黒の挿入方法を一括挿入から分割挿入に変化させる方法を提案する。切り替え時に画像の劣化が起こるのは前述のように輝度と黒の感覚の急激な変化であるため、本発明では図 8 9 に示す用に黒の間隔を複数のフレーム間にかけて徐々に分割して行く方法により、切り替え時の画像の劣化を防ぐ。図 8 0 は N 水平走査期間（以後、水平走査期間は H と表記する）分の間隔を作つて点灯水平走査線数を 2 分割した場合の輝度の変化を示している。S 本の水平走査線を点灯させている状況において 2 分割したスタートパルスの前段を 8 0 1 とし、後段を 8 0 2 とする 20 と 8 0 1 と 8 0 2 の点灯水平走査線数は S / 2 となる (S = 2 · 4 · 6 · · )。このため、前段のスタートパルス 8 0 1 がゲート信号線に出力された後、S / 2 (H) の間、EL 表示パネルの点灯している水平走査線数 p は (S / 2) - N 本である。その間の表示パネルの輝度は切り替え前に対しても

$$\{ (p / S) \times 100 \quad (\%) \quad \dots \quad (6) \quad 30$$

となる。図 8 1 に示したグラフは一度に図 7 9 と図 8 0 において N = 1 で分割した場合の輝度差をグラフで表現したものである。この分割時の輝度が画像劣化に大きく関わっていると考えられる。

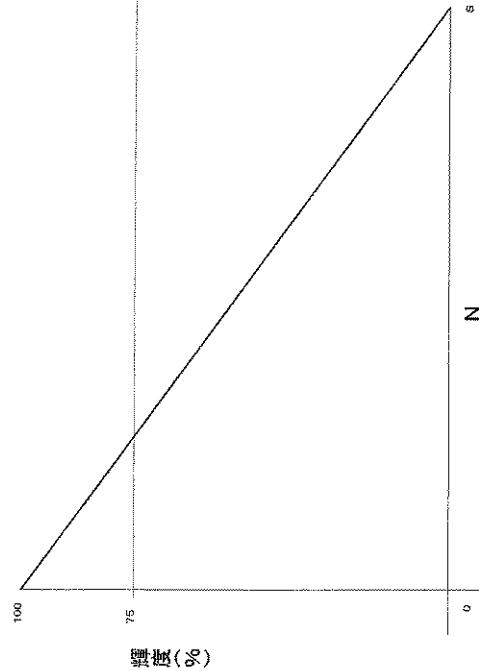

式 (6) の値は p = S - N のため図 1 0 0 に示すように S と N によって変化する。実測値より式 (6) の値が 75 % 未満になると画像の劣化が起こることが解析できた。そのため、本発明では式 (6) の値が 75 % 以上となる N の値、つまり式 (6) より N < S / 4 (ただし N > 1) ずつ黒の挿入間隔を広げて行く方法を提案する。式 (6) の値が 75 % 以上であれば画像劣化は起ららないが、80 % 以上であれば、更に効果が期待できる。最も好ましくは 90 % 以上 (N < S / 10) がよい。

ただし、本発明では輝度が 75 % 未満にならなければ、どのような変化をさせても構わない。図 7 9 では S 本の水平走査線が点灯している状態から点灯水平走査線数を 2 分割する場合に、S / 2 にしているがこれを S' 本と S - S' 本に分割しても構わない (S' < S)。また、一度に分割する量は 2 分割に限るものではない。仮に N = 3 であるとする、1 水平走査期間ずつの間隔をあけると一度に 4 分割しても輝度は 90 % 以上を保つことが可能であるため、処理に影響はない。図 8 2 では黒の挿入間隔を一定にする為、黒の挿入間隔が同じになる場所まで点灯間隔を制御した後に次の分割へと移っている。しかし、図 8 3 に示すように先に分割してから黒の挿入間隔を調整しても構わない。また、点灯間隔はそろえた方が画像劣化の改善効果が高いが必ずしもそろえる必要はない。

前記の方法は黒の挿入間隔を徐々に広げて行く方式であるが、図 8 4 のように逆に点灯水平走査線数を徐々に減らして行くやり方でも良い。S 本点灯している状況から S - N 本

とN本に分割し、次はS - 2N本と2N本に分割すると言う方法で点灯させると、輝度は90%未満にはならないため、輝度の変化による画像劣化は起こらない。この方法は画像劣化の二つ目の理由である黒の挿入間隔の急激な変化を起こしてしまうため、画像劣化が起こると考えられる。しかし前述の通り、輝度の変化による画像劣化は解決できる為、効果がある。

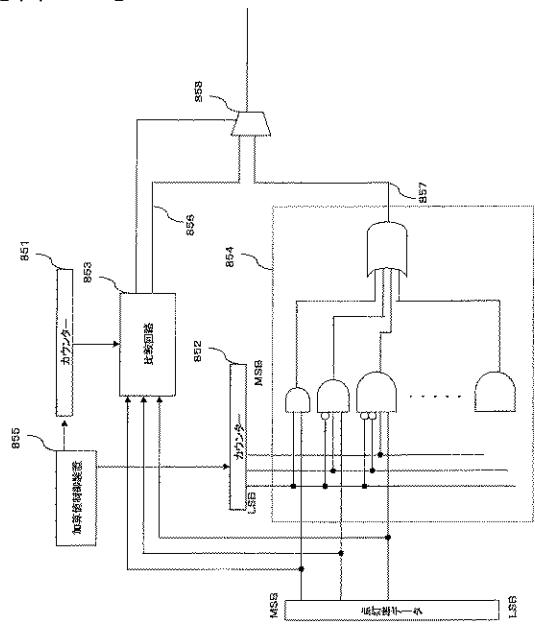

図85に本発明の駆動方法を実現する回路構成図を示す。本発明の回路構成は二つのカウンター回路851、852、その二つのカウンターから信号を生成する回路853、854とその二つのカウンターの加算値を制御する加算値制御回路855、そして853から出力される出力856と854から出力される出力857のどちらかを出力するセレクター858により構成される。

回路854は図73に示した点灯率制御値とカウンター554の値から波形を分割して出力する回路をより遅延の少ない回路に構成しなおしたものである。図73の回路と854は同じものであり、どちらを使用しても構わない。回路853はカウンター851が0のときに出力856をHIGHにする。また、加算値制御回路855内で、点灯率制御値から出力856をLOWにするカウンター値を生成する。点灯率制御値がNビットであり、ゲートドライバー12に入力するスタートパルスST2を2のt乗に分割する場合、点灯率制御値の上位(N-t)ビットの値になった時点で、出力856をLOWにする。また、カウンター851は(N-t)ビットが全部1になる値で0に初期化する用に設定する。このカウンター851を初期化する時に回路854からの出力857を選択するようにセレクター858を制御する。

上記のような設定を行うのは回路構成を容易にする為である。

点灯率制御値は必ずしも割り切れる値とは限らない。スタートパルスを2のt乗に分割する際に点灯率制御値が割り切れない場合は、分割したスタートパルスの長さが異なることになる。長さの違うスタートパルスを制御するのには新たな回路構成が必要となり、回路構成が複雑となる。

そこで上記のような回路構成を使う利点が生まれる。スタートパルスを2のt乗分割した場合、点灯率制御値の下位からtビット間の値は点灯率制御値を2のt乗分割した時の余りである。この余りの部分を補完することで回路の分割を可能にする。回路854と同等の図73に示す回路においてカウンター852の上位tビットが変化する時に点灯率制御値の下位からtビット間のデータに応じて出力する。カウンター852の上位tビット間が変化する時とカウンター851の初期化時は同期している為、カウンター851の初期化時に回路854の出力857をセレクター858で選択することにより、余りの部分を補完することが可能となり、補完することでスタートとパルスの分割を可能になる。この回路構成を用いることで回路規模を小さくすることが可能である。

実際の値を用いて、図86にて上記回路の処理の流れについて説明する。861が回路853の出力856であり、864が回路854の出力857である。863はカウンター851の値であり、864はカウンター852の値である。点灯率制御値が3ビットの容量を持ち、値が3であるとする。2進数で表記すると011である。これを2分割する場合、t=1となるのでカウンター851を初期化する値は2進数表記で11、つまり10進数で3であり、回路853において出力をLOWに落とす値は01で10進数で1である。回路853ではカウンター851が0で出力がHIGHになり、1で出力がLOWになる。回路854ではカウンター852が2・4・6のときに出力がHIGHになる。回路854の出力857を選択する期間はカウンター851の初期化時、つまりカウンター852が4のときであるので、この二つの出力を上記の回路構成により合成すると865のようになり、スタートパルスが2分割できることが確認できる。

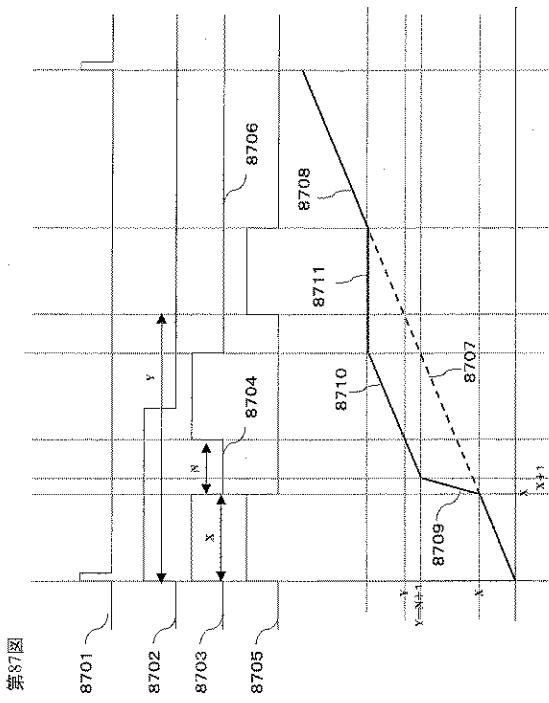

続いて、加算値制御装置を使用した黒の挿入間隔を徐々に変化させる回路構成について説明する。加算値制御装置855は二つのカウンター851、852を同時に制御する為に使用する。加算値制御装置855は1ずつ加算する状態と点灯率制御値と波形の分割数、または黒挿入の間隔から導き出される値を加算する状態と、何も加算しない状態を状況に応じて使い分けることにより、黒の挿入間隔を制御するものである。図87にて、加算

値制御装置の状態の変化について説明する。カウンター 851 が初期化される値を Y、出力 856 が LOW になる値を X とする。8701 は垂直同期信号であり、8702 は黒一括挿入状態のスタートパルス、8703 は前段の黒挿入の間隔 8704 を N (H) としたときの状態であり、8705 は前段の黒挿入の間隔 8704 と後段の黒挿入 8706 の間隔をほぼ同間隔にした状態である。8703 の状態から 8705 の状態に変化させると前述の画像劣化が起きるため、8703 の状態で前段の黒挿入の間隔 8704 を N・2N・3N・…と徐々に広げて、最終的に 8705 の状態にもって行くことで画像劣化を防ぐ。

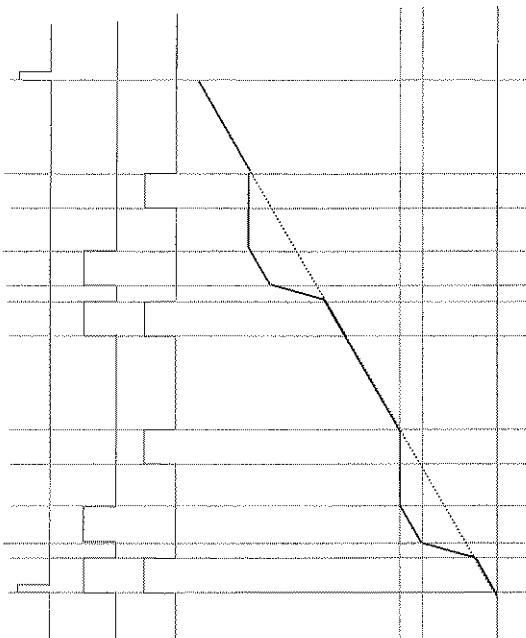

図 87 のグラフにより 8703 の状態の加算値制御回路 855 の動作について説明する。8707 に示す破線はカウンター 851, 852 が 1 ずつ上昇した場合のカウンターの値のグラフである。それに対して実線で示したグラフ 8708 は加算値制御回路 855 によってカウンター 851, 852 の増加値を制御されたカウンターの値のグラフである。カウンター 851 の値が X になるまで、加算値制御回路 855 はカウンター 851, 852 を 1 ずつ増やすように制御する。そしてカウンター 851 の値が X の時点でスタートパルスは LOW になる。本来、次にスタートパルスが HI になるのはカウンター 851 が初期化される Y のときであり、その間は Y - X (H) 期間あるはずである。ここで加算値制御装置 855 は 8709 に示すようにカウンター 851, 852 が Y - N の値になるよう 10 に値を加えるように制御する。これによってスタートパルスが次に HI になるまでの期間が N (H) に短縮される。ここで加算値制御装置 855 は 8710 のようにカウンター 851, 852 に加算する値を 1 に戻す。カウンター 851, 852 は N - 1 (H) 後には値が Y に達する。8709 の値の加算のやり方によって Y の値に到達するまでの期間は変化する。8709 がカウンタ 851 に対して非同期で行われる場合、Y の値に到達するまでの期間は N (H) になる可能性がある。本発明ではどちらの加え方でもよい。そこでカウンター 851 は初期化され、出力 857 が選択された後、再びスタートパルスが HI になる。これにより、前段の黒挿入の間隔 8704 が N (H) になる。スタートパルスが HI になってから X (H) 後、再びスタートパルスは LOW になる。ここで加算値制御装置 855 は 8711 に示すようにカウンター 851, 852 の値を 8707 の値に等しくする為に、カウンター 851, 852 が無加算状態になるように制御する。8709 の期間に加えた値と同様の期間、無加算状態を続けることにより、カウンター 851, 852 は 8707 の値と等しくなる。カウンター 851, 852 の値が 8707 と等しくなると、加算値制御装置 855 はカウンター 851, 852 の増加値を 1 にもどす。2 分割から 4 分割に変化するときのカウンター 851, 852 の変化図を図 88 に示し、その際の黒挿入間隔の変化を図 89 に示す。図 89 より上記の駆動方法を使用すると、急激な輝度変化による画像劣化と、急激な黒の挿入間隔の変化による画像劣化の問題を解決した黒の挿入間隔を徐々に調整する駆動方法が可能であることが分かる。

20

本発明は蓄積容量 19 にプログラミングされた電荷により駆動トランジスタ 11a、もしくは 271b が流す電流をスイッチングトランジスタ 11d が ON, OFF することにより、有機 EL 素子 15 に電流を印加する期間を制御する回路構成であれば、図 1 に限らず図 27 のような回路構成でも使用が可能である。また、回路構成に使用される TFT は P チャンネルでも N チャンネルでも本発明の駆動方法には影響しない。図 133 に示す回路構成は N チャンネルで構成されているが、この構成にも適用可能である。加えてソースドライバー 14 の構成には影響されない。図 90 のような蓄積容量 901 を直接電圧でチャージして駆動トランジスタ 902 を駆動させる電圧駆動方式のような回路であっても本発明の駆動方式は使用可能である。図 76 のような一般的にカレントミラーと呼ばれる TFT のミラー比を用いて電流量を決めるディスプレイにも使用可能である。

30

また、本駆動方式は点灯率の制御によりパネルの電流値を制御する駆動方法であるが、図 96 に示すように点灯率を制御するためにゲートドライバー 12 に入力されている信号線 ST2 を 961 のモジュールに入力し、図 97 のように点灯率に応じた電流値になるようにソースドライバー 14 の電子ボリュームを制御することによってソース信号泉 18 の電流を調整することでパネルの電流量を制御する方法も可能である。尚、962 は本発明に記載される電流量を制御するためのあらゆる駆動方法が適応されるものである。

40

50

前述の図98に示すような外部から送られてくるデータをもとに点灯率を制御する駆動方法は有機EL素子の寿命改善に効果がある。有機EL素子は図91に示すようにデバイスの温度 $t$ が上がると有機EL素子の寿命が劣化する。また、有機EL素子を用いたデバイスはデバイスに流れる電流量Iに比例して温度上昇値 $t$ が増加する。そのため、前述の点灯率を制御する駆動方法はデバイスに流れる電流量を抑制することが可能なため、デバイスの温度上昇を防ぐことができ、有機EL素子の寿命を改善することが可能である。

有機EL素子は図12に示すように有機EL素子15に流れる電流量に比例して発光量が大きくなる。そのため、有機EL素子を用いたディスプレイは有機EL素子に流れる電流を制御することにより映像の表現範囲を広げることが可能である。しかし、前述の通り有機EL素子を用いたデバイスはデバイスに流れる電流量に比例して温度が上昇する為、有機EL素子の劣化を引き起こしてしまう。そのために本発明では前述のように表示データから点灯率を制御することによりデバイスに流れる電流量を抑制する駆動を行い、映像の表現範囲を広げる駆動を提案した。しかしこの駆動方法でも点灯率の制御には限界がある為、映像の表現範囲を点灯率の倍率以上に広げることができない。

そこで本発明では図92に示すように入力される外部データが小さい場合、点灯率を上げるだけでなく、ソースドライバー14の電子ボリュームを制御することにより、ソース信号線に流す電流の基準電流値を制御し、画素に流れる電流量を大きくして有機EL素子を用いたディスプレイの映像表現範囲を広げる駆動方法を提案する。本駆動使用時の外部データとデバイス全体の電流量の図を図93に示す。931は本駆動不使用時の電流値であり、932は本発明の点灯率抑制駆動を用いた場合の電流値である。さらに電子ボリュームを制御した際に得られる電流値が933であり、この図のとおり、電子ボリュームを変化させる範囲は点灯率制御駆動での最大電流値になる外部データの値をpとすると、外部データxが $0 \times p$ となる。

図94に1画素あたりの階調と輝度の関係図を示す。941は点灯率制御駆動をしない場合の関係図である。942は点灯率を行った場合の最大点灯率時の関係図である。943は点灯率制御駆動に加えて、基準電流制御駆動を行った場合の関係図である。寿命、バッテリーの関係で941の関係でしか電流を流せない構成の場合、点灯率の最大と最小时の比が3:1で点灯率制御駆動を行うと942は941の4倍明るく点灯させることができる。それに加えて、さらにソースドライバー14の電子ボリュームにより、基準電流値を3倍まで可変する場合、943は942のさらに3倍の明るさで発光させることが可能になり、941と比較すると12倍もの明るさで発光させることができるために、1画素あたりの表現範囲は12倍になる。これにより、多彩な画像表現が可能となる。

有機EL素子15に流れる電流量を増やすには前述のようにソースドライバー14の電子ボリュームを制御する。制御する方法は電子ボリュームだけとは限らない、例えばD/Aコンバーターを使用して電圧を変化させても良い。蓄積容量19を電圧で直接チャージするような構成の場合でもチャージする電圧をデジタルデータにより制御できる構造であれば本発明を適用することが可能である。

電子ボリュームの設定には表示データ集計回路951の出力を利用する。表示データは図95では映像データであるRGBが入っているが、サーミスタを利用した温度データなどデバイスの状況を確認できるデータであればなんでも使用可能である。951は構造としては552と同じ構造を持つ。552と違う点は点灯率を制御するのに必要なビット数よりさらに数ビット下のビットまで出力することである。仮に952が点灯率を制御するのに必要なビット数が8bitの場合に映像データの合計値の上位10ビット分を出力するように設計したとする。この10bit分の上位8bitは点灯率を制御するのに使われる。その際に残りの下位2bitは上位8bitの小数点の部分と考えることができる。ソースドライバー14の電子ボリュームが6bitで、点灯率が10進数で1未満の領域において電子ボリュームを制御する場合、951は点灯率制御に必要な8bitにさらに小数点の部分で電子ボリュームを制御する為に6bit分を加えて計14bitを出力することになる。これは例えであり、951の出力を15bit以上出力し、そのうちの上位8bitを点灯率制御に使用し、下位6bitを電子ボリュームの制御に利用してもか

まわない。また、点灯率の制御に使用するビットと、電子ボリュームの制御に利用するビットが重なってもかまわない。たとえば 951 が 10 bit の出力を行い、上位 8 bit を点灯率の制御に利用し、下位 6 bit を電子ボリュームの制御に使用する場合、点灯率制御のデータの下位 4 bit と電子ボリュームの制御の上位 4 bit は同じビットを使うことになる。点灯率の制御と電子ボリュームの制御はともにデバイスの発光量を制御するものであるが、ともに明るさを制御する方向（明るくするか、暗くするか）が同じであるので映像上問題がない。まとめると点灯率の制御に a ビット必要とし、電子ボリュームの制御に b ビット必要である状態で 951 が X ビット出力する際に 951 の出力の上位 a ビットを点灯率の制御に利用し、下位 b ビットを電子ボリュームの制御に利用すればよい。951 の出力データが NOT 回路 953 により反転されているのは電子ボリュームの変化と表示データの関係は表示データが小さくなると、電子ボリュームの値が大きくなると言った反転の関係にあるからである。図 92 のように表示データが小さいほど、点灯率を大きくしていくような駆動をする場合、表示データが小さければ小さいほど、電子ボリュームの値を大きくしていく構造になる。そのため、データを NOT 回路により反転させることによりデータが小さければ電子ボリュームが大きくなると言う構造を NOT 回路一つで実現する。これにより回路規模を大きくせずに実現することが可能である。

比較回路 954 は電子ボリュームを制御するブロックに対してイネーブル信号を出すものである。比較回路 954 は 951 から出力されるデータが N ビットで、下位 n ビットで電子ボリュームをする際に上位 (N - n) ビットが 0 かどうか判断するとイネーブル信号を出力する。これにより回路規模を大きくせずに特定の表示データ以下で電子ボリュームを制御する回路構成が実現できる。

また、図 99 に示すように点灯率を制御する値の下位数ビットを使用してもかまわない。動作原理としては前述と同じであるが、点灯率を制御する値で制御する場合、点灯率が大きいほど電子ボリュームの値も大きくすれば良いので NOT 回路を入れる必要はない。この方式は図 61 のように表示データから点灯率を制御するデータを作る際にちらつき防止の遅延処理を行うようなモジュールを使用する場合に遅延処理と同時に使用することが可能であるため有効である。

NOT 回路が必要かどうかはソースドライバー 14 の電子ボリュームの構成でも変化する。電子ボリュームのスイッチが HI で動作するか、LOW で動作するかで NOT 回路が必要かどうかは変化する。

この方式は点灯率を制御するのに使用している信号線を利用して電子ボリュームを制御するため、回路規模はほとんど大きくせずに電子ボリュームを制御することが可能である。また、この処理により、1 画素あたりの表現範囲を大きくすることが可能になるため、より多彩な画像表示が可能となる。

有機 EL 素子の劣化はデバイスの温度に依存する。また、デバイスの温度上昇はデバイスに流れる電流量の総和と素子に流れる電流量に依存する部分が大きい。そのため、有機 EL 素子の劣化を防ぐためにデバイスの温度に応じて電流量を操作する仕組みが必要となる。デバイスの温度を感知する一つの方法としてデバイス内にサーミスタを配置して、サーミスタと A / D コンバータにより、デジタルデータに変換して感知する方法がある。しかし、この方法はデバイス内部、もしくは画素内部にサーミスタを配置しなければならず、更にデジタルデータとして感知するためには A / D コンバータも必要になるため、回路規模が大きくなると言う問題がある。

そのため、本発明では図 111 に示すような先に示した映像データから点灯走査線数を制御する仕組みを利用して温度制御をする駆動方法を提案する。

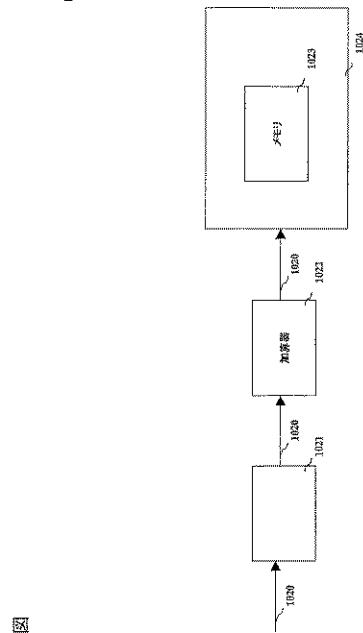

図 29 に先に示した映像データから点灯走査線数を制御する駆動方法を行った場合の映像データと点灯水平走査線数の関係を示す。点灯走査線数とデバイスに流れる電流の関係は 1010 のようになることから、点灯水平走査線数と映像データから演算処理を行うことにより、デバイスに流れる電流量を把握することが可能になる。そのため図 102 のような回路構成を利用する。1020 はデバイスに表示する映像データである。1021 は入力される映像データを加工するための回路である。仮に RGB の三色が入力されている