## (19) **日本国特許庁(JP)**

(E1) Int (1)

# (12) 特 許 公 報(B2)

DТ

(11)特許番号

特許第4681785号 (P4681785)

最終頁に続く

(45) 発行日 平成23年5月11日(2011.5.11)

(24) 登録日 平成23年2月10日(2011.2.10)

| (51) Int.CI.  | F I                           |                         |

|---------------|-------------------------------|-------------------------|

| GO9G 3/30     | <b>(2006.01)</b> GO9G         | 3/30 J                  |

| GO9G 3/20     | <b>(2006.01)</b> GO9G         | 3/20 6 2 4 B            |

| GO9F 9/30     | <b>(2006.01)</b> GO9G         | 3/20 6 4 1 D            |

| HO1L 27/32    | <b>(2006.01)</b> GO9G         | 3/20 6 4 2 C            |

| HO1L 51/50    | <b>(2006.01)</b> GO9G         | 3/20 6 4 2 P            |

|               |                               | 請求項の数 4 (全 10 頁) 最終頁に続く |

| (21) 出願番号     | 特願2001-528967 (P2001-528967)  | (73) 特許権者 590000248     |

| (86) (22) 出願日 | 平成12年9月18日 (2000.9.18)        | コーニンクレッカ フィリップス エレク     |

| (65) 公表番号     | 特表2003-511724 (P2003-511724A) | トロニクス エヌ ヴィ             |

| (43) 公表日      | 平成15年3月25日 (2003.3.25)        | オランダ国 5621 ベーアー アイン     |

| (86) 国際出願番号   | PCT/EP2000/009194             | ドーフェン フルーネヴァウツウェッハ      |

| (87) 国際公開番号   | W02001/026087                 | 1                       |

| (87) 国際公開日    | 平成13年4月12日 (2001.4.12)        | (74) 代理人 100070150      |

| 審査請求日         | 平成19年9月18日 (2007.9.18)        | 弁理士 伊東 忠彦               |

| (31) 優先権主張番号  | 9923261.3                     | (74) 代理人 100147485      |

| (32) 優先日      | 平成11年10月2日 (1999.10.2)        | 弁理士 杉村 憲司               |

| (33) 優先権主張国   | 英国 (GB)                       | (74) 代理人 100113745      |

|               |                               | 弁理士 藤原 英治               |

|               |                               | (74) 代理人 100072051      |

|               |                               | 弁理士 杉村 興作               |

|               |                               |                         |

(54) 【発明の名称】アクティブマトリクスエレクトロルミネッセンス表示装置

## (57)【特許請求の範囲】

## 【請求項1】

表示画素のアレーを具え、各画素がエレクトロルミネッセンス表示素子と、駆動期間において該表示素子を流れる電流を、駆動期間前のアドレス期間中に画素に供給され且つ蓄積キャパシタンスに電圧として蓄積された駆動信号に基づいて制御する駆動装置とを具えるアクティブマトリクスエレクトロルミネッセンス表示装置において、各画素は帰還調整手段を含み、該手段は駆動期間における表示素子の両端間の電位差に応答し、アドレス期間にキャパシタンスに蓄積された電圧をこの電位差に応じて調整するよう構成され、前記帰還調整手段が、表示素子に接続され、アドレス期間直後の表示素子両端間の電圧の上昇に応答してこの電圧上昇に応じた出力を発生し、この出力で蓄積キャパシタンスに蓄積される電圧の調整を制御する高域通過フィルタ回路を具えることを特徴とするアクティブマトリクスエレクトロルミネッセンス表示装置。

【請求項2】

各画素が、アドレス期間において表示素子に電流が流れるのを阻止するように動作し、 駆動期間において表示素子に電流が流れるのを許すように動作するスイッチング装置を含むことを特徴とする請求項 1 記載のアクティブマトリクスエレクトロルミネッセンス表示 装置。

## 【請求項3】

前記帰還調整手段が、駆動期間の開始時における表示素子両端間の過渡電位差増大に応答することを特徴とする請求項1又は2記載のアクティブマトリクスエレクトロルミネッ

センス表示装置。

## 【請求項4】

前記高域通過フィルタの出力が蓄積キャパシタンスと所定の電位との間に接続された他のスイッチング装置を制御し、これを動作させて蓄積キャパシタンスの補足充電を行なうことを特徴とする請求項 1 記載のアクティブマトリクスエレクトロルミネッセンス表示装置。

【発明の詳細な説明】

[0001]

#### (技術分野)

本発明は、エレクトロルミネッセンス表示画素のアレーを具えるアクティブマトリクスエレクトロルミネッセンス表示装置に関するものである。

[0002]

## (背景技術)

エレクトロルミネッセンス発光表示素子を用いるマトリクス表示装置は公知である。表示素子は、例えばポリマ材料を用いる有機薄膜エレクトロルミネッセンス素子、又は伝統的なIII・V半導体化合物を用いる発光ダイオード(LED)を具えるものとすることができる。有機エレクトロルミネッセンス材料、特にポリマ材料の最近の開発によりこれらの材料はビデオ表示装置に実用可能であることが証明されている。これらの材料は代表的には一対の電極間に挟まれた1以上のエレクトロルミネッセンス材料の層、例えば半導電性共役ポリマの層を具え、一方の電極は透明にし、他方の電極はポリマ層に正孔又は電子を注入するのに好適な材料で形成する。ポリマ材料層はCVDプロセスにより、又は簡単に可溶性共役ポリマの溶液を用いてスピンコーティング技術により製造することができる。

[0003]

有機エレクトロルミネッセンス材料はダイオードのような I - V 特性を示すため、これらの材料は表示機能とスイッチング機能の両方を提供することができるので、パッシブ形の表示装置に使用することができる。

[0004]

しかし、本発明は、各画素がエレクトロルミネッセンス(EL)表示素子と該表示素子を流れる電流を制御するスイッチング装置を具えるアクティブマトリクス表示装置に関する。アクティブマトリクスエレクトロルミネッセンス表示装置の種々の例がEP- A - 0 6 5 3 7 4 1 及びEP- A - 0 7 1 7 4 4 6 に開示されている。表示素子が容量性であるために実際上電流を流さず、駆動信号電圧をキャパシタに全フレーム期間に亘って蓄積することができるアクティブマトリクス液晶表示装置と異なり、エレクトロルミネッセンス表子は光を発生するためには連続的に電流を流す必要がある。画素の駆動装置は通常TFT(薄膜トランジスタ)を具え、表示素子を流れる電流を制御する必要がある。表示素子(薄膜トランジスタ)を具え、表示素子を流れる電流を制御する必要がある。表示素子の輝度はそれを流れる電流により決まる。画素のアドレス期間中に、その画素にその表示表子がらの所要の出力を決定する駆動(データ)信号が供給され、その電流制御駆動装置を続された蓄積キャパシタに蓄積され、キャパシタに蓄積された電圧が電流制御駆動装置の動作を制御して、その画素が再びアドレスされるまで、フレーム期間に相当する期間中スイッチング装置を表示素子に電流を供給する動作状態に維持する。

[0005]

既知の有機エレクトロルミネッセンス材料、特にポリマ材料に対する問題は、これらの材料は安定性が悪く、エージング効果を被るので、所定の駆動電流に対する光出力が動作期間中に減少する点にある。所定の用途ではこのようなエージング効果は臨界的でないが、画素化表示装置においては画素からの光出力の僅かな変化が観察者に容易に知覚されるのでその結果は重大になり得る。

[0006]

本発明の目的は、この問題を少なくともある程度克服したアクティブマトリクスエレクトロルミネッセンス表示装置を提供することにある。

[0007]

40

10

20

30

#### (発明の開示)

本発明は、表示画素のアレーを具え、各画素がエレクトロルミネッセンス表示素子と、駆動期間内に該表示素子を流れる電流を、駆動期間前のアドレス期間中に画素に供給され且つ蓄積キャパシタンスに電圧として蓄積された駆動信号に基づいて制御する駆動装置とを具えるアクティブマトリクスエレクトロルミネッセンス表示装置において、各画素が帰還調整手段を含み、該手段が駆動期間における表示素子の両端間の電位差に応答し、それに応じてアドレス期間にキャパシタンスに蓄積された電圧を調整するよう構成されていることを特徴とする。

## [0008]

EL表示素子は時間の経過とともに劣化するので、そのインピーダンス及びそのアノード - カソード間の電位差が増大する。この電位差の変化の値は表示素子の光出力/駆動電流 特性に関して表示素子の状態の正当な指示を与える。従って、アドレス後の表示素子駆動電流を決定する蓄積キャパシタンスに蓄積された電圧を、表示素子の光出力特性を表わす表示素子の両端間の電位差に従って正帰還により調整することによって、表示素子のエージング効果に対する適切な補償を表示素子の駆動において行なうことができるため、所定の供給駆動信号に対する所望の光出力がアレー内の各表示素子の駆動電流レベル/光出力レベル特性の可能な経時変化と無関係に維持される。

#### [0009]

本発明は、表示素子がポリマLED材料である装置に特に有利であるが、エレクトロルミネッセンス材料が同様にエージング効果を受け、動作期間に亘って所定の駆動電流に対する光出力の低下を生ずる如何なるエレクトロルミネッセンス装置にも有利に適用することができること勿論である。

#### [0010]

帰還調整手段内に、アドレス期間において表示素子に電流が流れるのを阻止し次の駆動期間において表示素子に電流を流れさせるスイッチング装置を含めるのが好ましい。このスイッチング装置によれば、アドレス期間の終了時及び駆動期間の開始時における表示素子の両端間の電位が既知のレベル、即ち0ボルトになるとともに、蓄積キャパシタンスへの駆動信号の蓄積が、さもなければこの時点で表示素子を流れる駆動電流により影響されることがなくなる。

## [0011]

好適実施例では、帰還調整手段は駆動期間の開始時における表示素子両端間の過渡電位差増大に応答するようにする。この目的のためには、表示素子に接続され、その両端間の電圧の上昇に応答してこの電圧上昇に応じた出力を発生し、蓄積電圧の調整を制御する高域通過フィルタ回路を用いるのが好都合である。この回路は、その出力で動作し、所定の電位源を蓄積キャパシタンスに接続して補足充電を行なう他のスイッチング装置を含むことができる。

## [0012]

## (発明を実施するための最良の形態)

以下、図面を参照して本発明をアクティブマトリクスエレクトロルミネッセンス表示装置の一実施例につき詳細に説明する。各図は略図である。また、各図において同一の符号は同一又は類似の部分を示す。

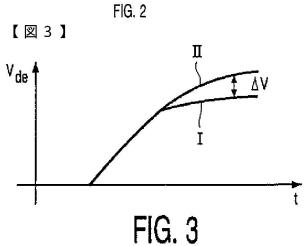

図1は既知のアクティブマトリクスエレクトロルミネッセンス表示装置の簡略構成図であり、このアクティブマトリクスエレクトロルミネッセンス表示装置はブロック10で示す等間隔配置の画素の行列マトリクスアレーを有するパネルを具え、各画素は交差する一群の行(選択)及び列(データ)アドレス導体12及び14の交点に位置するエレクトロルミネッセンス表示素子及び該表示素子を流れる電流を制御する関連の駆動装置を具える。図を簡単にするために少数の画素のみを示す。画素10は周辺駆動回路により行及び列アドレス導体を介してアドレスされ、この駆動回路は走査信号を行導体に順々に供給する行(走査)駆動回路16と、データ信号を列導体に供給しそれぞれの画素の表示素子からの表示出力を決定する列(データ)駆動回路18を具える。

10

20

30

40

10

20

30

40

50

#### [0013]

各画素行は回路16により該当する行導体12に供給される選択信号によって各行アドレス期間に順々にアドレスされ、当該行の画素に、回路18により列導体群に並列に供給されるそれぞれのデータ信号に従ってそれぞれの駆動信号を負荷する。各行がアドレスされるたびに、これに適切に同期して回路18により適切なデータ信号が供給される。

### [0014]

#### [0015]

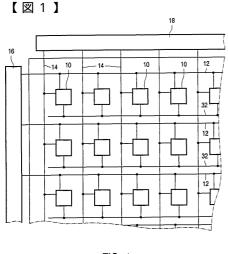

各画素 1 0 は、表示素子 2 0 を流れる電流、従って表示素子の動作を画素に供給されるデータ信号電圧に基づいて制御するTFT 2 2 の形態の駆動装置を含む。各画素の信号電圧は各列の画素に共通の列導体 1 4 から供給される。列導体 1 4 はアドレスTFT 2 6 を経て電流制御駆動トランジスタ 2 2 のゲートに結合される。一行の画素のアドレスTFT 2 6 のゲートは共通の行導体 1 2 に結合される。

#### [0016]

各行の画素 1 0 は、通常全画素に共通の連続電極として設けられる共通電圧供給ライン 3 0 も共有するとともに、各共通電流ライン 3 2 も共有する。表示素子 2 0 及び駆動装置 2 2 は電圧供給ライン 3 0 と共通電流ライン 3 2 との間に直列に接続され、電流供給ライン 3 2 は電圧供給ライン 3 0 に対し正電位にあり、表示素子 2 0 を流れる電流のための電流ドレインとして作用する。表示素子 2 0 を流れる電流はスイッチング装置 2 2 により制御され、トランジスタ 2 2 のゲート電圧の関数であり、このゲート電圧は列導体 1 4 に供給されるデータ信号により決まる蓄積制御信号に依存する。

## [0017]

行駆動回路16により選択パルスを各行導体12に供給して各行の画素のTFT26をスイッチオンすることにより各行の画素が各行アドレス期間において選択され、アドレスされる。ビデオ情報から得られた電圧レベルが駆動回路18により列導体14に供給され、アドレスTFT26により駆動トランジスタ22のゲートに転送される。各行の画素が行導体12を介してアドレスされてない期間中、アドレスTFT26はターンオフされるが、駆動トランジスタ22のゲートと共通電流ライン32との間に接続された画素蓄積キャパシタ36により維持される。駆動トランジスタ22のゲートと共通電流ライン32との間の電圧はアドレス期間直後の駆動期間において画素10の表示素子20を流れる電流を決定する。従って、表示素子を流れる電流は駆動トランジスタ22のゲート・ソース電圧の関数になる(トランジスタ22のソースは共通電流ライン32に接続され、トランジスタ22のドレインは表示素子20に接続される)。この電流が次に画素の光出力レベル(グレースケール)を制御する。

#### [0018]

スイッチングトランジスタ22は飽和状態で動作するように構成して、ドレイン・ソース

10

20

30

40

50

電圧と無関係にゲート・ソース電圧がトランジスタを流れる電流を決定するようにする。 その結果、ドレイン電圧の僅かな変化は表示素子 2 0 を流れる電流に影響を及ぼさない。 これがため、電圧供給ライン 3 0 の電圧は画素の正しい動作に対し臨界的でない。

### [0019]

各画素行を各行アドレス期間にて順々にアドレスし、各行の画素にそれぞれの駆動信号を順々に供給して各行の画素を次にアドレスされるまで駆動(フレーム)期間中所望の出力を発生するように設定する。

## [0020]

この既知の画素回路では、キャパシタ36に蓄積される電圧は供給データ信号電圧により実質的に決まり、この電圧が次に駆動トランジスタ22、従って表示素子20を流れる電流を制御するので、得られる表示素子の光出力レベルはいつでも表示素子の現在の電流/光出力レベル特性に依存することが分かる。表示素子のエレクトロルミネッセンス材料は動作期間中に劣化してエージング効果を生じ、その結果として所定の駆動電流レベルに対する光出力レベルの低下を生ずる。従って、長期間(又は強く)駆動された画素は低下した輝度を示し、表示が不均一になる。ポリマLED材料の場合にはこのようなエージング効果が顕著になり得る。

## [0021]

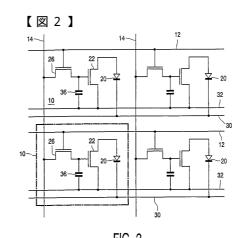

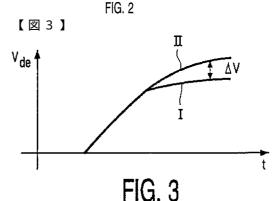

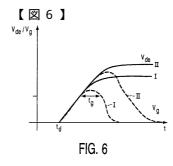

所定の電流を流す表示素子が劣化するにつれて、そのインピーダンス及びそのアノードとカソードとの間の電位差が増大することが確かめられた。表示素子20は固有のキャパシタンスを有する。図3は表示素子の一般的なエージング効果を、表示素子のターンオン時の充電期間における表示素子両端間の電圧(Vde)対時間(t)特性に関して、グラフで示すものであり、曲線Ⅰは初期状態の場合を示し、曲線Ⅱは例えば数千時間の動作後の場合を示す。これから明らかなように、この電圧は Vだけ増大し、その量はエージングの程度に従って変化する。一般に、 Vは時間の経過につれて増大する。

#### [0022]

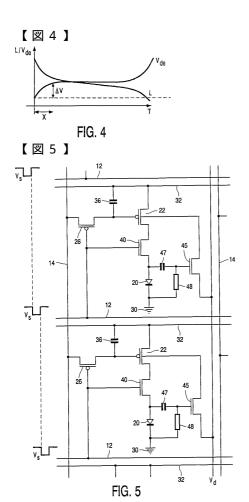

図4は一定の駆動電流で長い動作期間T、例えば数千時間に亘って動作させた場合の表示素子の輝度Lと表示素子両端間の電圧Vdeとの関係をグラフで示すものである。これから明らかのように、この電圧は表示素子の動作寿命の初期の段階では著しく増大し、平坦域になると相当長い期間に亘ってほぼ一定に維持され、次いで表示素子の寿命の終りに向って増大する。逆に、輝度の変化は、表示素子の寿命の初期段階では著しく低下し、次いでほぼ一定レベルに維持され、次いで再び低下する。

## [0023]

本発明では、各画素に、表示素子の両端間の電位差を検出し、その値を帰還変量として用いて表示素子の駆動を自動的に調整してこのようなエージング効果を少なくともある程度補償する手段を設け、これにより所定のデータ信号レベルに対する表示素子の所要の光出力レベルを維持する。

## [0024]

図5には、光出力低下エージング効果を少なくともある程度克服するよう構成された本発明表示装置の一実施例の代表的画素の等価回路が示されている。各画素10内には、表示素子20が再び電流ライン32と電圧供給ライン30(ここでは全画素に共通の共通電極層で構成される)との間に駆動トランジスタ22と直列に接続されている。アドレストランジスタ26のゲート及びソースは関連する行及び列導体12及び14にそれぞれ接続する。蓄積キャパシタ36も同様に駆動トランジスタ22のゲートとトランジスタ26のドレイン及び電流ライン32との間に接続する。

## [0025]

画素は、更に、表示素子20と制御TFT22との間に直列に接続された、同様にTFT 形態の、他のスイッチ装置40を含み、そのゲートは行導体12に接続する。更に、別の TFT、即ち帰還TFT45を設け、その両電流端子を駆動TFT22のゲートと、例え ばカソード電位に対応する所定の低レベルの電位源Vdとの間に接続する。TFT45の ゲートはキャパシタ47を経て表示素子のアノードとTFT40との接続点に接続すると

10

20

30

40

50

ともに、抵抗48を経て表示素子のカソード電圧供給ライン30にも接続する。抵抗48とキャパシタ47は相俟って受動微分器として作用する受動高域通過フィルタ回路を構成し、その出力を帰還TFT45のゲートに供給する。

TFT26及び22はp形TFTであり、TFT40及び45はn形TFTである。

## [0026]

前に述べて様に、画素の動作は2つのフェーズ、即ち画素を供給データ信号に応じて所望の表示出力を出力するようにセットするアドレスフェーズと、次いでそれらの表示素子をそれらが例えば次のフレーム期間において再びアドレスされるまで所要の表示出力を発生するように駆動する駆動フェーズを有する。代表的には、行アドレス期間は約30マイクロ秒、駆動(フレーム)期間は約16ミリ秒にすることができる。アドレスフェーズでは、該当する行導体の電圧は行駆動回路16により発生される選択信号Vsにより行アドレス期間に対応する期間中低レベルにされ、これによりp形アドレスTFT26がターンオンし、列駆動回路18により列導体14に供給されたデータ電圧を蓄積キャパシタ36に蓄積するとともにTFT22をターンオンする。この選択期間中、n形TFT40はオフに維持されるため、この時間には電流は表示素子を流れない。フレーム期間内の各画素の光出力を変化させるために(すなわちグレースケール)、供給データ信号電圧レベルを増大することによりアドレス期間中のTFT22のゲートノードの電荷を適切に調整する。

## [0027]

選択信号 V s の終了時に対応する行アドレス期間の終了時に、行導体 1 2 の電圧は高レベルに戻り、TFT 2 6 をターンオフさせ、キャパシタ 3 6 の一端を列導体 1 4 から切り離す。同時に,TFT 4 0 をターンオンする。このとき、駆動電流が直列接続のTFT 2 2 及び 4 0 を経て表示素子 2 0 に流れ、この電流のレベルはキャパシタ 3 6 に蓄積された電圧に従ってTFT 2 2 により決定される。

#### [0028]

行アドレス期間の終了時では、表示素子20の両端間の電位は零ボルトである。その直後にTFT22及び40が導通し、表示素子20が充電及び導通し始めるので、表示素子20の両端間の電位は増大し始める。充電期間は駆動期間の比較的小さな初期部分、代表的には10-20マイクロ秒を占めるだけである。この初期期間における表示素子両端間の増大する電位はキャパシタンス47と抵抗48からなる高域通過フィルタに至り、過渡ゲート・ソース電圧を帰還TFT45に供給し、TFT45をターンオンしてそのドレインとTFT22のゲート及びキャパシタ36のノードとの間の接続を経て蓄積キャパシタ36の過渡充電を生ずる。得られるキャパシタ36の比較的小さな補足充電は駆動期間のこの初期段階における表示素子両端間の検出電圧に依存し、駆動TFT22を表示素子20を流れる電流がそれに応じて僅かに増大するよう制御するのに有効である。補足充電の量は表示素子両端間の検出電位差のレベルに応じて変化し、代表的には全蓄積電荷の10%以下程度である。

## [0029]

表示素子が時間の経過とともに劣化するにつれて、その両端間の導通電圧は増大し、その結果として高域通過フィルタ及び帰還TFT45によるキャパシタ36の補足充電がこれに応じて増大し、これにより駆動TFT22が適切に制御され、TFT22により表示素子を流れる駆動電流のレベルが増大してこのエージング効果に対するある程度の補正が達成される。その結果として、表示素子の劣化が画素回路のデータ信号電圧/光出力特性に及ぼす影響が減少し、駆動フェーズにおいて所定の供給データ信号に対し表示素子により発生される光量は所望のレベルに維持されるようになる。

#### [0030]

この目的を達成するためには、帰還回路を正しく調整することが重要である。この点で、この調整は所定の電位 V dの値を対応して変化させることにより行なうことができる。 T F T 4 5 の動作を制御する R - C 高域通過フィルタ 4 7 、 4 8 の出力は実際上表示素子のアノード電圧の微分である。高域通過フィルタ 4 7 、 4 8 は一定電流での E L 表示素子の電圧上昇時間特性に調整する。好ましくは、フィルタ回路を(その構成要素値の適切な選

択により)フィルタ回路の電圧出力が充電期間中の表示素子のアノード電圧に追従するように調整する。所定の電位 V d は大地電位にすることができ、また表示素子のカソード電位が大地電位でない場合にはこのカソード電位にすることもでき、またTFT45が必要な時にターンオンするならば若干異なる値にすることもできる。この電位 V d は全画素に共通であり、画素アレー内に形成した導電格子パターンにより都合よく各画素に供給することができる。

#### [0031]

画素回路の帰還動作は表示素子のエージング特性の初期寿命部分、即ち図3のXで示す特性曲線の部分において最も有効であるが、全寿命に亘って有用である。

#### [0032]

## [0033]

上述したように各画素行が(図5に選択信号 Vsの相対的なタイミングで示すように)各アドレス期間において順々にアドレスされ、それらの画素の光出力がそれらの帰還回路の動作により適切に調整され、次のフィールドで再びアドレスされるまで維持される。

#### [0034]

画素回路のアクティブマトリクス素子はすべて絶縁性基板の上に薄膜素子(TFT、キャパシタ及び導電性相互接続)として容易に製造することができる。同様に、電位検出及び帰還回路の追加の素子、即ち追加のTFT40及び45、キャパシタ47及び抵抗48も同一のプロセスを用いて基板上に同時に製造することができ、TFTがポリシリコン形のTFTである場合には抵抗は例えばドープポリシリコンで構成することができる。或は又、アモルファスシリコン技術を用いつこともできる。

## [0035]

上述した実施例のTFTはn及びpチャネル形MOSTFTを具えている。反対の形のTFTを使用することもでき、この場合には表示素子20の極性及び駆動電圧の極性を逆にし、選択信号Vsは正電圧パルスを具えるものとする。

### [0036]

上述の実施例では電流ライン32は行方向に延在し、各行の画素に共通であるが、これら の電流ラインは列方向に延在させ、各電流ラインを各列の画素に共通にすることもできる

## [0037]

本発明は上述した実施例のように電圧駆動信号を用いるのではなく電流駆動 (データ) 信号を用いる種類の E L 表示装置にも使用することができる。このような装置の例はW O 9 9 / 6 5 0 1 2 に開示され、これを参照されたい。これに記載された装置では、各画素は駆動 T F T 2 2 のゲートノードと電流ライン 3 2 とアドレス T F T 2 6 の出力との間に相互接続されたカレントミラー回路を構成する 2 つの追加の T F T を含んでいる。このカレントミラー回路の動作が駆動 T F T 2 2 のしきい値電圧の変化によりアレーの画素に生ずる問題を克服する。この装置では、列導体 1 4を流れる画素入力データ電流を T F T 2 6 でサンプルし、駆動 T F T で鏡影して比例電流を生成し表示素子に流す。電流が安定すると、蓄積キャパシタの電圧はこの電流を生成するのに必要な T F T 2 2 のゲート電圧に等しくなる。素子 4 5 、 4 7 及び 4 8 からなる帰還回路を上述したように同様に使用して駆動期間における蓄積電圧を調整することができる。

## [0038]

50

20

10

30

従って、要約すれば、駆動期間内に各画素内のEL表示素子を流れる駆動電流が、その前のアドレス期間に画素に供給され関連する蓄積キャパシタに電圧として蓄積された駆動信号に基づいて駆動装置により制御されるアクティブマトリクスEL表示装置を記載している。所定の駆動信号レベルに対する表示素子の光出力が時間の経過とともに低下する表示素子のエージング効果を抑えるために、各画素は帰還回路を含み、該帰還回路がエージングの程度を表わす駆動期間の初期部分における表示素子両端間の電位差に応答し、それに応じて蓄積キャパシタに蓄積された電圧を調整するよう構成されている。

## [0039]

以上の説明を読めば、当業者は他の種々の変更が考えられる。これらの変更には、アクティブマトリクスエレクトロルミネッセンス表示装置及びその構成要素の分野において既知であって、上述した構成要件の代わりに又は加えて使用し得る他の構成要件も含むものとする。

10

## 【図面の簡単な説明】

【図1】 画素のアレーを具える既知のアクティブマトリクスエレクトロルミネッセンス表示装置の簡略構成図である。

【図2】 図1のアドレスマトリクスエレクトロルミネッセンス表示装置の数個の代表的画素の等価回路図を示す。

- 【図3】 表示素子のエージング効果を示すグラフである。

- 【図4】 表示素子の他のエージング効果を示すグラフである。

【図5】 本発明によるアクティブマトリクスエレクトロルミネッセンス表示装置の一実 20 施例内の数個の代表的な画素の等価回路を示す。

【図6】 図5の装置内の画素の動作の効果を示すグラフである。

FIG. 1

## フロントページの続き

(51) Int.CI. FI

G 0 9 G 3/20 6 7 0 J G 0 9 F 9/30 3 3 8 G 0 9 F 9/30 3 6 5 Z H 0 5 B 33/14 A

(72)発明者イアンエムハンターオランダ国5656アーアーアインドーフェンプロフホルストラーン6

審査官 樫本 剛

(56)参考文献 国際公開第98/040871(WO,A1) 国際公開第99/038148(WO,A1)

(58)調査した分野(Int.CI., DB名)

G09G 3/20 - 3/38 G09F 9/30

| 专利名称(译)        | 有源矩阵电致发光显示装置                                                                                                                          |         |            |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | JP4681785B2                                                                                                                           | 公开(公告)日 | 2011-05-11 |  |

| 申请号            | JP2001528967                                                                                                                          | 申请日     | 2000-09-18 |  |

| [标]申请(专利权)人(译) | 皇家飞利浦电子股份有限公司                                                                                                                         |         |            |  |

| 申请(专利权)人(译)    | 皇家飞利浦电子股份有限公司的V                                                                                                                       | ie      |            |  |

| 当前申请(专利权)人(译)  | 皇家飞利浦电子股份有限公司的V                                                                                                                       | ie      |            |  |

| [标]发明人         | イアンエムハンター                                                                                                                             |         |            |  |

| 发明人            | イアン エム ハンター                                                                                                                           |         |            |  |

| IPC分类号         | G09G3/30 G09G3/20 G09F9/30 H01L27/32 H01L51/50 G09G3/32                                                                               |         |            |  |

| CPC分类号         | G09G3/2014 G09G3/3233 G09G2300/0809 G09G2300/0814 G09G2300/0819 G09G2300/0852<br>G09G2300/0861 G09G2320/029 G09G2320/043 G09G2320/045 |         |            |  |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.641.D G09G3/20.642.C G09G3/20.642.P G09G3/20.670.J G09F9/30.338 G09F9/30.365.Z H05B33/14.A         |         |            |  |

| 代理人(译)         | 伊藤忠彦<br>杉村健二<br>藤原英治                                                                                                                  |         |            |  |

| 优先权            | 1999023261 1999-10-02 GB                                                                                                              |         |            |  |

| 其他公开文献         | JP2003511724A                                                                                                                         |         |            |  |

| 外部链接           | <u>Espacenet</u>                                                                                                                      |         |            |  |

|                |                                                                                                                                       |         |            |  |

## 摘要(译)

在有源矩阵电致发光显示装置中,在驱动周期中通过每个像素(10)中的EL显示元件(20)的驱动电流由驱动装置(22)基于在先前寻址周期中施加到像素的驱动信号来控制。 并且作为电压存储在相关的存储电容器(36)上。 为了抵消显示元件老化的影响,对于给定的驱动信号电平,该元件的光输出将随着时间的流逝而逐渐减小,该像素包括响应电势差的反馈电路(40、45、47、48) 在驱动周期的初始部分中,在显示元件上的跨接点指示老化的程度,并且布置成相应地调节存储在存储电容上的电压。