(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2019-102768

(P2019-102768A)

(43) 公開日 令和1年6月24日(2019.6.24)

| (51) Int.Cl.                | F 1  |       |   | テーマコード (参考) |  |

|-----------------------------|------|-------|---|-------------|--|

| <b>H01L 51/50</b> (2006.01) | H05B | 33/22 | D | 3K107       |  |

| <b>H01L 27/32</b> (2006.01) | H01L | 27/32 |   | 5C094       |  |

| <b>H05B 33/12</b> (2006.01) | H05B | 33/14 | A |             |  |

| <b>G09F 9/30</b> (2006.01)  | H05B | 33/22 | B |             |  |

| <b>G09F 9/302</b> (2006.01) | H05B | 33/12 | B |             |  |

審査請求 未請求 請求項の数 16 O.L. (全 16 頁) 最終頁に続く

|           |                              |            |                                                                                                                                                              |

|-----------|------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2017-235890 (P2017-235890) | (71) 出願人   | 502356528<br>株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目7番1号                                                                                                               |

| (22) 出願日  | 平成29年12月8日 (2017.12.8)       | (74) 代理人   | 110000408<br>特許業務法人高橋・林アンドパートナーズ                                                                                                                             |

|           |                              | (72) 発明者   | 坂本 亜沙美<br>東京都港区西新橋三丁目7番1号 株式会<br>社ジャパンディスプレイ内                                                                                                                |

|           |                              | F ターム (参考) | 3K107 AA01 BB01 CC04 CC14 DD71<br>DD76 DD78 DD80 EE06 FF04<br>FF12 FF13 FF14 FF15 FF19<br>5C094 AA10 AA22 BA03 BA27 CA20<br>DA13 DB04 EA04 FB01 FB14<br>JA04 |

(54) 【発明の名称】 表示装置

(57) 【要約】

【課題】表示装置の発光効率を向上させて電力消費を軽減することを目的の1つとする。

【解決手段】サブ画素を複数備える画素を有し、複数のサブ画素のうちの少なくとも1つは複数の発光素子を有し、複数の発光素子は、発光効率がピークとなる電流密度の大きさが互いに異なる表示装置。複数の発光素子は第1の発光素子及び第2の発光素子を有し、第1の発光素子は、第1の画素電極と、第1の発光層と、第1の画素電極と第1の発光層との間に位置する第1の有機層と、を有し、第2の発光素子は、第2の画素電極と、第2の発光層と、第2の画素電極と第2の発光層との間に位置する第2の有機層と、を有し、第2の有機層のHOMO準位は、第1の有機層のHOMO準位よりも小さくてもよい。

### 【選択図】図 3

**【特許請求の範囲】****【請求項 1】**

サブ画素を複数備える画素を有する表示装置であって、

前記サブ画素のうちの少なくとも1つは、複数の発光素子を有し、

前記複数の発光素子は、発光効率がピークとなる電流密度の大きさが互いに異なる、表示装置。

**【請求項 2】**

前記複数の発光素子は第1の発光素子及び第2の発光素子を有し、

前記第1の発光素子は、第1の画素電極と、第1の発光層と、前記第1の画素電極と前記第1の発光層との間に位置する第1の有機層と、を有し、

前記第2の発光素子は、第2の画素電極と、第2の発光層と、前記第2の画素電極と前記第2の発光層との間に位置する第2の有機層と、を有し、

前記第2の有機層のHOMO準位は、前記第1の有機層のHOMO準位よりも小さい、請求項1に記載の表示装置。

**【請求項 3】**

前記第1の有機層は、前記第1の発光素子の第1の正孔注入層であり、

前記第2の有機層は、前記第2の発光素子の第2の正孔注入層である、請求項2に記載の表示装置。

**【請求項 4】**

前記画素は、基板の上に配置され、

前記第1の正孔注入層と前記第1の発光層との間に、第1の正孔輸送層が位置し、

前記第2の正孔注入層と前記第2の発光層との間に、第2の正孔輸送層が位置し、

前記第2の正孔輸送層は前記第1の正孔輸送層よりも、前記基板の主面に垂直な方向の正孔移動度が大きい、請求項3に記載の表示装置。

**【請求項 5】**

前記画素は、基板の上に配置され、

前記複数の発光素子は第1の発光素子及び第2の発光素子を有し、

前記第1の発光素子は、第1の画素電極と、第1の発光層と、前記第1の画素電極と前記第1の発光層との間に位置する第1の有機層と、を有し、

前記第2の発光素子は、第2の画素電極と、第2の発光層と、前記第2の画素電極と前記第2の発光層との間に位置する第2の有機層と、を有し、

前記第2の有機層は前記第1の有機層よりも、前記基板の主面に垂直な方向の正孔移動度が大きい、請求項1に記載の表示装置。

**【請求項 6】**

前記第1の有機層は、前記第1の発光素子の第1の正孔輸送層であり、

前記第2の有機層は、前記第2の発光素子の第2の正孔輸送層である、請求項5に記載の表示装置。

**【請求項 7】**

前記複数の発光素子は第1の発光素子及び第2の発光素子を有し、

前記第1の発光素子は、第1の画素電極と、第1の発光層と、第1の対向電極と、前記第1の対向電極と前記第1の発光層との間に位置する第3の有機層と、を有し、

前記第2の発光素子は、第2の画素電極と、第2の発光層と、第2の対向電極と、前記第2の対向電極と前記第2の発光層との間に位置する第4の有機層と、を有し、

前記第4の有機層は前記第3の有機層よりも、リチウム錯体の含有量が多い、請求項1に記載の表示装置。

**【請求項 8】**

前記第3の有機層は、前記第1の発光素子の第1の電子輸送層であり、

前記第4の有機層は、前記第2の発光素子の第2の電子輸送層である、請求項7に記載の表示装置。

**【請求項 9】**

10

20

30

40

50

前記リチウム錯体は、Liqである、請求項7又は請求項8に記載の表示装置。

【請求項10】

前記第1の発光素子は、前記第2の発光素子に入力される信号とは独立した信号が入力される、請求項2から請求項9のいずれか1項に記載の表示装置。

【請求項11】

前記第1の発光素子と前記第2の発光素子とは、共通の信号が入力される、請求項2から請求項9のいずれか1項に記載の表示装置。

【請求項12】

前記画素は、前記複数の発光素子を有する第1のサブ画素と、発光素子を1つのみ有する第2のサブ画素と、を含む、請求項1から請求項11のいずれか1項に記載の表示装置。

10

【請求項13】

前記第2のサブ画素が有する前記発光素子の発光領域は、前記第1のサブ画素が有する前記発光素子の発光領域よりも大きい、請求項12に記載の表示装置。

【請求項14】

前記画素は、第1の色を発する前記複数の発光素子を有する第1のサブ画素と、第2の色を発する前記複数の発光素子を有する第2のサブ画素と、第3の色を発する前記複数の発光素子を有する第3のサブ画素とを備え、

前記第1のサブ画素及び前記第2のサブ画素は直線状に配置され、

前記第3のサブ画素は、前記第1のサブ画素及び前記第2のサブ画素が配置される直線とは異なる位置に配置され、

前記第3のサブ画素が有する前記発光素子の発光領域は、前記第1のサブ画素及び前記第2のサブ画素が有する前記発光素子の発光領域よりも大きい、請求項1から請求項11のいずれか1項に記載の表示装置。

20

【請求項15】

前記第3の色は青色である、請求項14に記載の表示装置。

【請求項16】

前記画素は、第1の色を発する前記複数の発光素子を有する第1のサブ画素と、第2の色を発する前記複数の発光素子を有する第2のサブ画素と、第3の色を発する発光素子を1つのみ有する第3のサブ画素とを備え、

30

前記第1のサブ画素及び前記第2のサブ画素は直線状に配置され、

前記第3のサブ画素は、前記第1のサブ画素及び前記第2のサブ画素が配置される直線とは異なる位置に配置され、

前記第3のサブ画素が有する前記発光素子の発光領域は、前記第1のサブ画素及び前記第2のサブ画素が有する前記発光素子の発光領域よりも大きい、請求項1から請求項11のいずれか1項に記載の表示装置。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明の一実施形態は表示装置に関する。

40

【背景技術】

【0002】

有機EL素子は低電流密度域で発光効率が小さくなる場合がある。低電流密度域で十分な発光効率が得られないと、消費電力が大きくなってしまうという問題がある。例えば、低電流密度での発光、すなわち低輝度の画像表示を行う際に、発光効率が小さくなる分、当該輝度の発光に必要な電力が大きくなる。

【0003】

このような問題に対し、ある程度発光効率が大きい電流密度領域で発光を行い、発光期間の一部に黒画面を挿入して輝度を低下させ、低輝度の画像表示を行うという技術が知られている。しかし、例えば車載ディスプレイ等、ディスプレイが振動する環境で黒画面を

50

挿入すると、フリッカーが生じ画質を損なってしまうという問題がある。よって、黒画面を挿入する技術によって、上述の問題を十分に解決することは難しい。

【0004】

従来、有機EL表示装置において広い階調性を得るために、同系統の発光色の光を発光する2つのサブピクセルの単位電流当たりの発光効率を、一方のサブピクセルより他方のサブピクセルをより低くし、最小電流値を制御する手段が開示されている（例えば、特許文献1参照。）。

【先行技術文献】

【特許文献】

【0005】

10

【特許文献1】特開2008-225101号公報

【0006】

しかしながら、特許文献1に記載の手段では、発光効率が小さい低電流密度域の発光効率を改善することはできない。

【発明の概要】

【発明が解決しようとする課題】

【0007】

このような課題に鑑み、本発明の一実施形態は、表示装置の発光効率を向上させて電力消費を軽減することを目的の一つとする。

【課題を解決するための手段】

20

【0008】

本発明の一実施形態に係る表示装置は、サブ画素を複数備える画素を有する表示装置であって、前記複数のサブ画素のうちの少なくとも1つは複数の発光素子を有し、前記複数の発光素子は、発光効率がピークとなる電流密度の大きさが互いに異なる。

【図面の簡単な説明】

【0009】

【図1】本発明の第一実施形態に係る表示装置100の上面模式図である。

【図2】本発明の第一実施形態に係る表示装置の断面を示す図である。

【図3】本発明の第一実施形態に係る表示装置の断面を示す図である。

【図4】本発明の第一実施形態に係る表示装置の発光素子の断面を示す図である。

30

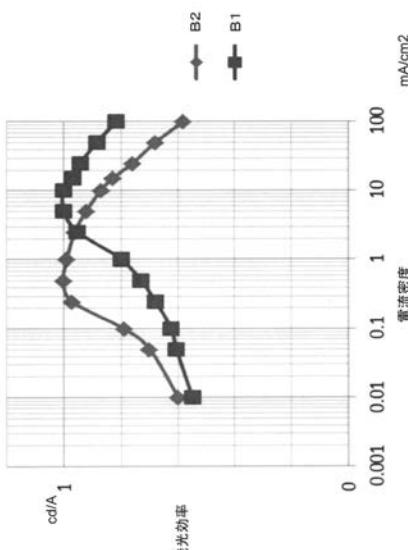

【図5】本発明の第一実施形態に係る表示装置の発光素子の発光効率と電流密度との関係を示す図である。

【図6】本発明の第二実施形態に係る表示装置の発光素子の断面を示す図である。

【図7】本発明の第二実施形態に係る表示装置の発光素子の発光効率と電流密度との関係を示す図である。

【図8】本発明の変形例1に係る表示装置の断面を示す図である。

【図9】本発明の変形例2に係る表示装置の画素の構成を示す図である。

【図10】本発明の変形例3に係る表示装置の画素の構成を示す図である。

【発明を実施するための形態】

【0010】

40

以下、本発明の実施の形態を、図面等を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、以下に例示する実施の形態の記載内容に限定して解釈されるものではない。図面は説明をより明確にするため、実際の態様に比べ、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同様の要素には、同一の符号（又は数字の後にa、bなどを付した符号）を付して、詳細な説明を適宜省略することがある。さらに各要素に対する「第1」、「第2」と付記された文字は、各要素を区別するために用いられる便宜的な標識であり、特段の説明がない限りそれ以上の意味を有さない。

【0011】

50

本明細書において、ある部材又は領域が他の部材又は領域の「上に（又は下に）」あるとする場合、特段の限定がない限りこれは他の部材又は領域の直上（又は直下）にある場合のみでなく他の部材又は領域の上方（又は下方）にある場合を含み、すなわち、他の部材又は領域の上方（又は下方）において間に別の構成要素が含まれている場合も含む。なお、以下の説明では、特に断りのない限り、断面図においては、基板に対して第1フィルムが配置される側を「上」又は「上方」といい、その逆を「下」又は「下方」として説明する。

【0012】

（第一実施形態）

<表示装置の構成>

10

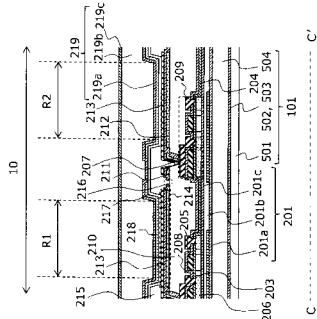

図1は、本発明の第一実施形態に係る表示装置100の上面模式図である。

【0013】

表示装置100は基板101を有し、その一表面上に、所望の形状にパターニングされた種々の導電層、半導体層、絶縁層、発光層を有する。これらの導電層、半導体層、絶縁層により、薄膜トランジスタ（あるいは画素回路）や発光素子が形成される。さらに、薄膜トランジスタや発光素子を備える複数の画素103が形成される。また、複数の画素103を駆動するためのゲート駆動回路104（走査信号駆動回路ともいう）、ソース駆動回路105（映像信号駆動回路ともいう）は、前述の導電層、半導体層、絶縁層を用いて複数の画素103が備える画素回路と同時に基板101上に形成されても良いし、ICを基板101の一表面上に実装しても良い。複数の画素103は例えばマトリクス状に配置され、これらの集合によって表示領域102が形成される。

20

【0014】

ゲート駆動回路104やソース駆動回路105は、表示領域102の外側の周辺領域に配置される。表示領域102、ゲート駆動回路104、及びソース駆動回路105からは、パターニングされた導電層で形成される種々の配線（図示せず）が基板101の一辺へ延び、それぞれの配線は基板101の端部付近に配置された端子106の一に接続される。これらの端子は、FPC（Flexible Printed Circuit、フレキシブルプリント回路基板）107と接続される。前述の駆動回路をICによって設ける場合には、基板101上ではなくFPC107上に実装しても良い。

30

【0015】

表示装置の外部のコントローラ（図示せず）から、FPC107を介して映像信号や各種制御信号が供給され、映像信号はソース駆動回路105によって処理されて複数の画素103に入力される。各種制御信号は、ゲート駆動回路104、及びソース駆動回路105に入力される。

【0016】

映像信号や各種制御信号の他、ゲート駆動回路104、ソース駆動回路105、及び複数の画素103を駆動するための電力が表示装置100に供給される。

【0017】

複数の画素103はそれぞれ複数のサブ画素10を有し、複数のサブ画素10のそれぞれは1つ又は複数の発光素子を有する。表示装置100に供給された電力の一部は、複数の発光素子のそれぞれに供給されて発光素子を発光させる。

40

【0018】

本発明の第一実施形態の表示装置100のサブ画素10のそれぞれは赤色を発する発光素子R1, R2を有する第1のサブ画素と、緑色を発する発光素子G1, G2を有する第2のサブ画素と、青色を発する発光素子B1, B2を有する第3のサブ画素とを備える。以下では第1から第3サブ画素の一つを例に挙げて説明することもあるが、この説明は、他の色を発するサブ画素にも共通する。

【0019】

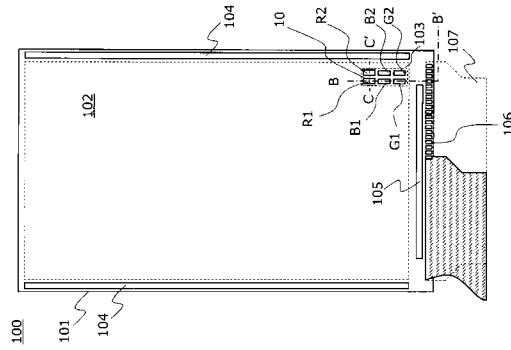

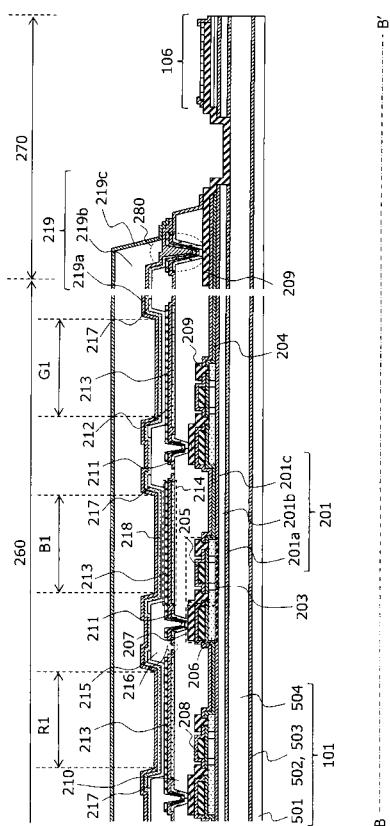

図2は、本発明の第一実施形態に係る表示装置を示す断面図である。

【0020】

50

図2は、図1における表示装置100の、B-B'断面構造を模式的に表したものである。図2は、表示領域260と周辺領域270の断面構造を併記している。図2は、主に図1に示す画素103（あるいは画素回路）を構成するNチャネル型の薄膜トランジスタ（以下、「TFT」ともいう。また、TFTがNチャネル型である場合には「NchTFT」といい、Pチャネル型である場合には「PchTFT」ということもある）を含む表示領域260（図1に示す表示領域102）について示している。

#### 【0021】

第1樹脂層501、第1無機絶縁層502、第2無機絶縁層503、第2樹脂層504を含む積層構造を有する基板101上に、アンダーコート層201としてシリコン酸化膜201a、シリコン窒化膜201b、シリコン酸化膜201cの三層積層構造を設けている。最下層のシリコン酸化膜201aは基板101との密着性向上のため、中層のシリコン窒化膜201bは、外部からの水分及び不純物のブロック膜として、最上層のシリコン酸化膜201cは、シリコン窒化膜201b中に含有する水素原子が後述する半導体層側に拡散しないようにするブロック膜として、それぞれ設けられるが、特にこの構造に限定するものではない。基板101上には、さらに積層があっても良いし、単層あるいは二層積層としても良い。

#### 【0022】

アンダーコート層201上には、TFT203が形成される。TFT203としてはポリシリコン206を具備するポリシリコンTFTを例とし、ここではNchTFTのみ示しているが、PchTFTを同時に形成しても良い。ポリシリコン206は、例えば低温ポリシリコン（LTPS）である。TFT203は酸化物半導体を用いて形成してもよい。NchTFTは、チャネル領域とソース・ドレイン領域との間に、低濃度不純物領域を設けた構造を取る。ゲート絶縁膜204としてはここではシリコン酸化膜を用い、ゲート電極205はMoW膜（第1配線層）としている。第1配線層は、TFT203のゲート電極205に加え、保持容量線を形成し、ポリシリコン206との間で、保持容量（Cs）207の形成にも用いられる。

#### 【0023】

TFT203上に、層間絶縁膜208となるシリコン窒化膜又はシリコン酸化膜をそれぞれ積層し、その後パターニングを行って、ポリシリコン206等に達するコンタクトホールを形成する。さらに、層間絶縁膜208の除去によって、アンダーコート層201が露出するので、これもパターニングを行って除去する。アンダーコート層201を除去すると、基板101を構成する第2樹脂層504が露出する。またこのとき、特に図示しないが、アンダーコート層201のエッティングを通じて、第2樹脂層504の表面が一部浸食されて膜減りを生ずる場合がある。

#### 【0024】

さらにソース・ドレイン電極及び引き回し配線となる導電層（第2配線層）209を形成する。ここでは、Ti、Al、Tiの三層積層構造を採用した。層間絶縁膜208、TFT203のゲート電極204と同層の導電層（第2配線層）で形成される電極、およびTFTのソース・ドレイン配線と同層の導電層で形成される電極とで、保持容量（Cs）207の一部が形成される。引き回し配線は、基板周縁の端部まで延在され、後にFPC107を接続する端子106を形成する。端子106は、ゲート電極205を形成する第1配線層と同層で形成されてもよい。

#### 【0025】

その後、TFT203及び引き回し配線を覆うように平坦化膜210を形成する。平坦化膜としては感光性アクリルやポリイミド等の有機材料が多く用いられる。CVD等により形成される無機絶縁材料に比べ、表面の平坦性に優れる。

#### 【0026】

平坦化膜210は、画素コンタクト部、及び周辺領域270の一部では除去される。平坦化膜の除去により導電層209が露出した箇所は、一旦、透明導電膜211にて被覆される。透明導電膜211としては、例えば、ITO（Indium tin oxide）

10

20

30

40

50

)が用いられる。透明導電膜211上は一旦、シリコン窒化膜212で被覆され、画素コンタクト部を再び開口する。さらに、シリコン窒化膜212の上に画素電極となる導電層213を形成する。ここでは、画素電極は反射電極として形成され、IZO、Ag、IZOの三層積層構造としている。画素部においては、透明導電膜211の導電層213と重なる部分、シリコン窒化膜212、導電層213によって付加容量(Cad)214が形成される。一方、透明導電膜211は端子106の表面にも形成される。端子106上の透明導電膜は、以後の工程で配線露出部がダメージを負わないようにバリア膜として設けることを目的の一としている。

#### 【0027】

ところで、画素電極(導電層213)のパターニング時、一部において透明導電膜211がエッチング環境にさらされるが、透明導電膜211の形成から導電層213の形成までの間に行われるアニール処理によって、透明導電膜211は導電層213のエッチングに対し十分な耐性を有する。

#### 【0028】

画素電極形成後、バンク(リブ)215と呼ばれる、サブ画素10の隔壁となる絶縁層を形成する。つまり、バンク215は、複数のサブ画素10を区分している。バンク215としては平坦化膜210と同じく感光性アクリルやポリイミド等の有機材料が用いられる。バンク215は、画素電極表面を発光領域として露出するように開口され、その開口端はなだらかなテーパー形状となるのが好ましい。開口端が急峻な形状になっていると、後で形成される有機層のカバレッジ不良を生ずる。

#### 【0029】

ここで、平坦化膜210とバンク215は、両者の間のシリコン窒化膜212に設けた開口216を通じて接触させている部位を有する。これは、バンク形成後の熱処理等を通じて、平坦化膜210から脱離する水分やガスを、バンク215を通じて引き抜くための開口部である。ここで脱離する水分やガスとは、前述した基板101の形成時に、第1樹脂層501や第2樹脂層504から脱離するものと同じ現象であり、開口216を通じて平坦化膜210からバンク215に引き抜くことで、平坦化膜210とシリコン窒化膜212との界面の剥離を抑制することができる。

#### 【0030】

バンク215形成後、有機EL層を構成する有機層217を積層形成する。図2では有機層217を単層の様に記載しているが、画素電極側から順に、正孔注入層、正孔輸送層、電子プロッキング層、発光層、ホールプロッキング層、電子輸送層、電子注入層を積層形成する。これらの層は、蒸着による形成であっても良いし、溶媒分散の上の塗布形成であっても良い。また、図2に示すように、有機層217は、各発光素子に対して選択的に形成しても良いし、表示領域260を覆う全面に、すなわち複数のサブ画素10に跨って形成されても良い。有機層217のうち、発光層を含む幾つかの層を各発光素子に対して選択的に形成し、残りの層を複数のサブ画素10に跨って形成してもよい。発光層を複数のサブ画素10に跨って形成する場合は、全画素(全サブ画素)において白色発光を得て、カラーフィルタ(図示せず)によって所望の色波長部分を取り出す構成とができる。

#### 【0031】

有機層217の形成後、対向電極218を形成する。ここでは、トップエミッション構造としているため、対向電極218は光透過性とする必要がある。なお、トップエミッション構造とは、基板101上に、有機層217を挟んで配置される対向電極218から光を射出する構造をいう。ここでは、対向電極218として、MgAg膜を、有機EL層からの射出光が透過する程度の薄膜として形成する。前述の有機層217の形成順序に従うと、画素電極側が陽極となり、対向電極側が陰極となる。対向電極218は、表示領域260上から周辺領域270に設けられた陰極コンタクト部280に亘って形成され、陰極コンタクト部280で下層の導電層209と接続され、最終的には端子106に引き出される。対向電極218には、陰極コンタクト部280で導電層209から陰極電圧が供給

10

20

30

40

50

される。

【0032】

対向電極の形成後、封止層219を形成する。封止層219は、先に形成した有機層を、外部からの水分侵入を防止することを機能の一としており、封止層としてはガスバリア性の高いものが要求される。ここでは、封止層219として、シリコン窒化膜を含む積層構造として、シリコン窒化膜219a、有機樹脂219b、シリコン窒化膜219cの積層される構造を示す。なお、特に図示しないが、シリコン窒化膜219aと有機樹脂219bとの間には、密着性向上を目的の一として、アモルファスシリコン層を設けても良い。

【0033】

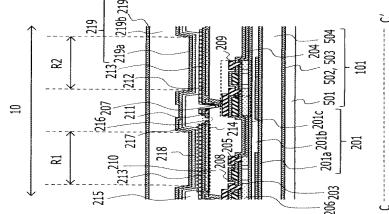

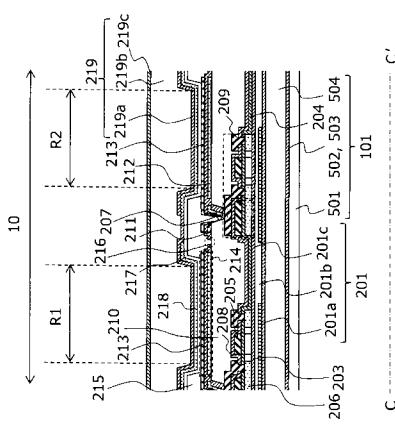

図3は、本発明の第一実施形態に係る表示装置の断面を示す図である。図3は、図1における表示装置100の、C-C'断面構造を模式的に表したものである。

【0034】

本発明の第一実施形態に係る表示装置のサブ画素10は複数の発光素子を有する。図3には、赤色を発する発光素子R1及びR2を有するサブ画素10を示している。発光素子R1の画素電極(導電層213)に接続するTFT203と、発光素子R2の画素電極(導電層213)に接続するTFT203とが、別々に配置されている。発光素子R1及び発光素子R2は独立した信号により駆動される。例えば、発光素子R1及びR2を有するサブ画素10へ入力される映像信号の階調に応じて、発光素子R1と発光素子R2とのどちらを発光させるか選択する。また、図3に示す2つのTFT203へ、同じ映像信号を同時に供給してもよい。緑色を発する発光素子G1及びG2を有するサブ画素10及び青色を発する発光素子B1及びB2を有するサブ画素10も、発光素子R1及びR2を有するサブ画素10と同様に形成される。

【0035】

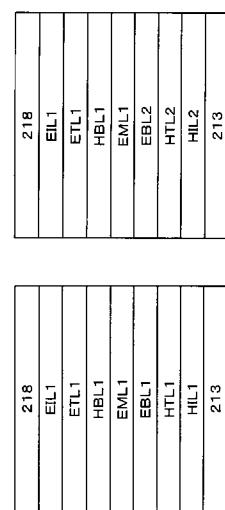

図4は、本発明の第一実施形態に係る表示装置の発光素子の積層構造を示す模式図である。

【0036】

図4に示すように、サブ画素10が有する2つの発光素子の一方(例えばB1)は、画素電極(導電層213)側から順に、正孔注入層HIL1、正孔輸送層HTL1、電子プロッキング層EBL1、発光層EML1、ホールプロッキング層HBL1、電子輸送層ETL1、電子注入層EIL1、対向電極218を積層して形成する。

【0037】

正孔注入層HIL1には、フタロシアニン(H<sub>2</sub>Pc)、銅(II)フタロシアニン(略称:CuPc)、バナジルフタロシアニン(VOPc)、4,4',4'''-トリス(N,N-ジフェニルアミノ)トリフェニルアミン(TDATA)、4,4',4'''-トリス[N-(3-メチルフェニル)-N-フェニルアミノ]トリフェニルアミン(MTDA)、4,4'-ビス[N-(4-ジフェニルアミノフェニル)-N-フェニルアミノ]ビフェニル(DPAB)、4,4'-ビス(N-{4-[N'-(3-メチルフェニル)-N-フェニルアミノ]フェニル}-N-フェニルアミノ)ビフェニル(DNTPD)、3-[N-(1-ナフチル)-N-(9-フェニルカルバゾール-3-イル)アミノ]-9-フェニルカルバゾール(PCzPCN1)、2,3,6,7,10,11-ヘキサシアノ-1,4,5,8,9,12-ヘキサアザトリフェニレン(HAT-CN)、ポリエチレンジオキシチオフェン-ポリスチレンスルホン酸(PEDOT-PSS)等から選ばれたいずれか一種を用いることができる。

【0038】

正孔輸送層HTL1には、例えば、4,4'-ビス[N-(ナフチル)-N-フェニルアミノ]ビフェニル(-NPD)、N,N'-ビス(3-メチルフェニル)-(1,1'-ビフェニル)-4,4'-ジアミン(TPD)、2-TNATA、4,4',4''-トリス(N-(3-メチルフェニル)N-フェニルアミノ)トリフェニルアミン(MTDA)、4,4'-ビス[N-(9,9-ジメチルフルオレン-2-イル)-N-フ

エニルアミノ]ビフェニル(DFLDPBi)、4,4'-ビス[N-(スピロ-9,9'-ビフルオレン-2-イル)-N-フェニルアミノ]ビフェニル(BSPB)から選ばれたいずれか一種を用いることができる。

#### 【0039】

電子ブロッキング層EBL1の材料としては、例えば、芳香族アミン誘導体、カルバゾール誘導体、9,10-ジヒドロアクリジン誘導体、ベンゾフラン誘導体、ベンゾチオフェン誘導体などを使用することができる。

#### 【0040】

発光層EML1は、ホスト材料とゲスト材料を組み合わせて形成することができる。ホスト材料とゲスト材料の組み合わせを用いると、励起状態のホスト分子のエネルギーがゲスト分子へ移動してゲスト分子がエネルギーを放出して発光する。ホスト化合物として、電子輸送材料、正孔輸送材料を用いることができる。例えば、Alq3等のキノリノール金属錯体に4-ジシアノメチレン-2-メチル-6-(p-ジメチルアミノスチリル)-4H-ピラン(DCM)、4-(ジシアノメチレン)-2-t-ブチル-6-(1,1,7,7-テトラメチルユロリジル-9-エニル)-4H-ピラン(DCJTB)等のピラン系誘導体、2,3-キナクリドン等のキナクリドン誘導体や、3-(2'-ベンゾチアゾール)-7-ジエチルアミノクマリン等のクマリン誘導体をドープしたもの、ビス(2-メチル-8-ヒドロキシキノリン)-4-フェニルフェノール-アルミニウム錯体に、ペリレン等の縮合多環芳香族をドープしたもの、あるいは4,4'-ビス(m-トリルフェニルアミノ)ビフェニル(TPD)にルブレン等をドープしたもの、4,4'-ビスカルバゾリルビフェニル(CBP)、4,4'-ビス(9-カルバゾリル)-2,2'-ジメチルビフェニル(CDBP)等のカルバゾール系化合物に、トリス-(2フェリニルピリジン)イリジウム(Ir(ppy)3)(緑色)、ビス(4,6-ジ-フルオロフェニル)-ピリジネート-N,C2)イリジウム(ピコリネート)(FIr(pic))(青色)、ビス(2-2'-ベンゾチエニル)-ピリジネート-N,C3イリジウム(アセチルアセトネート)(Btp2Ir(acac))(赤色)、トリス-(ピコリネート)イリジウム(Ir(pic)3)(赤色)、ビス(2-フェニルベンゾチオゾラト-N,C2)イリジウム(アセチルアセトネート)(Bt2Ir(acac))(黄色)等のイリジウム錯体や白金錯体をドープしたもの等が用いられる。

#### 【0041】

ホールブロッキング層HBL1は、4,4'-N,N'-ジカルボゾールビフェニル(CBP:4,4'-N,N'-dicarbozole-biphenyl)や、2,9-ジメチル-4,7-ジフェニル-1,10-フェナントロリン(BCP:2,9-dimethyl-4,7-diphenyl-1,10-phenanthroline)を使用することができる。

#### 【0042】

電子輸送層ETL1は、2,4-ビス(4-ビフェニル)-6-(4'-(2-ピリジル)-4-ジフェニル)-[1,3,5]トリアジン(MPT:2,4-bis(4-biphenyl)-6-(4'-(2-Pyridinyl)-4-biphenyl)-[1,3,5]triazine)にリチウムを5体積%加えたものを使用することができる。

#### 【0043】

電子注入層EIL1は、8-ヒドロキシキノリンアルミニウム(Alq3)、8-ヒドロキシメチルキノリンアルミニウム、アントラセン、ナフタレン、フェナントレン、ピレン、クリセン、ペリレン、ブタジエン、クマリン、アクリジン、スチルベン、又はこれらの誘導体等を使用することができる。

#### 【0044】

サブ画素10が有する2つの発光素子の他方(例えばB2)は、画素電極(導電層213)側から順に、正孔注入層HIL2、正孔輸送層HTL2、電子ブロッキング層EBL2、発光層EML1、ホールブロッキング層HBL1、電子輸送層ETL1、電子注入層

10

20

30

40

50

E I L 1、対向電極 2 1 8 を積層して形成する。すなわち、発光素子 B 1 と発光素子 B 2 とでは、正孔注入層、正孔輸送層、電子プロッキング層の構成が異なっている。

【0045】

本発明の第一実施形態では、図 4 に示す発光素子 B 1 と発光素子 B 2 とで、発光効率のピークとなる電流密度の大きさが異なるようにしている。発光効率のピークとなる電流密度の大きさ（後述する図 5 における発光効率のピーク位置）は、キャリアバランス（注入された正孔と電子のバランス）に依存する。キャリアバランスの調整手段としては、各電荷注入・輸送層（正孔注入層、正孔輸送層、電子注入層、電子輸送層）へのドーピングする材料の選択及び調整や、各電荷注入・輸送層の HOMO 準位および LUMO 準位の調整、各電荷注入・輸送層の移動度の調整などが挙げられる。

10

【0046】

図 4 に示す発光素子 B 1 と発光素子 B 2 とでは、発光素子 B 1 よりも低電流密度域で正孔と電子の再結合が生じるよう、発光素子 B 2 の発光層への正孔注入性を高めている。具体的には、発光素子 B 2 の正孔注入層 H I L 2（画素電極と発光層との間に位置する有機層ともいえる）の HOMO 準位が発光素子 B 1 の正孔注入層 H I L 1 の HOMO 準位よりも小さい。これにより、正孔注入層 H I L 2 の方が正孔注入層 H I L 1 よりも、画素電極（導電層 2 1 3）の仕事関数とのエネルギーギャップ差が小さくなり、正孔が注入しやすくなる。本発明の第一実施形態では、正孔注入層 H I L 2 の HOMO 準位は 5.5 eV 以下であり、正孔注入層 H I L 1 の HOMO 準位は 5.6 eV 以上である。

20

【0047】

また、正孔輸送層 H T L 2（画素電極と発光層との間に位置する有機層ともいえる）の方が正孔輸送層 H T L 1 よりも、基板 1 0 1 の正面に垂直な方向の正孔移動度が大きい。これにより、正孔輸送層 H T L 2 の方が正孔輸送層 H T L 1 よりも、発光層へ正孔を輸送しやすくなる。

【0048】

図 5 は、本発明の第一実施形態に係る表示装置の発光素子の発光効率と電流密度との関係を示す図である。図 5 において、画素電極（導電層 2 1 3）は ITO、対向電極 2 1 8 は MgAg である。図 5 を参照すると、本発明の第一実施形態に係る表示装置のサブ画素 1 0 の発光素子 B 2 の発光効率（cd/A）は、電流密度が約 0.1 mA/cm<sup>2</sup> のときにピークに達する。他方、発光素子 B 1 の発光効率（cd/A）は、電流密度が約 1.0 mA/cm<sup>2</sup> のときにピークに達する。このように、発光素子 B 1 と発光素子 B 2 とで発光効率のピークとなる電流密度の大きさがずれるようにする。すなわち、発光素子 B 1 及び発光素子 B 2 の発光効率のピークとなる電流密度の大きさを互いに異ならせ、発光素子 B 2 の発光効率（cd/A）のピークが、発光素子 B 1 の発光効率（cd/A）のピークよりも小さい電流密度（mA/cm<sup>2</sup>）の領域にくるようにする。

30

【0049】

本発明の第 1 実施形態に係る表示装置においては、発光素子 B 1 及び発光素子 B 2 を以上のように構成することで、電流密度が小さいときは主に発光素子 B 2 が発光し、大きいときは主に発光素子 B 1 が発光するので、電流密度が小さいときも発光効率を高く保つことができ、表示装置の発光効率を向上させて電力消費を軽減することができる。

40

【0050】

また、本発明の第 1 実施形態に係る表示装置においては、発光素子 B 1 及び発光素子 B 2 が独立した信号により駆動されるので、どちらの発光素子へ信号を入力するかを選択することや、それぞれの発光素子に異なる信号を入力することが可能となる。よって、映像、電流密度、低消費電力モードのオンオフ等に応じて複数の発光素子への信号の入力の有無や入力する信号の内容を異ならせることができるので、表示装置の発光効率を向上させて電力消費を軽減することができる。

【0051】

（第二実施形態）

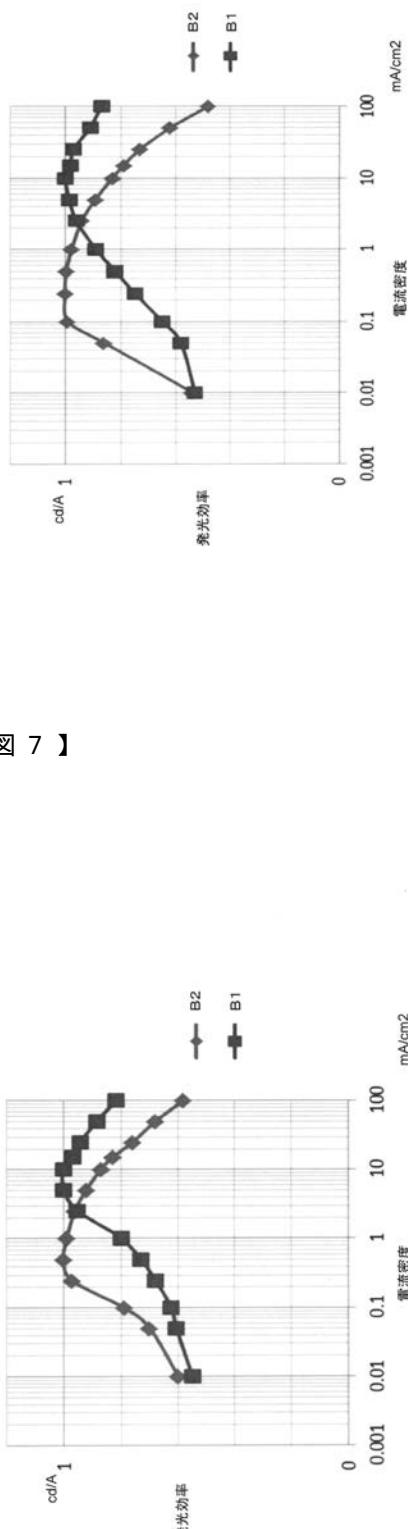

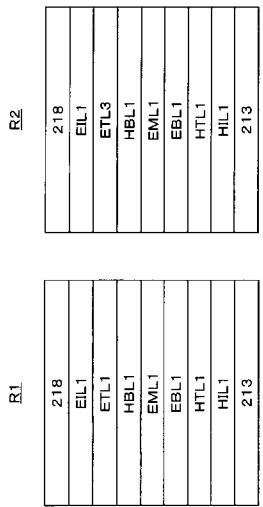

図 6 は、本発明の第二実施形態に係る表示装置の発光素子の断面を示す図である。本発

50

明の第二実施形態に係る表示装置の発光素子 B 1 は、本発明の第一実施形態に係る表示装置における発光素子 B 1 と同様である。

【 0 0 5 2 】

本発明の第二実施形態に係る表示装置の発光素子 B 2 は、画素電極（導電層 2 1 3）側から順に、正孔注入層 H I L 1、正孔輸送層 H T L 1、電子ブロッキング層 E B L 1、発光層 E M L 1、ホールブロッキング層 H B L 1、電子輸送層 E T L 3、電子注入層 E I L 1、対向電極 2 1 8 を積層して形成する。すなわち、本発明の第二実施形態に係る表示装置における発光素子 B 1 と発光素子 B 2 とでは、電子輸送層の構成が異なっている。

【 0 0 5 3 】

本発明の第二実施形態に係る表示装置の電子輸送層 E T L 3 には添加物がドーピングされる。電子輸送層 E T L 3（対向電極と発光層との間に位置する有機層ともいえる）には共蒸着により、例えば、リチウム錯体が添加される。換言すれば、発光素子 B 2 の電子輸送層 E T L 3 の方が発光素子 B 1 の電子輸送層 E T L 1 よりも、リチウム錯体の含有量が多い。本発明の第二実施形態の電子輸送層 E T L 3 には、リチウムキノラート錯体の 1 つである 8 - ヒドロキシキノラート - リチウム (Liq) が添加される。

10

【 0 0 5 4 】

図 7 は、本発明の第一実施形態に係る表示装置の発光素子の発光効率と電流密度との関係を示す図である。図 7 において、画素電極（導電層 2 1 3）は I T O、対向電極 2 1 8 は M g A g である

20

【 0 0 5 5 】

本発明の第二実施形態に係る表示装置の発光素子 B 2 の発光効率 (cd / A) は、電流密度が約 0.5 mA / cm<sup>2</sup> のときにピークに達する。他方、発光素子 B 1 の発光効率 (cd / A) は、電流密度が約 7 mA / cm<sup>2</sup> のときにピークに達する。このように、発光素子 B 1 と発光素子 B 2 とで発光効率のピークとなる電流密度の大きさがずれるようにする。すなわち、発光素子 B 1 及び発光素子 B 2 の発光効率のピークとなる電流密度の大きさを互いに異ならせ、発光素子 B 2 の発光効率 (cd / A) のピークが、発光素子 B 1 の発光効率 (cd / A) のピークよりも小さい電流密度 (mA / cm<sup>2</sup>) の領域にくるようとする。

30

【 0 0 5 6 】

本発明の第二実施形態に係る表示装置においては、発光 B 1 及び発光素子 B 2 を以上のように構成することで、電流密度が小さいときは主に発光素子 B 2 が発光し、大きいときは主に発光素子 B 1 が発光するので、電流密度が小さいときも発光効率を高く保つことができ、表示装置の発光効率を向上させて電力消費を軽減することができる。

【 0 0 5 7 】

(変形例 1)

図 8 は、本発明の変形例 1 に係る表示装置の断面を示す図である。

【 0 0 5 8 】

本発明の変形例 1 に係る表示装置では、発光素子 R 1 と発光素子 R 2 とは共通の信号により駆動される。すなわち、本発明の変形例 1 に係る表示装置では、画素電極（導電層 2 1 3）が発光素子 R 1 と発光素子 R 2 とで共通に用いられる。

40

【 0 0 5 9 】

本発明の変形例 1 に係る表示装置はこのような構成を有することでより容易に製造することができるので、製造工程の手間を省くことができる。

【 0 0 6 0 】

(変形例 2)

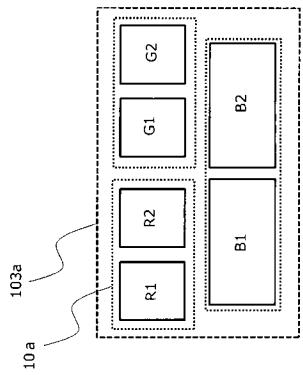

図 9 は、本発明の変形例 2 に係る表示装置の画素の構成を示す図である。

【 0 0 6 1 】

本発明の変形例 2 に係る表示装置の画素 1 0 3 a は、発光素子 R 1、R 2 を含むサブ画素 1 0 a 及び発光素子 G 1、G 2 を含むサブ画素 1 0 a が直線状に配置されて形成される。発光素子 B 1 及び B 2 を含むサブ画素 1 0 a は、発光素子 R 1、R 2 を含むサブ画素 1

50

0 a 及び発光素子 G 1、G 2 を含むサブ画素 10 a が配置される直線とは異なる直線上に配置される。また、発光素子 B 1 及び B 2 は、発光素子 R 1、R 2 及び発光素子 G 1、G 2 よりも大きな面積を有するように、詳述すれば大きな面積の発光領域を有するように形成される。

#### 【 0 0 6 2 】

一般的に、赤色の発光素子及び緑色の発光素子よりも青色の発光本の方が、発光効率が低い。本発明の変形例 2 に係る表示装置は、青色の発光素子 B 1、B 2 の面積を大きくして、青色の発光素子 B 1、B 2 の低い発光効率を補完している。なお、他の色の発光素子よりも大きい面積を有する発光素子の色は青色に限定されず、青以外の色であってもよい。

10

#### 【 0 0 6 3 】

##### (変形例 3 )

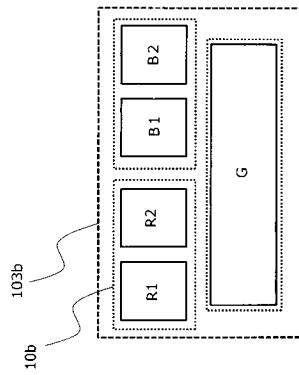

図 10 は、本発明の変形例 3 に係る表示装置の画素の構成を示す図である。

#### 【 0 0 6 4 】

本発明の変形例 3 に係る表示装置の画素 103 b は、発光素子 R 1、R 2 を含むサブ画素 10 b 及び発光素子 B 1、B 2 を含むサブ画素 10 b が直線状に配置されており、緑色の光を発する発光素子は 1 つの発光素子 G で構成される。発光素子 G で構成されるサブ画素 10 b は、発光素子 R 1、R 2 を含むサブ画素 10 b 及び発光素子 B 1、B 2 を含むサブ画素 10 b が配置される直線とは異なる直線上に配置される。また、発光素子 G は、発光素子 R 1、R 2 及び発光素子 G 1、G 2 よりも大きな面積を有するように形成される。

20

#### 【 0 0 6 5 】

画素 103 b が所定の輝度の白色を表示する際、赤色、緑色、青色のサブ画素 10 b は全て発光する。このとき、緑色のサブ画素 10 b の輝度が、赤色、青色のサブ画素 10 b の輝度よりも高い。本発明の変形例 3 に係る表示装置は、画像表示において他の色よりも高輝度で発光させることが頻出である緑色の発光素子 G の面積を大きくして、高輝度での発光に好適な構成にしている。また、全てのサブ画素 10 b に複数の発光素子を形成せず、1 つの発光素子からなるサブ画素 10 b を設けるので、より容易に製造することができ、製造工程の手間を省くことができる。1 つの発光素子からなるサブ画素 10 b は緑色に限定されず、緑以外の色であってもよい。また、画素 103 a が、2 つ以上の発光素子を備えるサブ画素 10 a を 1 つのみ有する構成にしてもよい。

30

#### 【 符号の説明 】

#### 【 0 0 6 6 】

R 1、R 2、G 1、G 2、B 1、B 2：発光素子、10、10 a、10 b：サブ画素、100：表示装置、101：基板、102：表示領域、103、103 a、103 b：画素、104：ゲート駆動回路、105：ソース駆動回路、106：端子、107：FPC、501：第 1 樹脂層、502：第 1 無機絶縁層、503：第 2 無機絶縁層、504：第 2 樹脂層、201：アンダーコート層、203：TFT、204：ゲート絶縁膜、205：ゲート電極、206：ポリシリコン、207：保持容量 (Cs)、208：層間絶縁膜、209：導電層、210：平坦化膜、211：透明導電膜、212：シリコン窒化膜、213：導電層、214：附加容量 (Cap)、215：バンク、216：開口、217：有機層、218：対向電極、219：封止層、260：表示領域、270：周辺領域、280：陰極コンタクト部

40

【 図 1 】

【 図 2 】

【 図 3 】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

|              |        |            |

|--------------|--------|------------|

| (51) Int.Cl. | F I    | テーマコード(参考) |

|              | G 09 F | 9/30 365   |

|              | G 09 F | 9/302 C    |

|                |                                                                                                                                                                                                                                                                                               |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <u>JP2019102768A</u>                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2019-06-24 |

| 申请号            | JP2017235890                                                                                                                                                                                                                                                                                  | 申请日     | 2017-12-08 |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 有限公司日本显示器                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 坂本亜沙美                                                                                                                                                                                                                                                                                         |         |            |

| 发明人            | 坂本 亜沙美                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | H01L51/50 H01L27/32 H05B33/12 G09F9/30 G09F9/302                                                                                                                                                                                                                                              |         |            |

| CPC分类号         | H01L27/3211 H01L27/3216 H01L27/3218 H01L27/3244 H01L51/5004 H01L51/5056 H01L51/5076 H01L51/5088 H01L51/5012 H01L51/5072 H01L51/5096 H01L2251/552                                                                                                                                              |         |            |

| FI分类号          | H05B33/22.D H01L27/32 H05B33/14.A H05B33/22.B H05B33/12.B G09F9/30.365 G09F9/302.C                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC04 3K107/CC14 3K107/DD71 3K107/DD76 3K107/DD78 3K107/DD80 3K107/EE06 3K107/FF04 3K107/FF12 3K107/FF13 3K107/FF14 3K107/FF15 3K107/FF19 5C094/AA10 5C094/AA22 5C094/BA03 5C094/BA27 5C094/CA20 5C094/DA13 5C094/DB04 5C094/EA04 5C094/FB01 5C094/FB14 5C094/JA04 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                     |         |            |

## 摘要(译)

一个目的是提高显示装置的发光效率以降低功耗。解决方案：存在具有多个子像素的像素，所述多个子像素中的至少一个具有多个发光元件，并且所述多个发光元件具有发光效率达到峰值的电流密度。有不同的显示设备。所述多个发光元件具有第一发光元件和第二发光元件，并且所述第一发光元件包括第一像素电极，第一发光层，第一像素电极和第一发光元件。并且第二有机发光元件设置在发光层和发光层之间，其中第二发光元件包括第二像素电极，第二发光层，第二像素电极和第二发光元件。第二有机层的HOMO能级可以低于第一有机层的HOMO能级。[选中图]图3