(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-317384

(P2007-317384A)

(43) 公開日 平成19年12月6日(2007.12.6)

|                             |                              |                                                                                          |

|-----------------------------|------------------------------|------------------------------------------------------------------------------------------|

| (51) Int.C1.                | F 1                          | テーマコード (参考)                                                                              |

| <b>H05B 33/10</b> (2006.01) | H05B 33/10                   | 3K107                                                                                    |

| <b>H05B 33/12</b> (2006.01) | H05B 33/12                   | Z 5C094                                                                                  |

| <b>H01L 51/50</b> (2006.01) | H05B 33/14                   | A 5G435                                                                                  |

| <b>G09F 9/00</b> (2006.01)  | G09F 9/00                    | 352                                                                                      |

| <b>G09F 9/30</b> (2006.01)  | G09F 9/30                    | 365Z                                                                                     |

|                             | 審査請求 未請求 請求項の数 24            | O L (全 32 頁) 最終頁に続く                                                                      |

| (21) 出願番号                   | 特願2006-142738 (P2006-142738) | (71) 出願人 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号                                      |

| (22) 出願日                    | 平成18年5月23日 (2006.5.23)       | (74) 代理人 100065385<br>弁理士 山下 橋平                                                          |

|                             |                              | (74) 代理人 100122921<br>弁理士 志村 博                                                           |

|                             |                              | (74) 代理人 100130029<br>弁理士 永井 道雄                                                          |

|                             |                              | (72) 発明者 永山 耕平<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内                                        |

|                             |                              | F ターム (参考) 3K107 AA01 BB01 CC29 CC33 CC35<br>CC43 CC45 DD44Y EE04 GG28<br>GG31 GG56 GG57 |

|                             |                              | 最終頁に続く                                                                                   |

(54) 【発明の名称】有機EL表示装置、その製造方法、リペア方法及びリペア装置

## (57) 【要約】

【課題】画素の正常部を劣化させることなく、欠陥部をオープン破壊させることのできる有機EL表示装置及びその製造方法を提供する。

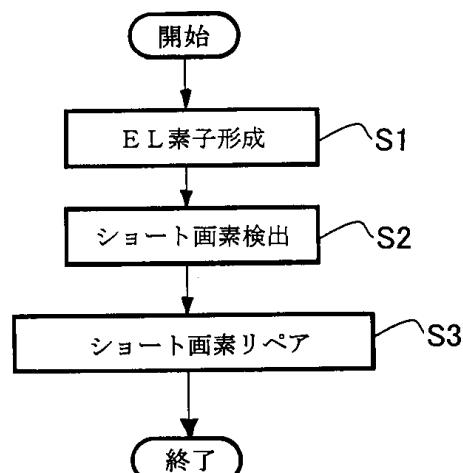

【解決手段】有機EL素子を含む複数の画素が配列されて成る有機EL表示装置の製造方法は、カソード電極とアノード電極の間に有機化合物からなる発光層からなる有機EL素子を形成する工程(ステップS1)を有する。また、カソード電極とアノード電極間がショートした画素の位置を検知する工程(ステップS2)と、検知された画素に対して選択的にカソード電極とアノード電極間に電圧を印加して欠陥部をオープン破壊させるリペア工程(ステップS3)とを備える。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

有機EL素子を含む複数の画素が配列されて成る有機EL表示装置の製造方法であって、

前記画素毎に、カソード電極とアノード電極の間に有機化合物からなる発光層からなる有機EL素子を形成する工程と、

前記複数の画素のうち、前記カソード電極と前記アノード電極間がショートした欠陥部を有する欠陥画素の位置を検知する欠陥画素検知工程と、

検知された前記欠陥画素に対して選択的に前記カソード電極と前記アノード電極間に電圧を印加して前記欠陥部をオープン破壊させるリペア工程とを備えることを特徴とする有機EL表示装置の製造方法。10

**【請求項 2】**

前記欠陥画素検知工程は、

前記有機EL表示装置を全面点灯させる工程と、

全面点灯させた前記有機EL表示装置の全ての画素のうち前記欠陥画素に対応する滅点画素を光学顕微鏡で捉えてその画素の位置を検知する工程とを含むことを特徴とする請求項1に記載の有機EL表示装置の製造方法。

**【請求項 3】**

前記欠陥画素検知工程は、前記カソード電極と前記アノード電極間に流れる電流を測定することにより、前記画素の欠陥を判定する工程を含むことを特徴とする請求項1に記載の有機EL表示装置の製造方法。20

**【請求項 4】**

前記欠陥画素検知工程と前記リペア工程とを繰り返し実施する工程をさらに有することを特徴とする請求項1に記載の有機EL表示装置の製造方法。

**【請求項 5】**

前記欠陥画素検知工程と前記リペア工程とを繰り返し実施する工程は、前記欠陥画素がなくなるまで繰り返し実施することを特徴とする請求項4に記載の有機EL表示装置の製造方法。

**【請求項 6】**

前記有機EL表示装置は、複数の信号線、複数の走査線、及び複数の電圧供給線の各1本にそれぞれ接続された複数の画素を有し、30

前記複数の画素の各々は、カソード電極とアノード電極の間に発光層を配置した有機EL素子と、前記信号線及び前記走査線に接続された画素選択トランジスタと、動作トランジスタと、前記動作トランジスタのゲート電位を保持するための保持容量とを含み、

前記動作トランジスタは、ゲートが前記保持容量及び前記画素選択トランジスタに接続され、ソース及びドレインの一方が前記電圧供給線に、その他方が前記アノード電極にそれぞれ接続されていることを特徴とする請求項1から5のいずれか1項に記載の有機EL表示装置の製造方法。

**【請求項 7】**

前記欠陥画素検知工程は、

全ての画素の前記動作トランジスタをオフ状態にする工程と、40

前記動作トランジスタを順次オン状態にして、前記アノード電極と前記カソード電極間に流れる電流を測定することにより前記画素の欠陥を判定する工程とを含むことを特徴とする請求項6に記載の有機EL表示装置の製造方法。

**【請求項 8】**

前記リペア工程は、前記電圧供給線または前記カソード電極の電圧を変調する工程を含むことを特徴とする請求項6または7に記載の有機EL表示装置の製造方法。

**【請求項 9】**

前記画素内に画素回路を有し、

前記画素回路は、前記複数の画素に接続された信号線を介して入力される電流信号に対50

応した電圧値を保持し、該保持した電圧値に応じた電流値を前記有機 E L 素子に出力するものであることを特徴とする請求項 1 に記載の有機 E L 表示装置の製造方法。

#### 【請求項 1 0】

前記有機 E L 表示装置は、前記複数の画素から成る表示領域の外周に、前記複数の画素に行制御線を介して接続される行制御回路と、前記複数の画素に前記信号線を介して接続される電流信号出力回路及び電圧電流変換回路とを備えた請求項 9 に記載の有機 E L 表示装置の製造方法。

#### 【請求項 1 1】

前記有機 E L 表示装置は、電流測定回路を備えた請求項 9 または 1 0 に記載の有機 E L 表示装置の製造方法。

10

#### 【請求項 1 2】

前記電流測定回路が前記信号線にスイッチを介して接続され、

前記欠陥画素検知工程は、前記有機 E L 素子が前記電流測定回路と接続され、前記電流測定回路により測定される電流量によって前記画素の欠陥を判定する工程を含むことを特徴とする請求項 1 1 に記載の有機 E L 表示装置の製造方法。

#### 【請求項 1 3】

前記欠陥画素検知工程は、前記行制御回路の出力電圧 V P 1 と、前記カソード電極の電圧 V c と、前記アノード電極の電圧 V a とを、  $V a > V c > V P 1 > 0$  に設定する工程を含むことを特徴とする請求項 1 2 に記載の有機 E L 表示装置の製造方法。

#### 【請求項 1 4】

複数の信号線、複数の走査線、及び複数の電圧供給線の各 1 本にそれぞれ接続された複数の画素を有し、

前記複数の画素の各々は、カソード電極とアノード電極の間に発光層を配置した有機 E L 素子と、前記信号線及び前記走査線に接続された画素選択トランジスタと、動作トランジスタと、前記動作トランジスタのゲート電位を保持するための保持容量とを含み、

前記動作トランジスタは、ゲートが前記保持容量及び前記画素選択トランジスタに接続され、ソース及びドレインの一方が前記電圧供給線に、その他方が前記アノード電極にそれぞれ接続され、

前記複数の画素から成る表示領域の外周に、前記走査線に接続されたゲート線駆動回路と、前記信号線に接続された信号線駆動回路とを備えた有機 E L 表示装置において、

30

前記複数の画素のうち、前記カソード電極と前記アノード電極間がショートした欠陥部を有する欠陥画素の位置を検知し且つ検知された前記欠陥画素に対して選択的に前記カソード電極と前記アノード電極間に電圧を印加して前記欠陥部をオーブン破壊するよう、前記電圧供給線または前記カソード電極の電圧を変調駆動する回路を備えることを特徴とする有機 E L 表示装置。

#### 【請求項 1 5】

前記複数の画素のうち、前記カソード電極と前記アノード電極間がショートした欠陥部を有する欠陥画素の位置を検知する信号として、前記カソード電極及びアノード電極間を流れる電流を測定する電流測定回路をさらに有することを特徴とする請求項 1 4 に記載の有機 E L 表示装置。

40

#### 【請求項 1 6】

複数の信号線、複数の走査線及び複数の電圧供給線の各 1 本にそれぞれ接続された複数の画素を有し、

前記複数の画素の各々は、カソード電極とアノード電極の間に発光層を配置した有機 E L 素子と、前記信号線及び前記走査線に接続された画素選択トランジスタと、動作トランジスタと、前記動作トランジスタのゲート電位を保持するための保持容量とを含み、

前記動作トランジスタは、ゲートが前記保持容量及び前記画素選択トランジスタに接続され、ソース及びドレインの一方が前記電圧供給線に、その他方が前記アノード電極にそれぞれ接続され、

前記複数の画素から成る表示領域の外周に、前記走査線に接続されたゲート線駆動回路

50

と、前記信号線に接続された信号線駆動回路とを備えた有機 E L 表示装置において、

前記複数の画素のうち、前記カソード電極と前記アノード電極間がショートした欠陥部を有する欠陥画素の位置を検知し且つ検知された前記欠陥画素に対して選択的に前記カソード電極と前記アノード電極間に電圧を印加して前記欠陥部をオープン破壊するように、前記ゲート線駆動回路と前記信号線駆動回路を駆動する電源線と、前記電圧供給線とがそれぞれ独立した電源に接続されていることを特徴とする有機 E L 表示装置。

【請求項 17】

カソード電極とアノード電極の間に発光層を配置した有機 E L 素子を含む画素が複数配列され、

前記複数の画素から成る表示領域の外周に、前記複数の画素に行制御線を介して接続される行制御回路と、前記複数の画素に信号線を介して接続される電流信号出力回路及び電圧電流変換回路とを備え、

前記画素内に画素回路を有し、前記画素回路は、前記電流信号出力回路からの信号に対応した電圧値を保持し、その電圧値に応じた電流値を前記有機 E L 素子に出力する有機 E L 表示装置において、

前記複数の画素のうち、前記カソード電極と前記アノード電極間がショートした欠陥部を有する欠陥画素の位置を検知するために、前記カソード電極及びアノード電極間の電流量を測定する電流測定回路を備えたことを特徴とする有機 E L 表示装置。

【請求項 18】

前記行制御回路の出力電圧と、前記カソード電極のカソード電圧とを変調する電圧変調回路をさらに備えた請求項 17 に記載の有機 E L 表示装置。

【請求項 19】

前記行制御回路の駆動電源と、前記電流信号出力回路の駆動電源とが独立して設けられていることを特徴とする請求項 17 に記載の有機 E L 表示装置。

【請求項 20】

前記カソード電極に接続される電源がグランドと独立して設けられていることを特徴とする請求項 17 に記載の有機 E L 表示装置。

【請求項 21】

前記カソード電極が金属であることを特徴とする請求項 14 から 20 のいずれか 1 項に記載の有機 E L 表示装置。

【請求項 22】

前記カソード電極の材料は、Ag、Mg、およびAlの少なくとも 1 つを含有することを特徴とする請求項 21 に記載の有機 E L 表示装置。

【請求項 23】

有機 E L 素子を含む複数の画素が配列されて成る有機 E L 表示装置のリペア方法であつて、

前記複数の画素のうち、前記カソード電極と前記アノード電極間がショートした欠陥部を有する欠陥画素の位置を検知する欠陥画素検知工程と、

検知された前記欠陥画素に対して選択的に前記カソード電極と前記アノード電極間に電圧を印加して前記欠陥部をオープン破壊させる工程とを備えることを特徴とする有機 E L 表示装置のリペア方法。

【請求項 24】

有機 E L 素子を含む複数の画素が配列されて成る有機 E L 表示装置のリペア装置であつて、

前記複数の画素のうち、前記カソード電極と前記アノード電極間がショートした欠陥部を有する欠陥画素の位置を検知する欠陥画素検知手段と、

検知された前記欠陥画素に対して選択的に前記カソード電極と前記アノード電極間に電圧を印加して前記欠陥部をオープン破壊させる手段とを備えることを特徴とする有機 E L 表示装置のリペア装置。

【発明の詳細な説明】

10

20

30

40

50

**【技術分野】****【0001】**

本発明は、有機EL表示装置、その製造方法、リペア方法及びリペア装置に関し、特にリペアディスプレイの歩留まりを向上させるため、有機EL素子のカソード電極とアノード電極間にショートした欠陥部を有する画素を選択的にリペアする方法に関する。

**【背景技術】****【0002】**

近年、CRT (cathode ray tube) に比べ薄型化が可能であり、液晶表示装置に比べ広い視野角が得られ、軽量、低コスト化が容易なEL (electroluminescence) 表示装置 (有機ELディスプレイ) の開発が盛んとなっている。

10

**【0003】**

有機ELディスプレイは、一般的に、有機発光層がアノード電極とカソード電極間に挟まれた構造であり、外部駆動回路により電極間に電流を流すことで発光する。有機発光層を挟むアノード電極とカソード電極とは、XYマトリクス電極を構成するよう配設され、互いに直交する。このXYマトリクス電極の交点が1画素を構成することとなる。

**【0004】**

TFT (thin Film Transistor) を付設した有機ELディスプレイの場合、アクティブマトリクス動作は、たとえばX電極に順次走査パルス電圧を印加して、これに接続されているTFTを一斉にオン状態とする。同時に、Y電極に信号電圧を印加して、TFTを通して各画素の静電容量に電荷を蓄積する。1ラインの走査が終了すると、TFTはオフ状態となり、画素容量に蓄積された電荷はそのまま保持されることになる。これにより、幅広い範囲で印加電圧を任意に設定でき、速い応答速度と高いコントラストを得ている。

20

**【特許文献1】特開2004-199970号公報****【特許文献2】特開昭61-114493号公報****【特許文献3】特許第2818255号公報****【特許文献4】特許第3562522号公報****【発明の開示】****【発明が解決しようとする課題】****【0005】**

上述した有機ELディスプレイでは、有機発光層を挟むアノード電極とカソード電極がショートした場合、その部分の有機EL素子が発光しなくなるため、非点灯欠陥が生じる。このように電極間にショートが発生する原因としては、異物の付着や有機発光層のピンホールなどがある。一般的に電極間に形成される有機発光層の厚さは、数10nmから100nm程度と非常に薄く、電極間ショートによる非点灯画素が多数発生しやすい。有機ELディスプレイでは、ディスプレイの面内にサブミクロン以下の異物を付着しないようにするには非常に困難であるため、非点灯画素の対策が望まれている。

30

**【0006】**

一方、このような非点灯欠陥は、ショート箇所をレーザーで焼き切ることにより絶縁化し、正常点灯できることが知られている。しかしながら、画素中のどの場所にショート箇所が存在するのかは発見し難く、特許文献1に示されるように赤外線温度画像検出顕微鏡の高倍率視野内で、ショートによる発熱箇所の位置を特定するという方法が開示されている。しかし、このような方法は、レーザーリペア (焼断補修) の工程が煩雑で時間がかかるため、パネル1枚のコストが大幅に増加してしまう。

40

**【0007】**

一方、他の焼断補修の方法としてエージング工程中にショート箇所を補修する方法が知られている。これは、有機EL素子の製造工程において、アノード電極とカソード電極との間に電圧を印加するエージング処理を行って膜欠陥部を予めオープン破壊させておくという方法である。オープン破壊とは、欠陥部を不導体化させることである。これは、エージングの際に生じるジュール熱によって当該膜欠陥部に対応する電極を破壊してオープン状態 (絶縁状態) としたり、酸化して不導体化したりする等の現象により発生すると考え

50

られる。このようなオープン破壊を行った膜欠陥部は、局所的な非発光状態となる。しかし、膜欠陥部は、もともと視認できない程度の微小なものであり、表示品質には影響しない。

#### 【0008】

このようなエージングによるオープン破壊を行うものとして、特許文献2には、無機EL素子によるエージング方法が開示されている。これは、第1のエージング工程として直流電圧を印加して、パネル内に存在する欠陥部を微小破壊させるというものである。

#### 【0009】

また、特許文献3においては、有機EL素子に対して、第1のエージング工程として、 $1 \times 10^4 \sim 1 \times 10^7$  [V/cm]の範囲内の電圧で、直流の順電圧を1秒以上、直流の逆電圧を1秒以上それぞれ順次印加してエージングする。その後、さらに第2のエージング工程として、第1のエージング工程よりも長時間直流の順電圧を印加する方法が提案されている。

#### 【0010】

また、特許文献4においては、欠陥部の破壊電圧及び有機EL素子の破壊電圧を求めた後、これら両破壊電圧の間の電圧範囲を、エージング処理における印加電圧の範囲としてエージング工程を行うという方法である。

#### 【0011】

これらの方法は、いずれも正常画素にも電圧を印加するため、正常画素の素子劣化を引き起こし、パネル輝度の低下や表示ムラの発生といった不都合が生じる。さらに、パネル面積が大きい場合には、パネルに流れる電流が大きくなるため、電源配線自体が発熱して断線したり、パネルの発熱による素子劣化も生じたりする。実際に、このようなエージング処理を適用するのは困難であった。

#### 【0012】

そこで、本発明は、上記問題に鑑み、画素の正常部を劣化させることなく、欠陥部をオープン破壊させることのできる有機EL表示装置及びその製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0013】

上記目的を達成するため、本発明に係る有機EL表示装置の製造方法は、有機EL素子を含む複数の画素が配列されて成るものであって、前記画素毎に、カソード電極とアノード電極の間に有機化合物からなる発光層からなる有機EL素子を形成する工程を有する。また、前記複数の画素のうち、前記カソード電極と前記アノード電極間にショートした欠陥部を有する欠陥画素の位置を検知する欠陥画素検知工程を有する。さらに、検知された前記欠陥画素に対して選択的に前記カソード電極と前記アノード電極間に電圧を印加して前記欠陥部をオープン破壊させるリペア工程を有する。

#### 【0014】

本発明に係る有機EL表示装置は、複数の信号線、複数の走査線、及び複数の電圧供給線の各1本にそれぞれ接続された複数の画素を有する。前記複数の画素の各々は、カソード電極とアノード電極の間に発光層を配置した有機EL素子と、前記信号線及び前記走査線に接続された画素選択トランジスタと、動作トランジスタと、前記動作トランジスタのゲート電位を保持するための保持容量とを含む。前記動作トランジスタは、ゲートが前記保持容量及び前記画素選択トランジスタに接続され、ソース及びドレインの一方が前記電圧供給線に、その他方が前記アノード電極にそれぞれ接続される。前記複数の画素から成る表示領域の外周に、前記走査線に接続されたゲート線駆動回路と、前記信号線に接続された信号線駆動回路とを備える。前記複数の画素のうち、前記カソード電極と前記アノード電極間にショートした欠陥部を有する欠陥画素の位置を検知し且つ検知された前記欠陥画素に対して選択的に前記カソード電極と前記アノード電極間に電圧を印加する。こうして前記欠陥部をオープン破壊せるように、前記電圧供給線または前記カソード電極の電圧を変調駆動する回路を備える。

10

20

30

40

50

## 【0015】

本発明に係る有機EL表示装置は、複数の信号線、複数の走査線及び複数の電圧供給線の各1本にそれぞれ接続された複数の画素を有する。前記複数の画素の各々は、カソード電極とアノード電極の間に発光層を配置した有機EL素子と、前記信号線及び前記走査線に接続された画素選択トランジスタと、動作トランジスタと、前記動作トランジスタのゲート電位を保持するための保持容量とを含む。前記動作トランジスタは、ゲートが前記保持容量及び前記画素選択トランジスタに接続され、ソース及びドレインの一方が前記電圧供給線に、その他方が前記アノード電極にそれぞれ接続される。前記複数の画素から成る表示領域の外周に、前記走査線に接続されたゲート線駆動回路と、前記信号線に接続された信号線駆動回路とを備える。前記複数の画素のうち、前記カソード電極と前記アノード電極間にショートした欠陥部を有する欠陥画素の位置を検知し且つ検知された前記欠陥画素に対して選択的に前記カソード電極と前記アノード電極間に電圧を印加する。こうして前記欠陥部をオープン破壊するように、前記ゲート線駆動回路と前記信号線駆動回路を駆動する電源線と、前記電圧供給線とがそれぞれ独立した電源に接続されている。

## 【0016】

本発明に係る有機EL表示装置は、カソード電極とアノード電極の間に発光層を配置した有機EL素子を含む画素が複数配列される。前記複数の画素から成る表示領域の外周に、前記複数の画素に行制御線を介して接続される行制御回路と、前記複数の画素に信号線を介して接続される電流信号出力回路及び電圧電流変換回路とを備える。前記画素内に画素回路を有し、前記画素回路は、前記電流信号出力回路からの信号に対応した電圧値を保持し、その電圧値に応じた電流値を前記有機EL素子に出力する。前記複数の画素のうち、前記カソード電極と前記アノード電極間にショートした欠陥部を有する欠陥画素の位置を検知するために、前記カソード電極及びアノード電極間の電流量を測定する電流測定回路を備える。

## 【0017】

本発明に係る有機EL表示装置のリペア方法は、有機EL素子を含む複数の画素が配列されて成るものであって、前記複数の画素のうち、前記カソード電極と前記アノード電極間にショートした欠陥部を有する欠陥画素の位置を検知する欠陥画素検知工程を有する。また、検知された前記欠陥画素に対して選択的に前記カソード電極と前記アノード電極間に電圧を印加して前記欠陥部をオープン破壊する工程を有する。

## 【0018】

本発明に係る有機EL表示装置のリペア装置は、有機EL素子を含む複数の画素が配列されて成るものであって、前記複数の画素のうち、前記カソード電極と前記アノード電極間にショートした欠陥部を有する欠陥画素の位置を検知する欠陥画素検知手段を有する。また、検知された前記欠陥画素に対して選択的に前記カソード電極と前記アノード電極間に電圧を印加して前記欠陥部をオープン破壊する手段を有する。

## 【発明の効果】

## 【0019】

本発明によれば、欠陥部を検知した後、欠陥部のみに電流を流すので、正常画素の劣化は発生しない。さらに、パネルに流れる電流は、全画素に電流を流す場合よりも大幅に抑えられるので、電源配線の断線やパネルの発熱による素子劣化は生じない。従って、画素の正常部を劣化させることなく、欠陥部をオープン破壊させることができ、レーザーリペアと比べて欠陥画素を短時間でリペアすることができるので、コストの増加はほとんどない。

## 【発明を実施するための最良の形態】

## 【0020】

以下、本発明に係る有機EL表示装置の製造方法及び有機EL表示装置の実施の形態について、図面を参照して説明する。

## (第1の実施の形態)

まず、図1～図5を参照して、本発明の第1の実施の形態について説明する。図1は、

10

20

30

40

50

本実施の形態に係る有機 E L 表示装置の構成を示すブロック図、図 2 はその製造方法の概略を示す流れ図である。

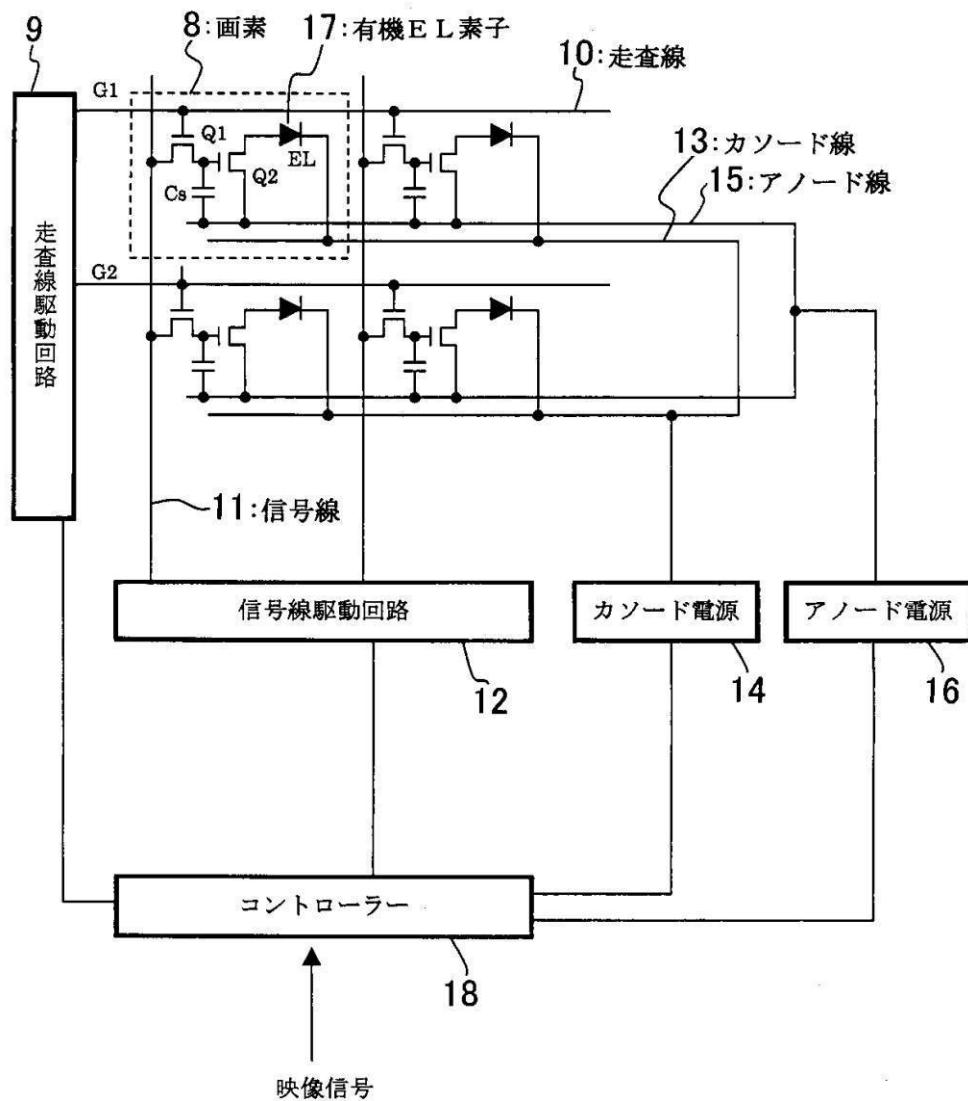

【 0 0 2 1 】

図 1 に示す有機 E L 表示装置において、絶縁性基板（アクティブマトリクス基板）上の画素マトリクスアレイ領域には、複数の画素 8 がマトリクスアレイ状に配列されている。複数の画素 8 の各々は、画素選択トランジスタ（TFT）Q 1、保持容量 C s、動作トランジスタ（TFT）Q 2、及び有機 E L 素子 17 を有する。また、絶縁性基板（アクティブマトリクス基板）上には、その行方向に沿って複数の走査線（ゲート線）10 が、またその列方向に沿って複数の信号線 11 がそれぞれ設けられている。図中の例では、G 1 は 1 行目の走査線 10 、 G 2 は 2 行目の走査線 10 をそれぞれ示す（2 行目以降は省略）。絶縁基板上には、さらに、各画素 8 の電圧供給線として、例えば行方向に沿って、複数のアノード線 15 が設けられている。絶縁基板上には、アノード電極が形成され、このアノード電極上には、有機発光層とカソード電極が順に形成されており、アノード電極、有機発光層、及びカソード電極により、有機 E L 素子 17 が構成される。カソード電極はカソード線 13 に接続される。

10

【 0 0 2 2 】

有機 E L 素子 17 は、その一端（アノード側）がアクティブマトリクス基板に形成された動作トランジスタ Q 2 のドレイン側の電極に接続されている。また、この有機 E L 素子 17 は、その他端（カソード側）がカソード線 13 を介してカソード電源 14 に各画素共通に接続されている。画素選択トランジスタ Q 1 は、ゲートが走査線 10 に、ソースが信号線 11 に、ドレインが動作トランジスタ Q 2 のゲート及び保持容量 C s の一端に、それぞれ接続されている。動作トランジスタ Q 2 は、ドレインが有機 E L 素子 17 の一端に接続されている。また、この動作トランジスタ Q 2 は、ソースがアノード線 15 を介してアノード電源 16 に各画素共通に接続されている。保持容量 C s は、その他端がアノード線 15 を介してアノード電源 16 に各画素共通に接続されている。

20

【 0 0 2 3 】

この画素マトリクスアレイ領域において、複数の走査線 10 は走査線駆動回路（ゲート線駆動回路）9 に、複数の信号線 11 は信号線駆動回路 12 にそれぞれ接続されている。これら走査線駆動回路 9 及び信号線駆動回路 12 は、アクティブマトリクス基板上に形成することもできる。この場合、走査線駆動回路 9 及び信号線駆動回路 12 は、各画素 8 が成す表示領域の外周に設けてもよい。

30

【 0 0 2 4 】

上記の走査線駆動回路 9 、信号線駆動回路 12 、カソード電源 14 、及びアノード電源 16 は、コントローラー 18 に接続される。コントローラー 18 には、映像信号が入力され、これに基づいて、走査線駆動回路 9 、信号線駆動回路 12 、カソード電源 14 、及びアノード電源 16 の動作が制御可能となっている。

40

【 0 0 2 5 】

次に、上記の有機 E L 表示装置の動作について説明する。

【 0 0 2 6 】

まず、コントローラー 18 に映像信号が入力される。入力された映像信号は、コントローラー 18 によって有機 E L 表示装置を駆動するための信号に変換され、走査線駆動回路 9 、及び信号線駆動回路 12 に送られる。

【 0 0 2 7 】

そして、コントローラー 18 から送られてくるスタート信号等のコントロール信号に基づき、走査線駆動回路 9 から各走査線 10 (G 1, G 2, ...) に、一水平走査期間 (1 H) だけオンする走査信号が供給される。これにより、まず第 1 行目の画素選択トランジスタ Q 1 が同時にオンされ、2 行目以降の画素選択トランジスタ Q 1 が行単位で順次選択される。

【 0 0 2 8 】

一方、信号線駆動系回路 12 から各信号線 11 に制御電圧が供給され、各画素 8 の保持

50

容量 C s に画素選択トランジスタ Q 1 を介して充電される。保持容量 C s が充電されると、動作トランジスタ Q 2 がオンし、これによりアノード電極から供給される電流が有機 E L 素子 1 7 に流れて、画素 8 が点灯する。なお、保持容量 C s に充電する電圧を制御することによって、有機 E L 素子 1 7 に流れる電流を制御できるので、多諧調表示が可能である。

#### 【 0 0 2 9 】

次に、図 2 を参照して、上記の有機 E L 表示装置の製造方法について説明する。

#### 【 0 0 3 0 】

図 2 に示す製造方法は、E L 素子形成工程、欠陥画素検知工程、及びリペア工程を有する。まず、最初の E L 素子形成工程では、カソード電極とアノード電極の間に有機化合物からなる発光層からなる有機 E L 素子 1 7 を形成する（ステップ S 1）。

10

#### 【 0 0 3 1 】

この工程では、一般的なアクティブマトリクス基板の製造方法により、ガラス基板上に走査線、信号線、トランジスタを形成し、その上有機 E L 素子 1 7 を形成する。有機 E L 素子 1 7 は、アノード電極、正孔輸送層、有機発光層、電子注入層、カソード電極を順に成膜して得られる。その後、有機 E L 素子 1 7 をガラスなどの封止基板と有機樹脂で封止し、有機 E L 素子 1 7 内への水分の浸入を防止する。封止方法としては、窒化シリコン膜などの保護膜を形成しても良く、この場合は封止基板が不要となり、有機 E L 表示装置の厚さが約半分と薄くすることができる。

20

#### 【 0 0 3 2 】

上記の工程後、欠陥画素検知工程では、形成された有機 E L 素子 1 7 のカソード電極とアノード電極間がショートした画素（ショート画素）の位置を検知する（ステップ S 3）。この工程後、リペア工程では、検知されたショート画素のカソード電極とアノード電極間に電圧を印加して欠陥部をオープン破壊させる（ステップ S 3）。

#### 【 0 0 3 3 】

リペア工程は、個々の欠陥画素ごとに電流を検知しながら徐々に電圧をあげてオープン破壊が起きるまで行ってもよいが、すべての欠陥画素に通常の動作電圧よりも高い一定の電圧を、一定時間（例えば、約 100 時間）印加し続けることにより行ってもよい。この場合の電圧と時間は、欠陥画素がすべてオープン破壊を起こすのに十分な電圧と時間に設定する。

30

#### 【 0 0 3 4 】

従って、本実施の形態によれば、欠陥部を検知した後、欠陥部のみに電流を流すので、正常画素の劣化は発生しない。さらに、パネルに流れるリペア時の電流は、全画素に電流を流す場合よりも大幅に抑えられるので、電源配線の断線やパネルの発熱による素子劣化は生じない。従って、画素の正常部を劣化させることなく、欠陥部をオープン破壊させることができ、レーザーリペアと比べて短時間で行うことができるので、コストの増加はほとんどない。

#### 【 0 0 3 5 】

さらに、欠陥画素を電気的に検知する場合においては、検出時間を短縮化できる上、リペア工程と欠陥画素検知工程を繰り返すことで、欠陥画素のない有機 E L 表示装置を簡便に製造することが可能である。さらに、カソード電極として、Ag、Mg、AL のいずれかを採用することによって、ショート部の不導体化が容易になるので、リペア工程の時間を大幅に短縮できる。また、画素回路内のトランジスタサイズが小さくても、欠陥画素を十分にリペアすることができるので、画素の高精細化が可能である。

40

#### 【 0 0 3 6 】

なお、上記の欠陥画素検知工程とリペア工程とは、有機 E L 表示装置のカソード成膜後であれば、その後の製造工程において、どの工程で行っても良く、製造容易性を考慮すると、封止後に行なうことが望ましい。

#### 【 0 0 3 7 】

上記のようにして欠陥を修復した後、正常画素も含めて全画素に電圧を一定の期間印加

50

し、エージングを行ってもよい。エージングは、製造直後の特性のばらつきを平均化し、各画素の特性を安定させるために行われる。短時間で行うために、駆動電圧よりも高い電圧を印加して特性変化を加速する。上記のリペアのために印加した電圧をそのまま全画素に印加して、リペア工程に引き続いてエージングを行うことができる。あるいは、リペア時よりも印加電圧をさらに大きくして、より短時間で行ってもよい。

#### 【0038】

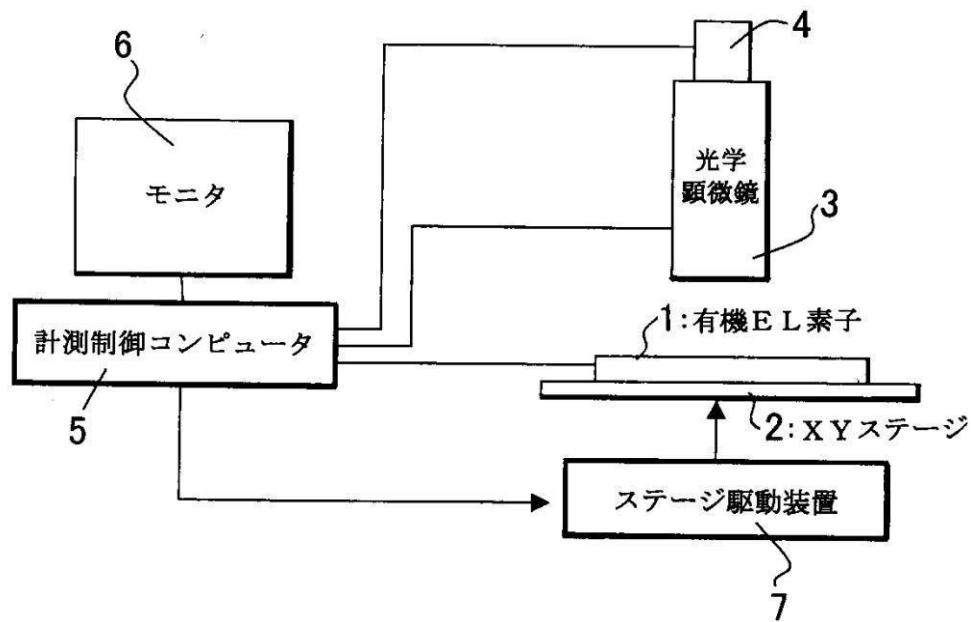

図3は、上記の製造方法のうち欠陥画素検知工程及びリペア工程で用いるリペア装置としての検査装置の概略図、図4は、その検査装置を用いた製造方法を説明する流れ図である。

#### 【0039】

図3に示す検査装置は、有機EL表示装置1が配置されるXYステージ2と、そのXYステージ2上の有機EL表示装置1を臨む対向位置に配置される光学顕微鏡3と、その光学顕微鏡3に付設される撮像装置としてのCCDカメラ4とを有する。また、この検査装置は、XYステージ2を駆動するステージ駆動装置7と、光学顕微鏡3、CCDカメラ4、およびステージ駆動装置7にそれぞれ接続される計測制御コンピュータ5と、その計測制御コンピュータ5に接続されるモニタ6とを有する。

#### 【0040】

上記の検査装置において、有機EL表示装置1は、XYステージ2からなる移動機構上に配置され、光学顕微鏡3でその画素の点灯状態を観察できるようになっている。光学顕微鏡3には、CCDカメラ4が付設され、CCDカメラ4の観測画像を撮像データとして計測制御コンピュータ5へ送出する。計測制御コンピュータ5には、モニタ6が接続され、CCDカメラ4から送られた撮像データを、観測画像として、このモニタ6に表示する。ステージ駆動装置7は、計測制御コンピュータ5によって制御され、XYステージ2を駆動することにより、有機EL表示装置1の表示面上における任意の位置を光学顕微鏡3の光軸に位置合わせができるように構成されている。

#### 【0041】

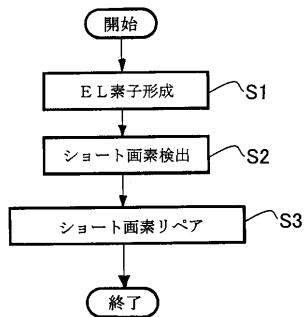

次に、有機ELパネルの製造方法について、図4を参照して説明する。

#### 【0042】

最初に、前述と同様のEL素子形成工程により、有機EL素子を形成する（ステップS11）。その後、図3に示す検査装置を用いた欠陥画素検知工程及びリペア工程に移行する。これに際し、まず、有機EL素子が形成された有機EL表示装置1をXYステージ2上に固定し、有機EL表示装置1の原点位置及び座標軸を設定する。この際、XYステージ2の駆動走査及び原点位置データの設定は、計測制御コンピュータ5によってステージ駆動装置7を介して行う。

#### 【0043】

次いで、計測制御コンピュータ5は、コントローラー18へ制御信号を送る。こうすることで、有機EL表示装置1を全面点灯させる（ステップS12）。この状態で、光学顕微鏡3にて、有機EL表示装置1のパネル表示面を走査し、モニタ6に表示された画像から、パネル表示面上で点灯していない欠陥画素（滅点画素）を検出する（ステップS13）。

#### 【0044】

ここで、複数分割された視野内に滅点画素を捉えるのは、例えば計測制御コンピュータ5から順次検出するようにステージ駆動装置7に駆動信号を送出することにより、自動で行うことができる。また、計測制御コンピュータ5は、滅点画素を画像処理により特定することができ、特定した滅点画素の位置データを記憶する（ステップS14）。この動作を繰り返すことで、表示領域全面の点灯状態を検査することができ、滅点画素の位置データを記憶する。

#### 【0045】

次に、計測制御コンピュータ5は、得られた滅点画素の位置データから、正常画素を非点灯状態に、滅点画素を点灯状態にするような画像パターンを作成し、この画像パターン

10

20

30

40

50

に対応する映像信号を有機EL表示装置1に送出する。すると、有機EL表示装置1では、コントローラー18により、各画素のうち滅点画素にだけ電流が流れるように制御され、この状態を維持することによって、滅点画素のみを選択的にリペアすることができる(ステップS15)。

【0046】

なお、この滅点画素の検出工程とリペア工程は、有機EL表示装置1のカソード成膜後であれば、その後の製造工程において、どの工程で行っても良く、製造容易性を考慮すると、封止後に行なうことが望ましい。

【0047】

このように、上述の有機EL表示装置の製造方法によれば、画素欠陥部のみに選択的に電流を流すので、正常画素の劣化は発生しない。さらに、パネルに流れる電流は、全画素に電流を流す場合よりも大幅に抑えられるので、電源配線の断線やパネルの発熱による素子劣化は生じない。従って、画素の正常部を劣化させることなく、欠陥部をオープン破壊させることができ、レーザーリペアと比べて短時間で欠陥画素をリペアすることができるので、コストの増加はほとんどない。

【0048】

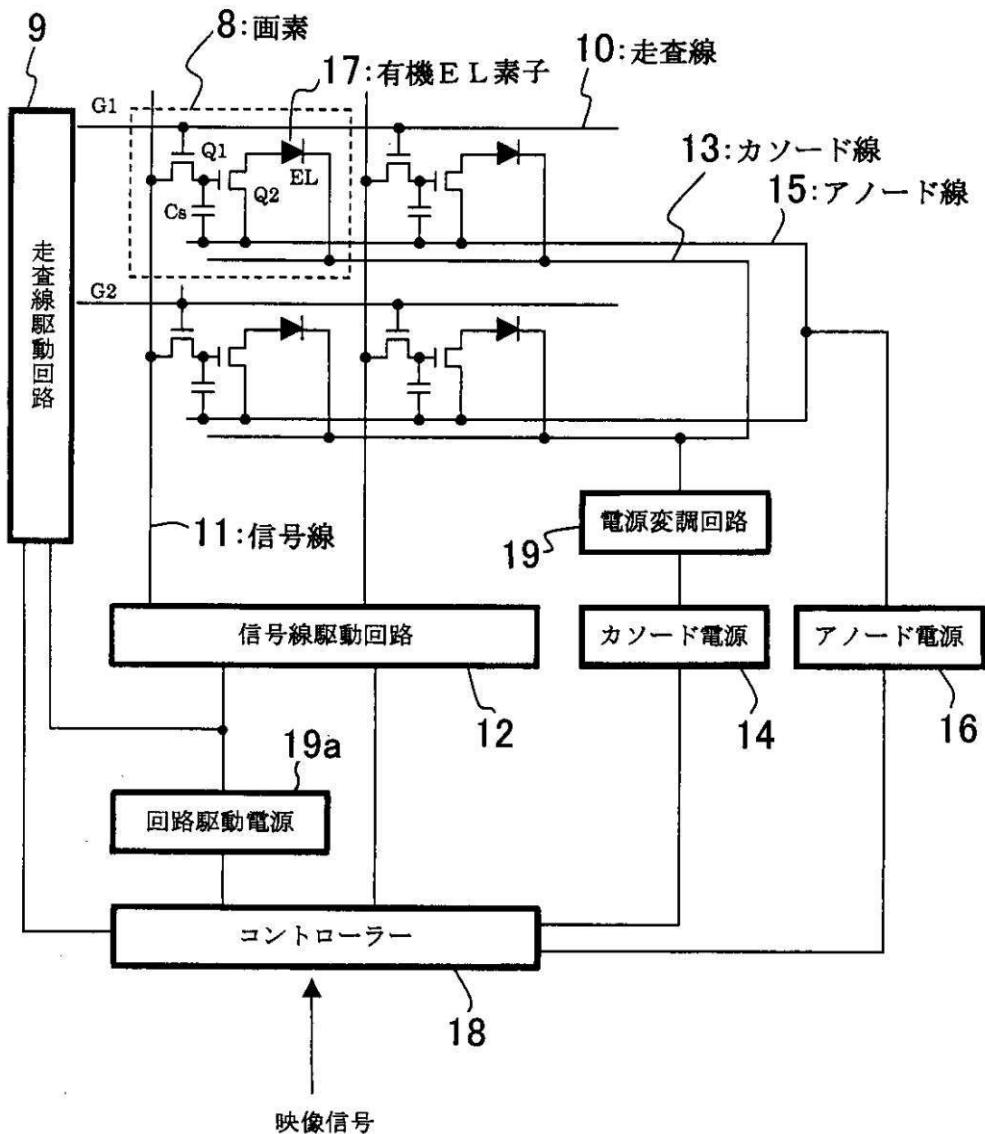

なお、本実施の形態では、欠陥画素のリペア時にアノード電圧またはカソード電圧を変調してアノード・カソード間の電位差を大きくすることによって、欠陥画素に流れる電流をより大きくでき、リペアに要する時間をさらに短縮することが可能である。この場合、アノード電圧またはカソード電圧を変調するために、図1に示す有機EL表示装置の構成に加え、電源変調回路を設けてもよい。図5は、カソード電圧を変調する場合の有機EL表示装置の構成例である。

【0049】

また、カソード電極は、一般的に共通電極として有機EL表示装置の表示領域全面に形成されており、通常0Vが印加される。また、走査線駆動回路9と信号線駆動回路12の回路駆動電源19aの電位として、0Vがコントローラー18から入力される。従って、カソード電圧の変調を行うためには、図5に示すように走査線駆動回路9及び信号線駆動回路12の回路駆動電源19aとカソード電源14とが独立に接続されている必要がある。

【0050】

さらに、カソード電極を例えばAg、Mg、またはAlなどの金属薄膜を使用してもよい。この場合には、ショート部が酸化し、不導体化しやすくなるので、有機EL素子の駆動トランジスタQ2の電流供給能力が小さくても十分に欠陥画素を正常化することができる。その結果、駆動トランジスタQ2が小さい高精細画素においても、欠陥画素を十分にリペアすることができる。

(第2の実施の形態)

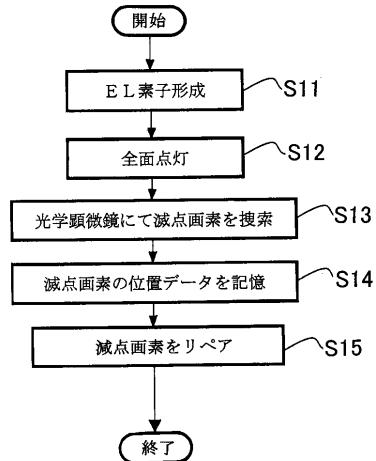

次に、図6～図8を参照して、本発明の第2の実施の形態について説明する。本実施の形態は、第1の実施の形態と異なり、欠陥画素検知工程に光学顕微鏡を用いず、欠陥画素を電気的に検出する方法である。

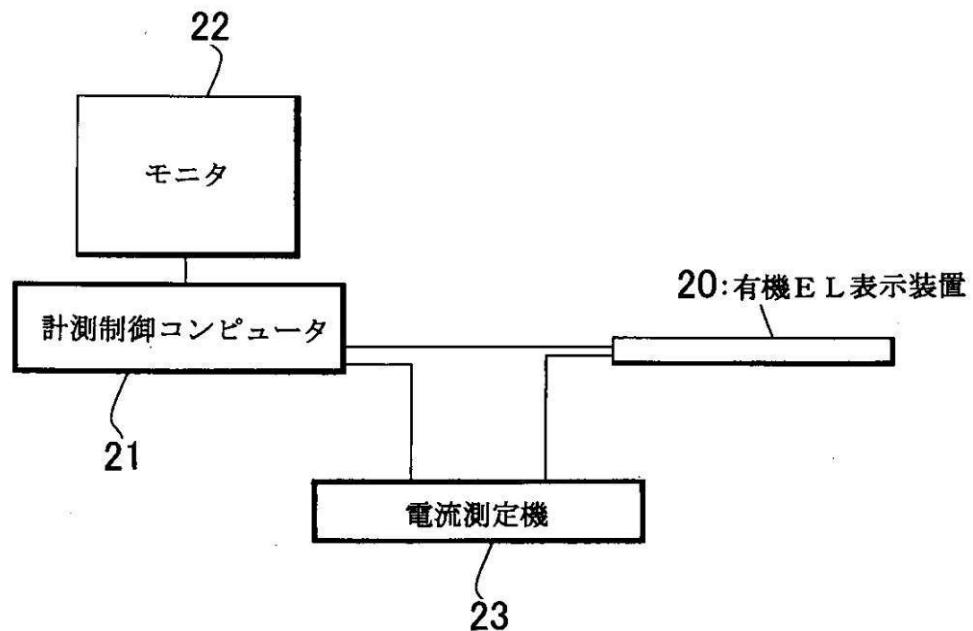

【0051】

図6は、本実施の形態に係る有機EL表示装置の製造方法のうち欠陥画素検知工程及びリペア工程で用いるリペア装置としての検査装置の概略図、図7は、その検査装置を用いた製造方法の概略を示す流れ図である。本実施の形態による有機EL表示装置の構成は、第1の実施の形態と同様であるため、その説明を省略する。

【0052】

図6に示す検査装置は、有機EL表示装置20に接続される計測制御コンピュータ21及びモニタ22と、有機EL表示装置20及び計測制御コンピュータ21に接続される電流測定機23とを備える。電流測定機23は、有機EL表示装置20のアノード電源(図1及び図5参照)に接続されており、アノード電極に流れる電流を測定し、その測定値を計測制御コンピュータ21に送る。

10

20

30

40

50

## 【0053】

図7において、まず、前述と同様のEL素子形成工程にて、有機EL素子17を形成する(ステップS21)。その後に、図6に示す検査装置を用いた欠陥画素検知工程及びリペア工程に移行する。これに際し、まず、図6に示すように有機EL表示装置20を計測制御コンピュータ21と電流測定機23に接続する。

## 【0054】

次いで、電流測定機23により、有機EL表示装置20のn番目の画素のアノード・カソード間に流れる電流を測定する(ステップS22)。そして、計測制御コンピュータ21により、その測定値に基づいてn番目の画素がショートしているかどうか判定し、そのショート画素の位置データ(座標値)を記憶する(ステップS23)。以後、ステップS22、S23の動作を全画素のショート判定が終了するまで繰り返し実行する(ステップS24)。全画素のショート判定の終了後、計測制御コンピュータ21により、得られたショート画素の位置データから、ショート画素のみを選択的に点灯状態にするような画像パターンを作成する。そして、この画像パターンに対応する映像信号を有機EL表示装置20に送出する。すると、有機EL表示装置20において、ショート画素にだけ電流が流れ、この状態を維持することによって、ショート画素のみを選択的にリペアすることができる(ステップS25)。

## 【0055】

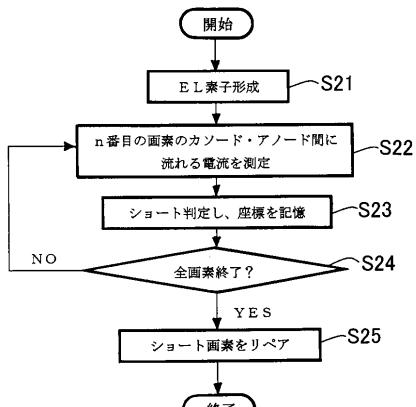

図8は、上述の製造方法の詳細を説明する流れ図である。

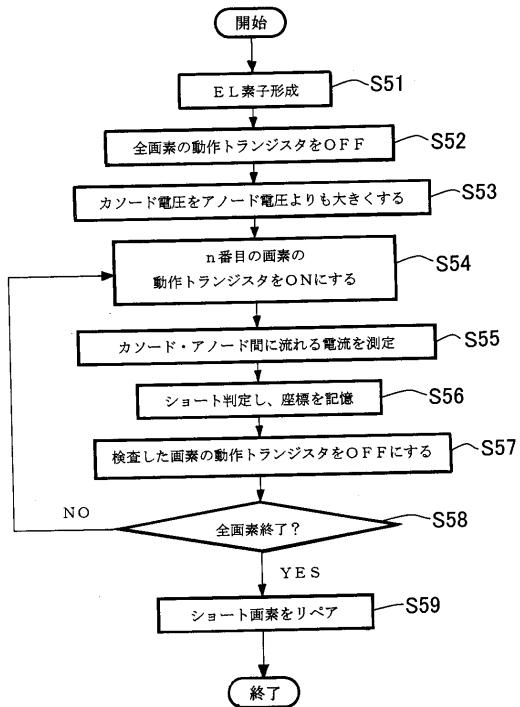

## 【0056】

図8において、前述と同様の前述と同様のEL素子形成工程にて、有機EL素子17を形成する(ステップS51)。その後に、図6に示すように有機EL表示装置20を計測制御コンピュータ21と電流測定機23に接続する。

## 【0057】

その後、計測制御コンピュータ21より画像信号を有機EL表示装置20に送出し、有機EL表示装置20は、コントローラー18により、全画素の動作トランジスタQ2がOFFになるように保持容量Csに信号線11を介して制御電圧を書き込む(ステップS52)。すると、全画素8の有機EL素子17は非点灯状態となる。次に、コントローラー18は、カソード電圧をアノード電圧よりも大きくなるように電圧を設定する(ステップS53)。その後、コントローラー18は、n番目の画素に対して、1画素のみに制御電圧を書き込んで、動作トランジスタQ2をONにする(ステップS54)。すると、有機EL素子17には逆バイアスが印加され、有機EL素子17が正常な場合には、アノード電極とカソード電極間に電流は流れず、アノード電極とカソード電極間がショートしている場合に電流が流れることになる。この電流を電流測定機23で測定する(ステップS55)。この測定結果は、計測制御コンピュータ21に送られる。

## 【0058】

これにより、計測制御コンピュータ21は、対象とするn番目の画素の欠陥を判定する。その欠陥判定を行った結果、ショートしている場合には、計測制御コンピュータ21は、そのショート画素の位置データ(座標値)を記憶する(ステップS56)。n番目の画素に対する欠陥判定後、計測制御コンピュータ21から有機EL表示装置20に制御信号が送られ、これによりコントローラー18は、動作トランジスタQ2をOFFにする(ステップS57)。以後、全ての画素に対する欠陥判定が終了するまで、上述の動作を繰り返す(ステップS58)。こうすることで、表示領域全面の点灯状態を検査することができる。

## 【0059】

次に、計測制御コンピュータ21は、得られた欠陥画素の位置データから、正常画素を非点灯状態に、欠陥画素を点灯状態にするような画像パターンを作成し、この画像パターンに対応する映像信号をコントローラー18に送出する。すると、有機EL表示装置20において、ショートが検出された欠陥画素にだけ電流が流れ、この状態を維持することによって、欠陥画素のみをリペアすることができる(ステップS59)。

10

20

30

40

50

## 【0060】

このような有機EL表示装置の製造方法であっても、第2の実施の形態と同様の効果が得られる。さらに、第2の実施の形態と比べて光学顕微鏡、CCDカメラ、XYステージ、ステージ駆動装置を必要としないので、検査装置の構成を簡素化してコストを削減することができるだけでなく、XYステージの移動時間がなくなるので検査時間が大幅に短縮される。

## 【0061】

なお、本実施の形態では、欠陥画素検知工程でアノード電流を測定する場合について説明したが、電流測定機をカソード電源に接続し、カソード電流を測定する場合についても同様の効果が得られる。

## (第3の実施の形態)

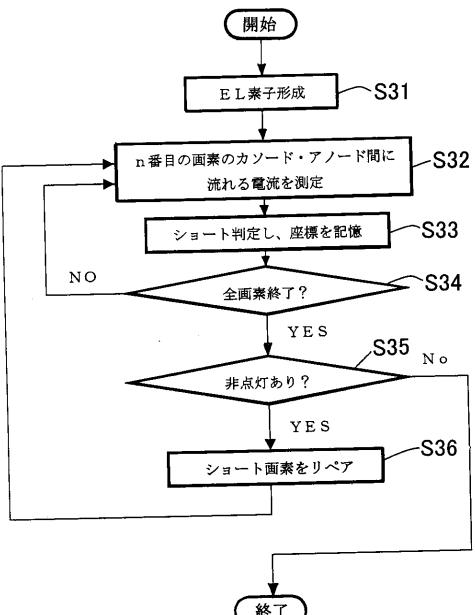

次に、図9を参照して、本発明の第3の実施の形態について説明する。図9は、本実施の形態に係る有機EL表示装置の製造方法の概略を示す流れ図である。本実施の形態による有機EL表示装置の構成は、第1の実施の形態と同じで、リペア方法が異なる。

## 【0062】

図9において、まず、前述と同様にEL素子形成(ステップS31)後に、n番目の画素のカソード電極とアノード電極間に電流を流し(ステップS32)、その測定結果により欠陥判定を行い、ショート画素の位置データ(座標値)を記憶する(ステップS33)。この動作を全ての画素の欠陥判定が終了するまで繰り返す(ステップS34)。その後、ショート画素に所定の時間、電圧を印加してリペアを行う。その後、再度、ショート画素の点灯状態の検査及びその判定を行って(ステップS35)、ショート画素があれば、そのショート画素を所定の時間、電圧を印加してリペアを行う(ステップS36)。

## 【0063】

従って、このような製造方法によれば、ショート画素が全て点灯化するまで、簡便にリペアを行うことができる。さらに、第3の実施形態では、点灯化した画素が輝度劣化を引き起こす恐れがあるが、本実施の形態では、リペア時間を短縮して、ショート検査の頻度を増すことによって、輝度劣化を最小限に抑えることができる。

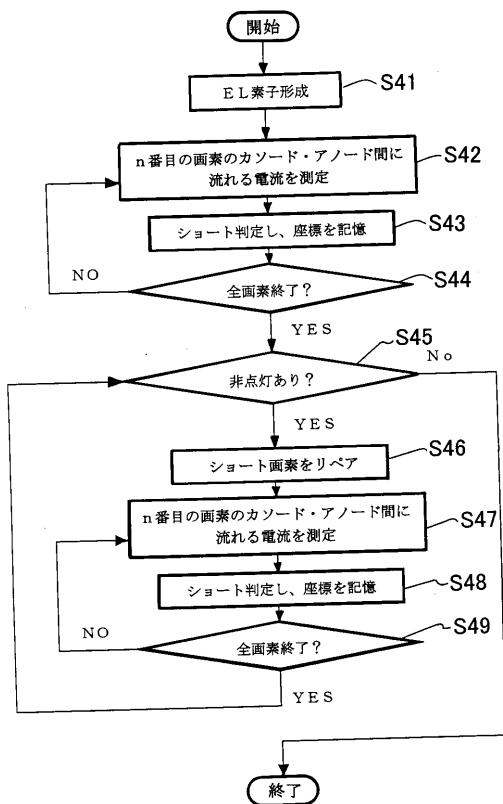

## (第4の実施の形態)

次に、図10を参照して、本発明の第4の実施の形態について説明する。図10は、本実施の形態に係る有機EL表示装置の製造方法の概略を示す流れ図である。本実施の形態による有機EL表示装置の構成及びその製造方法は、第1～第3の実施の形態と同じで、リペア方法が異なる。

## 【0064】

図10において、まず、前述と同様にEL素子形成(ステップS41)後に、n番目の画素のカソード電極とアノード電極間に電流を流し(ステップS42)、その測定結果により欠陥判定を行い、ショート画素の位置データを記憶する(ステップS43)。この動作を全ての画素の欠陥判定が終了するまで繰り返す(ステップS44)。その後、ショート画素に所定の時間、電圧を印加して欠陥部をリペアを行う。その後、再度、ショート画素の検査及び判定を行って(ステップS45)、ショート画素があれば、そのショート画素に所定の時間、電圧を印加してリペアを行う(ステップS46)。

## 【0065】

その後、n番目の画素のカソード電極とアノード電極間に電流を流し(ステップS47)、その測定結果により欠陥判定を行い、ショート画素の位置データを記憶し(ステップS48)、この動作を全ての画素のショート判定が終了するまで繰り返す(ステップS49)。

## 【0066】

従って、このような製造方法によれば、リペア後のショート検査をショート画素だけに行うので、ショート検査の回数を抑えることができる。従って、欠陥画素のリペア処理やショート検査による素子劣化を最小限に抑えることができるので、有機EL表示装置の歩留りをより高くすることが可能である。

## (第5の実施の形態)

次に、図11～図13を参照して、本発明の第5の実施の形態について説明する。

## 【0067】

前述した第1から第4の実施形態では、電圧設定方式による画素回路構成の有機EL表示装置を例に説明したが、本実施の形態では、電流設定方式の画素回路の場合について説明する。電圧設定方式では、TFTの特性ばらつきによって表示むらが発生しやすいが、電流設定方式では、TFTの特性ばらつきの影響を受けにくく、表示むらの少なくなる方式として知られている。

## 【0068】

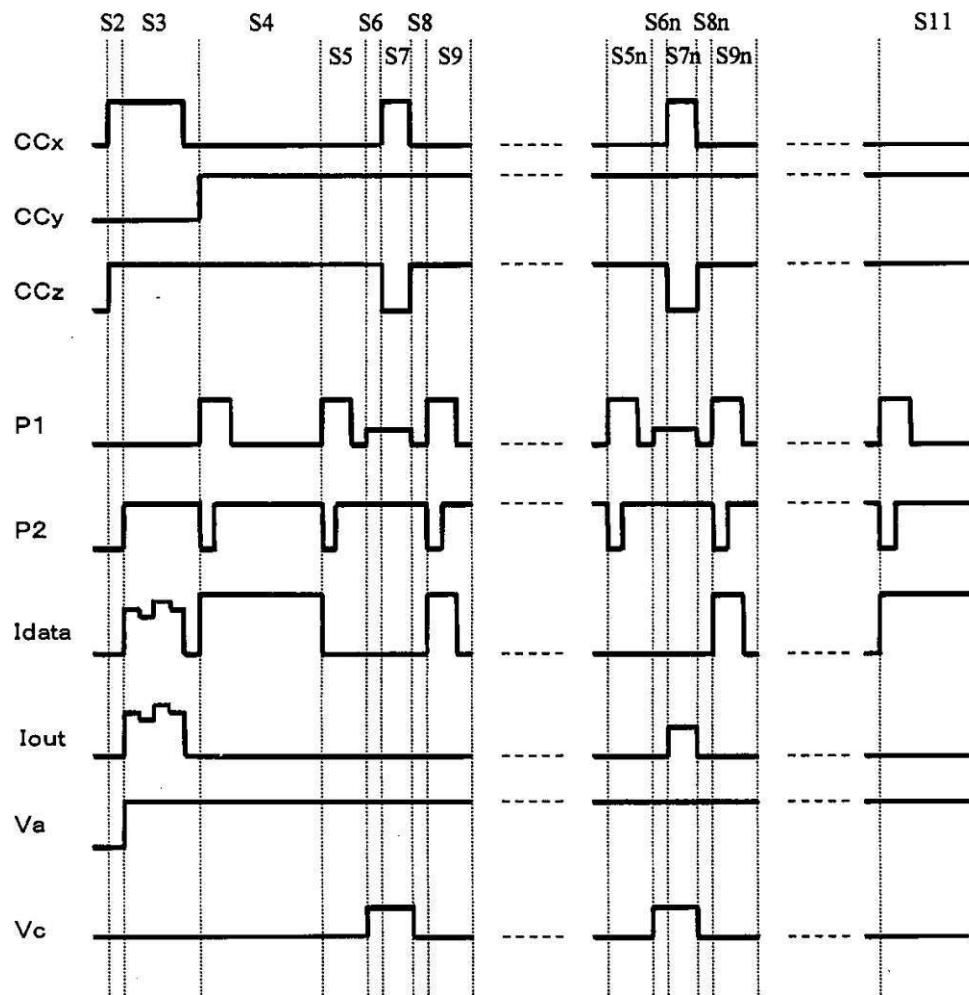

図11は、本実施の形態による有機EL表示装置の構成を示すブロック図、図12は、その画素内の画素回路の構成を示す回路図、図13は、その画素回路の動作を説明するタイミングチャートである。

## 【0069】

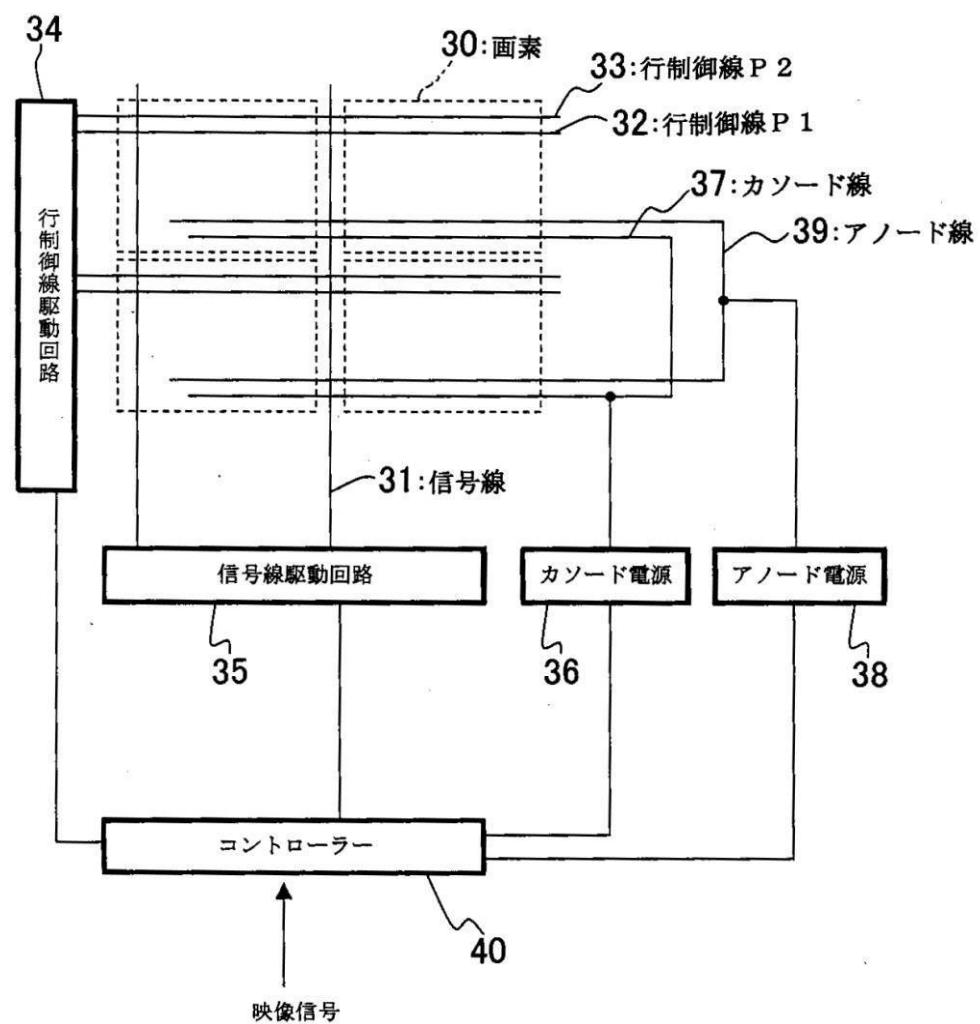

図11に示す有機EL表示装置において、画素マトリクスアレイ領域には、複数の画素30がマトリクスアレイ状に配列されている。複数の画素30の各々は、2つの行制御線32、33を介して行制御線駆動回路34に、信号線31を介して信号線駆動回路35に、カソード線37を介してカソード電源36に、アノード線39を介してアノード電源38にそれぞれ接続される。行制御線駆動回路34、信号線駆動回路35、カソード電源36、及びアノード電源38は、映像信号が入力されるコントローラー40に接続され、これにより各々の動作が制御される。

## 【0070】

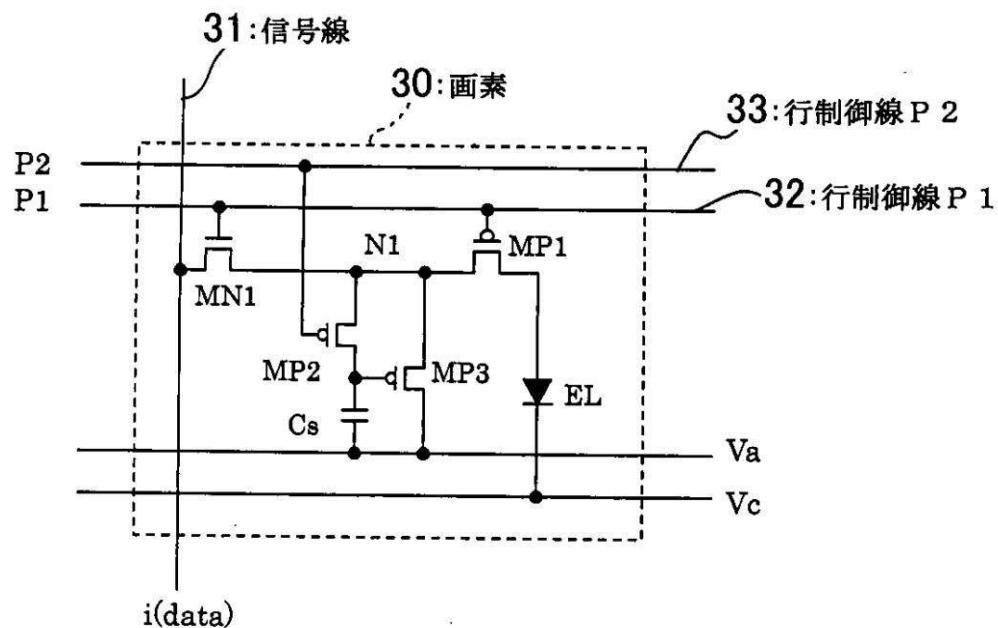

図12に示す画素回路は、1つの画素30に対応する。この画素30は、図11に示すようにマトリクスアレイ状に配置されている。図12に示す画素回路において、P1及びP2は、行制御線駆動回路34から行制御線32及び33に入力される行制御信号(走査信号)に対応する。i(data)は、信号線駆動回路35から信号線31に入力される列制御信号としての電流信号に対応する。ELは有機EL素子、MP1、MP2、MP3はP型TFT、MN1はN型TFT、Csは保持容量である。N1は、MN1のドレイン、MP1のソース、及びMP2のドレイン間を接続するノードである。

## 【0071】

有機EL素子は、アノード電極がMP1のドレインに、カソード電極がカソード電位Vcにそれぞれ接続される。MP1は、ゲート電極が行制御線P1に、ドレイン電極が有機EL素子のアノード電極に、ソース電極がMP3のドレイン電極及びノードN1にそれぞれ接続される。MP2は、ゲート電極が行制御線P2に、ドレイン電極がノードN1に、ソース電極がMP3のゲート電極及び保持容量Csの一端にそれぞれ接続される。MP3は、ゲート電極がMP2のソース電極及び保持容量Csの一端に、ソース電極がアノード電位Vaに、ドレイン電極がMP1のソース電極及びノードN1にそれぞれ接続される。MN1は、ゲート電極が行制御線P1に、ソース電極が信号線31の電流信号i(data)に、ドレイン電極がノードN1にそれぞれ接続される。保持容量Csは、一端がMP2のソース電極及びMP3のゲート電極に、他端がアノード電位Vaにそれぞれ接続される。

## 【0072】

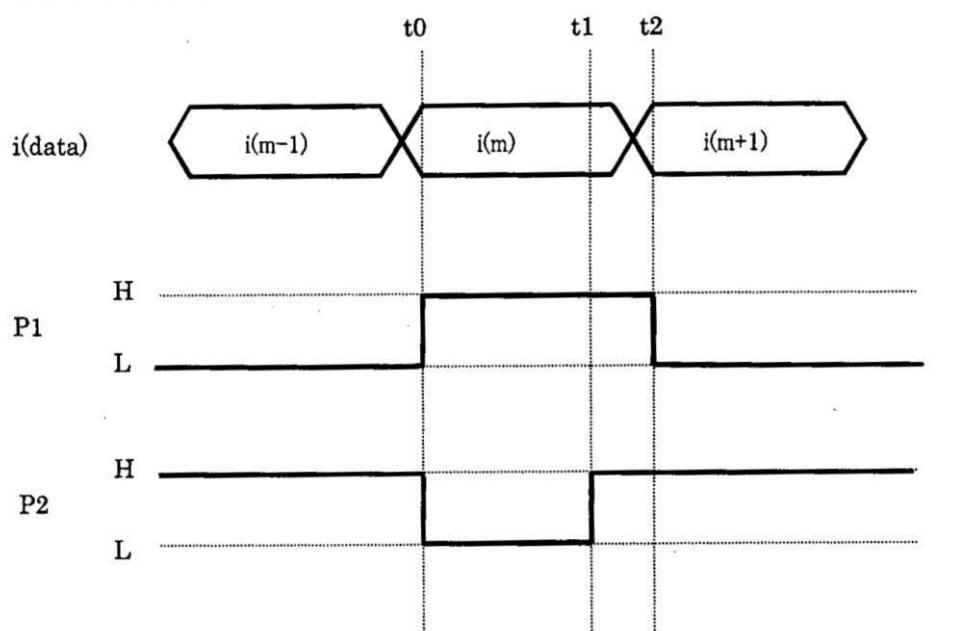

次に、図13のタイミングチャートを使用して、画素30内の画素回路の動作を説明する。図13において、I(m-1)、I(m)、I(m+1)は、m-1行(1行前)、m行(該当行)、m+1行(1行後)の該当行の画素回路に入力される電流信号i(data)を示す。

## 【0073】

まず、時刻t0以前において、該当m行のP1及びP2は、各々Lレベル及びHレベルである。このため、MN1及びMP2は共にOFFであり、MP1がONである。この状態では、MN1は導通状態でないため、該当m行の画素回路には、1行前の電流信号i(m-1)は流れない。

10

20

30

40

50

## 【0074】

次いで、時刻  $t_0$ において、該当  $m$  行の  $P_1$  及び  $P_2$  は、各々 H レベル及び L レベルに変化する。このとき、 $MN_1$  及び  $MP_2$  が ON、 $MP_1$  が OFF となる。この状態では、 $MN_1$  が ON のため、該当  $m$  行の画素回路に該当  $m$  行の電流データ  $I$  (data) に対応する  $I(m)$  が入力される。入力された電流信号  $I(m)$  により、 $MP_3$  の電流駆動能力に応じた電圧が、 $MP_3$  のゲート電極とアノード電源電位  $V_a$  の間に配置された保持容量  $C_s$  に生じる。このとき、 $MP_1$  は導通状態でないため、有機 EL 素子には電流が流れない。

## 【0075】

次いで、時刻  $t_1$  では、 $P_2$  に H レベルの信号が入力され、 $MP_2$  が OFF の状態となり、電流信号  $i(m)$  により設定（プログラミング）された保持容量  $C_s$  の電圧が保持される。さらに、時刻  $t_2$  では、 $P_1$  に L レベルの信号が入力され、 $MN_1$  が OFF、 $MP_1$  が ON となる。この状態は、該当  $m$  行の画素回路が電流信号  $i(dara)$  から切り離される。そして、 $MP_1$  が導通状態であるため、電流信号  $i(m)$  により保持容量  $C_s$  に生じた電圧により、 $MP_3$  の電流駆動能力に応じたソース・ドレイン間電流が、 $MP_1$  を介して有機 EL 素子に供給される。これにより、該当  $m$  行の画素回路に供給された電流信号  $i(m)$  に応じた輝度で有機 EL 素子が発光する。この状態は、次に  $MN_1$  が ON するまで継続される。

## 【0076】

従って、本実施の形態のような電流設定（プログラミング）方式の有機 EL 表示装置であっても、第 1 ~ 第 4 の実施の形態と同様に、非点灯画素を検出することができ、同様の効果が得られる。さらに、欠陥画素をリペアする際、欠陥画素の  $MP_3$  のゲート電位が負の電位になるように電流設定を行うと、 $MP_3$  のソース・ドレイン間に流れる電流がより大きくなるので、短時間で欠陥画素のリペアを行うことが可能となる。さらに、カソード電源 36 の出力電圧  $V_c$  とアノード電源 38 の出力電圧  $V_a$  とを変調することによって、アノード・カソード間電位差を大きくして欠陥画素のリペア時間を短くすることが可能である。

## (第 6 の実施の形態)

次に、図 14 ~ 図 18 を参照して、本発明の第 6 の実施の形態について説明する。

## 【0077】

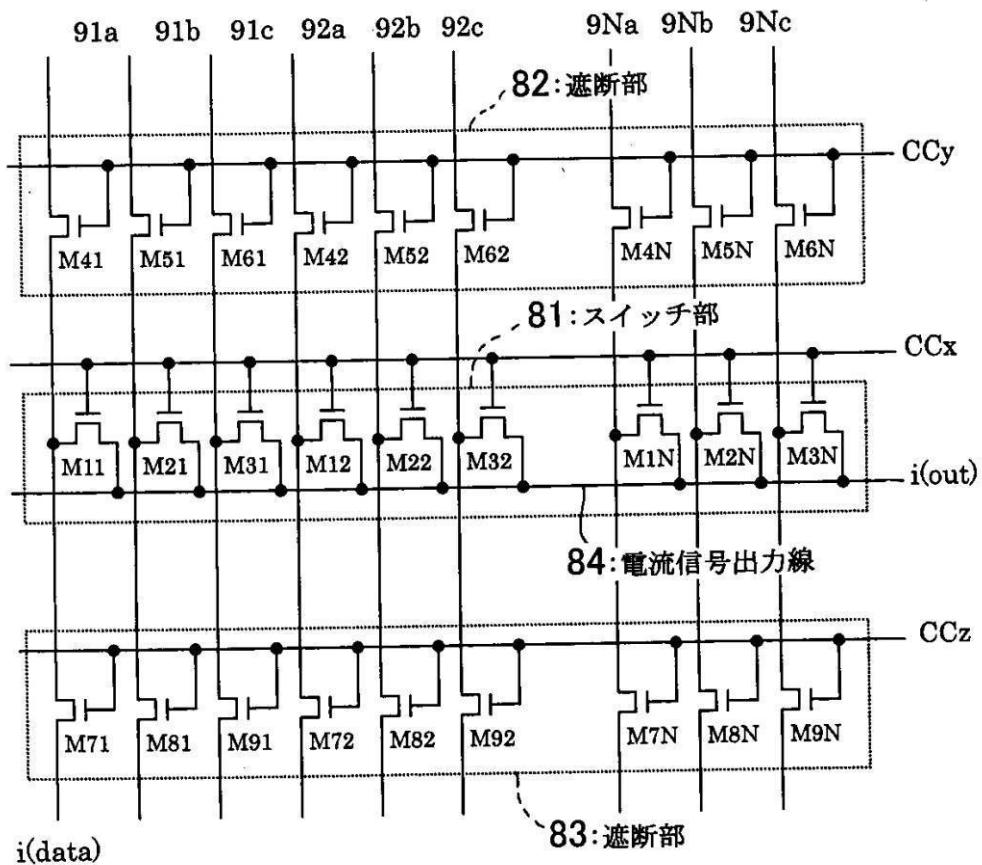

図 14 は、本実施の形態に係る有機 EL 表示装置の構成を示すブロック図、図 15 は、その信号線駆動回路内の構成を示す回路図である。

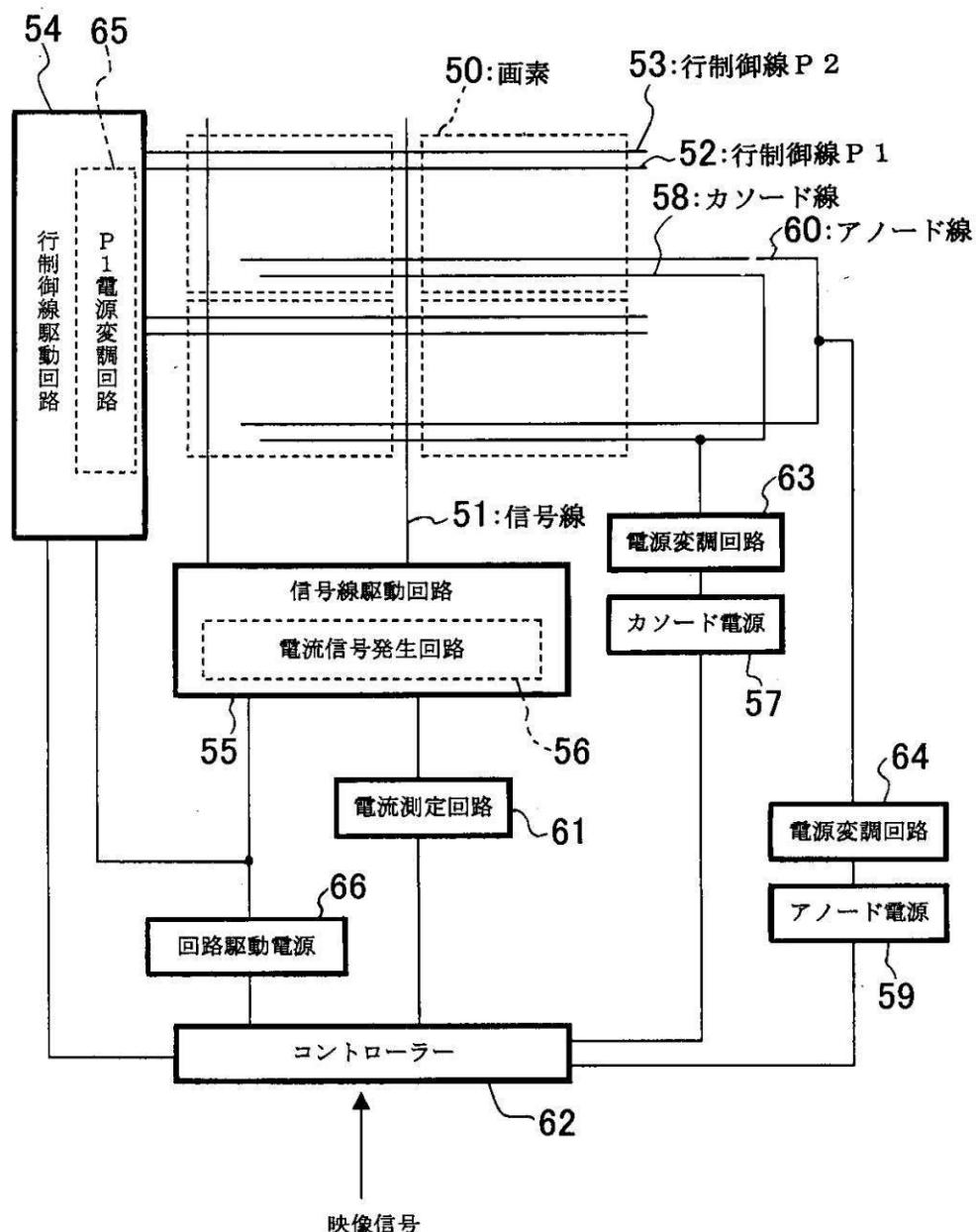

## 【0078】

図 14 は、第 5 の実施の形態と同様の電流設定方式の有機 EL 表示装置を適用したものである。図 14 に示す有機 EL 表示装置において、画素マトリクスアレイ領域には、複数の画素 50 がマトリクスアレイ状に配列されている。画素 50 は、前述の図 11 に示す回路を備え、前述の図 12 に示すタイムチャートでもって、第 5 の実施の形態と同様の動作をする。

## 【0079】

複数の画素 50 の各々は、2 つの行制御信号  $P_1$ 、 $P_2$  用の行制御線 53、54 を介して行制御線駆動回路（行制御回路）54 に、また信号線 51 を介して信号線駆動回路 55 にそれぞれ接続される。行制御線駆動回路 54 内には、行制御信号  $P_1$  の出力電圧を変調するための  $P_1$  電源変調回路 65 が設けられている。また、複数の画素 50 の各々は、カソード線 58 を介してカソード電源 57 に、アノード線 60 を介してアノード電源 59 にそれぞれ接続される。カソード線 58 とカソード電源 57 との間には、カソード電圧  $V_c$  を変調するための電源変調回路 63 が設けられている。また、アノード線 60 とアノード電源 59 との間には、アノード電圧  $V_a$  を変調するための電源変調回路 64 が設けられている。

## 【0080】

上記の行制御線駆動回路 54、信号線駆動回路 55、カソード電源 57、及びアノード

10

20

30

40

50

電源 5 9 は、コントローラー 6 2 に接続され、これにより各々の動作が制御される。行制御線駆動回路 5 4、信号線駆動回路 5 5 には、回路駆動電源 6 6 が接続される。信号線駆動回路 5 5 とコントローラー 6 2との間には、電流測定回路 6 1 が介挿される。信号線駆動回路 5 5 内には、電流信号発生回路 5 6 が形成され、コントローラー 6 2 から送出された映像信号を電流に変換する機能（電圧電流変換回路）を備える。

【 0 0 8 1 】

図 1 5 は、信号線駆動回路 5 5 内の出力部の回路構成を示す図である。

【 0 0 8 2 】

図中、8 4 は電流信号発生回路 5 6 の出力が共通に接続される電流信号出力線、8 1 は電流信号発生回路 5 6 の出力と電流信号出力線 8 4 との接続関係を制御するスイッチ部である。8 2 及び 8 3 は、図 1 4 に示す電流信号発生回路 5 6 と画素 5 0 側との接続関係を制御するスイッチ部である遮断部である。9 1 a ~ 9 N c は信号線である。M 1 1 ~ M 3 N、M 4 1 ~ M 6 N、及び M 7 1 ~ M 9 N はトランジスタ（電界効果トランジスタ）である。I (out) は、電流信号出力線 8 4 の総和電流である。C C x、C C y、C C z は、総和電流検出制御信号である。電流信号出力線 8 4 は、図 1 4 に示す電流測定回路 6 1 を介してグランドに接続される。電流測定回路 6 1 は、電流信号出力線 8 4 からグランドに流れ込む電流 I (out) を測定する。

【 0 0 8 3 】

スイッチ部 8 1 は、各信号線 9 1 a ~ 9 N c と電流信号出力線 8 4 とを接続し、開閉制御が自在なスイッチであるトランジスタ群 M 1 1 ~ M 1 N から構成される。遮断部 8 2 は、スイッチ部 8 1 と画素回路 5 0 間の各信号線 9 1 a ~ 9 N c に接続された、開閉制御が自在なスイッチである遮断トランジスタ群 M 4 1 ~ M 6 N から構成される。また、遮断部 8 3 は、スイッチ部 8 1 と信号線駆動回路 5 5 間の各信号線に接続された、開閉制御が自在なスイッチである遮断トランジスタ群 M 7 1 ~ M 9 N から構成される。

【 0 0 8 4 】

信号線駆動回路 5 5 と該当列の画素回路 5 0 とを接続する信号線 9 1 a ~ 9 N c は、遮断部 8 2 の M 4 1 ~ M 6 N を介してスイッチ部 8 1 の M 1 1 ~ M 6 N のソース電極と接続される。スイッチ部 8 1 の M 1 1 ~ M 3 N のドレイン電極は、全て共通に電流信号出力線 8 4 に接続される。この電流信号出力線 8 4 から総和電流 I (out) が出力される。

【 0 0 8 5 】

一方、遮断部 8 2 の M 4 1 ~ M 6 N のドレイン電極は、それぞれ該当列のデータ線 9 1 a ~ 9 N c に接続される。スイッチ部 8 1 の M 1 1 ~ M 3 N のゲート電極は、全て共通に接続され、コントローラー 6 2 からの総和電流検出制御信号 C C x が入力される。遮断部 8 2 の M 4 1 ~ M 6 N のゲート電極、及び遮断部 8 3 の M 7 1 ~ M 9 N のゲート電極は全て共通に接続されてコントローラー 6 2 からの総和電流検出制御信号 C C y、C C z がそれぞれ入力される。なお、全てのトランジスタはスイッチ動作をするものであり、適切に制御すれば、p 型及びn 型の限定や構成は限定されない。

【 0 0 8 6 】

表示パネルを構成する基板としては、ガラス基板を好適に用いることができる。ガラス基板には、アモルファスシリコンまたはポリシリコンを用いた TFT が形成され、信号線駆動回路 5 5 及び行制御線駆動回路 5 4 を構成している。しかしながら、TFT は、その特性上、CMOS トランジスタに比べて素子間のばらつきが大きく、電流信号発生回路 5 6 の電流出力も隣り合う信号線間ににおいてもばらつき、表示パネルに輝度むらが発生することがあった。本実施の形態では、電流信号発生回路 5 6 の出力を電流測定回路 6 1 で測定し、出力ばらつきを補正する機能を備えており、輝度むらを低減することが可能である。

【 0 0 8 7 】

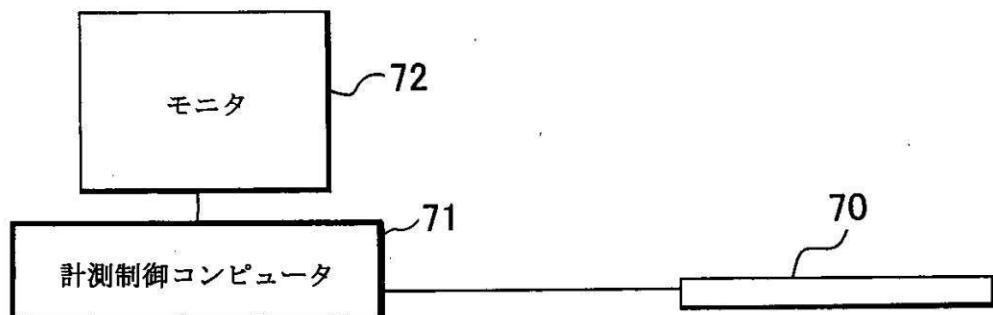

次に、図 1 6 ~ 図 1 7 を参照して、本実施の形態の有機EL表示装置の製造方法について説明する。図 1 6 は、その製造方法のうち欠陥画素検知工程及びリペア工程で用いるリペア装置としての検査装置の概略図、図 1 7 は、その検査装置を用いた製造方法の概略を

10

20

30

40

50

示す流れ図、図18は、その製造方法を説明するタイムチャートである。

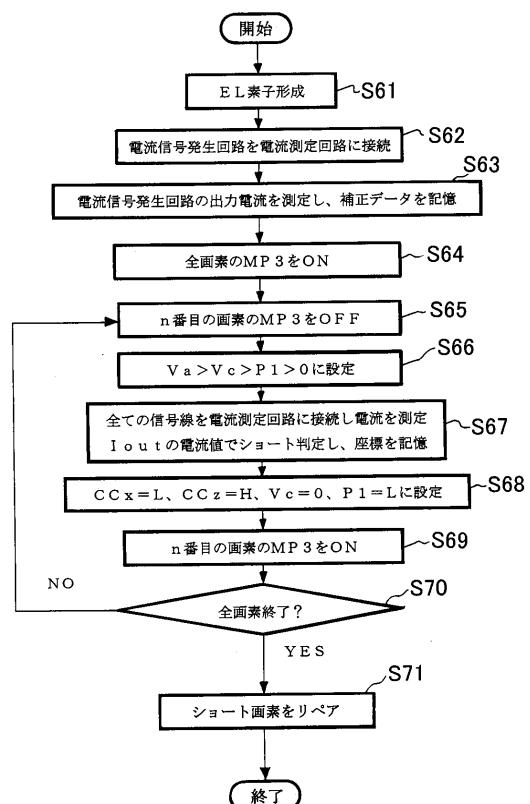

【0088】

まず、前述と同様のEL素子形成工程にて、有機EL素子を形成し(ステップS61)、その後に、図16に示す検査装置を用いた欠陥画素検知工程及びリペア工程に移行する。これに際し、まず、有機EL表示装置70を図16に示すように計測制御コンピュータ71に接続する。この計測制御コンピュータ71にはモニタ72が接続されている。

【0089】

次に、図18の期間S2において、計測制御コンピュータ71からコントローラー62を介して信号線駆動回路55に制御信号を送出し、CCxをHレベル、CCyをLレベル、CCzをHレベルにする。すると、信号線駆動回路55内の電流信号発生回路56と信号線91a～9Nc間が遮断部82により切り離され、全ての電流信号発生回路56の出力が電流測定回路61に接続される(ステップS62)。

10

【0090】

その後、期間S3で、コントローラー62から信号線駆動回路55に制御信号を送出して1つの電流信号Idataが出力されるように設定する。すると、信号線駆動回路55内の1つの電流信号発生回路56の出力電流が電流測定回路61に流れ、電流測定回路61により電流値Ioutを測定することができる。このような動作を順次行い、全ての電流信号発生回路56の電流量を測定し、測定結果を補正データとして記憶する(ステップS63)。その後、映像信号を信号線駆動回路55へ送出する場合には、記憶した補正データに基づいて信号を補正し、表示むらの発生を抑える。

20

【0091】

次に、期間S4で、計測制御コンピュータ71は、全画素が点灯するような映像信号をコントローラー62に送出し、全画素50のMP3をONにする(ステップS64)。その後、電流信号発生回路56の出力をOFFにする。このとき、P1がLレベル、P2がHレベルにあるので、MP1がOFFとなり、有機EL素子に電流は流れず、発光しない。

【0092】

次に、期間S5で、電流信号Idataを0に設定して、n番目の画素に電流プログラミングを行い、MP3をOFFにする(ステップS65)。

30

【0093】

次に、期間S6で、計測制御コンピュータ71は、コントローラー62を介してP1電源変調回路65及び電源変調回路63に制御信号を送出する。これにより、P1電源変調回路65及び電源変調回路63は、n番目の画素に属する行の行制御信号P1の電位及びカソード電位Vcを変調し、Va > Vc > P1 > 0となるように設定する(ステップS66)。

40

【0094】

次に、期間S7で、計測制御コンピュータ71からコントローラー62を介して信号線駆動回路55に制御信号を送出し、CCxをHレベル、CCzをLレベルに設定し、全ての信号線91a～9Ncを電流測定回路61に接続する(ステップS67)。ここで、信号線の電位は電流測定回路61を介してグランドに接続されているので0Vである。また、MN1のゲート電位はP1となる。よって、MN1はON状態となる。n番目の画素で有機EL素子がショートしていない場合には、ノードN1の電位はMN1を介して0Vとなる。すると、MP1のゲート電位がP1で、ノードN1の電位が0Vとなるので、MP1はOFFとなる。この場合、MP1のソース・ドレイン間がリーカして有機EL素子のアノード電位Vaが0Vとなったとしても、カソード電位VcがVc > 0の条件であるので、有機EL素子に電流は流れず、電流測定回路61で電流は検出されない。

40

【0095】

これに対し、n番目の画素の有機EL素子がショートしている場合には、期間S5～S6と同じ期間S5a～S6n後の期間S7nのように、アノード電位Vaが有機EL素子のショート箇所を介してVcとなる。これにより、MP1のゲート電位よりもMP1のソ

50

ース、ドレイン電位のほうが高くなる。よって、M P 1 がONになる。従って、カソード電源5 7 から有機E L 素子、M P 1 、及びM N 1 を介して信号線に電流が流れるので、そこから信号線駆動回路5 5 内のスイッチ部8 1 を介して電流測定回路6 1 で電流I o u t が検出される。ここで、n 番目の画素以外の画素については、M P 3 がONであることから、ノードN 1 の電位がM P 3 を介してV a となる。また、M N 1 のゲート電位P 1 よりもノードN 1 の電位が高くなる( $V a > P 1$ )。よって、M N 1 はOFFとなる。従って、n 番目の画素以外の画素からの電流測定回路6 1 への電流の流れ込みはなく、n 番目の画素の有機E L 素子のショート検査を精度良く行うことができる。

#### 【0 0 9 6】

次に、期間S 8 では、計測制御コンピュータ7 1 からコントローラー6 2 を介して信号線駆動回路5 5 に制御信号を送出し、C C x をL レベル、C C z をH レベル、V c を0 V 、P 1 をL レベルに設定する(ステップS 6 8 )。そして、期間S 9 で、n 番目の画素のM P 3 がONになるように、電流プログラミングを行って、n 番目の画素の検査を終了させる(ステップS 6 9 )。この動作は、期間S 8 n ~ S 9 n も同様である。

#### 【0 0 9 7】

上述の動作を全画素5 0 にわたって順次繰り返すことによって、表示領域全面の有機E L 素子の欠陥を検査することができる(ステップS 7 0 )。

#### 【0 0 9 8】

次いで、期間S 1 1 では、計測制御コンピュータ7 1 は、得られた欠陥画素の位置データから、正常画素を非点灯状態に、欠陥画素を点灯状態にするような画像パターンを作成し、この画像パターンに対応する映像信号をコントローラー6 2 に送出する。すると、有機E L 表示装置7 0 において、ショートが検出された欠陥画素にだけ電流が流れ、この状態を維持することによって、欠陥画素のみをリペアすることができる(ステップS 7 1 )。

#### 【0 0 9 9】

従って、本実施の形態のような上記有機E L 表示装置の製造方法であっても、第1の実施の形態と同様の効果が得られる。

#### 【0 1 0 0】

上述の効果を得るために、有機E L 表示装置の構成としては、図1 4 に示すようにアノード電圧またはカソード電圧を変調するための電源変調回路6 3 、6 4 を備えている必要がある。また、ショート画素を検出するために、行制御線駆動回路5 4 にP 1 電源変調回路6 5 を具備し、行制御信号P 1 を変調する。また、カソード電極は一般的に共通電極として表示領域全面に形成されており、通常0 V が印加される。また、行制御線駆動回路5 4 と信号線駆動回路5 6 の回路駆動電源6 6 の電位として、0 V がコントローラー6 2 から入力される。前述のカソード電圧V c の変調を行うためには、図1 4 に示すように駆動回路電源6 6 とカソード電源5 7 が独立に接続されている必要がある。

#### 【0 1 0 1】

さらに、信号線駆動回路5 6 内にシフトレジスタを備え、順次、信号線と電流測定回路6 1 を1本ずつ接続する回路を備えても同様に、ショート画素を検出することができ、上述と同様の効果が得られる。

#### 【0 1 0 2】

また、第1から第6の実施の形態においては、トランジスタ素子として表示パネルを構成するガラス基板にアモルファスシリコンまたはポリシリコンを用いたT F T を例に説明したが、本発明は必ずしもこれに限定されない。例えば、シリコン以外の無機半導体や有機半導体を用いたものであっても同様の効果は得られる。

#### 【実施例】

#### 【0 1 0 3】

以下、本発明の実施例について説明する。本実施例は、前述した第1の実施の形態に対応するものである。

#### 【0 1 0 4】

10

20

30

40

50

まず、本実施例では、画素数が横方向 960 個、縦方向 240 個、総画素数 23040 個、画素サイズ  $51 \mu\text{m} \times 153 \mu\text{m}$ 、対角寸法が 2.4 インチのアクティブマトリクス基板を作成した。その後、その上に、アノード電極として、AL と IZO をスパッタ法により、それぞれ順に 100 nm、20 nm を積層し、フォトエッチング法によって、各画素に対応する位置にアノード電極を形成した。

#### 【0105】

次に、正孔輸送性を有する NPD を抵抗加熱蒸着法により成膜速度 0.2 ~ 0.3 nm / sec の条件で成膜し、膜厚 35 nm 正孔輸送層を形成した。なお、正孔輸送層、発光層、および電子注入層は、同一の蒸着マスクを用いることにより所定の部分に蒸着した。

10

#### 【0106】

続いて、正孔輸送層の上にアルキレート錯体である Alq3 を抵抗加熱蒸着法により正孔輸送層と同様の成膜条件で膜厚 15 nm 成膜、発光層を形成した。

#### 【0107】

次に、発光層の上に抵抗加熱共蒸着法により Alq3 と炭酸セシウム (Cs3CO3) を膜厚比 9 : 1 の割合で混合されるよう、各々の蒸着速度を調整して成膜、膜厚 35 nm 電子注入層を形成した。詳しくは、それぞれの蒸着ポートにセットした材料を抵抗加熱方式で蒸発させ、有機層は 5 / sec の蒸着速度で膜形成を行った。

#### 【0108】

次に、電子注入層の上に、Ag ターゲットを用いて DC マグネットロンスパッタリング法により、膜厚が 10 nm になるようマスク成膜によりカソード電極を形成した。カソードとして Ag を採用しているが、膜厚が十分薄いため半透過膜として機能し、EL 発光した光がアノードとカソード間で多重反射することで、より色純度の高い光を取り出すことが可能である。

20

#### 【0109】

以上のようにして、基板上にアノード電極、絶縁層、正孔輸送層、発光層、電子注入電極層、カソード電極を設け、有機発光層を形成した。

#### 【0110】

次に、カバーガラス内側に酸化ストロンチウムの吸湿膜を形成し、カバーガラスの周囲に UV 硬化型シール剤を塗布し、有機 EL 素子基板に貼り合わせ、UV を 6 分照射して接着シールし、封止した。

30

#### 【0111】

このようにして作成された有機 EL 表示装置を点灯すると、4111 個の非点灯画素が検出された。これらの検出された各非点灯画素に電流 140 nA を 96 時間ほど流すと、非点灯画素は、77 個に低減した。

#### 【0112】

さらに、保護膜で封止したパネルにおいても同様の効果は見られており、保護膜としては CVD (Chemical Vapor Deposition) 装置を用いて、基板上に厚さ 3 μm の窒化シリコン膜を堆積形成したものを用いた。

40

#### 【0113】

なお、保護膜で封止した有機 EL 表示装置にレーザーリペアを試みたが、レーザー照射により保護膜が破壊され、水分が素子内に浸入し素子劣化が見られた。このように、窒化シリコン膜で封止した有機 EL 表示装置においては、レーザー照射によるリペアが非常に困難であるが、本実施例によれば、窒化シリコン膜にダメージを与えることなくリペアを行うことができるることも確認した。

#### 【図面の簡単な説明】

#### 【0114】

【図 1】本発明の第 1 の実施の形態に係る有機 EL 表示装置の構成を示すブロック図である。

#### 【図 2】第 1 の実施の形態に係る有機 EL 表示装置の製造方法の概略を示す流れ図である

50

【図3】第1の実施の形態に係る有機EL表示装置の製造方法で用いる検査装置の概略図である。

【図4】図3に示す検査装置を用いた製造方法の概略を示す流れ図である。

【図5】第1の実施の形態に係る有機EL表示装置のカソード電源を変調する場合の有機EL表示装置の構成を示すブロック図である。

【図6】本発明の第2の実施の形態に係る有機EL表示装置の製造方法で用いる検査装置の概略図である。

【図7】第2の実施の形態に係る有機EL表示装置の製造方法の概略を示す流れ図である。

【図8】第2の実施の形態に係る有機EL表示装置の製造方法の詳細を示す流れ図である。

【図9】本発明の第3の実施の形態に係る有機EL表示装置の製造方法の概略を示す流れ図である。

【図10】本発明の第4の実施の形態に係る有機EL表示装置の製造方法の概略を示す流れ図である。

【図11】本発明の第5の実施の形態に係る有機EL表示装置の構成を示すブロック図である。

【図12】第5の実施の形態に係る有機EL表示装置の画素回路図である。

【図13】図12に示す画素回路の動作を説明するタイムチャートである。

【図14】本発明の第6の実施の形態に係る有機EL表示装置の構成を示すブロック図である。

【図15】図14に示す信号線駆動回路の出力部の回路構成を示す図である。

【図16】第6の実施の形態に係る有機EL表示装置の製造方法で用いる検査装置の概略図である。

【図17】第6の実施の形態に係る有機EL表示装置の製造方法の概略を示す流れ図である。

【図18】第6の実施の形態に係る有機EL表示装置の製造方法で用いる電流検出方法を説明するタイムチャートである。

#### 【符号の説明】

##### 【0115】

1 有機EL表示装置

2 XYステージ

3 光学顕微鏡

4 CCDカメラ

5 計測制御コンピュータ

6 モニタ

7 ステージ駆動装置

8 画素

9 走査線駆動回路

10 走査線

11 信号線

12 信号線駆動回路

13 カソード線

14 カソード電源

15 アノード線

16 アノード電源

17 有機EL素子

18 コントローラー

19 電源変調回路

10

20

30

40

50

|                                             |             |    |

|---------------------------------------------|-------------|----|

| 2 0                                         | 有機 E L 表示装置 |    |

| 2 1                                         | 計測制御コンピュータ  |    |

| 2 2                                         | モニタ         |    |

| 2 3                                         | 電流測定機       |    |

| 3 0                                         | 画素          |    |

| 3 1                                         | 信号線         |    |

| 3 2                                         | 行制御線 P 1    | 10 |

| 3 3                                         | 行制御線 P 2    |    |

| 3 4                                         | 行制御線駆動回路    |    |

| 3 5                                         | 信号線駆動回路     |    |

| 3 6                                         | カソード電源      |    |

| 3 7                                         | カソード線       |    |

| 3 8                                         | アノード電源      |    |

| 3 9                                         | アノード線       |    |

| 4 0                                         | コントローラー     |    |

| 5 0                                         | 画素          |    |

| 5 2                                         | 行制御線 P 1    |    |

| 5 3                                         | 行制御線 P 2    |    |

| 5 4                                         | 行制御線駆動回路    |    |

| 5 5                                         | 信号線駆動回路     | 20 |

| 5 6                                         | 電流信号発生回路    |    |

| 5 7                                         | カソード電源      |    |

| 5 8                                         | カソード線       |    |

| 5 9                                         | アノード電源      |    |

| 6 0                                         | アノード線       |    |

| 6 1                                         | 電流測定回路      |    |

| 6 2                                         | コントローラー     |    |

| 6 3                                         | 電源変調回路      |    |

| 6 4                                         | 電源変調回路      |    |

| 6 5                                         | P 1 電源変調回路  | 30 |

| 6 6                                         | 回路駆動電源      |    |

| 7 0                                         | 有機 E L 表示装置 |    |

| 7 1                                         | 計測制御コンピュータ  |    |

| 7 2                                         | モニタ         |    |

| 8 1                                         | スイッチ部       |    |

| 8 2                                         | 遮断部         |    |

| 8 3                                         | 遮断部         |    |

| 8 4                                         | 電流信号出力線     |    |

| 9 1 a ~ 9 N c                               | 信号線         |    |

| C C x 、 C C y 、 C C z                       | 総和電流検出制御信号  | 40 |

| i ( o u t )                                 | 総和電流        |    |

| i ( d a t a )                               | 電流信号        |    |

| M 1 ~ M 1 2 、 M 1 1 ~ M 6 N 、 M 7 1 ~ M 9 N | T F T       |    |

【図2】

【図4】

【図7】

【図8】

【図9】

【図10】

【図17】

【図1】

Q1:画素選択トランジスタ

Q2:動作トランジスタ

Cs:保持容量

G1:1行目の走査線

G2:2行目の走査線

【図3】

【図5】

### Q1: 画素選択トランジスタ

## Q2:動作トランジスタ

### Cs:保持容量

### G1: 1行目の走査線

G1: 1行目の走査線

G2: 2行目の走査線

【図6】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図18】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

**H 01L 27/32 (2006.01)**F ターム(参考) 5C094 AA41 AA42 AA43 BA27 EA10 GA10 GB10

5G435 AA17 AA19 BB05 KK05

|                |                                                                                                                                                                                                                                                                          |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机EL显示装置及其制造方法                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP2007317384A5</a>                                                                                                                                                                                                                                           | 公开(公告)日 | 2009-07-09 |

| 申请号            | JP2006142738                                                                                                                                                                                                                                                             | 申请日     | 2006-05-23 |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 佳能公司                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 永山 耕平                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 永山 耕平                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | H05B33/10 H05B33/12 H01L51/50 G09F9/00 G09F9/30 H01L27/32                                                                                                                                                                                                                |         |            |

| CPC分类号         | G09G3/006 G09G3/3225 G09G2320/0223 G09G2320/043 G09G2330/08 H01L2251/568                                                                                                                                                                                                 |         |            |

| FI分类号          | H05B33/10 H05B33/12.Z H05B33/14.A G09F9/00.352 G09F9/30.365.Z                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC29 3K107/CC33 3K107/CC35 3K107/CC43 3K107/CC45 3K107/DD44Y 3K107/EE04 3K107/GG28 3K107/GG31 3K107/GG56 3K107/GG57 5C094/AA41 5C094/AA42 5C094/AA43 5C094/BA27 5C094/EA10 5C094/GA10 5C094/GB10 5G435/AA17 5G435/AA19 5G435/BB05 5G435/KK05 |         |            |

| 代理人(译)         | 永井道雄                                                                                                                                                                                                                                                                     |         |            |

| 其他公开文献         | JP2007317384A                                                                                                                                                                                                                                                            |         |            |

#### 摘要(译)

提供一种能够在不损害像素的正常部分的情况下断开缺陷部分的有机EL显示装置及其制造方法。包括多个包括有机EL元件的像素的有机EL显示装置的制造方法包括在阴极和阳极之间形成包括由有机化合物制成的发光层的有机EL元件的步骤(S1)。此外，该方法包括检测在阴极和阳极之间发生短路的像素的位置的步骤(S2)，在阴极和阳极之间选择性地施加电压到检测的像素的步骤以及用于破坏的修复步骤(S3)。The