(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-128521

(P2005-128521A)

(43) 公開日 平成17年5月19日(2005.5.19)

| (51) Int.CI. <sup>7</sup> | F 1                     | テーマコード (参考) |

|---------------------------|-------------------------|-------------|

| <b>G09G 3/30</b>          | G09G 3/30               | J 3K007     |

| <b>G09G 3/20</b>          | G09G 3/20               | 611H 5C080  |

| <b>H05B 33/14</b>         | G09G 3/20<br>H05B 33/14 | 624B A      |

審査請求 未請求 請求項の数 11 O L (全 15 頁)

|              |                              |            |                                                                               |

|--------------|------------------------------|------------|-------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2004-289368 (P2004-289368) | (71) 出願人   | 000001889<br>三洋電機株式会社<br>大阪府守口市京阪本通2丁目5番5号                                    |

| (22) 出願日     | 平成16年9月30日 (2004.9.30)       | (74) 代理人   | 100075258<br>弁理士 吉田 研二                                                        |

| (31) 優先権主張番号 | 特願2003-342469 (P2003-342469) | (74) 代理人   | 100096976<br>弁理士 石田 純                                                         |

| (32) 優先日     | 平成15年9月30日 (2003.9.30)       | (72) 発明者   | 佐々木 昭史<br>大阪府守口市京阪本通2丁目5番5号 三<br>洋電機株式会社内                                     |

| (33) 優先権主張国  | 日本国 (JP)                     | (72) 発明者   | 松本 昭一郎<br>大阪府守口市京阪本通2丁目5番5号 三<br>洋電機株式会社内                                     |

|              |                              | F ターム (参考) | 3K007 AB18 BA06 DB03 GA00<br>5C080 AA06 BB05 DD05 DD22 EE29<br>FF11 JJ03 JJ04 |

(54) 【発明の名称】有機EL画素回路

## (57) 【要約】

【課題】駆動トランジスタのしきい値電圧の変動を効果的に補償する。

【解決手段】選択TFT20がオフの状態において、制御TFT30をオフし、リセット制御TFT26、短絡TFT28をオンする。これによってコンデンサ22の選択TFT20側がPVDDにセットされた状態で、短絡TFT28がオンして駆動TFT24がダイオード接続される。そこで、駆動TFT24のゲートに駆動TFT24のしきい値電圧だけPVDDより低い電圧がセットされる。次に、リセット制御TFT26、短絡TFT28をオフし、制御TFT30をオンすることで、データラインDLのビデオ信号の電圧により駆動TFT24のゲート電圧がシフトされ、これによって駆動TFT24がオンして有機EL素子32に駆動電流が供給される。これによって、駆動TFT24のしきい値電圧によらず、ビデオ信号に応じて駆動電流を制御できる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

一端がデータラインに接続された選択トランジスタと、

この選択トランジスタの他端に一端が接続されたコンデンサと、

このコンデンサの他端に制御端が接続され、一端が電源ラインに接続された駆動トランジスタと、

この駆動トランジスタの他端に一端が接続された制御トランジスタと、

この制御トランジスタの他端に接続された有機EL素子と、

前記駆動トランジスタをダイオード接続する短絡トランジスタと、

前記選択トランジスタとコンデンサの接続部に一端が接続され、他端が一定電圧の電源に接続されたリセット制御トランジスタと、

を含み、

前記選択トランジスタがオフされている期間に、前記制御トランジスタをオフするとともに、前記短絡トランジスタおよびリセット制御トランジスタをオンして、前記駆動トランジスタの制御端に駆動トランジスタのしきい値電圧に対応する電圧を設定し、その後選択トランジスタをオンして、データラインに供給されるデータ電圧により前記駆動トランジスタの制御端の電圧をシフトさせて、このシフトした電圧に応じて駆動トランジスタに有機EL素子の駆動電流を流すことを特徴とする有機EL画素回路。10

**【請求項 2】**

請求項 1 に記載の有機EL画素回路において、20

前記リセット制御トランジスタの他端が接続される電源は、前記駆動トランジスタの一端が接続される電源ラインであることを特徴とする有機EL画素回路。

**【請求項 3】**

請求項 1 または 2 に記載の有機EL画素回路において、

前記短絡トランジスタと、リセット制御トランジスタは、同一極性であり、その制御端は、同一の第 1 リセット制御ラインに接続されていることを特徴とする有機EL画素回路。30

**【請求項 4】**

請求項 3 に記載の有機EL画素回路において、30

前記制御トランジスタの制御端は、前記短絡トランジスタおよびリセット制御トランジスタが接続される第 1 リセット制御ラインとは別に設けられた第 2 リセット制御ラインに接続されており、前記制御トランジスタをオフした後に前記短絡トランジスタおよびリセット制御トランジスタをオンし、前記短絡トランジスタおよびリセット制御トランジスタをオフした後に前記制御トランジスタをオンすることを特徴とする有機EL画素回路。

**【請求項 5】**

請求項 3 に記載の有機EL画素回路において、40

前記制御トランジスタの制御端は、前記短絡トランジスタおよびリセット制御トランジスタが接続される第 1 リセット制御ラインとは別に設けられた第 2 リセット制御ラインに接続されており、前記短絡トランジスタおよびリセット制御トランジスタをオンした後に前記制御トランジスタをオフし、前記短絡トランジスタおよびリセット制御トランジスタをオフした後に前記制御トランジスタをオンすることを特徴とする有機EL画素回路。

**【請求項 6】**

請求項 4 または 5 に記載の有機EL画素回路において、

前記制御トランジスタがオンした後に、前記選択トランジスタをオンして、データラインに供給されるデータ電圧により前記駆動トランジスタの制御端の電圧をシフトさせて、このシフトした電圧に応じて前記駆動トランジスタに有機EL素子の駆動電流を流すことを特徴とする有機EL画素回路。

**【請求項 7】**

請求項 4 または 5 に記載の有機EL画素回路において、

前記選択トランジスタをオンして、データラインに供給されるデータ電圧により前記駆動トランジスタをオンして、前記短絡トランジスタをオフし、前記短絡トランジスタおよびリセット制御トランジスタをオフした後に前記制御トランジスタをオンすることを特徴とする有機EL画素回路。50

動トランジスタの制御端の電圧をシフトさせた後、前記選択トランジスタがオンの期間において前記制御トランジスタをオンし、その後前記選択トランジスタをオフすることを特徴とする有機EL画素回路。

【請求項8】

請求項3に記載の有機EL画素回路において、

前記制御トランジスタは、前記短絡トランジスタおよびリセット制御トランジスタとは反対の極性であり、前記制御トランジスタの制御端は前記短絡トランジスタおよびリセット制御トランジスタと同一の第1リセット制御ラインに接続されていることを特徴とする有機EL画素回路。

【請求項9】

10

請求項1～8のいずれか1に記載の回路において、

前記駆動トランジスタは、pチャネルトランジスタであり、

前記制御トランジスタは、nチャネルトランジスタであることを特徴とする有機EL画素回路。

【請求項10】

請求項9に記載の回路において、

前記駆動トランジスタと、前記制御トランジスタとの間に、電流を駆動トランジスタ側から制御トランジスタ側へ向けて流すダイオードを配置することを特徴とする有機EL画素回路。

【請求項11】

20

請求項10に記載の回路において、

前記駆動トランジスタのドレインと、前記制御トランジスタのドレインを連続する半導体層によって形成し、これらドレイン同士の接続部において、PN接合のダイオードを形成することを特徴とする有機EL画素回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、有機EL素子などの発光素子を含む画素回路に関する。

【背景技術】

【0002】

30

従来より、有機EL素子を用いた有機ELパネルが知られており、その開発が進んでいる。この有機ELパネルにおいては、有機EL素子をマトリクス状に配置し、この有機EL素子の発光を個別に制御することで、表示を行う。特に、アクティブマトリクスタイプの有機ELパネルでは、画素毎に表示制御用のTFTを有し、このTFTの動作制御により画素毎の発光を制御できるため、非常に高精度の表示を行うことができる。

【0003】

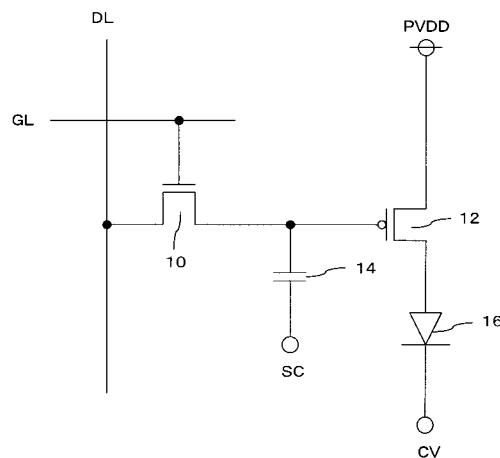

図5に、アクティブマトリクスタイプの有機ELパネルにおける画素回路の一例を示す。画素の輝度を示すデータ電圧が供給されるデータラインは、ゲートがゲートラインに接続されたnチャネルの選択TFT10を介し、駆動TFT12のゲートに接続されている。また、駆動TFT12のゲートには、他端が容量電源ラインに接続された保持容量14の一端が接続され、駆動TFT12のゲート電圧を保持する。

40

【0004】

駆動TFT12のソースは、EL電源ラインに接続され、ドレインは有機EL素子16のアノードに接続され、有機EL素子16のカソードがカソード電源に接続されている。

【0005】

このような画素回路がマトリクス状に配置されており、所定のタイミングで、水平ライン毎に設けられたゲートラインがHレベルとなり、その行の選択TFT10がオン状態になる。この状態で、データラインには、順次データ電圧が供給されるため、そのデータ電圧は保持容量14に供給保持され、ゲートラインがLレベルとなってもその時の電圧を保持する。

50

## 【0006】

そして、この保持容量14に保持された電圧に応じて、駆動TFT12が動作して対応する駆動電流がEL電源からの有機EL素子16を介し、カソード電源に流れ、有機EL素子16がデータ電圧に応じて発光する。

## 【0007】

そして、ゲートラインを順次Hレベルとして、入力されてくるビデオ信号を対応する画素にデータ電圧として順次供給することで、マトリクス状に配置された、有機EL素子16がデータ電圧に応じて発光し、ビデオ信号についての表示が行われる。

## 【0008】

【特許文献1】特表2002-514320号公報

10

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0009】

しかし、このような画素回路において、マトリクス状に配置された画素回路の駆動TFTのしきい値電圧がばらつくと、輝度がばらつくことになり、表示品質が低下するという問題がある。そして、表示パネル全体の画素回路を構成するTFTについて、その特性を同一にすることは難しく、そのオンオフのしきい値がばらつくことを防止することは難しい。

## 【0010】

そこで、駆動TFTにおけるしきい値のバラツキの表示に対する影響を防止することが望まれる。

20

## 【0011】

ここで、TFTのしきい値の変動への影響を防止するための回路については、従来より各種の提案がある（例えば、上記特許文献1）。

## 【0012】

しかし、この提案では、しきい値変動の補償をするための回路を必要とする。従って、このような回路を用いると、画素回路の素子数が増加し、開口率が小さくなってしまうという問題があった。また、補償のための回路を追加した場合、画素回路を駆動するための周辺回路についても変更が必要となるという問題もあった。

## 【0013】

本発明は、効果的に駆動トランジスタのしきい値電圧の変動を補償できる画素回路を提供する。

30

## 【課題を解決するための手段】

## 【0014】

本発明は、一端がデータラインに接続された選択トランジスタと、この選択トランジスタの他端に一端が接続されたコンデンサと、このコンデンサの他端に制御端が接続され、一端が電源ラインに接続された駆動トランジスタと、この駆動トランジスタの他端に一端が接続された制御トランジスタと、この制御トランジスタの他端に接続された有機EL素子と、前記駆動トランジスタをダイオード接続する短絡トランジスタと、前記選択トランジスタとコンデンサの接続部に一端が接続され、他端が一定電圧の電源に接続されたリセット制御トランジスタと、を含み、前記選択トランジスタがオフされている期間に、前記制御トランジスタをオフするとともに、前記短絡トランジスタおよびリセット制御トランジスタをオンして、前記駆動トランジスタの制御端に駆動トランジスタのしきい値電圧に対応する電圧を設定し、その後選択トランジスタをオンして、データラインに供給されるデータ電圧により前記駆動トランジスタの制御端の電圧をシフトさせて、このシフトした電圧に応じて駆動トランジスタに有機EL素子の駆動電流を流すことを特徴とする。

40

## 【0015】

また、前記リセット制御トランジスタの他端が接続される電源は、前記駆動トランジスタの一端が接続される電源ラインであることが好適である。

## 【0016】

50

また、前記短絡トランジスタと、リセット制御トランジスタは、同一極性であり、その制御端は、同一の第1リセット制御ラインに接続されていることが好適である。

【0017】

また、前記制御トランジスタの制御端は、前記短絡トランジスタおよびリセット制御トランジスタが接続される第1リセット制御ラインとは別に設けられた第2リセット制御ラインに接続されており、前記制御トランジスタをオフした後に前記短絡トランジスタおよびリセット制御トランジスタをオンし、前記短絡トランジスタおよびリセット制御トランジスタをオフした後に前記制御トランジスタをオンすることが好適である。

【0018】

また、前記制御トランジスタの制御端は、前記短絡トランジスタおよびリセット制御トランジスタが接続される第1リセット制御ラインとは別に設けられた第2リセット制御ラインに接続されており、前記短絡トランジスタおよびリセット制御トランジスタをオンした後に前記制御トランジスタをオフし、前記短絡トランジスタおよびリセット制御トランジスタをオフした後に前記制御トランジスタをオンすることが好適である。

【0019】

また、前記制御トランジスタがオンした後に、前記選択トランジスタをオンして、データラインに供給されるデータ電圧により前記駆動トランジスタの制御端の電圧をシフトさせて、このシフトした電圧に応じて前記駆動トランジスタに有機EL素子の駆動電流を流すことが好適である。

【0020】

また、前記選択トランジスタをオンして、データラインに供給されるデータ電圧により前記駆動トランジスタの制御端の電圧をシフトさせた後、前記選択トランジスタがオンの期間において前記制御トランジスタをオンし、その後前記選択トランジスタをオフすることが好適である。

【0021】

また、前記制御トランジスタは、前記短絡トランジスタおよびリセット制御トランジスタとは反対の極性であり、前記制御トランジスタの制御端は前記短絡トランジスタおよびリセット制御トランジスタと同一の第1リセット制御ラインに接続されていることが好適である。

【0022】

また、前記駆動トランジスタは、Pチャネルトランジスタであり、前記制御トランジスタは、nチャネルトランジスタであることが好適である。

【0023】

また、前記駆動トランジスタと、前記制御トランジスタとの間に、電流を駆動トランジスタ側から制御トランジスタ側へ向けて流すダイオードを配置することが好適である。

【0024】

また、前記駆動トランジスタのドレインと、前記制御トランジスタのドレインを連続する半導体層によって形成し、これらドレイン同士の接続部において、PN接合のダイオードを形成することが好適である。

【発明の効果】

【0025】

以上説明したように、本発明によれば、選択トランジスタがオフされている期間に、制御トランジスタをオフするとともに、短絡トランジスタおよびリセット制御トランジスタをオンして、駆動トランジスタの制御端に駆動トランジスタのしきい値電圧に対応する電圧を設定し、これをコンデンサに保持する。従って、各画素の駆動トランジスタの間でしきい値電圧にバラツキがあっても、これを補償して、ビデオ信号に応じた電流を有機EL素子に供給することができる。

【0026】

特に、リセット制御トランジスタにより、コンデンサの選択トランジスタ側の電圧を一定電位（例えば、電源電圧）に設定している。このため、前の書き込みデータ影響を排除

10

20

30

40

50

して、短絡トランジスタをオンしたときに、コンデンサに駆動トランジスタのしきい値電圧に応じた電圧を確実に保持することができる。また、しきい値電圧のセットの際には、データラインの電圧を変更する必要はなく、水平ドライバの動作が簡略化される。また、選択トランジスタがオフの期間であれば、データラインのリセットをいずれのタイミングでも行うことができ、リセットの時間を長くして、確実なしきい値電圧のセットが行える。

#### 【0027】

また、制御トランジスタの制御端と、短絡トランジスタおよびリセット制御トランジスタの制御端とを別のリセット制御ラインに接続することで、短絡トランジスタと、制御トランジスタの同時オンを確実に防止することができる。

10

#### 【0028】

また、制御トランジスタと短絡トランジスタおよびリセット制御トランジスタの極性を反対にし、制御トランジスタの制御端と、短絡トランジスタおよびリセット制御トランジスタの制御端とを同一リセット制御ラインに接続することで、ラインの本数を減少することができる。

#### 【0029】

また、選択トランジスタがオンの期間において制御トランジスタをオンし、その後選択トランジスタをオフする。制御トランジスタをオンすると、有機EL素子に電流が流れ始め、これによって、駆動トランジスタの有機EL素子側の端子の電圧が低くなり、これによって駆動トランジスタの制御端電圧が低くなりやすい。しかし、本発明では、この時に選択トランジスタがオンしている。そこで、コンデンサのデータライン側の電圧が変化しにくく、従って駆動トランジスタの制御端電圧の変動を抑制することができる。

20

#### 【0030】

また、前記駆動トランジスタは、pチャネルトランジスタであり、前記制御トランジスタは、nチャネルトランジスタであり、前記駆動トランジスタと、制御トランジスタとの間にダイオードが形成されていることで、駆動トランジスタと制御トランジスタを同一の半導体層を用いて形成することができ、効率的なレイアウトが可能になる。

20

#### 【発明を実施するための最良の形態】

#### 【0031】

以下、本発明の実施形態について、図面に基づいて説明する。

30

#### 【0032】

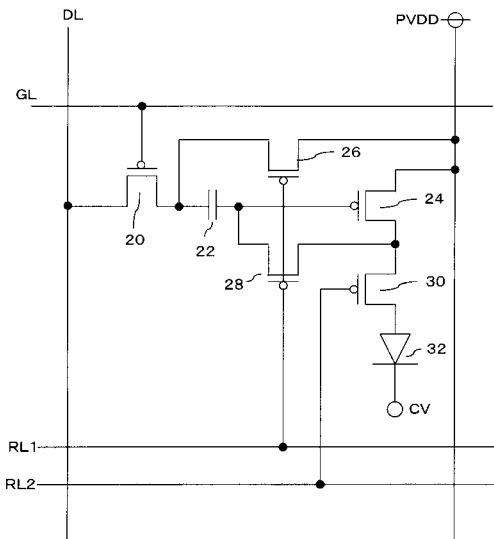

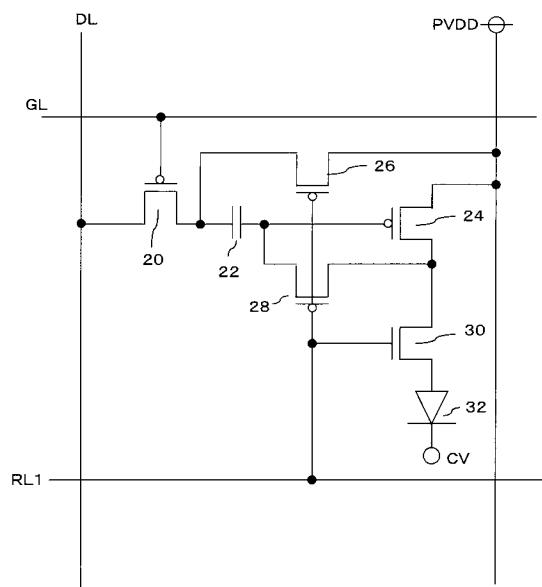

図1は、実施形態に係る1画素の画素回路の構成を示す図である。垂直方向に伸びるデータラインDLには、pチャネルの選択TFT20のドレインが接続されている。この選択TFT20のゲートは水平方向に伸びるゲートラインGLに接続され、ソースはコンデンサ22の一端に接続されている。コンデンサ22の他端はpチャネルの駆動TFT24のゲートに接続されている。さらに、選択TFT20のソースと、コンデンサ22の接続部には、pチャネルのリセット制御TFT26のドレインが接続されており、このリセット制御TFT26のソースは垂直方向に伸びる電源ラインPVDに接続されている。さらに、駆動TFT24のゲートには、pチャネルの短絡TFT28のソースが接続され、この短絡TFT28のドレインは、駆動TFT24のドレインに接続されている。そして、リセット制御TFT26と短絡TFT28のゲートは、リセットラインRL1に接続されている。

40

#### 【0033】

また、駆動TFT24のソースは、電源ラインPVDに接続され、ドレインはpチャネルの制御TFT30のソースに接続されている。この制御TFT30のドレインは、有機EL素子32のアノードに接続され、ゲートは水平方向に伸びるリセットラインRL2に接続されている。有機EL素子32のカソードは、カソード電源CVに接続されている。ここで、通常の場合、有機EL素子32のカソードは全画素共通になっており、このカソードが所定の電位のカソード電源CVに接続されている。

#### 【0034】

50

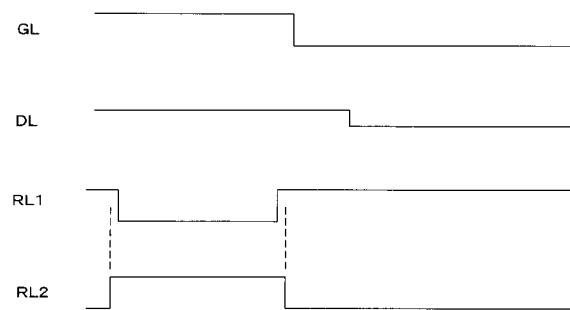

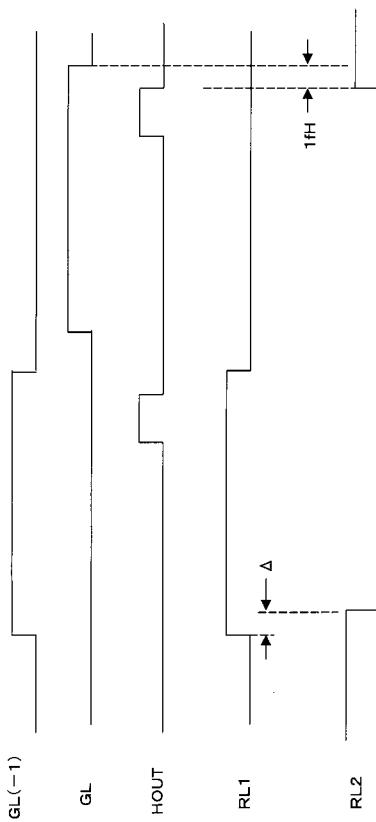

次に、この画素回路の動作について、図2に基づいて説明する。ゲートラインGLが該当水平ライン(行)の画素が選択される1H(水平期間)の選択期間だけLレベルになる。そして、この選択期間に先だって、リセットラインRL2がHレベルになり、次に所定の短期間だけ遅れてリセットラインRL1がLレベルになる。これによって、選択TFT20がオフされている状態で、制御TFT30がオフされ、さらにリセット制御TFT26と短絡TFT28がオンされる。

#### 【0035】

これによって、コンデンサ22の駆動TFT24のゲートに接続されているのと反対側がPVDDの電位に保たれている状態で、駆動TFT24のゲート・ドレイン間は短絡TFT28によって短絡され、駆動TFT24はダイオード接続される。そこで、駆動TFT24のゲート電位は、PVDDよりしきい値電圧Vtだけ低い電圧になり、このしきい値電圧Vtの電圧が、コンデンサ22に保持される。そして、このようなコンデンサ22への充電が完了した後、リセットラインRL1がHレベルとなり、これに対し所定の短時間後に、リセットラインRL2がLレベルになり、リセット制御TFT26と短絡TFT28がオフされ、その後制御TFT30がオンされる。

#### 【0036】

次に、該当水平ラインの選択期間に入り、ゲートラインGLがLレベルになり、これによって選択TFT20がオンになる。この状態で、水平ドライバは、ビデオラインから供給される各画素のビデオ信号を各データラインに順次供給する。従って、データラインDLには、対応する画素についてビデオ信号が設定される。そして、このデータラインDLは、ゲートラインGLがHレベルになるまで、ビデオ信号の電位を維持する。このために、データラインDLに、コンデンサなどを接続して、電位を維持できるようにするとい。

#### 【0037】

そして、ゲートラインGLをHレベルに戻した後、一旦データラインを一定電位(例えば、PVDD)に戻す。これによって、次のビデオ信号についてのデータラインDLへのセットに問題がなくなる。

#### 【0038】

データラインDLがビデオ信号の電位に設定されると、コンデンサ22の他端である駆動TFT24のゲート電位は、ビデオ信号の電位によりシフトされ、このゲート電位に応じた電流が駆動TFT24、制御TFT30を介し、有機EL素子32に流れる。そして、ゲートラインGLがHレベルに復帰して選択TFT20がオフした後も、駆動TFT24のゲート電位はそのときの電圧のまま保たれる。

#### 【0039】

このように、本実施形態では、最初に駆動TFT24のゲートに、PVDDより駆動TFT24のしきい値電圧Vt分だけ低い電圧を設定し、これをコンデンサ22に保持する。従って、各画素の駆動TFT24の間でしきい値電圧Vtにバラツキがあっても、これを補償して、ビデオ信号に応じた電流を有機EL素子32に供給することができる。

#### 【0040】

特に、リセット制御TFT26により、コンデンサ22の選択TFT20側の電圧を一定電位(この例ではPVDD)に設定している。このため、前フレームでの書き込みデータの影響を排除して、短絡TFT28をオンしたときに、コンデンサ22に駆動TFT24のしきい値電圧Vtに応じた電圧を確実に保持することができる。また、しきい値電圧のセットの際には、データラインDLの電圧を変更する必要はなく、水平ドライバの動作が簡略化される。また、該当するゲートラインGLがHレベルの期間であれば、データラインのリセットをいずれのタイミングでも行うことができ、リセットの時間を長くして、確実なしきい値電圧のセットが行える。

#### 【0041】

さらに、本実施形態では、リセット制御TFT26と短絡TFT28を同時に駆動するが、制御TFT30のオフの期間を、リセット制御TFT26と短絡TFT28のオンの

10

20

30

40

50

期間より長くして、制御 TFT30 のオフの期間にのみ、リセット制御 TFT26 と短絡 TFT28 がオンするようにしている。これによって、制御 TFT30 がオンしているときに、駆動 TFT24 がダイオード接続されることを確実に防止でき、有機 EL 素子 32 に不要な電流が流れてしまうことを確実に防止することができる。

#### 【0042】

また、本画素回路では、トランジスタとして、すべて p チャネル TFT を使用しており、その作成が容易となる。しかし、駆動 TFT24 以外は、n チャネル TFT に変更しても何ら問題はない。なお、制御信号の極性は反転する必要がある。また、駆動 TFT24 も、そのソース側電位を固定する手段を設ければ、n チャネル TFT を採用することができる。

10

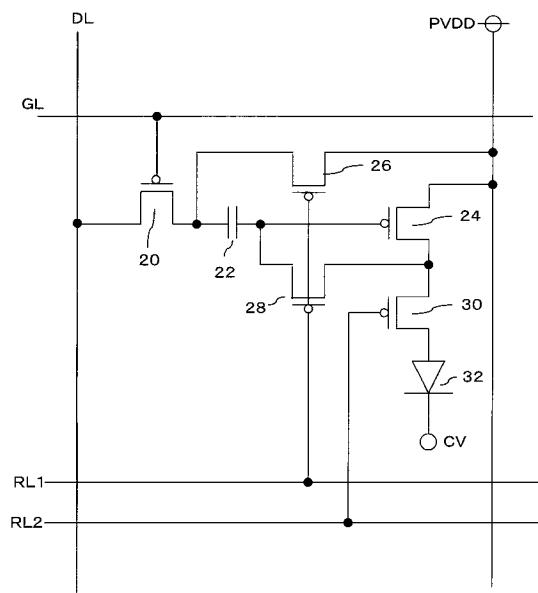

#### 【0043】

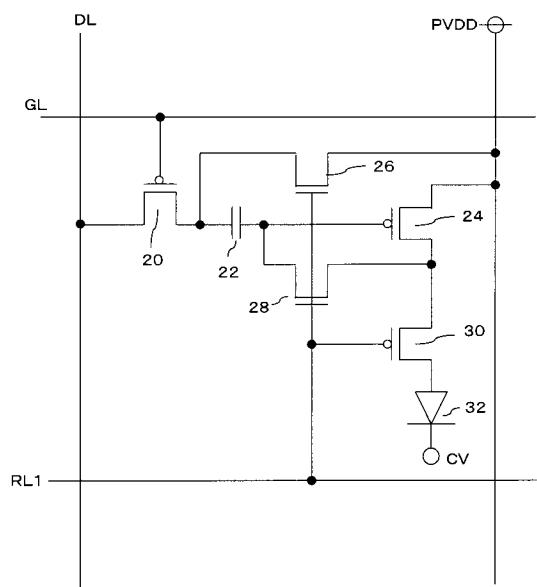

図 3 に、他の構成例を示す。この例では、制御 TFT30 にリセット制御 TFT26 および短絡 TFT28 とは、反対の極性である n チャネル TFT を利用している。そして、この n チャネルの制御 TFT30 のゲートは、リセット制御 TFT26 および短絡 TFT28 のゲートとともにリセットライン RL1 に接続されている。これによって、リセットライン RL1 を H レベルにセットすることで、制御 TFT30 がオン、リセット制御 TFT26 および短絡 TFT28 がオフされ、リセットライン RL1 を L レベルにセットすることで、制御 TFT30 がオフ、リセット制御 TFT26 および短絡 TFT28 がオンされる。

#### 【0044】

この構成では、1 本のリセットライン RL1 を利用して、制御 TFT30 、リセット制御 TFT26 および短絡 TFT28 のオンオフを制御する。従って、リセットラインを 1 本にすることができるというメリットがある。また、制御 TFT30 のオフと、短絡 TFT28 のオンが同時に行われるため、両者がオンする可能性があるが、制御 TFT30 が n チャネルであり、p チャネルの短絡 TFT28 より動作が速く先にオフするため、両者が同時オンすることを防止できている。

20

#### 【0045】

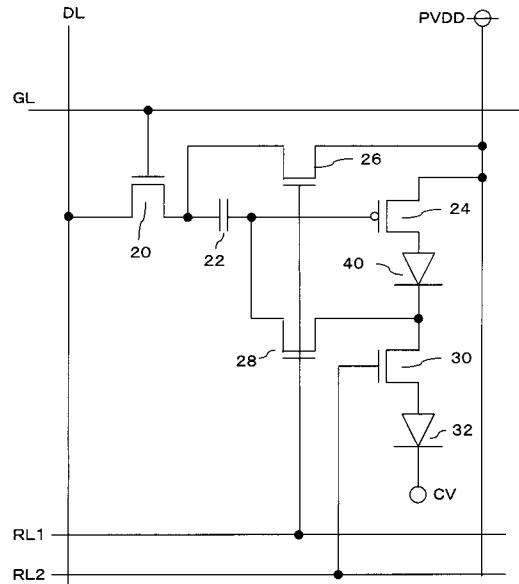

図 4 に、他の構成例を示す。この例では、リセット制御 TFT26 および短絡 TFT28 を n チャネル TFT とし、制御 TFT30 にその反対の極性の p チャネル TFT を利用している。そして、この p チャネルの制御 TFT30 のゲートは、リセット制御 TFT26 および短絡 TFT28 のゲートとともにリセットライン RL1 に接続されている。これによって、リセットライン RL1 を H レベルにセットすることで、リセット制御 TFT26 および短絡 TFT28 がオン、制御 TFT30 がオフされ、リセットライン RL1 を L レベルにセットすることで、リセット制御 TFT26 および短絡 TFT28 がオフ、制御 TFT30 がオンされる。

30

#### 【0046】

この構成では、図 3 の構成と同様に、1 本のリセットライン RL1 を利用して、リセット制御 TFT26 、短絡 TFT28 および制御 TFT30 のオンオフを制御しているため、同様にリセットラインを 1 本にできるというメリットを有する。

40

#### 【0047】

##### 「さらに他の構成例」

図 6 には、さらに他の構成例を示す。この例では、駆動 TFT24 以外の選択 TFT20 、リセット制御 TFT26 、短絡 TFT28 、制御 TFT30 に n チャネル TFT を利用している。

#### 【0048】

そして、駆動 TFT24 と、制御 TFT30 は、1 つの連続する半導体層を用いて構成されている。駆動 TFT24 のドレインは、p 型不純物がドープされており、一方制御 TFT30 のドレインは、n 型不純物がドープされている。ダイオード 40 は、この連続する半導体層における p-n 接合によって生じるものである。ここで、図のように、ダイオード 40 を短絡 TFT28 との接続部より、駆動 TFT24 側に配置することで、短絡 TFT

50

T 2 8 から制御 T F T 3 0 への電流が阻止されることはなくなり、駆動 T F T 2 4 のゲート電圧のリセットが問題なく行える。なお、駆動 T F T 2 4 と、制御 T F T 3 0 を別個の半導体層を用いて構成し、その接続はメタル層を利用すれば、ダイオード 4 0 を省略できるが、この場合メタル層との 2 つのコンタクトが必要となり、レイアウト時に不利となる。

#### 【 0 0 4 9 】

制御 T F T 3 0 のソースは、有機 E L 素子 3 2 のアノードに接続され、ゲートは水平方向に伸びるリセットライン R L 2 に接続されている。有機 E L 素子 3 2 のカソードは、カソード電源 C V に接続されている。ここで、通常の場合、有機 E L 素子 3 2 のカソードは全画素共通になっており、このカソードが所定の電位のカソード電源 C V に接続されている。

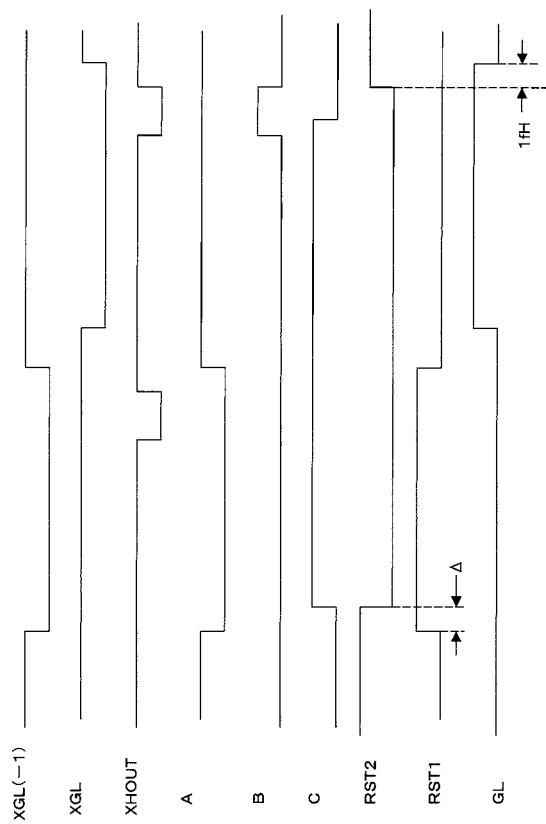

#### 【 0 0 5 0 】

次に、この画素回路の動作について、図 7 に基づいて説明する。ゲートライン G L が該当水平ライン（行）の画素が選択される 1 H ( 水平期間 ) の選択期間だけ H レベルになる。図において、ゲートライン G L ( - 1 ) は、該当水平ラインの 1 つ上の水平ラインについてのゲートラインであり、1 H 前のタイミングで H レベルになる。そして、G L ( - 1 ) が H レベルとなるとこれと同時にリセットライン R L 1 が H レベルになる。このリセットライン R L 1 の H レベルによって、選択 T F T 2 0 がオフ、制御 T F T 3 0 がオンの状態で、リセット制御 T F T 2 6 および短絡 T F T 2 8 がオンし、有機 E L 素子 3 2 に所定の電流が流れる。これによって、コンデンサ 2 2 の選択 T F T 2 0 側が電源電圧 P V D D の状態で、駆動 T F T 2 4 のドレインソース間が短絡され、駆動 T F T 2 4 のゲートから電荷が引き抜かれ、リセットされる。

#### 【 0 0 5 1 】

次に、所定の短期間だけ遅れてリセットライン R L 2 が L レベルになり、制御 T F T 3 0 がオフする。一方、リセット制御 T F T 2 6 と短絡 T F T 2 8 はオンしているため、コンデンサ 2 2 の駆動 T F T 2 4 のゲートに接続されているのと反対側が P V D D の電位に保たれている状態で、駆動 T F T 2 4 のゲート・ドレイン間は短絡 T F T 2 8 によって短絡され、駆動 T F T 2 4 はダイオード接続される。そこで、駆動 T F T 2 4 のゲート電位は、P V D D よりしきい値電圧 V t だけ低い電圧になり、このしきい値電圧 V t の電圧が、コンデンサ 2 2 に保持される。

#### 【 0 0 5 2 】

このように、1 H 前の水平期間において、コンデンサ 2 2 に駆動 T F T 2 4 のしきい値電圧 V t が充電される。次に、リセットライン R L 1 が L レベルとなり、リセット制御 T F T 2 6 と短絡 T F T 2 8 がオフされる。ここで、リセットライン R L 2 は、L レベルに維持され、制御 T F T 3 0 はオフのままにする。

#### 【 0 0 5 3 】

次に、該当水平ラインの選択期間に入り、ゲートライン G L が H レベルになり、これによって選択 T F T 2 0 がオンになる。この状態で、水平ドライバは、ビデオライン D L から供給される各画素のビデオ信号を各データライン D L に順次供給する。従って、データライン D L には、対応する画素についてビデオ信号が設定される。そして、このデータライン D L は、ゲートライン G L が L レベルになるまで、ビデオ信号の電位を維持する。このために、データライン D L に、コンデンサなどを接続して、電位を維持できるようになるとよい。

#### 【 0 0 5 4 】

データライン D L がビデオ信号の電位に設定されると、コンデンサ 2 2 の他端である駆動 T F T 2 4 のゲート電位は、ビデオ信号の電圧（データ電圧）によりシフトされる。そして、リセットライン R L 2 が H レベルとなり、制御 T F T 3 0 がオンとなり、駆動 T F T 2 4 にそのゲート電位に応じた電流が流れ、これが制御 T F T 3 0 を介し、有機 E L 素子 3 2 に流れる。ゲートライン G L が L レベルに復帰して選択 T F T 2 0 がオフした後も、駆動 T F T 2 4 のゲート電位はそのときの電圧のまま保たれ、有機 E L 素子 3 2 にはビ

10

20

30

40

50

デオ信号の電圧に応じた電流が流れ、発光する。

【0055】

そして、ゲートライン G L を L レベルに戻した後、一旦データライン D L を一定電位（例えば、P V D D）に戻す。これによって、次のビデオ信号についてのデータライン D L へのセットに問題がなくなる。

【0056】

このように、本実施形態では、最初に駆動 T F T 2 4 のゲートに、P V D D より駆動 T F T 2 4 のしきい値電圧 V t 分だけ低い電圧を設定し、これをコンデンサ 2 2 に保持する。従って、各画素の駆動 T F T 2 4 の間でしきい値電圧 V t にバラツキがあっても、これを補償して、ビデオ信号に応じた電流を有機 E L 素子 3 2 に供給することができる。

10

【0057】

特に、リセット制御 T F T 2 6 により、コンデンサ 2 2 の選択 T F T 2 0 側の電圧を一定電位（この例では P V D D）に設定している。このため、前フレームでの書き込みデータ影響を排除して、短絡 T F T 2 8 をオンしたときに、コンデンサ 2 2 に駆動 T F T 2 4 のしきい値電圧 V t に応じた電圧を確実に保持することができる。また、しきい値電圧 V t のセットの際には、データライン D L の電圧を変更する必要はなく、水平ドライバの動作が簡略化される。また、該当するゲートライン G L が L レベルの期間であれば、駆動トランジスタのゲート電圧のリセットをいずれのタイミングでも行うこともでき、リセットの時間を長くして、確実なしきい値電圧のセットが行える。

20

【0058】

さらに、制御 T F T 3 0 がオンしている状態で、リセット制御 T F T 2 6 と短絡 T F T 2 8 を同時にオンする。このため、駆動 T F T 2 4 のゲート電圧のリセットが確実に行える。

【0059】

そして、本実施形態では、ゲートライン G L が H レベルで選択 T F T 2 0 がオンしている状態で、リセットライン R L 2 を H レベルとして、制御 T F T 3 0 をオンする。制御 T F T 3 0 がオンすると、有機 E L 素子 3 2 に電流が流れ始め、駆動 T F T 2 4 のドレイン電圧が下がり、この影響でそのゲート電圧も下がりやすい。本実施形態では、この制御 T F T 3 0 がオンするときに、選択 T F T 2 0 がオンであり、コンデンサ 2 2 の一端がデータライン D L に接続されている。従って、制御 T F T 3 0 がオンすることで、駆動 T F T 2 4 のドレイン電位が変動しても、コンデンサ 2 2 の一端の電位は変動しにくいのでゲート電位は変動しにくく、入力されたビデオデータに則した電位を保持することができ、データ電圧に応じた有機 E L 素子 3 2 の発光が達成できる。

30

【0060】

また、制御 T F T 3 0 を p チャネルにすると、リーク電流が生じやすく、駆動 T F T 2 4 のゲートドレイン間を短絡 T F T 2 8 をオンして駆動 T F T 2 4 のゲート電圧を P V D D - V t にセットする際に、ゲート電圧が低くなる傾向がある。制御 T F T 3 0 を n チャネルにすることによって、リーク電流を減少して、駆動 T F T 2 4 の正確なゲート電圧セットが行える。

40

【0061】

また、本実施形態において、P V D D は 5 V 未満、データライン D L にセットされるデータ電圧の黒レベル電圧は P V D D より 2 V 程度高い電圧に設定される。これによって、黒レベルの際に駆動 T F T 2 4 のゲートをソースの電圧である P V D D に対し、十分高い電圧として、電流が流れるのを防止して、黒レベルを達成することができる。

【0062】

「タイミング発生回路の構成」

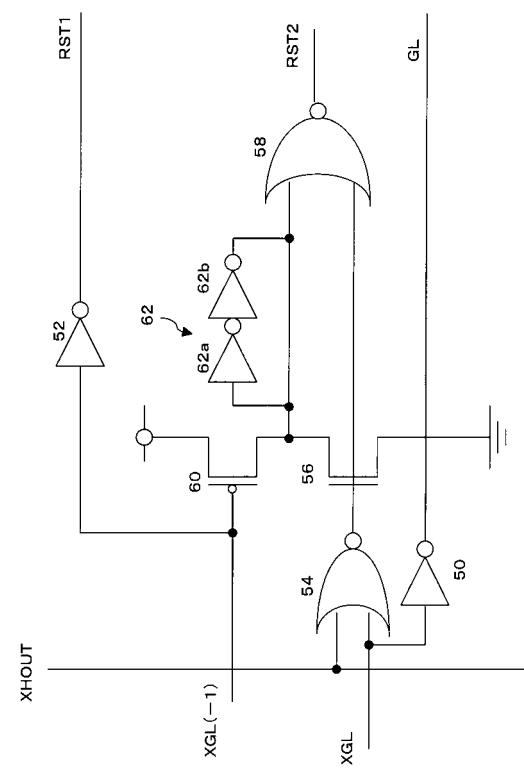

図 8 には、上述のようなりセットライン R L 1、R L 2 に供給する信号 R S T 1、R S T 2 の発生回路が示されている。

【0063】

入力信号としては、1 水平ライン上のゲート信号の反転信号である X G L (- 1) と、

50

当該水平ラインのゲート信号の反転信号である X G L と、水平方向のドライバ最終段の出力信号の反転信号である X H O U T と、を利用する。

【 0 0 6 4 】

X G L は、インバータ 5 0 によって反転され、G L が出力される。また、X G L ( - 1 ) がインバータ 5 2 によって反転されてリセット信号 R S T 1 として出力される。

【 0 0 6 5 】

X G L と、X H O U T は、ノアゲート 5 4 に入力される。このノアゲート 5 4 の出力は、n チャネル T F T 5 6 のゲートに供給されるとともに、ノアゲート 5 8 に入力される。

【 0 0 6 6 】

T F T 5 6 は、ソースがグランドに接続され、ドレインは p チャネル T F T 6 0 のドレインに接続され、この T F T 6 0 のソースが電源に接続されている。また、T F T 6 0 のゲートには、X G L ( - 1 ) が供給されている。

【 0 0 6 7 】

T F T 6 0 と T F T 5 6 の接続部は、ノアゲート 5 8 に入力されるとともに、この入力ラインには、インバータ 6 2 a、6 2 b の直列接続からなるラッチ回路 6 2 が接続されている。すなわち、T F T 6 0 と T F T 5 6 の接続部からノアゲート 5 8 の入力ラインには、インバータ 6 2 a に入力され、インバータ 6 2 b の出力が返されている。従って、T F T 6 0 と T F T 5 6 の接続部が変化した場合に、その変化がラッチ回路 6 2 に取り込まれた後、ノアゲート 5 8 への入力が変化する。

【 0 0 6 8 】

このような回路における動作について、図 9 に基づいて説明する。X G L ( - 1 )、X G L は、1 水平ラインの選択期間だけ L レベルになる信号であり、L レベルになる期間が 1 H だけシフトしている。X H O U T は、1 H に 1 回 L レベルになる信号であり、各ラインのゲート信号が L レベルになる期間の終了前において L レベルとなり、ゲート信号が H レベルになる若干前に H レベルに戻る。

【 0 0 6 9 】

このような信号によって、T F T 6 0 のゲートに入力される信号 A は、X G L ( - 1 ) と同じ信号となる。ノアゲート 5 4 の出力信号である信号 B は、X G L と、X H O U T の両方が L レベルの時のみ H レベルとなる。

【 0 0 7 0 】

さらに、ノアゲート 5 8 の入力ラインの信号 C は、X G L ( - 1 ) の L レベルによって立ち上がり、ノアゲート 5 4 の H レベルによって立ち下がる信号となる。ここで、T F T 6 0、5 6 の能力と、ラッチ回路 6 2 に能力に差があり、ラッチ回路 6 2 の書き込みに時間が掛かると、その能力差に応じて遅れることになる。すなわち、X G L ( - 1 ) の立ち下がりに応じて T F T 6 0、5 6 の接続点は上昇しようとするが、ラッチ回路 6 2 の出力が H レベルになるまでの期間だけ、立ち上がるるのが遅れる。一方、ノアゲート 5 4 の出力が H レベルとなった場合にも、信号 B は、だけ遅れて L レベルになる。

【 0 0 7 1 】

さらに、リセット信号 R S T 2 は、ノアゲート 5 8 の出力であり、ノアゲート 5 8 の入力が 2 つとも L レベルの時のみ H レベルを出力する。従って、リセット信号 R S T 2 は、信号 C の立ち上がりによって、L レベルとなり、その後の信号 B の立ち下がりによって、H レベルとなる。

【 0 0 7 2 】

このようにして、リセット信号 R S T 2 の立ち下がりタイミングは、リセット信号 R S T 1 の立ち上がりタイミングに比べ、若干遅れる。この遅れ時間は、T F T 6 0、5 6 の能力と、ラッチ回路 6 2 を構成するインバータ 6 2 a、6 2 b の能力に差によって決定される。例えば、ラッチ回路 6 2 を構成するインバータ 6 2 a、6 2 b の能力を T F T 6 0、5 6 の能力の 2 倍程度に設定することが好適である。これによって、例えば 4 0 0 n s e c 程度の遅延が得られる。一方、この程度の遅延を容量によって得ようとするとき、かなりの面積が必要となる。このため、この回路によって、効果的な信号の遅延を図ることで

10

20

30

40

50

きる。

#### 【0073】

一方、リセット信号RST2の立ち上がりは、信号XHOUTの立ち上がりに同期しており、予め定められたタイミングである。ゲートラインGLの立ち下がりより、所定の短時間1fH(ここで、1fHは、最小周期であり、例えば、200nsec程度である。)だけ、早い。従って、この回路によって、所定時間だけ、選択TFT20と、制御TFT30が両方オンする時間を設けることができる。

#### 【0074】

このように、本回路によれば、所定の遅延時間を2つのTFT56、60の直列接続からなるドライバーと、ラッチ回路62の能力差によって、得ることができる。従って、通常のように容量を設け、その充電時間を利用する回路に比べ、所要面積を小さくすることができる。

#### 【図面の簡単な説明】

#### 【0075】

【図1】実施形態の構成を示す回路図である。

【図2】実施形態の動作を説明するための信号の波形図である。

【図3】他の実施形態の構成を示す回路図である。

【図4】他の実施形態の構成を示す回路図である。

【図5】従来例の構成を示す回路図である。

【図6】他の実施形態の構成を示す回路図である。

【図7】他の実施形態の動作を説明するための信号の波形図である。

【図8】リセット信号RST1、RST2を生成する回路の構成を示す図である。

【図9】図8の回路の動作を説明するための信号の波形図である。

#### 【符号の説明】

#### 【0076】

10, 20 選択TFT、12, 24 駆動TFT、14 保持容量、16, 32 有機EL素子、22 コンデンサ、26 リセット制御TFT、28 短絡TFT、30 制御TFT、CV カソード電源、DL データライン、GL ゲートライン、PVDD 電源ライン、RL1, RL2 リセットライン。

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

【図7】

【 四 8 】

【図9】

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机EL画素回路                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP2005128521A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2005-05-19 |

| 申请号            | JP2004289368                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2004-09-30 |

| [标]申请(专利权)人(译) | 三洋电机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 三洋电机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 佐々木昭史<br>松本昭一郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 佐々木 昭史<br>松本 昭一郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.H G09G3/20.624.B H05B33/14.A G09G3/20.612.J G09G3/20.641.D G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291 G11C19/28.230                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 3K007/AB18 3K007/BA06 3K007/DB03 3K007/GA00 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD22 5C080/EE29 5C080/FF11 5C080/JJ03 5C080/JJ04 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE04 3K107/HH02 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB06 5C380/BA10 5C380/BA38 5C380/BA39 5C380/CA08 5C380/CA12 5C380/CB01 5C380/CC02 5C380/CC04 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC62 5C380/CC63 5C380/CC64 5C380/CC77 5C380/CD012 5C380/CD015 5C380/CE19 5C380/CF23 5C380/CF33 5C380/CF46 5C380/DA02 5C380/DA06 5C380/DA47 |         |            |

| 代理人(译)         | 吉田健治<br>石田 纯                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 优先权            | 2003342469 2003-09-30 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 其他公开文献         | <a href="#">JP5078223B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

#### 摘要(译)

要解决的问题：有效补偿驱动晶体管的阈值电压变化。在选择TFT 20截止的同时，控制TFT 30截止，并且复位控制TFT 26和短路TFT 28导通。结果，在电容器22的选择的TFT 20侧被设置为PVDD的情况下，短路TFT 28被导通并且驱动TFT 24被二极管连接。因此，在驱动TFT 24的栅极中设置比PVDD低驱动TFT 24的阈值电压的电压。接下来，通过关闭复位控制TFT26和短路TFT28并打开控制TFT30，驱动TFT24的栅极电压移动数据线DL的视频信号电压，从而驱动TFT24导通以打开有机EL元件。驱动电流提供给32。结果，可以根据视频信号来控制驱动电流，而不管驱动TFT 24的阈值电压如何。[选型图]图1