(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-9136

(P2016-9136A)

(43) 公開日 平成28年1月18日(2016.1.18)

|                               |                              |                                                |

|-------------------------------|------------------------------|------------------------------------------------|

| (51) Int.Cl.                  | F 1                          | テーマコード (参考)                                    |

| <b>G09G 3/30</b>              | <b>(2006.01)</b>             | <b>G09G 3/30</b> K 5C080                       |

| <b>G09G 3/20</b>              | <b>(2006.01)</b>             | <b>G09G 3/20</b> 611H 5C380                    |

|                               |                              | <b>G09G 3/20</b> 642A                          |

|                               |                              | <b>G09G 3/20</b> 670Q                          |

|                               |                              | <b>G09G 3/20</b> 641P                          |

| 審査請求 未請求 請求項の数 7 O L (全 21 頁) |                              |                                                |

| (21) 出願番号                     | 特願2014-130814 (P2014-130814) | (71) 出願人 514188173                             |

| (22) 出願日                      | 平成26年6月25日 (2014. 6. 25)     | 株式会社 J O L E D<br>東京都千代田区神田錦町三丁目23番地           |

|                               |                              | (74) 代理人 100189430<br>弁理士 吉川 修一                |

|                               |                              | (74) 代理人 100190805<br>弁理士 傍島 正朗                |

|                               |                              | (72) 発明者 根来 靖典<br>大阪府門真市大字門真1006番地 パナソニック株式会社内 |

|                               |                              | (72) 発明者 沖川 昌史<br>大阪府門真市大字門真1006番地 パナソニック株式会社内 |

| 最終頁に続く                        |                              |                                                |

(54) 【発明の名称】表示装置及びその製造方法

## (57) 【要約】

【課題】全表示階調にわたり輝度ムラを高精度に抑制できる表示装置の製造方法を提供する。

【解決手段】有機EL素子402と駆動トランジスタ401とを含む画素400が行列状に配置された表示装置1の製造方法であって、表示部113全体に共通する代表階調-輝度特性を取得する第1ステップと、表示階調範囲における下限階調を含まない複数の演算階調値を選択する第2ステップと、当該複数の演算階調値における発光輝度を画素ごとに測定し演算階調-輝度テーブルを作成する第3ステップと、演算階調-輝度テーブルの各データが代表階調-輝度特性上のデータと一致するよう、複数の演算階調値のシフト量を求める第4ステップと、当該シフト量によるシフト前後の複数の演算階調値の相關データに基づいて、表示階調範囲における任意の入力階調データを補正する階調変換テーブルを画素ごとに生成する第5ステップとを含む。

【選択図】図5

## 【特許請求の範囲】

## 【請求項 1】

発光素子と、当該発光素子の発光輝度を決定する入力階調データが供給されることにより、当該入力階調データに対応した駆動電流を前記発光素子へ流す駆動素子とを含む画素が行列状に配置された表示パネルを有する表示装置の製造方法であって、

入力階調と発光輝度との相関を表す画素ごとの階調・輝度特性を補正するターゲットとなる、前記表示パネル全体に共通する階調・輝度特性である代表階調・輝度特性を取得する第1ステップと、

前記入力階調データを補正する際に参照する階調変換テーブルを生成するための複数の階調値であって、映像として使用される階調範囲である表示階調範囲における下限階調を含まない複数の離散した演算階調値を選択する第2ステップと、

前記複数の離散した演算階調値における発光輝度を前記画素ごとに測定し、前記画素ごとの演算階調・輝度テーブルを作成する第3ステップと、

前記演算階調・輝度テーブルにおける、演算階調値と輝度との組み合わせに対応する各データが、前記代表階調・輝度特性上のデータと一致するような、前記画素ごとの前記複数の離散した演算階調値のシフト量を求める第4ステップと、

前記第4ステップで求められた前記シフト量でシフトした前記複数の離散した演算階調値と、シフト前の前記複数の離散した演算階調値との相関データに基づいて、前記表示階調範囲における任意の入力階調データを補正する前記階調変換テーブルを前記画素ごとに生成する第5ステップとを含む

表示装置の製造方法。

## 【請求項 2】

前記第2ステップでは、

全ての前記画素において、同一の前記複数の離散した演算階調値を選択する

請求項1に記載の表示装置の製造方法。

## 【請求項 3】

前記第5ステップでは、

前記シフト前の複数の離散した演算階調値をx、前記シフトした複数の離散した演算階調値をy、補正係数をa、及びオフセット値をbとした場合、前記階調変換テーブルを、

$y = a \cdot x + b$  で表される一次式として生成する

請求項1または2に記載の表示装置の製造方法。

## 【請求項 4】

前記第3ステップでは、前記複数の離散した演算階調値における発光輝度を輝度計にて測定し、

前記第2ステップでは、前記輝度計の検出可能な最低輝度に対応した階調値以上である前記複数の離散した演算階調値を選択する

請求項1～3のいずれか1項に記載の表示装置の製造方法。

## 【請求項 5】

前記第1ステップでは、

前記代表階調・輝度特性として、同一条件で製造される他の表示装置の製造方法において取得された代表階調・輝度特性を利用する

請求項1～4のいずれか1項に記載の表示装置の製造方法。

## 【請求項 6】

さらに、

前記第5ステップにおいて生成された各画素の前記階調変換テーブルを、所定のメモリに書き込む第6ステップ、を含む

請求項1～5のいずれか1項に記載の表示装置の製造方法。

## 【請求項 7】

発光素子及び当該発光素子の発光輝度を決定する入力階調データが供給されることにより当該入力階調データに対応した駆動電流を前記発光素子へ流す駆動素子を含む複数の画

10

20

30

40

50

素と、

前記複数の画素の各々に前記入力階調データを供給するための複数のデータ線と、

前記複数の画素の各々に走査信号を供給するための複数の走査線と、

前記複数のデータ線に前記入力階調データを供給するデータ線駆動回路と、

前記複数の走査線に前記走査信号を供給する走査線駆動回路と、

前記入力階調データを補正する際に参照する階調変換テーブルを前記複数の画素毎に格納するメモリと、

外部から入力された映像信号に対して前記記憶部から前記複数の画素の各々に対応する前記階調変換テーブルを読み出して、前記複数の画素の各々に対応する前記入力階調データを補正する補正部とを備え、

前記階調変換テーブルは、

入力階調と発光輝度との相関を表す画素ごとの階調・輝度特性を補正するターゲットとなる、前記複数の画素全体に共通する階調・輝度特性である代表階調・輝度特性を取得する第1ステップと、

前記階調変換テーブルを作成するための複数の階調値であって、映像として使用される階調範囲である表示階調範囲における下限階調を含まない複数の離散した演算階調値を選択する第2ステップと、

前記複数の離散した演算階調値における発光輝度を前記画素ごとに測定し、前記画素ごとの演算階調・輝度テーブルを作成する第3ステップと、

前記演算階調・輝度テーブルにおける、演算階調値と輝度との組み合わせに対応する各データが、前記代表階調・輝度特性上のデータと一致するような、前記画素ごとの前記複数の離散した演算階調値のシフト量を求める第4ステップと、

前記第4ステップで求められた前記シフト量でシフトした前記複数の離散した演算階調値と、シフト前の前記複数の離散した演算階調値との相関データに基づいて、前記表示階調範囲における任意の入力階調データを補正する前記階調変換テーブルを前記画素ごとに生成する第5ステップとにより生成される

表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、表示装置及びその製造方法に関する。

【背景技術】

【0002】

電流駆動型の発光素子を用いた画像表示装置として、有機EL素子を用いた画像表示装置（有機ELディスプレイ）が知られている。この有機ELディスプレイは、視野角特性が良好で、消費電力が少ないという利点を有するため、次世代のFPD（Flat Panel Display）候補として注目されている。

【0003】

有機ELディスプレイでは、通常、画素を構成する有機EL素子がマトリクス状に配置される。特に、アクティブマトリクス型の有機ELディスプレイでは、複数の走査線と複数のデータ線との交点に薄膜トランジスタ（TFT：Thin Film Transistor）が設けられる。このTFTに駆動トランジスタのゲートが接続され、選択した走査線を通じて当該TFTをオンさせてデータ線から入力階調信号が駆動トランジスタに入力され、当該駆動トランジスタにより有機EL素子が発光する。上記構成によれば、次の走査（選択）まで有機EL素子を発光させることができるので、デューティ比が上がってもディスプレイの輝度減少を招くようなことはない。しかしながら、アクティブマトリクス型の有機ELディスプレイでは、駆動トランジスタや有機EL素子の特性のばらつきに起因して、同じ入力階調信号を与えて、各画素において有機EL素子の輝度が異なり、輝度ムラが発生するという欠点がある。

【0004】

10

20

30

40

50

従来の有機ELディスプレイにおける、製造工程で生じる駆動トランジスタや有機EL素子の特性のばらつき（以下、特性の不均一と総称する）による輝度ムラの補償方法として、画素ごとに特性の不均一を補償する方法が提案されている。

#### 【0005】

特許文献1に開示された電気光学装置、電気光学装置の駆動方法、電気光学装置の製造方法、及び電子機器では、電流プログラム画素回路において、最低1種類の入力電流で各画素の輝度が測定される。そして、測定された各画素の輝度比が記憶容量に記憶され、当該輝度比に基づいて画像データが補正され、該補正後の画像データにより、電流プログラム画素回路が駆動される。これにより、輝度ムラが抑制され、均一な表示を可能にすることができる。

10

#### 【先行技術文献】

#### 【特許文献】

#### 【0006】

【特許文献1】特開2005-283816号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

しかしながら、有機ELディスプレイでは、最低階調（黒）から最高階調の全表示階調範囲にわたり輝度ムラが解消されることが要求されるため、特許文献1に記載された輝度ムラの補正方法では、予め記憶容量に記憶される各画素の輝度比の精度が問題となる。例えば、上記輝度比を取得するにあたり、入力電流値の種類が少ない、または、入力電流値の選択が適切でない場合には、一部の入力階調では輝度ムラが解消されても、全表示階調範囲にわたり輝度ムラを十分に解消できないといった問題が生じる。

20

#### 【0008】

本発明は、上記の課題に鑑みてなされたものであり、全表示階調にわたり輝度ムラを高精度に抑制できる表示装置及びその製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0009】

上記の課題を解決するために、本発明の一態様に係る表示装置の製造方法は、発光素子と、当該発光素子の発光輝度を決定する入力階調データが供給されることにより、当該入力階調データに対応した駆動電流を前記発光素子へ流す駆動素子とを含む画素が行列状に配置された表示パネルを有する表示装置の製造方法であって、入力階調と発光輝度との相関を表す画素ごとの階調・輝度特性を補正するターゲットとなる、前記表示パネル全体に共通する階調・輝度特性である代表階調・輝度特性を取得する第1ステップと、前記入力階調データを補正する際に参照する階調変換テーブルを生成するための複数の階調値であって、映像として使用される階調範囲である表示階調範囲における下限階調を含まない複数の離散した演算階調値を選択する第2ステップと、前記複数の離散した演算階調値における発光輝度を前記画素ごとに測定し、前記画素ごとの演算階調・輝度テーブルを作成する第3ステップと、前記演算階調・輝度テーブルにおける、演算階調値と輝度との組み合わせに対応する各データが、前記代表階調・輝度特性上のデータと一致するような、前記画素ごとの前記複数の離散した演算階調値のシフト量を求める第4ステップと、前記第4ステップで求められた前記シフト量でシフトした前記複数の離散した演算階調値と、シフト前の前記複数の離散した演算階調値との相関データに基づいて、前記表示階調範囲における任意の入力階調データを補正する前記階調変換テーブルを前記画素ごとに生成する第5ステップとを含むことを特徴とする。

30

#### 【発明の効果】

#### 【0010】

本発明に係る表示装置の製造方法によれば、入力階調データを補正する際に使用される演算階調値の数を、各画素で同一にできるので、全表示階調にわたり輝度ムラを高精度に抑制することが可能となる。

40

50

## 【図面の簡単な説明】

## 【0011】

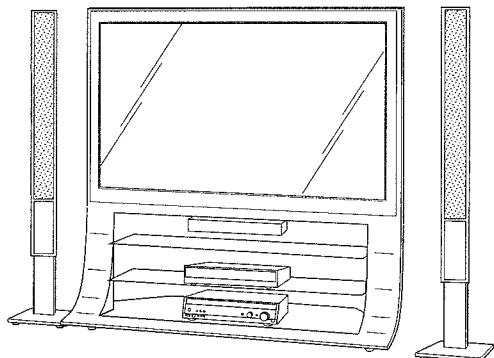

【図1】従来の輝度ムラ補償方法における演算階調 - 輝度テーブルを示す図である。

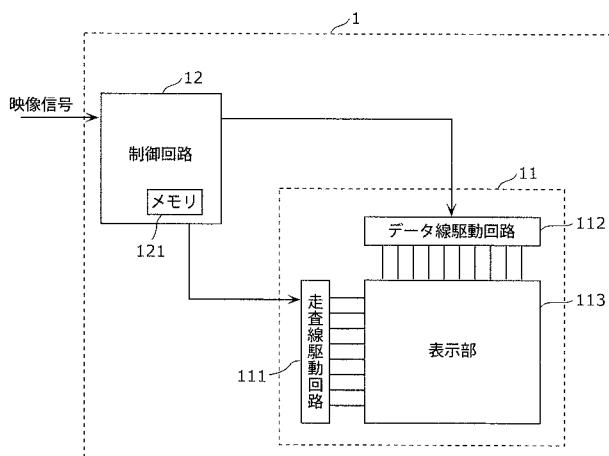

【図2】実施の形態に係る表示装置の電気的な構成を示すブロック図である。

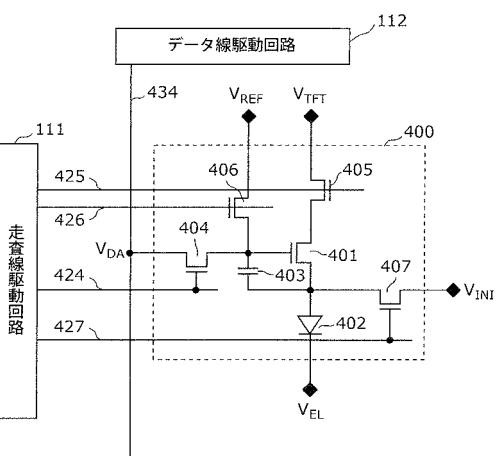

【図3】表示部が有する画素の回路構成の一例及びその周辺回路との接続を示す図である。

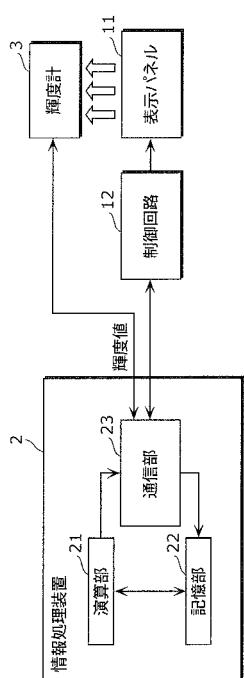

【図4】実施の形態に係る表示装置の製造システムの機能ブロック図である。

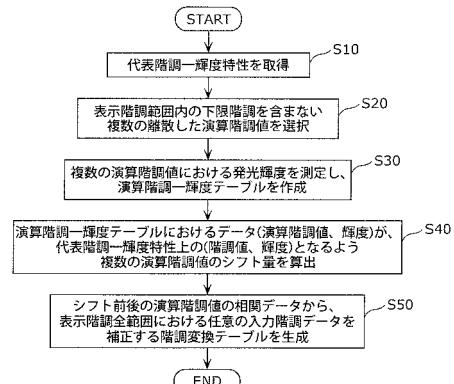

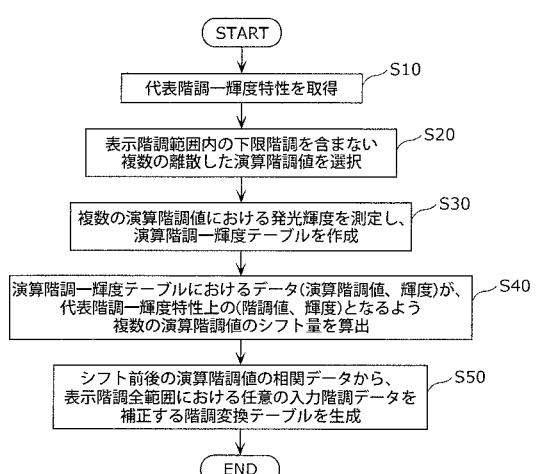

【図5】実施の形態に係る表示装置の製造方法を説明する動作フローチャートである。

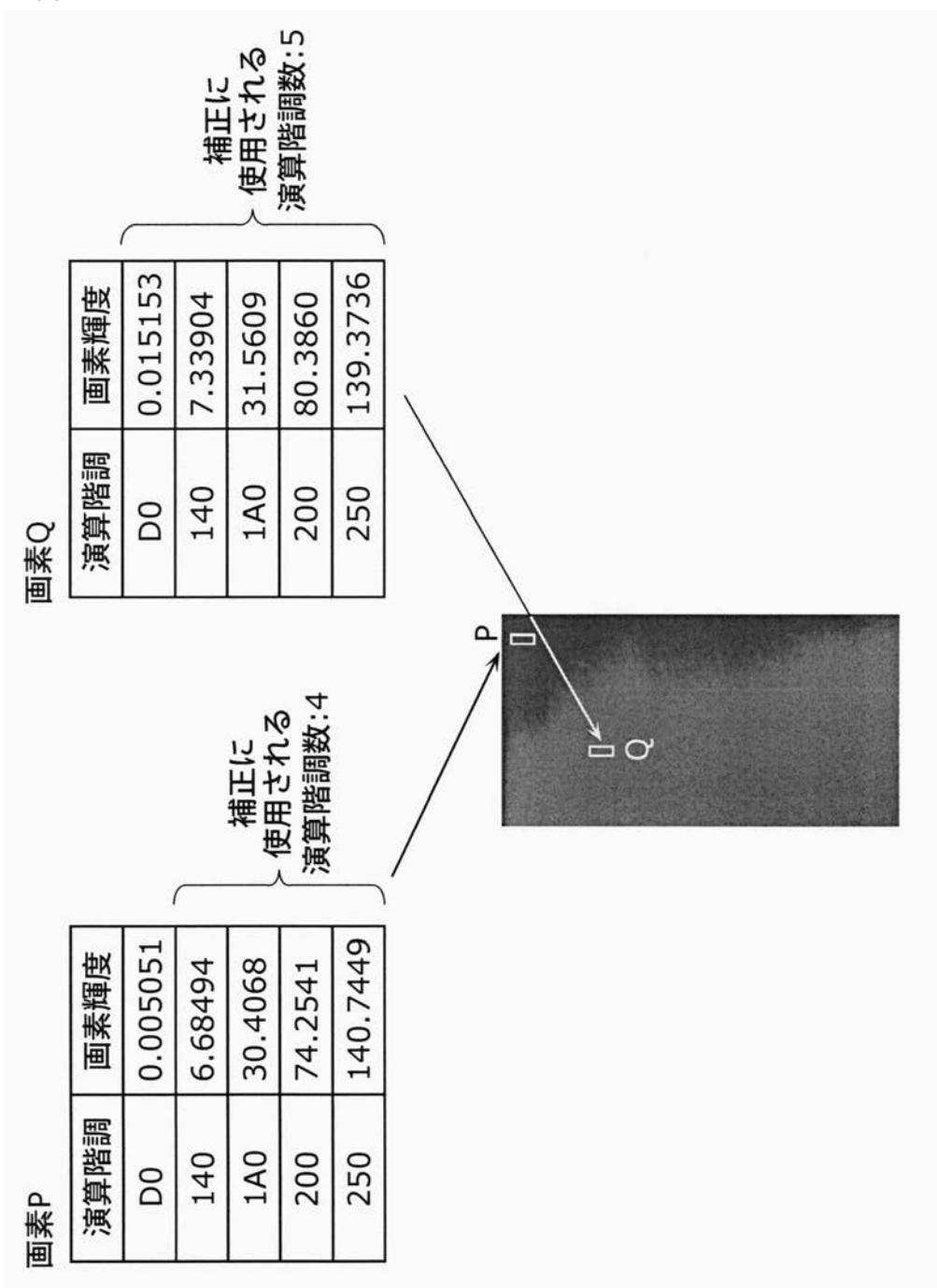

【図6】表示階調範囲およびステップS30での演算階調 - 輝度テーブルを示す図である。

10

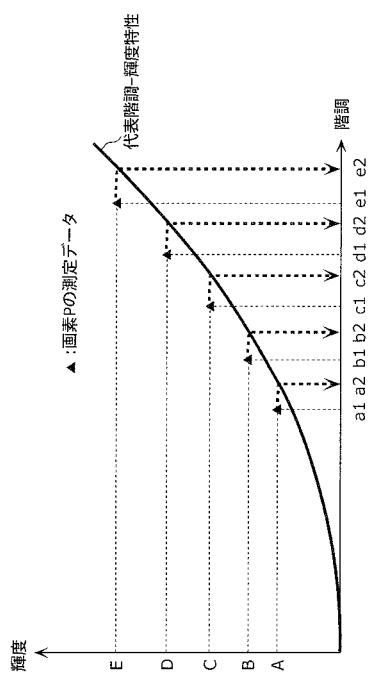

【図7】ステップS40での演算階調値の補正を説明するグラフである。

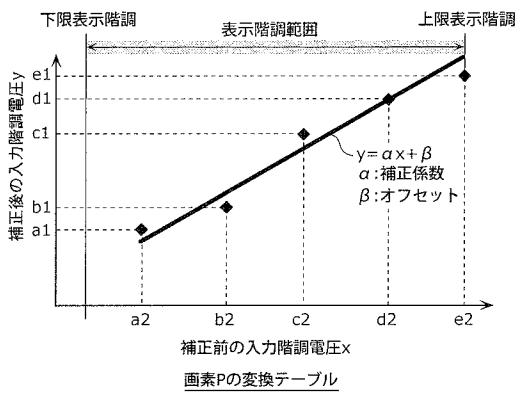

【図8】ステップS50における階調変換テーブルを示す図である。

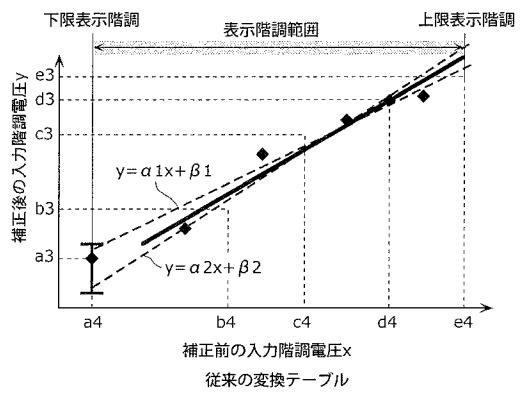

【図9】実施の形態に係る表示装置と従来の表示装置との補正精度を比較する図である。

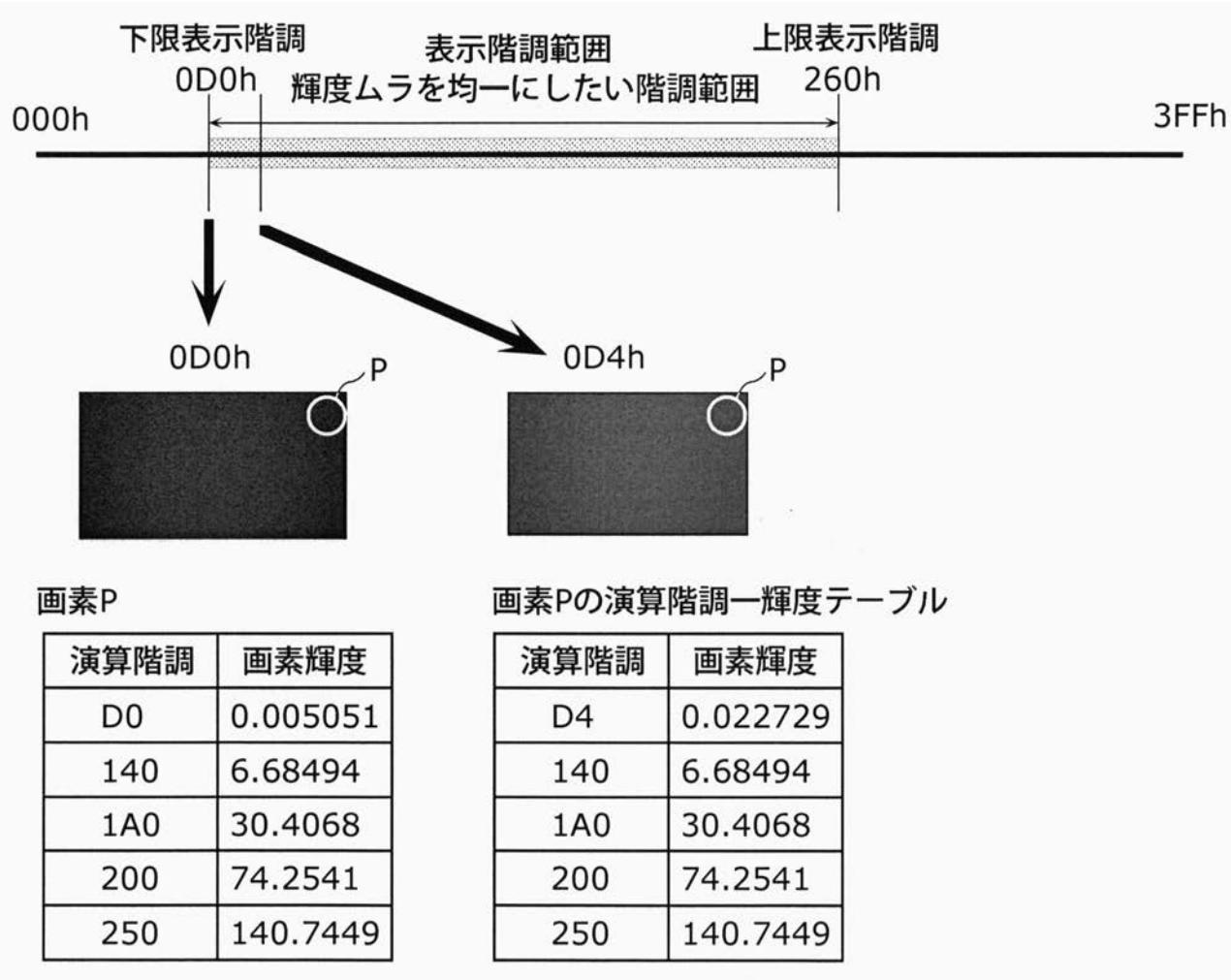

【図10】実施の形態に係る演算階調 - 輝度テーブルを示す図である。

【図11】実施の形態に係る有機EL表示パネルを内蔵した薄型フラットTVの外観図である。

## 【発明を実施するための形態】

## 【0012】

(本発明の基礎となった知見)

本発明者は、「背景技術」の欄において記載した表示パネルの輝度ムラ補償方法に関し、以下の問題が生じることを見出した。

## 【0013】

例えば、有機EL素子と、当該有機EL素子の発光輝度を決定する入力階調データが供給されることにより、当該入力階調データに対応した駆動電流を有機EL素子へ流す駆動トランジスタとを含む画素が行列状に配置された表示パネルにおける従来の輝度ムラ補償方法として、以下の方法が挙げられる。

## 【0014】

まず、入力階調と発光輝度との相関を表す画素ごとの階調 - 輝度特性を補正するターゲットとなる、表示パネル全体に共通する代表階調 - 輝度特性を取得する(S51)。

## 【0015】

次に、入力階調データを補正する際に参照する階調変換テーブルを生成するための複数の演算階調値を選択する(S52)。

## 【0016】

選択された複数の演算階調値における発光輝度を画素ごとに測定し、画素ごとの演算階調 - 輝度テーブルを作成する(S53)。

## 【0017】

上記演算階調 - 輝度テーブルの各データ(演算階調値、輝度)が、上記代表階調 - 輝度特性上のデータ(階調値、輝度)と一致するよう、画素ごとの複数の演算階調値をシフトさせる(S54)。

## 【0018】

シフトした複数の演算階調値と、シフト前の複数の演算階調値との相関データに基づいて、表示階調範囲における任意の入力階調データを補正する階調変換テーブルを画素ごとに生成する(S55)。

## 【0019】

最後に、外部入力された映像信号を反映した入力階調データを、上記階調変換テーブルにより補正し、補正後の入力階調データを各画素へ供給する(S56)。

## 【0020】

図1は、従来の輝度ムラ補償方法における演算階調 - 輝度テーブルを示す図である。同図は、具体的には、上述した従来の輝度ムラ補償方法におけるステップS53を説明する図である。表示パネルの各画素において、複数の演算階調値(D0、140、1A0、2

20

30

40

50

00、260:16進表記)が選択されている(S52)。階調D0は、映像として使用される下限階調(黒表示)であり、また、階調260は、映像として使用される上限階調である。つまり、階調D0から階調260までが、映像として使用される表示階調範囲である。そして、各演算階調値における発光輝度が測定されている(S53)。図1には、画素P及び画素Qにおける演算階調-輝度テーブルが示されている。

【0021】

ここで、画素Aの演算階調D0では、画素輝度として0.005051と測定されている。しかしながら、この測定輝度値は、輝度計の測定下限値を下回っており、正確な画素Pの発光輝度を反映したものとなっていない。したがって、画素Pにおいては、階調D0を、画素Pの階調変換テーブルを生成するための演算階調として選択せず、階調D0以外の4点の演算階調を選択する。

10

【0022】

一方、画素Qでは、5点の演算階調のいずれにおいても、測定された画素輝度は輝度計の測定可能な範囲内にあるため、当該5点の演算階調を、画素Qの階調変換テーブルを生成するための演算階調として選択する。

20

【0023】

上記のように、異なる演算階調数に基づいて各画素の階調変換テーブルを生成した場合、例えば、全画素同一の入力階調データを画素ごとに補正し、該補正された入力階調データを各画素に供給すると、図1に示すように、画素Pと画素Qとで発光輝度が異なる。つまり、表示パネル全体にわたって輝度ムラを効果的に抑制できないといった課題が発生する。

20

【0024】

このような問題を解決するために、本発明の一態様に係る表示装置の製造方法は、発光素子と、当該発光素子の発光輝度を決定する入力階調データが供給されることにより、当該入力階調データに対応した駆動電流を前記発光素子へ流す駆動素子とを含む画素が行列状に配置された表示パネルを有する表示装置の製造方法であって、入力階調と発光輝度との相関を表す画素ごとの階調-輝度特性を補正するターゲットとなる、前記表示パネル全体に共通する階調-輝度特性である代表階調-輝度特性を取得する第1ステップと、前記入力階調データを補正する際に参照する階調変換テーブルを生成するための複数の階調値であって、映像として使用される階調範囲である表示階調範囲における下限階調を含まない複数の離散した演算階調値を選択する第2ステップと、前記複数の離散した演算階調値における発光輝度を前記画素ごとに測定し、前記画素ごとの演算階調-輝度テーブルを作成する第3ステップと、前記演算階調-輝度テーブルにおける、演算階調値と輝度との組み合わせに対応する各データが、前記代表階調-輝度特性上のデータと一致するような、前記画素ごとの前記複数の離散した演算階調値のシフト量を求める第4ステップと、前記第4ステップで求められた前記シフト量でシフトした前記複数の離散した演算階調値と、シフト前の前記複数の離散した演算階調値との相関データに基づいて、前記表示階調範囲における任意の入力階調データを補正する前記階調変換テーブルを前記画素ごとに生成する第5ステップとを含むことを特徴とする。

30

【0025】

これによれば、表示階調範囲における下限階調を含まずに、入力階調データを補正する際に使用される複数の演算階調値を抽出するので、有効な測定輝度値が得られる演算階調値の数を各画素で同一にできる。よって、全表示階調にわたり輝度ムラを高精度に抑制することが可能となる。

40

【0026】

また、前記第2ステップでは、全ての前記画素において、同一の前記複数の離散した演算階調値を選択してもよい。

【0027】

これにより、選択された複数の演算階調値により生成された階調変換テーブルの精度を、全画素において一致させることが可能となる。

50

## 【0028】

また、前記第5ステップでは、前記シフト前の複数の離散した演算階調値をx、前記シフトした複数の離散した演算階調値をy、補正係数を、及びオフセット値をとした場合、前記階調変換テーブルを、 $y = x +$  で表される一次式として生成してもよい。

## 【0029】

これにより、補正前の入力階調データに対して、まず補正係数を乗算し、該乗算されたものにオフセット値を加算することで、補正後の入力階調データが生成される。よって、簡素化された補正演算処理で、輝度ムラを高精度に抑制することが可能となる。

## 【0030】

また、前記第3ステップでは、前記複数の離散した演算階調値における発光輝度を輝度計にて測定し、前記第2ステップでは、前記輝度計の検出可能な最低輝度に対応した階調値以上である前記複数の離散した演算階調値を選択してもよい。

10

## 【0031】

これにより、選択された複数の演算階調値において測定された発光輝度値は、いずれも測定誤差を極力含まない値とすることが可能となる。よって、これらの測定された発光輝度値により生成された階調変換テーブルの変換精度を向上させることが可能となる。

## 【0032】

また、前記第1ステップでは、前記代表階調・輝度特性として、同一条件で製造される他の表示装置の製造方法において取得された代表階調・輝度特性を利用してもよい。

20

## 【0033】

これにより、一の表示装置の製造方法で求められた代表階調・輝度特性を、当該一の表示装置と同一条件で製造される他の表示装置の製造方法で利用するので、複数の表示パネルの階調変換テーブルを生成する毎に代表階調・輝度特性を設定する手間を省くことができる。その結果、本装置の製造プロセスを短縮できる。

## 【0034】

また、さらに、前記第5ステップにおいて生成された各画素の前記階調変換テーブルを、所定のメモリに書き込む第6ステップ、を含んでもよい。

## 【0035】

これにより、映像表示動作ごとに階調変換テーブルを生成することなく、製造工程で一度生成された階調変換テーブルを、出荷後の表示動作の際に常に使用できる。よって、輝度ムラ補償処理を簡素化できる。

30

## 【0036】

また、本発明は、このような特徴的なステップを含む表示装置の製造方法として実現することができるだけでなく、当該製造方法に含まれる特徴的なステップを手段として生成された階調変換テーブルを有する表示装置としても、上記と同様の効果を奏す。

## 【0037】

以下、表示装置の製造方法の一実施の形態について、図面を用いて説明する。なお、以下に説明する実施の形態は、いずれも本開示における好ましい一具体例を示すものである。したがって、以下の実施の形態で示される、数値、形状、材料、構成要素、構成要素の配置位置及び接続形態、工程、並びに、工程の順序などは、一例であって本発明を限定する主旨ではない。よって、以下の実施の形態における構成要素のうち、本発明における最上位概念を示す独立請求項に記載されていない構成要素については、任意の構成要素として説明される。

40

## 【0038】

なお、各図は、模式図であり、必ずしも厳密に図示されたものではない。また、各図において、実質的に同一の構成に対しては同一の符号を付しており、重複する説明は省略又は簡略化する。

## 【0039】

(実施の形態)

以下、実施の形態に係る表示装置及びその製造方法について、図面を参照しながら説明

50

する。

【0040】

[1. 表示装置の基本構成]

図2は、実施の形態に係る表示装置の電気的な構成を示すブロック図である。同図における表示装置1は、制御回路12と、表示パネル11とを備える。制御回路12はメモリ121を有する。表示パネル11は、走査線駆動回路111と、データ線駆動回路112と、表示部113とを備える。なお、メモリ121は、表示装置1内であって制御回路12の外部に配置されていてもよい。

【0041】

制御回路12は、メモリ121、走査線駆動回路111、及びデータ線駆動回路112の制御を行う機能を有する。メモリ121には、本実施の形態で説明する製造方法による製造工程の完了後には、本実施の形態に係る表示装置の製造方法により生成された階調変換テーブルが記憶される。制御回路12は、表示動作時には、メモリ121に書き込まれた階調変換テーブルを読み出し、外部から入力された映像信号を反映した入力階調データを、階調変換テーブルに基づいて補正して、データ線駆動回路112へと出力する。言い換えると、制御回路12は、映像信号に対してメモリ121から階調変換テーブルを読み出して入力階調データを補正する補正部としての機能を有する。

【0042】

また、制御回路12は、製造工程においては、外部の情報処理装置と通信することにより、当該情報処理装置の指示に従って表示パネル11を駆動する機能を有する。

【0043】

表示部113は、複数の画素を備え、外部から表示装置1へ入力された映像信号に基づいて画像を表示する。

【0044】

[2. 画素回路構成]

図3は、表示部が有する画素の回路構成の一例及びその周辺回路との接続を示す図である。同図における画素400は、走査線424-427と、データ線434と、駆動トランジスタ401と、有機EL素子402と、保持容量素子403と、選択トランジスタ404と、イネーブルトランジスタ405と、参照トランジスタ406と、初期化トランジスタ407とを備える。また、周辺回路は、走査線駆動回路111と、データ線駆動回路112とで構成されている。

【0045】

走査線駆動回路111は、走査線424-427に接続されており、選択トランジスタ404、イネーブルトランジスタ405、参照トランジスタ406、及び初期化トランジスタ407の導通及び非導通を制御する。

【0046】

データ線駆動回路112は、データ線434に接続されており、映像信号を反映し、有機EL素子402の発光輝度を決定する入力階調データ（入力階調電圧）を出力して、駆動トランジスタ401に流れる駆動電流を決定する。

【0047】

駆動トランジスタ401は、ゲートが選択トランジスタ404を介してデータ線434に接続され、ソースが有機EL素子402のアノードに接続され、ドレインがイネーブルトランジスタ405を介して正電源線( $V_{TFT}$ )に接続された駆動素子である。これにより、駆動トランジスタ401は、入力階調電圧を、当該入力階調電圧に対応した駆動電流に変換し、変換された駆動電流を有機EL素子402に供給する。

【0048】

有機EL素子402は、電流駆動型の発光素子として機能し、有機EL素子402のカソードは、負電源線( $V_{EL}$ )に接続されている。

【0049】

保持容量素子403は、駆動トランジスタ401のゲート-ソース間に接続されている

10

20

30

40

50

。保持容量素子 403 は、例えば、選択トランジスタ 404 がオフ状態となった後も、直前のゲート - ソース間電圧を維持し、継続して駆動トランジスタ 401 から有機 EL 素子 402 へ駆動電流を供給させる機能を有する。

【0050】

選択トランジスタ 404 は、ゲートが走査線 424 に接続されており、データ線 434 の入力階調電圧を駆動トランジスタ 401 のゲートに供給するタイミングを制御するスイッチトランジスタである。

【0051】

イネーブルトランジスタ 405 は、ゲートが走査線 425 に接続されており、正電源線の電源電圧  $V_{TFT}$  を駆動トランジスタ 401 のドレインに供給するタイミングを制御する発光トランジスタである。

10

【0052】

参照トランジスタ 406 は、ゲートが走査線 426 に接続されており、閾値電圧を検出するために設けられた参照電源線の参照電圧  $V_{REF}$  を駆動トランジスタ 401 のゲートに供給するタイミングを制御するスイッチトランジスタである。

【0053】

初期化トランジスタ 407 は、ゲートが走査線 427 に接続されており、初期化電源線の初期化電圧  $V_{INI}$  を駆動トランジスタ 401 のソースに供給するタイミングを制御する。

20

【0054】

なお、図 3 には記載されていないが、正電源線は電源に接続されている。また、負電源線は、別の電源に接続、または接地されている。

【0055】

[3. 画素回路動作]

次に、図 3 に示された画素回路の駆動シーケンスについて説明する。

【0056】

まず、初期化トランジスタ 407 のみを導通状態として、駆動トランジスタ 401 のソース電位を初期化電圧  $V_{INI}$  に設定する（初期化期間）。

【0057】

次に、参照トランジスタ 406 を導通状態とする。これにより、参照電圧  $V_{REF}$  と初期化電圧  $V_{INI}$  との差分電圧が、保持容量素子 403 に充電される。

30

【0058】

次に、初期化トランジスタ 407 を非導通状態とし、参照トランジスタ 406 を導通状態に維持し、イネーブルトランジスタ 405 を導通状態とする。このとき、初期化期間での電圧設定により有機 EL 素子 402 には電流が流れない状態でドレイン電流が流れ、駆動トランジスタ 401 のソース電位が変化する。そして、保持容量素子 403 の両電極の電位差（駆動トランジスタ 401 のゲート - ソース間電圧）は、駆動トランジスタ 401 の閾値電圧  $V_{th}$  に相当する電位差となる。次に、イネーブルトランジスタ 405 を非導通状態にする。これにより、ドレイン電流の供給が停止され、閾値電圧検出動作が完了する（閾値電圧検出期間）。

40

【0059】

次に、参照トランジスタ 406 を非導通状態とし、選択トランジスタ 404 を導通状態とすることで、書き込み動作の準備がなされる。この状態で、データ線 434 を介して、補正された入力階調電圧が保持容量素子 403 の第 1 電極に印加される。これにより、保持容量素子 403 には、閾値電圧検出期間で保持された駆動トランジスタ 401 の閾値電圧  $V_{th}$  に、補正後の入力階調電圧と参照電圧との電圧差に対応した電圧が加算された電圧が記憶（保持）される（書き込み期間）。なお、上記補正された入力階調電圧は、本実施の形態に係る表示装置の製造方法により生成された階調変換テーブルに基づいて補正された入力階調データである。

【0060】

50

選択トランジスタ 404、参照トランジスタ 406、及び初期化トランジスタ 407 を非導通状態とし、イネーブルトランジスタ 405 を導通状態にする。これにより、保持容量素子 403 に蓄えられた電圧に応じて有機 EL 素子 402 に駆動電流が流れ、当該駆動電流に対応して有機 EL 素子 402 が発光する（発光期間）。有機 EL 素子 402 は、補正された入力階調電圧に対応した発光輝度で発光する。例えば、有機 EL 素子 402 は、下限階調電圧では発光せず（黒表示）、上限階調電圧では最大輝度で発光する。

【0061】

[4. 製造システムの構成]

次に、本実施の形態に係る表示装置の製造方法を実現する製造システムを説明する。

【0062】

図4は、実施の形態に係る表示装置の製造システムの機能ブロック図である。同図に記載された製造システムは、情報処理装置2と、輝度計3と、表示パネル11と、制御回路12とを備える。

【0063】

情報処理装置2は、演算部21と、記憶部22と、通信部23とを備え、階調変換テーブルを生成するまでの工程を制御する機能を有する。情報処理装置2としては、例えば、パーソナルコンピュータが適用される。

【0064】

輝度計3は、情報処理装置2の通信部23からの制御信号により、表示パネル11を撮像し、撮像された画像データを通信部23へ出力する。輝度計3としては、例えば、CCDカメラや輝度計が適用される。

【0065】

情報処理装置2は、表示装置1内の制御回路12及び輝度計3へ、通信部23を介して制御信号を出力し、制御回路12及び輝度計3から測定データを取得して当該測定データを記憶部22に格納し、格納された測定データを基に演算部21で演算して各種特性値やパラメータを算出する。なお、制御回路12は、表示装置1に内蔵されない制御回路を使用してもよい。

【0066】

より具体的には、代表階調・輝度特性の設定時には、情報処理装置2は、測定画素へ与える入力階調電圧値の制御を行い、輝度計3から測定輝度値を受信する。また、後述する画素400ごとの演算階調と発光輝度との相関を表す階調・輝度テーブルの生成時には、情報処理装置2は、測定画素へ与える演算階調電圧値の制御及び輝度計3の制御を行い、測定輝度値を受信する。

【0067】

演算部21は、階調・輝度テーブルの各データ（演算階調値、輝度）が、代表階調・輝度特性上のデータ（階調値、輝度）と一致するよう、画素400ごとに、演算階調値をシフトさせる。また、演算部21は、シフトした演算階調値と、シフト前の演算階調値との相関データに基づいて、表示階調範囲における任意の入力階調データを補正する階調変換テーブルを画素400ごとに生成する。

【0068】

制御回路12は、情報処理装置2からの制御信号により、表示パネル11の有する画素400へ与える階調電圧値を制御する。また、制御回路12は、情報処理装置2で生成された階調変換テーブルをメモリ121へ書き込む機能を有する。

【0069】

[5. 製造方法]

次に、本実施の形態に係る表示装置の製造方法を説明する。

【0070】

図5は、実施の形態に係る表示装置の製造方法を説明する動作フローチャートである。同図には、表示装置1が有する表示パネルの輝度ムラを補正するための高精度な階調変換テーブルを生成するまでの工程が記載されている。上記高精度な階調変換テーブルとは、

10

20

30

40

50

入力階調データを補正する際に使用される複数の演算階調値の数が各画素で同一である状態で生成されたものである。上記補正パラメータを生成するため、本製造方法では、表示階調範囲における下限階調を含まずに、複数の演算階調値を選択する。以下、図5に従って、製造工程を説明していく。

#### 【0071】

まず、情報処理装置2は、表示部113全体に共通する、入力階調と発光輝度との相関を表す代表階調・輝度特性を取得する(S10)。ここで、代表階調・輝度特性とは、各画素400の入力階調と発光輝度との相関を表す階調・輝度特性を補正するターゲットとなる階調・輝度特性のことである。なお、ステップS10は、第1ステップに相当する。具体的には以下のようにして、代表階調・輝度特性を取得する。

10

#### 【0072】

まず、表示部113の有する複数の画素から、代表階調・輝度特性を決定するための測定用画素を抽出する。この測定用画素は、1つであってもよいし、規則性に従い、または無作為に選択された複数の画素であってもよい。情報処理装置2は、制御回路12に対し測定用画素へ入力階調電圧を印加させて当該画素の有機EL素子402を発光させる。次に、情報処理装置2は、輝度計3に対し、上記測定用画素の発光輝度を測定させる。上記測定用画素への入力階調電圧の印加及び発光輝度測定を、異なる入力階調電圧値において複数回実行させる。なお、上記測定用画素への入力階調電圧の印加及び発光輝度測定を、複数の測定用画素で一斉に実行してもよいし、測定用画素ごとに繰り返して実行してもよい。これにより、情報処理装置2は、演算部21にて測定用画素ごとの階調・輝度特性を求める。次に、情報処理装置2は、複数の測定用画素の各々について得られた階調・輝度特性を平均化することにより代表階調・輝度特性を求める。

20

#### 【0073】

上記代表階調・輝度特性の取得プロセスにより、表示部113に含まれる全ての画素の電流を測定するのではなく、複数の測定用画素についてのみ発光輝度を測定するので、表示部113全体に共通する代表階調・輝度特性を設定するまでの時間を大幅に短縮することができる。

30

#### 【0074】

なお、代表階調・輝度特性を取得する上記プロセスは、表示装置1ごとにしなくてもよい。例えば、代表階調・輝度特性として、同一条件で製造される他の表示装置の製造方法において取得された代表階調・輝度特性を自己の表示装置の代表階調・輝度特性としてそのまま利用してもよい。これにより、ある表示装置の製造方法で求められた代表階調・輝度特性を、当該装置と同一条件で製造される他の表示装置の製造方法で利用するので、複数の表示パネルの補正パラメータを測定するたびに代表階調・輝度特性を設定する手間を省くことができる。その結果、本装置の製造プロセスを短縮できる。

#### 【0075】

次に、情報処理装置2は、表示階調範囲内の下限階調を含まない複数の離散した演算階調値を選択する(S20)。

#### 【0076】

図6は、表示階調範囲と演算階調・輝度テーブルを示す図である。図6の上段に示すように、有機EL素子402の発光による画素400の輝度レベルは、例えば、階調0D0h～260h(hは16進数を表す)の401階調に細分されている。ここで、階調0D0h～260hは、画素400が表示し得る輝度の範囲である表示階調範囲であり、階調0D0hは発光輝度の下限を示す下限表示階調(黒表示階調)であり、階調260hは発光輝度の上限を示す上限表示階調である。

40

#### 【0077】

従来の補正方法では、上記複数の演算階調値として、下限表示階調(0D0h)及び上限表示階調(260h)を含むように選択する。この場合、下限表示階調(0D0h)を演算階調値として画素Pに供給することにより測定される画素Aの測定輝度値は、図6の下段に示すように、例えば、0.005051である。この測定輝度値は、輝度計3の測

50

定下限を下回る値であり、画素 A の正確な発光輝度を表すものではない。したがって、演算階調値としては、0 D 0 h を選択せず、1 4 0 h、1 A 0 h、2 0 0 h 及び 2 6 0 h という 4 値を選択する。これにより、画素 P の演算階調 - 輝度テーブルは、上記演算階調値の 4 値とそれらに対応した測定輝度の組み合わせで構成されることとなる。

#### 【 0 0 7 8 】

これに対して、本実施の形態に係る製造方法では、上記複数の演算階調値として、下限表示階調 (0 D 0 h) を含まないように選択する。例えば、演算階調値としては、0 D 0 h を含まず、0 D 4 h、1 4 0 h、1 A 0 h、2 0 0 h 及び 2 6 0 h という 5 値を選択する。ここで、階調 0 D 4 h における画素 P の測定輝度値は、0 . 0 2 2 7 2 9 である。この測定輝度値は、輝度計 3 の測定下限を上回る有効値であり、画素 P の正確な発光輝度を表すものである。これにより、本実施の形態に係るステップ S 2 0 及び後述するステップ S 3 0 では、画素 P の演算階調 - 輝度テーブルは、上記演算階調値の 5 値とそれらに対応した測定輝度の組み合わせで構成されることとなる。

10

#### 【 0 0 7 9 】

次に、情報処理装置 2 は、ステップ S 2 0 で選択した、複数の離散した演算階調値における発光輝度を画素 4 0 0 ごとに測定し、演算階調 - 輝度テーブルを生成する (S 3 0)。なお、上述した従来の補正方法では、下限表示階調を演算階調として輝度測定した場合、図 6 に示す画素 P では、輝度計 3 の測定限界よりも低い輝度値が測定され、図 1 に示す画素 Q では、輝度計 3 の測定限界よりも高い輝度値が測定される。これは、表示部 1 1 3 が有する画素 4 0 0 の回路特性のばらつきによるものである。これにより、各画素の演算階調 - 輝度テーブルのデータ数がばらついてしまう。

20

#### 【 0 0 8 0 】

これに対して、本実施の形態に係るステップ S 2 0 で選択した複数の離散した演算階調値は、表示階調範囲における下限階調を含まないので、各演算階調値における測定輝度値は全て有効な値となる。よって、各画素 4 0 0 の演算階調 - 輝度テーブルのデータ数を同一とすることができます。

#### 【 0 0 8 1 】

次に、情報処理装置 2 は、ステップ S 3 0 で生成された演算階調 - 輝度テーブルにおける、演算階調値と輝度との組み合わせに対応する各データ（演算階調値、輝度）が、代表階調 - 輝度特性上のデータ（階調値、輝度）となるよう、演算階調 - 輝度テーブルの演算階調値のシフト量を求める (S 4 0)。

30

#### 【 0 0 8 2 】

図 7 は、ステップ S 4 0 における演算階調値のシフトを説明するグラフである。同図のグラフにおいて、横軸は画素 4 0 0 に供給される入力階調電圧を表し、縦軸は画素 4 0 0 の発光輝度を表す。また、同図のグラフには、代表階調 - 輝度特性と、画素 P の 5 点の実測データ（演算階調値、輝度値）とが示されている。情報処理装置 2 は、図 7 に示された代表階調 - 輝度特性と、画素 P の実測データ（演算階調値、輝度値）とを比較していく。例えば、情報処理装置 2 は、画素 P の実測データ (a 1, A) が、代表階調 - 輝度特性上のデータ (a 2, A) となるよう、演算階調のシフト量 (a 2 - a 1) を求める。他の 4 点の実測データも同様にして、演算階調 b 1, c 1, d 1 及び e 1 のシフト量 (b 2 - b 1), (c 2 - c 1), (d 2 - d 1), (e 2 - e 1) を、それぞれ算出する。

40

#### 【 0 0 8 3 】

次に、情報処理装置 2 は、ステップ S 4 0 で算出したシフト量によりシフト前後の演算階調値の相関データから、表示階調全範囲における任意の入力階調データを補正する変換テーブルを生成する (S 5 0)。

#### 【 0 0 8 4 】

図 8 は、ステップ S 5 0 における階調変換テーブルを示す図である。同図のグラフにおいて、横軸は補正前の入力階調電圧を表し、縦軸は補正後の入力階調電圧を表す。本ステップ S 2 0 では、まず、演算部 2 1 は、ステップ S 4 0 で取得したシフト前後の演算階調値の相関データ (a 2, a 1), (b 2, b 1), (c 2, c 1), (d 2, d 1), 及

50

び(  $e_2$  、  $e_1$  )を、上記グラフ上にプロットする。具体的には、シフト後の演算階調値(  $a_2$  、  $b_2$  、  $c_2$  、  $d_2$  、  $e_2$  )を、補正前の入力階調電圧を示す横軸として、また、シフト前の演算階調値(  $a_1$  、  $b_1$  、  $c_1$  、  $d_1$  、  $e$  )を、補正後の入力階調電圧を示す縦軸としてプロットする。

【 0 0 8 5 】

次に、演算部 2 1 は、上記 5 点の相関データから、表示階調範囲における入力階調電圧を補正する際に参照する階調変換テーブルを生成する。例えば、演算部は、上記 5 点の相関データから、一次式(  $y = x + \alpha$  )で表される階調変換テーブルを生成する。ここで、 $y$  は補正後の入力階調電圧、 $x$  は補正前の入力階調電圧、 $\alpha$  は補正係数、 $\beta$  はオフセット値である。

10

【 0 0 8 6 】

なお、ステップ S 5 0 の後、情報処理装置 2 は、ステップ S 5 0 において求められた各画素の階調変換テーブルを、表示装置 1 のメモリ 1 2 1 に書き込む(ステップ S 6 0)。なお、本ステップ S 1 0 は、第 6 ステップに相当する。具体的には、メモリ 1 2 1 には、例えば、画素ごとに(補正係数、オフセット値)で構成される階調変換データが、表示部 1 1 3 (M 行 × N 列) のマトリクスに対応して格納される。

【 0 0 8 7 】

以上のステップ S 1 0 ~ S 6 0 が実行されることにより、本実施の形態に係る表示パネルの輝度ムラが解消される。例えば、上記製造工程が完了した後の表示装置 1 の映像表示動作において、以下のような処理がなされる。

20

【 0 0 8 8 】

まず、制御回路 1 2 は、外部から入力された映像信号に対して、画素ごとの入力階調データを生成する。例えば、全画素を一様な輝度 A で表示させるとする。このとき、制御回路 1 2 は、図 7 に示された代表階調 - 輝度特性より、全画素に供給すべき入力階調電圧値を  $a_2$  であると決定する。ただし、全画素に、同一の入力階調電圧  $a_2$  を供給した場合、画素ごとの特性ばらつきにより、輝度ムラが発生する。そこで、制御回路 1 2 は、入力階調電圧  $a_2$  を補正する。例えば、画素 P を輝度 A で発光させるには、図 7 に示すように入力階調電圧を  $a_1$  とすればよい。制御回路 1 2 は、この入力階調電圧の変換を、メモリ 1 2 1 に記憶されている階調変換テーブルを用いて行う。画素 P の階調変換データが(  $\alpha_p$  、  $\beta_p$  )であるとすると、補正後の入力階調電圧は、 $a_1 = \alpha_p \times a_2 + \beta_p$  として算出される。

30

【 0 0 8 9 】

図 9 は、実施の形態に係る表示装置と従来の表示装置との補正精度を比較する図である。同図には、上記ステップ S 2 0 において選択された複数の演算階調値の中に、表示階調範囲における下限階調値  $a_3$  が含まれる場合に生成される階調変換テーブルが示されている。演算階調値  $a_3$  において測定された輝度は、大きな誤差を含む測定値であるため、当該測定値に基づいて  $a_3$  がシフトされた後の演算階調値  $a_4$  もまた、大きな誤差を含んでいる。このため、ステップ S 5 0 で生成される階調変換テーブルの精度も低い。例えば、図 9 に示すように、階調変換一次式は、一意に定まらず、補正係数  $\alpha$  は 1 ~ 2 及びオフセット値は 1 ~ 2 のばらつきを有することとなる。これにより、高精度に輝度ムラを抑制することができない。

40

【 0 0 9 0 】

これに対して、本実施の形態に係る表示装置 1 の製造方法では、上記ステップ S 2 0 において選択された複数の演算階調値の中に、表示階調範囲における下限階調値が含まれない。よって、演算階調値において測定された輝度も誤差を含まないので、当該測定輝度に基づいて算出されたシフト後の演算階調値もまた誤差を含まない。このため、ステップ S 5 0 で生成される階調変換テーブルの精度は高い。これにより、高精度に輝度ムラを抑制することが可能となる。

【 0 0 9 1 】

図 1 0 は、実施の形態に係る演算階調 - 輝度テーブルを示す図である。同図は、具体的

50

には、本実施の形態におけるステップ S 2 0 及び S 3 0 を説明する図である。表示部 1 1 3 の各画素 4 0 0 において、映像として使用される下限階調（黒表示）を含まない、複数の演算階調値（D 4、1 4 0、1 A 0、2 0 0、2 6 0：1 6 進表記）が選択されている（S 2 0）。図 1 0 には、画素 P 及び画素 Q における演算階調 - 輝度テーブルが示されている。

【0 0 9 2】

ここで、画素 P 及び画素 Q の演算階調 D 4 では、それぞれ、画素輝度として 0 . 0 2 2 7 2 9 及び 0 . 0 3 0 3 6 と測定されている。この測定輝度値は、いずれも輝度計 3 の測定下限値を上回っており、正確な発光輝度を反映したものとなっている。

【0 0 9 3】

上記のように、表示部 1 1 3 が有する全ての画素 4 0 0 において、同一の演算階調数に基づいて各画素 4 0 0 の階調変換テーブルを生成した場合、例えば、全画素同一の入力階調データを画素ごとに補正し、該補正された入力階調データを各画素に供給すると、図 1 0 に示すように、画素 P と画素 Q とで発光輝度が同一となる。つまり、表示パネル全体にわたって輝度ムラを効果的に抑制することが可能となる。

【0 0 9 4】

（その他の実施の形態）

以上、上記実施の形態に基づいて表示パネルの製造方法を説明してきたが、本発明は、上述した実施の形態に限定されるものではない。実施の形態における任意の構成要素を組み合わせて実現される別の実施の形態や、実施の形態に対して本発明の主旨を逸脱しない範囲で当業者が思いつく各種変形を施して得られる変形例や、本実施の形態に係る有機 E L 表示パネルを内蔵した各種機器も本発明に含まれる。

【0 0 9 5】

なお、上記実施の形態のステップ S 2 0 ~ ステップ S 5 0 では、複数の演算階調値の選択、演算階調 - 輝度テーブルの作成、演算階調値のシフト、及び、階調変換テーブルの生成を、画素ごとに実行したが、これに限られない。隣接または近傍の画素において取得された複数の演算階調値、演算階調 - 輝度テーブル、シフトした演算階調値、及び、階調変換テーブルを援用してもよい。これにより、輝度ムラの補正精度は低下することが想定されるが、補正処理に関する製造工程を簡素化できるという効果が奏される。

【0 0 9 6】

また、上記実施の形態では、本開示の表示部 1 1 3 が有する画素回路構成の一例を挙げたが、画素 4 0 0 の回路構成は上記回路構成に限定されない。例えば、上記実施の形態では、正電源線と負電源線との間に、イネーブルトランジスタ 4 0 5、駆動トランジスタ 4 0 1 及び有機 E L 素子 4 0 2 が、この順に配置されている構成を例示したが、これらの 3 素子が異なる順で配置されていてもよい。つまり、本開示の表示部 1 1 3 は、駆動トランジスタが n 型であっても p 型であっても、駆動トランジスタ 4 0 1 のドレイン及びソース、ならびに有機 E L 素子 4 0 2 のアノード及びカソードが、正電源線と負電源線との間の電流径路上に配置されていればよく、駆動トランジスタ 4 0 1 及び有機 E L 素子 4 0 2 の配置順には限定されない。

【0 0 9 7】

また、上記実施の形態において、選択トランジスタ 4 0 4、イネーブルトランジスタ 4 0 5、参照トランジスタ 4 0 6、及び初期化トランジスタ 4 0 7 は、n 型であっても p 型であっても、両方の組み合わせであってもよい。

【0 0 9 8】

また、上記実施の形態に係る表示装置の製造方法では、有機 E L 素子 4 0 2 を用いた表示装置 1 を製造する場合を例に述べたが、有機 E L 素子以外の発光素子を用いた表示装置の製造方法に適用してもよい。

【0 0 9 9】

また、本発明は、上記実施の形態で説明した特徴的なステップを含む表示装置 1 の製造方法として実現することができるだけでなく、当該製造方法に含まれる特徴的なステップ

を手段として生成された階調変換テーブルを有する表示装置1としても、上記と同様の効果を奏す。つまり、表示装置1は、有機EL素子402と、有機EL素子402の発光輝度を決定する入力階調データが供給されることにより、当該入力階調データに対応した駆動電流を前記発光素子へ流す駆動トランジスタ401素子とを含む複数の画素400と、画素400に入力階調データを供給するためのデータ線434と、画素400に走査信号を供給するための走査線424と、データ線434に入力階調データを供給するデータ線駆動回路112と、走査線424に走査信号を供給する走査線駆動回路111と、入力階調データを補正する際に参照する階調変換テーブルを画素400毎に格納するメモリ121と、外部から入力された映像信号に対してメモリ121から画素400ごとの階調変換テーブルを読み出して、入力階調データを補正する補正部とを備える。上記階調変換テーブルは、代表階調・輝度特性を取得する第1ステップと、表示階調範囲における下限階調を含まない複数の離散した演算階調値を選択する第2ステップと、画素400ごとの演算階調・輝度テーブルを作成する第3ステップと、演算階調・輝度テーブルの各データが、代表階調・輝度特性上のデータと一致するような演算階調値のシフト量を求める第4ステップと、第4ステップで求められたシフト量でシフトした演算階調値とシフト前の演算階調値との相関データに基づいて、表示階調範囲における任意の入力階調データを補正する階調変換テーブルを画素ごとに生成する第5ステップにより生成される。

10

## 【0100】

また、本実施の形態に係る表示装置の製造方法により製造された表示装置1は、図11に記載されたような薄型フラットTVに内蔵される。本実施の形態に係る表示装置の製造方法により、輝度ムラが高精度に抑制された高品質な薄型フラットTVが実現される。

20

## 【産業上の利用可能性】

## 【0101】

本発明に係る表示装置及びその製造方法は、大画面及び高解像度が要望される薄型テレビ及びパーソナルコンピュータのディスプレイなどの技術分野に有用である。

## 【符号の説明】

## 【0102】

1 表示装置

2 情報処理装置

3 輝度計

30

11 表示パネル

12 制御回路

21 演算部

22 記憶部

23 通信部

111 走査線駆動回路

112 データ線駆動回路

113 表示部

121 メモリ

400 画素

40

401 駆動トランジスタ

402 有機EL素子

403 保持容量素子

404 選択トランジスタ

405 イネーブルトランジスタ

406 参照トランジスタ

407 初期化トランジスタ

424、425、426、427 走査線

434 データ線

【図2】

【図3】

【図4】

【図5】

【図7】

【図8】

【図9】

【図11】

【図1】

【図6】

【図 10】

---

フロントページの続き

F ターム(参考) 5C080 AA06 BB05 DD05 DD15 DD28 EE29 FF11 JJ01 JJ02 JJ03

JJ05 JJ07 KK02 KK43

5C380 AA01 AB06 AC04 AC07 AC08 BA36 BA38 BB04 CA12 CB17

CC04 CC07 CC27 CC33 CC39 CC65 CD015 CF13 CF68 DA02

DA06 DA47 EA02 EA04 EA05 FA05 FA21 FA23 FA28 GA18

HA01

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2016009136A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2016-01-18 |

| 申请号            | JP2014130814                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2014-06-25 |

| [标]申请(专利权)人(译) | 日本有机雷特显示器股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 株式会社JOLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 根来靖典<br>沖川昌史                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 发明人            | 根来 靖典<br>沖川 昌史                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G09G3/30 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G09G3/30.K G09G3/20.611.H G09G3/20.642.A G09G3/20.670.Q G09G3/20.641.P G09G3/3225<br>G09G3/3233 G09G3/3266 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD15 5C080/DD28 5C080/EE29 5C080/FF11 5C080<br>/JJ01 5C080/JJ02 5C080/JJ03 5C080/JJ05 5C080/JJ07 5C080/KK02 5C080/KK43 5C380/AA01 5C380<br>/AB06 5C380/AC04 5C380/AC07 5C380/AC08 5C380/BA36 5C380/BA38 5C380/BB04 5C380/CA12<br>5C380/CB17 5C380/CC04 5C380/CC07 5C380/CC27 5C380/CC33 5C380/CC39 5C380/CC65 5C380<br>/CD015 5C380/CF13 5C380/CF68 5C380/DA02 5C380/DA06 5C380/DA47 5C380/EA02 5C380/EA04<br>5C380/EA05 5C380/FA05 5C380/FA21 5C380/FA23 5C380/FA28 5C380/GA18 5C380/HA01 |         |            |

| 代理人(译)         | 吉川修<br>Sobashima正雄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 其他公开文献         | JP6358615B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 摘要(译)          | <p>解决的问题：提供一种显示装置的制造方法，该显示装置的制造方法能够在所有显示等级上高精度地抑制亮度不均。一种制造显示装置1的方法，其中将每个包括有机EL元件402和驱动晶体管401的像素400排列成矩阵，并且获得整个显示部分113共有的代表性灰度-亮度特性。第一步，选择在显示灰度范围内不包括下限灰度的多个操作灰度值的第二步骤，并且针对每个像素测量在多个操作灰度值的每一个处的发光灰度 创建亮度表的第三步骤，以及获取多个计算灰度值的偏移量的第四步骤，以使计算灰度亮度表的每个数据与代表灰度亮度特性的数据相匹配，第五步骤，为每个像素生成灰度转换表，该灰度转换表基于在偏移量之前和之后所计算的多个灰度值的相关数据来校正显示灰度范围内的任何输入灰度数据。.. [选择图]图5</p>                                                                                                                                                                              |         |            |

| (21)出願番号       | 特願2014-130814 (P2014-130814)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| (22)出願日        | 平成26年6月25日 (2014.6.25)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| (71)出願人        | 514188173<br>株式会社JOLED<br>東京都千代田区神田錦町三丁目23番地                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| (74)代理人        | 100189430<br>弁理士 吉川 修一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| (74)代理人        | 100190805<br>弁理士 傀島 正朗                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| (72)発明者        | 根来 靖典<br>大阪府門真市大字門真1006番地 パナソニック株式会社内                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| (72)発明者        | 沖川 昌史<br>大阪府門真市大字門真1006番地 パナソニック株式会社内                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 最終頁に続く         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |