(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-145532

(P2011-145532A)

(43) 公開日 平成23年7月28日(2011.7.28)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | J 3K107     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 624B 5C080  |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 | 642A 5C380  |

|                             | G09G 3/20 | 611H        |

|                             | G09G 3/20 | 612G        |

審査請求 未請求 請求項の数 6 O L (全 19 頁) 最終頁に続く

|           |                          |          |                                        |

|-----------|--------------------------|----------|----------------------------------------|

| (21) 出願番号 | 特願2010-6991 (P2010-6991) | (71) 出願人 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号 |

| (22) 出願日  | 平成22年1月15日 (2010.1.15)   | (74) 代理人 | 100098785<br>弁理士 藤島 洋一郎                |

|           |                          | (74) 代理人 | 100109656<br>弁理士 三反崎 泰司                |

|           |                          | (74) 代理人 | 100130915<br>弁理士 長谷部 政男                |

|           |                          | (74) 代理人 | 100155376<br>弁理士 田名網 孝昭                |

|           |                          | (72) 発明者 | 三並 徹雄<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

最終頁に続く

(54) 【発明の名称】表示装置およびその駆動方法ならびに電子機器

## (57) 【要約】

【課題】ユニットスキャンにおいて、発光期間を短くすることなく、スジ状の模様が発生するのを防止することの可能な表示装置およびその駆動方法ならびに電子機器を提供する。

【解決手段】電源線 PSL が、複数の画素行を一つのユニットUとして、ユニットUごとに一つずつ設けられている。電源線PSLの電圧を利用して各駆動トランジスタTr<sub>1</sub>のゲート-ソース間電圧V<sub>gs</sub>を駆動トランジスタTr<sub>1</sub>の閾値電圧V<sub>th</sub>よりも大きくした上で、各駆動トランジスタTr<sub>1</sub>の閾値補正がなされる。その後、各有機EL素子11を発光させる前に再度、必要なラインに対して駆動トランジスタTr<sub>1</sub>の閾値電圧が補正される。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

行状に配置された複数の走査線および複数の電源線と、列状に配置された複数の信号線と、行列状に配置された複数の画素とを含む表示部と、

各画素を駆動する駆動部と

を備え、

各画素は、発光素子および画素回路を有し、

前記画素回路は、前記発光素子に流れる電流を制御する第1トランジスタと、前記信号線の電圧を前記第1トランジスタに書き込む第2トランジスタとを有し、

前記複数の電源線は、複数の画素行を1つのユニットとして、前記ユニットごとに1つずつ設けられ、

前記駆動部は、前記複数のユニットのうち第1ユニットにおいて、各発光素子を消光したのち、前記電源線の電圧をローにしている間であって各信号線に非階調信号を印加している間に前記第2トランジスタをオンする第1パルス信号を各走査線に印加して各第1トランジスタのゲート-ソース間電圧を前記第1トランジスタの閾値電圧よりも大きくし、続いて、前記電源線の電圧をハイにし、各信号線に非階調信号を印加している間に前記第2トランジスタをオンする第2パルス信号を各走査線に印加して各第1トランジスタの閾値電圧を補正し、さらに、各発光素子を発光させる前であって各信号線に非階調信号を印加している間に前記第1ユニットに含まれる複数の走査線のうち少なくとも最後に発光素子を発光させるラインの走査線に対して、前記第2トランジスタをオンする第3パルス信号を印加して当該第3パルス信号の印加されたラインの第1トランジスタの閾値電圧を補正する

表示装置。

**【請求項 2】**

前記駆動部は、前記第1ユニットにおいて、前記第1パルス信号を各走査線に同時に印加する

請求項1に記載の表示装置。

**【請求項 3】**

前記駆動部は、前記第1ユニットにおいて、前記第2パルス信号を各走査線に同時に印加する

請求項1または請求項2に記載の表示装置。

**【請求項 4】**

前記駆動部は、前記第1ユニットにおいて、前記第3パルス信号を各走査線に印加する

請求項1または請求項2に記載の表示装置。

**【請求項 5】**

行状に配置された複数の走査線および複数の電源線と、列状に配置された複数の信号線と、行列状に配置された複数の画素とを含む表示部と、

各画素を駆動する駆動部と

を備え、

各画素は、発光素子および画素回路を有し、

前記画素回路は、前記発光素子に流れる電流を制御する第1トランジスタと、前記信号線の電圧を前記第1トランジスタに書き込む第2トランジスタとを有し、

前記複数の電源線は、複数の画素行を1つのユニットとして、前記ユニットごとに1つずつ設けられた表示装置において、前記複数のユニットのうち第1ユニットにおいて、各発光素子を消光したのち、前記電源線の電圧をローにしている間であって各信号線に非階調信号を印加している間に前記第2トランジスタをオンする第1パルス信号を各走査線に印加して各第1トランジスタのゲート-ソース間電圧を前記第1トランジスタの閾値電圧よりも大きくし、続いて、前記電源線の電圧をハイにし、各信号線に非階調信号を印加している間に前記第2トランジスタをオンする第2パルス信号を各走査線に印加して各第1トランジスタの閾値電圧を補正し、さらに、各発光素子を発光させる前であって各信号線

10

20

30

40

50

に非階調信号を印加している間に前記第1ユニットに含まれる複数の走査線のうち少なくとも最後に発光素子を発光させるラインの走査線に対して、前記第2トランジスタをオンする第3パルス信号を印加して当該第3パルス信号の印加されたラインの第1トランジスタの閾値電圧を補正する

表示装置の駆動方法。

【請求項6】

表示装置を備え、

前記表示装置は、

行状に配置された複数の走査線および複数の電源線と、列状に配置された複数の信号線と、行列状に配置された複数の画素とを含む表示部と、

10

各画素を駆動する駆動部と

を備え、

各画素は、発光素子および画素回路を有し、

前記画素回路は、前記発光素子に流れる電流を制御する第1トランジスタと、前記信号線の電圧を前記第1トランジスタに書き込む第2トランジスタとを有し、

20

前記複数の電源線は、複数の画素行を1つのユニットとして、前記ユニットごとに1つずつ設けられ、

前記駆動部は、前記複数のユニットのうち第1ユニットにおいて、各発光素子を消光したのち、前記電源線の電圧をローにしている間であって各信号線に非階調信号を印加している間に前記第2トランジスタをオンする第1パルス信号を各走査線に印加して各第1トランジスタのゲート-ソース間電圧を前記第1トランジスタの閾値電圧よりも大きくし、続いて、前記電源線の電圧をハイにし、各信号線に非階調信号を印加している間に前記第2トランジスタをオンする第2パルス信号を各走査線に印加して各第1トランジスタの閾値電圧を補正し、さらに、各発光素子を発光させる前であって各信号線に非階調信号を印加している間に前記第1ユニットに含まれる複数の走査線のうち少なくとも最後に発光素子を発光させるラインの走査線に対して、前記第2トランジスタをオンする第3パルス信号を印加して当該第3パルス信号の印加されたラインの第1トランジスタの閾値電圧を補正する

電子機器。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画素ごとに配置した発光素子で画像を表示する表示装置およびその駆動方法に関する。また、本発明は、上記表示装置を備えた電子機器に関する。

【背景技術】

【0002】

近年、画像表示を行う表示装置の分野では、画素の発光素子として、流れる電流値に応じて発光輝度が変化する電流駆動型の光学素子、例えば有機EL(Electro Luminescence)素子を用いた表示装置が開発され、商品化が進められている。有機EL素子は、液晶素子などと異なり自発光素子である。そのため、有機EL素子を用いた表示装置(有機EL表示装置)では、光源(バックライト)が必要ないので、光源を必要とする液晶表示装置と比べて画像の視認性が高く、消費電力が低く、かつ素子の応答速度が速い。

40

【0003】

有機EL表示装置では、液晶表示装置と同様、その駆動方式として単純(パッシブ)マトリクス方式とアクティブマトリクス方式がある。前者は、構造が単純であるものの、大型かつ高精細の表示装置の実現が難しいなどの問題がある。そのため、現在では、アクティブマトリクス方式の開発が盛んに行なわれている。この方式は、画素ごとに配した発光素子に流れる電流を駆動トランジスタによって制御するものである。

【0004】

一般に、駆動トランジスタの閾値電圧 $V_{th}$ や移動度 $\mu$ が経時的に変化したり、製造プロ

50

セスのばらつきによって閾値電圧  $V_{th}$  や移動度  $\mu$  が画素ごとに異なったりする場合がある。閾値電圧  $V_{th}$  や移動度  $\mu$  が画素ごとに異なる場合には、駆動トランジスタに流れる電流値が画素ごとにばらつくので、駆動トランジスタのゲートに同じ電圧を印加しても、有機EL素子の発光輝度がばらつき、画面の一様性（ユニフォーミティ）が損なわれる。そこで、閾値電圧  $V_{th}$  や移動度  $\mu$  の変動に対する補正機能を組み込んだ表示装置が開発されている（例えば、特許文献 1 参照）。

#### 【0005】

ところで、アクティブマトリクス方式の表示装置では、信号線を駆動する水平駆動回路や、各画素を順次選択する書き込み走査回路、各画素に電力を供給する電源走査回路は、いずれも基本的にシフトレジスタ（図示せず）で構成されており、画素の各列または各行に対応して、1段ごとに信号出力部（図示せず）を備えている。そのため、画素の列および行の数が増えると、それに従って信号線やゲート線の本数が増え、シフトレジスタの出力段数もその分増加するので、表示装置の周辺回路の大型化を招いていた。

10

#### 【0006】

そこで、シフトレジスタの出力段を共用し、周辺回路の大型化を低減する方策が従来から行われている。例えば特許文献 2 では、信号線を複数の画素で共用化する方式が提案されている。この様にすれば、水平駆動回路内のシフトレジスタの出力段を複数の画素列で共用化でき、その分回路規模の縮小化、回路面積の縮小化、回路コストの低減化が可能になる。

20

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

【特許文献 1】特開 2008 - 083272 号公報

【特許文献 2】特開 2006 - 251322 号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

特許文献 2 には、水平駆動回路内のシフトレジスタの出力段を複数の画素列で共用化することが記載されていたが、書き込み走査回路や電源走査回路においてもシフトレジスタの出力段の共用化を図ることは表示装置のコストパフォーマンスを高める上で重要である。特に、電源走査回路については、電流供給能力の安定化のため、信号出力部のサイズを大きくとる必要があるので、電源走査回路内のシフトレジスタの出力段を複数の画素行で共用化し、信号出力部の数を少なくすることにより、表示装置の低コスト化および小型化を効果的に実現することができる。

30

#### 【0009】

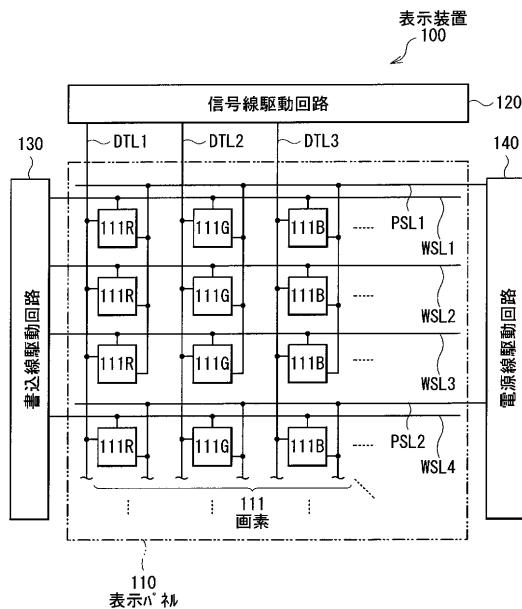

図 18 は、電源走査回路内の信号出力部が複数の画素行で共用化された表示装置の概略構成を表したものである。図 18 に記載の表示装置 100 では、電源線駆動回路 140 内の個々の信号出力部に電源線 PSL (PSL1, PSL2, ...) が一つずつ接続されており、個々の電源線 PSL (PSL1, PSL2, ...) に複数の画素行（図 18 では 3 行）に属する画素 111 が接続されている。一方、信号線駆動回路 120 内の個々の信号出力部に信号線 DTL (DTL1, DTL2, ...) が一つずつ接続されており、個々の信号線 (DTL1, DTL2, ...) に各行の画素 111 が一つずつ接続されている。また、書込線駆動回路 130 内の個々の信号出力部に書込線 WSL (WSL1, WSL2, ...) が一つずつ接続されており、個々の書込線 WSL (WSL1, WSL2, ...) に各列の画素 111 が一つずつ接続されている。

40

#### 【0010】

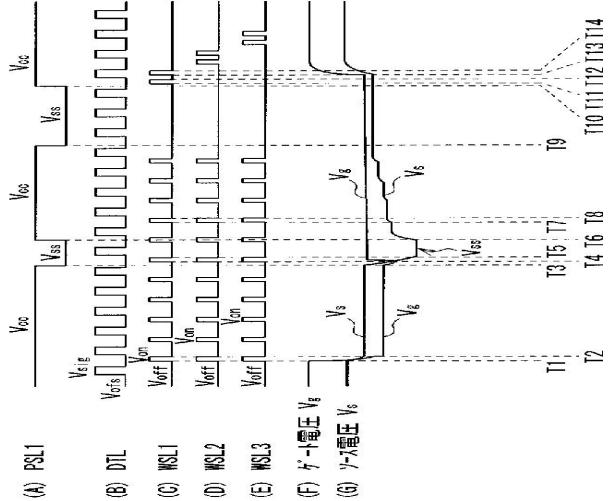

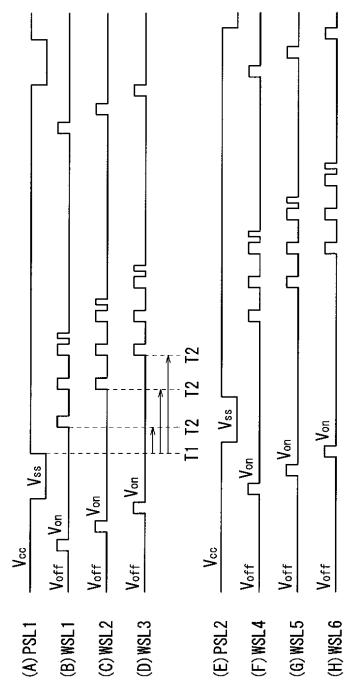

図 19 は、図 18 に記載の表示装置 100 における各種波形の一例を表したものである。図 19 には、電源線 PSL に 2 種類の電圧 ( $V_{cc}$ ,  $V_{ss}$  ( $< V_{cc}$ )) が、書込線 WSL 1 ~ WSL 6 に 2 種類の電圧 ( $V_{on}$ ,  $V_{off}$  ( $< V_{on}$ )) が印加されている様子が示されている。図 19 からわかるように、表示装置 100 では、複数の画素行（図 19 では 3 行

50

)を一つのユニットとして、電源線 PSL ( PSL1, PSL2, ..... )から各画素 111 にユニットごとに共通のタイミングで  $V_{cc}$  と  $V_{ss}$  が印加される。

#### 【0011】

図 19 に示したように、同一ユニット内において、電源線 PSL の電圧が  $V_{ss}$  から  $V_{cc}$  に上がった時 ( $T_1$ ) から閾値補正を開始する時 ( $T_2$ ) までの時間 (待ち時間) がラインによって異なっている。例えば、同一ユニット内に 30 ライン含まれている場合に、1 ライン目の待ち時間と 30 ライン目の待ち時間との差が 29H となる。この待ち時間の間、画素回路内において電流リークが生じているので、駆動トランジスタのソース電圧は、待ち時間が長ければ長いほど、上昇してしまう。そのため、一のユニット内において、最後のラインの画素 111 のゲート - ソース間電圧は最初のラインの画素 111 のゲート - ソース間電圧よりも小さくなる。その結果、一のユニットに含まれるライン数が多すぎると、時刻  $T_1$  ~  $T_2$  の間、最後のラインの輝度は最初のラインの輝度よりも暗くなってしまう、隣接するユニット間にスジ状の模様が発生してしまう。

#### 【0012】

そこで、上記の待ち時間を十分に長くし、各ラインの画素 111 のゲート - ソース間電圧の差を小さくする方策が考えられる。しかし、そのようにした場合には、発光期間が短くなってしまうという問題があった。

#### 【0013】

また、閾値補正を行う際には、駆動トランジスタのソース電圧を事前に所定の値よりも下げておくことが必要となるが、図 19 の例では、駆動トランジスタのソース電圧が  $V_{ss} + V_{th}$  までしか下がらない。そのため、 $V_{ss}$  を大きく下げる必要となるが、そのようにした場合には、電源線駆動回路 140 から印加される選択パルスによるカッピングにより、ユニット間にスジ状の模様が発生してしまう。

#### 【0014】

本発明はかかる問題点に鑑みてなされたもので、その目的は、ユニットスキャンにおいて、発光期間を短くすることなく、スジ状の模様が発生するのを防止することの可能な表示装置およびその駆動方法ならびに電子機器を提供することにある。

#### 【課題を解決するための手段】

#### 【0015】

本発明の表示装置は、行状に配置された複数の走査線および複数の電源線と、列状に配置された複数の信号線と、行列状に配置された複数の画素とを含む表示部を備えており、さらに、各画素を駆動する駆動部を備えている。各画素は、発光素子および画素回路を有している。画素回路は、発光素子に流れる電流を制御する第 1 トランジスタと、信号線の電圧を第 1 トランジスタに書き込む第 2 トランジスタとを有している。複数の電源線は、複数の画素行を 1 つのユニットとして、ユニットごとに 1 つずつ設けられている。駆動部は、複数のユニットのうち第 1 ユニットにおいて、以下の 3 つの動作を (A), (B), (C) の順に実行するようになっている。

(A) 各発光素子を消光したのち、電源線の電圧をローにしている間であって各信号線に非階調信号を印加している間に第 2 トランジスタをオンする第 1 パルス信号を各走査線に印加して各第 1 トランジスタのゲート - ソース間電圧を第 1 トランジスタの閾値電圧よりも大きくすること

(B) 続いて、電源線の電圧をハイにし、各信号線に非階調信号を印加している間に第 2 トランジスタをオンする第 2 パルス信号を各走査線に印加して各第 1 トランジスタの閾値電圧を補正すること

(C) さらに、各発光素子を発光させる前であって各信号線に非階調信号を印加している間に第 1 ユニットに含まれる複数の走査線のうち少なくとも最後に発光素子を発光させるラインの走査線に対して、第 2 トランジスタをオンする第 3 パルス信号を印加して当該第 3 パルス信号の印加されたラインの第 1 トランジスタの閾値電圧を補正すること

#### 【0016】

本発明の電子機器は、上記表示装置を備えたものである。

## 【0017】

本発明の表示装置の駆動方法は、以下の構成を備えた表示装置において、複数のユニットのうち第1ユニットに対して、以下の3つのステップを(A),(B),(C)の順に実行するものである。

(A) 各発光素子を消光したのち、電源線の電圧をローにしている間であって各信号線に非階調信号を印加している間に第2トランジスタをオンする第1パルス信号を各走査線に印加して各第1トランジスタのゲート-ソース間電圧を第1トランジスタの閾値電圧よりも大きくするステップ

(B) 続いて、電源線の電圧をハイにし、各信号線に非階調信号を印加している間に第2トランジスタをオンする第2パルス信号を各走査線に印加して各第1トランジスタの閾値電圧を補正するステップ

(C) さらに、各発光素子を発光させる前であって各信号線に非階調信号を印加している間に第1ユニットに含まれる複数の走査線のうち少なくとも最後に発光素子を発光させるラインの走査線に対して、第2トランジスタをオンする第3パルス信号を印加して当該第3パルス信号の印加されたラインの第1トランジスタの閾値電圧を補正するステップ

## 【0018】

上記駆動方法が用いられる表示装置は、行状に配置された複数の走査線および複数の電源線と、列状に配置された複数の信号線と、行列状に配置された複数の画素とを含む表示部を備えており、さらに、各画素を駆動する駆動部を備えている。各画素は、発光素子および画素回路を有している。画素回路は、発光素子に流れる電流を制御する第1トランジスタと、信号線の電圧を第1トランジスタに書き込む第2トランジスタとを有している。複数の電源線は、複数の画素行を1つのユニットとして、ユニットごとに1つずつ設けられている。

## 【0019】

本発明の表示装置およびその駆動方法ならびに電子機器では、電源線の電圧を利用して各第1トランジスタのゲート-ソース間電圧を第1トランジスタの閾値電圧よりも大きくした上で、各第1トランジスタの閾値補正がなされる。従って、電源線の電圧を大きく下げる必要がない。また、各発光素子を発光させる前に再度、必要なラインに対して第1トランジスタの閾値電圧が補正される。これにより、各ラインにおいて、第1トランジスタの閾値補正の待ち時間を短くすることができる。

## 【発明の効果】

## 【0020】

本発明の表示装置およびその駆動方法ならびに電子機器によれば、電源線の電圧を大きく下げる必要がないようにすると共に、各ラインにおいて、第1トランジスタの閾値補正の待ち時間を短くするようにした。これにより、ユニットスキャンにおいて、発光期間を短くすることなく、スジ状の模様が発生するのを防止することができる。

## 【図面の簡単な説明】

## 【0021】

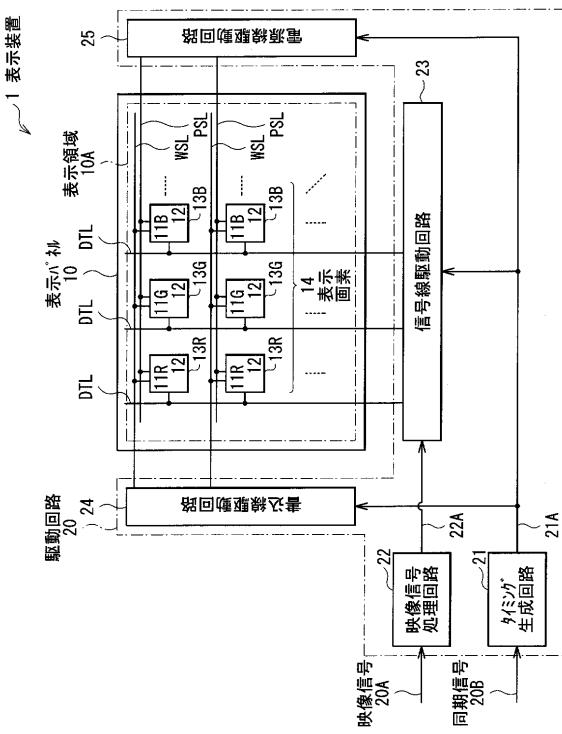

【図1】本発明の一実施の形態に係る表示装置の一例を表す構成図である。

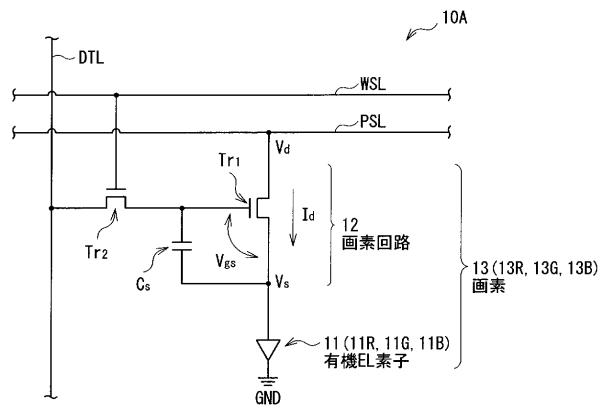

【図2】図1の画素の内部構成の一例を表す構成図である。

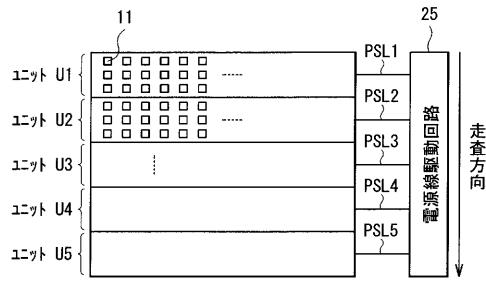

【図3】図1の表示装置のユニットスキャンについて説明するための概念図である。

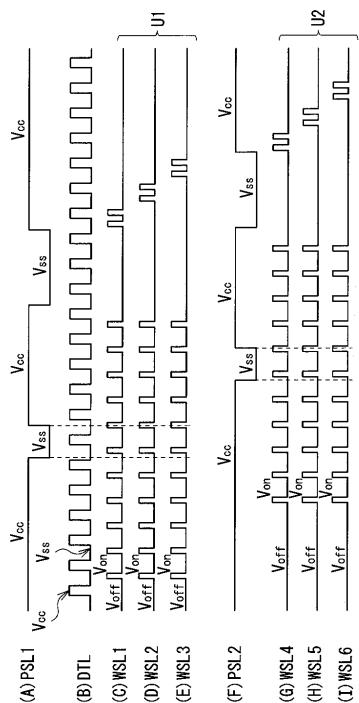

【図4】図1の表示装置の動作の一例について説明するための波形図である。

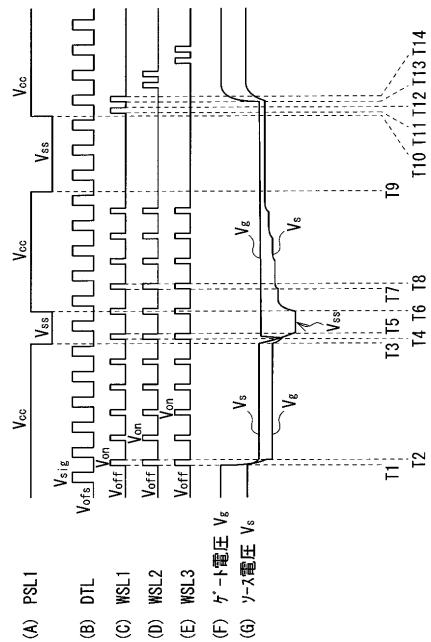

【図5】一の画素における動作の一例について説明するための波形図である。

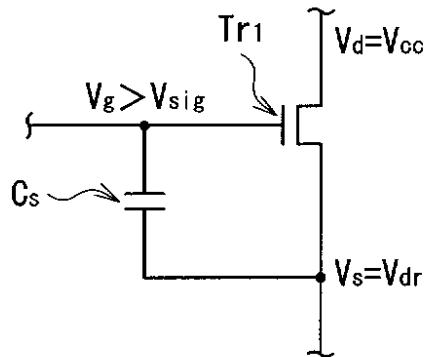

【図6】一の画素内の発光時の電圧関係について説明するための回路図である。

【図7】一の画素内の時刻T<sub>1</sub>の電圧関係について説明するための回路図である。

【図8】一の画素内の時刻T<sub>3</sub>の電圧関係について説明するための回路図である。

【図9】一の画素内の時刻T<sub>4</sub>の電圧関係について説明するための回路図である。

【図10】一の画素内の時刻T<sub>6</sub>の電圧関係について説明するための回路図である。

【図11】一の画素内の時刻T<sub>13</sub>の電圧関係について説明するための回路図である。

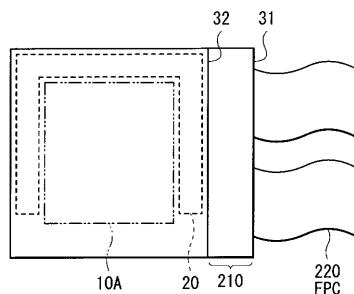

【図12】上記実施の形態の表示装置を含むモジュールの概略構成を表す平面図である。

10

20

30

40

50

【図13】上記実施の形態の表示装置の適用例1の外観を表す斜視図である。

【図14】(A)は適用例2の表側から見た外観を表す斜視図であり、(B)は裏側から見た外観を表す斜視図である。

【図15】適用例3の外観を表す斜視図である。

【図16】適用例4の外観を表す斜視図である。

【図17】(A)は適用例5の開いた状態の正面図、(B)はその側面図、(C)は閉じた状態の正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。

【図18】従来の表示装置の一例を表す構成図である。

【図19】図18の表示装置の動作の一例について説明するための波形図である。 10

【図20】図18の表示装置における電流リークについて説明するための回路図である。

【発明を実施するための形態】

【0022】

以下、発明を実施するための形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

1. 実施の形態(図1～図11)

2. モジュールおよび適用例(図12～図17)

3. 従来例(図18～図20)

【0023】 20

<実施の形態>

図1は、本発明の一実施の形態に係る表示装置1の全体構成の一例を表したものである。この表示装置1は、例えば、表示パネル10(表示部)と、駆動回路20(駆動部)とを備えている。

【0024】

(表示パネル10)

表示パネル10は、発光色の互いに異なる3種類の有機EL素子11R, 11G, 11B(発光素子)が2次元配置された表示領域10Aを有している。表示領域10Aとは、有機EL素子11R, 11G, 11Bから発せられる光を利用して映像を表示する領域である。有機EL素子11Rは赤色光を発する有機EL素子であり、有機EL素子11Gは緑色光を発する有機EL素子であり、有機EL素子11Bは青色光を発する有機EL素子である。なお、以下では、有機EL素子11R, 11G, 11Bの総称として有機EL素子11を適宜、用いるものとする。 30

【0025】

(表示領域10A)

図2は、表示領域10A内の回路構成の一例を表したものである。表示領域10A内には、複数の画素回路12が個々の有機EL素子11と対となって2次元配置されている。なお、本実施の形態では、一対の有機EL素子11および画素回路12が1つの画素13を構成している。より詳細には、図1に示したように、一対の有機EL素子11Rおよび画素回路12が1つの画素13R(赤色用の画素)を構成し、一対の有機EL素子11Gおよび画素回路12が1つの画素13G(緑色用の画素)を構成し、一対の有機EL素子11Bおよび画素回路12が1つの画素13B(青色用の画素)を構成している。さらに、互いに隣り合う3つの画素13R, 13G, 13Bが1つの表示画素14を構成している。 40

【0026】

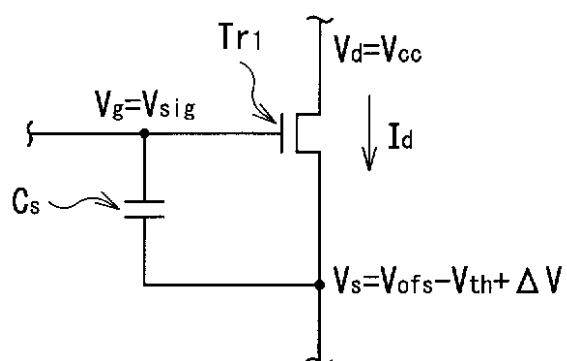

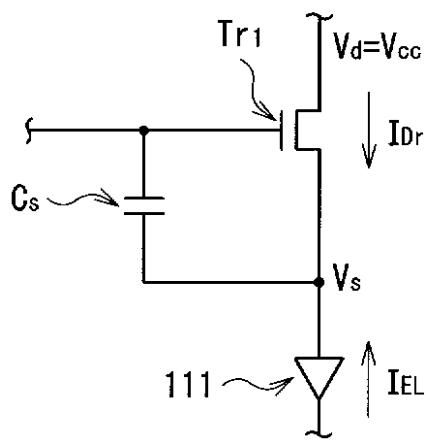

各画素回路12は、例えば、有機EL素子11に流れる電流を制御する駆動トランジスタTr<sub>1</sub>(第1トランジスタ)と、信号線DTLの電圧を駆動トランジスタTr<sub>1</sub>に書き込む書き込みトランジスタTr<sub>2</sub>(第2トランジスタ)と、保持容量Csとによって構成されたものであり、2Tr<sub>1</sub>Cの回路構成となっている。駆動トランジスタTr<sub>1</sub>および書き込みトランジスタTr<sub>2</sub>は、例えば、nチャネルMOS型の薄膜トランジスタ(TFT)(T 50

hin Film Transistor) )により形成されている。駆動トランジスタ  $T_{r_1}$  または書き込みトランジスタ  $T_{r_2}$  は、例えば、p チャネルMOS型の TFT であってもよい。

#### 【0027】

表示領域 10Aにおいて、複数の書き込み線 WSL (走査線) が行状に配置され、複数の信号線 DTL が列状に配置されている。表示領域 10A には、さらに、複数の電源線 PSL (電源電圧の供給される部材) が書き込み線 WSL に沿って行状に配置されている。各信号線 DTL と各走査線 WSLとの交差点近傍には、有機EL素子 11 が 1つずつ設けられている。各信号線 DTL は、後述の信号線駆動回路 23 の出力端 (図示せず) と、書き込みトランジスタ  $T_{r_2}$  のドレイン電極およびソース電極のいずれか一方 (図示せず) に接続されている。各走査線 WSL は、後述の書き込み線駆動回路 24 の出力端 (図示せず) と、書き込みトランジスタ  $T_{r_2}$  のゲート電極 (図示せず) に接続されている。各電源線 PSL は、後述の電源線駆動回路 25 の出力端 (図示せず) と、駆動トランジスタ  $T_{r_1}$  のドレイン電極およびソース電極のいずれか一方 (図示せず) に接続されている。書き込みトランジスタ  $T_{r_2}$  のドレイン電極およびソース電極のうち信号線 DTL に非接続の方 (図示せず) は、駆動トランジスタ  $T_{r_1}$  のゲート電極 (図示せず) と、保持容量  $C_s$  の一端に接続されている。駆動トランジスタ  $T_{r_1}$  のドレイン電極およびソース電極のうち電源線 PSL に非接続の方 (図示せず) と保持容量  $C_s$  の他端とが、有機EL素子 11 のアノード電極 (図示せず) に接続されている。有機EL素子 11 のカソード電極 (図示せず) は、例えば、グラウンド線 GND に接続されている。

10

20

#### 【0028】

電源線 PSL は、図 1、図 3 に示したように、複数の画素行を一つのユニット U として、ユニット Uごとに一つずつ設けられている。なお、図 3 には、ユニット U が 5 つ設けられている場合が例示されているが、ユニット数はそれに限られるものではない。また、図 3 では、5 つのユニット U に対して、電源線駆動回路 25 の走査方向に向かうにつれて、1 つずつ増えるサフィックスを付与している。従って、ユニット U 1 は走査方向の初回ユニットに相当し、ユニット U 5 は走査方向の最終ユニットに相当する。

30

#### 【0029】

##### (駆動回路 20)

次に、駆動回路 20 内の各回路について、図 1 を参照して説明する。駆動回路 20 は、タイミング生成回路 21、映像信号処理回路 22、信号線駆動回路 23、書き込み線駆動回路 24、および電源線駆動回路 25 を有している。

40

#### 【0030】

タイミング生成回路 21 は、映像信号処理回路 22、信号線駆動回路 23、書き込み線駆動回路 24、および電源線駆動回路 25 が連動して動作するように制御するものである。タイミング生成回路 21 は、例えば、外部から入力された同期信号 20B に応じて (同期して)、上述した各回路に対して制御信号 21A を出力するようになっている。

50

#### 【0031】

映像信号処理回路 22 は、外部から入力された映像信号 20A に対して所定の補正を行うと共に、補正した後の映像信号 22A を信号線駆動回路 23 に出力するようになっている。所定の補正としては、例えば、ガンマ補正や、オーバードライブ補正などが挙げられる。

50

#### 【0032】

信号線駆動回路 23 は、制御信号 21A の入力に応じて (同期して)、映像信号処理回路 22 から入力された映像信号 22A (信号電圧  $V_{sig}$ ) を各信号線 DTL に印加して、選択対象の画素 13 に書き込むものである。なお、書き込みとは、駆動トランジスタ  $T_{r_1}$  のゲートに所定の電圧を印加することを指している。

50

#### 【0033】

信号線駆動回路 23 は、例えばシフトレジスタ (図示せず) によって構成されており、画素 13 の各列に対応して、1 段ごとに信号出力部 (図示せず) を備えている。この信号線駆動回路 23 は、制御信号 21A の入力に応じて (同期して)、各信号線 DTL に対し

て、2種類の電圧( $V_{ofs}$ 、 $V_{sig}$ )を出力可能となっている。具体的には、信号線駆動回路23は、各画素13に接続された信号線DTLを介して、書込線駆動回路24により選択された画素13へ2種類の電圧( $V_{ofs}$ 、 $V_{sig}$ )を順番に供給するようになっている。

#### 【0034】

ここで、電圧 $V_{ofs}$ は、有機EL素子11の閾値電圧 $V_{el}$ よりも低い電圧値となっている。また、 $V_{sig}$ は、映像信号22Aに対応する電圧値となっている。 $V_{sig}$ の最小電圧は $V_{ofs}$ よりも低い電圧値となっており、 $V_{sig}$ の最大電圧は $V_{ofs}$ よりも高い電圧値となっている。

#### 【0035】

書込線駆動回路24は、例えばシフトレジスタ(図示せず)によって構成されており、

10

画素13の各行に対応して、1段ごとに信号出力部(図示せず)を備えている。この書込線駆動回路24は、制御信号21Aの入力に応じて(同期して)、各書込線WSLに対して、2種類の電圧( $V_{on}$ 、 $V_{off}$ )を出力可能となっている。具体的には、書込線駆動回路24は、各画素13に接続された書込線WSLを介して、駆動対象の画素13へ2種類の電圧( $V_{on}$ 、 $V_{off}$ )を供給し、書き込みトランジスタTr<sub>2</sub>を制御するようになっている。

#### 【0036】

ここで、電圧 $V_{on}$ は、書き込みトランジスタTr<sub>2</sub>のオン電圧以上の値となっている。

V<sub>on</sub>は、後述の消光時や閾値補正時に、書込線駆動回路24から出力される電圧値である。

V<sub>off</sub>は、書き込みトランジスタTr<sub>2</sub>のオン電圧よりも低い値となっており、かつ、V<sub>on</sub>よりも低い値となっている。

#### 【0037】

電源線駆動回路25は、例えばシフトレジスタ(図示せず)によって構成されており、各ユニット(U1～U5)に対応して、各ユニット(U1～U5)に含まれる行数と等しい数の段ごとに信号出力部(図示せず)を備えている。つまり、本実施の形態では、電源線駆動回路25内のシフトレジスタの出力段がユニット(U1～U5)ごとに共用化されており、ユニットスキヤン方式が採られている。そのため、各画素列に対応して1段ごとに信号出力部を設けた場合と比べて、電源線駆動回路25内の信号出力部の数が少ない。

#### 【0038】

この電源線駆動回路25は、制御信号21Aの入力に応じて(同期して)、2種類の電圧( $V_{ss}$ 、 $V_{cc}$ )を出力可能となっている。具体的には、電源線駆動回路25は、各画素13に接続された電源線PSLを介して、駆動対象の画素13へ2種類の電圧( $V_{ss}$ 、 $V_{cc}$ )を供給し、有機EL素子11の発光および消光を制御するようになっている。

#### 【0039】

ここで、 $V_{ss}$ は、有機EL素子11の閾値電圧 $V_{el}$ と、有機EL素子11のカソードの電圧 $V_{ca}$ とを足し合わせた電圧( $V_{el} + V_{ca}$ )よりも低い電圧値である。また、 $V_{cc}$ は、電圧( $V_{el} + V_{ca}$ )以上の電圧値である。

#### 【0040】

次に、本実施の形態の表示装置1の動作(消光から発光までの動作)の一例について説明する。本実施の形態では、駆動トランジスタTr<sub>1</sub>の閾値電圧 $V_{th}$ や移動度 $\mu$ が経時変化したりしても、それらの影響を受けることなく、有機EL素子11の発光輝度を一定に保つようにするために、閾値電圧 $V_{th}$ や移動度 $\mu$ の変動に対する補正動作が組み込まれている。

#### 【0041】

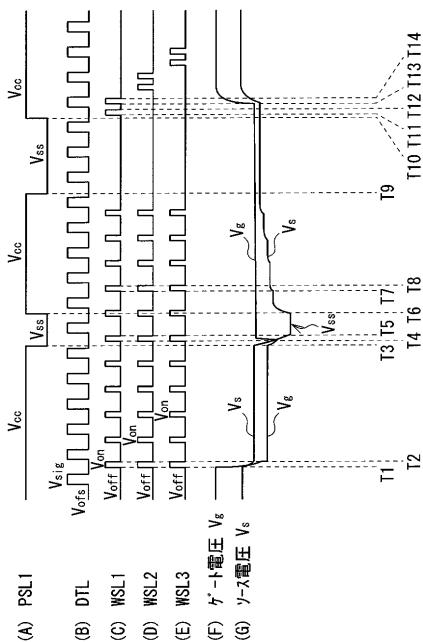

図4は、表示装置1における各種波形の一例を表したものである。図4には、電源線PSLに2種類の電圧( $V_{ss}$ 、 $V_{cc}$ )が、書込線WSL1～WSL6に2種類の電圧( $V_{on}$ 、 $V_{off}$ )が印加されている様子が示されている。図1、図4からわかるように、表示装置1では、電源線PSL(PSL1, PSL2, ...)から各画素13に、ユニット(U1～U5)ごとに共通のタイミングで $V_{ss}$ 、 $V_{cc}$ が印加される。

#### 【0042】

10

20

30

40

50

図5は、表示装置1のユニットU1に印加される電圧波形の一例を表したものである。具体的には、電源線PSL1に2種類の電圧( $V_{ss}$ 、 $V_{cc}$ )が、信号線DTLに2種類の電圧( $V_{sig}$ 、 $V_{ofs}$ )が、書込線WSL1、WSL2、WSL3に2種類の電圧( $V_{on}$ 、 $V_{off}$ )が印加されている様子が示されている。さらに、図5には、電源線PSL1、信号線DTLおよび書込線WSL1への電圧印加に応じて、駆動トランジスタTr1のゲート電圧 $V_g$ およびソース電圧 $V_s$ が時々刻々変化している様子が示されている。

#### 【0043】

##### (消光期間)

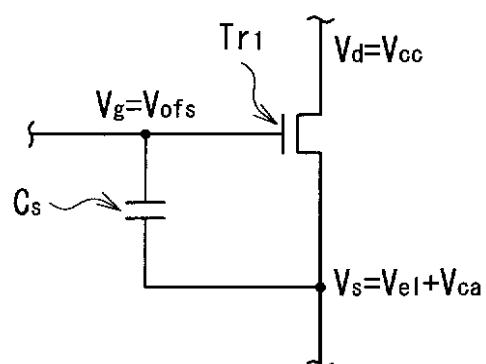

まず、有機EL素子11の消光を行う。具体的には、まず、駆動トランジスタTr1のドレイン電圧 $V_d$ の電圧が $V_{cc}$ となっており、駆動トランジスタTr1のゲート電圧 $V_g$ が $V_{sig}$ よりも高い電圧となっており、かつ駆動トランジスタTr1のソース電圧 $V_s$ が有機EL素子11の駆動電圧 $V_{dr}$ となっており、有機EL素子11が発光しているとする(図6)。このように有機EL素子11が発光している期間において、信号線DTLの電圧が $V_{ofs}$ となつたときに、書込線駆動回路24が書込線WSLの電圧を $V_{off}$ から $V_{on}$ に上げ(T<sub>1</sub>)、駆動トランジスタTr1のゲートを信号線DTLに接続する。すると、駆動トランジスタTr1のゲート電圧 $V_g$ が下がり始め、保持容量 $C_s$ を介したカップリングにより駆動トランジスタTr1のソース電圧 $V_s$ も下がり始める。その後、ゲート電圧 $V_g$ が $V_{ofs}$ となるとともに、ソース電圧 $V_s$ が $V_{el} + V_{ca}$ ( $V_{ca}$ は有機EL素子11のカソード電圧)となり、有機EL素子11が消光する(図7)。その後、有機EL素子11が消光したときに書込線駆動回路24が書込線WSLの電圧を $V_{on}$ から $V_{off}$ に下げ、駆動トランジスタTr1のゲートをフローティングにする(T<sub>2</sub>)。

#### 【0044】

##### (閾値補正準備期間)

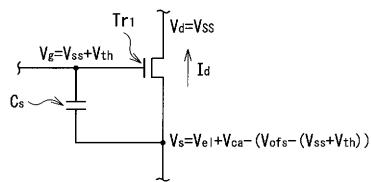

次に、閾値補正の準備を行う。具体的には、書込線WSL1の電圧が $V_{off}$ となっている時に、電源線駆動回路25が電源線PSL1の電圧(駆動トランジスタTr1のドレイン電圧 $V_d$ )を $V_{cc}$ から $V_{ss}$ に下げる(T<sub>3</sub>)(図8)。すると、駆動トランジスタTr1の電源線PSL1側がソースとなって駆動トランジスタTr1のドレイン-ソース間に電流 $I_d$ が流れ、ゲート電圧 $V_g$ が $V_{ss} + V_{th}$ となったところで、電流 $I_d$ が止まる。このとき、ソース電圧 $V_s$ が $V_{el} + V_{ca} - (V_{ofs} - (V_{ss} + V_{th}))$ となっており、電位差 $V_{gs}$ が $V_{th}$ よりも小さくなっている。

#### 【0045】

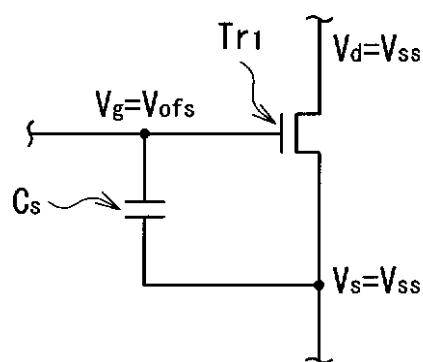

続いて、電源線PSL1の電圧(駆動トランジスタTr1のドレイン電圧 $V_d$ )が $V_{ss}$ となっており、かつ信号線DTLの電圧が $V_{ofs}$ となっている時に、書込線駆動回路24が書込線WSL1の電圧を $V_{off}$ から $V_{on}$ に上げ(T<sub>4</sub>)、駆動トランジスタTr1のゲートを信号線DTLに接続する。すると、駆動トランジスタTr1のゲート電圧 $V_g$ が上がり始め、駆動トランジスタTr1のソース電圧 $V_s$ は逆にさらに下がり始め、ゲート電圧 $V_g$ が $V_{ofs}$ となり、ソース電圧 $V_s$ が $V_{ss}$ となる(図9)。このとき、書込線駆動回路24が書込線WSL1の電圧を $V_{on}$ から $V_{off}$ に下げ、駆動トランジスタTr1のゲートをフローティングにする(T<sub>5</sub>)。

#### 【0046】

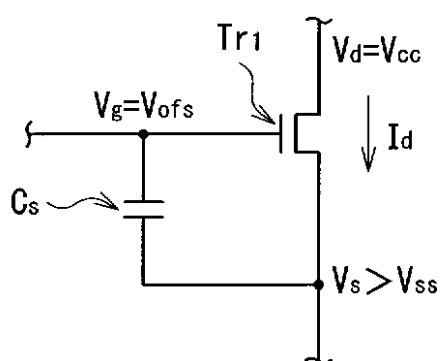

続いて、書込線WSL1の電圧が $V_{on}$ となっており、かつ信号線DTLの電圧が $V_{ofs}$ となっている時に、電源線駆動回路25が電源線PSL1の電圧を $V_{ss}$ から $V_{cc}$ に上げる(T<sub>6</sub>)(図10)。すると、駆動トランジスタTr1のドレイン-ソース間に電流 $I_d$ が流れ、ソース電圧 $V_s$ が、駆動トランジスタTr1のゲート-ドレイン間に寄生容量と、保持容量 $C_s$ との容量結合によって上昇する。

#### 【0047】

##### (最初の閾値補正期間)

次に、閾値補正を行う。具体的には、電源線PSL1の電圧が $V_{cc}$ となっており、かつ信号線DTLの電圧が $V_{ofs}$ となっている時に、書込線駆動回路24が書込線WSL1の電圧を $V_{off}$ から $V_{on}$ に上げて、駆動トランジスタTr1のゲート電圧 $V_g$ を $V_{ofs}$ にする(

10

20

30

40

50

$T_7$ ) (図10)。すると、駆動トランジスタ $T_{r1}$ のドレイン - ソース間に電流 $I_d$ が流れ、ソース電圧 $V_s$ が、駆動トランジスタ $T_{r1}$ のゲート - ドレイン間の寄生容量と、保持容量 $C_s$ との容量結合によって上昇する。その後、書込線駆動回路24が書込線WSLの電圧を $V_{on}$ から $V_{off}$ に下げる( $T_8$ )。すると、駆動トランジスタ $T_{r1}$ のゲートがフローティングとなり、閾値補正が一旦停止する。

#### 【0048】

(最初の閾値補正休止期間)

閾値補正が休止している期間中は、例えば、先の閾値補正を行った行(画素)とは異なる他の行(画素)において、信号線DTLの電圧のサンプリングが行われる。なお、このとき、先の閾値補正を行った行(画素)において、ソース電圧 $V_s$ が $V_{ofs} - V_{th}$ よりも低いので、閾値補正休止期間中にも、先の閾値補正を行った行(画素)において、駆動トランジスタ $T_{r1}$ のドレイン - ソース間に電流 $I_d$ が流れ、ソース電圧 $V_s$ が上昇し、保持容量 $C_s$ を介したカップリングによりゲート電圧 $V_g$ も上昇する。

10

#### 【0049】

(2回目の閾値補正期間)

閾値補正休止期間が終了した後、閾値補正を再び行う。具体的には、信号線DTLの電圧が $V_{ofs}$ となっており、閾値補正が可能となっている時に、書込線駆動回路24が書込線WSLの電圧を $V_{off}$ から $V_{on}$ に上げ、駆動トランジスタ $T_{r1}$ のゲートを $V_{ofs}$ にする( $T_7$ ) (図10)。このとき、ソース電圧 $V_s$ が $V_{ofs} - V_{th}$ よりも低い場合(閾値補正がまだ完了していない場合)には、駆動トランジスタ $T_{r1}$ がカットオフするまで(電位差 $V_{gs}$ が $V_{th}$ になるまで)、駆動トランジスタ $T_{r1}$ のドレイン - ソース間に電流 $I_d$ が流れれる。その後、信号線駆動回路23が信号線DTLの電圧を $V_{ofs}$ から $V_{sig}$ に切り替える前に、書込線駆動回路24が書込線WSLの電圧を $V_{on}$ から $V_{off}$ に下げる( $T_8$ )。すると、駆動トランジスタ $T_{r1}$ のゲートがフローティングとなるので、電位差 $V_{gs}$ を信号線DTLの電圧の大きさに拘わらず一定に維持することができる。

20

#### 【0050】

なお、この閾値補正期間において、保持容量 $C_s$ が $V_{th}$ に充電され、電位差 $V_{gs}$ が $V_{th}$ となった場合には、閾値補正を終了するが、電位差 $V_{gs}$ が $V_{th}$ にまで到達しなかった場合には、電位差 $V_{gs}$ が $V_{th}$ に到達するまで、閾値補正と、閾値補正休止とを繰り返し実行する。

30

#### 【0051】

(休止期間)

次に、必要に応じて、電源線駆動回路25が電源線PSL1の電圧を $V_{cc}$ から $V_{ss}$ に下げたのち( $T_9$ )、しばらくしてから $V_{ss}$ から $V_{cc}$ に上げる( $T_{10}$ )。これにより、駆動トランジスタ $T_{r1}$ のドレイン - ソース間や、有機EL素子11に生じる電流リークを抑える。

30

#### 【0052】

(最後の閾値補正期間)

信号書き込みを行う直前に、閾値補正を再び行う。具体的には、信号線DTLの電圧が $V_{ofs}$ となっており、閾値補正が可能となっている時に、書込線駆動回路24が書込線WSLの電圧を $V_{off}$ から $V_{on}$ に上げ、駆動トランジスタ $T_{r1}$ のゲートを $V_{ofs}$ にする( $T_{11}$ ) (図10)。このとき、ソース電圧 $V_s$ が $V_{ofs} - V_{th}$ よりも低い場合(閾値補正が完了していない場合)には、駆動トランジスタ $T_{r1}$ がカットオフするまで(電位差 $V_{gs}$ が $V_{th}$ になるまで)、駆動トランジスタ $T_{r1}$ のドレイン - ソース間に電流 $I_d$ が流れれる。その後、書込線駆動回路24が書込線WSLの電圧を $V_{on}$ から $V_{off}$ に下げる( $T_{12}$ )。すると、駆動トランジスタ $T_{r1}$ のゲートがフローティングとなるので、電位差 $V_{gs}$ を信号線DTLの電圧の大きさに拘わらず一定に維持することができる。

40

#### 【0053】

(書き込み・ $\mu$ 補正期間)

閾値補正期間が終了した後、書き込みと $\mu$ 補正を行う。具体的には、信号線DTLの電

50

圧が $V_{sig}$ となっている間に、書込線駆動回路24が書込線WSLの電圧を $V_{off}$ から $V_{on}$ に上げ( $T_{13}$ )、駆動トランジスタTr<sub>1</sub>のゲートを信号線DTLに接続する。すると、駆動トランジスタTr<sub>1</sub>のゲートの電圧が $V_{sig}$ となる(図11)。このとき、有機EL素子11のアノードの電圧はこの段階ではまだ有機EL素子11の閾値電圧 $V_{el}$ よりも小さく、有機EL素子11はカットオフしている。そのため、電流 $I_d$ は有機EL素子11の素子容量に流れ、素子容量が充電されるので、ソース電圧 $V_s$ が $V$ だけ上昇し、やがて、ソース電圧 $V_s$ が $V_{ofs} - V_{th} + V$ となり、電位差 $V_{gs}$ が $V_{sig} - (V_{ofs} - V_{th} + V)$ となる。このようにして、書き込みと同時にμ補正が行われる。

## 【0054】

(発光)

10

最後に、書込線駆動回路24が書込線WSLの電圧を $V_{on}$ から $V_{off}$ に下げる( $T_{14}$ )。すると、駆動トランジスタTr<sub>1</sub>のゲートがフローティングとなり、駆動トランジスタTr<sub>1</sub>のドレイン-ソース間に電流 $I_d$ が流れ、ソース電圧 $V_s$ が上昇する。その結果、有機EL素子11が所望の輝度で発光する。

## 【0055】

本実施の形態の表示装置1では、上記のようにして、各画素13において画素回路12がオンオフ制御され、各画素13の有機EL素子11に駆動電流が注入されることにより、正孔と電子とが再結合して発光が起こり、その光が外部に取り出される。その結果、表示パネル10の表示領域10Aにおいて画像が表示される。

## 【0056】

20

ところで、例えば、図18に示したような従来の表示装置100におけるユニットスキャン方式では、例えば、図19に示したように、同一ユニット内において、電源線PSLの電圧が $V_{ss}$ から $V_{cc}$ に上がった時( $T_1$ )から閾値補正を開始する時( $T_2$ )までの時間(待ち時間)がラインによって異なっている。例えば、同一ユニット内に30ライン含まれている場合に、1ライン目の待ち時間と30ライン目の待ち時間との差が29Hとなる。この待ち時間の間、例えば、図20に示したように、駆動トランジスタTr<sub>1</sub>のリーク電流 $I_{Dr}$ と、有機EL素子111のリーク電流 $I_{EL}$ とが生じているので、駆動トランジスタTr<sub>1</sub>のソース電圧 $V_s$ は、待ち時間が長ければ長いほど、上昇してしまう。そのため、同一のユニット内において、最後のラインの画素111のゲート-ソース間電圧(電位差 $V_{gs}$ )は最初のラインの画素111のゲート-ソース間電圧(電位差 $V_{gs}$ )よりも小さくなる。その結果、一のユニットに含まれるライン数が多くなると、時刻 $T_1 \sim T_2$ の間、最後のラインの輝度は最初のラインの輝度よりも暗くなってしまい、隣接するユニット間にスジ状の模様が発生してしまう。

30

## 【0057】

そこで、上記の待ち時間を十分に長くし、各ラインの画素111のゲート-ソース間電圧の差を小さくする方策が考えられる。しかし、そのようにした場合には、発光期間が短くなってしまうという問題があった。

## 【0058】

40

また、閾値補正を行う際には、駆動トランジスタのソース電圧を事前に所定の値よりも下げておくことが必要となるが、図19の例では、駆動トランジスタのソース電圧が $V_{ss} - V_{th}$ までしか下がらない。そのため、 $V_{ss}$ を大きく下げる必要となるが、そのようにした場合には、電源線駆動回路140から印加される選択パルスによるカップリングにより、ユニット間にスジ状の模様が発生してしまう。

## 【0059】

50

一方、本実施の形態の表示装置1では、電源線PSLの電圧を利用して各駆動トランジスタTr<sub>1</sub>のゲート-ソース間電圧 $V_{gs}$ を駆動トランジスタTr<sub>1</sub>の閾値電圧 $V_{th}$ よりも大きくした上で、各駆動トランジスタTr<sub>1</sub>の閾値補正がなされる。従って、電源線PSLの電圧を大きく下げる必要がない。また、各有機EL素子11を発光させる前に再度、必要なラインに対して駆動トランジスタTr<sub>1</sub>の閾値電圧が補正される。これにより、各ラインにおいて、駆動トランジスタTr<sub>1</sub>の閾値補正の待ち時間を短くすることができる。

これにより、ユニットスキャンにおいて、発光期間を短くすることなく、スジ状の模様が発生するのを防止することができる。

【0060】

<モジュールおよび適用例>

以下、上記実施の形態で説明した表示装置1の適用例について説明する。上記実施の形態の表示装置1は、テレビジョン装置、デジタルカメラ、ノート型パソコンコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなど、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。

【0061】

(モジュール)

上記実施の形態の表示装置1は、例えば、図12に示したようなモジュールとして、後述する適用例1～5などの種々の電子機器に組み込まれる。このモジュールは、例えば、基板31の一辺に、表示領域10Aを封止する封止用基板32から露出した領域210を設け、この露出した領域210に、駆動回路20の配線を延長して外部接続端子(図示せず)を形成したものである。外部接続端子には、信号の入出力のためのフレキシブルプリント配線基板(FPC;Flexible Printed Circuit)220が設けられていてもよい。

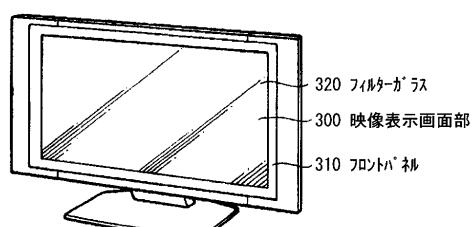

【0062】

(適用例1)

図13は、上記実施の形態の表示装置1が適用されるテレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300は、上記実施の形態に係る表示装置1により構成されている。

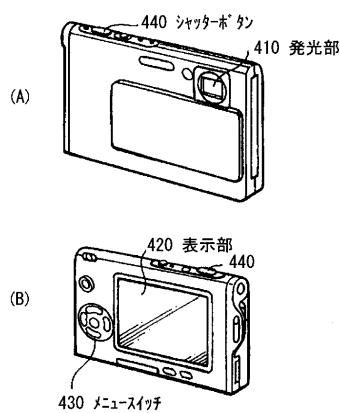

【0063】

(適用例2)

図14は、上記実施の形態の表示装置1が適用されるデジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、ニュースイッチ430およびシャッターボタン440を有しており、その表示部420は、上記実施の形態に係る表示装置1により構成されている。

【0064】

(適用例3)

図15は、上記実施の形態の表示装置1が適用されるノート型パソコンコンピュータの外観を表したものである。このノート型パソコンコンピュータは、例えば、本体510、文字等の入力操作のためのキーボード520および画像を表示する表示部530を有しており、その表示部530は、上記実施の形態に係る表示装置1により構成されている。

【0065】

(適用例4)

図16は、上記実施の形態の表示装置1が適用されるビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部610、この本体部610の前方側面に設けられた被写体撮影用のレンズ620、撮影時のスタート/ストップスイッチ630および表示部640を有しており、その表示部640は、上記実施の形態に係る表示装置1により構成されている。

【0066】

(適用例5)

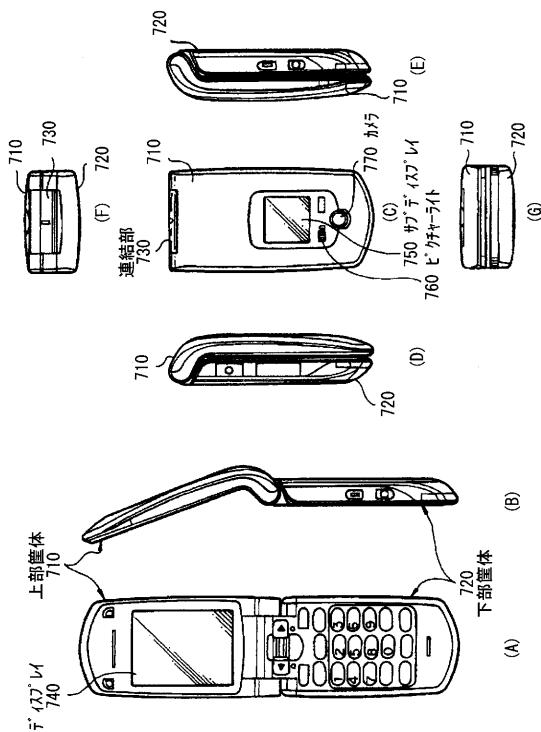

図17は、上記実施の形態の表示装置1が適用される携帯電話機の外観を表したものである。この携帯電話機は、例えば、上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740、サブディスプレイ750、ピクチャーライト760およびカメラ770を有している。そのディスプレイ740またはサブディスプレイ750は、上記実施の形態に係る表示装置1により構成されている。

## 【0067】

以上、実施の形態および適用例を挙げて本発明を説明したが、本発明は上記実施の形態等に限定されるものではなく、種々変形が可能である。

## 【0068】

例えば、上記実施の形態等では、表示装置1がアクティブマトリクス型である場合について説明したが、アクティブマトリクス駆動のための画素回路12の構成は上記実施の形態等で説明したものに限られず、必要に応じて容量素子やトランジスタを画素回路12に追加してもよい。その場合、画素回路12の変更に応じて、上述した信号線駆動回路23、書込線駆動回路24、電源線駆動回路25のほかに、必要な駆動回路を追加してもよい。

10

## 【0069】

また、上記実施の形態等では、信号線駆動回路23、書込線駆動回路24、電源線駆動回路25の駆動をタイミング生成回路21が制御していたが、他の回路がこれらの駆動を制御するようにしてもよい。また、信号線駆動回路23、書込線駆動回路24、電源線駆動回路25の制御は、ハードウェア（回路）で行われていてもよいし、ソフトウェア（プログラム）で行われていてもよい。

## 【0070】

また、上記実施の形態等では、画素回路12が、2Tr1Cの回路構成となっていたが、デュアルゲート型のトランジスタが有機EL素子11に直列に接続された回路構成を含んでいるものであれば、2Tr1Cの回路構成以外の回路構成となっていてもよい。

20

## 【0071】

また、上記実施の形態等では、駆動トランジスタTr<sub>1</sub>、書き込みトランジスタTr<sub>2</sub>は、nチャネルMOS型の薄膜トランジスタにより形成されている場合が例示されていたが、pチャネルトランジスタ（例えばpチャネルMOS型のTFT）により形成されていてもよい。ただし、その場合には、トランジスタTr<sub>2</sub>のソースおよびドレインのうち電源線PSLと未接続の方と保持容量C<sub>s</sub>の他端とを有機EL素子11のカソードに接続し、有機EL素子11のアノードをGNDなどに接続することが好ましい。

## 【符号の説明】

## 【0072】

1, 100...表示装置、10, 110...表示パネル、10A...表示領域、11, 11R, 11G, 11B, 111R, 111G, 111B...有機EL素子、12...画素回路、13, 13R, 13G, 13B, 111...画素、14...表示画素、20...駆動回路、20A, 22A...映像信号、20B...同期信号、21...タイミング生成回路、21A...制御信号、22...映像信号処理回路、23, 120...信号線駆動回路、24, 130...書込線駆動回路、25, 140...電源線駆動回路、31...基板、32...封止用基板、210...領域、220...FPC、300...映像表示画面部、310...フロントパネル、320...フィルターガラス、410...発光部、420, 530, 640...表示部、430...メニュースイッチ、440...シャッターボタン、510...本体、520...キーボード、610...本体部、620...レンズ、630...スタート/ストップスイッチ、710...上側筐体、720...下側筐体、730...連結部、740...ディスプレイ、750...サブディスプレイ、760...ピクチャーライト、770...カメラ、C<sub>s</sub>...保持容量、DTL(DTL1, DTL2, ...)...信号線、I<sub>d</sub>...電流、I<sub>Dr</sub>, I<sub>EL</sub>...リーク電流、GND...グラウンド線、PSL(PSL1, PSL2, ...)...電源線、Tr<sub>1</sub>...駆動トランジスタ、Tr<sub>2</sub>...書き込みトランジスタ、V<sub>g</sub>...ゲート電圧、V<sub>gs</sub>...電位差、V<sub>s</sub>...ソース電圧、V<sub>sig</sub>...信号電圧、V<sub>cc</sub>, V<sub>off</sub>, V<sub>ofs</sub>, V<sub>on</sub>, V<sub>ss</sub>, V...電圧、V<sub>th</sub>, V<sub>e1</sub>...閾値電圧、WSL(WSL1, WSL2, ...)...書込線、X...ユニット数、μ...移動度。

30

40

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 12】

【図 11】

【図 13】

【図14】

【図16】

【図15】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 G 3/20 6 2 3 X

H 0 5 B 33/14 A

テーマコード(参考)

(72)発明者 内野 勝秀

東京都港区港南1丁目7番1号 ソニー株式会社内

F ターム(参考) 3K107 AA01 BB01 CC33 EE03 HH02 HH04 HH05

5C080 AA06 BB05 CC03 DD05 JJ02 JJ03 JJ04 KK02 KK43 KK47

5C380 AA01 AB06 AB34 AB46 AC07 AC08 AC09 AC11 BA21 BA38

BA39 BB02 BD02 CA08 CA12 CA17 CB01 CB09 CB14 CB20

CB26 CC02 CC03 CC04 CC05 CC07 CC27 CC33 CC41 CC62

CD012 CE19 CF07 DA06 DA47 HA05 HA11

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置，其驱动方法和电子设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2011145532A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2011-07-28 |

| 申请号            | JP2010006991                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2010-01-15 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 三並徹雄<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 三並徹雄<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.642.A G09G3/20.611.H G09G3/20.612.G G09G3/20.623.X H05B33/14.A G09G3/3225 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH02 3K107/HH04 3K107/HH05 5C080 /AA06 5C080/BB05 5C080/CC03 5C080/DD05 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/KK02 5C080/KK43 5C080/KK47 5C380/AA01 5C380/AB06 5C380/AB34 5C380/AB46 5C380/AC07 5C380 /AC08 5C380/AC09 5C380/AC11 5C380/BA21 5C380/BA38 5C380/BA39 5C380/BB02 5C380/BD02 5C380/CA08 5C380/CA12 5C380/CA17 5C380/CB01 5C380/CB09 5C380/CB14 5C380/CB20 5C380 /CB26 5C380/CC02 5C380/CC03 5C380/CC04 5C380/CC05 5C380/CC07 5C380/CC27 5C380/CC33 5C380/CC41 5C380/CC62 5C380/CD012 5C380/CE19 5C380/CF07 5C380/DA06 5C380/DA47 5C380 /HA05 5C380/HA11 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

### 摘要(译)

要解决的问题：提供一种能够在不减少发光时段的情况下防止在单位扫描中产生条纹图案的显示装置，并提供一种用于驱动显示装置和电子设备的方法。解决方案：在每个单元U中提供电源线PSL，其包括多个像素行作为一个单元U。在设置每个驱动晶体管Tr的栅极-源极电压V<sub>gs</sub>之后通过使用电源线PSL的电压，每个驱动的阈值，1高于驱动晶体管Tr 1的阈值电压V<sub>th</sub>晶体管Tr 1被校正。然后，在每个有机EL元件11中发光之前，再次相对于必要的线校正驱动晶体管Tr 1的阈值电压。