(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-301290

(P2005-301290A)

(43) 公開日 平成17年10月27日(2005.10.27)

(51) Int.Cl. 7

G09G 3/30

G09G 3/20

H05B 33/14

F 1

G09G 3/30

J

テーマコード(参考)

3K007

G09G 3/20

611A

5C080

G09G 3/20

611H

G09G 3/20

621F

G09G 3/20

624B

審査請求 有 請求項の数 16 O L (全 23 頁) 最終頁に続く

(21) 出願番号

特願2005-126001(P2005-126001)

(22) 出願日

平成17年4月25日(2005.4.25)

(62) 分割の表示

特願2005-57115(P2005-57115)

の分割

原出願日 平成17年3月2日(2005.3.2)

(31) 優先権主張番号

0404919.3

(32) 優先日

平成16年3月4日(2004.3.4)

(33) 優先権主張国

英国(GB)

(71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107076

弁理士 藤岡 英吉

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 サイモン タム

イギリス ケンブリッジ CB4 0FE

9a ケンブリッジ サイエンスパーク

ミルトンロード エプソンケンブリッジ

研究所内

最終頁に続く

(54) 【発明の名称】画素回路、画素回路の駆動方法及びアクティブマトリクス装置

## (57) 【要約】

【課題】 電流駆動有機発光装置などの発光装置を駆動する画素回路において、駆動トランジスタの閾値電圧のバラツキを補正することが知られている。しかし、このような画素回路のプログラム化および初期化には時間がかかり、複数の制御線または信号線が必要となる。

【解決手段】 本発明は、前記駆動トランジスタをダイオード接続するn型トランジスタと、信号線および制御線の数を削減する手段とを有する画素回路を提供する。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

電流駆動素子を駆動する画素回路であって、

導電状態が前記電流駆動素子に供給される駆動電流の電流レベルに対応する第1のトランジスタと、ここで前記第1のトランジスタは、第1のゲート端子と、第1の端子と、第2の端子とを備え、

第2のゲート端子を備える第2のトランジスタと、

前記第1のゲート端子ならびに前記第1の端子および前記第2の端子の一方の間の電気接続を制御するよう配置された第3のトランジスタと、ここで前記第3のトランジスタは第3のゲート端子を備え、を含み、

前記第1の端子は、前記第2のトランジスタを介してデータ信号を受け取るよう配列され、ここで前記データ信号は前記第1のトランジスタの前記導電状態を決定するものあり、

前記第1のトランジスタの導電型は、前記第2のトランジスタの導電型とは異なるものである画素回路。

**【請求項 2】**

電流駆動素子を駆動する画素回路であって、

導電状態が前記電流駆動素子に供給される駆動電流の電流レベルに対応する第1のトランジスタと、ここで前記第1のトランジスタは、第1のゲート端子と、第1の端子と、第2の端子とを備え、

第2のゲート端子を備える第2のトランジスタと、

前記第1のゲート端子ならびに前記第1の端子および前記第2の端子の一方の間の電気接続を制御するよう配置された第3のトランジスタと、ここで前記第3のトランジスタは第3のゲート端子を備え、を含み、

前記第1の端子は、前記第2のトランジスタを介してデータ信号を受け取るよう配列され、ここで前記データ信号は前記第1のトランジスタの前記導電状態を決定するものあり、

前記第1のトランジスタの導電型は、前記第3のトランジスタの導電型とは異なるものである画素回路。

**【請求項 3】**

請求項1または2に記載の画素回路において、

前記電流駆動素子および前記第1のトランジスタの間に直列に接続され、第4のゲート端子を備える第4のトランジスタをさらに含む画素回路。

**【請求項 4】**

請求項3に記載の画素回路において、

前記第4のトランジスタの導電型は、前記第2のトランジスタの導電型とは異なるものである画素回路。

**【請求項 5】**

請求項3または4に記載の画素回路において、

前記第1のトランジスタおよび前記駆動電流が前記第1のトランジスタを介して前記電流駆動素子に供給される電源線の間に直列に接続され、第5のゲート端子を備える第5のトランジスタをさらに含む画素回路。

**【請求項 6】**

請求項5に記載の画素回路において、

前記第4のトランジスタの導電型は、前記第5のトランジスタの導電型と同じである画素回路。

**【請求項 7】**

請求項1または2に記載の画素回路において、前記第1のトランジスタの導電型はp型である画素回路。

**【請求項 8】**

10

20

30

40

50

請求項 3 に記載の画素回路において、

前記第 4 のゲート端子、前記第 2 のゲート端子、および前記第 3 のゲート端子は、一つの信号線に接続される画素回路。

**【請求項 9】**

請求項 5 に記載の画素回路において、

前記第 5 のゲート端子、前記第 2 のゲート端子、および前記第 3 のゲート端子は、一つの信号線に接続される画素回路。

**【請求項 10】**

請求項 5 に記載の画素回路において、

前記第 4 のトランジスタおよび前記電流駆動素子の間に直列に接続された第 6 のトランジスタをさらに含む画素回路。 10

**【請求項 11】**

請求項 1 から 10 のいずれかに記載の画素回路において、前記第 1 のゲートが容量素子を介して電源供給線に接続された画素回路。

**【請求項 12】**

請求項 11 に記載の画素回路において、前記第 1 のゲートおよび前記容量素子の間に接続された第 7 のトランジスタをさらに含む画素回路。

**【請求項 13】**

請求項 12 に記載の画素回路において、前記電源線および前記第 1 のゲートの間に直接接続された第 8 のトランジスタをさらに含む画素回路。 20

**【請求項 14】**

請求項 12 に記載の画素回路において、前記容量素子および前記第 2 の端子の間に接続された第 9 のトランジスタをさらに含む画素回路。

**【請求項 15】**

第 1 のゲート端子と第 1 の端子と第 2 の端子とを備える第 1 のトランジスタと、第 2 のゲート端子を備える第 2 のトランジスタと、第 3 のゲート端子を備え前記第 1 のゲート端子および前記第 2 の端子の間の電気接続を制御する第 3 のトランジスタと、第 4 のゲート端子を備え、電流駆動素子および前記第 1 のトランジスタの間の電気接続を制御する第 4 のトランジスタと、第 5 のゲート端子を備え、前記第 2 の端子および所定の電圧の間の電気接続を制御する第 5 のトランジスタとを含む、画素回路を駆動する方法であり、 30

前記第 5 のトランジスタをオン状態にすることにより前記第 2 の端子が所定の電圧に設定される、前記画素回路の第 1 の状態を生成し、

前記第 1 の端子が前記第 2 のトランジスタを介してデータ信号を受け取る第 1 の期間の少なくとも一部において、前記第 1 のゲート端子が前記第 3 のトランジスタを介して前記第 2 の端子に電気的に接続される、前記画素回路の第 2 の状態を生成し、

電流レベルが前記第 2 の状態において設定される導電状態に対応する駆動電流が、前記第 1 のトランジスタ及び前記第 4 のトランジスタを介して電流駆動素子に供給される、前記画素回路の第 3 の状態を生成することを含み、

前記第 2 の端子は、前記第 2 の状態において、前記所定の電圧から電気的に分離され、前記第 1 の端子は、前記第 2 の状態において、前記電流駆動素子から電気的に分離され、 40

一つの制御信号が、前記第 2 のゲート端子、前記第 3 のゲート端子、前記第 4 のゲート端子、および前記第 5 のゲート端子に共通に供給されること、

を特徴とする画素回路の駆動方法。

**【請求項 16】**

請求項 1 乃至 15 のいずれかに記載の画素回路、あるいは請求項 15 に記載の画素回路の駆動方法によって駆動されるアクティブマトリクス装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、画素回路、画素回路の駆動方法、アクティブマトリクス装置に関する。

【背景技術】

【0002】

表示システムは一般的に、光源としての有機発光装置（OLED）を備える画素回路の配列、および前記OLEDを受け取ったデータ信号に応じて駆動する駆動回路を含む。前記OLEDは、陽極層および陰極層に挟まれた発光高分子（LEP）層等からなる。前記OLEDは、電気的にはダイオードとして機能し、光学的には順方向バイアスされているときに発光し、その発光の明るさは順方向バイアス電流の増加に従い強まる。前記配列における個々の画素回路の前記駆動回路を低温ポリシリコン薄膜トランジスタ（TFT）技術によって一体化することにより、個々のOLEDの明るさを制御し、画面上に静止画または動画を表示させることができる。10

【0003】

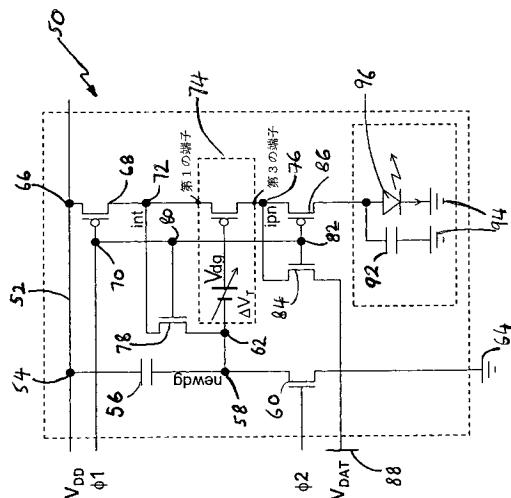

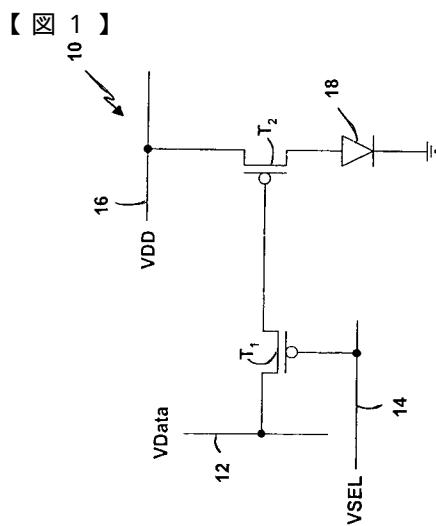

OLEDは電流駆動素子であるため、前記画素回路が電気信号を受け取ると、その受け取った電気信号に応じて駆動トランジスタなどが適量の電流を前記OLEDに供給する。図1は、アクティブ・マトリクスOLED表示装置に適用される公知の電圧駆動画素回路の例である。図1に示すように、画素回路10は、第1のp型TFT T<sub>1</sub>および第2のp型TFT T<sub>2</sub>を含む。前記第1のTFT T<sub>1</sub>は、前記画素回路10をアドレス指定するスイッチであり、電圧データ信号VDataを受け取る第1の供給線12に接続された端子を含む。前記第1のTFT T<sub>1</sub>は、また、供給電圧VSELを受け取る第2の供給線14に接続されたゲート端子と、前記第2のTFT T<sub>2</sub>のゲート端子に接続された端子とを含む。前記第2のTFT T<sub>2</sub>は、供給電圧VDDを受け取る第3の供給線16に接続された端子と、OELD18の陽極端子に接続された端子とを含む。前記OELD18の陰極端子は接地される。前記第2のTFT T<sub>2</sub>は、前記電圧データ信号VDataを電流信号に変換するアナログ駆動TFTであり、この信号により前記OELD18を指定された明るさに駆動する。20

【0004】

図1に例示する電圧駆動画素回路の配列を使用した表示システムでは、前記配列における個々の駆動TFTに同一の電圧データ信号および供給電圧を供給しても、表示された画像に不均一性が生じる可能性がある。この不均一性は、表示を形成する画素回路の配列内における、個々の駆動TFTの閾値電圧の空間的バラツキに起因する。よって各OLEDは、前記駆動TFT間の閾値電圧の差異に対応した異なる輝度となる。この不均一性の問題を解決するための一つの方法として、非特許文献1に開示されている。Choiほかの開示する画素回路の実施形態を図2に示す。30

【非特許文献1】S. M. Choiほか著「A self-compensated voltage programming pixel structure for active-matrix organic light emitting diodes」(International Display Workshop 2003年、535～538頁)

【0005】

図2に示すように、個々の駆動TFTの閾値電圧のバラツキを補正する画素回路20は、6つのTFT M1、M2、M3、M4、M5、M6と、容量素子C1と、2つの水平制御線である走査[n-1]、走査[n]とを含む。M2、M3、M4、M5、M6は、切替えTFTである。一方M1は、電流を供給するアナログ駆動TFTであり、この電流により1フレーム期間中、OELD22を指定された明るさに駆動する。40

【0006】

作動中は、前記第4のTFT M4は電流路を形成し、前記駆動TFT M1のゲート端子電圧を所定の値で成立させる。前記容量素子C1は蓄積容量素子であり、前記駆動TFT M1のゲート端子電圧を蓄える。前記画素回路20は、データのプログラム化を完了させるために2列の線にかかる時間が必要となるため、走査[n]（現在の列走査）および走査[n-1]（前回の列走査）信号を印加して前記画素回路20をプログラム化す50

る。

【0007】

前回の列走査の間、前記走査 [n - 1] 信号が論理 L (ローレベル) である場合、前記駆動 TFT M1 のゲート端子電圧は、初期化と呼ばれるステップにおいて印加されて電圧 V1 になる。これに続く現在の列走査の間、前記走査 [n] 信号がローレベルである場合、TFT M2 および M3 がオン状態になり、この結果電圧データ信号データ [m] は、ダイオード接続された駆動 TFT M1 を介して前記駆動 TFT M1 のゲート・ノードへプログラムされる。このとき、前記駆動 TFT M1 のゲート・ノードにプログラムされた電圧は、前記駆動 TFT M1 の閾値電圧 VTH より小さいデータ信号電圧データ [m] へと自動的に減少する。初期化およびプログラム化の間、TFT M5 および M6 はオフ状態になる。10

【0008】

前回および現在の列走査に引き続き、em [n] 信号により TFT M5 および M6 がオン状態になることにより VDD からアースへの電流路が形成され、この結果前記駆動 TFT M1 を介して電流が流れ、前記 OLE D 2 2 を駆動する。したがって前記駆動 TFT M1 は、前記閾値電圧 VTH とは関係なく前記電流を抑制する。

【発明の開示】

【発明が解決しようとする課題】

【0009】

前記画素回路 20 は、個々の駆動 TFT の電圧閾値変動を補正する手段を実現するが、20 画素回路がプログラム化される速度を高める必要がある。これは、高帯域データが供給された場合や大型表示装置に適用された場合にも、表示システムが適切に動作するために必要である。さらに、電源の寿命を延ばし、前記システムの機能性を高めるため、より低い電力消費を特徴とする小型表示装置も必要となる。

【課題を解決するための手段】

【0010】

本発明の第 1 の態様に係る画素回路は、

電源線および基準線の間に直列に接続された第 1 のトランジスタおよび容量素子と、ここで前記第 1 のトランジスタのゲート端子は第 1 の制御信号を受け取るよう配置され、30 前記電源線およびもう一つの線の間に直列に接続された駆動トランジスタおよび発光装置と、ここで前記駆動トランジスタは、前記第 1 のトランジスタおよび前記容量素子の間の第 1 のノードに接続されたゲート端子と、データ信号を受け取る第 1 の端子とを備え、

第 2 のトランジスタと、ここで前記第 2 のトランジスタは、前記第 2 のトランジスタのゲート端子において受け取られた第 2 の制御信号に応じて前記駆動トランジスタをダイオード接続するよう配列され、これにより前記データ信号は、ダイオード接続され前記第 1 のノードに保持された場合に前記駆動トランジスタを介して渡され、前記第 2 のトランジスタは n 型トランジスタである、を含む画素回路である。

【0011】

好ましくは、前記電源線および前記駆動トランジスタの間に第 3 のトランジスタが直列に接続され、前記発光装置および前記駆動トランジスタの間に第 4 のトランジスタが直列に接続され、ここで前記駆動トランジスタおよび前記第 3 のトランジスタの間の第 2 のノードにおいて、前記第 2 のトランジスタの一つの端子が、前記駆動トランジスタの第 2 の端子に接続される。40

好ましくは、前記第 3 および第 4 のトランジスタは p 型トランジスタであり、これらのゲート端子は前記第 2 の制御信号を受け取るよう配列される。より好ましくは、データ信号線ならびに前記駆動トランジスタおよび前記第 4 のトランジスタの間の第 3 のノードの間に、第 5 のトランジスタが接続される。前記第 5 のトランジスタは n 型トランジスタでもよく、前記第 2 の制御信号を受け取るゲート端子を含んでもよい。

【0012】

好ましくは、前記第 5 のトランジスタおよび前記発光装置の間に第 6 のトランジスタが50

直列に接続され、ここで前記第6のトランジスタは、前記第1のトランジスタとは逆の型であり、前記第1の制御信号を受け取るゲート端子を備える。

【0013】

好ましくは、前記駆動トランジスタの前記ゲート端子および前記第1のノードの間に第7のトランジスタが直列に接続され、前記電源線ならびに前記第7のトランジスタの一つの端子および前記駆動トランジスタの前記ゲート端子の間の第4のノードの間に、第8のトランジスタが接続され、ここで前記第8のトランジスタは前記第1のトランジスタと同じ型であり、前記第7のトランジスタは前記第1のトランジスタとは逆の型であり、前記第7および第8のトランジスタのゲート端子は前記第1の制御信号を受け取るよう配置される。

10

【0014】

前記画素回路はさらに、前記第1のノード、および前記駆動トランジスタの前記ゲート端子に接続された前記第2のトランジスタの前記端子の間に接続された第9のトランジスタと、前記第1のノード、および前記駆動トランジスタの第2の端子に接続された前記第2のトランジスタのもう一方の端子の間に接続された第10のトランジスタとを含んでもよく、ここで前記第9のトランジスタはp型トランジスタであり、前記第10のトランジスタはn型トランジスタであり、前記第9および第10のトランジスタのゲート端子は、それぞれ前記第1および第2の制御信号を受け取るよう配置される。

【0015】

本発明の別の態様に係る画素回路は、電流駆動素子を駆動する画素回路であって、導電状態が前記電流駆動素子に供給される駆動電流の電流レベルに対応する第1のトランジスタと、ここで前記第1のトランジスタは、第1のゲート端子と、第1の端子と、第2の端子とを備え、

20

第2のゲート端子を備える第2のトランジスタと、

前記第1のゲート端子ならびに前記第1の端子および前記第2の端子の一方の間の電気接続を制御するよう配置された第3のトランジスタと、ここで前記第3のトランジスタは第3のゲート端子を備え、を含む画素回路であり、

前記第1の端子は、前記第2のトランジスタを介してデータ信号を受け取るよう配列され、ここで前記データ信号は前記第1のトランジスタの前記導電状態を決定するものであり、

30

前記第1のトランジスタの導電型は、前記第2のトランジスタの導電型とは異なるものである。

【0016】

本発明の別の態様に係る画素回路は、電流駆動素子を駆動する画素回路であって、導電状態が前記電流駆動素子に供給される駆動電流の電流レベルに対応する第1のトランジスタと、ここで前記第1のトランジスタは、第1のゲート端子と、第1の端子と、第2の端子とを備え、

40

第2のゲート端子を備える第2のトランジスタと、

前記第1のゲート端子ならびに前記第1の端子および前記第2の端子の一方の間の電気接続を制御するよう配置された第3のトランジスタと、ここで前記第3のトランジスタは第3のゲート端子を備え、を含む画素回路であり、

前記第1の端子は、前記第2のトランジスタを介してデータ信号を受け取るよう配列され、ここで前記データ信号は前記第1のトランジスタの前記導電状態を決定するものであり、

前記第1のトランジスタの導電型は、前記第3のトランジスタの導電型とは異なるものである。

【0017】

好ましくは、前記電流駆動素子および前記第1のトランジスタの間に第4のゲート端子を備える第4のトランジスタが直列に接続される。より好ましくは、前記第4のトランジスタの導電型は、前記第2のトランジスタの導電型とは異なるものである。

50

## 【0018】

好ましくは、前記第1のトランジスタおよび電源線の間に第5のゲート端子を備える第5のトランジスタが直列に接続される。前記電源線からは、前記駆動電流が、前記第1のトランジスタを介して前記電流駆動素子に供給される。

## 【0019】

前記第4のトランジスタの導電型は、前記第5のトランジスタの導電型と同じでもよい。前記第1のトランジスタの導電型は、p型でもよい。好ましくは、前記第4のゲート端子、前記第2のゲート端子、および前記第3のゲート端子は、一つの信号線に接続される。好ましくは、前記第5のゲート端子、前記第2のゲート端子、および前記第3のゲート端子は、一つの信号線に接続される。好ましくは、前記第4のトランジスタおよび前記電流駆動素子の間に第6のトランジスタが直列に接続される。

10

## 【0020】

好ましくは、前記第1のゲートが容量素子を介して電源供給線に接続される。より好ましくは、前記第1のゲートおよび前記第1の容量素子の間に第7のトランジスタが接続される。

## 【0021】

好ましくは、前記電源供給線および前記第1のゲートの間に第8のトランジスタが直接接続される。

## 【0022】

好ましくは、前記容量素子および前記第2の端子の間に第9のトランジスタが接続される。

20

## 【0023】

本発明の別の態様に係る表示装置は、複数の前述した画素回路を含む表示装置である。好ましくは、前記表示装置は少なくとも、マトリクス状の第1の信号線と、第2の信号線と、第3の信号線と、データ信号線とからなり、前記第1の制御信号線は第1の画素回路に第1の制御信号を供給し、前記第2の制御信号線は前記第1の画素回路に第2の制御信号を供給し、ここで第2の画素回路への第1の制御信号は前記第2の制御線によって供給される前記第1の画素回路への前記第2の制御信号であり、前記第3の制御線は前記第2の画素回路に第2の制御信号を供給する。

30

## 【0024】

本発明の別の態様に係る画素回路の駆動方法は、

第1の制御信号を印加することにより、電源線および基準線の間に接続され、第1の容量素子に直列に接続された第1のトランジスタをオンにし、

第2の制御信号を印加することにより、第2のトランジスタをオンにし駆動トランジスタをダイオード接続し、ここで前記第2のトランジスタはn型トランジスタであり、前記駆動トランジスタは前記電源供給線およびもう一つの線の間の発光装置に直列に接続され、前記駆動トランジスタのゲート端子は前記第1のトランジスタおよび前記第1の容量素子の間の第1のノードに接続され、前記駆動トランジスタの第1の端子はデータ信号を受け取るよう配置され、

40

前記第1の制御信号を印加することにより、前記第1のトランジスタをオフにし、

前記データ信号を前記駆動トランジスタの前記第1の端子に印加し、

前記第2の制御信号を印加することにより、前記第2のトランジスタをオフにすることを含む、画素回路の駆動方法である。

## 【0025】

好ましくは、前記方法はさらに、前記第2の制御信号を、前記電源線および前記駆動トランジスタの間に直列に接続された第3のトランジスタに印加し、前記発光装置および前記駆動トランジスタの間に直列に接続された第4のトランジスタに印加することにより、前記第2のトランジスタをオンにする間は前記第3および第4のトランジスタをオフにし、前記第2のトランジスタをオフにする間は前記第3および第4のトランジスタをオンにすることを含み、ここで前記駆動トランジスタおよび前記第3のトランジスタの間の第2

50

のノードにおいて、前記第2のトランジスタの一つの端子が前記駆動トランジスタの一つの端子に接続される。

【0026】

好ましくは、前記第3および第4のトランジスタはp型トランジスタである。好ましくは、前記方法はさらに、前記第2の制御信号を、データ信号線ならびに前記駆動トランジスタおよび前記第4のトランジスタの間の第3のノードの間に接続された、第5のトランジスタに印加することにより、前記第2のトランジスタをオンにする間は前記第5のトランジスタをオンにし、前記第2のトランジスタをオフにする間は前記第5のトランジスタをオフにすることを含む。

【0027】

好ましくは、前記方法はさらに、前記第1の制御信号を、前記第4のトランジスタおよび前記発光装置の間に直列に接続された、第6のトランジスタに印加することにより、前記第1のトランジスタをオンにする間は前記第6のトランジスタをオフにすることを含み、ここで前記第6のトランジスタは前記第1のトランジスタとは逆の型である。

【0028】

好ましくは、前記方法はさらに、前記第1の制御信号を、前記駆動トランジスタの前記ゲート端子および前記第1のノードの間に直列に接続された、第7のトランジスタに印加し、前記電源供給線ならびに前記第7のトランジスタの一つの端子および前記駆動トランジスタの前記ゲート端子の間の第4のノードの間に接続された、第8のトランジスタに印加することにより、前記第1のトランジスタをオンにする間は前記第7のトランジスタをオフにし前記第8のトランジスタをオンにすることを含み、ここで前記第8のトランジスタは前記第1のトランジスタと同じ型であり、前記第7のトランジスタは前記第1のトランジスタとは逆の型である。

【0029】

好ましくは、前記方法はさらに、前記第1の制御信号を、前記第1のノードおよび前記駆動トランジスタの前記ゲート端子に接続された前記第2のトランジスタの前記端子の間に接続された、第9のトランジスタに印加し、前記第2の制御信号を、前記第1のノードおよび前記駆動トランジスタの第2の端子に接続された前記第2のトランジスタのもう一方の端子との間に接続された、第10のトランジスタに印加することにより、前記第1のトランジスタをオンにする間は前記第9のトランジスタをオフにし、前記第2のトランジスタをオンにする間は前記第10のトランジスタをオンにすることを含み、ここで前記第9のトランジスタはp型トランジスタであり、前記第10のトランジスタはn型トランジスタである。

【0030】

前記基準線はデータ信号線であってもよく、または、前記第1のトランジスタは前記第5のトランジスタおよび前記容量素子の間に直列に接続され、前記データ信号線は前記基準線であり、前記方法はさらに、

前記第1の制御信号を印加することにより前記第1のトランジスタをオンにした後に、また前記第1の制御信号を印加することにより前記第1のトランジスタをオフにする前に、前記データ信号線にプリチャージ信号を印加することを含み、ここで前記プリチャージ信号は前記データ信号より低い値を有する。

【0031】

本発明の別の態様に係る画素回路の駆動方法は、第1のゲート端子と第1の端子と第2の端子とを備える第1のトランジスタと、第2のゲート端子を備える第2のトランジスタと、第3のゲート端子を備え前記第1のゲート端子および前記第2の端子の間の電気接続を制御する第3のトランジスタと、第4のゲート端子を備え、電流駆動素子および前記第1のトランジスタの間の電気接続を制御する第4のトランジスタと、第5のゲート端子を備え、前記第2の端子および所定の電圧の間の電気接続を制御する第5のトランジスタとを含む、画素回路を駆動する方法であり、前記第5のトランジスタをオン状態にすることにより前記第2の端子が所定の電圧に設定される、前記画素回路の第1の状態を生成し、

前記第1の端子が前記第2のトランジスタを介してデータ信号を受け取る第1の期間の少なくとも一部において、前記第1のゲート端子が前記第3のトランジスタを介して前記第2の端子に電気的に接続される、前記画素回路の第2の状態を生成し、電流レベルが前記第2の状態において設定される導電状態に対応する駆動電流が、前記第1のトランジスタ及び前記第4のトランジスタを介して電流駆動素子に供給される、前記画素回路の第3の状態を生成することを含み、前記第2の端子は、前記第2の状態において、前記所定の電圧から電気的に分離され、前記第1の端子は、前記第2の状態において、前記電流駆動素子から電気的に分離され、一つの制御信号が、前記第2のゲート端子、前記第3のゲート端子、前記第4のゲート端子、および前記第5のゲート端子に共通に供給されることを特徴とする。

10

## 【0032】

使用に際して、本発明に係る前記画素回路の初期化およびプログラマ化にかかる時間は減少し、これによって背景技術より効率的、高速で、用途の広い表示システムが実現する。前記画素回路の構造により信号  $e_m[n]$  および走査  $[n]$  を单一の制御信号に置き換えることが可能であるため、背景技術に使用される第3の信号  $e_m[n]$  は必要ない。ある好適な実施形態では、基準信号供給線は必要なく、これによってより小型の表示システムが実現する。また制御線の数を減らすことができ、この点においても背景技術より小型で効率的な表示システムが実現する。

## 【発明を実施するための最良の形態】

## 【0033】

以下、詳細を例示するために、本発明の実施の形態を図面に基づいて説明する。以下の説明において、同一の参照符号は同一部を指す。

20

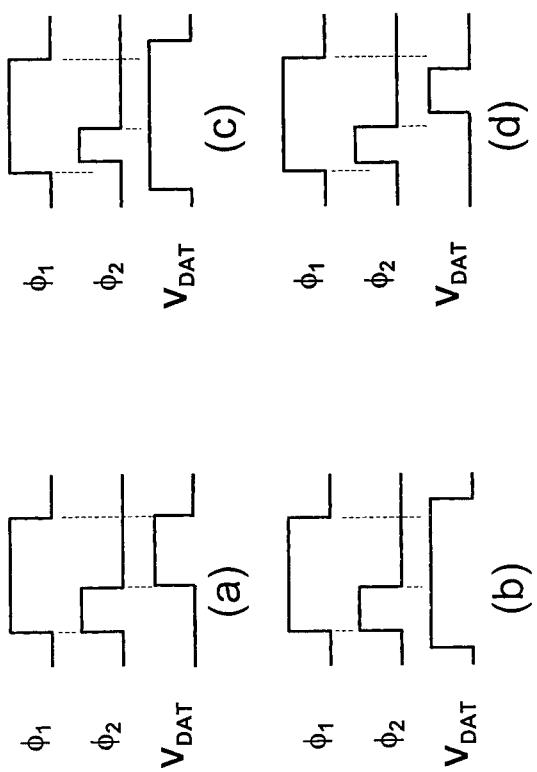

## 【0034】

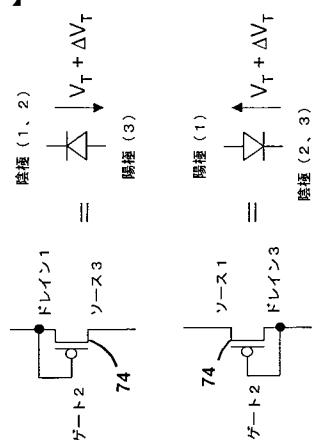

図3に示すように、ピン1、2、3を備える駆動トランジスタ74は、二つの方法でダイオード接続できる。ダイオード接続トランジスタのいずれの構造においても、ゲート端子は常にドレイン端子に接続される。ピン1、2は接続されて陰極端子を形成し、ピン3は陽極端子を形成してもよい。あるいは、ピン2、3が接続されて陰極端子を形成し、ピン1が陽極端子を形成してもよい。

## 【0035】

上述したように、同時に同じ工程で製造された同様のTFTであっても、閾値電圧は変位する。一つの配列におけるすべてのTFTは、共通の名目上の閾値電圧  $V_T$  を有すると考えられる。これに加え、個々のTFTは異なる閾値電圧変位  $V_T$  を有すると考えられる。したがって、各TFTの実際の閾値電圧は、 $V_T$  のTFTごとの変位を加味して、 $(V_T + V_T)$  によって求められる。

30

## 【0036】

本発明における駆動トランジスタは、閾値電圧  $(V_T + V_T)$  が、電流の流れる方向、すなわちどの端子がソースやドレインとして設定されているかに関わらず、同一であるという特性を備える。

## 【0037】

この特性は、ソース端子およびドレイン端子の間が対称であり、応力のかけられていない駆動トランジスタに備わる。対称型駆動トランジスタにおいて、ソース端子およびドレイン端子は等しくドープされ、ゲート端子に関して対称である。このようなトランジスタは、一般に自己整合される。名目上の閾値電圧  $V_T$  および閾値電圧変位  $V_T$  を有する対称型駆動トランジスタ74に関して、ダイオード接続されているときの前記駆動トランジスタ74の閾値電圧の測定値は  $(V_T + V_T)$  であり、前記駆動トランジスタ74がどのようにダイオード接続されているかはこれに影響しない。

40

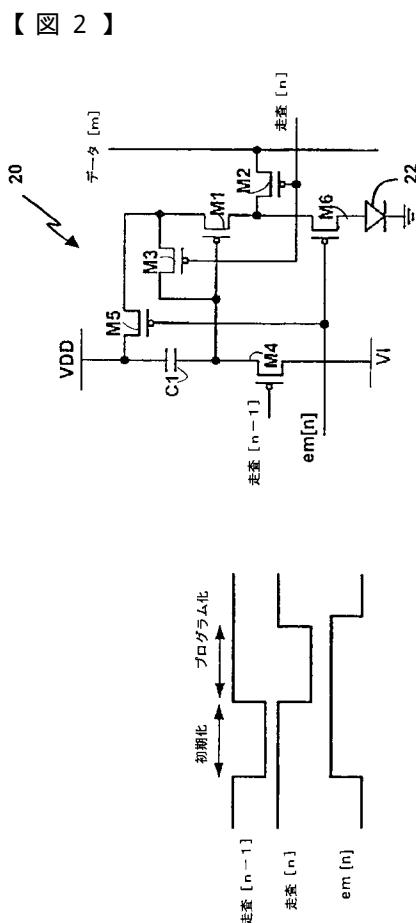

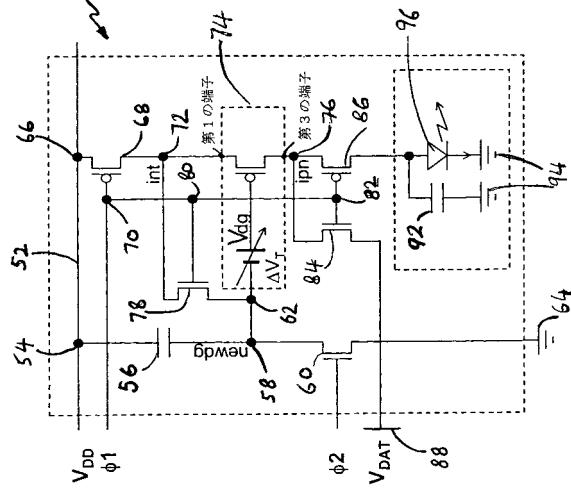

図4に示すように、本発明の第1の実施形態に係る画素回路50は、第1の容量素子56の第1の端子に接続された第1のノード54を備えた第1のレール52を含む。前記第1の容量素子56の第2の端子は、第2のノード58(n e w d g)に接続される。前記第2のノード58は、第1のn型トランジスタ60のソース端子と、第3のノード62と

50

に接続された。前記第1のn型トランジスタ60は、ゲート端子と、第2のレール64とに接続されるドレイン端子とを含む。

【0038】

前記第1のレール52は、第1のp型トランジスタ68のソース端子に接続された第4のノード66を含む。前記第1のp型トランジスタ68は、第5のノード70に接続されたゲート端子と、第6のノード72(int)に接続されたドレイン端子とを含む。前記第6のノード72(int)は、前記駆動トランジスタ74の第1の端子に接続される。前記駆動トランジスタ74はまた、ゲート端子および第3の端子を含み、第2のp型トランジスタである。図3に示され、さらに詳細は図5を参照に後述されるように、前記駆動トランジスタ74の前記第1の端子および第3の端子は、前記駆動トランジスタ74がダイオード接続されているか否かによりソース端子およびドレイン端子として入れ替え可能である。前記駆動トランジスタ74の前記第3の端子は第7のノード76(ipn)に接続され、前記ゲート端子は前記第3のノード62に接続される。

10

【0039】

前記第6のノード72(int)はまた、第2のn型トランジスタ78のソース端子に接続される。前記第2のn型トランジスタ78は、第8のノード80に接続されたゲート端子と、前記第3のノード62に接続されたドレイン端子とを含む。前記第8のノード80は、第9のノード82に接続される。前記第9のノード82は、第3のn型トランジスタ84のゲート端子に接続され、また第3のp型トランジスタ86のゲート端子に接続される。前記第3のn型トランジスタ84のドレイン端子は前記第7のノード76(ipn)に接続され、ソース端子は第3のレール88に接続される。前記第3のp型トランジスタ86のソース端子は前記第7のノード76(ipn)に接続され、ドレイン端子はOLED96の陽極端子に接続される。前記OLED96はまた、第4のレール94に接続された陰極端子を含む。前記画素回路50はまた第2の容量素子92を含み、これは前記OLED96の付随する寄生容量を示す。

20

【0040】

上記の説明に関し、また後述の説明において、前記画素回路50におけるノードは説明の目的でのみ言及される。例えば、図4のノード70、80、82の代わりに1つの接続として示すこともできる。

30

【0041】

作動中、例えば5Vの電圧 $V_{DD}$ を前記画素回路50の全体にわたってかけ、前記OLED96を駆動する。これ以外の電圧値でも可能である。図3を参照し上述したように、前記駆動トランジスタ74は名目上の閾値電圧 $V_T$ および閾値電圧変位 $V_T$ を有する。したがって、ダイオード接続されているとき、前記駆動トランジスタ74の閾値電圧の測定値は( $V_T + V_T$ )である。閾値電圧変位 $V_T$ は、図4および以降の図において、前記駆動トランジスタ74のゲート端子に直列に接続された可変電圧源として示される。前記第1のn型トランジスタ60、第2のn型トランジスタ78、および第3のn型トランジスタ84は、前記第1のp型トランジスタ68および第3のp型トランジスタ86とともに、第1の信号1および第2の信号2の制御によりスイッチとして機能する。一方、前記第2のp型トランジスタは、前記OLED96へと制御量の電流を供給する前記駆動トランジスタ74である。

40

【0042】

前記画素回路50の動作には、プリチャージ、自己整合、および出力の三段階がある。

【0043】

プリチャージ段階では、前記第1の信号1はローレベルであり、前記第2のn型トランジスタ78、第3のn型トランジスタ84、第1のp型トランジスタ68、および第3のp型トランジスタ86のゲート端子に印加される。したがって、前記第2のn型トランジスタ78および第3のn型トランジスタはオンになり、一方で前記第1のp型トランジスタ68および第3のp型トランジスタ86はオフになる。前記プリチャージ段階ではまた、前記第2の信号2はローレベルであり、前記第1のn型トランジスタ60のゲート

50

端子に印加され、これにより前記第1のn型トランジスタ60はオンになる。したがって、前記駆動トランジスタ74は、前記第2のn型トランジスタ78を使用してダイオード接続され、前記第1のp型トランジスタ68をオフにすることにより $V_{DD}$ からアースへの経路から分離され、前記第2のノード58(newdg)は前記第1のn型トランジスタ60をオンにすることにより接地される。

#### 【0044】

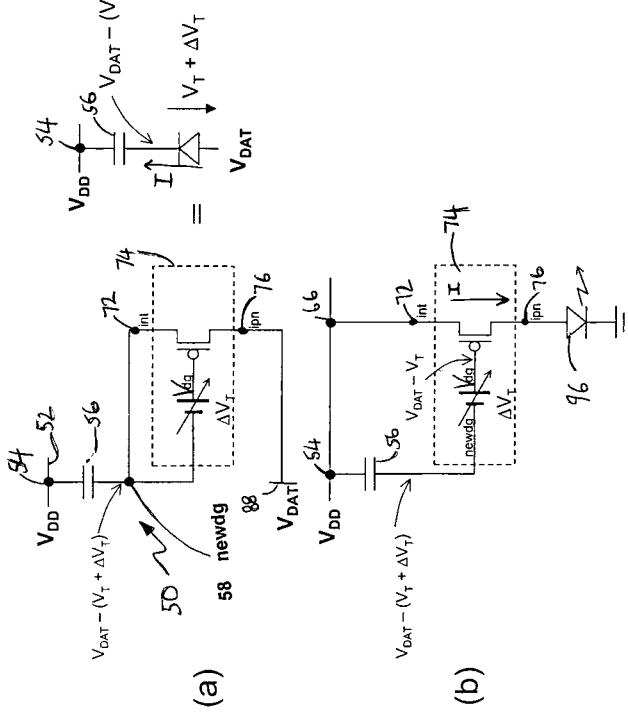

前記第3のレール88は、電圧 $V_{DAT}$ であり、本実施形態の前記プリチャージ段階では例えれば0Vである。これ以外の電圧値でも可能である。これにより、前記第2のノード58(newdg)は、たとえばアース(0V)などの前記第2のレール64と同等の電圧 $V_{newdg}$ にプリチャージされ、前記画素回路50は図5(a)に示す前記画素回路50と表される。前記第1の容量素子56の全体にわたる電圧は、 $V_{DD} - V_{newdg} = 5V$ と求められる。

#### 【0045】

前記第2のノード58(newdg)および第6のノード72(int)は、前記第2のn型トランジスタ78を介して接続され、前記第2のノード58の全体にわたる電圧 $V_{newdg}$ は、前記第6のノード72の全体にわたる電圧 $V_{int}$ に等しい。前記電圧 $V_{DAT}$ を供給する前記供給レール88は、前記第3のn型トランジスタ84を介して前記第7のノード76(ipn)に接続され、前記第7のノード76の全体にわたる電圧 $V_{ipn}$ は $V_{DAT}$ に等しい。前記第2のノード58(newdg)はダイオード接続された前記駆動トランジスタ74の陰極端子であり、前記第7のノード76(ipn)は陽極端子である。

#### 【0046】

自己整合段階では、具体的には自己整合段階のデータ転送の間、前記第1の信号1はローレベルのままであり、前記第2のn型トランジスタ78、第3のn型トランジスタ84、第1のp型トランジスタ68、および第3のp型トランジスタ86のゲート端子に印加される。前記第2のn型トランジスタ78および第3のn型トランジスタはオンのままであり、一方で前記第1のp型トランジスタ68および第3のp型トランジスタ86はオフのままである。

#### 【0047】

前記第2の信号2は論理ゼロとなり、前記第1のn型トランジスタ60のゲート端子に印加され、これにより前記第1のn型トランジスタ60をオフにする。その結果、前記第2のノード(newdg)はもはや接地されていない。

#### 【0048】

ここで電圧 $V_{DAT}$ は脈動し、前記OLE96を駆動するため必要な値、例えは3Vになる。好ましくは、 $V_{DAT}$ の必要な値への脈動は、前記第1のn型トランジスタ60をオフにすると同時に、またはこれより後に開始される。

#### 【0049】

前記第2のノード58(newdg)がアース(0V)にプリチャージされ、 $V_{DAT}$ (3V)よりも低いため、ダイオード接続された前記駆動トランジスタ74は順方向バイアスされ、電流Iが前記第1の容量素子56に流れ、安定した状態になるまで前記第1の容量素子56を放電する。

#### 【0050】

安定した状態では、 $V_{newdg} = V_{DAT} - (V_T + V_T)$ である。したがって、前記第1の容量素子56の全体にわたる電圧は $V_{DD} - V_{newdg} = V_{DD} - (V_{DAT} - (V_T + V_T))$ となる。前記名目上の閾値電圧 $V_T$ が1.1Vの場合、安定状態において前記第1の容量素子56の全体にわたる電圧は、(3.1V + V<sub>T</sub>)により求められる。安定状態に達するまでの時間は、前記第1の容量素子56と、前記駆動トランジスタ74をダイオード接続可能にする前記第2のn型トランジスタ78のインピーダンスとの間に発生するRC時定数に主に左右される。それほど重要ではないが、前記駆動トランジスタ74および第3のn型トランジスタ84の抵抗も、安定状態に達するまでにかかる時間に影響

10

20

30

40

50

する。

【0051】

前記ゲート端子の有効電圧は  $V_{dg}$  は、 $(V_{newdg} + V_T)$  により求められる。したがって安定状態に達すると、前記ゲート端子の有効電圧  $V_{dg}$  は閾値変位  $V_T$  に関係なく、 $V_{dg} = V_{DAT} - V_T = 1.9V$  となる。

【0052】

出力段階では、前記第1の信号 1 は論理ゼロであり、前記第2の n 型トランジスタ 7 8、第3の n 型トランジスタ 8 4、第1の p 型トランジスタ 6 8、および第3の p 型トランジスタ 8 6 のゲート端子に印加される。したがって、前記第2の n 型トランジスタ 7 8 および第3の n 型トランジスタはオフになり、一方で前記第1の p 型トランジスタ 6 8 および第3の p 型トランジスタ 8 6 はオンになる。前記出力段階では、前記第2の信号 2 は論理ゼロのままである。

【0053】

図 5 (b) に示されるように、前記出力段階において前記駆動トランジスタ 7 4 は、前記第1の端子およびゲート端子の間でもはやダイオード接続されておらず、したがって前記 O LED 9 6 の定電流源として機能する。前記駆動トランジスタ 7 4 によって前記 O LED 9 6 へと渡される電流の振幅は、前記閾値変位  $V_T$  ではなく  $V_{DAT}$  の値（具体的には前記自己整合段階において  $V_{DAT}$  の脈動した値）に左右される。したがって、表示装置を形成する一つの配列におけるすべての画素回路 5 0 は、同一の値  $V_{DAT}$  によって同一の明るさに駆動される。

【0054】

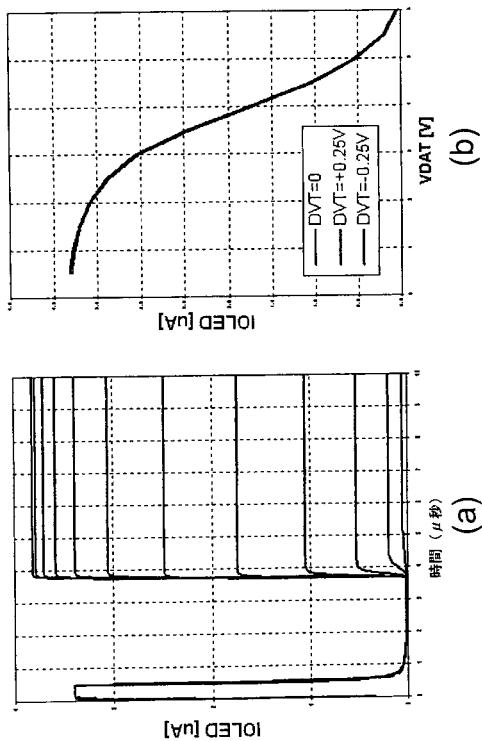

図 10 は、図 4 に示す前記画素回路 5 0 の典型的な駆動波形を示す。図 10 (a) によると、前記第1の信号 1 および第2の信号 2 はともにローレベルであり、前述のように前記第2のノード 5 8 (newdg) をアースと同等の電圧に設定するための前記プリチャージ段階の開始を示している。前記第2の信号 2 は論理ゼロに落ちるため、前記自己整合段階が開始され、 $V_{DAT}$  は脈動して例えば 3V になる。前記第2のノード 5 8 (newdg) がアースと同等の電圧にプリチャージされ、 $V_{DAT}$  (3V) よりも低いため、ダイオード接続された前記駆動トランジスタ 7 4 は順方向バイアスされ、電流 I が前記第1の容量素子 5 6 に流れ、安定した状態になるまで前記第1の容量素子 5 6 を放電する。安定状態に達すると、前記第1の信号 1 論理ゼロになり、閾値変位  $V_T$  と関係なく前記 O LED 9 6 を駆動するために前記出力段階が開始される。当業者には明らかなように、図 10 (b) から (d) に示された駆動波形も同様に、上述のように前記画素回路 5 0 との使用に適用できる。

【0055】

後述する構成と同様に、図 4 に示す構成には前記画素回路の初期化およびプログラム化にかかる時間を背景技術の構成と比較して大幅に削減できるという利点があり、したがってより効率的、高速で、用途の広い表示システムが実現する。さらに、本発明では個々の画素回路を小型化することができるため、開口比のより高い、より小型で効率的な表示装置が実現する。

【0056】

図 4 の前記画素回路 5 0 の別の実施形態では、前記第1の n 型トランジスタ 6 0 は前記第2のレール 6 4 ではなく供給線  $V_{ss}$  に接続される。前記 O LED 9 6 の陰極端子も同様に、または代わりに、前記第4のレール 9 4 ではなく前記供給線  $V_{ss}$  に接続することができる。

【0057】

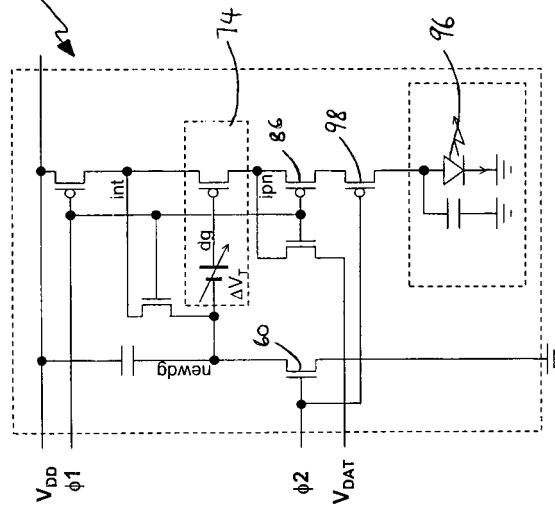

図 6 は、図 4 の前記画素回路 5 0 の本発明の第2の実施形態に係る構造を示す。ここで前記画素回路 5 0 は、第4の p 型トランジスタ 9 8 をさらに含む。前記第4の p 型トランジスタ 9 8 は、前記第3の p 型トランジスタ 8 6 のドレイン端子に接続されたソース端子と、前記 O LED 9 6 の陽極端子に接続されたドレイン端子とを含む。

【0058】

10

20

30

40

50

作動中、前記プリチャージ段階では、前記第2の信号 2 が前記第4の p 型トランジスタ 9 8 のゲート端子に印加される。前記第1の n 型トランジスタ 6 0 はオンに、前記第4の p 型トランジスタ 9 8 はオフになる。これにより、前記第2の信号 2 がロー・レベルの場合、前記第1の信号 1 が論理ゼロであっても、前記プリチャージ段階において前記 O L E D 9 6 は分離される。したがって第2の実施形態では、図 11 ( a ) および ( b ) を参照して後述されるように、異なる駆動波形を使用することが可能である。

#### 【 0 0 5 9 】

図 11 ( a ) および ( b ) に示すように、前記第1の信号 1 がロー・レベルになる前に前記第2の信号 2 はロー・レベルである。これらの駆動波形が図 4 の前記回路に使用されると、前記第2の信号 2 はロー・レベルのとき、ノード 5 8 ( newdg ) は接地され、前記 p 型駆動トランジスタのゲート電圧も接地される。こうして、前記第1の信号 1 がロー・レベルでありトランジスタ 6 8 および 8 6 がオフになる前に、前記駆動トランジスタ 7 4 が短時間オンになってもよい。そのとき前記 O L E D 9 6 は、短時間駆動されて最大の明るさとなり得る。しかし図 6 の前記画素回路では、上述のようにスイッチ 6 0 がオフとなるときスイッチ 9 8 はオフとなり前記 O L E D 9 6 は分離されるため、この点は問題にならない。

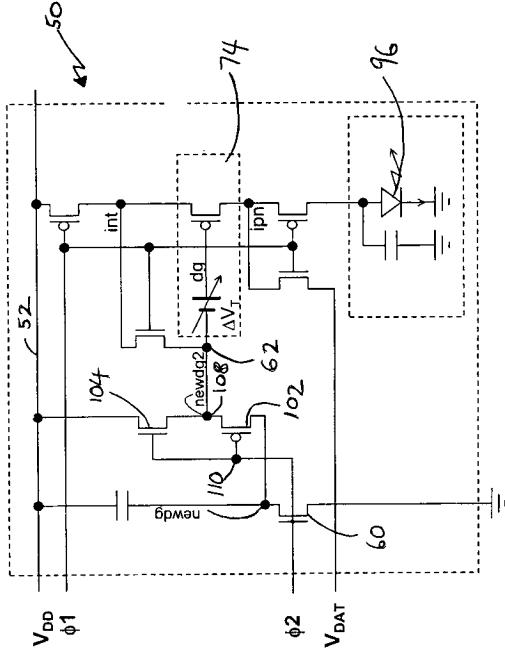

#### 【 0 0 6 0 】

図 7 は、図 4 の前記画素回路 5 0 の本発明の第3の実施形態に係る構造を示す。ここで前記画素回路 5 0 は、第5の p 型トランジスタ 1 0 2 と、第4の n 型トランジスタ 1 0 4 とをさらに含む。前記第5の n 型トランジスタ 1 0 4 は、前記第1のレール 5 2 に接続されたソース端子と、ノード 1 0 8 ( newdg2 ) に接続されたドレイン端子とを含む。前記ノード ( newdg2 ) は、前記第3のノード 6 2 に接続される。つまり、ノード ( newdg2 ) および前記第3のノード 6 2 は技術的に同一である。前記ノード ( newdg2 ) はまた、前記第5の p 型トランジスタ 1 0 2 の第1の端子に接続される。前記第5の p 型トランジスタ 1 0 2 は、前記第2のノード 5 8 ( newdg ) に接続された第2の端子を含む。

#### 【 0 0 6 1 】

作動中、前記プリチャージ段階では、前記第2の信号 2 が前記第4の n 型トランジスタ 1 0 4 のゲート端子と、前記第5の p 型トランジスタ 1 0 2 のゲート端子とに印加される。前記第2の信号 2 がロー・レベルであり前記第1の n 型トランジスタ 6 0 がオンになる場合、前記第5の p 型トランジスタ 1 0 2 はオフになり前記第4の n 型トランジスタ 1 0 4 はオンになる。これにより、前記駆動トランジスタ 7 4 を確実にオフになり前記 O L E D 9 6 を分離する。

#### 【 0 0 6 2 】

図 11 ( a ) および ( b ) を参照に上述および後述する駆動波形は、図 7 の前記画素回路 5 0 においても適用できる。具体的には、図 7 においてノード 1 0 8 ( newdg2 ) はノード 5 8 ( newdg ) が接地されている間は常に  $V_{DD}$  に保たれるため、前記駆動トランジスタのゲート電圧は  $V_{DD}$  に等しくなり、前記駆動トランジスタはオンにならない。したがって、図 6 の構成には備えられたトランジスタ 9 8 はここでは必要ない。

#### 【 0 0 6 3 】

図 7 の構成の代わりに、トランジスタ 1 0 4 を n 型トランジスタから p 型トランジスタに変え、トランジスタ 1 0 2 を p 型トランジスタから n 型トランジスタに変えることも可能である。これは電源  $V_{DD}$  から電流を引くのに好適である。しかし、こうして変更された両トランジスタのゲートは第2の信号 2 に接続されているため、両トランジスタは一つのインバータとして機能する。ただこの変更を加えることにより、結果としてできた前記インバータは反転信号 2 ( バー ) をノード ( newdg2 ) に出力してしまう。つまり 2 がハイであるためトランジスタ 6 0 はオンになり、ノード ( newdg ) は接地され、トランジスタ 1 0 4 および 1 0 2 によって形成されるインバータは反転信号 2 ( バー ) ( すなわちロー ) を newdg2 に出力してしまう。この状況で、前記 p 型駆動トランジスタはオンになり、 1 がハイになる前および前記駆動トランジスタがダイオード接続

10

20

30

40

50

される前に、前記 O L E D は発光してしまう。

【 0 0 6 4 】

これを防ぐため、前記第2の信号線および変更されたトランジスタ104、102により形成された前記インバータの間にインバータを追加する。これにより、変更されたトランジスタ104、102により形成された前記インバータに入力される信号は2(バー)である。つまり2がハイであるためトランジスタ60はオンになり、ノード(newdg)は接地され、トランジスタ104、102により形成された前記インバータは2(バー)を入力として受け、2(すなわちハイ)をnewdg2に出力する。この結果、前記p型駆動トランジスタはオフになり、1がハイになる前および前記駆動トランジスタがダイオード接続される前には、前記O L E D は発光しない。

10

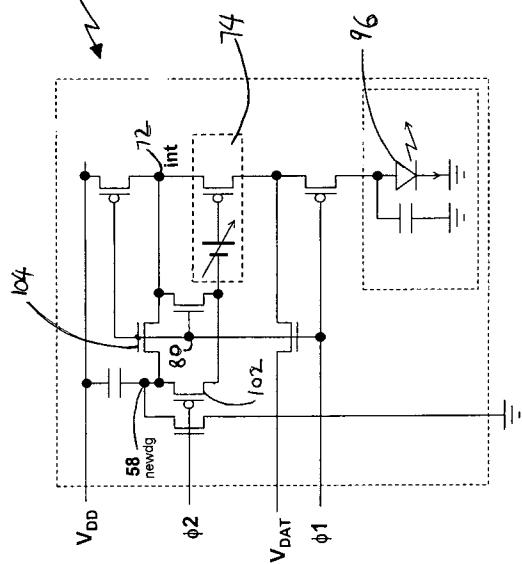

【 0 0 6 5 】

図8は、前記第4のn型トランジスタ104を備える図7の前記画素回路50の本発明の第4の実施形態に係る別の構成を示す。ここで前記第4のn型トランジスタ104は、前記第6のノード72(int)に接続された端子と、前記第2のノード(newdg)に接続された端子を含む。前記第4のn型トランジスタ104はまた、前記第1の信号1を受け取る前記第8のノード80に接続されたゲート端子を含む。

20

【 0 0 6 6 】

作動中、ならびに前記プリチャージ段階および自己整合段階において前記第1の信号1がローレベルであるとき、前記第4のn型トランジスタ104はオンになり、前記第7のノード(ipn)および第2のノード(newdg)の間の導電性を高める。

20

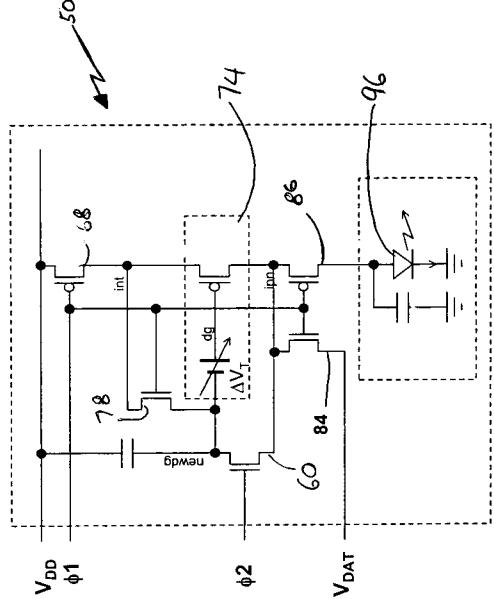

【 0 0 6 7 】

図9は、図4の前記画素回路50の本発明の第5の実施形態に係る構造を示す。ここで前記画素回路50は、前記第2のレール64ではなく前記第7のノード(ipn)に接続された前記第1のn型トランジスタ60の端子を含む。したがって、前記駆動トランジスタ74は、前記第3のp型トランジスタ86の端子と、前記第3のn型トランジスタ84の端子とに接続される。

30

【 0 0 6 8 】

作動中、前記電圧V<sub>DAT</sub>は前記第4のn型トランジスタ60および第3のn型トランジスタ84を介して前記第2のノード(newdg)にプリチャージ段階電圧を供給する。これにより、アース(0V)としての前記第2のレール64はもはや必要なく、供給線V<sub>ss</sub>に置き換える必要もない。前記プリチャージ段階において、前記電圧V<sub>DAT</sub>は、前記駆動トランジスタ74が順方向バイアスされたダイオード接続トランジスタとして機能できるよう、前記電圧V<sub>DAT</sub>が前記自己整合段階に脈動する電圧よりも低い必要がある。

30

【 0 0 6 9 】

図11(b)に、図9に示されるような前記画素回路50の典型的な駆動波形を示す。前記プリチャージ段階において、前記第1の信号1が論理ゼロであり、前記第2の信号2がローレベルになるとき、ノード(newdg)は最初は前記第1のn型トランジスタ60を介して前記第3のp型トランジスタ86およびO L E D 96をアースに放電する。前記第1の信号1はローレベルになり、V<sub>DAT</sub>はV<sub>DAT</sub>ローへと増加する。前記駆動トランジスタ74はダイオード接続され、前記ノード(newdg)は前記第3のn型トランジスタ84、第1のn型トランジスタ60、駆動トランジスタ74、および第2のn型トランジスタ78を介して前記V<sub>DAT</sub>ローへと初期化される。

40

【 0 0 7 0 】

前記第2の信号2は論理ゼロに落ちるため、前記自己整合段階においては、V<sub>DAT</sub>ローがV<sub>DAT</sub>ハイへと増加する。前記ノード(newdg)は前記第3のn型トランジスタ84、駆動トランジスタ74、および第2のn型トランジスタ78を介して(V<sub>DAT</sub>ハイ-(V<sub>T</sub>+V<sub>T</sub>))から求められる値へと増加する。

【 0 0 7 1 】

前記出力段階では、前記第1の信号1が論理ゼロであり、前記駆動トランジスタ74はその第1の端子およびゲート端子の間にあってもはやダイオード接続されていない。し

50

たがって、前記駆動トランジスタ74は、前記第1のp型トランジスタ68、駆動トランジスタ74、および第3のp型トランジスタ86を介して、前記OLED96の定電流源として機能する。前記駆動トランジスタ74によって前記OLED96へと渡される電流の振幅は、前記閾値変位  $V_T$  ではなく  $V_{DAT}$  の値（具体的には前記自己整合段階における  $V_{DAT}$  ハイの値）に左右される。これにより、表示装置を形成する一つの配列におけるすべての画素回路50は、同一の明るさに駆動される。

#### 【0072】

さらにこれに代わり、図6の前記トランジスタ98はまた、図7から9の各構成に含めることもできる。こうして各構成において、前記画素回路は前記トランジスタ86およびOLED96の間に直列に接続された前記p型トランジスタ98を含む。前記制御信号2がp型トランジスタ98のゲートに印加され、これにより前記n型トランジスタ60をオンにする間は前記p型トランジスタ98をオフにする。

#### 【0073】

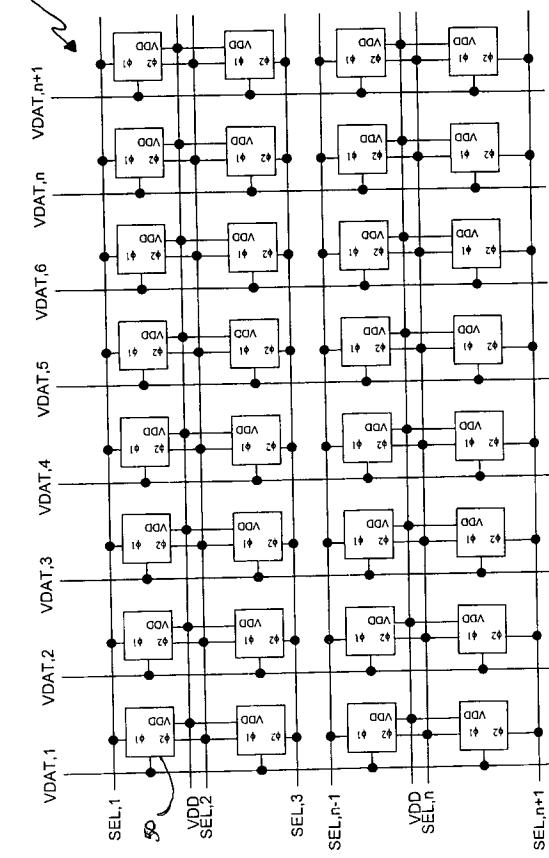

図12は、表示システムを形成する配列150における図4、6、7、8に示す前記画素回路50の構造を示す。前記配列150は、図10または11(a)の典型的な駆動波形のいずれかによって駆動される。前記配列150の各画素回路50は、アース線Gndを含み、これは上述したように供給線  $V_{SS}$  で置き換えることも可能である。この構造はまた、前記第1および第2の供給信号1、2を供給する二本の個別の水平制御線を含む。

#### 【0074】

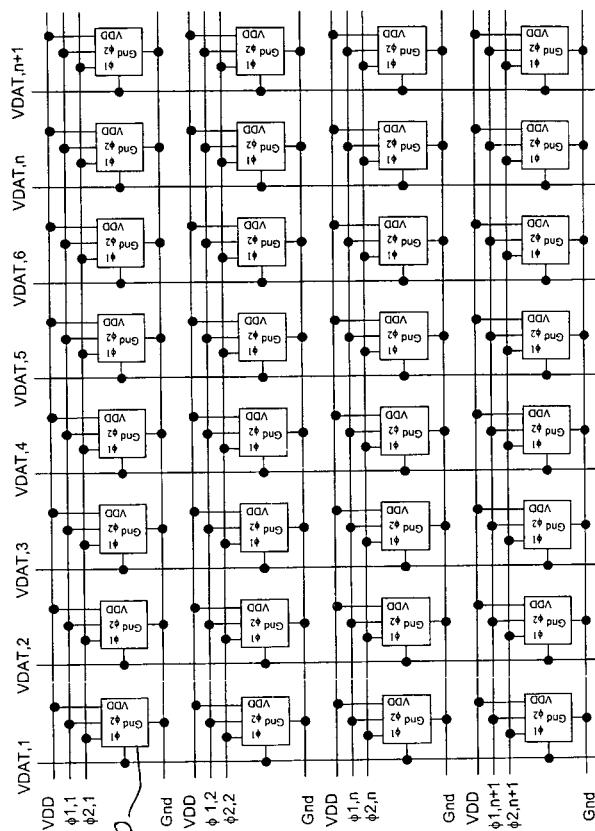

図13は、表示システムを形成する配列200における図9に示す前記画素回路50の構造を示す。図9に示す前記画素回路50において図11(d)に示す波形を使用することにより、図12の構造と比較して水平制御線の数が減る。

#### 【0075】

水平制御線の数が減るのは、制御線SEL<sub>1</sub>、2（図11(c)および(d)では制御信号  $V_{SEL_{n+1}}$ ）が隣接する画素回路50に前記第1の制御信号1および第2の制御信号2を供給するためである。

#### 【0076】

画素の各列に二本の信号線が備わる図12の構造を図13と同様に、各画素回路に含まれる容量素子がアースGndの代わりにデータ線  $V_{DAT}$  に放電するよう調整することもできる。図6、7、8の前記画素回路50において図11(c)に示す波形を使用することにより、図12の構造と比較して水平線の数が減る。

#### 【0077】

同様に、画素の隣接する列が信号線を共有する図13の構造を図12と同様に、各画素回路に含まれる容量素子がデータ線  $V_{DAT}$  の代わりにアースGndに放電するよう調整することもできる。図9の前記画素回路50において図11(b)に示す波形を使用することにより、図12の構造と比較して水平制御線の数が減る。

#### 【0078】

図12および13の配列はまた、上述していないものも含め、本発明の前記画素回路のあらゆる実施形態に適用可能である。

#### 【0079】

図11(a)から(d)の各図において、前記第1および第2の制御信号1、2は重複しているということも注意すべきである。つまり、1は2がハイである時間の一部においてハイであり、2は1がハイである時間の一部においてハイである。しかし、1は2がローである時間の一部においてもハイであり、2は1がローである時間の一部においてもハイである。この重複する制御信号を使用することにより、公知ではないが、走査速度が高まり、結果として表示される動画の質が向上する。

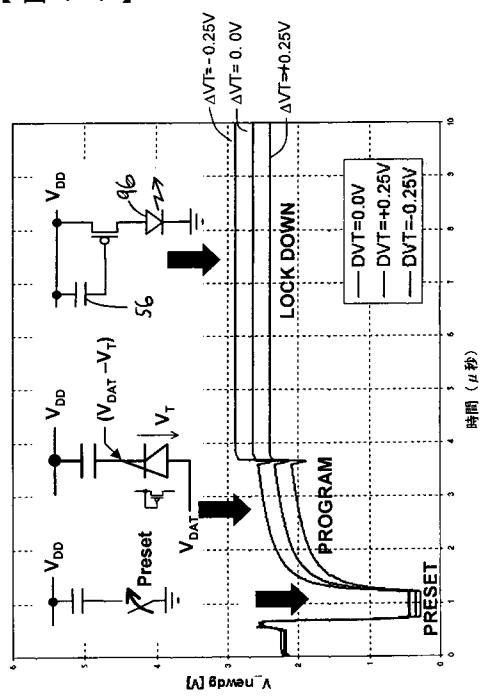

#### 【0080】

図14は、図4に示す前記画素回路50の前記第2のノード58における電圧  $V_{new}$  のシミュレーションをミリ秒単位で示すグラフである。前記プリチャージ段階（図1

10

20

30

40

50

2におけるP R E S E T)において、前記電圧V newdgは実質的にアース(0V)に落ちる。前記自己調整段階(図12におけるP R O G R A M)では、前記電圧V newdgは、V DATが脈動して前記O L E D 9 6を駆動する電圧になるに従い、値(V DAT - (V T + V T))へと増加する。前記出力段階(図12におけるL O C K D O W N)においては、前記電圧V newdgは工程が繰り返されるまで前記第1の容量素子56によって保たれる。図12に明白なように、前記電圧V newdgは変位値V Tに応じて変動する。

#### 【0081】

図14から、前記プリチャージ段階および自己調整段階は、ほんの数ミリ秒の間に完了できることがわかる。これは背景技術と比較しておよそ二桁分(つまり100倍)早い。これに加えて、低圧が使用可能である。したがって本発明は、表示の質を高め、電力消費を抑えることができる。さらに、本発明に係る画素回路および表示装置は、背景技術のこれらと比較して小型である。

#### 【0082】

図15は、変位値V Tに対する前記O L E D 9 6を駆動する出力電流(I O L E D)のシミュレーションを示す。図15はV Tに関わらず前記出力電流(I O L E D)が同一であることを示し、これにより一つの配列を形成する前記画素回路を変位値V Tに関わらず同じ明るさに駆動することができる。

#### 【0083】

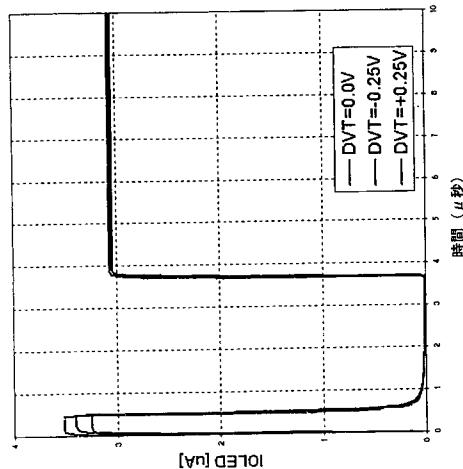

図16も同様の効果を示す。図16(a)は、異なる入力電圧V DDに対する出力電流(I O L E D)をマイクロ秒単位で示すグラフである。出力電力(I O L E D)の振幅は異なっており、一方で変位値V Tは前記出力(I O L E D)に影響しない。図16(b)は、異なるV Tに対する、V DATの変化に応じたI O L E Dの変位を示す。出力電力(I O L E D)はV Tに関わらず実質的に同一であり、したがって各V T値に対する出力電力(I O L E D)は重なっている。よって、一つの配列を形成する前記画素回路を、変位値V Tに関わらず同じ明るさに駆動することができる。

#### 【0084】

上述したように前記画素回路50を使用する表示システム1000は、携帯電話、携帯端末(P D A)、コンピュータ、C Dプレイヤ、D V Dプレイヤなど、またこれらに限らず、小型で携帯用の電子製品に使用するのに好適である。

#### 【0085】

前記表示システム1000を内蔵可能な端末装置の例を以下に説明する。

#### 【0086】

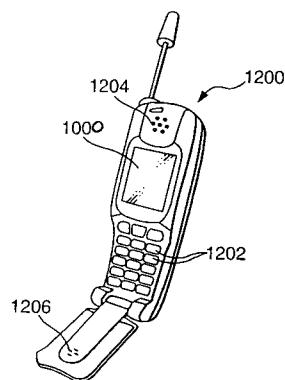

携帯電話に前記表示システム1000を適用した例を説明する。図17は、携帯電話の構成を示す等角図である。この図では、携帯電話1200は、複数の操作キー1202と、受話部1204と、送話部1206と、表示パネルとしての前記表示システム1000とを備える。前記送話部1206または受話部1204は、会話を出力させるために使用されてもよい。

#### 【0087】

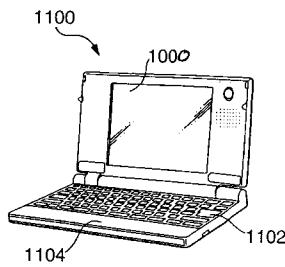

携帯用パーソナル・コンピュータに上記の実施形態の一つに係る前記表示システム1000を適用した例を説明する。

#### 【0088】

図18は、パーソナル・コンピュータの構成を示す等角図である。この図では、パーソナル・コンピュータ1100は、キーボード1102を含む本体1104と、表示パネルとしての前記表示システム1000とを備える。

#### 【0089】

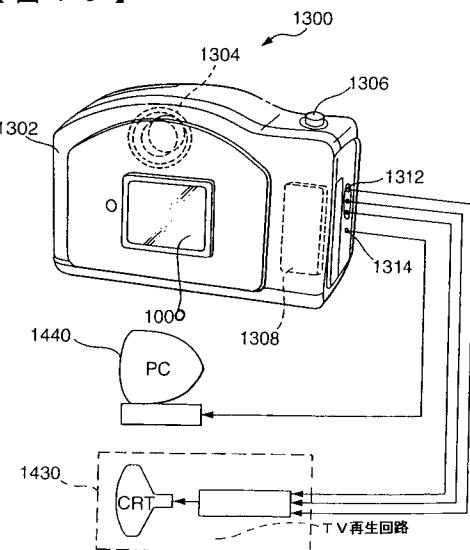

次に、前記表示システム1000を使用したデジタル・カメラについて説明する。図19は、デジタル・カメラの構成および外部装置との接続を簡単に示す等角図である。

#### 【0090】

典型的なカメラは、物体からの光学像に基づいてフィルムを感光させる。一方、デジタ

10

20

30

40

50

ル・カメラ 1300 は、たとえば電荷結合素子 (C C D) を使用した光電変換によって物体の光学像からの画像信号を生成する。前記デジタル・カメラ 1300 は、C C Dからの画像信号に基づいて表示をおこなうため、ケース 1302 の背面に表示パネルとしての前記表示システム 1000 を備える。こうして、前記表示システム 1000 は物体を表示するファインダとして機能する。光学レンズおよび C C D を含む受光素子 1304 は、前記ケース 1302 の表面 (図面における裏側) に備えられる。前記表示システム 1000 は、このデジタル・カメラにおいて実施してもよい。

【0091】

図 17 の前記携帯電話、図 18 の前記パーソナル・コンピュータ、図 19 の前記デジタル・カメラ以外にも、端末装置の別の例として、携帯端末 (P D A)、テレビ、ファインダ型およびモニタ型ビデオ・レコーダ、カー・ナビゲーション・システム、ポケットベル、電子手帳、携帯計算機、ワード・プロセッサ、ワークステーション、テレビ電話、店舗販売時点情報管理 (P O S) 端末、タッチ・パネルを備える装置などが挙げられる。本発明の前記表示システムは、これらの端末装置のいずれにも適用可能である。

【0092】

本明細書の記載はあくまで一例であり、本発明はその範囲から逸脱することなく、当業者の知識に基づき変更を加えて実施可能である。

【図面の簡単な説明】

【0093】

【図 1】アクティブ・マトリクス O L E D 表示装置に適用される背景技術による電圧駆動画素回路の概略図である。

【図 2】アクティブ・マトリクス O L E D 表示装置に適用される背景技術による自己補正電圧プログラム化画素構造の概略図。

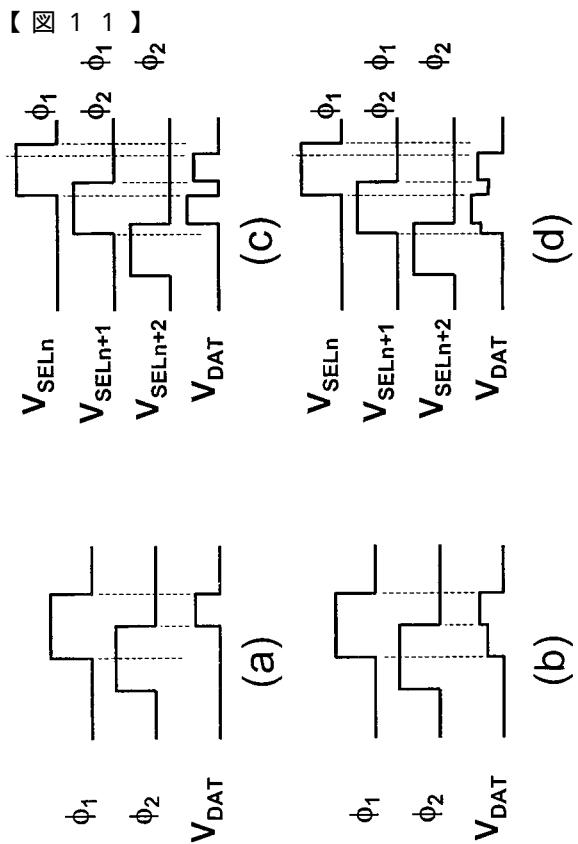

【図 3】トランジスタをダイオード接続する二つの方法を示す概略図。

【図 4】本発明の第 1 の実施形態に係る画素回路の概略図。

【図 5】定常電圧における図 4 の画素回路の一部を示す概略図。

【図 6】本発明の第 2 の実施形態に係る画素回路の概略図。

【図 7】本発明の第 3 の実施形態に係る画素回路の概略図。

【図 8】本発明の第 4 の実施形態に係る画素回路の概略図。

【図 9】本発明の第 5 の実施形態に係る画素回路の概略図。

【図 10】図 4、6、7、8、9 の画素回路の一般駆動波形を示す概略図。

【図 11】図 6、7、8、9 の画素回路の一般駆動波形を示す概略図。

【図 12】図 4、6、7、8 の画素回路の構造を示す概略図。

【図 13】図 9 の画素回路の構造を示す概略図。

【図 14】図 4 の画素回路のノード n e w d g における電圧のシミュレーションを示す概略図。

【図 15】変位値  $V_T$  による出力電流のシミュレーションを示す概略図。

【図 16】異なる入力電圧および変位値  $V_T$  による出力電流のシミュレーションを示す概略図。

【図 17】本発明に係る表示システムを内蔵する携帯電話の概略図。

【図 18】本発明に係る表示システムを内蔵するモバイル・パーソナル・コンピュータの概略図。

【図 19】本発明に係る表示システムを内蔵するデジタル・カメラの概略図。

【符号の説明】

【0094】

1、2、3 ... ピン、5 0 ... 画素回路、5 2 ... 第 1 のレール、5 4 ... 第 1 のノード、5 6 ... 第 1 の容量素子、5 8 ... 第 2 のノード、6 0 ... 第 1 の n 型トランジスタ、6 2 ... 第 3 のノード、6 4 ... 第 2 のレール、6 6 ... 第 4 のノード、6 8 ... 第 1 の p 型トランジスタ、7 0 ... 第 5 のノード、7 2 ... 第 6 のノード、7 4 ... 駆動トランジスタ (第 2 の p 型トランジスタ)、7 6 ... 第 7 のノード、7 8 ... 第 2 の n 型トランジスタ、8 0 ... 第 8 のノード、8

10

20

30

40

50

2 ... 第 9 のノード、8 4 ... 第 3 の n 型トランジスタ、8 6 ... 第 3 の p 型トランジスタ、8 8 ... 第 3 のレール、9 2 ... 第 2 の容量素子、9 4 ... 第 4 のレール、9 6 ... O L E D、9 8 ... 第 4 の p 型トランジスタ、1 0 2 ... 第 5 の p 型トランジスタ、1 0 4 ... 第 4 の n 型トランジスタ。

"A self-compensated voltage programming pixel structure for active-matrix organic light emitting diodes," by S. M. Choi, et.al., International Display Workshop 2003 年, 535~538 頁

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【 図 1 3 】

【 図 1 2 】

【 図 1 4 】

【図15】

【図16】

【図17】

【図18】

【図19】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

H 05 B 33/14

A

F ターム(参考) 3K007 AB05 AB17 BA06 DB03 GA00 GA04

5C080 AA06 BB05 DD05 DD08 DD26 EE29 FF11 HH09 JJ03 JJ04

JJ06 KK01 KK07 KK43 KK47

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路，像素电路的驱动方法和有源矩阵器件                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP2005301290A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2005-10-27 |

| 申请号            | JP2005126001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 申请日     | 2005-04-25 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | サイモンタム                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | サイモン タム                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 G09G3/32 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0426 G09G2300/0819 G09G2300/0842 G09G2310/0262 G09G2320/0233 G09G2320/0252 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.A G09G3/20.611.H G09G3/20.621.F G09G3/20.624.B H05B33/14.A G09G3/3233                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 3K007/AB05 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 5C080/AA06 5C080 /BB05 5C080/DD05 5C080/DD08 5C080/DD26 5C080/EE29 5C080/FF11 5C080/HH09 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C080/KK01 5C080/KK07 5C080/KK43 5C080/KK47 3K107/AA01 3K107 /BB01 3K107/CC14 3K107/EE04 3K107/HH05 5C380/AA01 5C380/AB06 5C380/AB24 5C380/AC04 5C380/AC05 5C380/AC07 5C380/AC08 5C380/AC09 5C380/AC11 5C380/AC12 5C380/AC13 5C380 /BA01 5C380/BA11 5C380/BA38 5C380/BA39 5C380/BC01 5C380/CC02 5C380/CC03 5C380/CC07 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC51 5C380/CC52 5C380/CC62 5C380/CC63 5C380 /CC64 5C380/CD016 5C380/CD025 5C380/CD027 5C380/CD028 5C380/CD072 5C380/DA02 5C380 /DA06 5C380/DA41 5C380/DA42 |         |            |

| 代理人(译)         | 须泽 修                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 优先权            | 2004004919 2004-03-04 GB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 其他公开文献         | JP4289321B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

#### 摘要(译)

已知用于驱动诸如电流驱动的有机发光器件之类的发光器件的像素电路校正驱动晶体管的阈值电压的变化。然而，编程和初始化这种像素电路需要花费时间，并且需要多条控制线或信号线。本发明提供一种像素电路，该像素电路包括：将驱动晶体管与二极管连接的n型晶体管；以及用于减少信号线和控制线的数量的装置。[选择图]图4