(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-227562

(P2005-227562A)

(43) 公開日 平成17年8月25日(2005.8.25)

(51) Int.Cl.<sup>7</sup>

**G09G** 3/30

**G09F** 9/30

**G09F** 9/35

**G09G** 3/20

**H05B** 33/14

F 1

G09G 3/30 J 3K007

G09F 9/30 338 5C080

G09F 9/35 365Z 5C094

G09G 3/35

G09G 3/20

G09G 3/20 611H

テーマコード(参考)

審査請求 未請求 請求項の数 8 O L (全 23 頁) 最終頁に続く

(21) 出願番号

特願2004-36504 (P2004-36504)

(22) 出願日

平成16年2月13日 (2004.2.13)

(71) 出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100086298

弁理士 船橋 國則

(72) 発明者 山本 哲郎

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 内野 勝秀

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 山下 淳一

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

最終頁に続く

(54) 【発明の名称】画素回路および表示装置

## (57) 【要約】

【課題】キャパシタ(画素容量)の容量と駆動トランジスタのゲート・ソース間容量との和がスイッチングトランジスタの寄生容量よりも小さないと、駆動トランジスタのソース電位の変化量により当該駆動トランジスタのゲート・ソース間電位の値が変化してしまい、所望の発光が望めない。

【解決手段】駆動トランジスタであるTFT22のゲート・ソース間にキャパシタ23を接続するとともに、TFT22のソースをスイッチングトランジスタであるTFT25を介して接地電位GNDに選択的に接続する構成の画素回路11において、レイアウト上、有機EL素子21のアノード電極層211とキャパシタ23を形成するキャパシタ形成層231, 232とをオーバーラップさせた構造とする。

【選択図】図10

## 【特許請求の範囲】

## 【請求項 1】

一端が第 1 の電源電位に接続された電気光学素子と、

前記電気光学素子の他端と第 2 の電源電位との間に接続された駆動トランジスタと、

前記駆動トランジスタのゲートとソースの間に接続された第 1 のキャパシタと、

前記駆動トランジスタのゲートに対して輝度情報に応じた信号を選択的に取り込む第 1 のスイッチングトランジスタと、

前記駆動トランジスタのソースと第 3 の電源電位との間に接続された第 2 のスイッチングトランジスタとを有し、

前記電気光学素子の前記一端側の層と前記第 1 のキャパシタを形成するキャパシタ形成層とがオーバーラップしている

ことを特徴とする画素回路。 10

## 【請求項 2】

前記駆動トランジスタは、N チャネル電界効果トランジスタである

ことを特徴とする請求項 1 記載の画素回路。

## 【請求項 3】

前記駆動トランジスタの閾値電圧のバラツキをキャンセルする回路をさらに有する

ことを特徴とする請求項 1 記載の画素回路。

## 【請求項 4】

前記駆動トランジスタのゲートと前記第 1 のスイッチングトランジスタとの間に接続された第 2 のキャパシタをさらに有し、

前記電気光学素子の前記一端側の層と前記第 2 のキャパシタを形成するキャパシタ形成層とがオーバーラップしている

ことを特徴とする請求項 3 記載の画素回路。 20

## 【請求項 5】

一端が第 1 の電源電位に接続された電気光学素子と、前記電気光学素子の他端と第 2 の電源電位との間に接続された駆動トランジスタと、前記駆動トランジスタのゲートとソースの間に接続された第 1 のキャパシタと、前記駆動トランジスタのゲートとデータ線との間に接続された第 1 のスイッチングトランジスタと、前記駆動トランジスタのソースと第 3 の電源電位との間に接続された第 2 のスイッチングトランジスタとを有し、前記電気光学素子の前記一端側の層と前記第 1 のキャパシタを形成するキャパシタ形成層とがオーバーラップしてなる画素回路が行列状に配置されてなる画素アレイ部と、

前記データ線に輝度情報に応じた信号を供給するデータ線駆動回路と、

前記第 1 のスイッチングトランジスタを駆動する書き込み走査回路と、

前記第 2 のスイッチングトランジスタを駆動する駆動走査回路と

を備えたことを特徴とする表示装置。 30

## 【請求項 6】

前記駆動トランジスタは、N チャネル電界効果トランジスタである

ことを特徴とする請求項 5 記載の表示装置。

## 【請求項 7】

前記画素回路は、前記駆動トランジスタの閾値電圧のバラツキをキャンセルする回路をさらに有する

ことを特徴とする請求項 5 記載の表示装置。 40

## 【請求項 8】

前記画素回路は、前記駆動トランジスタのゲートと前記第 1 のスイッチングトランジスタとの間に接続された第 2 のキャパシタをさらに有し、

前記電気光学素子の前記一端側の層と前記第 2 のキャパシタを形成するキャパシタ形成層とがオーバーラップしている

ことを特徴とする請求項 7 記載の表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、画素回路および表示装置に関し、特に流れる電流によって輝度が変化する電気光学素子を表示素子として有する画素回路、当該画素回路が行列状に配置されてなり、画素回路（画素）毎に能動素子を有して当該能動素子によって画素単位で表示駆動が行われる表示装置に関する。

## 【背景技術】

## 【0002】

表示装置、例えば画素の表示素子として液晶セルを用いた液晶表示装置においては、液晶セルを含む画素を多数マトリクス状に配列し、表示すべき画像情報に応じて画素毎に光強度を制御することによって画像の表示駆動が行われるようになっている。この表示駆動は、画素の表示素子として、流れる電流によって輝度が変化する電気光学素子、例えば有機EL (electro luminescence) 素子を用いた有機EL表示装置でも同様である。

## 【0003】

ただし、有機EL表示装置の場合は、画素の表示素子として、自発光素子である有機EL素子を用いたいわゆる自発光型の表示装置であるため、光源（バックライト）からの光強度を制御することによって画像の視認性が高い、バックライトが不要、応答速度が速い等の利点を持っている。また、有機EL素子の発光輝度がそれに流れる電流値によって制御される、即ち有機EL素子が電流制御型であるという点で、液晶セルが電圧制御型である液晶表示装置とは大きく異なっている。

## 【0004】

有機EL表示装置においては、液晶表示装置と同様、その駆動方式として単純（パッシブ）マトリクス方式とアクティブマトリクス方式とを採ることができる。ただし、単純マトリクス方式の表示装置は、構造が単純であるものの、大型でかつ高精細の表示装置の実現が難しいなどの問題がある。このため、近年、画素内部の発光素子に流れる電流を、同様に画素内部に設けた能動素子、例えば絶縁ゲート型電界効果トランジスタ（一般には、薄膜トランジスタ（Thin Film Transistor; TFT）によって制御する、アクティブマトリクス方式の開発が盛んに行われている。

## 【0005】

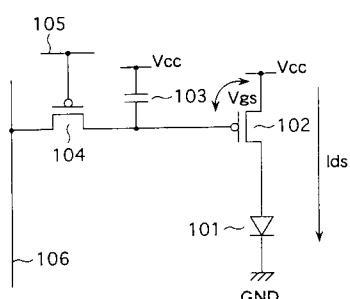

図25は、アクティブマトリクス型有機EL表示装置における画素回路（単位画素の回路）の従来例を示す回路図である。

## 【0006】

この従来例に係る画素回路は、図25から明らかなように、例えばカソード（陰極）が接地電位GNDに接続された有機EL素子101と、ドレインが有機EL素子101のアノード（陽極）に接続され、ソースが正電源電位Vccに接続されたPチャネルTFT102と、このTFT102のゲートと正電源電位Vccとの間に接続されたキャパシタ103と、ソースがTFT102のゲートに、ゲートが走査線105に、ドレインがデータ線106にそれぞれ接続されたPチャネルTFT104とを有する構成となっている（例えば、特許文献1,2参照）。

## 【0007】

ここで、有機EL素子は多くの場合整流性があるため、OLED (Organic Light Emitting Diode)と呼ばれることがある。したがって、図25およびその他の図では、OLEDとしてダイオードの記号を用いて示している。ただし、以下の説明において、OLEDには必ずしも整流性が要求されるものではない。

## 【0008】

続いて、上記構成の画素回路の動作について説明する。先ず、走査線105の電位を選択状態（ここでは、低レベル状態）とし、データ線106に書き込み電位Vdataを印加すると、TFT104が導通してキャパシタ103が充電または放電される。これにより、TFT102のゲート電位は書き込み電位Vdataとなる。次に、走査線105の電位を非選択状態（ここでは、高レベル状態）とすると、走査線105とTFT102と

10

20

30

40

50

は電気的に切り離されるが、TFT102のゲート電位はキャパシタ103によって安定に保持される。

【0009】

そして、TFT102および有機EL素子101に流れる電流は、TFT102のゲート・ソース間電圧Vgsに応じた値となる。すると、有機EL素子101は、その電流値に応じた輝度で発光し続ける。ここで、データ線106を通して供給される輝度情報を、走査線105を選択し、TFT104を通して画素内部に伝える動作を、以下、「書き込み」と呼ぶこととする。

【0010】

上述したように、図25の画素回路では、一度電位Vdataの書き込みを行えば、次に電位Vdataの書き込みが行われるまでの間、有機EL素子101は一定の輝度で発光を継続する。また、駆動トランジスタであるTFT102のゲート電圧を変化させることで、有機EL素子101に流れる電流値を制御している。このとき、TFT102は、ソースが正電源電位Vccに接続されており、常に飽和領域で動作しているため、下記の式(1)に示した電流値Idsを持つ定電流源となっている。

【0011】

$$I_{ds} = 1/2 \cdot \mu (W/L) Cox (V_{gs} - |V_{th}|)^2 \dots (1)$$

ここで、VthはTFT102のしきい値、μはキャリアの移動度、Wはチャネル幅、Lはチャネル長、Coxは単位面積当たりのゲート容量、Vgsはゲート・ソース間電圧である。

【0012】

単純マトリクス型表示装置では、各発光素子は、選択された瞬間にのみ発光する。これに対して、アクティブマトリクス型表示装置では、書き込み終了後も発光素子が発光を継続する。したがって、アクティブマトリクス型表示装置は、単純マトリクス型表示装置に比べて発光素子のピーク輝度、ピーク電流を下げることができるなどの点で、とりわけ大型・高精細の表示装置では有利となる。

【0013】

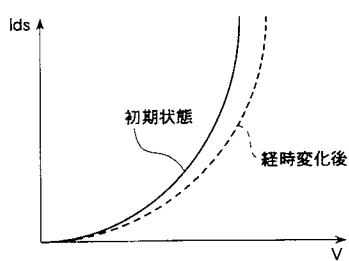

図26は、有機EL素子の電流-電圧特性(I-V特性)の経時変化を示す特性図である。図26において、実線で示す曲線が初期状態時の特性を示し、破線で示す曲線が経時変化後の特性を示している。

【0014】

一般的に、有機EL素子のI-V特性は、図26に示すように、時間が経過するにつれて劣化してしまう。ところが、図25の画素回路では、先述したように、駆動トランジスタであるTFT102による定電流駆動のために有機EL素子101には定電流が流れ続け、有機EL素子のI-V特性が劣化してもその発光輝度が低下することはない。

【0015】

ところで、図25の画素回路は、PチャネルのTFTによって構成されている。このPチャネルのTFTに代えて、NチャネルのTFTによって画素回路を構成することができれば、TFT作成において、従来のアモルファスシリコン(a-Si)プロセスを用いることができるようになるため、TFT基板の低コスト化を図ることができる。

【0016】

ここで、PチャネルのTFTをNチャネルのTFTに置き換えた画素回路について考察する。

【0017】

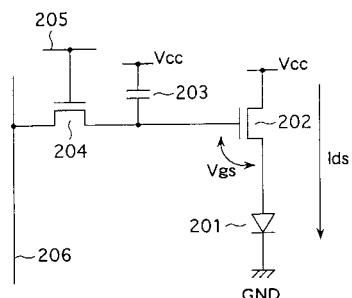

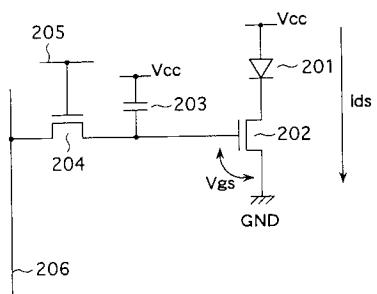

図27は、図25のPチャネルTFTをNチャネルTFTに置き換えた画素回路の構成を示す回路図である。

【0018】

この画素回路は、図27から明らかなように、例えばカソードが接地電位GNDに接続された有機EL素子201と、ソースが有機EL素子201のアノードに接続され、ドレインが正電源電位Vccに接続されたNチャネルTFT202と、このTFT202のゲ

10

20

30

40

50

ートと正電源電位  $V_{cc}$  との間に接続されたキャパシタ 203 と、ドレインが TFT 202 のゲートに、ゲートが走査線 205 に、ソースがデータ線 206 にそれぞれ接続された N チャネル TFT 204 とを有するソースフォロア回路構成となっている。

【0019】

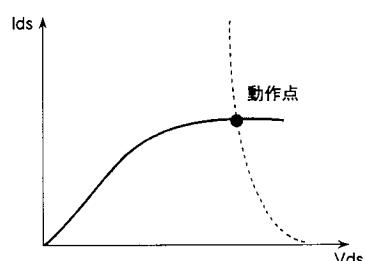

図 28 は、初期状態における駆動トランジスタとしての TFT 202 と有機 EL 素子 201 の動作点を示す図である。図 28 において、横軸は TFT 202 のドレイン・ソース間電圧  $V_{ds}$  を、横軸はドレイン・ソース間電流  $I_{ds}$  をそれぞれ示している。図 28 に示すように、ソース電圧は TFT 202 と有機 EL 素子 201 との動作点で決まり、ゲート電圧によって異なる値を持つ。この TFT 202 は飽和領域で駆動されるため、動作点のソース電圧に対したゲート・ソース間電圧  $V_{gs}$  に関して式 (1) で与えられる電流値の電流  $I_{ds}$  を流す。

10

【0020】

【特許文献 1】米国特許第 5 6 8 4 3 6 5 号明細書

【特許文献 2】特開平 8 - 2 3 4 6 8 3 号公報

【発明の開示】

【発明が解決しようとする課題】

【0021】

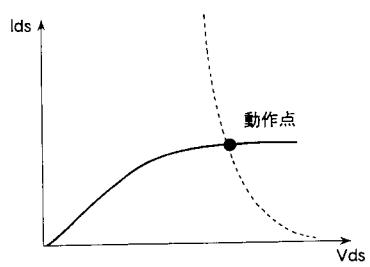

しかしながら、P チャネルの TFT を N チャネルの TFT に置き換えた画素回路においても、有機 EL 素子の I - V 特性の経時変化に伴う劣化は避けられず、これにより、図 29 に示すように、動作点が変動してしまうため、駆動トランジスタである TFT 202 に同じゲート電圧を印加したとしてもそのソース電圧は変動する。これにより、TFT 202 のゲート・ソース間電圧  $V_{gs}$  が変化してしまい、当該 TFT 202 に流れる電流値が変動する。同時に、有機 EL 素子 201 に流れる電流値も変化するため、有機 EL 素子 201 の I - V 特性が変化すると、それに伴って有機 EL 素子 201 の発光輝度も経時変化してしまう。

20

【0022】

また、図 28 の画素回路の変形例として、図 30 に示すように、有機 EL 素子 201 のアノードを正電源電位  $V_{cc}$  に接続し、駆動トランジスタとしての N チャネル TFT 202 のドレインを有機 EL 素子 201 のカソードに、ソースを接地電位 GND にそれぞれ接続する回路構成を探ることも考えられる。

30

【0023】

この変形例に係る画素回路においては、図 25 の P チャネル TFT 102 による駆動の場合と同様に、N チャネル TFT 202 はソース電位が接地電位 GND に固定され、定電流源として動作する。したがって、有機 EL 素子 201 の I - V 特性の劣化による輝度変化を防止できる。

30

【0024】

しかしながら、この変形例に係る画素回路では、駆動トランジスタである N チャネル TFT 202 を有機 EL 素子 201 のカソード側に接続する構成を探らざるを得ない。このカソード接続の構成を探るためには、有機 EL 素子に関して新規にアノード・カソードの電極の開発が必要である。このアノード・カソードの電極の開発は、現状の技術では非常に困難であるとされている。このような観点から、従来は、有機 EL 素子の I - V 特性の経時変化に伴う輝度の変化を抑えた N チャネルトランジスタによる画素回路の開発は為されていなかった。

40

【0025】

本発明は、上記課題に鑑みてなされたものであって、その目的とするところは、発光素子の電流 - 電圧特性が経時変化しても、それに伴う輝度変化のない N チャネルトランジスタによって実現可能な画素回路、当該画素回路が行列状に配置されてなる表示装置を提供することにある。

【課題を解決するための手段】

【0026】

50

上記目的を達成するために、本発明では、一端が第1の電源電位に接続された電気光学素子と、前記電気光学素子の他端と第2の電源電位との間に接続された駆動トランジスタと、前記駆動トランジスタのゲートとソースの間に接続されたキャパシタと、前記駆動トランジスタのゲートに対して輝度情報に応じた信号を選択的に取り込む第1のスイッチングトランジスタと、前記駆動トランジスタのソースと第3の電源電位との間に接続された第2のスイッチングトランジスタとを有する画素回路または当該画素回路が行列状に配置されてなる表示装置において、前記電気光学素子の前記一端側の層と前記キャパシタを形成するキャパシタ形成層とをオーバーラップさせた構成を探っている。

## 【0027】

上記構成の画素回路または当該画素回路が行列状に配置されてなる表示装置において、第2のスイッチングトランジスタをオン状態にして駆動トランジスタのソース電位を第3の電源電位に設定し、キャパシタに充電される電圧を入力電圧と第3の電源電位との差に確定させる。そして、キャパシタへの書き込みが終了した後、電気光学素子の発光期間において、第2のスイッチングトランジスタをオフ状態にすることで、電気光学素子に電流が流れ始める。このとき、駆動トランジスタが定電流源として動作することから、電気光学素子の電流・電圧特性が経時変化し、これに伴って駆動トランジスタのソース電位が変化したとしても、キャパシタによって駆動トランジスタのゲート・ソース間の電位差が一定に保たれているので、電気光学素子に流れる電流は変わらず、したがって当該電気光学素子の発光輝度も一定に保たれる。

## 【0028】

また、電気光学素子の一端側の層とキャパシタを形成するキャパシタ形成層とがオーバーラップしていることで、これらの層間に容量が形成される。その結果、当該容量の分だけ、駆動トランジスタのゲートとソースとの間の容量がオーバーラップさせない構造に比べて大きくなる。これにより、駆動トランジスタのソース電位に対するゲート電位の上昇の割合を大きくすることができるため所望の発光が得やすくなる。

## 【発明の効果】

## 【0029】

本発明によれば、電気光学素子の電流・電圧特性が経時変化し、これに伴って駆動トランジスタのソース電位が変化したとしても、電気光学素子の発光輝度を一定に保つことができ、さらに駆動トランジスタのゲートとソースとの間の容量を大きくできることで、所望の発光を得ることができ、また当該容量の増加分だけ画素容量を小さくできることにより画素サイズを縮小化できるため、表示装置の多画素化・高精細化に大きく寄与できる。

## 【発明を実施するための最良の形態】

## 【0030】

以下、本発明の実施の形態について図面を参照して詳細に説明する。

## 【0031】

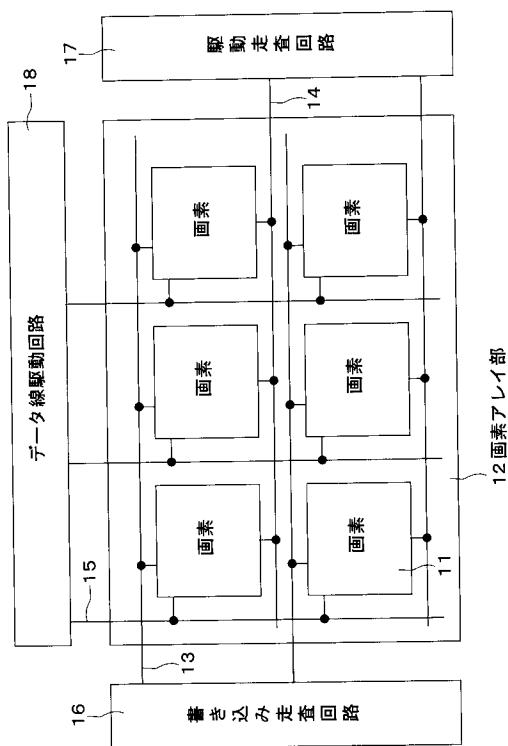

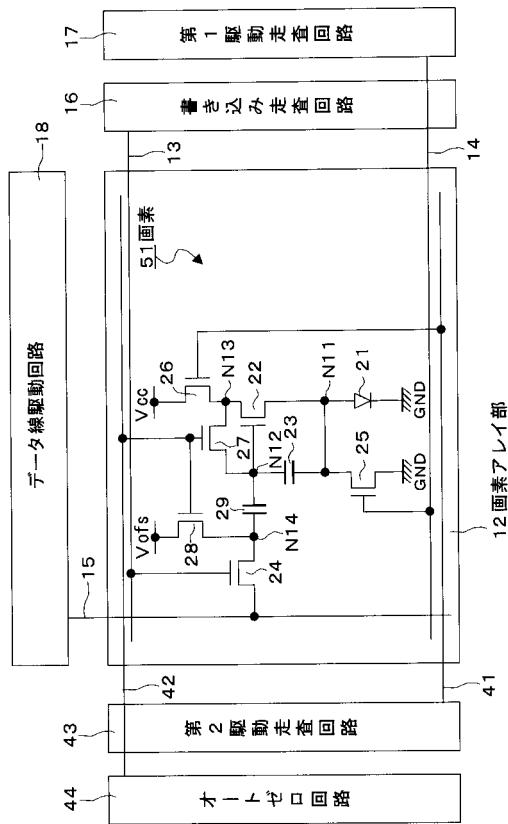

図1は、本発明が適用されるアクティブマトリクス型表示装置の構成の概略を示すプロック図である。本適用例に係るアクティブマトリクス型表示装置は、流れる電流によって輝度が変化する電気光学素子を表示素子として含む画素(画素回路)11がマトリクス状にm列n行配列されてなる画素アレイ部12を有している。ここでは、図面の簡略化のために、画素アレイ部12が3列2行の画素配列の場合を例に挙げて示している。

## 【0032】

この画素アレイ部12において、画素12の各々に対して各行毎に走査線13および駆動線14が配線され、また各列毎にデータ線15が配線されている。この画素アレイ部12の周囲には、走査線13を駆動する書き込み走査回路16と、駆動線14を駆動する駆動走査回路17と、輝度情報に応じたデータ信号をデータ線15に供給するデータ線駆動回路18とが配置されている。

## 【0033】

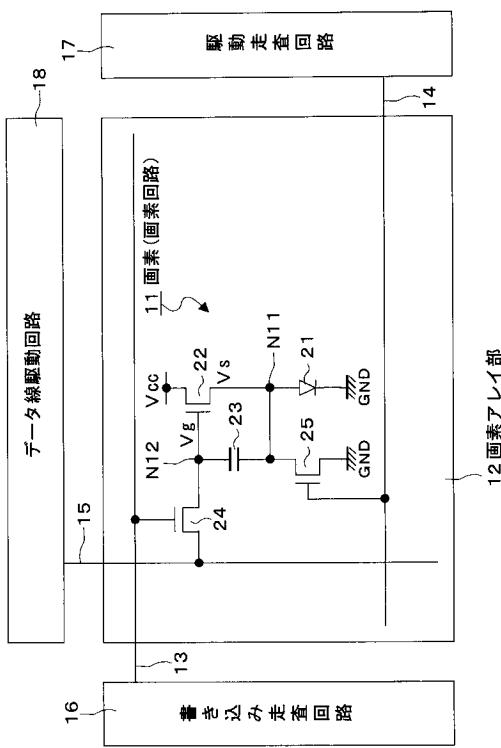

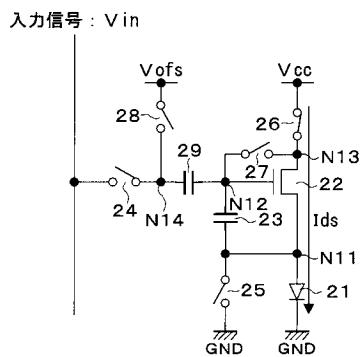

## [第1実施形態]

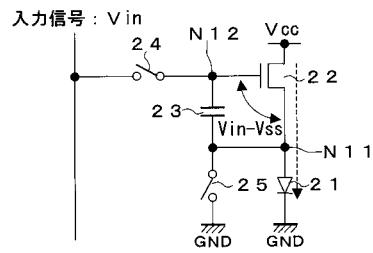

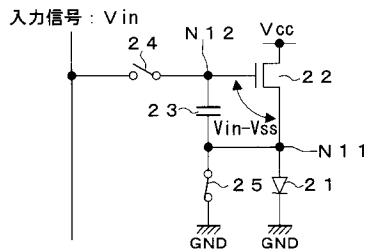

図2は、本発明の第1実施形態に係る画素回路および当該画素回路を用いたアクティブ

10

20

30

40

50

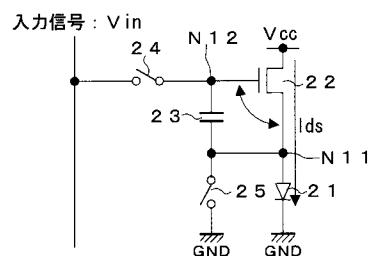

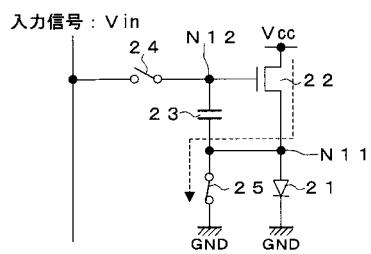

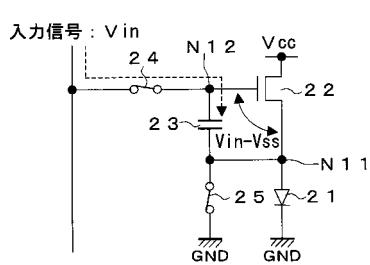

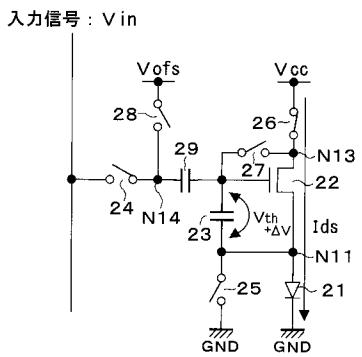

マトリクス型表示装置の構成例を示す回路図である。本実施形態に係る画素回路 1 1 は、表示素子である電気光学素子として有機 EL 素子 2 1 を用いており、当該有機 EL 素子 2 1 以外に、駆動トランジスタ 2 2 、キャパシタ（画素容量）2 3 および第 1 、第 2 のスイッチングトランジスタ 2 4 、2 5 を回路素子として有する構成となっている。駆動トランジスタ 2 2 およびスイッチングトランジスタ 2 4 、2 5 は、N チャネル電界効果トランジスタ、例えば N チャネル TFT（薄膜トランジスタ）である。以下、駆動トランジスタ 2 2 およびスイッチングトランジスタ 2 4 、2 5 を、TFT 2 2 および TFT 2 4 、2 5 と記す。

#### 【 0 0 3 4 】

図 2 において、有機 EL 素子 2 1 は、カソード電極が第 1 の電源電位（本例では、接地電位 GND）に接続されて設けられている。TFT 2 2 は、有機 EL 素子 2 1 を発光駆動する駆動トランジスタであり、ドレインが第 2 の電源電位（本例では、電源電位 Vcc）に、ソースが有機 EL 素子 2 1 のアノード電極にそれぞれ接続されてソースフォロア回路を形成している。キャパシタ 2 3 は、一端が TFT 2 2 のゲートに、他端が TFT 2 2 のソースと有機 EL 素子 2 1 のアノード電極との接続ノード N 1 1 にそれぞれ接続されている。TFT 2 4 は、ソースがデータ線 1 6 に、ゲートが走査線 1 3 に、ドレインが TFT 2 2 のゲートとキャパシタ 2 3 の一端との接続ノード N 1 2 にそれぞれ接続されている。TFT 2 5 は、ドレインが接続ノード N 1 1 に、ソースが第 3 の電源電位（本例では、接地電位 GND）にそれぞれ接続されている。

#### 【 0 0 3 5 】

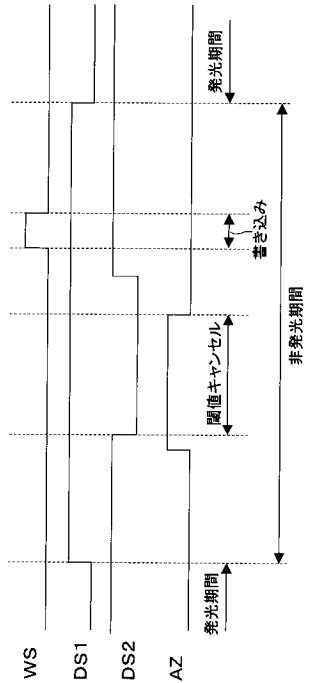

続いて、上記構成の第 1 実施形態に画素回路 1 1 を行列状に 2 次元配置してなるアクティブマトリクス型有機 EL 表示装置の回路動作について、図 3 のタイミングチャートおよび図 4 ~ 図 8 の動作説明図を用いて説明する。

#### 【 0 0 3 6 】

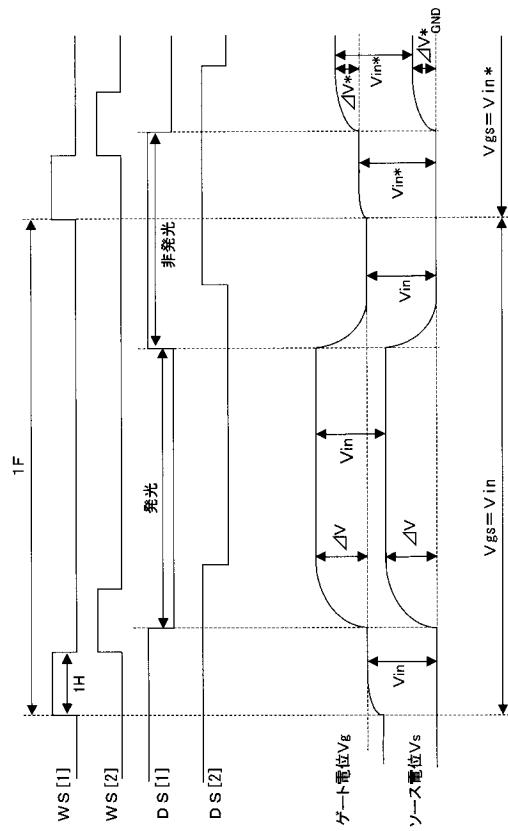

図 3 には、連続する 2 行の画素回路 1 1 を駆動する際に、書き込み走査回路 1 6 から走査線 1 3 を介して画素回路 1 1 に与えられる書き込み信号 WS [ 1 ] 、WS [ 2 ] 、駆動走査回路 1 7 から駆動線 1 4 を介して画素回路 1 1 に与えられる駆動信号 DS [ 1 ] 、DS [ 2 ] ならびに TFT 2 2 のゲート電位 Vg およびソース電位 Vs（図 2 を参照）の 1 フィールド（1F）期間におけるタイミング関係を示している。また、図 4 ~ 図 8 の動作説明図では、TFT 2 2 、2 4 、2 5 についてはスイッチのシンボルを用いて図示するものとする。

#### 【 0 0 3 7 】

通常の発光状態では、書き込み走査回路 1 6 および駆動走査回路 1 7 からそれぞれ出力される書き込み信号 WS および駆動信号 DS がほぼ接地電位 GND（以下、「“ L ” レベル」と記す）にあるため、図 4 に示すように、TFT 2 4 、2 5 はオフした状態にある。このとき、駆動トランジスタである TFT 2 2 は、飽和領域で動作するよう設計されている。すなわち、TFT 2 2 は定電流源として動作する。

#### 【 0 0 3 8 】

次に、TFT 2 4 がオフした状態で駆動走査回路 1 7 から出力される駆動信号 DS がほぼ電源電位 Vcc（以下、「“ H ” レベル」と記す）になることで、TFT 2 5 がオン状態となる。このとき、図 5 に示すように、TFT 2 5 を介して電流が流れるため、TFT 2 2 のソース電位 Vs が接地電位 GND まで下降する。これにより、有機 EL 素子 2 1 が非発光状態となる。

#### 【 0 0 3 9 】

次に、TFT 2 5 がオンした状態で書き込み走査回路 1 6 から出力される書き込み信号 WS が 1 水平走査期間（1H）に亘って “ H ” レベルになることで、図 6 に示すように、TFT 2 4 がオン状態となって入力信号電圧 Vin をキャパシタ 2 3 に書き込む。このとき、TFT 2 2 のソース電位 Vs が接地電位 GND (0[V]) にあるため、TFT 2 2 のゲート - ソース間の電位差が Vin となり、この電位差 Vin がキャパシタ 2 3 に書き込まれる。

10

20

30

40

50

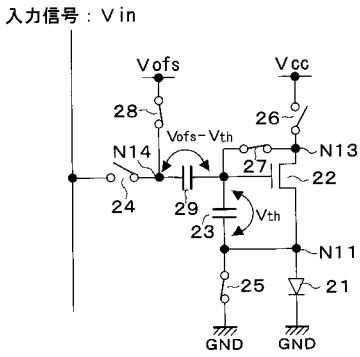

## 【0040】

その後、書き込み信号WSが“L”レベルとなり、図7に示すように、TFT24がオフ状態になることで、キャパシタ23への入力信号電圧Vinの書き込みが終了する。そして、駆動走査回路17から出力される駆動信号DSが“L”レベルとなることで、図8に示すように、TFT25がオフ状態となる。これにより、TFT22のソース電位Vsが上昇し、有機EL素子21に電流が流れる。

## 【0041】

TFT22のソース電位Vsが変動するにも拘わらず、TFT22のゲート・ソース間にはキャパシタ23が接続されていることから、ソース電位Vsの上昇に対してゲート電位Vgの上昇を高い割合で追従させることができるために、TFT22のゲート・ソース間の電位差は常にほぼVinに保たれる。ソース電位Vsの上昇に対するゲート電位Vgの上昇の割合(ゲイン)は、キャパシタ23の容量値で決定される。

10

## 【0042】

このとき、TFT22が飽和領域で動作しているため、このTFT22に流れる電流値Idsは、ゲート・ソース間の電位差Vinによって決められる。この電流値Idsは有機EL素子21にも同様に流れるため、当該有機EL素子21は発光する。このとき、接続ノードN11の電位は、有機EL素子21に電流Idsが流れる際のTFT22のゲート電位まで上昇する。このゲート電位の上昇に伴い、キャパシタ23を介して接続ノードN12の電位も同様に上昇する。これにより、前述した通り、TFT22のゲート・ソース間の電位差はほぼVinに保たれる。

20

## 【0043】

ここで、上述したように、NチャネルTFTを用いたソースフォロア回路構成の画素回路11において、駆動トランジスタであるTFT22のゲート・ソース間にキャパシタ23を接続するとともに、TFT22のソースをスイッチングトランジスタであるTFT25を介して固定電位(本例では、接地電位GND)に選択的に接続するようにした構成を採ることによる作用効果について説明する。

20

## 【0044】

入力電圧Vinをキャパシタ23に書き込む時間に、TFT25をオン状態にしてTFT22のソース電位Vsを接地電位GNDに設定し、キャパシタ23に充電される電圧をほぼVinに確定させる。キャパシタ23への書き込み終了後、有機EL素子21の発光期間において、TFT25をオフ状態にすることで、有機EL素子21に電流が流れ始める。このとき、TFT22のゲート・ソース間にはキャパシタ23が存在するため、TFT22のソース電位Vsの変動に拘わらず、TFT22のゲート・ソース間の電位差は常にほぼVinである。

30

## 【0045】

また、TFT22が定電流源として動作することから、有機EL素子21のI-V特性が経時変化し、これに伴ってTFT22のソース電位Vsが変化したとしても、キャパシタ23によってTFT22のゲート・ソース間電位Vgsが一定(Vin)に保たれているため、有機EL素子21に流れる電流は変わらず、したがって当該有機EL素子21の発光輝度も一定に保たれる。以下、この輝度補正のための動作をブートストラップ動作と呼ぶこととする。このブートストラップ動作により、有機EL素子21のI-V特性が経時的に変化しても、それに伴う輝度劣化のない画像表示が可能になる。

40

## 【0046】

また、Nチャネルトランジスタを用いたソースフォロア回路によって画素回路を構成することができるために、現状のアノード・カソード電極の有機EL素子をそのまま用いても、当該有機EL素子の駆動が可能になる。しかも、Nチャネルのみのトランジスタを用いて画素回路を構成することができ、TFT作成においてもアモルファスシリコン(a-Si)プロセスを用いることができるようになるため、TFT基板の低コスト化が図れることになる。

## 【0047】

50

ところで、TFT25をオフして有機EL素子21に一定電流を流したとき、TFT22のソース電位Vsが変化量Vだけ上昇したとすると、これに合わせてTFT22のゲート電位Vgsは、下記の式(2)で表される値Vx0だけ上昇する。

$$Vx0 = (C + Cgs) \times V / (C + Cg + Cgs) \dots \dots (2)$$

式(2)において、Cはキャパシタ23の容量(値)、CgsはTFT22のゲート・ソース間容量、CgはTFT24の寄生容量である。

#### 【0048】

ここで、キャパシタ23の容量CとTFT22のゲート・ソース間容量Cgsとの和、即ち接続ノードN11と接続ノード12との間の容量が、TFT24の寄生容量Cgよりも大きければ、TFT22のゲート・ソース間電位Vgsは入力信号電位Vinを保ったまま変動する。しかし、接続ノードN11と接続ノード12との間の容量がTFT24の寄生容量Cgと同程度、もしくは当該寄生容量Cgよりも小さければ、TFT22のソース電位Vsの変化量Vによってゲート・ソース間電位Vgsの値が変化してしまい、所望の発光が望めないことになる。

#### 【0049】

すなわち、表示装置の多画素化・高精細化が進むにつれて画素サイズが小さくなり、それに伴ってキャパシタ23の面積を小さくせざるを得なく、また表示装置の大型化が進めば大きなトランジスタを使用する必要があるため、トランジスタの寄生容量が大きくなってしまい、やはりキャパシタ23の面積を大きくとれなくなり、キャパシタ23の容量CとTFT22のゲート・ソース間容量Cgsとの和がTFT24の寄生容量Cgよりも小さくなる状況が発生する。その結果、ソース電位Vsの変化量Vによってゲート・ソース間電位Vgsの値が変化してしまうのである。

#### 【0050】

そこで、本実施形態に係る画素回路11では、レイアウト上において、有機EL素子21のアノード電極層とキャパシタ23を形成する層(以下、「キャパシタ形成層」と記す)とをオーバーラップさせた構造を採用することを特徴としている。以下に、この特徴部分についてより具体的に説明する。

#### 【0051】

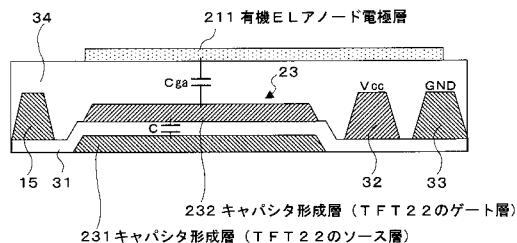

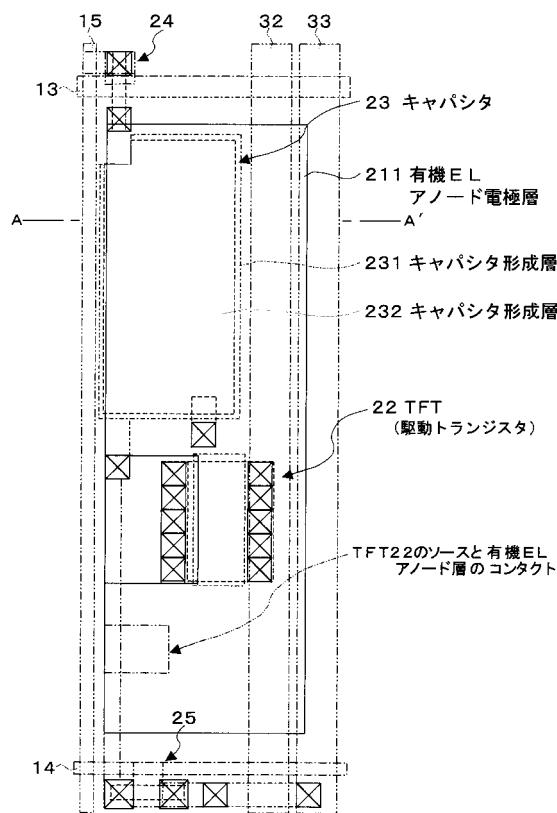

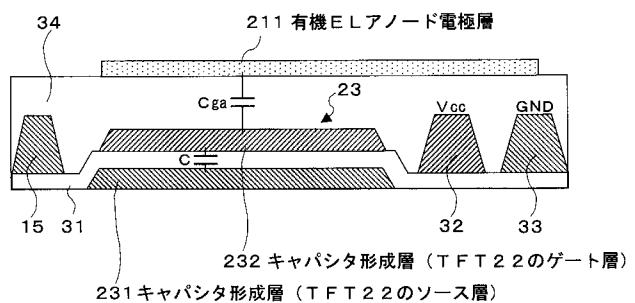

図9は、第1実施形態に係る画素回路11のレイアウトの一例を示す概略平面パターン図である。また、図10に、図9のA-A線に沿った断面構造を示す。因みに、図9、図10には図示していないが、有機EL素子21は、透明導電膜からなるアノード電極層の上に正孔輸送層、発光層、電子輸送層および電子注入層を順次堆積させて有機層を形成し、この有機層の上にカソード電極層を形成した構造となっている。

#### 【0052】

図9、図10に示すように、図示せぬ基板上に、キャパシタ23が絶縁層31を挟んで形成されるとともに、当該絶縁層31上にデータ線15、電源電位Vccを与える電源線32および接地電位GNDを与える接地線33が一定の間隔を置いて平行に配線され、その上にさらに絶縁層34を介して有機EL素子21のアノード電極層211が画素エリアの大部分に亘って形成されている。

#### 【0053】

キャパシタ23は、TFT(駆動トランジスタ)22のソース層でもあるキャパシタ形成層231と当該TFT22のゲート層でもあるキャパシタ形成層232とが絶縁層31を挟んで対向配置されて形成されている。このキャパシタ23は、キャパシタ形成層232(これと対向配置されているキャパシタ形成層231も同じ)が、有機EL素子21のアノード電極層211とオーバーラップするように、好ましくはキャパシタ形成層232の全体がアノード電極層211とオーバーラップするように形成されている。

#### 【0054】

なお、図9において、有機EL素子21のアノード電極層211を含む層を実線で、キャパシタ形成層231、走査線13および駆動線14等の配線を含む層を一点鎖線で、キャパシタ形成層232を含む層を点線で、データ線15、電源線32および接地線33等

10

20

30

40

50

の配線層を二点鎖線でそれぞれ示している。

【0055】

このように、駆動トランジスタであるTFT22のゲート・ソース間にキャパシタ23を接続するとともに、TFT22のソースをスイッチングトランジスタであるTFT25を介して固定電位（本例では、接地電位GND）に選択的に接続する構成の画素回路11において、レイアウト上、有機EL素子21のアノード電極層211とキャパシタ23を形成するキャパシタ形成層231, 232とをオーバーラップさせた構造とすることにより、次のような作用効果を得ることができる。

【0056】

すなわち、有機EL素子21のアノード電極層211とキャパシタ形成層231, 232とをオーバーラップさせることで、アノード電極層211とキャパシタ形成層232との間にも容量Cgaが形成されるため、接続ノードN11と接続ノード12との間の容量は、キャパシタ23の容量CとTFT22のゲート・ソース間容量Cgsとアノード電極層211とキャパシタ形成層232との間の容量Cgaとの和となる。すなわち、接続ノードN11と接続ノード12との間の容量を容量Cgaの分だけ大きくできる。

【0057】

この画素回路11において、TFT25をオフして有機EL素子21に定電流を流したときに、TFT22のソース電位Vsが変化量Vだけ上昇し、これに合わせてTFT2のゲート電位Vgが下記の式（3）で表される値Vx1だけ上昇する。

$$Vx1 = (C + Cgs + Cga) \times V \\ / (C + Cg + Cgs + Cga) \quad \dots \dots (3)$$

【0058】

上記の式（3）と先の式（2）との対比から明らかなように、有機EL素子21のアノード電極層211とキャパシタ23を形成するキャパシタ形成層231, 232とをオーバーラップさせた構造を採った場合におけるTFT22のゲート電位Vgの変化量Vx1は、オーバーラップさせない構造を採った場合における変化量Vx0と比較して大きくなる。すなわち、有機EL素子21のアノード電極層211とキャパシタ形成層231, 232とをオーバーラップさせた構造を採ることにより、オーバーラップさせない構造に比較して、接続ノードN11と接続ノード12との間の容量を容量Cgaの分だけ大きくできるため、TFT22のソース電位Vsに対するゲート電位Vgの上昇の割合（ゲイン）を大きくすることができ、その結果所望の発光が得やすくなる。

【0059】

また逆に、接続ノードN11と接続ノード12との間の容量を容量Cgaの分だけ大きくできるということは、画素回路11の特性を有機EL素子21のアノード電極層211とキャパシタ形成層231, 232とをオーバーラップさせない構造のものと同じで良いとした場合には、キャパシタ23の容量Cが容量Cgaの分だけ小さくて良いということを意味するため、その分だけキャパシタ23のサイズを小さくとることができる。これにより、画素サイズを小さくできるため、表示装置の多画素化・高精細化に大きく寄与できることになる。

【0060】

[第2実施形態]

図11は、本発明の第2実施形態に係る画素回路および当該画素回路を用いたアクティブラトリクス型表示装置の構成例を示す回路図であり、図中、図2と同等部分には同一符号を付して示している。

【0061】

図11において、画素アレイ部12には、走査線13および第1駆動線14に加えて、第2駆動線41およびオートゼロ線42が各行毎に配線されている。そして、第2駆動線41およびオートゼロ線42を駆動する第2駆動走査回路43およびオートゼロ回路44が画素アレイ部12の周囲に配置されている。本例では、書き込み走査回路16および第1駆動走査回路17が画素アレイ部12の一方側に配置され、その反対側に第2駆動走査

10

20

30

40

50

回路43およびオートゼロ回路44を配置された構成となっている。

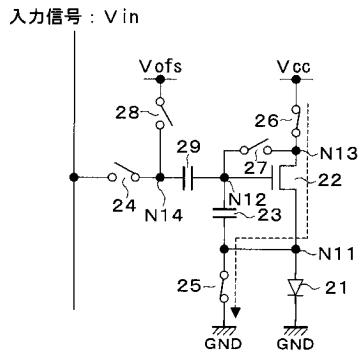

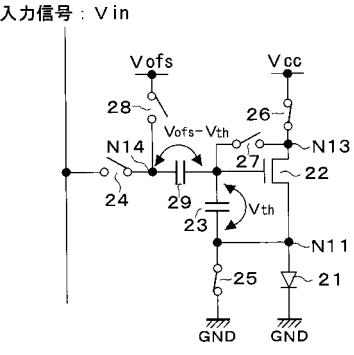

【0062】

本実施形態に係る画素回路51は、第1実施形態に係る画素回路11の構成に加えて、例えばNチャネルのTFT26～28およびキャパシタ29を有する構成となっている。TFT26は、ドレインが電源電位Vccに、ソースがTFT22のドレインに、ゲートが第2駆動線41にそれぞれ接続されている。TFT27は、ドレインがTFT22のドレインとTFT26のソースとの接続ノードN13に、ソースが接続ノードN12に、ゲートがオートゼロ線42にそれぞれ接続されている。TFT28は、ドレインが所定電位Vofsに、ソースがTFT24のドレインに、ゲートがオートゼロ線42にそれぞれ接続されている。キャパシタ29は、一端がTFT24のドレインとTFT28のソースとの接続ノード24に、他端が接続ノードN12にそれぞれ接続されている。

10

【0063】

続いて、上記構成の第2実施形態に係る画素回路51を行列状に2次元配置してなるアクティブマトリクス型有機EL表示装置の回路動作について、図12のタイミングチャートおよび図13～図18の動作説明図を用いて説明する。

【0064】

図12には、ある行の画素回路51を駆動する際に、書き込み走査回路16から走査線13を介して画素回路51に与えられる書き込み信号WS、駆動走査回路17, 43から駆動線14, 41を介して画素回路51に与えられる駆動信号DS1, 2およびオートゼロ回路44からオートゼロ線42を介して画素回路51に与えられるオートゼロ信号AZのタイミング関係を示している。また、図13～図18の動作説明図では、TFT22, 24～28についてはスイッチのシンボルを用いて図示するものとする。

20

【0065】

通常の発光状態では、書き込み走査回路16から出力される書き込み信号WS、駆動走査回路17から出力される駆動信号DS1およびオートゼロ回路44から出力されるオートゼロ信号AZが“L”レベルにあり、駆動走査回路43から出力される駆動信号DS2が“H”レベルにあるため、図13に示すように、TFT24, 25, 27, 28はオフした状態にあり、TFT26がオンした状態にある。このとき、駆動トランジスタであるTFT22は、飽和領域で動作するように設計されている。したがって、TFT22は定電流源として動作し、有機EL素子21に一定電流Idsを供給する。

30

【0066】

次に、TFT24, 27, 28がオフし、TFT26がオンした状態で駆動走査回路17から出力される駆動信号DSが“H”レベルになることで、TFT25がオン状態となる。このとき、図14に示すように、TFT25を介して電流が流れるため、TFT22のソース電位Vsが接地電位GNDまで下降する。これにより、有機EL素子21が非発光状態となる。

【0067】

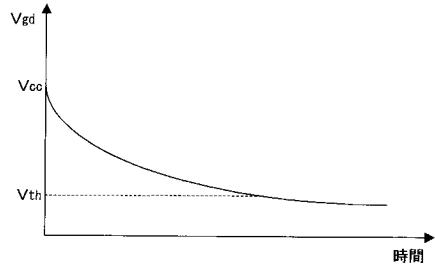

次に、有機EL素子21の非発光期間において、TFT24がオフし、TFT25, 26がオンした状態でオートゼロ回路44から出力されるオートゼロ信号AZが“H”レベルとなることで、TFT27, 28がオン状態となり、TFT22の閾値電圧Vthをキャンセル（補正）する閾値キャンセル期間に入る。その後、駆動走査回路43から出力される駆動信号DS2が“L”レベルになることで、図15に示すように、TFT26がオフ状態となる。このとき、TFT22は、ゲートとドレインがTFT27を介して接続されているため飽和領域で動作する。

40

【0068】

また、TFT22のゲートには、キャパシタ23, 29が並列に接続されているため、TFT22のゲート・ドレイン間電位Vgdは、図19に示すように、時間が経過するにつれて緩やかに減少してゆく。そして、一定期間が経過した後、TFT22のゲート・ソース間電位VgsはTFT22の閾値電圧Vthとなる。このとき、キャパシタ29には(Vofs - Vth)の電圧が、キャパシタ23にはVthの電圧がそれぞれ充電される

50

ことになる。

【0069】

次に、TFT24, 26がオフし、TFT25がオンした状態でオートゼロ回路44から出力されるオートゼロ信号AZが“H”レベルから“L”レベルに遷移することで、TFT27, 28がオフ状態となり、閾値キャンセル期間の終了となる。閾値キャンセル期間の経過後、駆動走査回路43から出力される駆動信号DS2が“L”レベルから“H”レベルに遷移することで、図16に示すように、TFT26がオン状態となる。これにより、TFT22のドレイン電位Vdが電源電位Vccとなる。

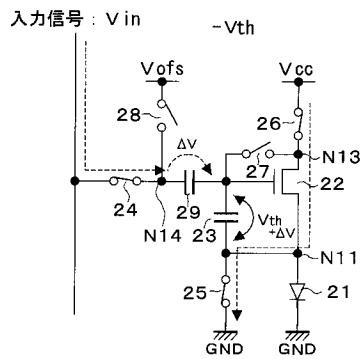

【0070】

次に、TFT24, 27, 28がオフし、TFT25, 26がオンした状態で書き込み走査回路16から出力される書き込み信号WSが“H”レベルになることで、入力信号電圧Vinの書き込み期間となる。この書き込み期間では、図17に示すように、TFT24がオン状態となる。これにより、TFT24は、データ線15を通して供給される入力信号電圧Vinを取り込むことで、接続ノードN14の電圧変化量Vを、キャパシタ29を介してTFT22のゲートにカップリングさせる。

【0071】

このとき、TFT22のゲート電位Vgは閾値電圧Vthという値であり、カップリング量Vはキャパシタ23の容量C1、キャパシタ29の容量C2およびTFT22の寄生容量C3によって下記の式(4)のように決定される。

$$V = \{ C_2 / (C_1 + C_2 + C_3) \} \cdot (V_{in} - V_{off}) \dots (4)$$

【0072】

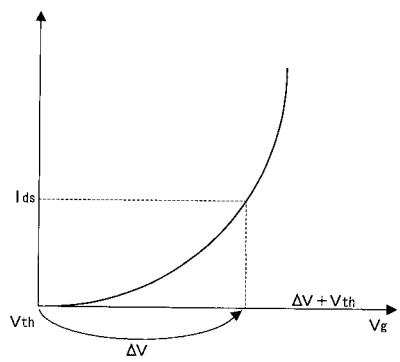

したがって、キャパシタ23, 29の容量C1, C2をTFT22の寄生容量C3に比べて十分大きく設定すれば、TFT22のゲートへのカップリング量Vは、キャパシタ23, 29の容量C1, C2のみによって決定される。TFT22は、飽和領域で動作するよう設計させているため、図20に示すように、ゲートへのカップリング量Vに応じた一定電流Idsを流す。この電流Idsは、図17に点線で示すように、TFT25を通って流れる。

【0073】

書き込み期間の終了後、TFT24, 27, 28がオフし、TFT26がオンした状態で駆動走査回路17から出力される駆動信号DS1が“L”レベルになることで、図18に示すように、TFT25がオフ状態となる。このとき、TFT25がオフしても、TFT22は、ゲート・ソース間電位Vgsが一定であるため一定電流Idsを有機EL素子21に流す。これにより、有機EL素子21が発光する。

【0074】

ここで、本実施形態に係る画素回路51においても、有機EL素子21は発光時間が長くなるとそのI-V特性が変化してしまう。そのため、接続ノードN11の電位も変化する。しかしながら、TFT22のゲート・ソース間電位Vgsが一定値に保たれているため、有機EL素子21に流れる電流は変化しない。したがって、有機EL素子21のI-V特性が劣化しても、一定電流Idsが常に流れ続けるため、有機EL素子21の輝度が変化することはない。また、閾値キャンセル期間におけるTFT27の作用により、TFT22の閾値電圧Vthをキャンセルし、当該閾値電圧Vthのバラツキの影響を受けない一定電流Idsを流すことができるため、高画質の画像を得ることができる。

【0075】

なお、上述した動作説明では、TFT26をオンさせてからTFT24をオンさせて書き込み期間を設定するタイミング関係としたが、TFT24をオフさせ、書き込み期間の終了後にTFT26をオンさせるタイミング関係とすることも可能である。ただし、TFT24をオフさせてからTFT26をオンさせると、TFT22は線形領域から飽和領域へと動作する。トランジスタは、線形領域よりも飽和領域の方が、チャネル長が長くなるためTFT22の寄生容量C3は小さい。

【0076】

10

20

30

40

50

したがって、TFT26をオンさせてからTFT24をオンさせるタイミング関係の方が、TFT24をオフさせてからTFT26をオンさせるタイミング関係よりも、TFT22の寄生容量C3を小さくすることができる。寄生容量C3を小さくすることができれば、TFT26をオンした際に、TFT22のドレインからゲートへのカップリング量を小さくすることができ、かつキャパシタ23, 29の容量C1, C2を寄生容量C3に比べて十分大きくとることができるので、TFT24をオンしたときの接続ノードN14の電位変化量が、容量C1, C2の大きさに応じてTFT22のゲートへカップリングされるようになる。

## 【0077】

上記構成の閾値キャンセル機能を持つ画素回路51において、TFT25をオフして有機EL素子21に一定電流を流したとき、TFT22のソース電位Vsが変化量Vだけ上昇したとすると、これに合わせてTFT22のゲート電位Vgは、下記の式(5)で表される値Vx2だけ上昇する。

## 【0078】

## 【数1】

$$V_{x2} = \frac{(C_1 + C_{gs}) \times \Delta V}{(C_1 + C_{gs} + \frac{1}{\frac{1}{C_2} + \frac{1}{C_{t1} + C_{t2}}})} \quad \dots\dots (5)$$

10

20

## 【0079】

式(4)において、C1はキャパシタ23の容量(値)、C2はキャパシタ29の容量、CgsはTFT22のゲート・ソース間容量、Ct1はTFT24の寄生容量、Ct2はTFT28の寄生容量である。

## 【0080】

この画素回路51においても、キャパシタ23の容量C1とTFT22のゲート・ソース間容量Cgsとの和、即ち接続ノードN11と接続ノード12との間の容量が、TFT24, 28, 27の寄生容量Ct1, Ct2, Ct3よりも大きければ、TFT22のゲート・ソース間電位Vgsは入力信号電位Vinを保ったまま変動するが、そうでなければTFT22のソース電位Vsの変化量Vによってゲート・ソース間電位Vgsの値が変化してしまい、所望の発光が望めないことになる。キャパシタ23の容量C1を大きくとることができない理由は先述した通りである。

30

## 【0081】

そこで、本実施形態に係る画素回路51においても、レイアウト上において、有機EL素子21のアノード電極層とキャパシタ23を形成するキャパシタ形成層とをオーバーラップさせた構造を探るようにしている。

## 【0082】

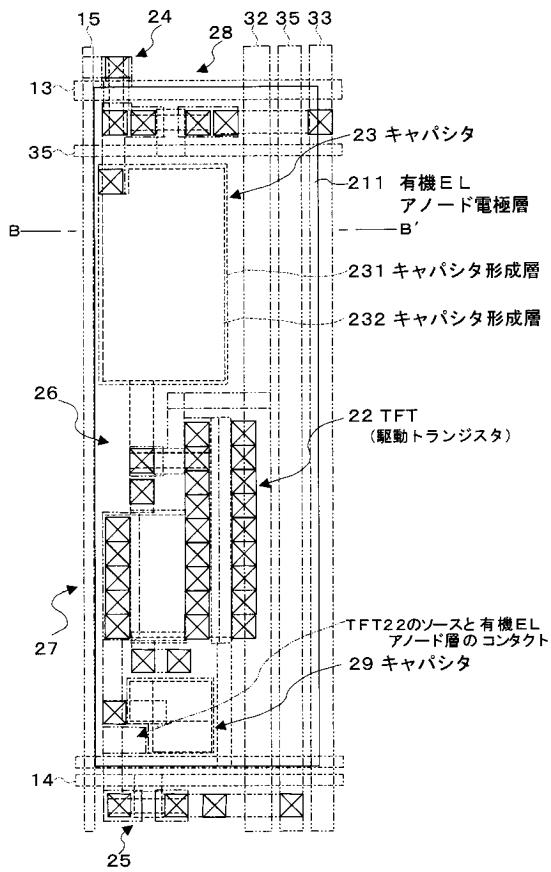

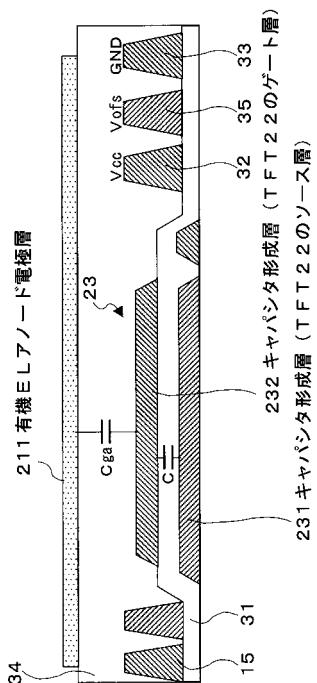

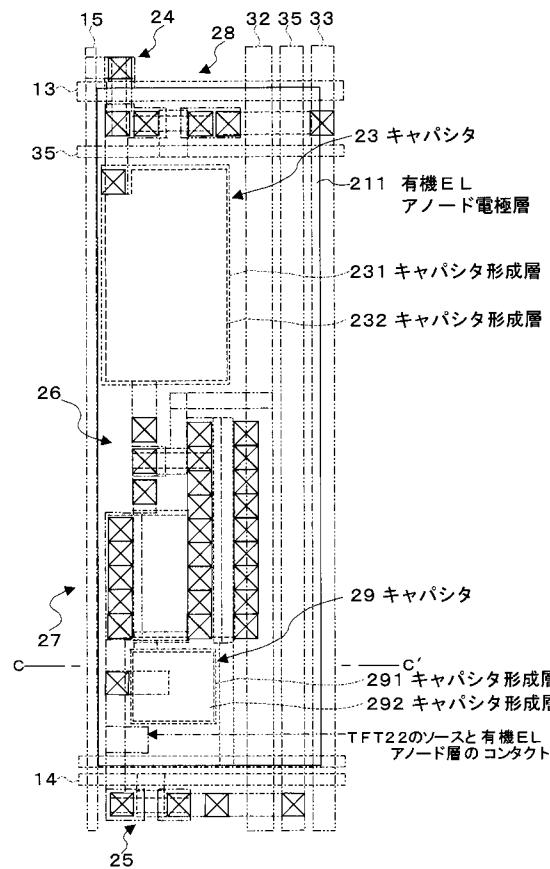

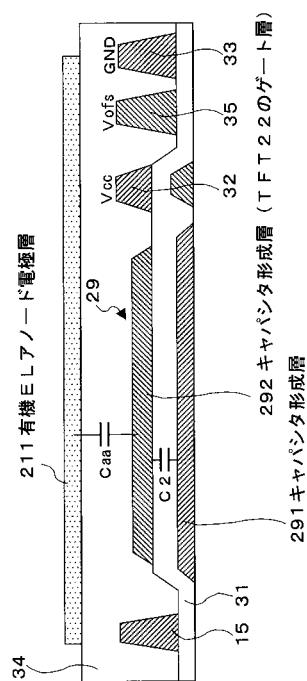

図21は、第1実施形態に係る画素回路51のレイアウトの一例を示す概略平面パターン図である。また、図22に、図20のB-B線に沿った断面構造を示す。図21、図22において、図9、図10と同等部分には同一符号を付して示している。

40

## 【0083】

図21および図22に示すように、図示せぬ基板上に、キャパシタ23が絶縁層31を挟んで形成されるとともに、当該絶縁層31上にデータ線15、電源電位Vccを与える電源線32、オートゼロ信号Vofsを与えるオートゼロ線35および接地電位GNDを与える接地線33が一定の間隔を置いて平行に配線され、その上にさらに絶縁層34を介して有機EL素子21のアノード電極層211が画素エリアの大部分に亘って形成されている。

## 【0084】

50

キャパシタ23は、TFT(駆動トランジスタ)22のソース層でもあるキャパシタ形成層231と当該TFT22のゲート層でもあるキャパシタ形成層232とが絶縁層31を挟んで対向配置されて形成されている。このキャパシタ23は、キャパシタ形成層232(これと対向配置されているキャパシタ形成層231も同じ)が、有機EL素子21のアノード電極層211とオーバーラップするように、好ましくはキャパシタ形成層232の全体がアノード電極層211とオーバーラップするように形成されている。

## 【0085】

なお、図21において、有機EL素子21のアノード電極層211を含む層を実線で、キャパシタ形成層231、走査線13および駆動線14等の配線を含む層を一点鎖線で、キャパシタ形成層232を含む層を点線で、データ線15、電源線32、接地線32およびオートゼロ線35等の配線層を二点鎖線でそれぞれ示している。

## 【0086】

このように、閾値キャンセル機能を有する画素回路51において、レイアウト上、有機EL素子21のアノード電極層211とキャパシタ23を形成するキャパシタ形成層231、232とをオーバーラップさせた構造とすることにより、第1実施形態に係る画素回路11の場合と同様の理由により、接続ノードN11と接続ノード12との間の容量を容量Cgaの分だけ大きくできる。

## 【0087】

この画素回路51において、TFT25をオフして有機EL素子21に定電流を流したときに、TFT22のソース電位Vsが変化量Vだけ上昇し、これに合わせてTFT22のゲート電位Vgが下記の式(6)で表される値Vx3だけ上昇する。

## 【0088】

## 【数2】

$$V_{x3} = \frac{(C_1 + C_{gs} + C_{ga}) \times \Delta V}{(C_1 + C_{gs} + C_{ga} + \frac{1}{\frac{1}{C_2} + \frac{1}{C_{t1} + C_{t2}}})} \quad \dots \dots (6)$$

## 【0089】

上記の式(6)と先の式(5)との対比から明らかなように、有機EL素子21のアノード電極層211とキャパシタ形成層231、232とをオーバーラップさせた構造を探ることにより、オーバーラップさせない構造に比較して、接続ノードN11と接続ノード12との間の容量を容量Cgaの分だけ大きくできるため、TFT22のソース電位Vsに対するゲート電位Vgの上昇の割合(ゲイン)を大きくすることができ、その結果所望の発光が得やすくなる。また、キャパシタ23のサイズを小さくとることができるために、表示装置の多画素化・高精細化に大きく寄与できることになる。

## 【0090】

## (第2実施形態の応用例)

上記実施形態では、レイアウト上において、有機EL素子21のアノード電極層とキャパシタ23のキャパシタ形成層とをオーバーラップさせた構成を探るとしたが、さらにキャパシタ29のキャパシタ形成層についても有機EL素子21のアノード電極層とオーバーラップさせた構成を探ることも可能である。

## 【0091】

図23は、第1実施形態に係る画素回路51のレイアウトの一例を示す概略平面パターン図である。また、図24に、図23のC-C線に沿った断面構造を示す。図23、図24において、図21、図22と同等部分には同一符号を付して示している。

## 【0092】

特に図24から明らかなように、キャパシタ29は、キャパシタ形成層291とTFT22のゲート層でもあるキャパシタ形成層292とが絶縁層31を挟んで対向配置されて

形成されている。このキャパシタ29は、キャパシタ形成層292（これと対向配置されているキャパシタ形成層291も同じ）が、有機EL素子21のアノード電極層211とオーバーラップするように、好ましくはキャパシタ形成層292の全体がアノード電極層211とオーバーラップするように形成されている。

【0093】

このように、閾値キャンセル機能を有する画素回路51において、レイアウト上、有機EL素子21のアノード電極層211とキャパシタ23を形成するキャパシタ形成層231, 232とをオーバーラップさせるとともに、キャパシタ29のキャパシタ形成層291, 292についても有機EL素子21のアノード電極層とオーバーラップさせた構造とすることにより、有機EL素子21のアノード電極層211とキャパシタ29のキャパシタ形成層292との間に容量Caaが形成されるため、接続ノードN11と接続ノード12との間の容量を容量Cgaの分だけ大きくできることに加えて、容量Caaの分だけ大きくできる。

【0094】

この画素回路51において、TFT25をオフして有機EL素子21に定電流を流したときに、TFT22のソース電位Vsが変化量Vだけ上昇し、これに合わせてTFT22のゲート電位Vgが下記の式（7）で表される値Vx4だけ上昇する。

【0095】

【数3】

$$V_{x4} = \frac{(C_1 + C_{gs} + \frac{1}{C_2} + \frac{1}{C_{aa}}) \times \Delta V}{(C_1 + C_{gs} + C_{ga} + \frac{1}{C_2} + \frac{1}{C_{t1} + C_{t2}} + \frac{1}{C_2} + \frac{1}{C_{aa}})} \dots (7)$$

20

【0096】

上記の式（7）と先の式（5）との対比から明らかなように、有機EL素子21のアノード電極層211と、キャパシタ23のキャパシタ形成層231, 232およびキャパシタ29のキャパシタ形成層291, 292とをオーバーラップさせた構造を採ることにより、TFT22のソース電位Vsに対するゲート電位Vgの上昇の割合（ゲイン）を大きくすることができるため、所望の発光が得やすくなるとともに、表示装置の多画素化・高精細化に大きく寄与できることに加えて、入力信号電圧Vinの電圧振幅に対するTFT22のゲート入力の電圧振幅が減少しないという作用効果を得ることができる。

【0097】

なお、上記実施形態では、第1, 第3の電源電位を接地電位GND、第2の電源電位を正電源電位とした画素回路を例に挙げて説明したが、この電位関係に限られるものではなく、例えば第1の電源電位を負電源電位、第2の電源電位を接地電位GNDとしり、第3の電源電位を正電位に設定した画素回路にも同様に適用可能である。

【0098】

また、上記実施形態では、画素の表示素子として、有機EL素子を用いた有機EL表示装置に適用した場合を例に挙げて説明したが、これに限られるものではなく、流れる電流によって輝度が変化する電気光学素子を画素の表示素子として用いた表示装置全般に適用可能である。

【図面の簡単な説明】

【0099】

【図1】本発明が適用されるアクティブマトリクス型表示装置の構成の概略を示すプロック図である。

【図2】本発明の第1実施形態に係る画素回路の構成例を示す回路図である。

30

40

50

【図3】第1実施形態に係る画素回路の動作を説明するためのタイミングチャートである。

【図4】第1実施形態に係る画素回路の動作説明図（その1）である。

【図5】第1実施形態に係る画素回路の動作説明図（その2）である。

【図6】第1実施形態に係る画素回路の動作説明図（その3）である。

【図7】第1実施形態に係る画素回路の動作説明図（その4）である。

【図8】第1実施形態に係る画素回路の動作説明図（その5）である。

【図9】第1実施形態に係る画素回路のレイアウトの一例を示す概略平面パターン図である。

【図10】図9のA-A線に沿った断面構造図である。

10

【図11】本発明の第2実施形態に係る画素回路の構成例を示す回路図である。

【図12】第2実施形態に係る画素回路の動作を説明するためのタイミングチャートである。

【図13】第2実施形態に係る画素回路の動作説明図（その1）である。

【図14】第2実施形態に係る画素回路の動作説明図（その2）である。

【図15】第2実施形態に係る画素回路の動作説明図（その3）である。

【図16】第2実施形態に係る画素回路の動作説明図（その4）である。

【図17】第2実施形態に係る画素回路の動作説明図（その5）である。

【図18】第2実施形態に係る画素回路の動作説明図（その6）である。

【図19】第2実施形態に係る画素回路の動作説明に供する特性図である。

20

【図20】第2実施形態に係る画素回路の動作説明に供する特性図である。

【図21】第2実施形態に係る画素回路のレイアウトの一例を示す概略平面パターン図である。

【図22】図21のB-B線に沿った断面構造図である。

【図23】第2実施形態の応用例に係る画素回路のレイアウトの一例を示す概略平面パターン図である。

【図24】図23のC-C線に沿った断面構造図である。

【図25】従来例に係る画素回路を示す回路図である。

【図26】有機EL素子のI-V特性の経時変化を示す特性図である

【図27】NチャネルTFTで構成した従来例に係る画素回路を示す回路図である。

30

【図28】初期状態における駆動トランジスタであるTFTと有機EL素子の動作点を示す図である。

【図29】経時変化後の駆動トランジスタであるTFTと有機EL素子の動作点を示す図である。

【図30】NチャネルTFTのソースを接地電位に接続した構成の画素回路を示す回路図である。

【符号の説明】

【0100】

11, 51...画素（画素回路）、12...画素アレイ部、13...走査線、14, 41...駆動線、15...データ線、16...書き込み走査回路、17, 43...駆動走査回路、18...データ線駆動回路、21...有機EL素子、22...駆動トランジスタ（TFT）、23, 29...キャパシタ、24~28...スイッチングトランジスタ（TFT）、42...オートゼロ線、44...オートゼロ回路

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図7】

【図9】

【図10】

【 図 1 1 】

【 図 1 2 】

【図13】

【図15】

### 【図14】

【 図 1 6 】

【 図 17 】

【 図 1 9 】

【図18】

【 図 2 0 】

【 図 2 1 】

## 【 図 2 2 】

【図23】

【図24】

【図25】

【図27】

【図26】

【図28】

【図29】

【図30】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 4 B |

| G 0 9 G | 3/20  | 6 4 1 D |

| G 0 9 G | 3/20  | 6 4 2 A |

| G 0 9 G | 3/20  | 6 7 0 J |

| H 0 5 B | 33/14 | A       |

F ターム(参考) 3K007 AB02 AB17 BA06 DB03 GA00 GA04

5C080 AA06 BB05 DD05 DD22 DD29 EE28 FF11 JJ02 JJ03 JJ04

JJ05 JJ06

5C094 AA04 AA23 AA53 AA55 BA03 BA29 BA43 CA19 DA20

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路和显示设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2005227562A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2005-08-25 |

| 申请号            | JP2004036504                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2004-02-13 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| [标]发明人         | 山本哲郎<br>内野勝秀<br>山下淳一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | 山本 哲郎<br>内野 勝秀<br>山下 淳一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | H01L51/50 G09F9/30 G09F9/35 G09G3/20 G09G3/30 H01L27/32 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| FI分类号          | G09G3/30.J G09F9/30.338 G09F9/30.365.Z G09F9/35 G09G3/20.611.H G09G3/20.624.B G09G3/20.641.D G09G3/20.642.A G09G3/20.670.J H05B33/14.A G09F9/30.365 G09G3/3233 G09G3/3266 G09G3/3291 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 3K007/AB02 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD22 5C080/DD29 5C080/EE28 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5C094/AA04 5C094/AA23 5C094/AA53 5C094/AA55 5C094/BA03 5C094/BA29 5C094/BA43 5C094/CA19 5C094/DA20 3K107/AA01 3K107/BB01 3K107/CC21 3K107/EE04 3K107/HH05 5C380/AA01 5C380/AB06 5C380/AB22 5C380/AB46 5C380/BA28 5C380/BA39 5C380/BA50 5C380/BD02 5C380/BD05 5C380/CA12 5C380/CB17 5C380/CB26 5C380/CB31 5C380/CC04 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC61 5C380/CC63 5C380/CC64 5C380/CC77 5C380/CD013 5C380/CD026 5C380/DA02 5C380/HA03 5C380/HA05 5C380/HA08 |         |            |

| 代理人(译)         | 船桥 国则                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 其他公开文献         | <a href="#">JP4529467B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

### 摘要(译)

要解决的问题：为了解决如果电容器（像素电容器）的容量和驱动晶体管的栅极和源极之间的容量之和小于开关晶体管的寄生电容器的问题，驱动晶体管的栅极和源极之间的电位值是由驱动晶体管的源极电位的变化量引起的，并且不能期望期望的发光。 ŽSOLUTION：有机EL元件21的阳极电极层211和形成电容器23的电容器形成层231和232在布局上重叠的构造用于像素电路11，其构造为在栅极和栅极之间连接电容器23。 TFT22的源极是驱动晶体管，并且通过作为开关晶体管的TFT25选择性地将TFT22的源极连接到接地电位GND。 Ž