(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-189643

(P2005-189643A)

(43) 公開日 平成17年7月14日(2005.7.14)

(51) Int.Cl.<sup>7</sup>**G09G 3/30****G09G 3/20****H05B 33/14**

F 1

G09G 3/30

J

テーマコード(参考)

3K007

G09G 3/20

611A

5C080

G09G 3/20

611D

G09G 3/20

624B

G09G 3/20

641D

審査請求 未請求 請求項の数 4 O L (全 17 頁) 最終頁に続く

(21) 出願番号

特願2003-432738 (P2003-432738)

(22) 出願日

平成15年12月26日 (2003.12.26)

(71) 出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100102185

弁理士 多田 繁範

(72) 発明者 山下 淳一

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 内野 勝秀

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

F ターム(参考) 3K007 AB03 AB17 BA06 DB03 GA00

5C080 AA06 BB05 DD05 DD10 DD26

DD29 EE29 FF11 HH09 JJ01

JJ02 JJ04 JJ05

(54) 【発明の名称】ディスプレイ装置及びディスプレイ装置の駆動方法

## (57) 【要約】

**【課題】** 本発明は、ディスプレイ装置及びディスプレイ装置の駆動方法に関し、例えば有機EL表示装置等の電流駆動による自発光の表示装置に適用して、消費電力を低減し、さらには隣接する画素からの影響を有効に回避することができるようとする。

**【解決手段】** 本発明は、信号レベル保持用のコンデンサC2の端子間電圧によるゲートソース電圧V<sub>GS</sub>によりソースフォロワ回路構成によるトランジスタTR2で発光素子12を駆動する構成において、トランジスタTR2のゲート電圧をカットオフ電圧に設定して発光素子12の発光、非発光を制御する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

電流駆動による画素をマトリックス状に配置してなる画素部と、前記画素部を駆動して前記画素の階調を設定する駆動回路とを有するディスプレイ装置において、

前記画素が、

発光素子と、

ゲートソース間に信号レベル保持用のコンデンサを保持し、前記信号レベル保持用のコンデンサの端子間電圧によるゲートソース間電圧により前記発光素子を駆動するソースフォロワ回路によるトランジスタと、

前記トランジスタのゲートを信号線に接続する信号線用のスイッチ回路と、

前記トランジスタのゲートを、前記トランジスタをカットオフするカットオフ電圧に接続するカットオフ用のスイッチ回路とを有し、

前記駆動回路は、

前記カットオフ用のスイッチ回路をオン状態に設定することにより、前記トランジスタをカットオフさせて前記発光素子の発光を停止させる期間を設定し、

前記カットオフ用のスイッチ回路をオフ状態に設定した後、前記信号線用のスイッチ回路をオン状態に設定して、前記信号線の信号レベルにより前記信号レベル保持用のコンデンサの端子間電圧を設定する

ことを特徴とするディスプレイ装置。

**【請求項 2】**

電流駆動による画素をマトリックス状に配置してなる画素部を有するディスプレイ装置において、

前記画素が、

発光素子と、

ゲートソース間に信号レベル保持用のコンデンサを保持し、前記信号レベル保持用のコンデンサの端子間電圧によるゲートソース間電圧により前記発光素子を駆動するソースフォロワ回路によるトランジスタと、

前記トランジスタのゲートを一時的にカットオフ電圧に接続し、前記トランジスタをカットオフさせることにより、前記発光素子の発光を停止させるカットオフ用のスイッチ回路と、

前記カットオフ用のスイッチ回路のオフ動作に続いて、前記トランジスタのゲートを信号線に接続して前記信号レベル保持用のコンデンサの端子間電圧を前記信号線の信号レベルにより設定する信号線用のスイッチ回路とを有する

ことを特徴とするディスプレイ装置。

**【請求項 3】**

有機EL素子による画素をマトリックス状に配置してなる画素部を有するディスプレイ装置において、

前記画素が、

前記有機EL素子と、

ゲートソース間に信号レベル保持用のコンデンサを保持し、前記信号レベル保持用のコンデンサの端子間電圧によるゲートソース間電圧により前記有機EL素子を駆動するソースフォロワ回路によるトランジスタと、

前記トランジスタのゲートを一時的にカットオフ電圧に接続し、前記トランジスタをカットオフさせることにより、前記有機EL素子の発光を停止させるカットオフ用のスイッチ回路と、

前記カットオフ用のスイッチ回路のオフ動作に続いて、前記トランジスタのゲートを信号線に接続して前記信号レベル保持用のコンデンサの端子間電圧を前記信号線の信号レベルにより設定する信号線用のスイッチ回路とを有する

ことを特徴とするディスプレイ装置。

**【請求項 4】**

10

20

30

40

50

電流駆動による画素をマトリックス状に配置してなる画素部を有するディスプレイ装置の駆動方法において、

前記画素が、

発光素子と、

ゲートソース間に信号レベル保持用のコンデンサを保持し、前記信号レベル保持用のコンデンサの端子間電圧によるゲートソース間電圧により前記発光素子を駆動するソースフォロワ回路によるトランジスタと、

前記トランジスタのゲートを信号線に接続する信号線用のスイッチ回路と、

前記トランジスタのゲートを、前記トランジスタをカットオフするカットオフ電圧に接続するカットオフ用のスイッチ回路とを有し、

前記ディスプレイ装置の駆動方法は、

前記カットオフ用のスイッチ回路をオン状態に設定することにより、前記トランジスタをカットオフさせて前記発光素子の発光を停止させる期間を設定し、

前記カットオフ用のスイッチ回路をオフ状態に設定した後、前記信号線用のスイッチ回路をオン状態に設定して、前記信号線の信号レベルにより前記信号レベル保持用のコンデンサの端子間電圧を設定する

ことを特徴とするディスプレイ装置の駆動方法。

10

20

30

40

50

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、ディスプレイ装置及びディスプレイ装置の駆動方法に関し、例えば有機EL(Electro Luminescence)表示装置等の電流駆動による自発光の表示装置に適用することができる。本発明は、信号レベル保持用のコンデンサの端子間電圧によるゲートソース電圧によりソースフォロワ回路構成によるトランジスタで発光素子を駆動する構成において、このトランジスタTR2のゲート電圧をカットオフ電圧に設定して発光素子の発光、非発光を制御することにより、消費電力を低減し、さらには隣接する画素からの影響を効果的に回避することができるようとする。

#### 【背景技術】

#### 【0002】

従来、有機ELの表示装置においては、例えばU.S.P.5,684,365、特開平8-234683号公報等にディスプレイ装置への応用が種々に提案されるようになされている。

#### 【0003】

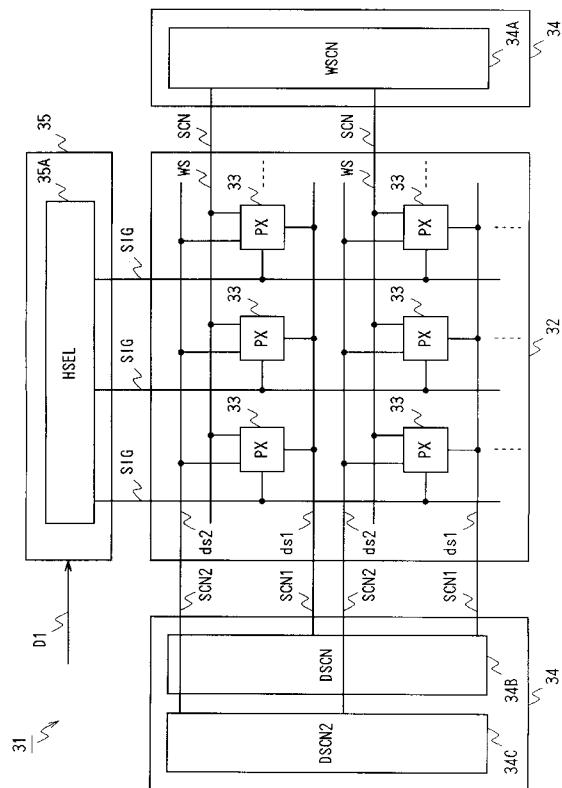

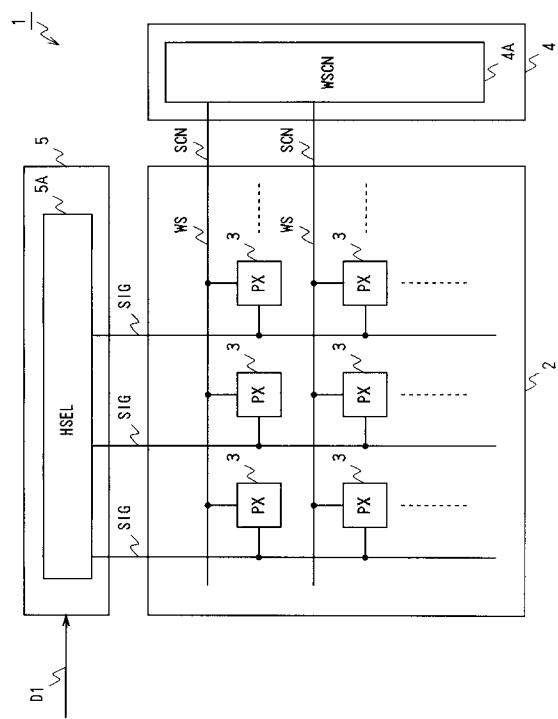

すなわち図7に示すように、この種のディスプレイ装置1において、画素部2は、マトリックス状に配置されてなる画素(PX)3に対して、走査線SCNがライン単位で水平方向に設けられ、またこの走査線SCNと直交するように信号線SIGが各列毎に垂直方向に設けられる。このようにして形成されてなる画素部2に対して、ディスプレイ装置1は、垂直駆動回路4により走査線SCNを駆動して順次ライン単位で画素部2の画素3を選択すると共に、この画素3の選択に対応するように水平駆動回路5により信号線SIGを駆動して各画素3の階調を設定するようになされている。

#### 【0004】

このため垂直駆動回路4は、ライトスキャン回路(WSCN)4Aにより、各画素3への書き込みをライン単位で順次指示する書き込み信号wsを生成し、この書き込み信号wsを走査線SCNに出力して各画素3における階調の設定を制御するようになされている。また水平駆動回路5は、各画素3の階調を指示する階調データD1に応じて駆動信号を生成し、この駆動信号を水平セレクタ(HSEL)5Aにより各信号線SIGに振り分けて出力し、これらによりディスプレイ装置1は、ライン単位で各画素3の階調を設定するようになされている。

#### 【0005】

有機EL素子の表示装置においては、このようにして駆動される各画素3が、電流駆動による自発光型の素子である有機ELによる有機EL素子と、この有機EL素子を駆動する各画素の駆動回路（以下、画素回路と呼ぶ）により形成されるようになされている。

#### 【0006】

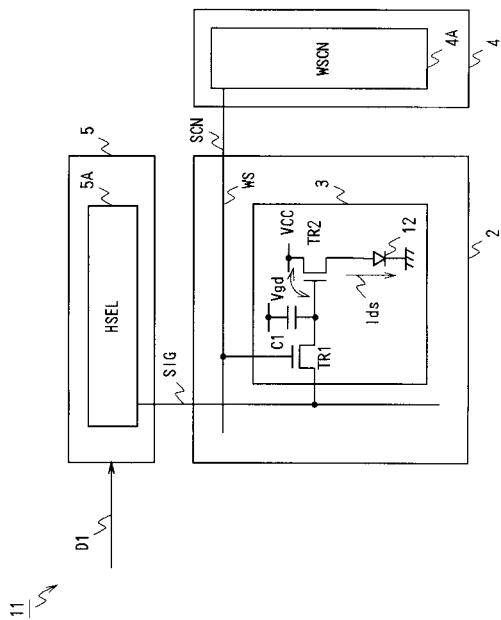

しかしてこのようにして形成されるディスプレイ装置においては、nチャンネルMOS型のTFT（Thin Film Transistor）により各画素回路を形成することにより、有機EL素子と画素回路とをガラス基板上に一体に形成することができ、これにより図8に示すように、ソースフォロワ回路構成により有機EL素子12を駆動するようになされている。

#### 【0007】

すなわちこの図8に示すディスプレイ装置11は、各画素3において、有機EL素子12のアノードにソースを接続してなるソースフォロワ回路構成のトランジスタTR2により有機EL素子12を電流駆動するように形成され、このトランジスタTR2のゲートに信号レベル保持用のコンデンサC1が設けられる。ディスプレイ装置11は、ライトスキャン4Aから出力される書き込み信号wsによりオン動作するトランジスタTR1により、この信号レベル保持用のコンデンサC1が信号線SIGに接続され、これにより書き込み信号wsに応動して信号線SIGに出力される駆動信号の信号レベルによりトランジスタTR2のゲート電圧Vgが設定される。これによりこのディスプレイ装置11は、このように設定されたゲート電圧Vgに応じた電流により有機EL素子12を駆動し、階調データD1に応じた階調により各画素3の有機EL素子12を発光させて所望の画像を表示できるようになされている。

#### 【0008】

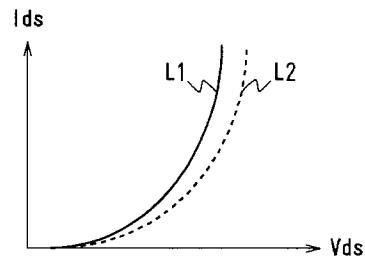

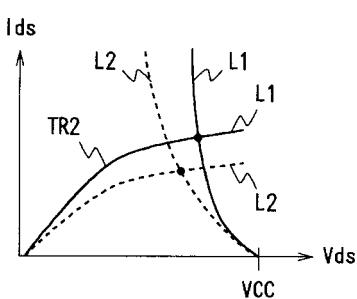

しかしながら有機EL素子においては、図9に示すように、使用により電流が流れ難くなる方向に電流電圧特性が変化する。なおこの図9及び図10において、符号L1が初期の特性を示し、符号L2が経時変化による特性を示すものである。これに対して図8について上述したソースフォロワ回路による駆動においては、図10に示すように、トランジスタTR2のドレインソース間電圧Vds - ドレインソース電流Idsの特性曲線に対して、負荷による特性曲線が交差してなる交点が動作点となる。これにより有機EL素子において、電圧電流特性が変化すると、その分、有機EL素子に流れる電流が減少し、これらにより各画素の輝度が徐々に低下する問題がある。

#### 【0009】

この問題を解決する1つの方法として、単なるゲート電圧Vgによる階調の設定に代えてゲートソース間電圧Vgsによる階調の設定により有機EL素子12の駆動電流を制御する方法が考えられる。すなわちTFTのドレイン電流Idsにおいては、 $(1/2) \times \mu \times (W/L) C_o \times (V_{gs} - V_{th})^2 \dots \dots (1)$ により表され、これによりゲートソース間電圧Vgsによる階調の設定により経時変化による駆動電流の変化を防止することができる。ここでμはキャリアの移動度、Wはゲート幅、Lはゲート長、Coは単位面積当たりのゲート容量、Vthはしきい値電圧である。

#### 【0010】

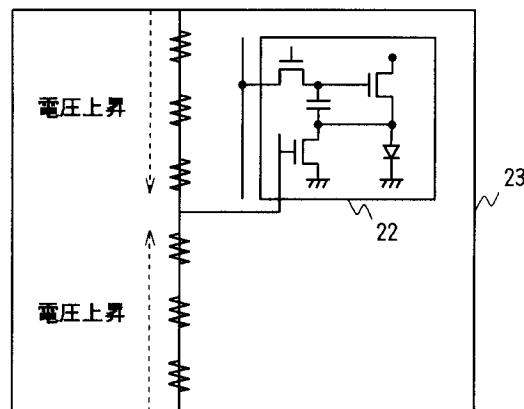

これにより図8との対比により図11に示すように、各画素22において、トランジスタTR2のゲートに対する信号レベル保持用のコンデンサC1の配置に代えて、このトランジスタTR2のゲートソース間に信号レベル保持用のコンデンサC2を配置し、この信号レベル保持用のコンデンサC2に信号線SIGの信号レベルを設定する。またドライブスキャン信号dsによりオン動作するトランジスタTR3をトランジスタTR2のソースに接続し、信号レベル保持用のコンデンサC2に信号線SIGの信号レベルを設定する期間の間、このトランジスタTR3によりトランジスタTR2のソース電位を一定電位に設定する。なお図11においては、この一定電位がアース電位の場合である。またこのような画素22による画素部23の構成に対応して、垂直駆動回路24においては、ライトスキャン回路24Aに加えて、このライトスキャン回路24Aによる書き込み信号wsの出力に同期してドライブスキャン信号dsを出力するドライブスキャン回路(DSCN)24Bを設ける。

10

20

30

40

50

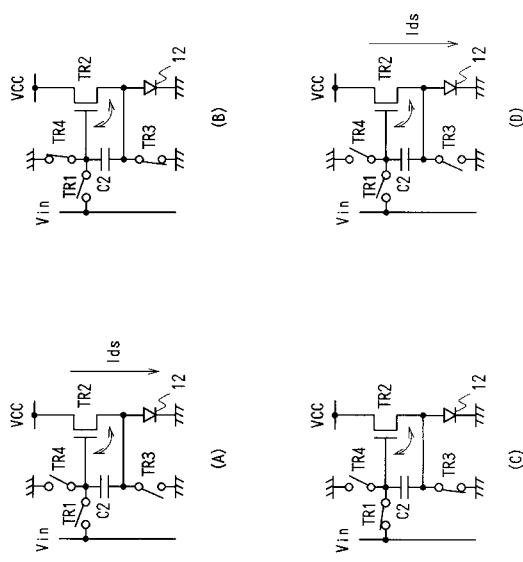

## 【0011】

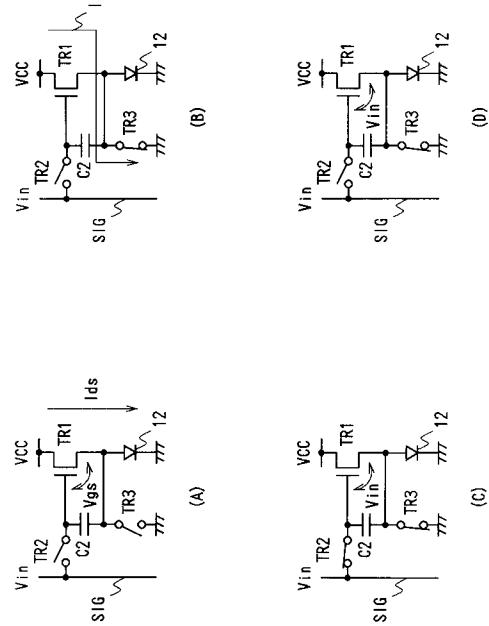

しかして実際上、図12及び図13に示すように、このようにトランジスタTR3をオン状態に切り換えて、トランジスタTR2のソース電位においては、立ち下がりに時間を要することになる。これにより書き込み信号wsによるコンデンサC2への信号線SIGの信号レベルの設定に先行して、ドライブスキャン信号dsによりトランジスタTR3をオン動作させ、トランジスタTR2のソース電圧Vsが十分に一定の電位となった後、書き込み信号wsによりトランジスタTR3をオン動作させ、信号レベル保持用のコンデンサC2に信号線SIGの信号レベルVinを設定する。またその後、書き込み信号wsを立ち下げてトランジスタTR2をオフ状態に設定した後、ドライブスキャン信号dsを立ち下げ、これによりソース電圧Vsが立ち上がって信号レベル保持用のコンデンサC2に設定された信号レベルVinに応じた電流駆動により有機EL素子12が発光を開始する。なお図13(A)～(D)は、図12の各期間T1～T4に対応するトランジスタTR2、TR3の設定を示す接続図である。

## 【0012】

このようにしてゲートソース間電圧Vgsによる階調の設定により有機EL素子12の駆動電流を制御すれば、有機EL素子12の特性が変化した場合であっても、階調データにより決まる一定電流により駆動し得、これにより経時変化による画質の劣化等を有効に回避することができる。

## 【0013】

しかしながらこの図11に示す構成においては、ドライブスキャン信号dsによりトランジスタTR3をオン動作させている期間T2、T3、T4の間、トランジスタTR2、トランジスタTR3に電源Vccから貫通電流が流れ続けることになる。これにより消費電力が増大する問題がある。

## 【0014】

またこのような期間T2、T3、T4においては、書き込み信号wsにより信号レベル保持用のコンデンサC2に信号線SIGの信号レベルを設定する期間T3に比して広くすることが必要なことにより、複数ラインでこれらの期間T2、T3、T4が重なり合い、これにより隣接する画素の影響が現れる。具体的には、図14に示すように、トランジスタTR3のソース電位を設定する配線パターンにこれら期間T2～T4が重なり合ってなる画素回路の電流が流れることにより、またこの配線パターンにおいては、ある程度の抵抗値を有することにより、例えば画素部23の上下でこれらの配線パターンを接地する場合には、垂直方向の画面中央側の画素程、トランジスタTR3のソース電位が上昇し、その分、信号レベル保持用のコンデンサC2の端子間電圧が低下し、これにより図15に示すように、中央側で明るさが低下してなるようなシェーディングが発生する。

## 【0015】

また図16に示すように、周囲を中間階調に設定し、中央に低階調の領域を形成した場合、この低階調の領域の下側に、階調の高い領域が形成され、いわゆる縦方向のクロストークが発生する。

## 【0016】

なお有機EL素子12を発光させている期間にあっても、各画素23ではトランジスタTR2に電流が流れ、この電流が、有機EL素子12を介してアースラインより流出する。しかしながらこの有機EL素子12からの電流流出先のアースラインにあっては、画素回路が設けられている基板に対して、対向するように設けられた対向基板側のアースラインである。これによりこのように非発光の期間におけるこれらの期間T2、T3、T4が複数ラインで重なり合って、これらの期間T2、T3、T4でトランジスタTR2より電流が流出すると、これらシェーディング等による隣接する画素からの影響が発生する。

【特許文献1】U.S.P.5,684,365

【特許文献2】特開平8-234683号

【発明の開示】

【発明が解決しようとする課題】

10

20

30

40

50

**【 0 0 1 7 】**

本発明は以上の点を考慮してなされたもので、信号レベル保持用のコンデンサの端子間電圧によるゲートソース電圧によりソースフォロワ回路構成によるトランジスタで発光素子を駆動する構成において、消費電力を低減し、さらには隣接する画素からの影響を有効に回避することができるディスプレイ装置、ディスプレイ装置の駆動方法を提案しようとするものである。

**【課題を解決するための手段】****【 0 0 1 8 】**

かかる課題を解決するため請求項1の発明においては、電流駆動による画素をマトリックス状に配置してなる画素部と、画素部を駆動して画素の階調を設定する駆動回路とを有するディスプレイ装置に適用して、画素が、発光素子と、ゲートソース間に信号レベル保持用のコンデンサを保持し、信号レベル保持用のコンデンサの端子間電圧によるゲートソース間電圧により発光素子を駆動するソースフォロワ回路によるトランジスタと、トランジスタのゲートを信号線に接続する信号線用のスイッチ回路と、トランジスタのゲートを、トランジスタをカットオフするカットオフ電圧に接続するカットオフ用のスイッチ回路とを有し、駆動回路は、カットオフ用のスイッチ回路をオン状態に設定することにより、トランジスタをカットオフさせて発光素子の発光を停止させる期間を設定し、カットオフ用のスイッチ回路をオン状態に設定した後、信号線用のスイッチ回路をオン状態に設定して、信号線の信号レベルにより信号レベル保持用のコンデンサの端子間電圧を設定する。

**【 0 0 1 9 】**

また請求項2の発明においては、電流駆動による画素をマトリックス状に配置してなる画素部を有するディスプレイ装置に適用して、画素が、発光素子と、ゲートソース間に信号レベル保持用のコンデンサを保持し、信号レベル保持用のコンデンサの端子間電圧によるゲートソース間電圧により発光素子を駆動するソースフォロワ回路によるトランジスタと、トランジスタのゲートを一時的にカットオフ電圧に接続し、トランジスタをカットオフさせることにより、発光素子の発光を停止させるカットオフ用のスイッチ回路と、カットオフ用のスイッチ回路のオフ動作に続いて、トランジスタのゲートを信号線に接続して信号レベル保持用のコンデンサの端子間電圧を信号線の信号レベルにより設定する信号線用のスイッチ回路とを有するようとする。

**【 0 0 2 0 】**

また請求項3の発明においては、有機EL素子による画素をマトリックス状に配置してなる画素部を有するディスプレイ装置に適用して、画素が、有機EL素子と、ゲートソース間に信号レベル保持用のコンデンサを保持し、信号レベル保持用のコンデンサの端子間電圧によるゲートソース間電圧により有機EL素子を駆動するソースフォロワ回路によるトランジスタと、トランジスタのゲートを一時的にカットオフ電圧に接続し、トランジスタをカットオフさせることにより、有機EL素子の発光を停止させるカットオフ用のスイッチ回路と、カットオフ用のスイッチ回路のオフ動作に続いて、トランジスタのゲートを信号線に接続して信号レベル保持用のコンデンサの端子間電圧を信号線の信号レベルにより設定する信号線用のスイッチ回路とを有するようとする。

**【 0 0 2 1 】**

また請求項4の発明においては、電流駆動による画素をマトリックス状に配置してなる画素部を有するディスプレイ装置の駆動方法に適用して、画素が、発光素子と、ゲートソース間に信号レベル保持用のコンデンサを保持し、信号レベル保持用のコンデンサの端子間電圧によるゲートソース間電圧により発光素子を駆動するソースフォロワ回路によるトランジスタと、トランジスタのゲートを信号線に接続する信号線用のスイッチ回路と、トランジスタのゲートを、トランジスタをカットオフするカットオフ電圧に接続するカットオフ用のスイッチ回路とを有し、ディスプレイ装置の駆動方法は、カットオフ用のスイッチ回路をオン状態に設定することにより、トランジスタをカットオフさせて発光素子の発光を停止させる期間を設定し、カットオフ用のスイッチ回路をオフ状態に設定した後、信号線用のスイッチ回路をオン状態に設定して、信号線用信号レベルにより信号レベル保持

10

20

30

40

50

用のコンデンサの端子間電圧を設定するようとする。

**【0022】**

請求項1の構成により、電流駆動による画素をマトリックス状に配置してなる画素部と、画素部を駆動して画素の階調を設定する駆動回路とを有するディスプレイ装置に適用して、画素が、発光素子と、ゲートソース間に信号レベル保持用のコンデンサを保持し、信号レベル保持用のコンデンサの端子間電圧によるゲートソース間電圧により発光素子を駆動するソースフォロワ回路によるトランジスタと、トランジスタのゲートを信号線に接続する信号線用のスイッチ回路と、トランジスタのゲートを、トランジスタをカットオフするカットオフ電圧に接続するカットオフ用のスイッチ回路とを有し、駆動回路は、カットオフ用のスイッチ回路をオン状態に設定することにより、トランジスタをカットオフさせて、発光素子の発光を停止させる期間を設定すれば、発光素子を非発光とする場合には、トランジスタで電力を消費しないようにすることができ、これにより消費電力を低減することができる。またカットオフ用のスイッチ回路をオン状態に設定した後、信号線用のスイッチ回路をオフ状態に設定して、信号線の信号レベルにより信号レベル保持用のコンデンサの端子間電圧を設定すれば、この信号レベル保持用のコンデンサの端子電圧の設定期間を順次各ラインに設定して、この期間が複数ラインで重なり合わないようにし得、これにより例えばスイッチ回路により信号レベル保持用のコンデンサの他端の電圧を、アース電位等の基準電圧に設定して信号レベル保持用のコンデンサの端子間電圧を設定する場合に、隣接画素からの影響を有效地に回避することができる。これらにより信号レベル保持用のコンデンサの端子間電圧によるゲートソース電圧によりソースフォロワ回路構成によるトランジスタで発光素子を駆動する構成において、消費電力を低減し、さらには隣接する画素からの影響を有效地に回避することができる。

10

20

30

**【0023】**

これにより請求項2、請求項3の構成によれば、信号レベル保持用のコンデンサの端子間電圧によるゲートソース電圧によりソースフォロワ回路構成によるトランジスタで発光素子を駆動する構成において、消費電力を低減し、さらには隣接する画素からの影響を有效地に回避することができるディスプレイ装置を提供することができ、請求項4の構成によれば、信号レベル保持用のコンデンサの端子間電圧によるゲートソース電圧によりソースフォロワ回路構成によるトランジスタで発光素子を駆動する構成において、消費電力を低減し、さらには隣接する画素からの影響を有效地に回避することができるディスプレイ装置の駆動方法を提供することができる。

**【発明の効果】**

**【0024】**

本発明によれば、信号レベル保持用のコンデンサの端子間電圧によるゲートソース電圧によりソースフォロワ回路構成によるトランジスタで発光素子を駆動する構成において、消費電力を低減し、さらには隣接する画素からの影響を有效地に回避することができる。

**【発明を実施するための最良の形態】**

**【0025】**

以下、適宜図面を参照しながら本発明の実施例を詳述する。

**【実施例1】**

**【0026】**

(1) 実施例の構成

図2は、図7との対比により本発明の実施例に係るディスプレイ装置を示すブロック図である。このディスプレイ装置31において、画素部32は、電流駆動による画素(PX)33がマトリックス状に配置され、この画素33に対して、3つの走査線SCN、SCN1、SCN2がライン単位で水平方向に設けられる。またこれらの走査線SCN、SCN1、SCN2と直交するように信号線SIGが各列毎に垂直方向に設けられる。このようにして形成されてなる画素部32に対して、ディスプレイ装置31は、垂直駆動回路34により走査線SCN、SCN1、SCN2を駆動して順次ライン単位で画素33に設けられた画素回路の動作を制御すると共に、この画素回路の制御に対応するように水平駆動

40

50

回路 3 5 により信号線 S I G を駆動して各画素 3 3 の階調を設定するようになされている。

#### 【 0 0 2 7 】

このため垂直駆動回路 3 4 は、ライトスキャン回路 ( W S C N ) 3 4 A により、各画素 3 3 への書き込みをライン単位で順次指示する書き込み信号 w s を生成し、この書き込み信号 w s を走査線 S C N に出力して各画素 3 3 における階調の設定を制御するようになされている。またこのライトスキャン回路 3 4 A による書き込み信号 w s の出力に同期してドライブスキャン信号 d s 1 、 d s 2 をそれぞれ出力するドライブスキャン回路 ( D S C N ) 3 4 B 、ドライブスキャン回路 ( D S C N 2 ) 3 4 C が設けられるようになされている。

10

#### 【 0 0 2 8 】

また水平駆動回路 3 5 においては、各画素 3 3 の階調を指示する階調データ D 1 に応じて駆動信号を生成し、この駆動信号を水平セレクタ ( H S E L ) 3 5 A により各信号線 S I G に振り分けて出力するようになされている。

#### 【 0 0 2 9 】

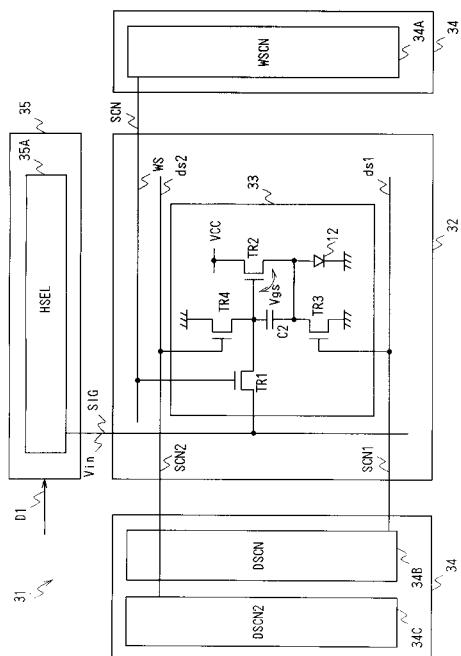

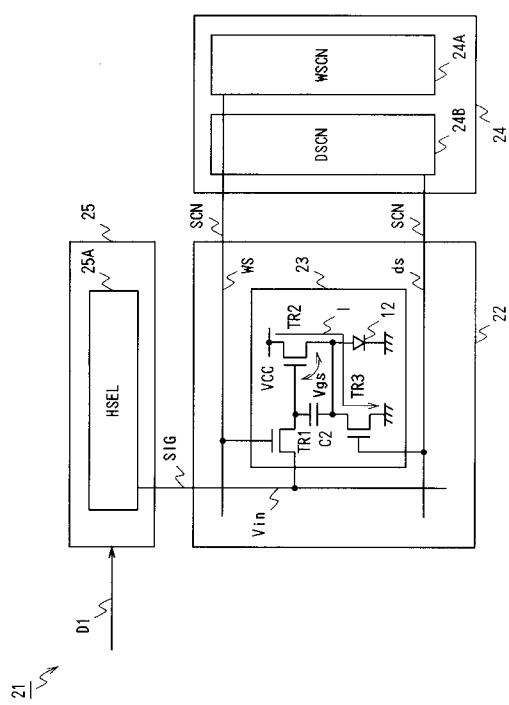

図 1 は、図 1 1 との対比によりこのディスプレイ装置 3 1 に係る各画素 3 3 を示す接続図である。なお画素 3 3 を構成するトランジスタ T R 1 ~ T R 4 は、n チャンネル M O S 型の T F T であり、水平駆動回路 3 5 、垂直駆動回路 3 4 と共にガラス基板上に、アモルファスプロセスにより一体に作成されるようになされている。

20

#### 【 0 0 3 0 】

このディスプレイ装置 3 1 に係る画素 3 3 においては、ソースフォロワ回路によるトランジスタ T R 2 により有機 E L 素子 1 2 を駆動するように形成され、このトランジスタ T R 2 のゲートソース間に設けられた信号レベル保持用のコンデンサ C 2 の端子間電圧の設定により、このトランジスタ T R 2 のゲートソース電圧 V g s が設定されて、この有機 E L 素子 1 2 の駆動電流が設定されるようになされている。

#### 【 0 0 3 1 】

またこの信号レベル保持用のコンデンサ C 2 のソース側端を基準電圧に設定するトランジスタ T R 3 によるスイッチ回路と、信号レベル保持用のコンデンサ C 2 のゲート側端を信号線 S I G に接続するトランジスタ T R 1 とが設けられ、これらトランジスタ T R 1 、 T R 2 により信号レベル保持用のコンデンサの端子間電圧を設定するようになされている。

30

#### 【 0 0 3 2 】

この画素 3 3 では、さらにトランジスタ T R 2 のゲートを、このトランジスタ T R 2 をカットオフするカットオフ電圧に接続するトランジスタ T R 4 による電源用のスイッチ回路が設けられる。なおこの実施例では、トランジスタ T R 3 に係る基準電圧、トランジスタ T R 4 に係るカットオフ電圧がアース電圧に設定されるようになされている。

#### 【 0 0 3 3 】

これによりこの実施例では、このトランジスタ T R 4 によりトランジスタ T R 2 のカットオフに設定して有機 E L 素子 1 2 を非発光に制御し、この非発光の期間の間において、トランジスタ T R 2 に電流が流れないように設定され、消費電力を低減し、さらには垂直方向に隣接する画素による各種の影響を防止するようになされている。

40

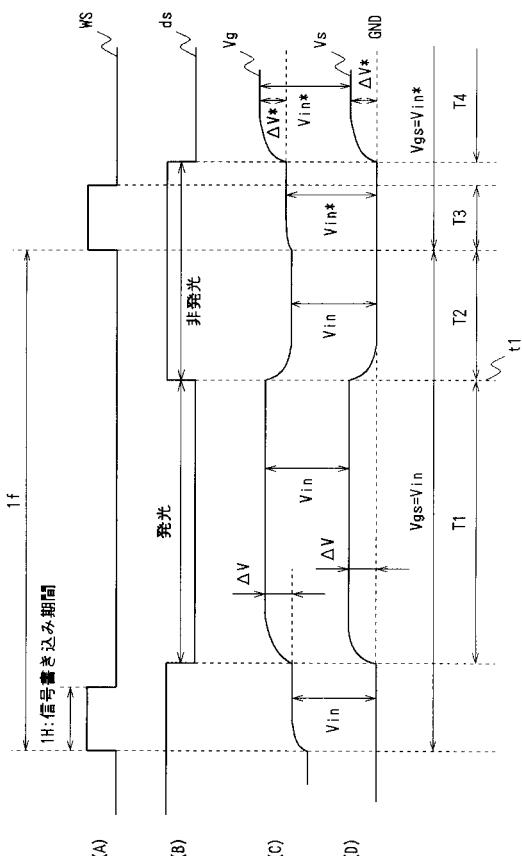

#### 【 0 0 3 4 】

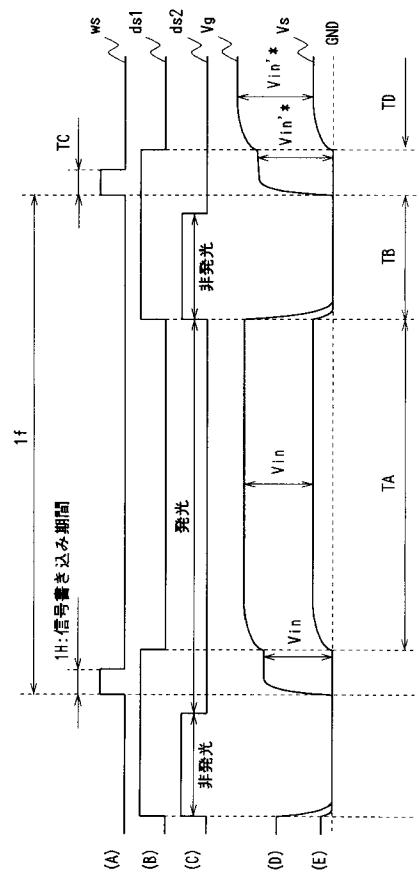

すなわち図 3 及び図 4 に示すように、垂直駆動回路 3 4 においては、ライトスキャン回路 3 4 A により、階調データ D 1 による 1 フレーム ( 1 f ) の水平走査期間 ( 1 H ) で順次走査線 S C N の書き込み信号 w s を立ち上げ ( 図 3 ( A ) ) 、これにより対応するラインの画素回路において、トランジスタ T R 1 をオン状態に設定して信号レベル保持用のコンデンサ C 2 の一端を信号線 S I G の電圧 V i n に設定する。なお図 4 ( A ) ~ ( D ) は、それぞれ図 3 の期間 T A ~ T D に対応する画素 3 3 の接続である。

#### 【 0 0 3 5 】

このようにして信号レベル保持用のコンデンサ C 2 に信号線 S I G の信号レベル V i n

50

を設定する際に、垂直駆動回路 34 は、ドライブスキャン回路 34B よりドライブスキャン信号 d<sub>s</sub>1 を立ち上げ（図 3（B））、これにより信号レベル保持用のコンデンサ C2 の他端を基準電圧であるアース電圧に設定する。これによりディスプレイ装置 31 では、いわゆるポートストラップ回路により、信号線 SIG の信号レベルをコンデンサ C2 に確実に設定するようになされている。

#### 【0036】

垂直駆動回路 34 は、このようにして書き込み信号 w<sub>s</sub> の立ち上げにより信号線 SIG の信号レベル V<sub>in</sub> により信号レベル保持用のコンデンサ C2 の端子間電圧を設定するようにして、この書き込み信号 w<sub>s</sub> の立ち上げに先行して所定期間の間、ドライブスキャン回路 34B よりドライブスキャン信号 d<sub>s</sub>2 を立ち上げ（図 3（C））、これによりトランジスタ TR2 をカットオフさせて有機 EL 素子 12 の駆動を停止する（図 3（D）及び（E））。またこのドライブスキャン信号 d<sub>s</sub>2 の立ち上げに同期してドライブスキャン信号 d<sub>s</sub>1 を立ち上げることにより、このような有機 EL 素子 12 の駆動の停止により、即座に、有機 EL 素子 12 の発光を停止させる（図 4（B））。

#### 【0037】

これらによりこの画素 33 においては、このトランジスタ TR4 により有機 EL 素子 12 の発光、非発光を制御して、信号レベル保持用のコンデンサ C2 の端子間電圧によるゲートソース間電圧 V<sub>gs</sub> によりトランジスタ TR2 で有機 EL 素子 12 を駆動するようになされている（図 4（A）及び（D））。

#### 【0038】

##### （2）実施例の動作

以上の構成において、このディスプレイ装置 31 は（図 2）、垂直駆動回路 34 による走査線 SCN、SCN1、SCN2 の駆動により順次ライン単位で画素部 32 の画素 33 に水平駆動回路 35 により駆動される信号線 SIG の信号レベルが設定される。ディスプレイ装置 31 は、この設定した信号レベルにより各画素が発光して所望の画像が表示される。

#### 【0039】

ディスプレイ装置 31 では（図 1、図 3、図 4）、各画素 33 において、有機 EL 素子 12 を駆動するソースフォロワ回路構成のトランジスタ TR2 のゲートソースに信号レベル保持用のコンデンサ C2 が設けられ、トランジスタ TR3 によるスイッチ回路によりこの信号レベル保持用のコンデンサ C2 のソース側端を基準電圧であるアース電位に設定した状態で、トランジスタ TR1 によるスイッチ回路により信号レベル保持用のコンデンサ C2 のゲート側端を信号線 SIG に接続することにより、このような信号線 SIG の信号レベルに係る各画素 33 の設定が実行される。

#### 【0040】

これによりこのディスプレイ装置 31 では、有機 EL 素子 12 の特性が経時変化した場合でも、階調データ D1 に応じた電流駆動により有機 EL 素子 12 を駆動することができる。また画素回路を n チャンネル MOS 型による TFT により構成して、ソースフォロワ回路構成による有機 EL 素子 12 を電流駆動して、このような駆動を実現することができる。

#### 【0041】

しかしながら何ら対策を講じない場合には、非発光の期間でトランジスタ TR2、TR3 を介して電流が流れ続け、その分、無駄に電力を消費して消費電力が増大することになる。またこの電流による基準電圧の変化により垂直方向に隣接する画素による影響が発生し、縦シェーディング、クロストークが発生する。

#### 【0042】

このためこの実施例においては、トランジスタ TR2 のゲートにトランジスタ TR4 が設けられ、トランジスタ TR2 により有機 EL 素子 12 を駆動していない期間であって、かつ信号レベル保持用のコンデンサ C2 を信号線 SIG の信号レベル V<sub>in</sub> により設定する期間以外の期間の間、トランジスタ TR2 のゲート電圧がトランジスタ TR2 をカット

10

20

30

40

50

オフさせる電圧に設定される。これにより画素33では、トランジスタTR2、TR3を介して電源Vccから電流が流れないようにし得、このような電流が流れ続けてなることによる消費電力の増大が防止される。

#### 【0043】

またこのようにして非発光の期間では電流が流れないようにして、順次ライン単位で各画素に信号線SIGの信号レベルVinを設定することにより、トランジスタTR3により設定される基準電圧においては、ほぼ一定電圧に保持し得、これにより垂直方向に隣接する画素による影響を防止して縦シェーディング、クロストークを防止し、ユニフォーミティの高い画質を得ることができる。

#### 【0044】

##### (3) 実施例の効果

以上の構成によれば、信号レベル保持用のコンデンサの端子間電圧によるゲートソース電圧によりソースフォロワ回路構成によるトランジスタで発光素子を駆動する構成において、このトランジスタTR2のゲート電圧をカットオフ電圧に設定して発光素子の発光、非発光を制御することにより、消費電力を低減し、さらには隣接する画素からの影響を有效地に回避することができる。

#### 【実施例2】

#### 【0045】

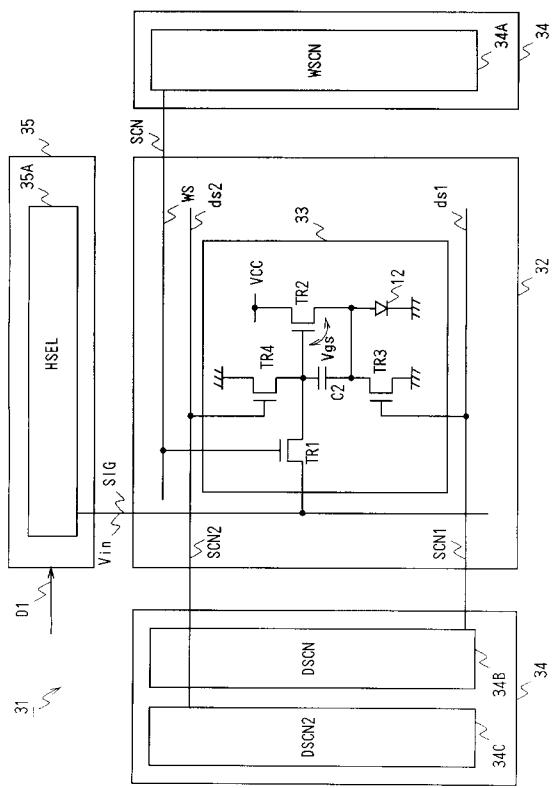

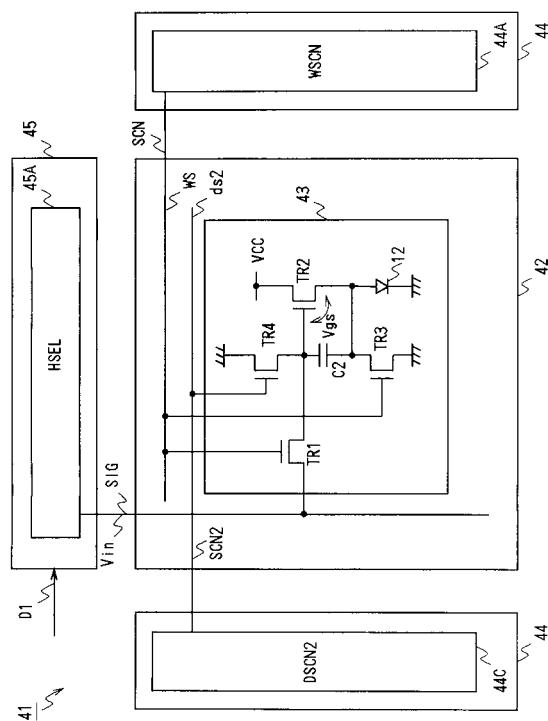

図5は、図1との対比により本発明の実施例に係るディスプレイ装置を示す接続図である。このディスプレイ装置41においては、各画素43において、信号レベル保持用のコンデンサC2のソース側端を基準電圧に設定するトランジスタTR3が、書き込み信号wsにより制御される。このディスプレイ装置41においては、書き込み信号wsによる制御に関連する構成が異なる点を除いて、実施例1のディスプレイ装置31と同一に構成される。

#### 【0046】

これによりこのディスプレイ装置41では、垂直駆動回路44において、ライトスキャン回路(WSCN)44A、ドライブスキャン回路(DSCN2)44Cによりそれぞれ書き込み信号ws、ドライブスキャン信号da2を生成して出力し、また水平駆動回路45においては、階調データD1に応じた駆動信号を水平セレクタ(HSEL)45Aにより各信号線SIGに出力するようになされている。

#### 【0047】

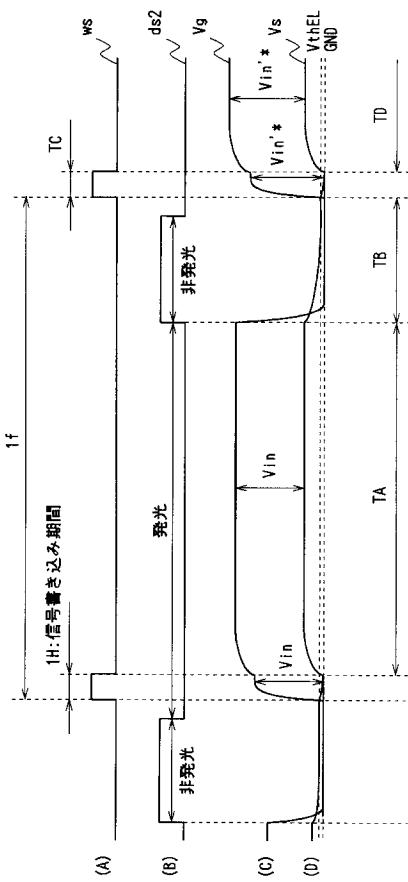

図6に示すように、このように信号レベル保持用のコンデンサC2のソース側端を基準電圧に設定するトランジスタTR3を書き込み信号wsにより併せて制御するようにして、ディスプレイ装置41は、実施例1に係るディスプレイ装置31と同一に、書き込み信号ws、ドライブスキャン信号ds2を出力する(図6(A)及び(B))。これによりディスプレイ装置41では、ドライブスキャン信号ds2の立ち上げにより、トランジスタTR2をカットオフして有機EL素子12への電流の供給を停止し、これにより有機EL素子12の発光、非発光を制御するようになされている。しかしてこのように有機EL12への電流の供給を停止すると、有機EL素子12の端子電圧においては、有機EL素子12のしきい値電圧VthELまで低下し、これにより有機EL素子12が発光を停止することになる。

#### 【0048】

またこのようにして有機EL素子12の発光を停止して、ディスプレイ装置41では、対応する水平走査期間の直前で、ドライブスキャン信号ds2が立ち下げられ、その後、書き込み信号wsの立ち上げにより、信号レベル保持用のコンデンサC2のソース側端がアース電圧に設定された状態で、信号レベル保持用のコンデンサC2の他端が信号線SIGの信号レベルVinにより設定され、これにより信号レベル保持用のコンデンサC2の端子間電圧が信号線SIGの信号レベルVinにより設定される。

#### 【0049】

これによりこの実施例においても、この対応する水平走査期間で信号線SIGの信号レ

ベル  $V_{in}$  により信号レベル保持用のコンデンサ C 2 の端子間電圧を設定する期間の間の僅かの期間だけ、トランジスタ T R 2、T R 3 に電流が流れるようにして、全体として消費電力を低減し、さらには隣接する画素からの影響を有効に回避することができるようになされている。

#### 【0050】

この実施例のように信号レベル保持用のコンデンサ C 2 のソース側端を基準電圧に設定するトランジスタ T R 3 を書き込み信号  $w_s$  により制御することにより、その分、走査線の数を低減して、実施例 1 と同様の効果を得ることができる。

#### 【実施例 3】

#### 【0051】

なお上述の実施例においては、アモルファスシリコンのプロセスを適用して有機 E L 素子と画素回路とをガラス基板上に作成する場合について述べたが、本発明はこれに限らず、ポリシリコンによるトランジスタを作成する場合、さらには画素部と別体にシリコン基板により駆動回路を作成した後、画素部と接続して一体化する場合等にも広く適用することができる。

#### 【0052】

また上述の実施例においては、有機 E L 素子による発光素子を電流駆動する場合について述べたが、本発明はこれに限らず、電流駆動に係る種々の発光素子によるディスプレイ装置に広く適用することができる。

#### 【産業上の利用可能性】

#### 【0053】

本発明は、ディスプレイ装置及びディスプレイ装置の駆動方法に関し、例えば有機 E L 表示装置等の電流駆動による自発光の表示装置に適用することができる。

#### 【図面の簡単な説明】

#### 【0054】

【図 1】本発明の実施例 1 に係るディスプレイ装置の画素を周辺構成と共に示す接続図である。

【図 2】本発明の実施例 1 に係るディスプレイ装置を示すブロック図である。

【図 3】図 1 の画素の動作の説明に供するタイムチャートである。

【図 4】図 3 のタイムチャートの説明に供する接続図である。

【図 5】本発明の実施例 2 に係るディスプレイ装置の画素を周辺構成と共に示す接続図である。

【図 6】図 5 の画素の動作の説明に供するタイムチャートである。

【図 7】ディスプレイ装置の構成を示すブロック図である。

【図 8】有機 E L 素子によるディスプレイ装置の構成を示す接続図である。

【図 9】有機 E L 素子の特性を示す特性曲線図である。

【図 10】有機 E L 素子の動作点の変化の説明に供する特性曲線図である。

【図 11】ソースフォロワ回路構成による画素回路を周辺構成と共に示す接続図である。

【図 12】図 11 の画素回路の動作の説明に供するタイムチャートである。

【図 13】図 12 のタイムチャートの説明に供する接続図である。

【図 14】基準電圧の変動の説明に供する略線図である。

【図 15】縦シェーディングを示す略線図である。

【図 16】クロストークを示す略線図である。

#### 【符号の説明】

#### 【0055】

1、11、21、31、41 …… ディスプレイ装置、2、22、32、42 …… 画素部

、3、23、33、43 …… 画素、4、24、34、44 …… 垂直駆動回路、4A、24

A、34A、44A …… ライトスキヤン回路、5、25、35、45 …… 水平駆動回路、

12 …… E L 素子、24B、34B、34C、44C …… ドライブスキヤン回路、25A

、35A、45A …… 水平セレクタ、C1、C2 …… コンデンサ、TR1 ~ TR4 …… ト

10

20

30

40

50

## ランジスタ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図16】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 4 2 A |

| G 0 9 G | 3/20  | 6 7 0 K |

| H 0 5 B | 33/14 | A       |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置和显示装置的驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP2005189643A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2005-07-14 |

| 申请号            | JP2003432738                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 申请日     | 2003-12-26 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人         | 山下淳一<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 山下淳一<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.A G09G3/20.611.D G09G3/20.624.B G09G3/20.641.D G09G3/20.642.A<br>G09G3/20.670.K H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 3K007/AB03 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 5C080/AA06 5C080/BB05 5C080<br>/DD05 5C080/DD10 5C080/DD26 5C080/DD29 5C080/EE29 5C080/FF11 5C080/HH09 5C080/JJ01<br>5C080/JJ02 5C080/JJ04 5C080/JJ05 3K107/AA01 3K107/BB01 3K107/BB03 3K107/CC14 3K107<br>/CC24 3K107/CC33 3K107/EE03 3K107/HH04 5C380/AA01 5C380/AB06 5C380/AB18 5C380/AB22<br>5C380/AB23 5C380/BA01 5C380/BB08 5C380/BD02 5C380/BD05 5C380/CA08 5C380/CA12 5C380<br>/CB01 5C380/CB17 5C380/CB26 5C380/CB27 5C380/CC01 5C380/CC02 5C380/CC27 5C380/CC30<br>5C380/CC33 5C380/CC38 5C380/CC52 5C380/CC61 5C380/CC62 5C380/CC63 5C380/CC64 5C380<br>/CD012 5C380/CD013 5C380/CD014 5C380/DA02 5C380/DA06 5C380/DA47 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

### 摘要(译)

显示装置和驱动该显示装置的方法技术领域本发明涉及一种显示装置和用于驱动该显示装置的方法，并且被应用于诸如有机EL显示装置之类的由电流驱动的自发光显示装置，以减少功耗并且进一步减少来自相邻像素的功耗。能够有效避免影响。本发明在具有源极跟随器电路配置的晶体管TR2通过由用于保持信号电平的电容器C2的端子之间的电压产生的栅极源极电压Vgs驱动发光元件12的配置中切断晶体管TR2的栅极电压。设置电压以控制发光元件12的发光和不发光。[选型图]图1