(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-31651

(P2005-31651A)

(43) 公開日 平成17年2月3日(2005.2.3)

(51) Int.Cl.<sup>7</sup>

G09F 9/30

H05B 33/14

H05B 33/26

F 1

G09F 9/30

338

テーマコード(参考)

3K007

G09F 9/30

365Z

5C094

H05B 33/14

A

H05B 33/26

Z

審査請求 未請求 請求項の数 10 O L (全 26 頁)

(21) 出願番号 特願2004-179165 (P2004-179165)

(22) 出願日 平成16年6月17日 (2004.6.17)

(31) 優先権主張番号 特願2003-172009 (P2003-172009)

(32) 優先日 平成15年6月17日 (2003.6.17)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地株式会社半

導体エネルギー研究所内

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地株式会社半

導体エネルギー研究所内

F ターム(参考) 3K007 AB02 AB17 AB18 BA06 BB07

CB00 DB03 GA00

5C094 AA04 AA14 AA25 AA44 BA03

BA27 BA43 DB10 FB14

(54) 【発明の名称】表示装置及び電子機器

## (57) 【要約】

【課題】 本発明は、トランジスタの特性バラツキにより生じる輝度ムラが抑制された表示装置を提供することを課題とする。また、本発明は、抵抗値の相違に起因した画質不良が抑制された表示装置を提供することを課題とする。

【解決手段】 本発明は、非晶質半導体又は有機半導体でチャネル部を形成するトランジスタと、トランジスタのソース電極又はドレイン電極に接続する接続配線と、画素電極と電界発光層と対向電極とが積層する発光素子と、画素電極の端部を囲む絶縁層と、トランジスタのゲート電極又は接続配線又は画素電極と同じ層に設けられた補助配線とを有する。そして、接続配線は画素電極に接続し、補助配線は絶縁層に設けられた開口部を介して対向電極に接続することを特徴とする。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

非晶質半導体又は有機半導体でチャネル部を形成するトランジスタと、

前記トランジスタのソース電極又はドレイン電極に接続する接続配線と、

画素電極と、電界発光層と、対向電極とが積層する発光素子と、

前記画素電極の端部を囲む絶縁層と、

前記トランジスタのゲート電極、前記接続配線、又は前記画素電極と同じ層に設けられた

補助配線とを有し、

前記接続配線は、前記画素電極に接続し、

前記補助配線は、前記絶縁層に設けられた開口部を介して、前記対向電極に接続すること 10

を特徴とする表示装置。

**【請求項 2】**

非晶質半導体又は有機半導体でチャネル部を形成するトランジスタと、

前記トランジスタのソース電極又はドレイン電極に接続する接続配線と、

画素電極と、電界発光層と、対向電極とが積層する発光素子と、

前記画素電極の端部を囲む絶縁層と、

前記トランジスタのゲート電極、前記接続配線、又は前記画素電極と同じ層に設けられた

補助配線と、

前記トランジスタと前記発光素子を制御する駆動回路とを有し、

前記接続配線は、前記画素電極に接続し、

前記補助配線は、前記絶縁層に設けられた開口部を介して、前記対向電極に接続し、

前記駆動回路は、非晶質半導体でチャネル部を形成するN型トランジスタと有機半導体で

チャネル部を形成するP型トランジスタの一方又は両方を有することを特徴とする表示装置。 20

**【請求項 3】**

請求項1又は請求項2において、前記トランジスタと前記発光素子を制御するドライバICを有し、

前記ドライバICは、前記トランジスタと前記発光素子が設けられた基板上に貼り付けられることを特徴とする表示装置。

**【請求項 4】**

請求項1又は請求項2において、前記トランジスタと前記発光素子を制御するドライバICを有し、

前記ドライバICは、前記トランジスタと前記発光素子が設けられた基板上に貼り付けられた接続フィルムに接続することを特徴とする表示装置。 30

**【請求項 5】**

請求項1乃至請求項4のいずれか一項において、前記トランジスタはチャネルエッチ型の

トランジスタであることを特徴とする表示装置。

**【請求項 6】**

請求項1乃至請求項4のいずれか一項において、前記トランジスタはチャネル保護型のト

ランジスタであることを特徴とする表示装置。 40

**【請求項 7】**

請求項1乃至請求項4のいずれか一項において、前記トランジスタはデュアルゲート型の

トランジスタであることを特徴とする表示装置。

**【請求項 8】**

請求項1乃至請求項4のいずれか一項において、前記発光素子と前記トランジスタは可撓

性基板上に設けられることを特徴とする表示装置。

**【請求項 9】**

請求項1乃至請求項4のいずれか一項において、前記発光素子に逆方向バイアスを印加する

逆方向バイアス印加回路を有することを特徴とする表示装置。

**【請求項 10】**

50

請求項 1 乃至 請求項 9 のいずれか一項に記載の前記表示装置を用いることを特徴とする電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、自発光型の発光素子と非晶質半導体又は有機半導体でチャネル部を形成するトランジスタを含む表示装置に関する。

【背景技術】

【0002】

近年、発光素子を有する表示装置の開発が活発に進められている。この表示装置は、既存の液晶表示装置がもつ利点の他、応答速度が速く動画表示に優れ、なおかつ視野角が広いなどの特徴を有し、次世代のフラットパネルディスプレイとして大きく注目されている。

【0003】

表示装置は、発光素子と少なくとも 2 つのトランジスタを具備した画素を複数有し、画素において発光素子と直列に接続されたトランジスタは、発光素子の発光又は非発光を制御する。トランジスタは、その高い電界効果移動度から結晶質半導体（ポリシリコン）を用いることが多い。また、発光素子は、2 つの電極間に電界発光層が挟まれた構造を有し、パターン加工された第 1 の導電膜（第 1 の電極）上に電界発光層を形成し、該電界発光層上の全面を覆うように第 2 の導電膜（第 2 の電極）を形成する。

【0004】

発光素子を制御するトランジスタとしてアモルファスシリコン TFT を用いるものがある（例えば、特許文献 1 参照）。

【特許文献 1】特開 2003-255856 号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ポリシリコンを用いたトランジスタは、結晶粒界に形成される欠陥に起因してその特性にバラツキが生じやすい。従って、トランジスタのドレイン電流にバラツキが生じていた場合、入力された信号電圧が同じであっても、そのドレイン電流が画素毎に異なってしまい、結果的に輝度ムラが生じてしまう。

【0006】

上記の実情を鑑み、本発明は、トランジスタの特性バラツキにより生じる輝度ムラが抑制された表示装置を提供することを課題とする。

【0007】

また、電界発光層上に形成された第 2 の導電膜（第 2 の電極）は、熱処理を施すことにより低抵抗化を図ることが好適である。しかしながら、電界発光層は耐熱性が低く、高温の熱処理を行うことができない。従って、抵抗値の相違により、端部と中心部とで両電極間に印加される電圧値が異なり、そのために画質不良が生じる場合がある。

【0008】

上記の実情を鑑み、本発明は、抵抗値の相違に起因した画質不良が抑制された表示装置を提供することを課題とする。

【課題を解決するための手段】

【0009】

上述した従来技術の課題を解決するために、本発明は以下の手段を講じる。

【0010】

本発明は、発光素子を駆動するトランジスタとして、非晶質半導体（代表的にはアモルファスシリコン、a-Si : H）、又は有機半導体でチャネル部を形成するトランジスタを用いることを特徴とする。前記トランジスタは、電界効果移動度などの特性にバラツキが少ない。従って、トランジスタの特性バラツキにより生じる輝度ムラを改善した表示装置

10

20

30

40

50

を提供することができる。また、非晶質半導体を用いる本発明は、数インチから数十インチの大型のパネルを作製する場合に大変有効であり、また結晶化の工程が不要でマスク数が少なくて済むので、作製費用を低減することができる。

#### 【0011】

本発明は、電界発光層上に積層される導電膜に、補助的な導電膜（配線）を接続することにより、該導電膜の低抵抗化を図ることを特徴とする。上記特徴により、熱処理を施すことなく、前記導電膜の低抵抗化を図ることができ、画質不良が抑制された表示装置を提供することができる。本特徴は、数十インチの大型のパネルを作製する場合に大変有効であり、これは、パネルのインチ数が大きくなる程、その抵抗値が問題になるためである。

#### 【0012】

本発明は、一对の電極間に発光材料を含む発光素子と、非晶質半導体でチャネル部を形成するトランジスタが複数配置された画素部及び該画素部の周辺に配置された駆動回路を含む基板と、前記基板に張り合わされたドライバICとを有する。基板上に形成された駆動回路は、非晶質半導体でチャネル部を形成するN型トランジスタ（以下a-Si:H TFTと表記することがある）と、有機半導体でチャネル部を形成するP型トランジスタ（以下有機TFTと表記することがある）を含むことを特徴とする。有機TFTは、ペンタセンなどの有機低分子、PEDOT（ポリチオフェン系）やPPV（ポリフェニレンビニレン）などの有機高分子などを含むトランジスタに相当する。このa-Si:H TFTと有機TFTは、画素部と共に同一基板上に作製することが可能であり、このCMOS回路を1つの単位回路として、シフトレジスタやバッファなどを構成することができる。また、N型トランジスタのみ、P型トランジスタのみで駆動回路を構成することも可能であり、その場合は、a-Si:H TFTのみ、有機TFTのみで駆動回路を構成することができる。

#### 【0013】

本発明は、アノード線に接続された第1の電極と、カソード線に接続された第2の電極間に発光材料を含む発光素子と、非晶質半導体でチャネル部を形成するトランジスタとを有し、前記アノード線と前記カソード線の電位を反転させて、前記発光素子に逆方向バイアスを印加する逆方向バイアス印加回路を有することを特徴とする。上記構成により、発光素子の経時劣化が抑制され、信頼性を向上させた表示装置を提供することができる。

#### 【0014】

本発明は、一对の電極間に発光材料を含む発光素子と、電位が一定に保たれた第1の電源にゲート電極が接続された第1のトランジスタと、信号線にゲート電極が接続された第2のトランジスタとを有し、前記発光素子並びに前記第1及び前記第2のトランジスタは、低電位電圧と同電位である第2の電源と、高電位電圧と同電位である第3の電源との間に直列に接続される。そして、前記第1及び前記第2のトランジスタは、非晶質半導体でチャネル部を形成することを特徴とする表示装置を提供する。

上記構成において、第2のトランジスタは線形領域で動作するために、第1のトランジスタの $V_{GS}$ の僅かな変動は発光素子の電流値に影響を及ぼさない。つまり、発光素子の電流値は、飽和領域で動作する第1のトランジスタにより決定される。従って、上記構成を有する本発明は、トランジスタの特性バラツキに起因した発光素子の輝度ムラを改善して画質を向上させた表示装置を提供することができる。

#### 【発明の効果】

#### 【0015】

上記構成を有する本発明は、トランジスタの特性バラツキにより生じる輝度ムラを改善した表示装置を提供することができる。また、熱処理を施すことなく、前記導電膜の低抵抗化を図ることができ、画質不良が抑制された表示装置を提供することができる。さらに、非晶質半導体をチャネル部とするトランジスタを含む本発明は、安価で大型の表示装置を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0016】

10

20

30

40

50

## (実施の形態 1 )

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。

## 【0017】

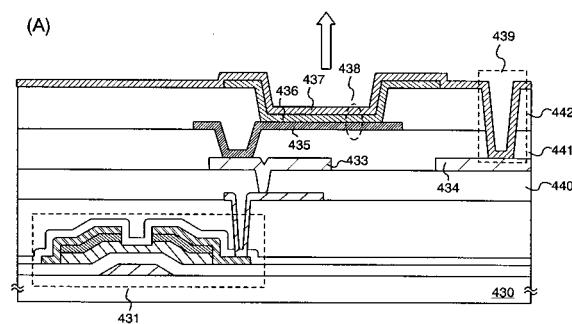

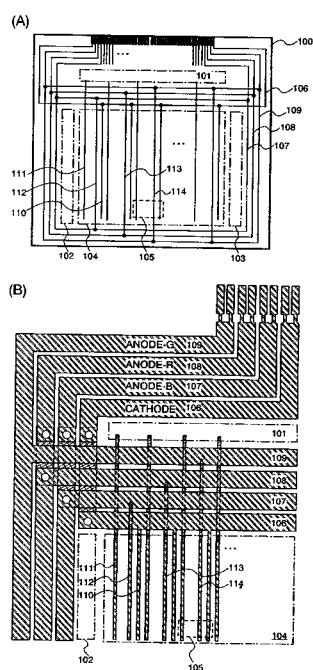

まず、パネルにおける配線の配置、特に高電位電圧 V D D と同電位である電源線（以下アノード線と表記）と、低電位電圧 V S S と同電位である電源線（以下カソード線と表記）の配置について、図 4 を用いて説明する。なお、図 4 では、画素部 104 において列方向に配置される配線のみを図示する。

## 【0018】

図 4 (A) はパネルの上面図を示したものであり、基板 100 上に、マトリクス状に複数の画素 105 が配置された画素部 104、該画素部 104 の周辺に信号線駆動回路 101、走査線駆動回路 102、103 が配置される。これらの駆動回路の個数は特に限定されず、画素 105 の構成に応じて適宜変更すればよい。また基板 100 上に一体形成せずに、COG 法などを用いてドライバ IC を貼り合わせてもよい。

## 【0019】

画素部 104 内において列方向に配置された信号線 111 は、信号線駆動回路 101 と接続する。同様に、列方向に配置された電源線 112 ~ 114 は、アノード線 107 ~ 109 のいずれかと接続する。また同様に、列方向に配置された補助配線 110 は、カソード線 106 と接続する。アノード線 107 ~ 109 及びカソード線 106 は、画素部 104 とその周辺に配置された駆動回路の周りを囲むように引き回して、FPC の端子と接続する。

## 【0020】

アノード線 107 ~ 109 は、RGB のいずれかの色に対応したものである。これは、各アノード線 107 ~ 109 の電位を変えることで、各色間で生じる輝度バラツキの補正を目的としたものである。つまり、発光素子の電界発光層の電流密度が各色で異なるために、同じ電流値を流しても各色で輝度が異なってしまう問題を改善するものである。なお、ここでは、RGB で電界発光層を塗り分ける場合を想定しているが、カラー化の方法として、白色を発光する発光素子とカラーフィルタを用いる方法など、各色での電流密度の相違が問題とならない方法を採用した場合やモノクロ表示を行う場合には、アノード線を複数本設けなくてもよい。

## 【0021】

図 4 (B) はマスクレイアウト図を簡単に示したものであり、信号線駆動回路 101 の周囲にアノード線 107 ~ 109、カソード線 106 が配置され、アノード線 107 ~ 109 は、画素部 104 内において列方向に配置された電源線 112 ~ 114 と接続する。図示するように、カソード線 106 と補助配線 110 は同じレイヤーの導電体により形成される。

## 【0022】

そして、カソード線 106 及び補助配線 110 を形成後、発光素子の第 1 の導電膜（第 1 の電極）が形成され、その後絶縁膜（土手ともよばれる）が形成される。次に、カソード線 106 及び補助配線 110 の上方に位置する絶縁膜には開口部が形成される。前記開口部の形成により、カソード線 106 及び補助配線 110 は露出した状態となり、この状態で、電界発光層が形成される。電界発光層は、カソード線 106 及び補助配線 110 の上方に形成された開口部には積層されないように塗り分けが行われる。次に、第 2 の導電膜（第 2 の電極）が全面に形成され、この際、該第 2 の導電膜は、電界発光層、カソード線 106 及び補助配線 110 上に積層して形成される。上記工程により、第 2 の導電膜は、カソード線 106 及び補助配線 110 と電気的に接続し、本実施の形態では、この構成を大きな特徴とする。本特徴により、電界発光層を覆うように形成される第 2 の導電膜の低抵

10

20

30

40

50

抗化を図ることができるため、この第2の導電膜の抵抗値に起因した画質不良を改善することができる。本特徴は、数十インチの大型のパネルを作製する場合に大変有効であり、これは、パネルのインチ数が大きくなる程、その抵抗値が問題になるためである。

#### 【0023】

なお、本実施の形態では、第2の導電膜がカソード線に接続された場合を例に挙げるが、本発明はこれに限定されない。第2の導電膜は、アノード線に接続してもよく、この場合は、発光素子の対向電極が陽極となるように設定する。

#### 【0024】

また、補助配線110を形成する層は、図4に示すように列方向に配置される信号線と同じ層の導電体に限らず、行方向に配置される走査線と同じ層の導電膜を用いてもよい。また、補助配線110と第2の導電膜とのコンタクト（接続）は、列方向に線状に設けててもよいし、点状に設けててもよいし、それらを組み合わせてもよい。また行方向に線状に設けててもよいし、点状に設けててもよいし、それらを組み合わせてもよい。そこで、以下には、いくつかの場合を例に挙げて、そのマスクレイアウト図について、図5～図7を用いて説明する。なお、図5～図7は簡略化した図面であり、画素105内には画素電極のみを図示する。また、電源線112の図示は省略する。

#### 【0025】

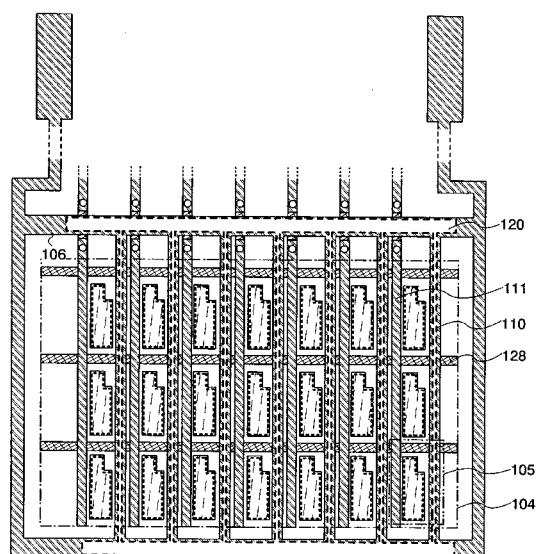

まず、補助配線110と信号線111と同じ層の導電体で形成し、線状に形成された開口部を介して、補助配線110と第2の導電膜が接続する場合について図5を用いて説明する。図5において、画素部104には複数の画素105がマトリクス状に配置され、またこの画素部104には列方向に信号線111と補助配線110、行方向に走査線128が配置される。この補助配線110はカソード線106と接続される。なお、補助配線110とカソード線106は、同じレイヤーの導電体により形成される配線であるが、ここでは、画素部104内に配置される配線を補助配線110とよび、それ以外の領域に配置される配線をカソード線106とよぶ。

#### 【0026】

そして、カソード線106と補助配線110の上方には線状の開口部120が形成され、この開口部120を介して、補助配線110及びカソード線106と、第2の導電膜とが接続する。この場合、補助配線110は、線状に形成された開口部120を介して、第2の導電膜と接続する。

#### 【0027】

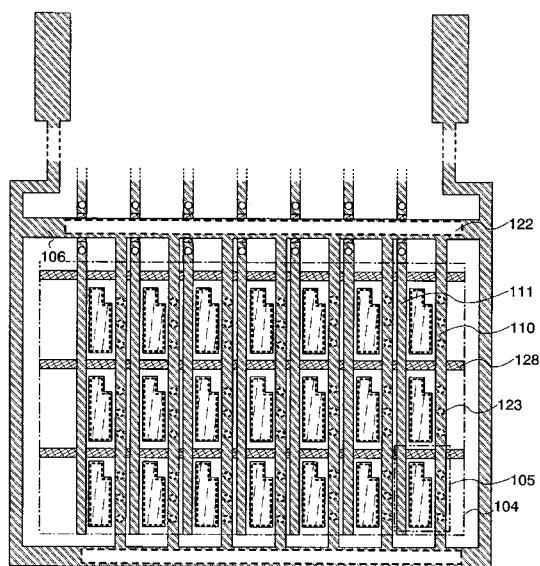

次いで、カソード線106の上方に線状の開口部122が形成され、補助配線110上に点状の開口部123が形成された場合について、図6を用いて説明する。この場合、補助配線110は、点状に形成された開口部123を介して、第2の導電膜と接続する。それ以外は、図5の構成と同じである。

#### 【0028】

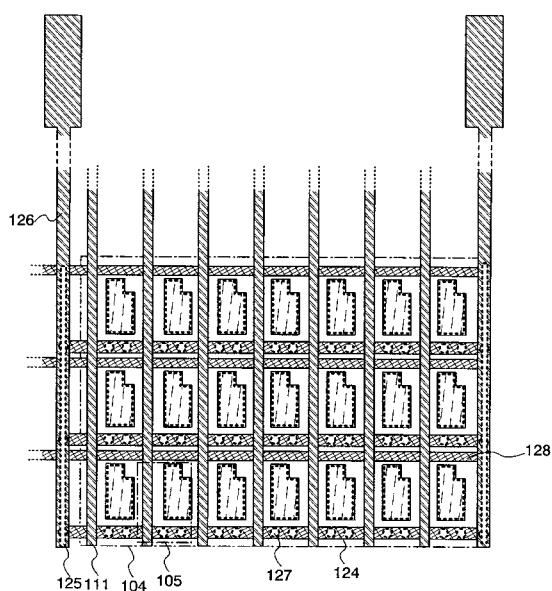

最後に、補助配線124と走査線128を同じレイヤーの導電体で形成し、点状に形成された開口部を介して、補助配線124と第2の導電膜が接続する場合について図7を用いて説明する。図7において、画素部104には複数の画素105がマトリクス状に配置され、またこの画素部104には列方向に信号線111、行方向に走査線128と補助配線124が配置される。この補助配線124は、カソード線126と接続される。補助配線124とカソード線126は、別のレイヤーの導電体により形成され、コンタクトホールを介して接続される。

#### 【0029】

そして、カソード線126の上方に線状の開口部125が形成され、補助配線124の上方に点状の開口部127が形成され、これらの開口部を介して、カソード線126及び補助配線124と、第2の導電膜とが接続する。この場合、補助配線124は、点状に形成された開口部127を介して、第2の導電膜と接続する。

#### 【0030】

このように、補助配線は、列方向に配置される配線（例えば信号線）と同じ層の導電体で

10

20

30

40

50

形成する方法(図5、6)と、行方向に配置される配線(例えば走査線)と同じ層の導電体で形成する方法(図7)が主な方法として挙げられ、これらの方法は、新たにマスクなどを作製する必要がない。従って、マスクの増加に伴う作製費用の上昇や信頼性の低減といった問題を回避することができる。また、補助配線と第2の導電膜とのコンタクトを点状に設けた場合、該コンタクトの形成箇所を画素の端部に配置すると、開口部の低減を抑制することができ、より明るい画像を提供することができる。

#### 【0031】

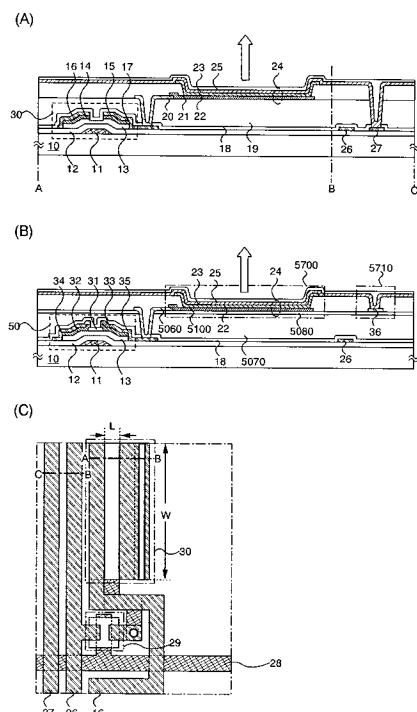

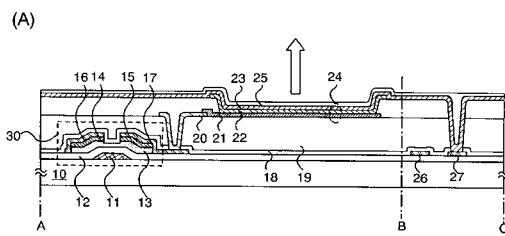

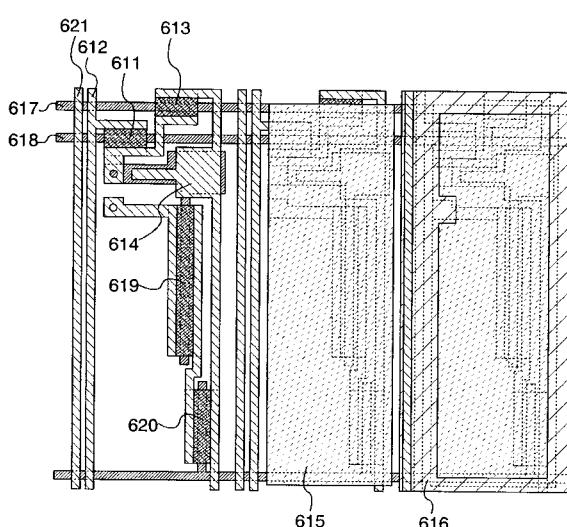

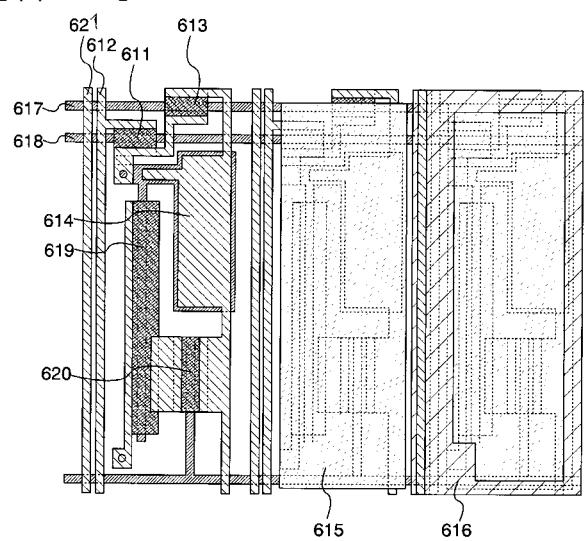

続いて、絶縁表面を有する基板上に、駆動用トランジスタ、発光素子及び補助配線を設けたときの断面構造とそのマスクレイアウト図について、図1～3を用いて説明する。

#### 【0032】

図1(C)は、1画素分のマスクレイアウトを示したものであり、列方向に電源線として機能する導電体16、信号線として機能する導電体26、補助配線として機能する導電体27が配置され、行方向に走査線として機能する導電体28が配置される。また、スイッチング用トランジスタ29と、駆動用トランジスタ30が設けられる。

#### 【0033】

図1(A)は、図1(C)のマスクレイアウト図のA-B-Cにおける断面構造を示す図に相当する。絶縁表面を有する基板10上に、ゲート電極11、該ゲート電極11上にゲート絶縁膜12が形成される。次に、非晶質半導体、N型半導体、導電体が積層して形成され、それらを同時にパターン加工して、非晶質半導体13、N型半導体14、15、導電体16、17が形成される。次に絶縁体18、19を形成し、導電体17の一部が露出するように所定の領域に開口部を形成後、導電体20が形成される。その後、導電体20と電気的に接続するように、導電体(第1の電極、画素電極)21、電界発光層22及び導電体(第2の電極、対向電極)23が形成される。この導電体21、電界発光層22及び導電体23の積層体が発光素子24に相当する。次に、保護膜25が全面に形成される。

#### 【0034】

なお、導電体16、17が形成される際、導電体26、27が同時に形成される。導電体26は信号線に相当し、導電体27は補助配線に相当する。導電体(第2の電極、対向電極)23を成膜する前に、導電体27を露出させた状態にしておくことで、導電体23と導電体27は積層して形成され、導電体23の低抵抗化が実現される。なお、図1(A)に示す断面構造では、補助配線として機能する導電体27は、導電体16、17と同じ層の導電体で形成されている。

#### 【0035】

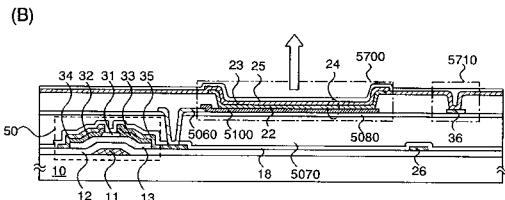

図1(B)は、駆動用トランジスタ50と発光素子24の断面構造を示す。絶縁表面を有する基板10上に、ゲート電極11、該ゲート電極11上にゲート絶縁膜12が形成される。次に非晶質半導体13が形成され、次にエッティングストップとなる絶縁体31が形成され、続いて、N型半導体、導電体が積層して形成され、それらを同時にパターン加工して、N型半導体32、33、導電体34、35が形成される。次に絶縁体18、5070、5080を形成し、導電体35の一部が露出するように所定の領域に開口部を形成後、導電体からなる接続配線5060が形成される。その後、導電体21、電界発光層22及び導電体23を含む発光素子24が形成され、その後保護膜25が形成される。

#### 【0036】

なお、導電体34、35が形成される際、導電体26が同時に形成され、また、導電体20が形成される際、導電体36が同時に形成される。導電体26は信号線に相当し、導電体36は補助配線に相当する。導電体(対向電極)23を成膜する前に、導電体36を露出させた状態にしておくことで、導電体36と導電体23は積層して形成され、導電体23の低抵抗化が実現される。なお図1(B)に示す断面構造では、補助配線として機能する導電体36は、導電体20と同じ層の導電体で形成されている。

#### 【0037】

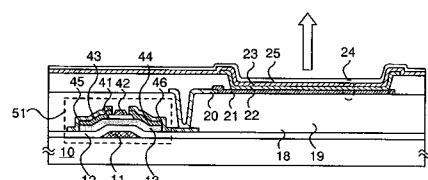

図2は、駆動用トランジスタ51と発光素子24の断面構造を示す。絶縁表面を有する基板10上に、ゲート電極11、該ゲート電極11にゲート絶縁膜12が形成される。次に

10

20

30

40

50

非晶質半導体 13 が形成され、次にエッティングストップとなる絶縁体 41 が形成され、ゲート電極 42 が形成される。続いて、N型半導体、導電体が積層して形成され、それらを同時にパターン加工して、N型半導体 43、44、導電体 45、46 が形成される。次に絶縁体 18、19 を形成し、導電体 46 の一部が露出するように所定の領域に開口部を形成後、導電体 20 が形成される。その後、導電体 21、電界発光層 22 及び導電体 23 を含む発光素子 24 が形成され、その後保護膜 25 が形成される。また、補助配線として機能する導電体 36 は、導電体 23 と電気的に接続される。

## 【0038】

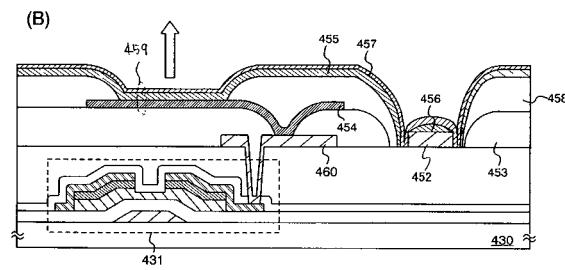

図 3 (A) は、駆動用トランジスタ 431 と発光素子 438 の断面構造を示す。絶縁表面を有する基板 430 上に、駆動用トランジスタ 431 が形成され、該駆動用トランジスタ 431 上に絶縁体 440 が形成され、所定の箇所に開口部が形成された後、該絶縁体 440 上に導電体 433、434 が形成される。続いて、画素電極に相当する導電体 435 が形成され、次に、絶縁体 442 が形成される。絶縁体 441、442 の所定の箇所に開口部 439 が形成された後、該絶縁体 442 上に電界発光層 436、該電界発光層 436 上に、対向電極に相当する導電体 437 が形成される。このように、図 3 (A) に示す構成では、4 層の絶縁体を積層した構成となっている。

## 【0039】

図 3 (B) は、駆動用トランジスタ 431 と発光素子 459 の断面構造を示す。絶縁表面を有する基板 430 上に、駆動用トランジスタ 431 が形成され、該駆動用トランジスタ 431 と電気的に接続された配線 460、補助配線 452 が形成される。その後、絶縁体 453 が形成され、該絶縁体 453 の所定の箇所に開口部が形成される。続いて、画素電極に相当する導電体 454 が形成され、該導電体 454 上に絶縁体 458 が形成され、該絶縁体 458 の所定の箇所に開口部が形成される。次に、導電体 454 上に電界発光層 455、456、該電界発光層 455、456 上に対向電極に相当する導電体 457 が形成される。導電体 454、電界発光層 455 及び導電体 457 の積層体が発光素子 459 に相当する。

## 【0040】

図 3 (B) に示す構成では、補助配線 452 上の電界発光層 456 の膜厚は薄く、また蒸着法で形成されるため、補助配線 452 の側面までには形成されない。本構成はその点を活用しており、そのために、補助配線 452 の側面と導電体 457 とは電気的に接続される。

## 【0041】

図 1～図 3 に図示したように、本発明は、非晶質半導体を有するトランジスタと、発光素子を具備する。そして、発光素子と直列に接続された駆動用トランジスタは、電流能力の向上から、チャネル幅 W / チャネル長 L = 1～100 (好ましくは 5～20) に設定することが好適である。具体的には、チャネル長を 5～15 μm、チャネル幅 W を 20～1200 μm (好ましくは 40～600 μm) に設定することが好適である。なお、チャネル幅 W とチャネル長を上記のように設定すると、画素内におけるトランジスタの占有面積が大きくなってしまう。従って、発光素子は基板と反対の方向に出射する上面出射を行うことが好ましい。

## 【0042】

非晶質半導体でチャネル部を形成するトランジスタは、大別して、チャネルエッチ型 (図 1 (A)、図 3 (A) (B))、チャネル保護型 (図 1 (B))、デュアルゲート型 (図 2) が挙げられ、本発明ではいずれを用いても構わない。

## 【0043】

発光素子を構成する一対の電極は、一方は陽極、他方は陰極に相当する。陽極及び陰極には、金属、合金、電気伝導体化合物及びこれらの混合物といった材料を用いることが好ましく、陽極には仕事関数の大きい材料、陰極には仕事関数の小さい材料を用いる。陽極と陰極の間に挟まれる電界発光層は、有機材料、無機材料の広汎に渡る材料により形成され、この電界発光層におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の

10

20

30

40

50

発光（蛍光）と、三重項励起状態から基底状態に戻る際の発光（リン光）とが含まれる。

【0044】

また、絶縁膜には、有機材料、無機材料のいずれの材料を用いてもよい。但し、有機材料は、その吸湿性に問題があるため、窒化珪素膜などのバリア膜を設けるとよい。有機材料のうち、レジスト材料は、アクリルやポリイミドといった他の有機材料よりも低コストで、コンタクトホールの径が小さく、且つ吸湿性が低いため、バリア膜を必要としないため、用いることが好適である。しかし、レジスト材料は有色であるため、上面出射型の表示装置に用いることが好適である。具体的なレジスト材料としては、クレゾール樹脂等を溶媒（プロピレングリコールモノメチルエーテルアセテート；PGMEA）を溶かした溶液が挙げられ、該溶液をスピンドル法により塗布して形成する。

10

【0045】

上記構成を有する本発明は、トランジスタの特性にバラツキが少ないため、該トランジスタの特性バラツキにより生じる輝度ムラを改善した表示装置を提供することができる。また、非晶質半導体を用いる本発明は、数インチから数十インチの大型のパネルの作製に好適である。これは、結晶化の工程が不要であり、またマスク数も少なくて済むので、作製費用を抑制することができるためである。さらに、工程における熱処理温度にもよるが、非晶質半導体は、プラスチックなどの軽量、薄型、安価の可撓性基板上に作製することができるため、表示装置の用途を広げることができる。

【0046】

また、補助配線の配置により、第2の導電膜の抵抗値を低減することができ、その結果消費電力の低減が実現する。さらに、配線抵抗による信号の書き込み不良や階調不良などの防止や、電圧降下の発生が抑制され、発光素子に対して均一な電圧を印加することができる。従って、画像品質を向上させた表示装置を提供することができる。本構成は、数十インチの大型のパネルを作製する場合に大変有効であり、これは、パネルのインチ数が大きくなる程、その抵抗値が問題になるためである。

20

【0047】

（実施の形態2）

本発明の実施の形態について図面を用いて説明する。

【0048】

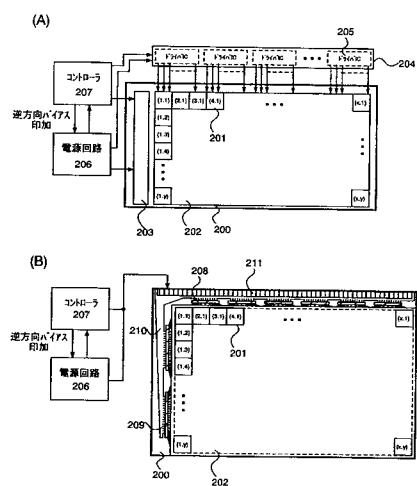

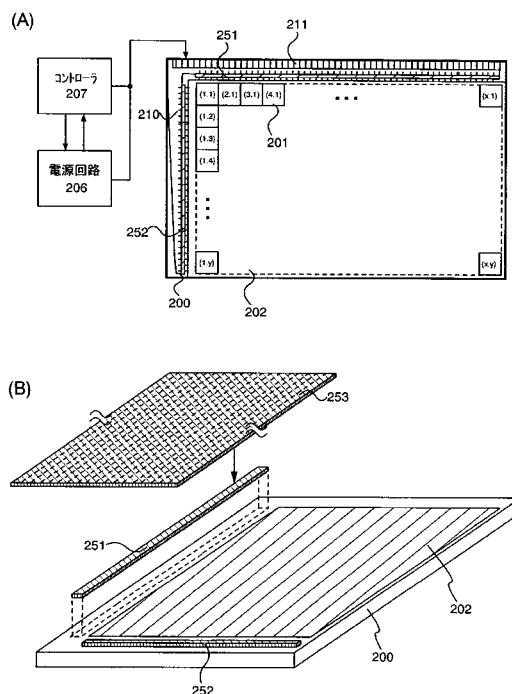

図8（A）はパネルの上面図を示したものであり、絶縁表面を有する基板200上に、マトリクス状に配置された複数の画素201を含む画素部202と走査線駆動回路203を有する。前記基板200には複数のドライバIC205が貼り付けられ、この複数のドライバIC205は信号線駆動回路204に相当する。走査線駆動回路203及び信号線駆動回路204は、電源回路206とコントローラ207に接続する。

30

【0049】

電源回路206は、パネルに電源を供給するものであり、具体的には、画素部202内に配置された電源線と接続する。この電源線はアノード線又はカソード線ともよばれ、該アノード線は高電位電圧VDDと同電位、該カソード線は低電位電圧VSSと同電位である。コントローラ207は、クロック、クロックバック、スタートパルス及びビデオ信号を信号線駆動回路204及び走査線駆動回路203に供給する役割を担う。また、本パネルのように、信号線駆動回路204として複数のドライバIC205を具備する場合には、どのドライバICにどのビデオ信号を供給するのかを決定する役割、つまり信号を振り分ける役割もある。

40

【0050】

なお図8（A）には、走査線側の駆動回路のみ基板上に一体形成する場合を示したが、本発明はこれに限定されず、その駆動回路の動作周波数によっては、同一基板上に信号線側の駆動回路も形成してもよい。但し、好適には、走査線側の駆動回路は基板上に一体形成し、信号線側の駆動回路はドライバICを用いるとよい。これは、走査線駆動回路と信号線駆動回路の各々の要求に応えるものであり、信号線駆動回路は、周波数50MHz以上（例えは65MHz以上）で駆動し、走査線駆動回路は、信号線駆動回路と比較するとそ

50

の駆動周波数は約100分の1となる100kHz程度で駆動するためである。このように、各々の駆動回路の動作周波数に応じて、基板上に集積された駆動回路を用いる方法か、ドライバICを貼り合わせる方法のどちらかを選択するとよい。

#### 【0051】

図8(B)はパネルの上面図を示したものであり、絶縁表面を有する基板200上に、マトリクス状に配置された複数の画素201を含む画素部202を有する。また、COG方式により貼り付けられた信号線側のドライバIC209と、走査線側のドライバIC208を有する。これらのドライバIC208、209は、接続配線210により、外部入力端子211に接続される。そして、外部入力端子211を介して、電源回路206とコントローラ207に接続する。なお図8(B)には、COG方式により貼り付けられた場合を示したが、本発明はこれに限定されず、TAB方式や、基板上に貼り付けずにFPCを介してドライバICと接続させてもよい。また実装するドライバICの長辺、短辺の長さやその個数も特に限定されない。

#### 【0052】

両パネルが有する各画素201は、一対の電極間に発光材料を含む発光素子と、非晶質半導体又は有機半導体でチャネル部を形成するトランジスタを有する。発光素子の第1の電極はアノード線、第2の電極はカソード線に接続され、本発明では、発光素子が発光していない期間に、アノード線とカソード線の電位を入れ替えて、該発光素子に逆方向バイアスを印加することを特徴とする。発光素子に逆方向バイアスを印加するタイミングは、コントローラ207から、所定の信号を電源回路206に供給することで行うことで決定される。従って、本発明では電源回路206とコントローラ207とをあわせて逆方向バイアス印加回路とよぶ。

#### 【0053】

ところで、本発明の表示装置を用いて多階調の画像を表示する場合、時間階調方式を用いることが好適である。これは、発光素子が発光しない期間に逆方向バイアスを印加するように設定すれば、階調表示に影響を及ぼすことなく、逆方向バイアスを印加することができるためである。

#### 【0054】

また、通常、アノード線及びカソード線の一方の配線は、全ての画素に共通で接続されている。そのため、逆方向バイアスを印加するタイミングは、全ての画素で同時にを行う必要が生じる。従って、逆方向バイアスを発光素子に印加するために、新たに半導体素子を配置してもよい。この半導体素子とは、トランジスタ又はダイオードに相当し、この半導体素子を用いることで、画素毎又はライン毎などの任意の画素毎に逆バイアスを印加することが出来るようになる。具体的には、前記半導体素子が導通状態になると同時に、発光素子に逆方向バイアスが印加されるようになる。つまり前記半導体素子が導通状態になると、ある配線と発光素子とが電気的に接続される状態になるようになる。このとき、このある配線の電位を発光素子の対向電位よりも低くしておくことで、発光素子に逆方向バイアスが印加されるようになる。逆方向バイアスを印加すると、発光素子は必然的に非発光となるが、上記構成を有する場合は、任意の画素に任意のタイミングで逆方向バイアスを印加することができるため、階調表示に影響を及ぼすことはない。この方法は、時間階調方式だけでなく、多階調を表現する方法として、アナログ駆動などの他の方式を用いた場合にも好適な方法である。

#### 【0055】

上記構成を有する本発明は、発光素子の経時劣化を抑制することができ、信頼性の向上や素子の長寿命化を実現した表示装置を提供することができる。本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

#### 【0056】

##### (実施の形態3)

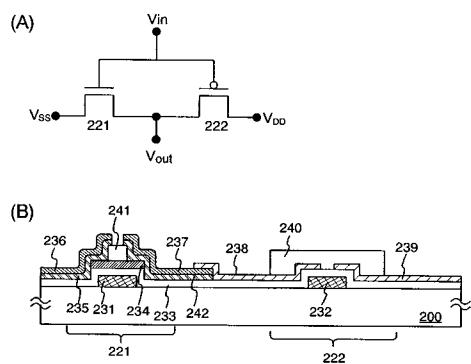

本実施の形態では、非晶質半導体でチャネル部を形成するN型トランジスタと、有機半導体でチャネル部を形成するP型トランジスタを含むCMOS回路の断面構造について、図

10を用いて説明する。

【0057】

図10(A)は等価回路図であり、P型トランジスタ221とN型トランジスタ222が直列に接続され、一端はVDD、他端はVSSと同電位に設定されている。図10(B)は、これらのトランジスタの断面構造を示したものであり、基板200上に導電体231、232が設けられ、該導電体231、232上に窒化シリコン233が設けられる。次に、窒化シリコン233上に非晶質半導体234が設けられ、該非晶質半導体234上に再度窒化シリコン241が設けられる。次に、窒化シリコン241上にN型半導体と導電体が積層して設けられ、これらを同時にパターン加工して、N型半導体235、242、電極236、237が設けられる。その後、電極238、239が設けられ、続いて、チャネル層となる有機半導体240を設けられる。有機半導体240としては、ペントセンなどの有機低分子、PEDOTやPPVなどの有機高分子などを用いればよく、ペントセンのパターン加工には、蒸着法にメタルマスクを併用する方法を用いるとよい。このようにして、非晶質半導体234でチャネル部を形成するN型トランジスタと、有機半導体240でチャネル部を形成するP型トランジスタを含むCMOS回路が完成する。

【0058】

このCMOS回路は、シフトレジスタやバッファなどを構成するクロックドインバータ等の単位回路となるため、駆動回路に用いてもよいし、また画素回路に用いてもよい。また本構成は、その動作周波数から、走査線側の駆動回路に用いることが好適である。具体的には、図8(A)に示すように、走査線側の駆動回路を本構成のCMOS回路で形成し、信号線側の駆動回路としてドライバICを用いることが好適である。なお本実施の形態では、CMOS回路で駆動回路を構成する場合を説明したが、本発明はこれに限定されない。勿論、N型トランジスタ(a-Si:HTFT)のみ、P型トランジスタ(有機TFT)のみで駆動回路を構成しても構わない。

【0059】

本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

【0060】

(実施の形態4)

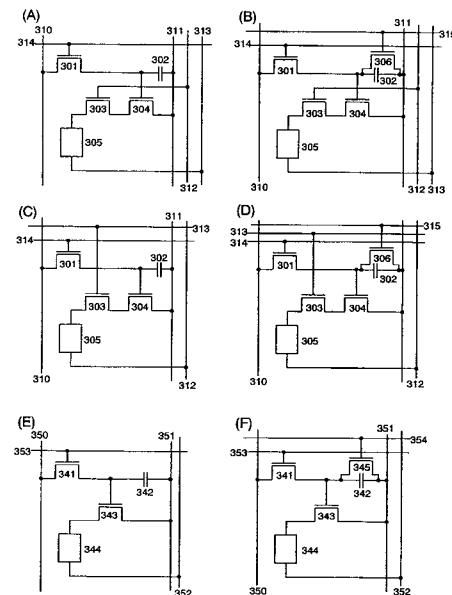

本発明は、一対の電極間に発光材料を含む発光素子と、非晶質半導体、又は有機半導体でチャネル部を形成するトランジスタを含む画素を複数有する表示装置を提供するものであり、ここでは、該画素の構成について、図11を用いて説明する。

【0061】

図11(A)に示す画素は、列方向に信号線310及び電源線311～313、行方向に走査線314が配置される。また、スイッチング用のトランジスタ301、駆動用のトランジスタ303、電流制御用のトランジスタ304、容量素子302及び発光素子305を有する。

【0062】

図11(C)に示す画素は、トランジスタ303のゲート電極が、行方向に配置された電源線313に接続される点が異なっており、それ以外は図11(A)に示す画素と同じ構成である。つまり、図11(A)(C)に示す両画素は、同じ等価回路図を示す。しかしながら、行方向に電源線312が配置される場合(図11(A))と、列方向に電源線312が配置される場合(図11(C))では、各電源線は異なる層の導電体で形成される。ここでは、トランジスタ303のゲート電極が接続される配線に注目し、これらを作製する層が異なることを表すために、図11(A)(C)として分けて記載する。

【0063】

図11(A)(C)に示す画素の特徴として、画素内にトランジスタ303、304が直列に接続されており、トランジスタ303のチャネル長L<sub>3</sub>、チャネル幅W<sub>3</sub>、トランジスタ304のチャネル長L<sub>4</sub>、チャネル幅W<sub>4</sub>は、L<sub>3</sub>/W<sub>3</sub>:L<sub>4</sub>/W<sub>4</sub>=5~6000:1を満たすように設定される点が挙げられる。6000:1を満たす場合の一例としては、L<sub>3</sub>が500μm、W<sub>3</sub>が3μm、L<sub>4</sub>が3μm、W<sub>4</sub>が100μmの場合がある。

10

20

30

40

50

## 【0064】

なお、トランジスタ303は、飽和領域で動作し発光素子305に流れる電流値を制御する役目を有し、トランジスタ304は線形領域で動作し発光素子305に対する電流の供給を制御する役目を有する。両トランジスタは同じ導電型を有していると作製工程上好ましい。またトランジスタ303には、エンハンスマント型だけでなく、ディブリーション型のトランジスタを用いててもよい。上記構成を有する本発明は、トランジスタ304が線形領域で動作するために、トランジスタ304の $V_{GS}$ の僅かな変動は発光素子305の電流値に影響を及ぼさない。つまり、発光素子305の電流値は、飽和領域で動作するトランジスタ303により決定される。上記構成を有する本発明は、トランジスタの特性バラツキに起因した発光素子の輝度ムラを改善して画質を向上させた表示装置を提供することができる。10

## 【0065】

図11(A)～(D)に示す画素において、トランジスタ301は、画素に対するビデオ信号の入力を制御するものであり、トランジスタ301がオンして、画素内にビデオ信号が入力されると、容量素子302にそのビデオ信号が保持される。なお図11(A)(C)には、容量素子302を設けた構成を示したが、本発明はこれに限定されず、ビデオ信号を保持する容量がゲート容量などでもかなうことが可能な場合には、明示的に容量素子302を設けなくてもよい。

## 【0066】

発光素子305は、2つの電極間に電界発光層が挟まれた構造を有し、順バイアス方向の電圧が印加されるように、画素電極と対向電極の間(陽極と陰極の間)に電位差が設けられる。電界発光層は有機材料や無機材料等の広汎に渡る材料により構成され、この電界発光層におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光(蛍光)と、三重項励起状態から基底状態に戻る際の発光(リン光)とが含まれる。20

## 【0067】

図11(B)に示す画素は、トランジスタ306と走査線315を追加している以外は、図11(A)に示す画素構成と同じである。同様に、図11(D)に示す画素は、トランジスタ306と走査線315を追加している以外は、図11(C)に示す画素構成と同じである。

## 【0068】

トランジスタ306は、新たに配置された走査線315によりオン又はオフが制御される。トランジスタ306がオンになると、容量素子302に保持された電荷は放電し、トランジスタ306がオフする。つまり、トランジスタ306の配置により、強制的に発光素子305に電流が流れない状態を作ることができる。従って、図11(B)(D)の構成は、全ての画素に対する信号の書き込みを待つことなく、書き込み期間の開始と同時に直後に点灯期間を開始することができるため、デューティ比を向上することが可能となる。30

## 【0069】

図11(E)に示す画素は、列方向に信号線350、電源線351、352、行方向に走査線353が配置される。また、スイッチング用トランジスタ341、駆動用トランジスタ343、容量素子342及び発光素子344を有する。図11(F)に示す画素は、トランジスタ345と走査線354を追加している以外は、図11(E)に示す画素構成と同じである。なお、図11(F)の構成も、トランジスタ345の配置により、デューティ比を向上することが可能となる。40

## 【0070】

本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

## 【実施例1】

## 【0071】

本発明の必須の構成要素として、一対の電極間に発光材料を含む発光素子と、非晶質半導体又は有機半導体を含むトランジスタが挙げられ、該発光素子と該トランジスタは各画素50

に具備されている。このように、非晶質半導体を含むトランジスタを各画素に含む場合、多くの場合において、ドライバＩＣをCOG方式やTAB方式により実装したり、FPCを介して接続したりする。本実施例では、矩形上の基板に複数のドライバＩＣを形成し、該ドライバＩＣを実装する実施例について説明する。

【0072】

図9(A)に示すパネルの上面図は、走査線側と信号線側の各々に1つのドライバＩＣ251、252が設けられている。それ以外の構成は、図8(B)に示すパネルと同じであるため、ここでは説明を省略する。

【0073】

図9(B)は、基板にドライバＩＣを貼り付ける様子を示した斜視図である。基板253上には、複数の駆動回路と該複数の駆動回路を接続する入出力端子が設けられる。各駆動回路と、当該駆動回路に対応した入力出力端子を1つのユニットとして、基板253を短冊状又は矩形状に分断すると、複数のドライバＩＣが得られる。そして、このドライバＩＣを基板200に貼り合わせると、表示装置が完成する。図9(B)では、走査線駆動回路に相当するドライバＩＣ252と、信号線駆動回路に相当するドライバＩＣ251が実装された形態を示す。

【0074】

信号線及び走査線のピッチは、ドライバＩＣの出力端子のピッチと合わせることが好適である。そうすると、画素部202の端部で数ブロック毎に区分して引出線を形成する必要がなく、プロセス上、歩留まりよく作製することができる。また、これらのドライバＩＣは、矩形状の基板200上に複数個作り込むと、大量に形成することができるため、生産性を向上させる観点から好ましい。従って、基板200として、大面積の基板を用いることが好ましく、例えば、一辺が300mmから1000mm程度の大面積の基板を用いることが好ましい。これは、円形のシリコンウェハからＩＣチップを取り出す場合と比較すると、大きな優位点である。さらに、切り出す際、ドライバＩＣの長辺の長さを、画素部202の縦方向又は横方向の長さと同じ長さにすると、貼り付けるドライバＩＣの個数が減少させることができ、信頼性が向上する。

【0075】

また、これらのドライバＩＣは結晶質半導体により形成されることが好適であり、前記結晶質半導体は連続発振のレーザ光を照射することで形成されることが好適である。従って、当該レーザ光を発生させる発振器としては、連続発振の固体レーザ又は気体レーザを用いることが好適である。これは、連続発振のレーザ光を照射すると、その走査方向に、結晶粒界が延びることを活用するものであり、結晶粒界が延びた方向とチャネル長方向とが平行になるように、半導体層をパターン加工すると、十分な電気的特性が得られた結晶質半導体を活性層として用いた薄膜トランジスタを形成することができるためである。

【0076】

ドライバＩＣの構成は、走査線側と信号線側で異なる構成であることが好適である。具体的には、信号線側に配置する駆動回路と、走査線側に配置する駆動回路とで、薄膜トランジスタのゲート絶縁膜の膜厚を変えることが好適である。これは、信号線(データ線)側と走査線側の各々の要求に応えるものであり、具体的には、信号線駆動回路を構成する薄膜トランジスタのゲート絶縁膜の厚さは20~70nm、チャネル長は0.3~1μmに設定する。一方、走査線駆動回路を構成する薄膜トランジスタのゲート絶縁膜の厚さは150~250nm、チャネル長は1~2μmに設定する。上記構成により、各々の駆動回路の動作周波数に応じたドライバＩＣを有する表示装置を提供することができる。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

【実施例2】

【0077】

本発明の必須の構成要素として、一対の電極間に発光材料を含む発光素子と、非晶質半導体又は有機半導体を含むトランジスタが挙げられ、該発光素子と該トランジスタは各画素に具備される。このような、非晶質半導体を含むトランジスタは、その電気特性(しきい

10

20

30

40

50

値電圧、電界効果移動度等)が経時的に変化する性質を有する。そこで、ここでは、しきい値電圧に注目し、しきい値補正回路について説明する。

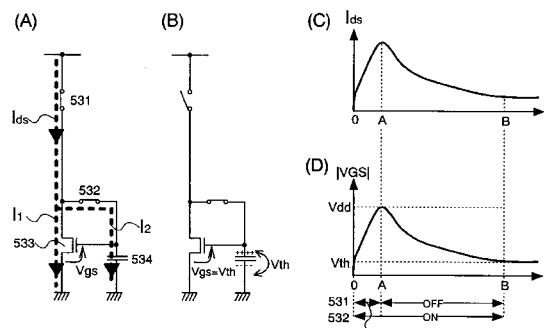

【0078】

まず、しきい値補正回路について、図17(A)~(D)を用いて説明する。図17(A)は等価回路図を示し、トランジスタ等からなるスイッチ531、532、トランジスタ533、容量素子534を有する。この回路の動作について、以下に簡単に説明する。

【0079】

まず、スイッチ531、532をオンにする(図17(A))。そうすると、スイッチ531からトランジスタ533の方向と、スイッチ531から容量素子534の方向に向かって電流 $I_{DS}$ が流れる。このとき、電流 $I_{DS}$ は $I_1$ と $I_2$ に分かれて流れ、 $I_{DS} = I_1 + I_2$ を満たす。電流が流れ始めた瞬間には、容量素子534に電荷は保持されず、トランジスタ533はオフである。従って、 $I_2 = 0$ 、 $I_{DS} = I_1$ である。しかしながら、徐々に容量素子534に電荷が蓄積されて、容量素子534の両電極間に電位差が生じ始める。両電極間の電位差が $V_{TH}$ になると、トランジスタ534がオンになり、 $I_2 > 0$ となる。このとき、 $I_{DS} = I_1 + I_2$ を満たすので、 $I_1$ は次第に減少するが、以前電流は流れている。そして、容量素子534では、その両電極間の電位差が $V_{DD}$ になるまで、電荷の蓄積が続けられる。容量素子534の両電極間の電位差が $V_{DD}$ になると、 $I_2$ は流れなくなり、トランジスタ533はオンであるため、 $I_{DS} = I_1$ となる(図17(C)(D)、A点)。

【0080】

続いて、スイッチ531をオフにする(図17(B))。そうすると、容量素子534に保持された電荷は、スイッチ532を介してトランジスタ533の方向に流れていき、放電する。この動作は、トランジスタ533がオフになるまで行われる。つまり、容量素子534に保持された電荷が、トランジスタ533のしきい値電圧と同じ値になるまで電荷が保持される(図17(C)(D)、B点)。

【0081】

このようにすると、容量素子の両電極間の電位差を、あるトランジスタのしきい値電圧と同じ値になるように設定することができる。そして、トランジスタの $V_{GS}$ をそのまま保持して、該トランジスタのゲート電極に信号電圧を入力する。そうすると、トランジスタのゲート電極には、容量素子に保持されている $V_{GS}$ に加えて、前記信号電圧を上乗せした値が入力される。つまり、トランジスタ間のしきい値電圧にバラツキが生じていても、信号電圧が入力されるトランジスタは、常に該トランジスタのしきい値電圧と信号電圧を足した値が入力される。従って、トランジスタ間のしきい値電圧のバラツキの影響を抑制することができる。

【0082】

しきい値補正回路を設けることで、発光素子を駆動する駆動用トランジスタのしきい値電圧のバラツキを抑制することができ、これらのバラツキに起因した輝度ムラを改善して、高画質の画像を表示する表示装置を提供することができる。なお、本実施例で示したしきい値補正回路は、図11に図示した画素回路にも適用することができる。その際、ゲート電極に信号電圧が入力される駆動用トランジスタのしきい値電圧を補正できるように、本しきい値補正回路を設けるとよい。

【0083】

なお本実施例では、しきい値電圧の補正手段を例示したが、他の電気特性の補正手段を有していてもよく、例えば、電界効果移動度の補正手段を設けてもよい。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

【実施例3】

【0084】

発光素子は、正孔注入層、正孔輸送層、正孔阻止層(ホールプロッキング層)、電子輸送層等が適宜組み合わされて形成される。但し、電子注入層は、電子のみの輸送性に優れた材料として知られているバソキュプロイン(BCP)にリチウム(Li)をドーピングし

10

20

30

40

50

た場合に電極からの電子注入性を著しく向上させることができるとよい。

【0085】

また、ベンゾオキサゾール誘導体（BzOS）、又はピリジン誘導体が、優れた電子輸送性を有し、かつ成膜した場合に結晶化しにくい材料であり、さらにアルカリ金属、アルカリ土類金属、または遷移金属のうちの少なくとも一種を含むことにより電子注入性に優れた層を形成する。そこで、一対の電極間に発光物質を含む層を有する発光素子において、発光物質を含む層の一部にベンゾオキサゾール誘導体、又はピリジン誘導体を用いることが好適である。

【0086】

つまり、ベンゾオキサゾール誘導体、又はピリジン誘導体と、アルカリ金属、アルカリ土類金属、または遷移金属のうちの少なくとも一種とを含む発光素子用電子注入性組成物を用いて電子注入層を形成することにより、陰極として機能する電極からの電子注入性を高めることができる。さらに、ピリジン誘導体は成膜した場合に結晶化しにくい材料であることから、従来よりも素子特性に優れ、素子寿命の長い発光素子、およびそれを用いた表示装置を提供することができる。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

【実施例4】

【0087】

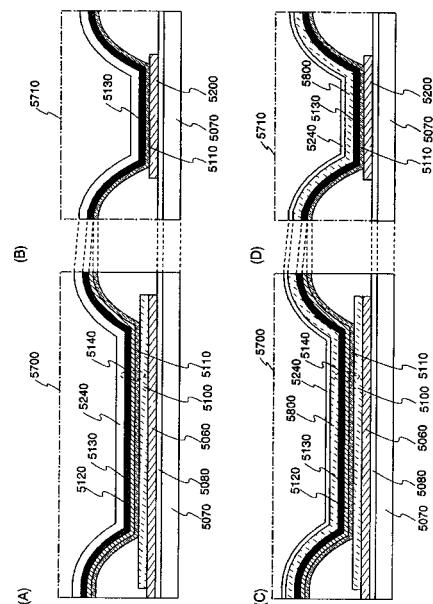

本実施例では、発光素子の積層構造について説明する。ここでは、図1(B)において、破線5700、5710で囲んだ部分の拡大図を用いて説明する。なお、図18(A)(C)、図19(A)は、破線5700で囲んだ部分の拡大図に相当し、図18(B)(D)、図21(B)は、破線5710で囲んだ部分の拡大図に相当する。なお、図1(B)の断面構造と、図18、19に示す断面構造とは、絶縁膜5070、パッシベーション膜5080、接続配線5060及び画素電極5100が形成されている点は同じであるが、それ以外の構造は異なっており、以下には、異なる符号を用いて説明する。

【0088】

図18(A)(B)において、絶縁膜5070上にパッシベーション膜5080が形成され、該パッシベーション膜5080上に接続配線5060が形成される。この接続配線5060は、駆動用トランジスタのソース電極又はドレイン電極と電気的に接続されている。また、パッシベーション膜5080上には、接続配線5060と共に導電体をパターン加工することで得られた補助配線5200が形成される。そして接続配線5060に接続するように画素電極5100が形成され、該画素電極5100上に正孔注入層5110、発光層5120、電子注入層5130が順に積層される。最後に、保護膜5240が形成される。画素電極5100、正孔注入層5110、発光層5120及び電子注入層5130との積層体が発光素子5140に相当する。

【0089】

この発光層5120は、開口部を完全に覆わず、補助配線5200の一部を露出させるように、メタルマスクを用いて形成する。従って、開口部においては、補助配線5200上に、正孔注入層5110、電子注入層5130が順に積層されている。なお、本発明はこれに限定されず、正孔注入層5110及び発光層5120を、メタルマスクを用いて形成することで、補助配線5200上に電子注入層5130のみが形成された構成としてもよい。

【0090】

また、図18(A)(B)では、発光素子5140から発せられる光が基板側に出射する構成を示すが、光が基板側とは反対側に向かう構造を有していてもよい。

【0091】

図18(C)(D)に示す断面構造は、接続配線5060と接続するように、画素電極5100が形成され、該画素電極5100上に正孔注入層5110、発光層5120、電子注入層5130、透明導電膜5800が順に積層される。最後に保護膜5240が形成さ

10

20

30

40

50

れる。電子注入層 5130 に接するように透明導電膜 5800 を形成することで、対向電極として機能する電子注入層 5130 自体の抵抗が高まても、電位降下を抑えることができる。

【0092】

この発光層 5120 は、開口部を完全に覆わず、補助配線 5200 の一部を露出させるように、メタルマスクを用いて形成する。従って、開口部においては、補助配線 5200 上に、正孔注入層 5110、電子注入層 5130、透明導電膜 5800 が順に積層されている。なお、本発明はこれに限定されず、正孔注入層 5110 及び発光層 5120 を、メタルマスクを用いて形成することで、補助配線 5200 上に電子注入層 5130 及び透明導電膜 5800 のみが形成された構成としてもよい。また、正孔注入層 5110、発光層 5120 及び電子注入層 5130 を、メタルマスクを用いて形成することで、補助配線 5200 上に透明導電膜 5800 のみが形成された構成としてもよい。10

【0093】

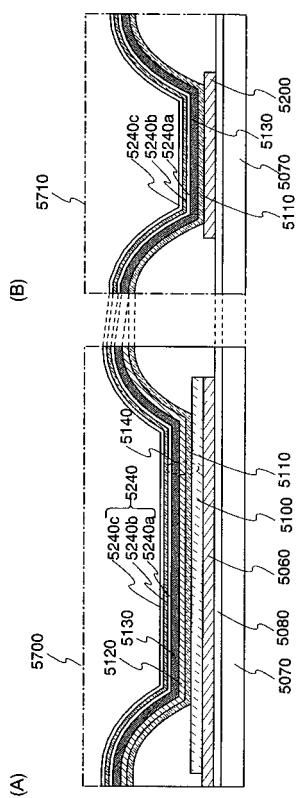

なお、図 18 (A) (B) において、保護膜 5240 は、無機絶縁膜と有機絶縁膜の積層構造を有していてもよく、そのときの断面構造について、図 19 (A) (B) を用いて説明する。

【0094】

図 19 (A) (B) において、保護膜 5240 は積層構造を有しており、電子注入層 5130 に接するように無機絶縁膜 5240a、該無機絶縁膜 5240a 上に有機樹脂膜 5240b、該有機樹脂膜 5240b 上に無機絶縁膜 5240c が形成される。無機絶縁膜 5240a、5240c としては、窒化珪素、窒化酸化珪素、酸化アルミニウム、窒化アルミニウム等を用いることで、発光素子 5140 に対する水分や酸素の劣化を促進させる物質の侵入を防止することができる。また、無機絶縁膜 5240a と無機絶縁膜 5240c との間に、内部応力が小さい有機樹脂膜 5240b を設けることで、保護膜 5240 が応力によって剥離することを防止することができる。この有機樹脂膜 5240b としては、ポリイミド、ポリアミド、ポリイミドアミド等を用いることができる。20

【0095】

この発光層 5120 は、開口部を完全に覆わず、補助配線 5200 の一部を露出させるように、メタルマスクを用いて形成する。従って、開口部においては、補助配線 5200 上に、正孔注入層 5110、電子注入層 5130、無機絶縁膜 5240a、有機樹脂膜 5240b 及び無機絶縁膜 5240c が順に積層されている。なお、本発明はこれに限定されず、正孔注入層 5110 及び発光層 5120 を、メタルマスクを用いて形成することで、補助配線 5200 上に電子注入層 5130、無機絶縁膜 5240a、有機樹脂膜 5240b 及び無機絶縁膜 5240c が順に形成された構成としてもよい。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。30

【実施例 5】

【0096】

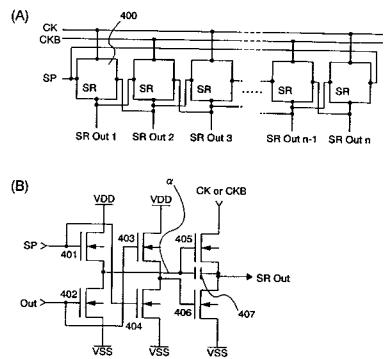

本発明の必須の構成要素として、一対の電極間に発光材料を含む発光素子と、非晶質半導体又は有機半導体を含むトランジスタが挙げられ、該発光素子と該トランジスタは各画素に具備される。このようなトランジスタを各画素に含む場合、同一基板上に形成する駆動回路も非晶質半導体又は有機半導体を含むトランジスタにより形成することが好適である。但し、非晶質半導体を含むトランジスタは N 型トランジスタしか形成できない。そこで、本実施例では、N 型トランジスタのみでシフトレジスタを構成する例について説明する。40

【0097】

図 12 (A) において、400 で示すブロックが 1 段分のサンプリングパルスを出力するパルス出力回路に相当し、シフトレジスタは n 個のパルス出力回路により構成される。図 12 (B) は、パルス出力回路 400 の具体的な構成を示したものであり、N 型のトランジスタ 401 ~ 406 と、容量素子 407 を有する。このパルス出力回路は、ブーストストラップ法を応用することで、N 型トランジスタのみでの構成が可能となった回路である。50

詳しい動作については、特開2002-335153号公報に記載されているため、本公報を参考にするとよい。

【0098】

なお本実施例では、N型トランジスタのみで構成する例を示したが、本発明はこれに限定されない。チャネル部に有機半導体を含むP型トランジスタで駆動回路を構成してもよい。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

【実施例6】

【0099】

本発明の表示装置をデジタル駆動する場合、多階調の画像を表現するためには時間階調方式を用いることが好適である。本実施例は時間階調方式について説明するものであり、図13(A)は、縦軸は走査線、横軸は時間のときのタイミングチャートを示し、図13(B)はj行目の走査線のタイミングチャートを示す。

【0100】

表示装置は、そのフレーム周波数を通常60Hz程度とする。つまり、1秒間に60回程度の画面の描画が行われ、画面の描画を1回行う期間を1フレーム期間と呼ぶ。時間階調方式では、1フレーム期間を複数のサブフレーム期間に分割する。このときの分割数は、階調ビット数に等しい場合が多く、ここでは簡単のために、分割数が階調ビット数に等しい場合を示す。つまり本実施例では5ビット階調を例示しているので、5つのサブフレーム期間SF1～SF5に分割した例を示す。各サブフレーム期間は、画素にビデオ信号を書き込むアドレス期間Taと、画素が点灯又は非点灯するサステイン期間Tsを有する。サステイン期間Ts1～Ts5は、その長さの比をTs1：…：Ts5 = 16：8：4：2：1とする。つまり、nビット階調を表現する場合、n個のサステイン期間は、その長さの比を $2^{(n-1)} : 2^{(n-2)} : \dots : 2^1 : 2^0$ とする。

【0101】

そして、書き込み期間よりも短い点灯期間を有するサブフレーム期間（ここではサブフレーム期間SF5が該当）は消去期間Te5を有する。消去期間Te5は、画素に書き込まれたビデオ信号をリセットし、発光素子が強制的にリセットされる期間であり、点灯期間の終了後、直ちに次の期間が開始しないようにする。

【0102】

なお、表示階調数を増やしたい場合は、サブフレーム期間の分割数を増やせば良い。また、サブフレーム期間の順序は、必ずしも上位ビットから下位ビットといった順序である必要はなく、1フレーム期間中、ランダムに並んでいても良い。さらにフレーム期間毎に、その順序が変化してもよい。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

【実施例7】

【0103】

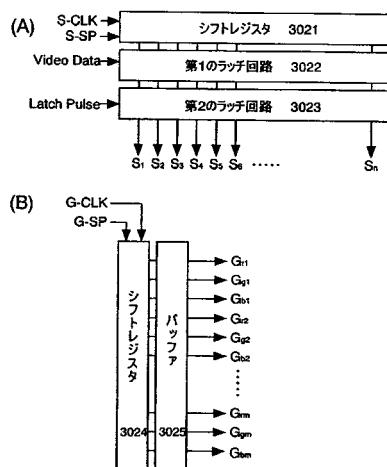

本実施例では、信号線駆動回路と走査線駆動回路の構成の一例について、図14を用いて説明する。

【0104】

図14(A)に示すように、信号線駆動回路は、シフトレジスタ3021、第1のラッチ回路3022及び第2のラッチ回路3023を有する。また、図14(B)に示すように、走査線駆動回路は、シフトレジスタ3024、バッファ3025を有する。但し図示する構成はあくまで一例であり、例えば、信号線駆動回路にレベルシフタやバッファを新たに配置した構成にしたり、走査線駆動回路において、シフトレジスタ3024とバッファ3025の間にレベルシフタを配置した構成にしたりしてもよい。レベルシフタを配置すると、ロジック回路部とバッファ部の電圧振幅を変えることが出来る。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

【実施例8】

【0105】

本発明を適用して作製される電子機器の一例として、ビデオカメラ、デジタルカメラ、ゴ

10

20

30

40

50

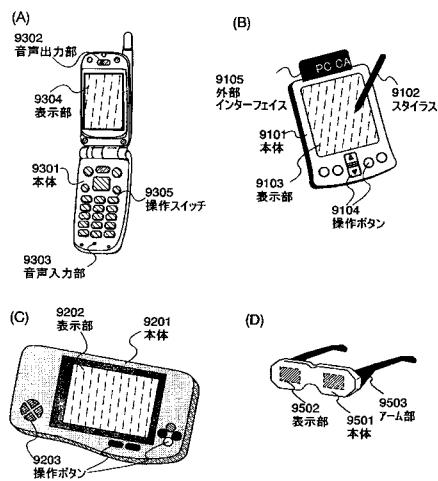

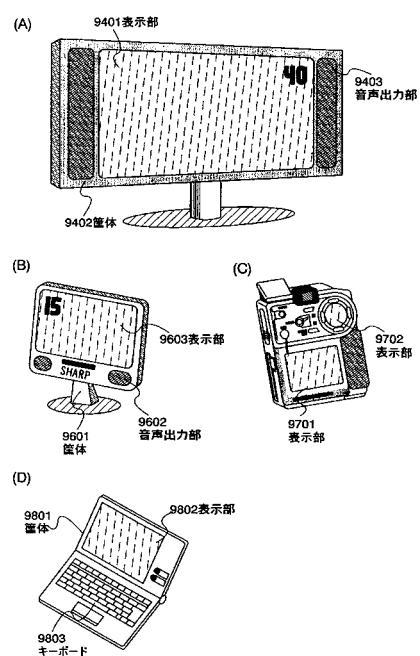

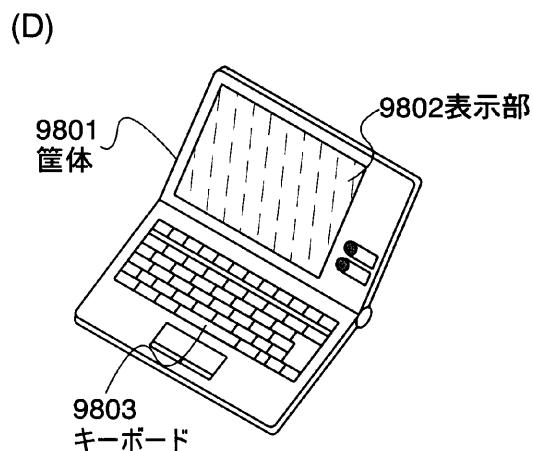

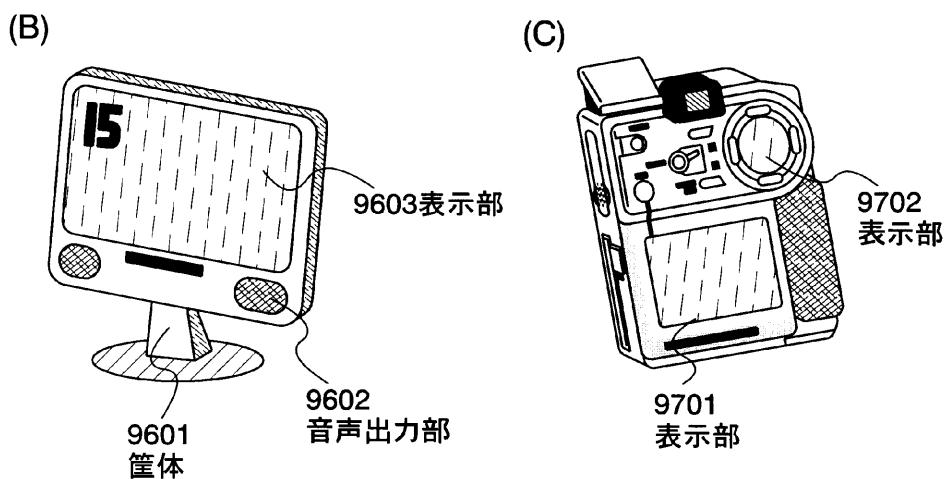

ーグル型ディスプレイ、ナビゲーションシステム、カーオーディオなどの音響再生装置、ノート型パソコンコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等)、家庭用ゲーム機などの記録媒体を備えた画像再生装置(具体的にはDVD等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。それら電子機器の具体例を図15、16に示す。

【0106】

図15(A)は、携帯端末であり、本体9301、音声出力部9302、音声入力部9303、表示部9304及び操作スイッチ9305等を含む。図15(B)はPDAであり、本体9101、スタイルス9102、表示部9103、操作ボタン9104及び外部インターフェース9105等を含む。図15(C)は、携帯型ゲーム機器であり、本体9201、表示部9202及び操作ボタン9203等を含む。図15(D)は、ゴーグル型ディスプレイであり、本体9501、表示部9502及びアーム部9503等を含む。

【0107】

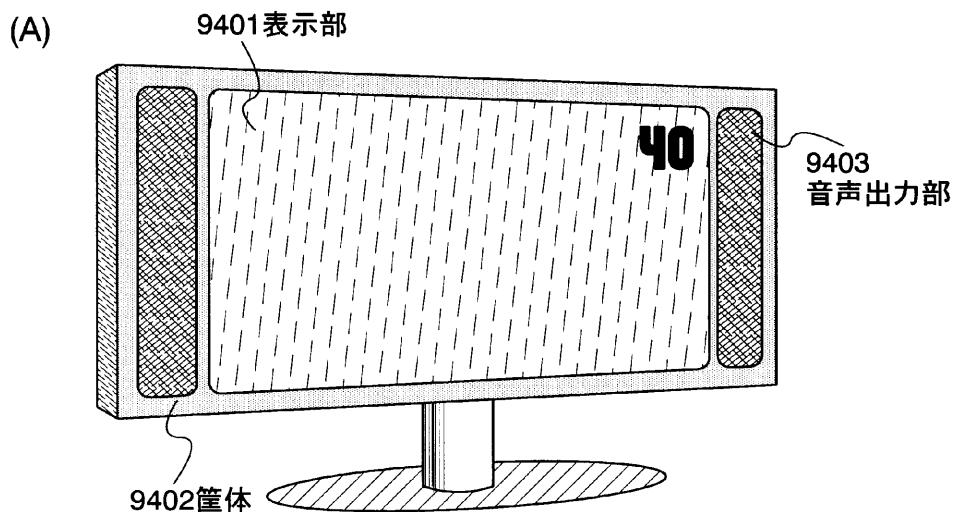

図16(A)は、40インチ程度の大型の液晶テレビであり、表示部9401、筐体9402及び音声出力部9403等を含む。図16(B)は、モニターであり、筐体9601、音声出力部9602及び表示部9603等を含む。図16(C)は、デジタルビデオカメラであり、表示部9701、9702等を含む。図16(D)は、ノートパソコンであり、筐体9801、表示部9802及びキーボード9803等を含む。

【0108】

上記に挙げた電子機器において、表示部9304、9103、9202、9502、9401、9603、9701、9702及び9802を含むパネルには、本発明の表示装置を用いることが好適である。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

【実施例9】

【0109】

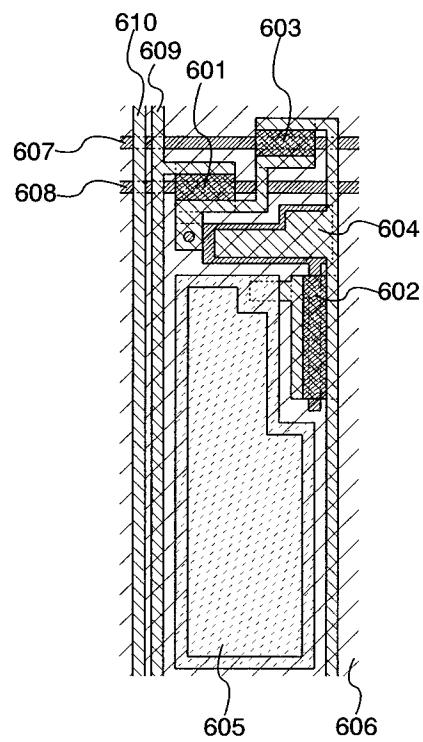

本実施例では、実施の形態4で説明した画素回路のレイアウト例について説明する。これから説明するレイアウト例では、発光素子が含む画素電極と、当該画素電極の端部を囲む絶縁層までを形成した場合を示す。また、図21～23で示すレイアウト例では、隣接する3つの画素を示し、1つの画素はトランジスタと容量素子までを形成したときのレイアウト、1つの画素は画素電極までを形成したときのレイアウト、1つの画素は隔壁層として機能する絶縁層までを形成したときのレイアウトを示す。

【0110】

1つのレイアウト例と2つ目のレイアウト例は、1つの画素に3つのトランジスタが設けられた場合(3 TFT / Cell)であり、スイッチング用のトランジスタ601、駆動用のトランジスタ602、消去用のトランジスタ603、容量素子604、列方向に配置された信号線609と補助配線610、行方向に配置された走査線607、608が設けられる(図20、21参照)。また、発光素子が含む画素電極605と絶縁層606が設けられる。

絶縁層606は、隣接する画素電極605の間に設けられている。また、絶縁層606には、補助配線610と画素電極605が露出するように、開口部が設けられている。絶縁層606に設けられた開口部を介して、補助配線610と対向電極とが接続する。また、絶縁層606に設けられた開口部を介して、画素電極605と接するように電界発光層が設けられ、当該電界発光層と接するように対向電極が設けられる。

【0111】

なお、図20に示すレイアウト例では、上面出射、下面出射、両面出射のいずれの方式を用いてもよい。一方、図21に示すレイアウト例では、画素電極605は、トランジスタ601～603の上方に設けられているため、上面出射の方式を採用するとよい。但し、図21に示すレイアウト例では、両面出射の方式を採用しても構わないが、その場合は、トランジスタ601～603に光が当たらないように、絶縁層606は、遮光性を有する材料で形成するとよい。

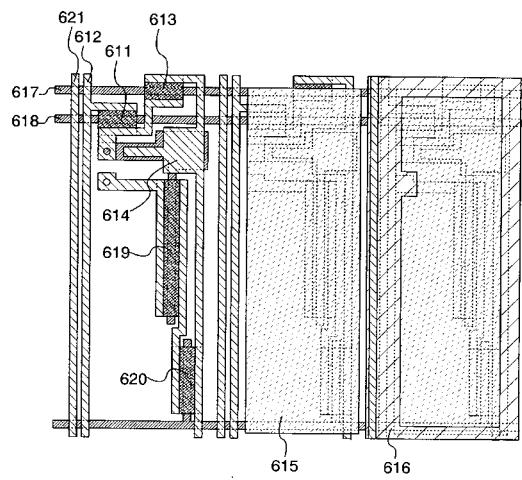

## 【0112】

3つ目のレイアウト例と4つ目のレイアウト例は、1つの画素に4つのトランジスタが設けられた場合(4 TFT / C e 11)であり、スイッチング用のトランジスタ611、駆動用のトランジスタ619、電流制御用のトランジスタ620、消去用のトランジスタ613、容量素子614、列方向に配置された信号線612と補助配線621、行方向に配置された走査線617、618が設けられる(図22、23参照)。また、発光素子が含む画素電極605と、絶縁層616が設けられる。

絶縁層616には、補助配線621と画素電極615が露出するように、開口部が設けられている。絶縁層616に設けられた開口部を介して、補助配線621と対向電極とが接続する。また、絶縁層616に設けられた開口部を介して、画素電極615と接するよう10に電界発光層が設けられ、当該電界発光層と接するように対向電極が設けられる。

図示する構成によると、画素電極615は、トランジスタ611、613、619、620の上方に設けられており、開口率を向上させることができる。従って、この構成では、上面出射の方式を採用するとよい。なお、図22に示すレイアウト例では、両面出射の方式を採用してもよいが、その場合は、トランジスタ611、613、619、620に光が当たらないように、絶縁層616は遮光性を有する材料で形成するとよい。

## 【0113】

なお、上記構成において、トランジスタ601～603、611、613、619、620は、非晶質半導体又は有機半導体でチャネル部を形成するトランジスタである。また、補助配線610、621は、トランジスタ601～603、611、613、619、620のゲート電極と同じ層、トランジスタ601～603、611、613、619、620のソース電極又はドレイン電極に接続する接続配線と同じ層、又は画素電極605、615と同じ層に設けられる。

## 【図面の簡単な説明】

## 【0114】

【図1】非晶質半導体をチャネル部としたトランジスタ(チャネル保護タイプ、チャネルエッチタイプ)、発光素子及び前記発光素子の一方の電極が補助配線と接続した断面構造を示す図。

【図2】非晶質半導体をチャネル部としたトランジスタ(dual gateタイプ)、発光素子及び前記発光素子の一方の電極が補助配線と接続した断面構造を示す図。

【図3】非晶質半導体をチャネル部としたトランジスタ、発光素子及び前記発光素子の一方の電極が補助配線と接続した断面構造を示す図。

【図4】パネルの上面図とアノード線、カソード線及び補助配線の配置を説明する図。

【図5】アノード線、カソード線及び補助配線の配置と開口部を説明する図。

【図6】アノード線、カソード線及び補助配線の配置と開口部を説明する図。

【図7】アノード線、カソード線及び補助配線の配置と開口部を説明する図。

【図8】ドライバICが実装されたパネルの上面図。

【図9】線状のドライバICが実装されたパネルの上面図と斜視図。

【図10】有機トランジスタとa-Siトランジスタで構成されたCMOS回路の断面構造を示す図。

【図11】非晶質半導体をチャネル部としたトランジスタと発光素子を含む画素の回路図。

【図12】N型トランジスタのみで構成されるシフトレジスタの回路図。

【図13】時間階調方式のタイミングチャートを示す図。

【図14】信号線駆動回路、走査線駆動回路の構成を説明する図。

【図15】本発明が適用される電子機器を示す図。

【図16】本発明が適用される電子機器を示す図。

【図17】しきい値補正回路を説明する図。

【図18】発光素子の積層構造を説明する図。

【図19】発光素子の積層構造を説明する図。

- 【図20】画素回路(3 TFT/Cell)のレイアウト図。

【図21】画素回路(3 TFT/Cell)のレイアウト図。

【図22】画素回路(4 TFT/Cel1)のレイアウト図。

【図23】画素回路(4 TFT/Cel1)のレイアウト図。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【 図 1 7 】

【 図 1 8 】

【図19】

【 図 2 0 】

【図21】

【図22】

【図23】

## 【手続補正書】

【提出日】平成16年12月3日(2004.12.3)

## 【手続補正1】

【補正対象書類名】図面

【補正対象項目名】図16

【補正方法】変更

【補正の内容】

【図16】

|                |                                                                                                                                                                                                                                                                                                                     |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置及び電子机器                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2005031651A</a>                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2005-02-03 |

| 申请号            | JP2004179165                                                                                                                                                                                                                                                                                                        | 申请日     | 2004-06-17 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 半导体能源研究所有限公司                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 山崎舜平<br>小山潤                                                                                                                                                                                                                                                                                                         |         |            |

| 发明人            | 山崎 舜平<br>小山 潤                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | H01L51/50 G09F9/30 H01L27/32 H05B33/14 H05B33/26                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09F9/30.338 G09F9/30.365.Z H05B33/14.A H05B33/26.Z G09F9/30.365 H01L27/32                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 3K007/AB02 3K007/AB17 3K007/AB18 3K007/BA06 3K007/BB07 3K007/CB00 3K007/DB03 3K007/GA00 5C094/AA04 5C094/AA14 5C094/AA25 5C094/AA44 5C094/BA03 5C094/BA27 5C094/BA43 5C094/DB10 5C094/FB14 3K107/AA01 3K107/BB01 3K107/CC33 3K107/CC42 3K107/DD17 3K107/DD39 3K107/DD91 3K107/EE04 3K107/EE58 3K107/HH02 3K107/HH05 |         |            |

| 优先权            | 2003172009 2003-06-17 JP                                                                                                                                                                                                                                                                                            |         |            |

| 其他公开文献         | JP2005031651A5<br>JP4593179B2                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                           |         |            |

### 摘要(译)

本发明的目的是提供一种显示装置，其中抑制了由晶体管的特性变化引起的亮度不均匀。本发明的另一个目的是提供一种显示装置，其中抑制了由于电阻值差异引起的图像质量下降。根据本发明，将其中沟道部分由非晶半导体或有机半导体形成的晶体管，连接至该晶体管的源电极或漏电极的连接布线，像素电极，电致发光层和对电极堆叠。发光元件，围绕像素电极的端部的绝缘层，以及在与晶体管或像素电极的栅电极或连接配线相同的层中设置的辅助配线。连接布线连接到像素电极，辅助布线通过设置在绝缘层中的开口连接到对电极。[选型图]图1