(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4501429号

(P4501429)

(45) 発行日 平成22年7月14日(2010.7.14)

(24) 登録日 平成22年4月30日(2010.4.30)

(51) Int.Cl.

F 1

G09G 3/30 (2006.01)

G09G 3/20 (2006.01)G09G 3/30 J

G09G 3/20 624B

G09G 3/20 624E

G09G 3/20 641D

G09G 3/20 642P

請求項の数 2 (全 19 頁) 最終頁に続く

(21) 出願番号

特願2004-592 (P2004-592)

(22) 出願日

平成16年1月5日(2004.1.5)

(65) 公開番号

特開2005-195756 (P2005-195756A)

(43) 公開日

平成17年7月21日(2005.7.21)

審査請求日

平成18年8月3日(2006.8.3)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100082131

弁理士 稲本 義雄

(72) 発明者 内野 勝秀

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 山下 淳一

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

審査官 西島 篤宏

最終頁に続く

(54) 【発明の名称】画素回路及び表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

行状の走査線と列状の信号線とが交差する部分に各々配された画素回路であって、少くとも薄膜型のサンプリングトランジスタと保持容量と薄膜型のドライブトランジスタと負荷素子とを含み、

前記サンプリングトランジスタは、ゲートが該走査線によって選択された時ソース／ドレイン間が導通して該信号線から信号をサンプリングし且つサンプリングした信号を該保持容量に保持させ、

前記ドライブトランジスタは、ゲートが該保持容量に保持された信号電位によってソース基準で正極性となる順バイアスを受け、且つ該順バイアスに応じてソース／ドレイン間に流れる電流で該負荷素子に通電し、

該ドライブトランジスタのゲートにソース基準で負極性となる逆バイアスを所定時間印加する逆バイアス印加手段を備えており、該順バイアスの印加によって生じた該ドライブトランジスタの閾電圧の変動を所定時間の該逆バイアスの印加によって補正し、

前記逆バイアス印加手段は、該ドライブトランジスタのゲートに逆バイアスを印加する為にオン／オフ駆動される薄膜型のスイッチングトランジスタを含み、

前記スイッチングトランジスタは、順バイアスのゲートパルスに応じてオン状態となって、該ドライブトランジスタのゲートに対する逆バイアスの印加を開始し、

前記スイッチングトランジスタがオン状態にある時間は、逆バイアスを印加する所定時間より短く設定されており、順バイアスのゲートパルスの印加によるスイッチングトラン

10

20

ジスタ自体の閾電圧の変動を軽減し、

前記スイッチングトランジスタは、ドレインが該ドライブトランジスタのゲートに接続し、ソースが該ドライブトランジスタのソース電位よりも低く設定された負電位の電源に接続し、該ゲートパルスが入力された時ドレイン／ソース間がオン状態となって該負電位を逆バイアスとして該ドライブトランジスタのゲートに印加するとともに、該負電位を該保持容量に書き込み、

前記保持容量は、該スイッチングトランジスタがオフした後該保持した負電位によって該ドライブトランジスタに対する逆バイアスの印加を所定時間まで維持され、

該負荷素子の通電に先だって該ドライブトランジスタの閾電圧を検知しあらかじめその変動をキャンセルする為に必要な電位を該保持容量に保持させて、該ドライブトランジスタのゲートに印加する閾電圧キャンセル回路を備えており、

10

前記閾電圧キャンセル回路は、該ドライブトランジスタの閾電圧を検知するための検知トランジスタを含んでおり、

前記検知トランジスタは、そのソース／ドレインが、該ドライブトランジスタのドレンとゲートとの間に接続され、そのゲートは該ドライブトランジスタの閾電圧を検知するとき以外負電位に維持されており、

前記スイッチングトランジスタは、そのソースが該検知トランジスタのゲートに接続し、これに印加される負電位を逆バイアスとして利用する

画素回路。

#### 【請求項 2】

20

行状の走査線と、列状の信号線と、両者が交差する部分に各々配された画素回路とからなり、前記画素回路は、少くとも薄膜型のサンプリングトランジスタと保持容量と薄膜型のドライブトランジスタと発光素子とを含み、前記サンプリングトランジスタは、ゲートが該走査線によって選択された時ソース／ドレイン間が導通して該信号線から映像信号をサンプリングし且つサンプリングした映像信号を該保持容量に保持させ、前記ドライブトランジスタは、ゲートが該保持容量に保持された信号電位によってソース基準で正極性となる順バイアスを受け、且つ該順バイアスに応じてソース／ドレイン間に流れる電流で該発光素子を通電して表示を行なう表示装置において、

前記画素回路は、該ドライブトランジスタのゲートにソース基準で負極性となる逆バイアスを所定時間印加する逆バイアス印加手段を備えており、該順バイアスの印加によって生じた該ドライブトランジスタの閾電圧の変動を所定時間の該逆バイアスの印加によって補正し、

30

前記逆バイアス印加手段は、該ドライブトランジスタのゲートに逆バイアスを印加する為にオン／オフ駆動される薄膜型のスイッチングトランジスタを含み、

前記スイッチングトランジスタは、順バイアスのゲートパルスに応じてオン状態となって、該ドライブトランジスタのゲートに対する逆バイアスの印加を開始し、

前記スイッチングトランジスタがオン状態にある時間は、逆バイアスを印加する所定時間より短く設定されており、順バイアスのゲートパルスの印加によるスイッチングトランジスタ自体の閾電圧の変動を軽減し、

前記スイッチングトランジスタは、ドレインが該ドライブトランジスタのゲートに接続し、ソースが該ドライブトランジスタのソース電位よりも低く設定された負電位の電源に接続し、該ゲートパルスが入力された時ドレイン／ソース間がオン状態となって該負電位を逆バイアスとして該ドライブトランジスタのゲートに印加するとともに、該負電位を該保持容量に書き込み、

40

前記保持容量は、該スイッチングトランジスタがオフした後該保持した負電位によって該ドライブトランジスタに対する逆バイアスの印加を所定時間まで維持され、

該発光素子の通電に先だって該ドライブトランジスタの閾電圧を検知しあらかじめその変動をキャンセルする為に必要な電位を該保持容量に保持させて、該ドライブトランジスタのゲートに印加する閾電圧キャンセル回路を備えており、

前記閾電圧キャンセル回路は、該ドライブトランジスタの閾電圧を検知するための検知

50

トランジスタを含んでおり、

前記検知トランジスタは、そのソース／ドレインが、該ドライブトランジスタのドレイ

ンとゲートとの間に接続され、そのゲートは該ドライブトランジスタの閾電圧を検知する

とき以外負電位に維持されており、

前記スイッチングトランジスタは、そのソースが該検知トランジスタのゲートに接続し

、これに印加される負電位を逆バイアスとして利用する

表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、画素毎に配した負荷素子を電流駆動する画素回路に関する。又この画素回路がマトリクス状に配列された表示装置であって、特に各画素回路内に設けた絶縁ゲート型電界効果トランジスタによって有機EL発光素子などの負荷素子に通電する電流量を制御する、いわゆるアクティブマトリクス型の表示装置に関する。

【背景技術】

【0002】

20

画像表示装置、例えば液晶ディスプレイなどでは、多数の液晶画素をマトリクス状に並べ、表示すべき画像情報に応じて画素毎に入射光の透過強度又は反射強度を制御することによって画像を表示する。これは、有機EL素子を画素に用いた有機ELディスプレイなどにおいても同様であるが、液晶画素と異なり有機EL素子は自発光素子である。その為、有機ELディスプレイは液晶ディスプレイに比べて画像の視認性が高く、バックライトが不要であり、応答速度が速いなどの利点を有する。又、各発光素子の輝度レベル（階調）はそれに流れる電流値によって制御可能であり、いわゆる電流制御型であるという点で液晶ディスプレイなどとは大きく異なる。

【0003】

30

有機ELディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として単純マトリクス方式とアクティブマトリクス方式がある。前者は構造が単純であるものの、大型且つ高精細のディスプレイの実現が難しいなどの問題がある為、現在はアクティブマトリクス方式の開発が盛んに行なわれている。この方式は、各画素回路内部の発光素子に流れる電流を、画素回路内部に設けた能動素子（一般には薄膜トランジスタ、TFT）によって制御するものである。

【特許文献1】U.S.P.5,684,365

【特許文献2】特開平8-234683号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

従来の画素回路は、行状の走査線と列状の信号線とが交差する部分に各々配されている。各画素回路は、少くとも薄膜型のサンプリングトランジスタと保持容量と薄膜型のドライブトランジスタと発光素子などの負荷素子とを含んでいる。サンプリングトランジスタは、そのゲートが走査線によって選択された時ソース／ドレイン間が導通して信号線から映像信号をサンプリングする。サンプリングされた信号は保持容量に書き込まれ保持される。ドライブトランジスタは、そのゲートが保持容量に接続され、ソース／ドレインの片方が発光素子などの負荷素子に接続している。ドライブトランジスタのゲートは、保持容量に保持された信号電位によってソース基準で正極性となる順バイアスを受ける。ドライブトランジスタはこの順バイアスに応じてソース／ドレイン間に電流を流し、発光素子に通電する。一般に発光素子の輝度は通電量に比例している。更にドライブトランジスタの通電量は保持容量に書き込まれた信号電位によって制御される。従って、発光素子は映像信号に応じた輝度で発光することになる。

【0005】

ドライブトランジスタの動作特性は以下の式で表わされる。

40

50

$$I_{ds} = (1/2) \mu (W/L) C_o x (V_{gs} - V_{th})^2$$

このトランジスタ特性式において、 $I_{ds}$ はドレン電流を表わしている。 $V_{gs}$ はソースを基準としてゲートに印加される電圧を表わしており、これが正の値である時上記の順バイアスと呼んでいる。 $V_{th}$ はトランジスタの閾電圧である。その他 $\mu$ はトランジスタのチャネルを構成する半導体薄膜の移動度を表わし、 $W$ はチャネル幅を表わし、 $L$ はチャネル長を表わし、 $C_o$ はゲート容量を表わしている。このトランジスタ特性式から明らかなる様に、薄膜トランジスタは飽和領域で動作する時、ゲート電圧 $V_{gs}$ が閾電圧 $V_{th}$ を超えて正側に大きくなると、オン状態となってドレン電流 $I_{ds}$ が流れる。換言すると順バイアス( $V_{gs}$ )が閾電圧( $V_{th}$ )を超えるとオン状態となる。逆に $V_{gs}$ が $V_{th}$ を下回ると薄膜トランジスタはカットオフし、ドレン電流 $I_{ds}$ は流れなくなる。

10

#### 【0006】

ところで薄膜トランジスタの閾電圧 $V_{th}$ は必ずしも一定ではなく経時に変動する傾向にある。前述のトランジスタ特性式から明らかなる様に、ドライブトランジスタの閾電圧 $V_{th}$ が変動すると、ゲート電圧 $V_{gs}$ が一定であってもドレン電流 $I_{ds}$ が変動する。これにより発光素子の通電量が変わってしまう為発光輝度の変化が生じるという課題がある。すなわち所定の映像信号を送っても実際の発光輝度が変化してしまう為意図する表示が得られないという課題がある。

#### 【課題を解決するための手段】

#### 【0007】

20

上述した従来の技術の課題に鑑み、本発明はドライブトランジスタの閾電圧の経時変化を抑制可能な画素回路及び表示装置とこれらの駆動方法を提供することを目的とする。係る目的を達成する為に以下の手段を講じた。即ち本発明は、行状の走査線と列状の信号線とが交差する部分に各々配された画素回路であって、少くとも薄膜型のサンプリングトランジスタと保持容量と薄膜型のドライブトランジスタと負荷素子とを含む。前記サンプリングトランジスタは、ゲートが該走査線によって選択された時ソース／ドレン間が導通して該信号線から信号をサンプリングし且つサンプリングした信号を該保持容量に保持させる。前記ドライブトランジスタは、ゲートが該保持容量に保持された信号電位によってソース基準で正極性となる順バイアスを受け、且つ該順バイアスに応じてソース／ドレン間に流れる電流で該負荷素子に通電する。特徴事項として、該ドライブトランジスタのゲートにソース基準で負極性となる逆バイアスを所定時間印加する逆バイアス印加手段を備えており、該順バイアスの印加によって生じた該ドライブトランジスタの閾電圧の変動を所定時間の該逆バイアスの印加によって補正する。前記逆バイアス印加手段は、該ドライブトランジスタのゲートに逆バイアスを印加する為にオン／オフ駆動される薄膜型のスイッチングトランジスタを含む。前記スイッチングトランジスタは、順バイアスのゲートパルスに応じてオン状態となって、該ドライブトランジスタのゲートに対する逆バイアスの印加を開始する。前記スイッチングトランジスタがオン状態にある時間は、逆バイアスを印加する所定時間より短く設定されており、順バイアスのゲートパルスの印加によるスイッチングトランジスタ自体の閾電圧の変動を軽減する。

30

#### 【0008】

40

前記スイッチングトランジスタは、ドレンが該ドライブトランジスタのゲートに接続し、ソースが該ドライブトランジスタのソース電位よりも低く設定された負電位の電源に接続し、該ゲートパルスが入力された時ドレン／ソース間がオン状態となって該負電位を逆バイアスとして該ドライブトランジスタのゲートに印加するとともに、該負電位を該保持容量に書き込む。前記保持容量は、該スイッチングトランジスタがオフした後該保持した負電位によって該ドライブトランジスタに対する逆バイアスの印加を所定時間まで維持する。

また、該負荷素子の通電に先だって該ドライブトランジスタの閾電圧を検知しあらかじめその変動をキャンセルする為に必要な電位を該保持容量に保持させて、該ドライブトランジスタのゲートに印加する閾電圧キャンセル回路を備えている。前記閾電圧キャンセル

50

回路は、該ドライブトランジスタの閾電圧を検知するための検知トランジスタを含んでいる。前記検知トランジスタは、そのソース／ドレインが、該ドライブトランジスタのドレインとゲートとの間に接続され、そのゲートは該ドライブトランジスタの閾電圧を検知するとき以外負電位に維持されている。前記スイッチングトランジスタは、そのソースが該検知トランジスタのゲートに接続し、これに印加される負電位を逆バイアスとして利用する。

#### 【0009】

又本発明は、行状の走査線と、列状の信号線と、両者が交差する部分に各々配された画素回路とからなる表示装置を包含する。各画素回路は、少くとも薄膜型のサンプリングトランジスタと保持容量と薄膜型のドライブトランジスタと発光素子とを含む。前記サンプリングトランジスタは、ゲートが該走査線によって選択された時ソース／ドレイン間が導通して該信号線から映像信号をサンプリングし且つサンプリングした映像信号を該保持容量に保持させる。前記ドライブトランジスタは、ゲートが該保持容量に保持された信号電位によってソース基準で正極性となる順バイアスを受け、且つ該順バイアスに応じてソース／ドレイン間に流れる電流で該発光素子を通電して表示を行なう。特徴事項として、各画素回路は、該ドライブトランジスタのゲートにソース基準で負極性となる逆バイアスを所定時間印加する逆バイアス印加手段を備えており、該順バイアスの印加によって生じた該ドライブトランジスタの閾電圧の変動を所定時間の該逆バイアスの印加によって補正する。前記逆バイアス印加手段は、該ドライブトランジスタのゲートに逆バイアスを印加する為にオン／オフ駆動される薄膜型のスイッチングトランジスタを含む。前記スイッチングトランジスタは、順バイアスのゲートパルスに応じてオン状態となって、該ドライブトランジスタのゲートに対する逆バイアスの印加を開始する。前記スイッチングトランジスタがオン状態にある時間は、逆バイアスを印加する所定時間より短く設定されており、順バイアスのゲートパルスの印加によるスイッチングトランジスタ自体の閾電圧の変動を軽減する。

#### 【0010】

前記スイッチングトランジスタは、ドレインが該ドライブトランジスタのゲートに接続し、ソースが該ドライブトランジスタのソース電位よりも低く設定された負電位の電源に接続し、該ゲートパルスが入力された時ドレイン／ソース間がオン状態となって該負電位を逆バイアスとして該ドライブトランジスタのゲートに印加するとともに、該負電位を該保持容量に書き込む。前記保持容量は、該スイッチングトランジスタがオフした後該保持した負電位によって該ドライブトランジスタに対する逆バイアスの印加を所定時間まで維持する。

また、該発光素子の通電に先だって該ドライブトランジスタの閾電圧を検知しあらかじめその変動をキャンセルする為に必要な電位を該保持容量に保持させて、該ドライブトランジスタのゲートに印加する閾電圧キャンセル回路を備えている。前記閾電圧キャンセル回路は、該ドライブトランジスタの閾電圧を検知するための検知トランジスタを含む。前記検知トランジスタは、そのソース／ドレインが、該ドライブトランジスタのドレインとゲートとの間に接続され、そのゲートは該ドライブトランジスタの閾電圧を検知するとき以外負電位に維持されている。前記スイッチングトランジスタは、そのソースが該検知トランジスタのゲートに接続し、これに印加される負電位を逆バイアスとして利用する。

#### 【発明の効果】

#### 【0013】

順バイアスの印加で生じたドライブトランジスタの閾電圧の上方変動を、逆バイアスの印加で下方修正し、以って閾電圧の変動を抑制することが可能となる。

#### 【0014】

スイッチングトランジスタの誤動作を防止でき、常にドライブトランジスタに対して適切なタイミングで逆バイアスを確実に印加できる様になる。

#### 【発明を実施するための最良の形態】

#### 【0015】

10

20

30

40

50

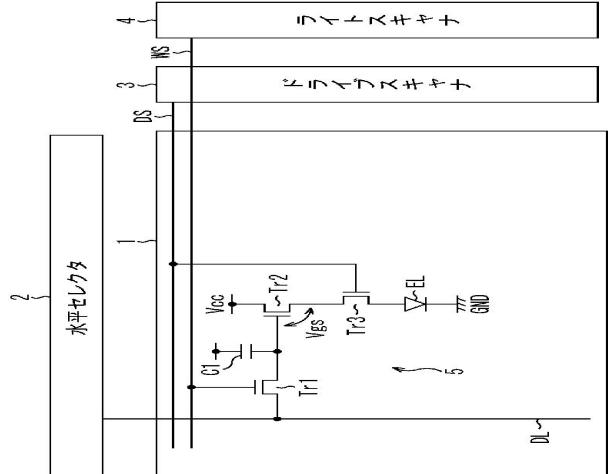

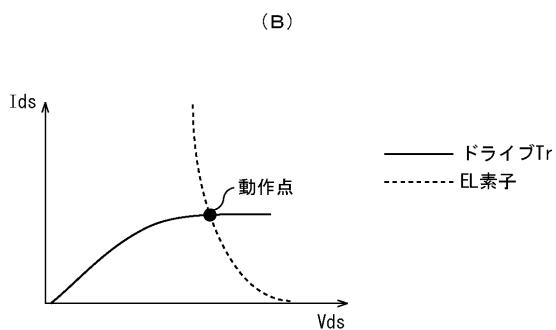

以下図面を参照して本発明の実施の形態を詳細に説明する。まず最初に本発明の背景を明らかにする為、図1を参照してアクティブマトリクス表示装置及びこれに含まれる画素回路の一般的な構成を参考例として説明する。図示する様に、アクティブマトリクス表示装置は主要部となる画素アレイ1と周辺の回路群とで構成されている。周辺の回路群は水平セレクタ2、ドライブスキャナ3、ライトスキャナ4などを含んでいる。

#### 【0016】

画素アレイ1は行状の走査線WSと列状の信号線DLと両者の交差する部分にマトリクス状に配列した画素回路5とで構成されている。信号線DLは水平セレクタ2によって駆動される。走査線WSはライトスキャナ4によって走査される。尚、走査線WSと平行に別の走査線DSも配線されており、これはドライブスキャナ3によって走査される。各画素回路5は、走査線WSによって選択された時信号線DLから信号をサンプリングする。更に走査線DSによって選択された時、該サンプリングされた信号に応じて負荷素子を駆動する。この負荷素子は各画素回路5に形成された電流駆動型の発光素子などである。

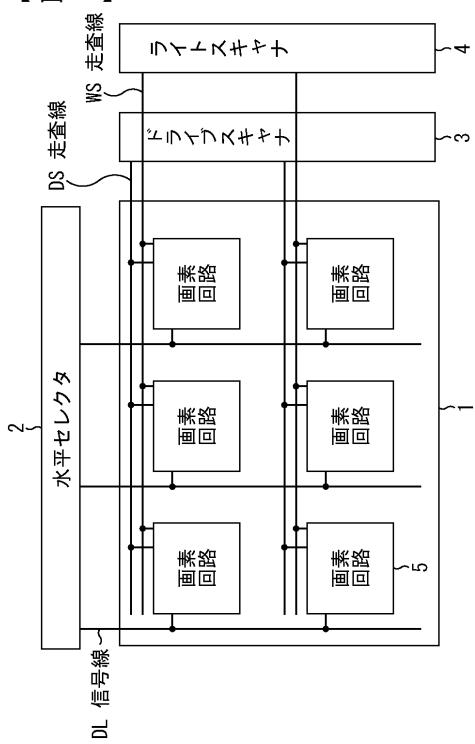

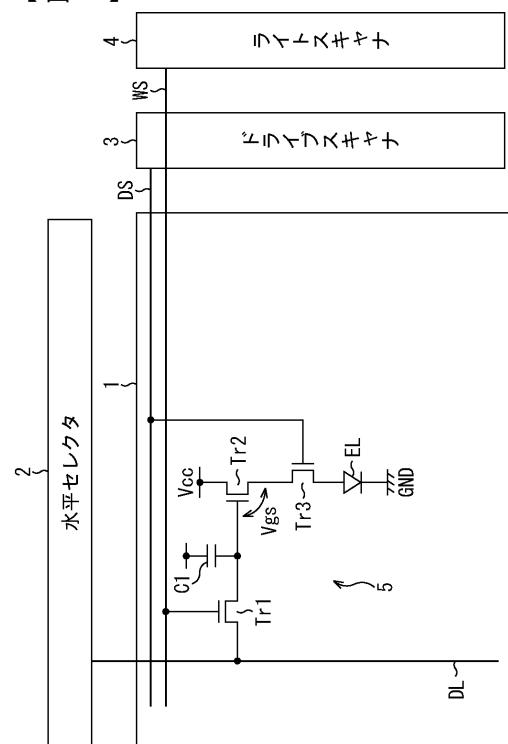

#### 【0017】

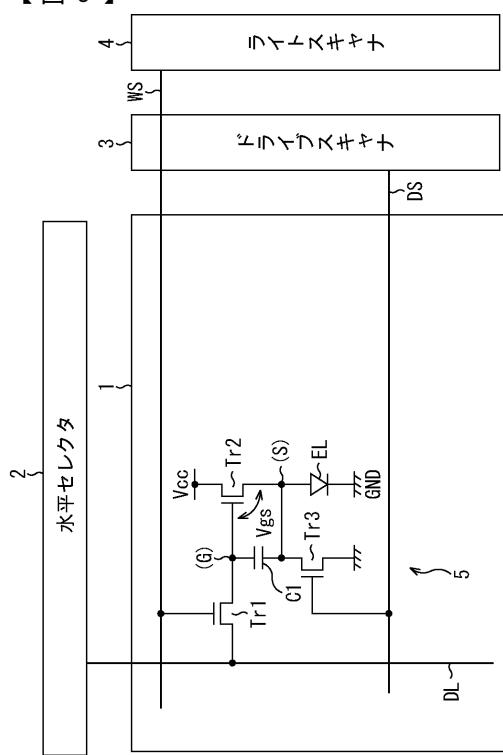

図2は、図1に示した画素回路5の基本的な構成を示す参考図である。本画素回路5は、サンプリング用薄膜トランジスタ（サンプリングトランジスタTr1）、ドライブ用薄膜トランジスタ（ドライブトランジスタTr2）、スイッチング用薄膜トランジスタ（スイッチングトランジスタTr3）、保持容量C1、負荷素子（有機EL発光素子）などで構成されている。

#### 【0018】

サンプリングトランジスタTr1は走査線WSによって選択された時導通し、信号線DLから映像信号をサンプリングして保持容量C1に保持する。ドライブトランジスタTr2は保持容量C1に保持された信号電位に応じて発光素子ELに対する通電量を制御する。スイッチングトランジスタTr3は走査線DSによって制御され、発光素子ELに対する通電をオン／オフする。すなわち、ドライブトランジスタTr2は通電量に応じて発光素子ELの発光輝度（明るさ）を制御する一方、スイッチングトランジスタTr3は発光素子ELの発光時間を制御している。これらの制御により、各画素回路5に含まれる発光素子ELは映像信号に応じた輝度を呈し、画素アレイ1に所望の表示が映し出される。

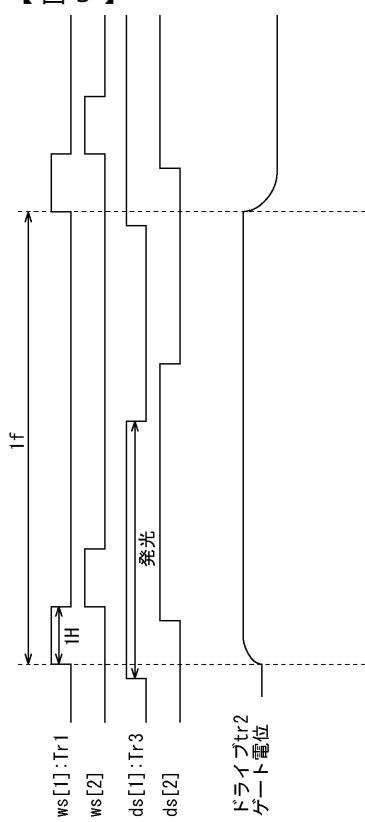

#### 【0019】

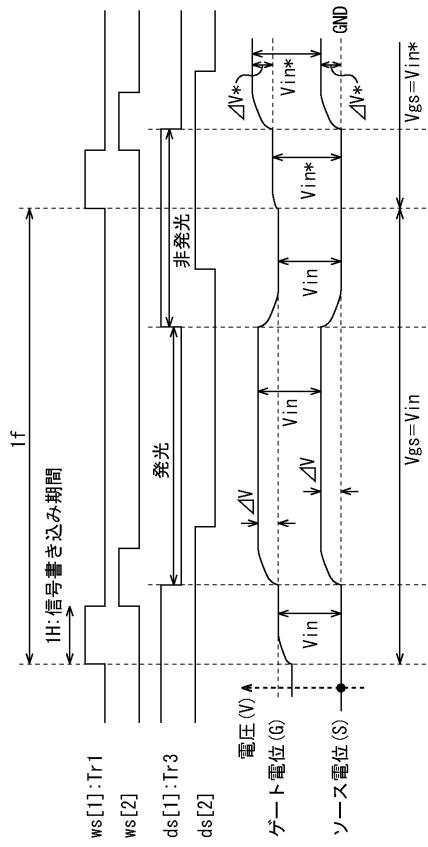

図3は、図2に示した画素アレイ1及び画素回路5の動作説明に供するタイミングチャートである。1フィールド期間(1f)の先頭で、1水平期間(1H)の間1行目の画素回路5に走査線WSを介して選択パルスws[1]が印加され、サンプリングトランジスタTr1が導通する。これにより信号線DLから映像信号がサンプリングされ、保持容量C1に書き込まれる。保持容量C1の一端はドライブトランジスタTr2のゲートに接続している。従って、映像信号が保持容量C1に書き込まれると、ドライブトランジスタTr2のゲート電位が、書き込まれた信号電位に応じて上昇する。この時、他の走査線DSを介してスイッチングトランジスタTr3に選択パルスds[1]が印加される。この間発光素子ELは発光を続ける。1フィールド期間1fの後半はds[1]がローレベルになるので発光素子ELは非発光状態となる。パルスds[1]のデューティを調整することで、発光期間と非発光期間の割合を調整でき、所望の画面輝度が得られる。次の水平期間に移行すると、2行目の画素回路に対し、各走査線WS, DSからそれぞれ走査用の信号パルスws[2], ds[2]が印加される。

#### 【0020】

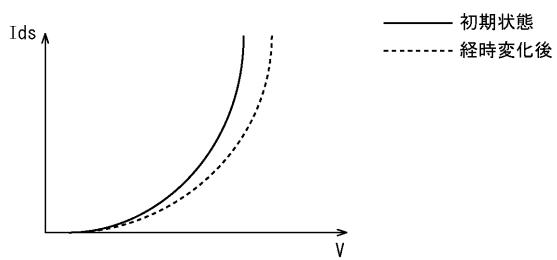

図4は、発光素子として画素回路5に組み込まれる有機EL素子の電流-電圧(I-V)特性の経時変化を示すグラフである。グラフにおいて、実線で示す曲線が初期状態時の特性を示し、破線で示す曲線が経時変化後の特性を示している。一般的に、有機EL素子のI-V特性は、グラフに示す様に時間が経過すると劣化してしまう。図2に示した参考例の画素回路はドライブトランジスタがソースフォロワ構成となっており、EL素子のI-V特性の経時変化に対処できず、発光輝度の劣化が生じるという問題がある。

#### 【0021】

10

20

30

40

50

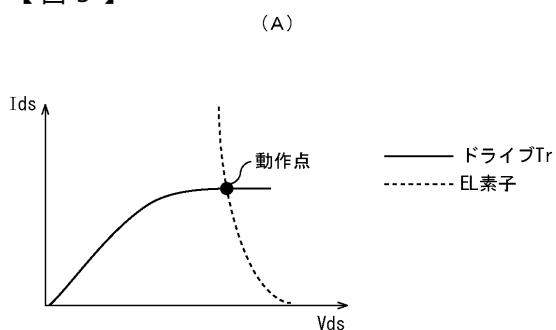

図5の(A)は、初期状態におけるドライブトランジスタTr2と発光素子ELの動作点を示すグラフである。図において、縦軸はドライブトランジスタTr2のドレイン・ソース間電圧Vdsを示し、縦軸はドレイン・ソース間電流Idsを示している。図示する様に、ソース電位はドライブトランジスタTr2と発光素子ELとの動作点で決まり、その電圧値はゲート電圧によって異なる値を持つ。ドライブトランジスタTr2は飽和領域で動作するので、動作点のソース電圧に対応したVgsに関し、前述のトランジスタ特性式で規定された電流値の駆動電流Idsを流す。

#### 【0022】

しかしながら発光素子ELのI-V特性は図4に示した様に経時劣化する。図5の(B)に示す様に、この経時劣化により動作点が変化してしまい、同じゲート電圧を印加してもトランジスタのソース電圧は変化してしまう。これによりドライブトランジスタTr2のゲート・ソース間電圧Vgsは変化してしまい、流れる電流値が変動する。同時に発光素子ELに流れる電流値も変化する。この様に発光素子ELのI-V特性が変化すると、図2に示した参考例のソースフォロワ構成の画素回路では、発光素子ELの輝度が経時に変化してしまうという問題がある。

#### 【0023】

図6は画素回路の他の参考例を表わしており、図2に示した先の参考例の問題点に対処したものである。理解を容易にする為、図2の参考例と対応する部分には対応する参照符号を付けてある。改良点は、スイッチングトランジスタTr3の結線を代えたことであり、これによりブートストラップ機能を実現している。具体的には、スイッチングトランジスタTr3のソースは接地され、ドレインはドライブトランジスタTr2のソース(S)と保持容量C1の一方の電極とに接続され、ゲートには走査線DSが接続している。尚保持容量C1の他方の電極はドライブトランジスタTr2のゲート(G)に接続されている。

#### 【0024】

図7は、図6に示した画素回路5の動作説明に供するタイミングチャートである。フィールド期間1fのうち最初の水平期間1Hで、ライトスキャナ4から走査線WSを介して1行目の画素回路5に選択パルスws[1]が送られる。尚[]の中の数字は、マトリクス配置された画素回路の行番号に対応している。選択パルスが印加されるとサンプリングトランジスタTr1が導通し、信号線DLから入力信号Vinがサンプリングされ、保持容量C1に書き込まれる。この時スイッチングトランジスタTr3にはドライブスキャナ3から走査線DSを介して選択パルスds[1]が印加されており、オン状態となっている。従って保持容量C1の片方の電極並びにドライブトランジスタTr2のソース(S)はGNDレベルとなっている。このGNDレベルを基準として保持容量C1に入力信号Vinが書き込まれる為、ドライブトランジスタTr2のゲート電位(G)はVinになる。

#### 【0025】

この後サンプリングトランジスタTr1に対する選択パルスws[1]が解除され、続いてスイッチングトランジスタTr3に対する選択パルスds[1]も解除される。これによりサンプリングトランジスタTr1及びスイッチングトランジスタTr3はオフする。従ってドライブトランジスタTr2のソース(S)はGNDから切り離され、発光素子ELのアノードに対する接続ノードとなる。

#### 【0026】

ドライブトランジスタTr2は保持容量C1に保持された入力信号Vinをゲートに受け、その値に応じてドレイン電流をVcc側からGND側に向かって流す。この通電により発光素子ELは発光を行なう。その際、発光素子ELに対する通電により電圧降下が生じるが、その分だけソース電位(S)がGND側からVcc側に向かって上昇する。図7のタイミングチャートではこの上昇分をVで表わしている。保持容量C1の一端はTr2のソース(S)に接続され、他端はハイインピーダンスのゲート(G)に接続されている。従ってソース電位(S)がVだけ上昇するとその分だけゲート電位(G)も持ち上

10

20

30

40

50

がり、正味の入力信号  $V_{in}$  はそのまま維持される。従って、発光素子 E L の電流 - 電圧特性に応じてソース電位 ( S ) が  $V$  だけ変動しても、常にゲート電圧  $V_{gs} = V_{in}$  が成立し、ドレイン電流は一定に保たれる。すなわちドライブトランジスタ Tr 2 はソースフォロワ構成であるにも関わらず、上述したブートストラップ機能により、発光素子 E L に対し定電流源として機能する。

#### 【 0 0 2 7 】

この後選択パルス d s [ 1 ] がハイレベルに復帰するとスイッチングトランジスタ Tr 3 が導通し、発光素子 E L に供給されるべき電流はバイパスされるので非発光状態になる。この様にしてフィールド期間 1 f が終了すると、次のフィールド期間に入り、再びサンプリングトランジスタ Tr 1 に選択パルス w s [ 1 ] が印加され入力映像信号  $V_{in}^*$  のサンプリングが行なわれる。先のフィールド期間と今回のフィールド期間ではサンプリングされる映像信号のレベルが異なる場合があるので、これを区別する為入力映像信号  $V_{in}$  に \* 印を付してある。尚、この様な映像信号の書き込み及び発光動作は線順次（行単位）で行なわれる。この為画素の各行に対し選択パルス w s [ 1 ]、w s [ 2 ] …… が順次印加されることになる。同様に選択パルス d s [ 1 ]、d s [ 2 ] …… も順次印加されることになる。

#### 【 0 0 2 8 】

以上の様に図 6 の画素回路は、ドライブトランジスタ Tr 2 が N チャネル型であっても発光素子 E L を定電流駆動でき、発光素子 E L の I - V 特性の経時変化による輝度劣化を防ぐことができた。しかしながら、エージングによる経時変化は発光素子 E L だけではなくアモルファスシリコンやポリシリコンの薄膜を素子領域とする薄膜トランジスタも、その閾電圧  $V_{th}$  が変動してしまう。図 6 に示した画素回路 5 で  $V_{th}$  変動が最も顕著になるのはドライブトランジスタ Tr 2 である。これは 1 フィールド期間 ( 1 f ) 発光素子 E L に電流を流し続ける為、ドライブトランジスタ Tr 2 がオン状態に維持されその間ゲートに順バイアスがかかっているからである。一般に薄膜トランジスタの  $V_{th}$  変動は、オノン状態が持続する時間（順バイアスが印加されている時間）及び順バイアス値にある関数で比例して大きくなる傾向にある。前述のトランジスタ特性式から明らかな様に、 $V_{th}$  が変動するとゲート電圧  $V_{gs}$  が一定であっても、発光素子 E L を駆動する電流  $I_{ds}$  が変化してしまう。この為、発光素子 E L の輝度劣化が生じてしまう。本発明は、この  $V_{th}$  変動に対処する為、ドライブトランジスタのゲートに逆バイアスをかけて回路的に補正するものである。

#### 【 0 0 2 9 】

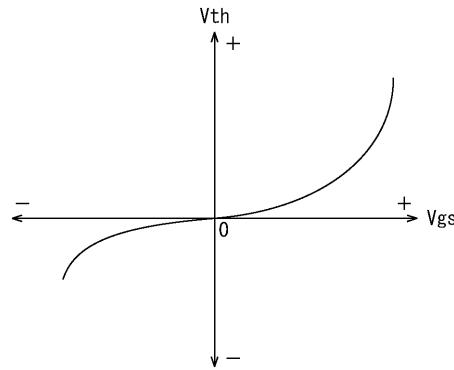

図 8 は、薄膜トランジスタのゲートバイアスと閾電圧変動との関係を示すグラフである。アモルファスシリコン薄膜トランジスタやポリシリコン薄膜トランジスタのデバイス特性は、図 8 のグラフに示す様に、ゲート / ソース間に電圧  $V_{gs}$  を印加し一定の時間エージングすると、 $V_{gs}$  がプラスの場合（すなわち順バイアスが印加されていると） $V_{th}$  はプラスにシフトする。逆に  $V_{gs}$  がマイナスで印加されると（すなわち逆バイアスが印加されると） $V_{th}$  変動はマイナスにシフトする特性を持っている。そして、 $V_{gs}$  の絶対値が大きければ大きい程、 $V_{th}$  変動の絶対値も大きくなる傾向にあることが判明した。本発明はこのデバイス特性を積極的に利用して、1 フィールドのうち発光期間に順バイアスをかけ非発光期間に逆バイアスをかける様にしている。すなわちドライブトランジスタに対し +  $V_{gs}$  が印加されている発光期間以外の非発光期間では、ドライブトランジスタに -  $V_{gs}$  を印加する。そして、 $V_{gs}$  の電圧値及び電圧印加時間を調整して、結果的に  $V_{th}$  変動を抑制している。つまり発光期間になると繰り返し印加される順バイアスでドライブトランジスタの閾電圧  $V_{th}$  は上方シフトする。これを下方修正する為に、非発光期間にドライブトランジスタに対して逆バイアスを印加し、以って閾電圧変動を抑制している。

#### 【 0 0 3 0 】

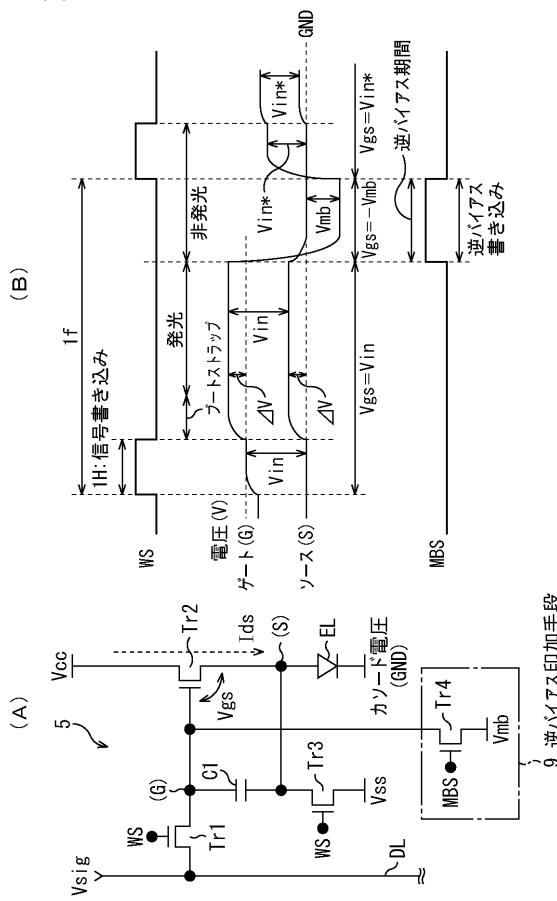

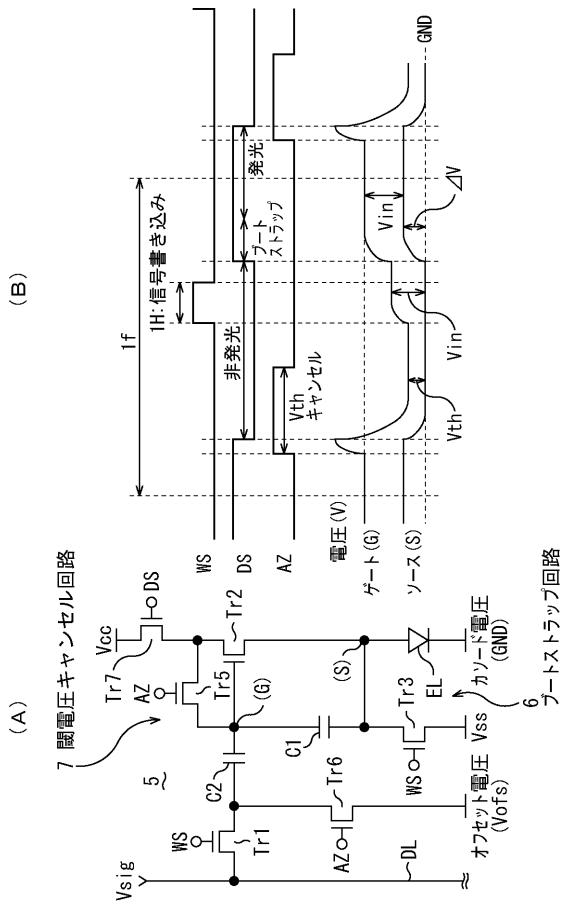

図 9 は、本発明の元になったプロトタイプを表わしており、( A ) は構成を示す回路図、( B ) は動作を示すタイミングチャートである。このプロトタイプは図 6 に示した参考

10

20

30

40

50

例の画素回路の問題点を解決するものであって、上述した原理に基づき逆バイアス印加手段を画素回路中に導入したものである。

#### 【0031】

(A)に示す様に、本画素回路5は、行状の走査線WSと列状の信号線DLとが交差する部分に配されている。画素回路5は、薄膜型のサンプリングトランジスタTr1と保持容量C1と同じく薄膜型のドライブトランジスタTr2と負荷素子(発光素子EL)とを含む。サンプリングトランジスタTr1はゲートが走査線WSによって選択された時ソース/ドレイン間が導通して、信号線DLから映像信号Vsigをサンプリングし、且つサンプリングした信号Vsigを保持容量C1に保持させる。ドライブトランジスタTr2は、そのゲート(G)が保持容量C1に保持された信号電位によってソース(S)基準で正極性となる順バイアスを受け、且つこの順バイアスに応じてソース/ドレイン間に流れ電流Idsで発光素子ELに通電する。10

#### 【0032】

本プロトタイプの特徴事項として画素回路5は逆バイアス印加手段9を備えている。この逆バイアス印加手段9は、ドライブトランジスタTr2のゲート(G)にソース(S)基準で負極性となる逆バイアスを印加するものであって、順バイアスの印加によって生じたドライブトランジスタTr2の閾電圧Vthの変動を逆バイアスの印加によって補正するものである。この逆バイアス印加手段9は、ドライブトランジスタTr2の動作特性及び動作点に応じて逆バイアスの電圧値及び印加時間を設定し、以って閾電圧Vthの変動を過不足なく補正する。例えばこの逆バイアス印加手段9は、順バイアスの印加時間より逆バイアスの印加時間が短い程、順バイアスの絶対値より逆バイアスの絶対値を大きく設定可能である。20

#### 【0033】

本プロトタイプによると、この逆バイアス印加手段9は、ドライブトランジスタTr2のゲート(G)に逆バイアスを印加する為にオン/オフ駆動される薄膜型のスイッチングトランジスタTr4を含む。このスイッチングトランジスタTr4は、ドレインがドライブトランジスタTr2のゲート(G)に接続し、ソースがドライブトランジスタTr2のソース(S)電位よりも低く設定された負電位Vm bの電源に接続し、ゲートに制御線MBSを介してパルスが入力された時ドレイン/ソース間がオンして負電位Vm bを逆バイアスとしてドライブトランジスタTr2のゲート(G)に印加する。スイッチングトランジスタTr4のゲートに入力されるパルスの印加時間及び振幅と、スイッチングトランジスタTr4のソースに供給される負電位Vm bのレベルとは、ドライブトランジスタTr2の閾電圧Vthの変動を抑える為最適に設定されている。加えて制御線MBSから供給されるパルスの振幅及び負電位Vm bのレベルはスイッチングトランジスタTr4自身の閾電圧の変動を抑える様に設定されている。尚負荷素子は通電によって発光する有機EL素子からなり、スイッチングトランジスタTr4は制御線MBSを介してゲートに入力されるパルスに応答してドライブトランジスタTr2をオン/オフ制御し、以って有機EL素子の発光時間と非発光時間を規定している。30

#### 【0034】

(B)を参照して、引続き本プロトタイプに係る画素回路5の動作を説明する。フィールド期間1fの先頭に位置する水平期間(1H)で走査線WSに選択パルスが印加され、サンプリングトランジスタTr1が導通する。本実施形態ではスイッチングトランジスタTr3のゲートにもこの選択パルスが同時に印加される様になっている。この結果サンプリングされた映像信号Vsigは保持容量C1に入力信号Vinとして保持される。選択パルスが解除されると直ちにドライブトランジスタTr2はVinに応答してドレイン電流Idsを流し、発光素子ELを通電駆動する。発光期間の当初でブートストラップ動作が働き、ドライブトランジスタTr2のソース(S)が発光素子ELの特性変動分Vだけ上昇する。これに伴いゲート(G)電位も上昇するので入力信号Vinは一定に維持される。この発光期間中ドライブトランジスタTr2のゲート(G)には順バイアスが印加される。4050

## 【0035】

続いて非発光期間が始まる時間もしくはその付近の時間に逆バイアス印加手段9を構成するスイッチングトランジスタTr4をオンさせる。このオペレーションによりトランジスタTr4がオンの時間はドライブトランジスタTr2のゲート電位(G)がVm bの電圧となる。又ドライブトランジスタTr2のソース(S)は、ゲート電圧が下がっていくことから電流値が下がり、これに伴う発光素子ELの電圧降下が起こり最終的にカソード電位(GND)まで下がる。この結果、ドライブトランジスタTr2のゲート/ソース間に-Vm bの逆バイアスをかけることができる。この様にしてVth変動が最も起きやすいドライブトランジスタTr2のゲート/ソース間に逆バイアスを印加して、Vth変動を補正する。尚、Vm b電圧やMBSパルス振幅、又これに伴うWSパルス振幅は、トランジスタの正常動作とVth変動を補正できる電圧や振幅に設定する。本プロトタイプにより非晶質シリコン TFT やポリシリコン TFT の閾電圧が変動しても、回路上で自動的に補正をかけることができる為、EL発光素子の輝度劣化を防ぐことができ、高品質な有機ELディスプレイを提供できる。

## 【0036】

ところで図9に示したプロトタイプは、逆バイアス印加手段9としてスイッチングトランジスタTr4を含んでいる。図9(B)のタイミングチャートから明らかな様に、このスイッチングトランジスタTr4は逆バイアス期間中(非発光期間内)ゲートパルスMBSがハイレベルにあってオンしている。すなわちスイッチングトランジスタTr4自体に非発光期間中順バイアスがかかっていることになる。結局スイッチングトランジスタTr4の閾電圧が変動してしまう恐れがある。これを放置すると、閾電圧の上方変動を招き、最悪の場合スイッチングトランジスタTr4はオンしなくなり、ドライブトランジスタTr2に逆バイアスを印加できなくなる恐れがある。これを回避する為には、スイッチングトランジスタTr4に印加するゲートパルスMBSの振幅を大きくし、ロー側の電位を大きく負電位とすれば、スイッチングトランジスタTr4にも逆バイアスをかけることができるので、閾電圧上方変動の問題は解決することが可能である。しかしながら、ゲートパルスのロー側を大きく負電位にする為には、ダイナミックレンジを大きくしなければならず、スイッチングトランジスタTr4にゲートパルスを供給するパルスドライバの耐圧に影響しコスト増にもなる。

## 【0037】

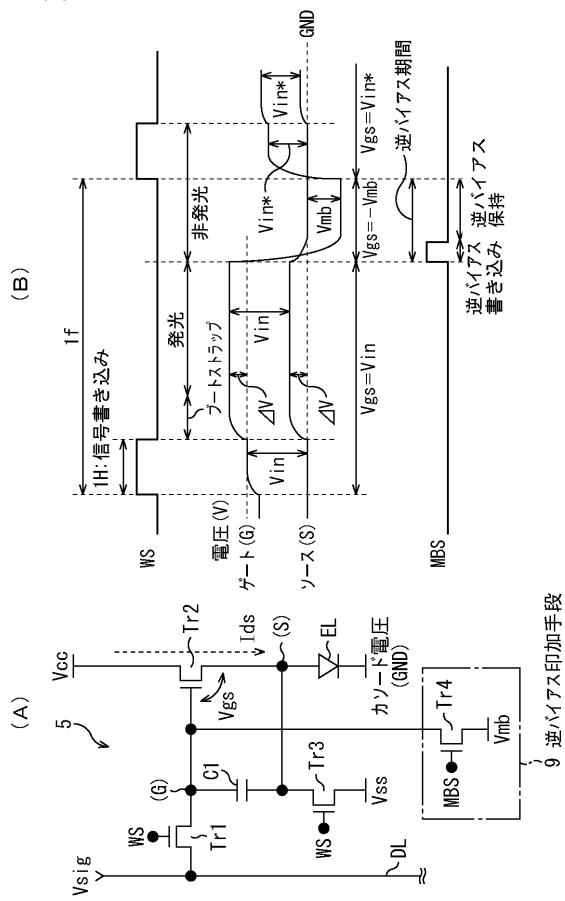

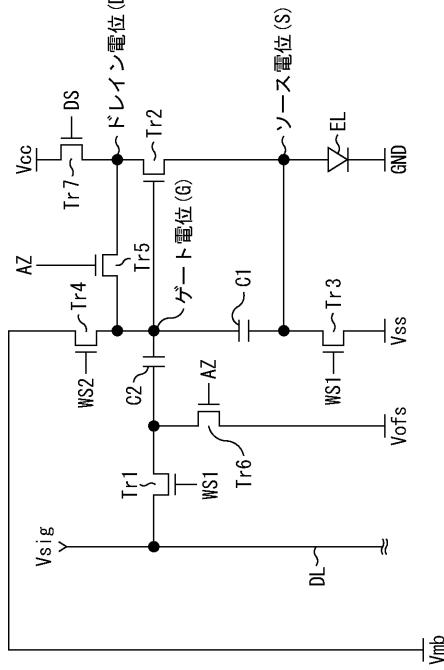

図10は、図9に示したプロトタイプを改良した本発明の実施形態であって、(A)は構成を示す回路図、(B)は動作を示すタイミングチャートである。本実施形態は基本的には図9に示したプロトタイプと共通する点が多く、対応する部分には対応する参照番号を付して理解を容易にしている。

## 【0038】

図10の(A)に示す様に、本実施形態の画素回路5は、サンプリングトランジスタTr1と保持容量C1とドライブトランジスタTr2と負荷素子ELを含んでいる。サンプリングトランジスタTr1は、ゲートが走査線WSによって選択された時ソース/ドレイン間が導通して信号線DLから信号Vsigをサンプリングし且つサンプリングした信号Vsigを保持容量C1に保持させる。ドライブトランジスタTr2は、ゲートが保持容量C1に保持された信号電位によってソース(S)基準で正極性となる順バイアス(Vgs)を受け、且つ順バイアス(Vgs)に応じてソース/ドレイン間に流れる電流IDSで負荷素子ELに通電する。本実施形態の特徴事項として、逆バイアス印加手段9を備えており、ドライブトランジスタTr2のゲート(G)にソース(S)基準で負極性となる逆バイアスVm bを所定時間印加する。この様にして、順バイアスの印加によって生じたドライブトランジスタTr2の閾電圧の変動を所定時間の逆バイアスVm bの印加によって補正する。

## 【0039】

逆バイアス印加手段9はドライブトランジスタTr2のゲート(G)に逆バイアスVm bを印加する為にオン/オフ駆動される薄膜型のスイッチングトランジスタTr4を含ん

10

20

30

40

50

でいる。このスイッチングトランジスタTr4は、順バイアスのゲートパルスMBSに応じてオン状態となって、ドライブトランジスタTr2のゲート(G)に対する逆バイアスVm bの印加を開始する。ここで図10(B)のタイミングチャートから明らかな様に、スイッチングトランジスタTr4がオン状態にある時間(逆バイアス書き込み時間)は、逆バイアスを印加する所定時間(逆バイアス期間)より短く設定されており、順バイアスのゲートパルスMBSの印加によるスイッチングトランジスタTr4自体の閾電圧の変動を軽減している。

#### 【0040】

具体的に見ると、スイッチングトランジスタTr4は、ドレインがドライブトランジスタTr2のゲート(G)に接続し、ソースがドライブトランジスタTr2のソース(S)電位よりも低く設定された負電位(Vmb)の電源に接続し、ゲートパルスMBSが入力された時ドレイン/ソース間がオン状態となって負電位Vm bを逆バイアスとしてドライブトランジスタTr2のゲート(G)に印加するとともに、この負電位Vm bを保持容量C1に書き込む様にしている。ここで再び図10(B)のタイミングチャートを参照すると明らかな様に、保持容量C1は、スイッチングトランジスタTr4がオフした後、保持した負電位Vm bによってドライブトランジスタTr2に対する逆バイアスの印加を所定時間(非発光期間)まで維持する。換言すると、逆バイアス印加期間は、スイッチングトランジスタTr4がオン状態にある逆バイアス書き込期間とオフ状態にある逆バイアス保持期間とに分かれている。図9に示したプロトタイプと比較すれば明らかな様に、本実施形態はスイッチングトランジスタTr4のオン状態にある時間が短縮されているので、順バイアスの印加による閾電圧の上方変動を軽減もしくは無視できる。

#### 【0041】

図9のプロトタイプでは、スイッチングトランジスタTr4を逆バイアス期間中常にオンさせている為、ゲートパルスMBSはハイレベルとなっている。これに対し図10の改良形態では、スイッチングトランジスタTr4のオン時間はタイミングチャートに示す様に短縮されている。つまり短縮化されたオン時間以外はオフさせている。この為、スイッチングトランジスタTr4に短い時間しか順バイアスが印加されない為、閾電圧変動は少なくて済む。ここで、逆バイアス印加期間でスイッチングトランジスタTr4がオフしている状態では、保持容量C1によってドライブトランジスタTr2のゲート(G)電位はVm bとなっている。これは、先にスイッチングトランジスタTr4がオンした時、保持容量C1に負電位Vm bを充電しているからである。つまりスイッチングトランジスタTr4がオフしていても逆バイアスVm bがホールドされ、この結果、ドライブトランジスタTr2にも必要な逆バイアスを印加し続けることができる。この様にして、本発明の画素回路は、逆バイアス印加手段によってドライブトランジスタの閾変動を補正しながら、逆バイアス印加用のスイッチングトランジスタ自体の閾変動も軽減できる様にしている。

#### 【0042】

図11は、図2に示した単純な画素回路に改良を加えた別の参考例に係る画素回路を表わしており、(A)は構成を示した回路図、(B)は動作を示したタイミングチャートである。

#### 【0043】

(A)に示す様に、この参考例は、図2の単純な画素回路に、ブートストラップ回路6と閾電圧キャセル回路7を加えた構成となっている。尚、図6に示した先の参考例は、単純な画素回路にブートストラップ回路のみを加えた構成である。図11に示すように、ブートストラップ回路6は発光素子ELの特性変動を吸収する様に、ドライブトランジスタTr2のゲート(G)に印加される信号電位のレベルを自動的に制御するものであり、スイッチングトランジスタTr3を含んでいる。このスイッチングトランジスタTr3のゲートには走査線WSが接続し、ソースは電源電位Vssに接続し、ドレインは保持容量C1の一端に接続するとともにドライブトランジスタTr2のソース(S)に接続している。走査線WSに選択パルスが印加されると、サンプリングトランジスタTr1がオンするとともにスイッチングトランジスタTr3もオンする。これにより、結合容量C2を介

10

20

30

40

50

して保持容量 C 1 に映像信号 V s i g が書き込まれる。この後走査線 W S から選択パルスが解除されるとスイッチングトランジスタ T r 3 がオフする為、保持容量 C 1 は電源電位 V s s から切り離され、ドライブトランジスタ T r 2 のソース ( S ) に結合される。この後走査線 D S に選択パルスが印加されるとスイッチングトランジスタ T r 7 がオンしドライブトランジスタ T r 2 を通って駆動電流が発光素子 E L に供給される。発光素子 E L は発光を開始するとともにその電流 / 電圧特性に応じアノード電位が上昇しドライブトランジスタ T r 2 のソース電位の上昇をもたらす。この時保持容量 C 1 は V s s から切り離されている為ソース電位の上昇とともに保持された信号電位も上昇 ( ブートストラップ ) し、ドライブトランジスタ T r 2 のゲート ( G ) の電位上昇をもたらす。すなわち、発光素子 E L の特性変動があっても、ドライブトランジスタ T r 2 のゲート電圧 V g s は常に保持容量 C 1 に保持された正味の信号電位と一致する様になっている。この様なブートストラップ動作により、発光素子 E L の特性変動があっても、常にドライブトランジスタ T r 2 のドレン電流は保持容量 C 1 に保持された信号電位によって一定に保たれ、発光素子 E L の輝度の変化が生じない。この様なブートストラップ手段 6 を追加することで、ドライブトランジスタ T r 2 は発光素子 E L に対し正確な定電流源として機能できる。

#### 【 0 0 4 4 】

閾電圧キャンセル回路 7 はドライブトランジスタ T r 2 の閾電圧の変動をキャンセルする様にドライブトランジスタ T r 2 のゲート ( G ) に印加される信号電位のレベルを調節するものであり、スイッチングトランジスタ T r 5 , T r 6 を含んでいる。スイッチングトランジスタ T r 5 のゲートは別の走査線 A Z に接続され、ドレン / ソースはドライブトランジスタ T r 2 のゲートとドレンとの間に接続されている。スイッチングトランジスタ T r 6 のゲートは同じく走査線 A Z に接続され、ソースは所定のオフセット電圧 V o f s に接続され、ドレンは結合容量 C 2 の一方の電極に接続されている。尚、図示の例ではオフセット電圧 V o f s 、電源電位 V s s 、カソード電圧 ( G N D ) はそれぞれ異なった電位を取り得るが、場合により全て共通の電位 ( 例えば G N D ) に合わせてもよい。

#### 【 0 0 4 5 】

走査線 A Z に制御パルスが印加されるとスイッチングトランジスタ T r 5 が導通し、 V c c 側からドライブトランジスタ T r 2 のゲートに向かって電流が流れる為、ゲート ( G ) 電位が上昇する。これによりドライブトランジスタ T r 2 にドレン電流が流れ出し、ソース ( S ) の電位が上昇する。ちょうどゲート電位 ( G ) とソース電位 ( S ) の電位差 V g s がドライブトランジスタ T r 2 の閾電圧 V t h と一致したところで、前述のトランジスタ特性式に従って、ドレン電流は流れなくなる。この時のソース / ゲート間電圧 V g s がトランジスタ T r 2 の閾電圧 V t h として保持容量 C 1 に書き込まれる。この保持容量 C 1 に書き込まれた V t h は信号電位 V s i g に上載せしてドライブトランジスタ T r 2 のゲートに印加されるので、閾電圧 V t h の効果はキャンセルされる。従ってドライブトランジスタ T r 2 の閾電圧 V t h が経時的に変動しても、閾電圧キャンセル回路 7 はこの変動をキャンセルすることができる。

#### 【 0 0 4 6 】

( B ) は各走査線 W S , D S , A Z に印加される走査パルス波形とドライブトランジスタ T r 2 のゲート ( G ) 及びソース ( S ) の電位波形を表わすタイミングチャートである。図示する様に V t h キャンセル期間に入ると走査線 A Z にパルスが印加され、スイッチングトランジスタ T r 5 が導通して、 T r 2 のゲート電位が上昇する。その後走査線 D S のパルスが立ち下がる為電源 V c c 側からの電流供給が断たれる。これによりゲート電位とソース電位の差が縮小しちょうど V t h となったところで電流が 0 になる。この結果、 V t h が T r 2 のゲート / ソース間に接続された保持容量 C 1 に書き込まれる。次に走査線 W S に選択パルスが印加されるとサンプリングトランジスタ T r 1 がオンし、結合容量 C 2 を介して保持容量 C 1 に信号 V s i g が書き込まれる。これにより、ドライブトランジスタ T r 2 のゲートに入力される信号 V i n は先に書き込まれた V t h と所定のゲインで保持された V s i g の和となる。更に走査線 D S にパルスが印加され、スイッチングトランジスタ T r 7 がオンする。これによりドライブトランジスタ T r 2 が入力ゲート信号

10

20

30

40

50

$V_{in}$ に応じてドレイン電流を発光素子ELに供給し、発光が開始する。これにより発光素子ELのアノード電位が $V$ だけ上昇するが、ブートストラップ効果によりこの $V$ がドライブトランジスタTr2に対する入力信号 $V_{in}$ に上載せされる。以上の閾電圧キャンセル機能及びブートストラップ機能により、ドライブトランジスタTr2の閾電圧変動や発光素子ELの特性変動があっても、これらをキャンセルして発光輝度を一定に保つことが可能である。

#### 【0047】

ところでドライブトランジスタTr2のゲートには1フィールド期間 $t_f$ を通してソースよりも高い電圧が印加されており、常時順バイアスがかかった状態となっている。ゲートに対する順バイアスの継続的な印加により、ドライブトランジスタTr2の閾電圧 $V_{th}$ は上方変動する。この変動は閾電圧キャンセル回路7によりキャンセル可能であるが、変動が程度を超えるとキャンセル機能が追いつかず発光素子ELの輝度変化をもたらす恐れがある。又スイッチングトランジスタTr7は発光期間中オン状態となり順バイアスがかかっている。これによりスイッチングトランジスタTr7の閾電圧は上方変動し、最悪の場合にはスイッチングトランジスタTr7が常時カットオフ状態に陥ることも有り得る。

#### 【0048】

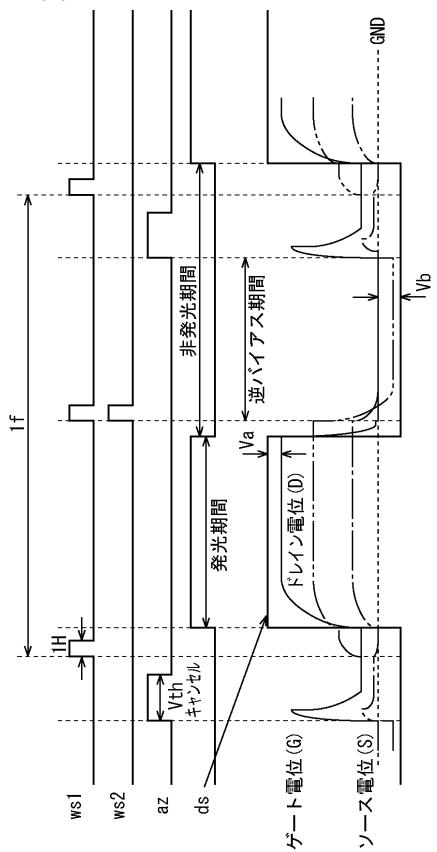

図12は本発明に係る画素回路の他の実施形態を示しており、図11の画素回路の問題点に対処する為、ドライブトランジスタTr2及びスイッチングトランジスタTr7にそれぞれ閾電圧変動抑制用の逆バイアス印加手段を付けたものである。

#### 【0049】

ドライブトランジスタTr2に対する逆バイアス印加手段は、スイッチングトランジスタTr4で構成されている。Tr4のゲートには追加の走査線WS2が接続し、ソースには負電源Vmbが接続し、ドレインはドライブトランジスタTr2のゲート(G)に接続している。この走査線WS2はサンプリングトランジスタTr1やスイッチングトランジスタTr3に接続する走査線WS1と走査タイミングが異なる為、両者を別々に分けて、WS1とWS2にしている。ここで負電源Vmbの電位は接地電位GNDよりも低く設定されている。従って画素回路の動作に影響を与えないタイミングでWS2に選択パルスが印加されると、Tr4がオンしドライブトランジスタTr2のゲート(G)に逆バイアス(Vmb)を印加することができる。これにより順バイアスの継続的な印加で上方シフトしたトランジスタTr2の閾電圧 $V_{th}$ を下方修正することができる。

#### 【0050】

スイッチングトランジスタTr7に対する逆バイアス印加手段は、走査線DSに接続したドライブスキーナ3(図1参照)に組み込まれている。発光期間ではスイッチングトランジスタTr7のゲートに走査線DSを介して順バイアスが印加され、ドレイン電流が $V_{cc}$ からGNDに向かって流れる。非発光期間に入ると走査線DSの電位がGND以下となり、スイッチングトランジスタTr7に逆バイアスが印加される。これによりTr7の閾電圧の上方変動を下方修正できる。

#### 【0051】

図13は、図12に示した画素回路の動作説明に供するタイミングチャートである。走査線WS1に印加されるパルスをws1で表わし、走査線WS2に印加されるパルスをws2で表わし、走査線AZに印加されるパルスをazで表わし、走査線DSに印加されるパルスをdsで表わしている。更に、ドライブトランジスタTr2のゲート電位(G)、ドレイン電位(D)及びソース電位(S)の変動をパルスdsのレベル変化と重ねて表わしてある。尚、ドライブトランジスタTr2のドレイン電位(D)は同時にスイッチングトランジスタTr7のソース電位となっている。

#### 【0052】

$V_{th}$ キャンセル期間ではパルスazがトランジスタTr5及びTr6に印加され、ドライブトランジスタTr2の閾電圧 $V_{th}$ が検知される。この検知された $V_{th}$ はTr2のゲート電位(G)とソース電位(S)との間の差として保持容量C1に保持される。次

10

20

30

40

50

にパルス  $w_s 1$  がサンプリングトランジスタ  $T_r 1$  及びスイッチングトランジスタ  $T_r 3$  に印加されると、映像信号  $V_{sig}$  がサンプリングされ、結合容量  $C_2$  を介して保持容量  $C_1$  に書き込まれる。保持容量  $C_1$  に書き込まれた  $V_{th}$  及び  $V_{sig}$  の和が、 $T_r 2$  のゲート電位 ( $G$ ) とソース電位 ( $S$ ) の差としてタイミングチャートに表われている。更に発光期間に入つてスイッチングトランジスタ  $T_r 7$  にパルス  $d_s$  が印加されると、ドライブトランジスタ  $T_r 2$  を通してドレイン電流が発光素子  $E_L$  に流れる。これによりソース電位 ( $S$ ) が上昇するが、ブートストラップ機能によりゲート電位 ( $G$ ) との電位差は一定に保たれる。ソース電位 ( $S$ ) の上昇に伴つてドレイン電位 ( $D$ ) も上昇する。このドレイン電位 ( $D$ ) はスイッチングトランジスタ  $T_r 7$  のソース電位となっているが、パルス  $D_s$  の振幅はこのドレイン電位 ( $D$ ) よりも十分高く設定されているので、トランジスタ  $T_r 7$  のオン動作に必要な順バイアス  $V_a$  が印加できる。その後非発光期間に入るとパルス  $D_s$  がローレベルに切り替わり、トランジスタ  $T_r 7$  はカットオフする。ドレイン電流の遮断によりドライブトランジスタ  $T_r 2$  のドレイン電位 ( $D$ ) は  $V_{cc}$  側から  $GND$  まで下がる。この時パルス  $d_s$  のローレベルは  $GND$  よりも低く設定されている為、スイッチングトランジスタ  $T_r 7$  のゲートには逆バイアス  $V_b$  が印加される。又非発光期間にはトランジスタ  $T_r 4$  のゲートにパルス  $w_s 2$  が印加される。これにより  $T_r 4$  が導通し逆バイアス  $V_{mb}$  がドライブトランジスタ  $T_r 2$  のゲート ( $G$ ) に印加される。以上の説明から明らかな様に、ドライブトランジスタ  $T_r 2$  及びスイッチングトランジスタ  $T_r 7$  にそれぞれ適切なタイミングで逆バイアスが印加される為、それぞれの閾電圧の変動を抑制できる。

10

20

### 【0053】

図14は本発明に係る画素回路の別の実施形態を表わしており、図12に示した先の実施形態の改良版となっている。理解を容易にする為、図12に示した実施形態と対応する部分には対応する参照番号を付してある。先の実施形態と同様に、本実施形態も閾電圧キャンセル回路を備えている。前述した様に、この閾電圧キャンセル回路は、負荷素子  $E_L$  の通電に先立つてドライブトランジスタ  $T_r 2$  の閾電圧を検知し、あらかじめその影響をキャンセルする為に必要な電位を保持容量  $C_1$  に保持させて、ドライブトランジスタ  $T_r 2$  のゲートに印加するものである。この閾電圧キャンセル回路は、ドライブトランジスタ  $T_r 2$  の閾電圧を検知する為の検知トランジスタ  $T_r 5$  を含んでいる。検知トランジスタ  $T_r 5$  は、そのソース / ドレインが、ドライブトランジスタ  $T_r 2$  のドレイン ( $D$ ) とゲート ( $G$ ) との間に接続され、そのゲートはドライブトランジスタ  $T_r 2$  の閾電圧を検知する時以外負電位に維持されている。換言すると、検知トランジスタ  $T_r 5$  のゲートには走査線  $A_Z$  を介してパルスが印加され、ドライブトランジスタ  $T_r 2$  の閾電圧を検知して保持容量  $C_1$  に書き込んでいる。この走査線  $A_Z$  の基準レベルは負電位に設定されている。従つて、検知トランジスタ  $T_r 5$  のゲートはドライブトランジスタ  $T_r 2$  の閾電圧を検知する時以外負電位に維持されることになる。本実施形態の特徴事項として、逆バイアス印加用のスイッチングトランジスタ  $T_r 4$  は、そのソースが検知トランジスタ  $T_r 5$  のゲートに接続し、これに印加される負電位を逆バイアスとして利用している。換言すると、逆バイアス印加用のスイッチングトランジスタ  $T_r 4$  のソースには走査線  $A_Z$  が接続されている。これにより、別途負電位  $V_{mb}$  の電源ラインを用意する必要がなくなり、画素回路のレイアウトを簡略化できる。この様に本改良版は、スイッチングトランジスタ  $T_r 4$  のソース側となるノードを負電位  $V_{mb}$  に接続せず、走査線  $A_Z$  に接続する。逆バイアス印加期間中、スイッチングトランジスタ  $T_r 4$  がオンしている状態の時、走査線  $A_Z$  は負電位にある為、図12の実施形態と同等の効果が得られ、ドライブトランジスタ  $T_r 2$  の閾変動を容易に抑えることが可能である。

30

40

### 【図面の簡単な説明】

#### 【0054】

【図1】アクティブマトリクス表示装置及び画素回路の一般的な構成を示すブロック図である。

【図2】画素回路の参考例を示す回路図である。

50

【図3】図2に示した画素回路の動作説明に供するタイミングチャートである。

【図4】有機EL素子のI-V特性の経時変化を示すグラフである。

【図5】ドライブトランジスタと有機EL素子の動作点の経時変化を示すグラフである。

【図6】画素回路の他の参考例を示す回路図である。

【図7】図6に示した画素回路の動作説明に供するタイミングチャートである。

【図8】薄膜トランジスタのデバイス特性を示すグラフである。

【図9】本発明に係る画素回路の実施形態を示す模式図である。

【図10】本発明に係る画素回路のプロトタイプを示す回路図及びタイミングチャートである。

【図11】画素回路の別の参考例を示す模式図である。

10

【図12】本発明に係る画素回路の他の実施形態を示す回路図である。

【図13】図12に示した実施形態の動作説明に供するタイミングチャートである。

【図14】本発明に係る画素回路の更なる改良形態を示す回路図である。

【符号の説明】

【0055】

1 …… 画素アレイ、2 …… 水平セレクタ、3 …… ドライブスキャナ、4 …… ライ

トスキャナ、5 …… 画素回路、9 …… 逆バイアス印加手段

【図1】

【図2】

【図3】

【図4】

EL素子のI-V特性の経時変化

【図5】

(A)

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 G 3/20 6 7 0 J

(56)参考文献 特開2002-236470(JP,A)

特開2003-202833(JP,A)

特開2004-118132(JP,A)

特開2004-102278(JP,A)

特開2005-164894(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路和显示设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP4501429B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2010-07-14 |

| 申请号            | JP2004000592                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2004-01-05 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| [标]发明人         | 内野勝秀<br>山下淳一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 内野 勝秀<br>山下 淳一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| CPC分类号         | G09G2310/0254                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.624.E G09G3/20.641.D G09G3/20.642.P G09G3/20.670.J<br>G09G3/20.670.K G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291 H05B33/14.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 3K007/AB02 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 3K107/AA01 3K107/<br>/BB01 3K107/CC21 3K107/CC31 3K107/EE03 3K107/HH04 5C080/AA06 5C080/BB05 5C080/DD29<br>5C080/EE28 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C380/AA01 5C380/AB06<br>5C380/AB22 5C380/AB23 5C380/BA38 5C380/BA39 5C380/BB02 5C380/BB21 5C380/BD02 5C380<br>/BD05 5C380/BD08 5C380/BD10 5C380/CA08 5C380/CA12 5C380/CB01 5C380/CB16 5C380/CB18<br>5C380/CB19 5C380/CB27 5C380/CC02 5C380/CC04 5C380/CC07 5C380/CC27 5C380/CC30 5C380<br>/CC33 5C380/CC39 5C380/CC52 5C380/CC61 5C380/CC63 5C380/CC64 5C380/CC65 5C380/CD013<br>5C380/CD014 5C380/CD026 5C380/CD027 5C380/DA02 5C380/DA06 5C380/DA47 |         |            |

| 其他公开文献         | JP2005195756A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

## 摘要(译)

要解决的问题：提供一种像素电路，其中抑制了驱动晶体管的阈值电压随时间的变化。ΣSOLUTION：在采样晶体管Tr1中，当通过扫描线WS选择栅极时，源极和漏极之间的线变为导通，并且来自信号线DL的信号Vsig被采样并保持在保持电容C1中。在驱动晶体管Tr2中，栅极G接收正极性的正向偏压，通过保持电容C1中保持的信号电位参考源极S，以及根据正向流动在源极和漏极之间流动的电流Ids。偏压，导致流向负载装置EL。反向偏压施加装置9包括用于将负电位Vmb写入电容C1的开关晶体管Tr4，施加负电位Vmb作为反向偏压，即相对于源极S的负极性，并执行向下调节通过施加正向偏压产生的阈值电压的向上变化。Σ

【图2】