(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-233129

(P2008-233129A)

(43) 公開日 平成20年10月2日(2008.10.2)

(51) Int.Cl.

**G09G** 3/30 (2006.01)

**G09G** 3/20 (2006.01)

**H01L** 51/50 (2006.01)

F 1

|         |      |   |

|---------|------|---|

| G O 9 G | 3/30 |   |

| G O 9 G | 3/20 | 6 |

| G O 9 G | 3/20 | 6 |

| G O 9 G | 3/20 | 6 |

| G O 9 G | 3/20 | 6 |

### テーマコード（参考）

3K107

5C080

審査請求 未請求 請求項の数 7 O.L. (全 34 頁) 最終頁に続く

(21) 出願番号

(22) 出願日

特願2007-68020 (P2007-68020)

平成19年3月16日 (2007. 3. 16)

(71) 出願人 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

100086298

弁理士 船橋 國則

豊村 直史

東京都港区港南1丁目7番1号 ソニー株

式会社内

式会社内

内野 动男

東京都港区港南1丁目7番1号 ソニー株

式会社内

式芸社内

東京都港区港南1丁目7番1号 ソニー株式会社内

最終頁に続く

(54) 【発明の名称】 画素回路および表示装置とその駆動方法

(57) 【要約】

【課題】移動度補正機能を有する有機EL表示装置において、映像信号振幅を大きくしなくても、移動度補正に起因する発光輝度低下を防止できるようにする。

【解決手段】発光制御トランジスタ122のゲート端Gと駆動トランジスタ121のソース端Sに容量素子129を追加する。移動度補正によるゲート・ソース間電圧 $V_{gs}$ の低下分 $V$ を、移動度補正動作の開始時に、移動度補正時に消費される分の電圧 $V$ を発光制御トランジスタ122に供給される走査駆動パルスDSによるカッピングにより電圧 $V_{DSb}$ の分だけ上乗せし補うことで、発光期間におけるゲート・ソース間電圧 $V_{gs}$ を広げる。移動度補正に起因する発光輝度低下を防止でき、映像信号 $V_{sig}$ の振幅を下げる事ができ、通常の映像信号 $V_{sig}$ のみを保持容量120に書き込むだけによく、低消費電力化に寄与できる。

【選択図】 図 7

## 【特許請求の範囲】

## 【請求項 1】

駆動電流を生成する駆動トランジスタ、前記駆動トランジスタの出力端に接続された電気光学素子、映像信号の信号電位に応じた情報を保持する保持容量、前記信号電位に応じた情報を前記保持容量に書き込むサンプリングトランジスタ、および一方の端子が前記駆動トランジスタの出力端に接続され他方の端子にパルス信号が供給される容量素子を具備し、前記保持容量に保持された情報に基づく駆動電流を前記駆動トランジスタで生成して前記電気光学素子に流すことで当該電気光学素子が発光する画素回路が行列状に配置されている画素アレイ部と、

前記サンプリングトランジスタを水平周期で順次制御することで前記画素回路を線順次走査して1行分の各保持容量に映像信号の信号電位に応じた情報を書き込むための書き込み走査パルスを前記サンプリングトランジスタに出力する書き込み走査部、前記サンプリングトランジスタによる信号電位の書き込み動作に合わせて1行分の映像信号を前記映像信号線に供給する水平駆動部を具備する制御部とを備え、

前記制御部は、前記サンプリングトランジスタを導通状態にして前記信号電位に応じた情報を前記保持容量に保持させた後に前記サンプリングトランジスタを導通状態にしたままで前記駆動トランジスタの移動度に対する補正分を前記保持容量に書き込まれる情報に加えるための移動度補正動作を行なうように制御し、

前記容量素子の他方の端子は前記移動度補正動作を開始させるパルスに対応する情報が供給され、

前記駆動トランジスタの出力端は、当該駆動トランジスタの制御入力端と出力端の電位差が大きくなる方向の遷移情報が前記容量素子を介して供給される

ことを特徴とする表示装置。

## 【請求項 2】

前記電気光学素子の発光期間と非発光期間のデューティを調整する発光制御トランジスタを備え、

前記発光制御トランジスタの制御入力端に供給される走査駆動パルスを、前記移動度補正動作を開始させるパルスとする

ことを特徴とする請求項1に記載の表示装置。

## 【請求項 3】

n型およびp型の何れか一方の型の前記駆動トランジスタの電源供給端側に前記電気光学素子の発光期間と非発光期間のデューティを調整する前記n型およびp型の他方の型の発光制御トランジスタを備え、

前記容量素子の他方の端子は前記発光制御トランジスタの制御入力端に接続されており、

前記発光制御トランジスタの制御入力端に供給される走査駆動パルスを、前記移動度補正動作を開始させるパルスとする

ことを特徴とする請求項1に記載の表示装置。

## 【請求項 4】

前記制御部は、前記サンプリングトランジスタに基準電位が供給されている時間帯で前記サンプリングトランジスタを導通させ、前記駆動トランジスタの閾値電圧に対応する電圧を前記保持容量に保持するための閾値補正動作を行なうように制御し、この閾値補正動作の後、前記駆動トランジスタの移動度に対する補正分を前記保持容量に書き込まれる情報に加えるための移動度補正動作を行なうように制御する

ことを特徴とする請求項1に記載の表示装置。

## 【請求項 5】

前記画素回路は、前記駆動トランジスタおよび前記サンプリングトランジスタの他に、前記制御部による閾値補正動作や前記移動度補正動作時の制御パルスに基づいてオン／オフ動作するスイッチトランジスタを具備する

ことを特徴とする請求項4に記載の表示装置。

10

20

30

40

50

**【請求項 6】**

駆動電流を生成する駆動トランジスタと、

前記駆動トランジスタの出力端に接続された電気光学素子と、

映像信号の信号電位に応じた情報を保持する保持容量と、

前記信号電位に応じた情報を前記保持容量に書き込むサンプリングトランジスタと、

一方の端子が前記駆動トランジスタの出力端に接続された容量素子と

を具備し、

前記容量素子の他方の端子は、前記駆動トランジスタの移動度に対する補正分を前記保持容量に書き込まれる情報に加えるための移動度補正動作を開始させるパルスに対応する

10 、前記駆動トランジスタの制御入力端と出力端の電位差を大きくする方向の遷移情報が供給される

ことを特徴とする画素回路。

**【請求項 7】**

駆動電流を生成する駆動トランジスタと、前記駆動トランジスタの出力端に接続された電気光学素子と、映像信号の信号電位に応じた情報を保持する保持容量と、前記信号電位に応じた情報を前記保持容量に書き込むサンプリングトランジスタと、一方の端子が前記駆動トランジスタの出力端に接続され他方の端子にパルス信号が供給される容量素子とを具備し、前記保持容量に保持された情報に基づく駆動電流を前記駆動トランジスタで生成して前記電気光学素子に流すことで当該電気光学素子が発光する画素回路の駆動方法であつて、

前記サンプリングトランジスタを導通状態にして前記信号電位に応じた情報を前記保持容量に保持させた後に前記サンプリングトランジスタを導通状態にしたままで前記駆動トランジスタの移動度に対する補正分を前記保持容量に書き込まれる情報に加えるための移動度補正動作を行なう際に、前記移動度補正動作を開始させるパルスに対応する情報を前記容量素子の他方の端子に供給して、前記駆動トランジスタの制御入力端と出力端の電位差を大きくする

20

ことを特徴とする駆動方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、電気光学素子（表示素子や発光素子とも称される）を具備する画素回路（画素とも称される）と、この画素回路が行列状に配列された画素アレイ部を有する表示装置と、その駆動方法に関する。より詳細には、駆動信号の大小によって輝度が変化する電気光学素子を表示素子として有する画素回路と、この画素回路が行列状に配置されてなり、画素回路ごとに能動素子を有して当該能動素子によって画素単位で表示駆動が行なわれるアクティブマトリクス型の表示装置と、その駆動方法に関する。

30

**【背景技術】****【0002】**

画素の表示素子として、印加される電圧や流れる電流によって輝度が変化する電気光学素子を用いた表示装置がある。たとえば、印加される電圧によって輝度が変化する電気光学素子としては液晶表示素子が代表例であり、流れる電流によって輝度が変化する電気光学素子としては、有機エレクトロルミネッセンス（Organic Electro Luminescence, 有機EL, Organic Light Emitting Diode, OLED；以下、有機ELと記す）素子が代表例である。後者の有機EL素子を用いた有機EL表示装置は、画素の表示素子として、自発光素子である電気光学素子を用いたいわゆる自発光型の表示装置である。

40

**【0003】**

有機EL素子は有機薄膜に電界をかけると発光する現象を利用した電気光学素子である。有機EL素子は比較的低い印加電圧（たとえば10V以下）で駆動できるため低消費電力である。また有機EL素子は自ら光を発する自発光素子であるため、液晶表示装置では必要とされるバックライトなどの補助照明部材を必要とせず、軽量化および薄型化が容易

50

である。さらに、有機EL素子の応答速度は非常に高速である（たとえば数μs程度）ので、動画表示時の残像が発生しない。これらの利点があることから、電気光学素子として有機EL素子を用いた平面自発光型の表示装置の開発が近年盛んになっている。

#### 【0004】

ところで、液晶表示素子を用いた液晶表示装置や有機EL素子を用いた有機EL表示装置を始めとする電気光学素子を用いた表示装置においては、その駆動方式として、単純（パッシブ）マトリクス方式とアクティブマトリクス方式とを探ることができる。ただし、単純マトリクス方式の表示装置は、構造が単純であるもの、大型でかつ高精細の表示装置の実現が難しいなどの問題がある。

#### 【0005】

このため、近年、画素内部の発光素子に供給する画素信号を、同様に画素内部に設けた能動素子、たとえば絶縁ゲート型電界効果トランジスタ（一般には、薄膜トランジスタ（Thin Film Transistor ; TFT）をスイッチングトランジスタとして使用して制御するアクティブマトリクス方式の開発が盛んに行なわれている。

#### 【0006】

ここで、画素回路内の電気光学素子を発光させる際には、映像信号線を介して供給される入力画像信号をスイッチングトランジスタで駆動トランジスタのゲート端（制御入力端子）に設けられた保持容量（画素容量とも称する）に取り込み、取り込んだ入力画像信号に応じた駆動信号を電気光学素子に供給する。

#### 【0007】

電気光学素子として液晶表示素子を用いる液晶表示装置では、液晶表示素子が電圧駆動型の素子であることから、保持容量に取り込んだ入力画像信号に応じた電圧信号そのもので液晶表示素子を駆動する。これに対して、電気光学素子として有機EL素子などの電流駆動型の素子を用いる有機EL表示装置では、保持容量に取り込んだ入力画像信号に応じた駆動信号（電圧信号）を駆動トランジスタで電流信号に変換して、その駆動電流を有機EL素子などに供給する。

#### 【0008】

有機EL素子を代表例とする電流駆動型の電気光学素子では、駆動電流値が異なると発光輝度も異なる。よって、安定した輝度で発光させるためには、安定した駆動電流を電気光学素子に供給することが肝要となる。たとえば、有機EL素子に駆動電流を供給する駆動方式としては、定電流駆動方式と定電圧駆動方式とに大別できる（周知の技術であるので、ここでは公知文献の提示はしない）。

#### 【0009】

有機EL素子の電圧・電流特性は傾きの大きい特性を有するので、定電圧駆動を行なうと、僅かな電圧のばらつきや素子特性のばらつきが大きな電流のばらつきを生じ大きな輝度ばらつきをもたらす。よって、一般的には、駆動トランジスタを飽和領域で使用する定電流駆動が用いられる。もちろん、定電流駆動でも、電流変動があれば輝度ばらつきを招くが、小さな電流ばらつきであれば小さな輝度ばらつきしか生じない。

#### 【0010】

逆に言えば、定電流駆動方式であっても、電気光学素子の発光輝度が不变であるためには、入力画像信号に応じて保持容量に書き込まれ保持される駆動信号が一定であることが重要となる。たとえば、有機EL素子の発光輝度が不变であるためには、入力画像信号に応じた駆動電流が一定であることが重要となる。

#### 【0011】

ところが、プロセス変動により電気光学素子を駆動する能動素子（駆動トランジスタ）の閾値電圧や移動度がばらついてしまう。また、有機EL素子などの電気光学素子の特性が経時的に変動する。このような駆動用の能動素子の特性ばらつきや電気光学素子の特性変動があると、定電流駆動方式であっても、発光輝度に影響を与えてしまう。

#### 【0012】

このため、表示装置の画面全体に亘って発光輝度を均一に制御するため、各画素回路内

10

20

30

40

50

で上述した駆動用の能動素子や電気光学素子の特性変動に起因する輝度変動を補正するための仕組みが種々検討されている。

【0013】

【特許文献1】特開2006-215213号公報

【0014】

たとえば、特許文献1に記載の仕組みでは、有機EL素子用の画素回路として、駆動トランジスタの閾値電圧にばらつきや経時変化があった場合でも駆動電流を一定にするための閾値補正機能や、駆動トランジスタの移動度にばらつきや経時変化があった場合でも駆動電流を一定にするための移動度補正機能や、有機EL素子の電流・電圧特性に経時変化があった場合でも駆動電流を一定にするためのブーストアップ機能が提案されている。 10

【発明の開示】

【発明が解決しようとする課題】

【0015】

しかしながら、特許文献1に記載の仕組みでは、サンプリングトランジスタをオンさせて映像信号に対応する駆動電位を保持容量に保持させた後にサンプリングトランジスタをオンさせたままで移動度補正期間に入る。このため、駆動トランジスタのゲート電位が固定された状態で移動度補正動作が行なわれるで、移動度補正によりゲート・ソース間電圧が減少し、そのままでは発光輝度が低下してしまう弊害がある。

【0016】

この移動度補正に起因する発光輝度低下を防止する一手法として、たとえば、移動度補正によるゲート・ソース間電圧の減少分を補うように、より大きな映像信号を供給して保持容量に駆動電位を書き込むことが考えられる。しかしながらこの手法では、移動度補正を行なわない場合に比べて映像信号振幅を大きくしなければならず、電源電圧や書き込み駆動パルスを大きくする必要が生じ、消費電圧の増大へと繋がってしまう。 20

【0017】

本発明は、前記事情に鑑みてなされたもので、映像信号振幅を大きくしなくとも、移動度補正に起因する発光輝度低下を防止することのできる仕組みを提供することを目的とする。

【課題を解決するための手段】

【0018】

本発明に係る表示装置の一実施形態は、映像信号に基づいて画素回路内の電気光学素子を発光させる表示装置であって、先ず、画素アレイ部に行列状に配される画素回路内に、少なくとも、駆動電流を生成する駆動トランジスタ、駆動トランジスタの出力端に接続された電気光学素子、映像信号の信号電位に応じた情報（駆動電位）を保持する保持容量、保持容量に映像信号における信号電位に応じた情報を書き込むサンプリングトランジスタを備える。この画素回路においては、保持容量に保持された情報に基づく駆動電流を駆動トランジスタで生成して電気光学素子に流すことで電気光学素子を発光させる。 30

【0019】

サンプリングトランジスタで保持容量に信号電位に応じた情報を駆動電位として書き込むので、サンプリングトランジスタは、その入力端（ソース端もしくはドレイン端の一方）に信号電位を取り込み、その出力端（ソース端もしくはドレイン端の他方）に接続された保持容量に信号電位に応じた情報を書き込む。もちろん、サンプリングトランジスタの出力端は、駆動トランジスタの制御入力端にも接続されている。 40

【0020】

なお、ここで示した画素回路の接続構成は、最も基本的な構成を示したもので、画素回路は、少なくとも前述の各構成要素を含むものであればよく、これらの構成要素以外（つまり他の構成要素）が含まれていてもよい。また、「接続」は、直接に接続されている場合に限らず、他の構成要素を介在して接続されている場合でもよい。

【0021】

たとえば、接続間には、必要に応じてさらに、スイッチング用のトランジスタや、ある

10

20

30

40

50

機能を持った機能部などを介在させるなどの変更が加えられることがある。典型的には、表示期間（換言すれば非発光時間）を動的に制御するためにスイッチング用のトランジスタ（発光制御トランジスタ）を、駆動トランジスタの出力端と電気光学素子との間に、もしくは駆動トランジスタの電源供給端（ドレイン端が典型例）と電源供給用の配線である電源線との間に配することがある。

#### 【0022】

このような変形態様の画素回路であっても、本項（課題を解決するための手段）で説明する構成や作用を実現し得るものである限り、それらの変形態様も、本発明に係る表示装置の一実施形態を実現する画素回路である。

#### 【0023】

また、画素回路を駆動するための周辺部には、たとえば、サンプリングトランジスタを水平周期で順次制御することで画素回路を線順次走査して、1行分の各保持容量に映像信号の信号電位に応じた情報を書き込む書込走査部、および書込走査部での線順次走査に合わせて1行分の各駆動トランジスタの電源供給端に印加される電源供給を制御するための走査駆動パルスを出力する駆動走査部を具備する制御部を設ける。

#### 【0024】

また、制御部には、書込走査部での線順次走査に合わせて各水平周期内に基準電位と信号電位で切り替わる映像信号がサンプリングトランジスタに供給されるように制御する水平駆動部を設ける。

#### 【0025】

制御部は、さらに少なくとも、サンプリングトランジスタを導通状態にして信号電位に応じた情報（駆動電位）を保持容量に保持させた後にサンプリングトランジスタを導通状態にしたままで駆動トランジスタの移動度に対する補正分を保持容量に書き込まれる情報に加えるための移動度補正動作を行なうように制御する。必要に応じて、その制御のための補正走査部を設ける。

#### 【0026】

制御部は、さらに好ましくは、駆動電流を流すために使用される第1電位に対応する電圧（いわゆる電源電圧）が駆動トランジスタの電源供給端に供給されている時間帯で駆動トランジスタの閾値電圧に対応する電圧を保持容量に保持するための閾値補正動作を行なうように制御する。必要に応じて、その制御のための補正走査部を設ける。

#### 【0027】

移動度補正動作用の補正走査部と閾値補正動作用の補正走査部とは、別物であってもよいし、画素回路の構成によっては兼用されたものとすることもできる。それに合わせて、画素回路も移動度補正動作用や閾値補正動作用の補正走査部からのパルスを受けて動作する補正用スイッチトランジスタを1つもしくは2つ設ける。なお、発光制御トランジスタを設ける場合には、補正用スイッチトランジスタだけでなく、発光制御トランジスタも移動度補正動作や閾値補正動作に関わりを持つようになる。発光制御トランジスタは、補正用スイッチトランジスタとしての機能も持つのである。

#### 【0028】

この閾値補正動作は、必要に応じて、信号電位の保持容量への書き込みに先行する複数の水平周期で繰り返し実行するとよい。ここで「必要に応じて」とは、1水平周期内の閾値補正期間では駆動トランジスタの閾値電圧に相当する電圧を十分に保持容量へ保持させることができない場合を意味する。閾値補正動作の複数回の実行により、確実に駆動トランジスタの閾値電圧に相当する電圧を保持容量に保持させるのである。

#### 【0029】

また、さらに好ましくは、制御部は、閾値補正動作に先立って、駆動トランジスタの制御入力端と出力端の電位を、両端の電位差が閾値電圧以上になるように初期化する閾値補正用の準備動作を実行するように制御する。より詳しくは、制御入力端と出力端との間に保持容量を接続しておくことで、保持容量の両端の電位差が閾値電圧以上になるように設定するのである。

10

20

30

40

50

## 【0030】

さらに好ましくは、制御部は、閾値補正動作の後、サンプリングトランジスタに信号電位が供給されている時間帯でサンプリングトランジスタを導通させることで、保持容量に信号電位の情報を書き込んでから、駆動トランジスタの移動度に対する補正分を保持容量に書き込まれる信号に加えるように制御する。

## 【0031】

さらに好ましくは、制御部は、保持容量に信号電位に対応する情報が書き込まれた時点でサンプリングトランジスタを非導通状態にして駆動トランジスタの制御入力端への映像信号の供給を停止させ、駆動トランジスタの出力端の電位変動に制御入力端の電位が連動するブートストラップ動作を行なうように制御する。

10

## 【0032】

制御部は、好ましくはブートストラップ動作を、サンプリング動作の終了後の特に発光開始の初期でも実行するようとする。すなわち、信号電位がサンプリングトランジスタに供給されている状態でサンプリングトランジスタを導通状態にした後にサンプリングトランジスタを非導通状態にすることで、駆動トランジスタの制御入力端と出力端の電位差が一定に維持されるようとする。

20

## 【0033】

また、制御部は、好ましくはブートストラップ動作を、発光期間において電気光学素子の経時変動補正動作を実現するように制御する。このため、制御部は、保持容量に保持された情報に基づく駆動電流が電気光学素子に流れている期間は継続的にサンプリングトランジスタを非導通状態にしておくことで、制御入力端と出力端の電圧を一定に維持可能にして電気光学素子の経時変動補正動作を実現するとよい。

30

## 【0034】

ここで、本発明に係る画素回路および表示装置の一実施形態における特徴的な事項として、前述の構成の画素回路をベースとして、画素回路ごとに、一方の端子が駆動トランジスタの出力端に接続され他方の端子にパルス信号が供給される容量素子を設ける。そして、容量素子の他方の端子には、移動度補正動作を開始させるパルス信号を供給する。これにより、駆動トランジスタの出力端は、駆動トランジスタの制御入力端と出力端の電位差が大きくなる方向の遷移情報が容量素子を介して供給されるようになる。こうすることで、移動度補正開始時に駆動トランジスタの制御入力端と出力端の電位差を広げておいてから移動度補正を行なうことができる。

40

## 【0035】

容量素子の他方の端子に供給する、移動度補正動作を開始させるパルス信号は、画素回路の構成や駆動タイミングに応じて様々なものが考えられる。たとえば、駆動トランジスタおよびサンプリングトランジスタの他に、閾値補正動作や移動度補正動作時の制御パルスに基づいてオン／オフ動作する2つのスイッチトランジスタを備え、また発光期間のデューティを調整する発光制御トランジスタを備える特許文献1に記載のような5TR構成の場合において、サンプリングトランジスタに供給する書込駆動パルスと発光制御トランジスタに供給する走査駆動パルスがともにアクティブとなる期間で移動度補正動作を行なう場合、発光制御トランジスタの制御入力端に供給される走査駆動パルスを、移動度補正動作を開始させるパルスとするのがよい。

40

## 【0036】

さらにこの場合において、n型およびp型の何れか一方の型の駆動トランジスタの電源供給端側にn型およびp型の他方の型の発光制御トランジスタを備える構成の場合には、容量素子の他方の端子を発光制御トランジスタの制御入力端に接続して、他方の端子に走査駆動パルスを供給するようすればよい。

50

## 【0037】

もちろんこれは一例であり、駆動トランジスタの電気光学素子側である出力端に容量素子の一方の端子を接続し、他方の端子に移動度補正動作を開始するパルスに対応する情報を供給することで、そのパルスの遷移情報（特に移動度補正開始時の駆動トランジスタの

ゲート・ソース間電圧を広げる方向の情報)を駆動トランジスタの出力端に供給するものであればよい。

**【発明の効果】**

**【0038】**

本発明の一実施形態によれば、容量素子を追加し、その容量素子の一方の端子を駆動トランジスタの出力端に接続し、他方の端子に移動度補正動作を開始させるパルスに対応する情報を供給して、駆動トランジスタの制御入力端と出力端の電位差を大きくするようにした。

**【0039】**

サンプリングトランジスタを導通状態にして信号電位に応じた情報を保持容量に保持させた後にサンプリングトランジスタを導通状態にしたままで移動度補正動作を行なう際に、移動度補正開始時に駆動トランジスタの制御入力端と出力端の電位差を予め広げておいてから移動度補正を行なうことができるので、駆動トランジスタの制御入力端と出力端の電位差の移動度補正に伴う減少分を補うことができる。

**【0040】**

その結果、発光期間における駆動電位を広げることができるので、映像信号振幅を大きくしなくとも、移動度補正に起因する発光輝度低下を防止できる。映像信号振幅を大きくしなくとも済むので、低消費電力化に寄与することもできる。

**【発明を実施するための最良の形態】**

**【0041】**

以下、図面を参照して本発明の実施形態について詳細に説明する。

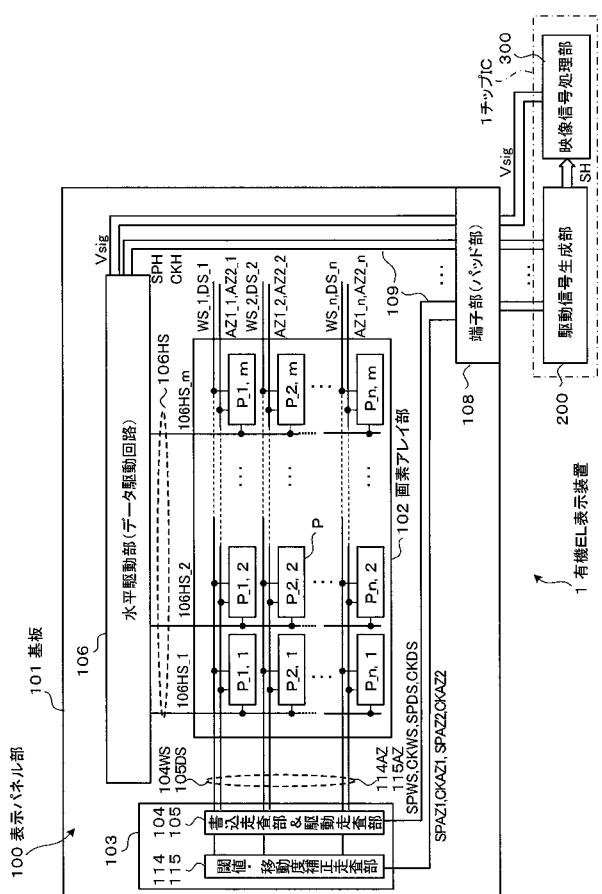

**【0042】**

<表示装置の全体概要>

図1は、本発明に係る表示装置の一実施形態であるアクティブマトリクス型表示装置の構成の概略を示すプロック図である。本実施形態では、たとえば画素の表示素子として有機EL素子を、能動素子としてポリシリコン薄膜トランジスタ(TFT; Thin Film Transistor)をそれぞれ用い、薄膜トランジスタを形成した半導体基板上に有機EL素子を形成してなるアクティブマトリクス型有機ELディスプレイ(以下「有機EL表示装置」と称する)に適用した場合を例に採って説明する。

**【0043】**

なお、以下においては、画素の表示素子として有機EL素子を例に具体的に説明するが、これは一例であって、対象となる表示素子は有機EL素子に限らない。一般的に電流駆動で発光する発光素子の全てに、後述する全ての実施形態が同様に適用できる。

**【0044】**

図1に示すように、有機EL表示装置1は、複数の表示素子としての有機EL素子(図示せず)を持った画素回路(画素とも称される)110が表示アスペクト比である縦横比がX:Y(たとえば9:16)の有效映像領域を構成するように配置された表示パネル部100と、この表示パネル部100を駆動制御する種々のパルス信号を発するパネル制御部の一例である駆動信号生成部200と、映像信号処理部300を備えている。駆動信号生成部200と映像信号処理部300とは、1チップのIC(Integrated Circuit; 半導体集積回路)に内蔵されている。

**【0045】**

なお、製品形態としては、図示のように、表示パネル部100、駆動信号生成部200、および映像信号処理部300の全てを備えたモジュール(複合部品)形態の有機EL表示装置1として提供されることに限らず、たとえば、表示パネル部100のみで有機EL表示装置1として提供することも可能である。また、このような有機EL表示装置1は、半導体メモリやミニディスク(MD)やカセットテープなどの記録媒体を利用した携帯型の音楽プレイヤーやその他の電子機器の表示部に利用される。

**【0046】**

表示パネル部100は、基板101の上に、画素回路Pがn行×m列のマトリクス状に

10

20

30

40

50

配列された画素アレイ部 102 と、画素回路 P を垂直方向に走査する垂直駆動部 103 と、画素回路 P を水平方向に走査する水平駆動部（水平セレクタあるいはデータ線駆動部とも称される）106 と、外部接続用の端子部（パッド部）108 などが集積形成されている。すなわち、垂直駆動部 103 や水平駆動部 106 などの周辺駆動回路が、画素アレイ部 102 と同一の基板 101 上に形成された構成となっている。

#### 【0047】

垂直駆動部 103 としては、たとえば、書込走査部（ライトスキャナ WS ; Write Scan）104 や駆動走査部（ドライブスキャナ DS ; Drive Scan）105（図では両者を一体的に示している）と、2つの閾値 & 移動度補正走査部 114, 115（図では両者を一体的に示している）とを有する。

10

#### 【0048】

画素アレイ部 102 は、一例として、図示する左右方向の一方側もしくは両側から書込走査部 104、駆動走査部 105、閾値 & 移動度補正走査部 114, 115 で駆動され、かつ図示する上下方向の一方側もしくは両側から水平駆動部 106 で駆動されるようになっている。端子部 108 には、有機 EL 表示装置 1 の外部に配された駆動信号生成部 200 から、種々のパルス信号が供給されるようになっている。また同様に、映像信号処理部 300 から映像信号 Vsig が供給されるようになっている。

#### 【0049】

一例としては、垂直駆動用のパルス信号として、垂直方向の書き込み開始パルスの一例であるシフトスタートパルス SPDS, SPWS や垂直走査クロック CKDS, CKWS など必要なパルス信号が供給される。また、閾値や移動度を補正するためのパルス信号として、垂直方向の閾値検知開始パルスの一例であるシフトスタートパルス SPAZ1, SPAZ2 や垂直走査クロック CKAZ1, CKAZ2 など必要なパルス信号が供給される。また、水平駆動用のパルス信号として、水平方向の書き込み開始パルスの一例である水平スタートパルス SPH や水平走査クロック CKH など必要なパルス信号が供給される。

20

#### 【0050】

端子部 108 の各端子は、配線 109 を介して、垂直駆動部 103 や水平駆動部 106 に接続されるようになっている。たとえば、端子部 108 に供給された各パルスは、必要に応じて図示を割愛したレベルシフタ部で電圧レベルを内部的に調整した後、バッファを介して垂直駆動部 103 の各部や水平駆動部 106 に供給される。

30

#### 【0051】

画素アレイ部 102 は、図示を割愛するが（詳細は後述する）、表示素子としての有機 EL 素子に対して画素トランジスタが設けられた画素回路 P が行列状に 2 次元配置され、この画素配列に対して行ごとに走査線が配線されるとともに、列ごとに信号線が配線された構成となっている。

#### 【0052】

たとえば、画素アレイ部 102 には、走査線（ゲート線）104 WS, 105 DS や閾値 & 移動度補正走査線 114 AZ, 115 AZ と信号線（データ線）106 HS が形成されている。両者の交差部分には図示を割愛した有機 EL 素子とこれを駆動する薄膜トランジスタ（TFT ; Thin Film Transistor）が形成される。有機 EL 素子と薄膜トランジスタの組み合いで画素回路 P を構成する。

40

#### 【0053】

具体的には、マトリクス状に配列された各画素回路 P に対しては、書込走査部 104 によって書込駆動パルス WS で駆動される n 行分の書込走査線 104 WS\_1 ~ 104 WS\_n および駆動走査部 105 によって走査駆動パルス DS で駆動される n 行分の駆動走査線 105 DS\_1 ~ 105 DS\_n、また第 1 の閾値 & 移動度補正走査部 114 によって閾値 & 移動度補正パルス AZ1 で駆動される n 行分の閾値 & 移動度補正走査線 114 AZ\_1 ~ 114 AZ\_n および第 2 の閾値 & 移動度補正走査部 115 によって閾値 & 移動度補正パルス AZ2 で駆動される n 行分の閾値 & 移動度補正走査線 115 AZ\_1 ~ 115 AZ\_n が画素行ごとに配線される。

#### 【0054】

50

書き走査部 104 および駆動走査部 105 は、駆動信号生成部 200 から供給される垂直駆動系のパルス信号に基づいて、各走査線 105DS, 104WS を介して各画素回路 P を順次選択する。水平駆動部 106 は、駆動信号生成部 200 から供給される水平駆動系のパルス信号に基づいて、選択された画素回路 P に対し信号線 106HS を介して画像信号を書き込む。

#### 【0055】

垂直駆動部 103 の各部は線順次で画素アレイ部 102 を走査するとともに、これに同期して水平駆動部 106 が、画像信号を 1 水平ライン分について水平方向に順番に（つまり画素ごとに）、もしくは 1 水平ライン分を同時に、画素アレイ部 102 に書き込む。前者は全体として点順次駆動となり、後者は全体として線順次駆動となる。

10

#### 【0056】

点順次駆動に対応する場合、水平駆動部 106 は、シフトレジスタやサンプリングスイッチ（水平スイッチ）などによって構成されており、映像信号処理部 300 から入力される画素信号を、垂直駆動部 103 の各部によって選択された行の各画素回路 P に対して、画素単位で書き込む。つまり、垂直走査による選択行の各画素回路 P に対して映像信号を画素単位で書き込む点順次駆動を行なう。

#### 【0057】

一方、線順次駆動に対応する場合、水平駆動部 106 は、全列の信号線 106HS 上に設けられた図示を割愛したスイッチを一斉にオンさせるドライバ回路を備えて構成され、映像信号処理部 300 から入力される画素信号を、垂直駆動部 103 によって選択された行の 1 ライン分の全ての画素回路 P に同時に書き込むべく、全列の信号線 106HS 上に設けられた図示を割愛したスイッチを一斉にオンさせる。

20

#### 【0058】

垂直駆動部 103 の各部は、論理ゲートの組合せ（ラッチも含む）によって構成され、画素アレイ部 102 の各画素回路 P を行単位で選択する。なお、図 1 では、画素アレイ部 102 の一方側にのみ垂直駆動部 103 を配置する構成を示しているが、画素アレイ部 102 を挟んで左右両側に垂直駆動部 103 を配置する構成を探ることも可能である。

#### 【0059】

同様に、図 1 では、画素アレイ部 102 の一方側にのみ水平駆動部 106 を配置する構成を示しているが、画素アレイ部 102 を挟んで上下両側に水平駆動部 106 を配置する構成を探ることも可能である。

30

#### 【0060】

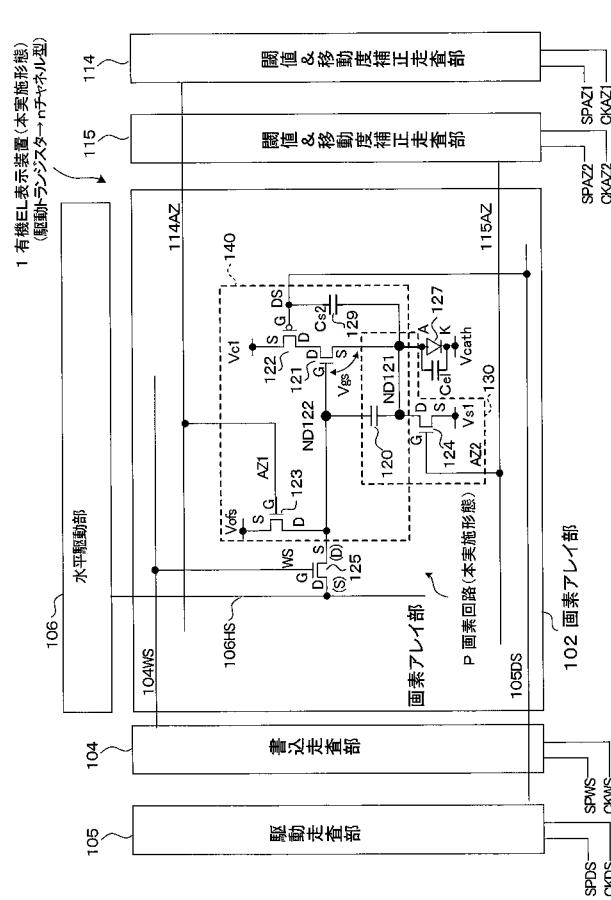

##### <画素回路；比較例>

図 2 は、図 1 に示した有機 EL 表示装置 1 を構成する本実施形態の画素回路 P に対する比較例を示す図である。なお、表示パネル部 100 の基板 101 上において画素回路 P の周辺部に設けられた垂直駆動部 103 と水平駆動部 106 も合わせて示している。

40

#### 【0061】

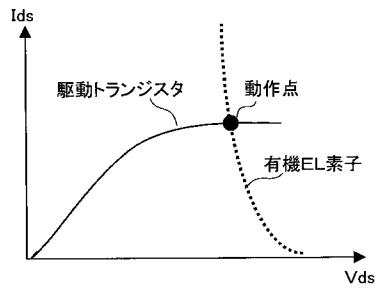

図 3 は有機 EL 素子や駆動トランジスタの動作点を説明する図である。図 3A は、有機 EL 素子や駆動トランジスタの特性ばらつきが駆動電流  $I_{ds}$  に与える影響を説明する図である。図 3B および図 3C はその改善手法の概念を説明する図である。

#### 【0062】

図 2 に示す比較例や後述する本実施形態の画素回路 P は、基本的に n チャネル型の薄膜電界効果トランジスタでドライブトランジスタが構成されている点に特徴を有する。また、有機 EL 素子の経時劣化による当該有機 EL 素子への駆動電流  $I_{ds}$  の変動を抑制するための回路、すなわち電気光学素子の一例である有機 EL 素子の電流 - 電圧特性の変化を補正して駆動電流  $I_{ds}$  を一定に維持する閾値補正機能や移動度補正機能を実現する駆動信号一定化回路（その 1）を備えた点に特徴を有する。加えて、有機 EL 素子の電流 - 電圧特性に経時変化があった場合でも駆動電流を一定にするブーストアップ機能を実現する駆動信号一定化回路（その 2）を備えた点に特徴を有する。

#### 【0063】

50

全てのスイッチトランジスタを p チャネル型のトランジスタではなく、 n チャネル型のトランジスタで構成することができれば、トランジスタ作成において従来のアモルファスシリコン ( a - S i ) プロセスを用いることが可能になる。これにより、トランジスタ基板の低コスト化が可能となり、このような構成の画素回路 P の開発が期待される。図 2 に示す比較例や後述する本実施形態の画素回路 P では、発光制御トランジスタとして p 型を用いており、不利な面はある。

#### 【 0 0 6 4 】

駆動トランジスタを始めとする各トランジスタとしては M O S トランジスタを使用する。この場合、駆動トランジスタについては、ゲート端を制御入力端として取り扱い、ソース端およびドレイン端の何れか一方（ここではソース端とする）を出力端として取り扱い、他方を電源供給端（ここではドレイン端とする）として取り扱う。10

#### 【 0 0 6 5 】

先ず、本実施形態の画素回路 P の特徴を説明するまでの比較例として、図 2 に示す比較例の画素回路 P について説明する。

#### 【 0 0 6 6 】

比較例の画素回路 P は、保持容量（画素容量とも称される） 1 2 0 、 n チャネル型の駆動トランジスタ 1 2 1 、アクティブ L の駆動パルス（走査駆動パルス DS ）が制御入力端であるゲート端 G に供給される p チャネル型の発光制御トランジスタ 1 2 2 、アクティブ H の駆動パルス（書き駆動パルス WS ）が制御入力端であるゲート端 G 供給される n チャネル型のサンプリングトランジスタ 1 2 5 、電流が流れることで発光する電気光学素子（発光素子）の一例である有機 E L 素子 1 2 7 とを有する。20

#### 【 0 0 6 7 】

サンプリングトランジスタ 1 2 5 は、駆動トランジスタ 1 2 1 のゲート端 G （制御入力端子）側に設けられたスイッチングトランジスタであり、また、発光制御トランジスタ 1 2 2 もスイッチングトランジスタである。

#### 【 0 0 6 8 】

一般に、有機 E L 素子 1 2 7 は整流性があるためダイオードの記号で表わしている。なお、有機 E L 素子 1 2 7 には、寄生容量（等価容量） C e l が存在する。図では、この寄生容量 C e l を有機 E L 素子 1 2 7 と並列に示す。

#### 【 0 0 6 9 】

ここで、比較例の画素回路 P は、駆動トランジスタ 1 2 1 のドレイン端 D 側に発光制御トランジスタ 1 2 2 を配し、かつ保持容量 1 2 0 を駆動トランジスタ 1 2 1 のゲート・ソース間に接続するととともに、ブートストラップ回路 1 3 0 と、閾値 & 移動度補正回路 1 4 0 とを備える点に特徴を有する。30

#### 【 0 0 7 0 】

有機 E L 素子 1 2 7 は電流発光素子のため、有機 E L 素子 1 2 7 に流れる電流量をコントロールすることで発色の階調を得る。このため、駆動トランジスタ 1 2 1 のゲート端 G への印加電圧を変化させることで、有機 E L 素子 1 2 7 に流れる電流値をコントロールする。

#### 【 0 0 7 1 】

この際、ブートストラップ回路 1 3 0 や閾値 & 移動度補正回路 1 4 0 を備えることで、有機 E L 素子 1 2 7 の経時変化や駆動トランジスタ 1 2 1 の特性ばらつきの影響を受けないようにしている。このため、画素回路 P を駆動する垂直駆動部 1 0 3 には、書き走査部 1 0 4 および駆動走査部 1 0 5 に加えて、 2 つの閾値 & 移動度補正走査部 1 1 4 , 1 1 5 を備える。40

#### 【 0 0 7 2 】

図では、 1 つの画素回路 P のみを示しているが、図 1 でも説明したように、同様の構成の画素回路 P がマトリクス状に配列される。そして、マトリクス状に配列された各画素回路 P に対しては、書き走査部 1 0 4 によって書き駆動パルス WS で駆動される n 行分の書き走査線 1 0 4 WS\_1 ~ 1 0 4 WS\_n および駆動走査部 1 0 5 によって走査駆動パルス DS で駆動50

される n 行分の駆動走査線 1 0 5 DS\_1 ~ 1 0 5 DS\_n の他に、第 1 の閾値 & 移動度補正走査部 1 1 4 によって閾値 & 移動度補正パルス AZ\_1 で駆動される n 行分の閾値 & 移動度補正走査線 1 1 4 AZ\_1 ~ 1 1 4 AZ\_n および第 2 の閾値 & 移動度補正走査部 1 1 5 によって閾値 & 移動度補正パルス AZ\_2 で駆動される n 行分の閾値 & 移動度補正走査線 1 1 5 AZ\_1 ~ 1 1 5 AZ\_n が画素行ごとに配線される。

#### 【 0 0 7 3 】

ブートストラップ回路 1 3 0 は、有機 E L 素子 1 2 7 と並列に接続されたアクティブ H の閾値 & 移動度補正パルス AZ\_2 が供給される n チャネル型の検知トランジスタ 1 2 4 を備え、この検知トランジスタ 1 2 4 と駆動トランジスタ 1 2 1 のゲート・ソース間に接続された保持容量 1 2 0 とで構成される。保持容量 1 2 0 は、ブートストラップ容量としても機能するようになっている。10

#### 【 0 0 7 4 】

閾値 & 移動度補正回路 1 4 0 は、駆動トランジスタ 1 2 1 のゲート端 G と第 2 電源電位 Vc2との間にアクティブ H の閾値 & 移動度補正パルス AZ\_1 が供給される n チャネル型の検知トランジスタ 1 2 3 を備え、検知トランジスタ 1 2 3 と、駆動トランジスタ 1 2 1 と、発光制御トランジスタ 1 2 2 と、駆動トランジスタ 1 2 1 のゲート・ソース間に接続された保持容量 1 2 0 で構成される。保持容量 1 2 0 は、検知した閾値電圧 Vth を保持する閾値電圧保持容量としても機能するようになっている。

#### 【 0 0 7 5 】

駆動トランジスタ 1 2 1 は、先ず、ドレイン端 D が発光制御トランジスタ 1 2 2 のドレン端 D に接続されている。発光制御トランジスタ 1 2 2 のソース端 S は第 1 電源電位 Vc1 に接続されている。また、駆動トランジスタ 1 2 1 は、ソース端 S が直接に有機 E L 素子 1 2 7 のアノード端 A に接続される。その接続点をノード ND 1 2 1 とする。有機 E L 素子 1 2 7 のカソード端 K は基準電位を供給する全画素共通の接地配線 Vcath ( GND ) に接続されてカソード電位 Vcath が供給されるようになっている。20

#### 【 0 0 7 6 】

サンプリングトランジスタ 1 2 5 は、ゲート端 G が書込走査部 1 0 4 からの書込走査線 1 0 4 WS に接続され、ドレイン端 D が映像信号線 1 0 6 HS に接続され、ソース端 S が駆動トランジスタ 1 2 1 のゲート端 G に接続されている。その接続点をノード ND 1 2 2 とする。サンプリングトランジスタ 1 2 5 のゲート端 G には、書込走査部 1 0 4 からアクティブ H の書込駆動パルス WS が供給される。サンプリングトランジスタ 1 2 5 は、ソース端 S とドレイン端 D とを逆転させた接続態様とすることもできる。保持容量 1 2 0 は、一方の端子が駆動トランジスタ 1 2 1 のソース端 S に接続され、他方の端子が同じく駆動トランジスタ 1 2 1 のゲート端 G に接続されている。30

#### 【 0 0 7 7 】

検知トランジスタ 1 2 3 は、駆動トランジスタ 1 2 1 のゲート端 G ( 制御入力端子 ) 側に設けられたスイッチングトランジスタであり、ソース端 S がオフセット電圧の一例である接地電位 Vofs に接続され、ドレイン端 D が駆動トランジスタ 1 2 1 のゲート端 G ( ノード ND 1 2 2 ) に接続され、制御入力端であるゲート端 G は閾値 & 移動度補正走査線 1 1 4 AZ に接続されている。検知トランジスタ 1 2 3 がオンすることで、駆動トランジスタ 1 2 1 のゲート端 G の電位を検知トランジスタ 1 2 3 を介して固定電位である接地電位 Vofs に接続するように構成している。40

#### 【 0 0 7 8 】

検知トランジスタ 1 2 4 は、スイッチングトランジスタであり、ドレイン端 D が駆動トランジスタ 1 2 1 のソース端 S と有機 E L 素子 1 2 7 のアノード端 A との接続点であるノード ND 1 2 1 に接続され、ソース端 S は、基準電位の一例である接地電位 Vs1 に接続され、制御入力端であるゲート端 G は閾値 & 移動度補正走査線 1 1 5 AZ に接続されている。

#### 【 0 0 7 9 】

駆動トランジスタ 1 2 1 のゲート・ソース間に保持容量 1 2 0 を接続し、検知トランジスタ 1 2 4 がオンすることで、駆動トランジスタ 1 2 1 のソース端 S の電位を検知トラン50

ジスタ 124 を介して固定電位である接地電位 Vs1 に接続するように構成している。

【0080】

サンプリングトランジスタ 125 は、書込走査線 104WS によって選択されたとき動作し、信号線 106HS から画素信号 Vsig ( の信号電位 Vin ) をサンプリングしてノード ND112 を介し保持容量 120 に信号電位 Vin に対応する大きさの電圧を保持する。保持容量 120 に保持される電位は理想的には信号電位 Vin と同じ大きさであるが実際にはそれよりも小さくなる。

【0081】

駆動トランジスタ 121 は、発光制御トランジスタ 122 が走査駆動パルス DS の元でオンしているときに保持容量 120 に保持された駆動電位 ( その時点の駆動トランジスタ 121 のゲート・ソース間電圧 Vgs ) に応じて有機 EL 素子 127 を電流駆動する。発光制御トランジスタ 122 は駆動走査線 105DS によって選択されたときに導通して第 1 電源電位 Vc1 から駆動トランジスタ 121 に電流を供給する。

10

【0082】

このように、駆動トランジスタ 121 の電源供給端であるドレイン端 D 側を発光制御トランジスタ 122 を介して第 1 電源電位 Vc1 に接続し、発光制御トランジスタ 122 のオン期間を制御することで有機 EL 素子 127 の発光期間と非発光期間を調整し、デューティ ( Duty ) 駆動を行なうことを可能にしている。

【0083】

検知トランジスタ 123, 124 は閾値 & 移動度補正走査部 114, 115 からアクティブ H の閾値 & 移動度補正パルス AZ1, AZ2 を閾値 & 移動度補正走査線 114AZ, 115AZ に供給してそれを選択状態としたとき動作し、予め決められた補正動作 ( ここでは閾値電圧 Vth や移動度 μ のばらつきを補正する動作 ) を行なう。

20

【0084】

たとえば、有機 EL 素子 127 の電流駆動に先立って駆動トランジスタ 121 の閾値電圧 Vth を検知し、予めその影響をキャンセルするため、検知した電位を保持容量 120 に保持する。

【0085】

このような構成の画素回路 P の正常な動作を保証するための条件として、接地電位 Vs1 は、接地電位 Vofs から駆動トランジスタ 121 の閾値電圧 Vth を差し引いたレベルよりも低く設定されている。すなわち、 “ Vs1 < Vofs - Vth ” である。

30

【0086】

また、有機 EL 素子 127 のカソード端 K の電位 Vcath に有機 EL 素子 127 の閾値電圧 VthEL を加えたレベルは、接地電位 Vs1 から駆動トランジスタ 121 の閾値電圧 Vth を差し引いたレベルよりも高く設定されている。すなわち、 “ Vcath + VthEL > Vs1 - Vth ” となっている。好ましくは、接地電位 Vofs のレベルは、信号線 106HS から供給される画素信号 Vsig の最低レベルの近傍に ( 最低レベル以下の範囲で ) 設定されている。

【0087】

このような構成を持つ比較例の画素回路 P において、サンプリングトランジスタ 125 は、所定の信号書込期間 ( サンプリング期間 ) に書込走査線 104WS から供給される書込駆動パルス WS に応じ導通して信号線 106HS から供給された映像信号 Vsig を保持容量 120 にサンプリングする。保持容量 120 は、サンプリングされた映像信号 Vsig に応じて駆動トランジスタ 121 のゲート・ソース間に入力電圧 ( ゲート・ソース間電圧 Vgs ) を印加する。

40

【0088】

駆動トランジスタ 121 は、所定の発光期間中に、ゲート・ソース間電圧 Vgs に応じた出力電流を駆動電流 Ids として有機 EL 素子 127 に供給する。なお、この駆動電流 Ids は駆動トランジスタ 121 のチャネル領域のキャリア移動度 μ および閾値電圧 Vth に対して依存性を有する。有機 EL 素子 127 は、駆動トランジスタ 121 から供給された駆動電流 Ids により映像信号 Vsig ( 特に信号電位 Vin ) に応じた輝度で発光する。

50

## 【0089】

ここで、比較例の画素回路Pにおいては、スイッチングトランジスタ（発光制御トランジスタ122および検知トランジスタ123，124）で構成される補正手段を備えており、駆動電流 $I_{ds}$ のキャリア移動度 $\mu$ に対する依存性を打ち消すために、予め発光期間の先頭で保持容量120に保持されたゲート・ソース間電圧 $V_{gs}$ を補正する。

## 【0090】

具体的には、この補正手段（スイッチングトランジスタ122，123，124）は、書込走査線104WSおよび駆動走査線105DSから供給される書込駆動パルスWSおよび走査駆動パルスDSに応じて信号書込期間の一部（たとえば後半側）で動作し、映像信号 $V_{sig}$ がサンプリングされている状態で駆動トランジスタ121から駆動電流 $I_{ds}$ を取り出し、これを保持容量120に負帰還してゲート・ソース間電圧 $V_{gs}$ を補正する。さらにこの補正手段（スイッチングトランジスタ122，123，124）は、駆動電流 $I_{ds}$ の閾値電圧 $V_{th}$ に対する依存性を打ち消すために、予め信号書込期間に先立って駆動トランジスタ121の閾値電圧 $V_{th}$ を検出し、かつ検出された閾値電圧 $V_{th}$ をゲート・ソース間電圧 $V_{gs}$ に足し込む。10

## 【0091】

特に、比較例の画素回路Pでは、駆動トランジスタ121はnチャネル型トランジスタでドレインを正電源側に接続する一方、ソースが有機EL素子127側に接続している。この場合、前述した補正手段は、信号書込期間の後部分に重なる発光期間の先頭部分で駆動トランジスタ121から駆動電流 $I_{ds}$ を取り出して、保持容量120側に負帰還する。20

## 【0092】

その際、補正手段は、発光期間の先頭部分で駆動トランジスタ121のソース端S側から取り出した駆動電流 $I_{ds}$ が、有機EL素子127の有する寄生容量 $C_{el}$ に流れ込むよう正在している。具体的には、有機EL素子127はアノード端Aおよびカソード端Kを備えたダイオード型の発光素子であり、アノード端A側が駆動トランジスタ121のソース端Sに接続される一方、カソード端K側が接地側（本例ではカソード電位 $V_{cath}$ ）に接続される。

## 【0093】

この構成で、補正手段（スイッチングトランジスタ122，123，124）は、予め有機EL素子127のアノード・カソード間を逆バイアス状態にセットしておき、駆動トランジスタ121のソース端S側から取り出した駆動電流 $I_{ds}$ が有機EL素子127に流れ込むとき、ダイオード型の有機EL素子127を容量性素子として機能させている。30

## 【0094】

なお補正手段は、信号書込期間内で駆動トランジスタ121から駆動電流 $I_{ds}$ を取り出す時間幅 $t$ を調整可能であり、これにより保持容量120に対する駆動電流 $I_{ds}$ の負帰還量を最適化する。

## 【0095】

ここで、「負帰還量を最適化する」とは、映像信号電位の黒レベルから白レベルまでの範囲で、どのレベルにおいても適切に移動度補正を行なうことができるようすることを意味する。ゲート・ソース間電圧 $V_{gs}$ にかける負帰還量は、駆動電流 $I_{ds}$ の取り出し時間に依存しており、取り出し時間を長く取るほど、負帰還量が大きくなる。40

## 【0096】

たとえば、映像線信号電位である信号線106HSの電圧の立ち上がりもしくは書込走査線104WSの書込駆動パルスWSの遷移特性に傾斜をつけることで、移動度補正期間 $t$ を映像線信号電位に自動的に追従させて、その最適化を図る。すなわち、移動度補正期間 $t$ は書込走査線104WSと信号線106HSの位相差で決定でき、さらに信号線106HSの電位によっても決定できる。移動度補正パラメータ $V$ は $V = I_{ds} \cdot C_{el} / t$ である。

## 【0097】

この式から明らかなように、駆動トランジスタ121のドレイン・ソース間電流である駆動電流 $I_{ds}$ が大きいほど、移動度補正パラメータ $V$ は大きくなる。逆に、駆動トラン

ジスタ 121 の駆動電流  $I_{ds}$  が小さいとき、移動度補正パラメータ  $V$  は小さくなる。このように、移動度補正パラメータ  $V$  は駆動電流  $I_{ds}$  に応じて決まる。

#### 【0098】

その際、移動度補正期間  $t$  は必ずしも一定である必要はなく、逆に駆動電流  $I_{ds}$  に応じて調整することが好ましい場合がある。たとえば、駆動電流  $I_{ds}$  が大きい場合、移動度補正期間  $t$  は短めにし、逆に駆動電流  $I_{ds}$  が小さくなると、移動度補正期間  $t$  は長めに設定することがよい。

#### 【0099】

そこで、映像信号線電位（信号線 106HS の電位）の立上りもしくは書込走査線 104WS の書込駆動パルス WS の遷移特性に傾斜をつけることで、信号線 106HS の電位が高いとき（駆動電流  $I_{ds}$  が大きいとき）補正期間  $t$  が短くなり、信号線 106HS の電位が低いとき（駆動電流  $I_{ds}$  が小さいとき）補正期間  $t$  は長くなるように、自動的に調整する。こうすることで、映像信号電位（映像信号  $V_{sig}$  の信号電位  $V_{in}$ ）に追従して、適切な補正期間を自動的に設定できるため、画像の輝度や絵柄によらず最適な移動度補正が可能となる。

10

#### 【0100】

##### < 基本動作 >

先ず、図 2 や後述する本実施形態の画素回路 P の特徴を説明するまでの比較例として、発光制御トランジスタ 122，検知トランジスタ 123，検知トランジスタ 124 を備えておらず、また、保持容量 120 は、一方の端子がノード ND122 に接続され、他方の端子が全画素共通の接地配線  $V_{cath}$  (GND) に接続されている場合での動作について説明する。以下、このような画素回路 P を第 1 比較例の画素回路 P と称し、それとの区別のため、図 2 に示す画素回路 P を第 2 比較例の画素回路 P と称する。第 2 比較例の画素回路 P を画素アレイ部 102 に備える有機 E L 表示装置 1 を第 2 比較例の有機 E L 表示装置 1 と称する。

20

#### 【0101】

第 1 比較例の画素回路 P では、駆動トランジスタ 121 のソース端 S の電位（ソース電位  $V_s$ ）は、駆動トランジスタ 121 と有機 E L 素子 127 との動作点で決まり、その電圧値は駆動トランジスタ 121 のゲート電位  $V_g$  によって異なる値を持つてしまう。

30

#### 【0102】

一般的に、図 3 に示すように、駆動トランジスタ 121 は飽和領域で駆動される。よって、飽和領域で動作するトランジスタのドレイン端 - ソース間に流れる電流を  $I_{ds}$ 、移動度を  $\mu$ 、チャネル幅（ゲート幅）を W、チャネル長（ゲート長）を L、ゲート容量（単位面積当たりのゲート酸化膜容量）を  $C_{ox}$  は、トランジスタの閾値電圧を  $V_{th}$  とすると、駆動トランジスタ 121 は下記の式（1）に示した値を持つ定電流源となっている。なお、“ $\wedge$ ” はべき乗を示す。式（1）から明らかなように、飽和領域ではトランジスタのドレイン電流  $I_{ds}$  はゲート・ソース間電圧  $V_{gs}$  によって制御され定電流源として動作する。

40

#### 【0103】

##### 【数 1】

$$I_{ds} = \frac{1}{2} \mu \frac{W}{L} C_{ox} (V_{gs} - V_{th})^2 \dots (1)$$

#### 【0104】

##### < 発光素子の $I_{el}$ - $V_{el}$ 特性と I - V 特性 >

図 3A (1) に示す有機 E L 素子で代表される電流駆動型の発光素子の電流 - 電圧 ( $I_{el}$  -  $V_{el}$ ) 特性において、実線で示す曲線が初期状態時の特性を示し、破線で示す曲線が経時変化後の特性を示している。一般的に有機 E L 素子を始めとする電流駆動型の発光素子の I - V 特性は、グラフに示すように時間が経過すると劣化する。

50

## 【0105】

たとえば、発光素子の一例である有機EL素子127に発光電流 $I_{el}$ が流れると、そのアノード・カソード間電圧 $V_{el}$ は一意的に決定される。図3A(1)に示すように、発光期間中では、有機EL素子127のアノード端Aは駆動トランジスタ121のドレイン・ソース間電流 $I_{ds}$ (=駆動電流 $I_{ds}$ )で決定される発光電流 $I_{el}$ が流れ、それによってアノード・カソード間電圧 $V_{el}$ だけ上昇する。

## 【0106】

第1比較例の画素回路Pでは、この有機EL素子127のI-V特性の経時変化により同じ発光電流 $I_{el}$ に対するアノード・カソード間電圧 $V_{el}$ が $V_{el1}$ から $V_{el2}$ へと変化することで、駆動トランジスタ121の動作点が変化してしまい、同じゲート電位 $V_g$ を印加しても駆動トランジスタ121のソース電位 $V_s$ は変化してしまい、その結果として、駆動トランジスタ121のゲート・ソース間電圧 $V_{gs}$ は変化してしまう。

10

## 【0107】

駆動トランジスタ121としてnチャネル型を使用した単純な回路では、ソース端Sが有機EL素子127側に接続されてしまうため、有機EL素子127のI-V特性の経時変化の影響を受けてしまい、有機EL素子127に流れる電流量(発光電流 $I_{el}$ )が変化し、その結果、発光輝度は変化してしまうことになる。

## 【0108】

具体的には、第1比較例の画素回路Pでは、有機EL素子127のI-V特性の経時変化により動作点が変化してしまい、同じゲート電位 $V_g$ を印加しても駆動トランジスタ121のソース電位 $V_s$ は変化してしまう。これにより、駆動トランジスタ121のゲート・ソース間電圧 $V_{gs}$ は変化してしまう。特性式(1)から明らかのように、ゲート・ソース間電圧 $V_{gs}$ が変動すると、たとえゲート電位 $V_g$ が一定であっても駆動電流 $I_{ds}$ が変動し、同時に有機EL素子127に流れる電流値も変化する。このように有機EL素子127のI-V特性が変化すると、第1比較例の画素回路Pでは、有機EL素子127の発光輝度が経時的に変化してしまう。

20

## 【0109】

駆動トランジスタ121としてnチャネル型を使用した単純な回路では、ソース端Sが有機EL素子127側に接続されてしまうため、有機EL素子127の経時変化とともに、ゲート・ソース間電圧 $V_{gs}$ が変化してしまい、有機EL素子127に流れる電流量が変化し、その結果、発光輝度は変化してしまうのである。

30

## 【0110】

発光素子の一例である有機EL素子127の特性の経時変動による有機EL素子127のアノード電位変動は、駆動トランジスタ121のゲート・ソース間電圧 $V_{gs}$ の変動となって現れ、ドレイン電流(駆動電流 $I_{ds}$ )の変動を引き起す。この原因による駆動電流の変動は画素回路Pごとの発光輝度のばらつきとなって現れ、画質の劣化が起きる。

## 【0111】

これに対して、詳細は後述するが、保持容量120に信号電位 $V_{in}$ に対応する情報が書き込まれた時点で(さらにその後の有機EL素子127の発光期間は継続的に)サンプリングトランジスタ125を非導通状態にすることで駆動トランジスタ121のソース端Sの電位 $V_s$ の変動にゲート端Gの電位 $V_g$ が連動するようとするブートストラップ機能を実現する回路構成および駆動タイミングとするブートストラップ動作をさせる。

40

## 【0112】

これにより、有機EL素子127の特性の経時変動による有機EL素子127のアノード電位変動(つまりソース電位変動)があっても、その変動を相殺するようにゲート電位 $V_g$ を変動させることで、画面輝度の均一性(ユニフォーミティ)を確保できる。ブートストラップ機能により、有機EL素子を代表とする電流駆動型の発光素子の経時変動補正能力を向上させることができる。

## 【0113】

このブートストラップ機能は、書き込み駆動パルスWSをインアクティブLに切り替えてサン

50

プリングトランジスタ 125 をオフさせた発光開始時点で開始させることができ、その後、有機 E L 素子 127 に発光電流  $I_{el}$  が流れ始め、それとともにアノード・カソード間電圧  $V_{el}$  が安定となるまで上昇していく過程で、アノード・カソード間電圧  $V_{el}$  の変動に伴って駆動トランジスタ 121 のソース電位  $V_s$  が変動する際にも機能する。

## 【0114】

<駆動トランジスタの  $V_{gs}$  -  $I_{ds}$  特性>

また、駆動トランジスタ 121 の製造プロセスのばらつきにより、画素回路 P ごとに閾値電圧や移動度などの特性変動がある。駆動トランジスタ 121 を飽和領域で駆動する場合においても、この特性変動により、駆動トランジスタ 121 に同一のゲート電位を与えて、画素回路 P ごとにドレイン電流（駆動電流  $I_{ds}$ ）が変動し、発光輝度のばらつきになつて現れる。10

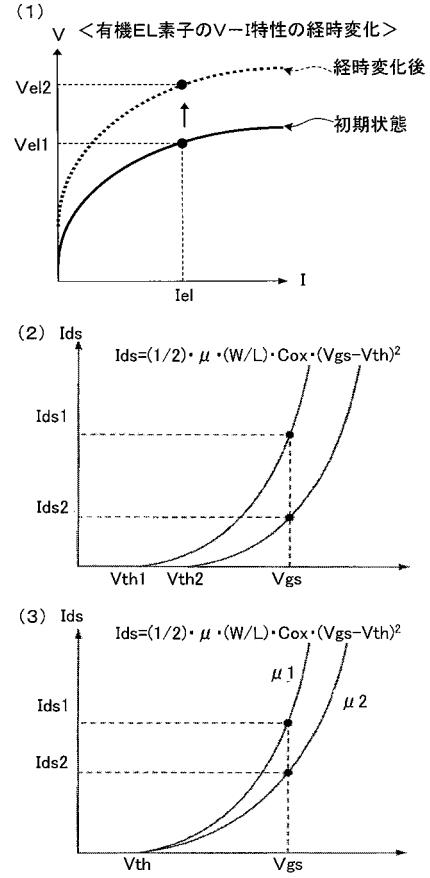

## 【0115】

たとえば、図 3A(2) は、駆動トランジスタ 121 の閾値ばらつきに着目した電圧電流 ( $V_{gs}$  -  $I_{ds}$ ) 特性を示す図である。閾値電圧が  $V_{th1}$  と  $V_{th2}$  で異なる 2 個の駆動トランジスタ 121 について、それぞれ特性カーブを挙げてある。

## 【0116】

前述のように、駆動トランジスタ 121 が飽和領域で動作しているときのドレイン電流  $I_{ds}$  は、特性式 (1) で表される。特性式 (1) から明らかなように、閾値電圧  $V_{th}$  が変動すると、ゲート・ソース間電圧  $V_{gs}$  が一定であってもドレイン電流  $I_{ds}$  が変動する。つまり、閾値電圧  $V_{th}$  のばらつきに対して何ら対策を施さないと、図 3A(2) に示すように、閾値電圧が  $V_{th1}$  のとき  $V_{gs}$  に対応する駆動電流が  $I_{ds1}$  となるのに対して、閾値電圧が  $V_{th2}$  のときの同じゲート電圧  $V_{gs}$  に対応する駆動電流  $I_{ds2}$  は  $I_{ds1}$  と異なってしまう。20

## 【0117】

また、図 3A(3) は、駆動トランジスタ 121 の移動度ばらつきに着目した電圧電流 ( $V_{gs}$  -  $I_{ds}$ ) 特性を示す図である。移動度が  $\mu_1$  と  $\mu_2$  で異なる 2 個の駆動トランジスタ 121 について、それぞれ特性カーブを挙げてある。

## 【0118】

特性式 (1) から明らかなように、移動度  $\mu$  が変動すると、ゲート・ソース間電圧  $V_{gs}$  が一定であってもドレイン電流  $I_{ds}$  が変動する。つまり、移動度  $\mu$  のばらつきに対して何ら対策を施さないと、図 3A(3) に示すように、移動度が  $\mu_1$  のとき  $V_{gs}$  に対応する駆動電流が  $I_{ds1}$  となるのに対して、移動度が  $\mu_2$  のときの同じゲート電圧  $V_{gs}$  に対応する駆動電流が  $I_{ds2}$  となり、 $I_{ds1}$  と異なってしまう。30

## 【0119】

図 3A(2) や図 3A(3) に示すように、閾値電圧  $V_{th}$  や移動度  $\mu$  の違いで  $V_{in}$  -  $I_{ds}$  特性に大きな違いが出てしまうと、同じ信号電位  $V_{in}$  を与えても、駆動電流  $I_{ds}$  すなわち発光輝度が異なってしまい、画面輝度の均一性（ユニフォーミティ）が得られない。

## 【0120】

<閾値補正および移動度補正の概念>

これに対して、閾値補正機能および移動度補正機能を実現する駆動タイミング（詳細は後述する）とすることで、それらの変動の影響を抑制でき、画面輝度の均一性（ユニフォーミティ）を確保できる。40

## 【0121】

第 2 比較例や本実施形態の閾値補正動作および移動度補正動作では、詳細は後述するが、発光時のゲート・ソース間電圧  $V_{gs}$  が “ $V_{in} + V_{th} - V$ ” で表されるようにすることで、ドレイン・ソース間電流  $I_{ds}$  が、閾値電圧  $V_{th}$  のばらつきや変動に依存しないようにするとともに、移動度  $\mu$  のばらつきや変動に依存しないようにする。結果として、閾値電圧  $V_{th}$  や移動度  $\mu$  が製造プロセスや経時により変動しても、駆動電流  $I_{ds}$  は変動せず、有機 E L 素子 127 の発光輝度も変動しない。

## 【0122】

10

20

30

40

50

たとえば、図3Bは、移動度補正時における駆動トランジスタ121の動作点を説明するグラフである。製造プロセスや経時における移動度 $\mu_1$ ,  $\mu_2$ のばらつきに対して、発光時のゲート・ソース間電圧 $V_{gs}$ が“ $V_{in} + V_{th} - V$ ”で表されるようにする閾値補正および移動度補正をかけると、先ず移動度の観点からは、移動度 $\mu_1$ に対しては移動度補正パラメータ $V_1$ が決定され、また移動度 $\mu_2$ に対しては移動度補正パラメータ $V_2$ が決定される。

#### 【0123】

これにより、何れの移動度に対しても適正な移動度補正パラメータが決定されるので、駆動トランジスタ121の移動度 $\mu_1$ 時の駆動電流 $I_{ds\alpha}$ および移動度 $\mu_2$ 時の駆動電流 $I_{ds\beta}$ が決定される。移動度補正前には大きな電流ばらつきのあったものが、移動度補正によって電流ばらつきは小さくなり、移動度 $\mu$ の違いは抑制される。最適な状態では“ $I_{ds\alpha} = I_{ds\beta}$ ”とすることができる、移動度 $\mu$ の違いを除去（キャンセル）できる。

10

#### 【0124】

仮に移動度補正をかけないと、図3(3)にも示したが、ゲート・ソース間電圧 $V_{gs}$ に対して、移動度が $\mu_1$ ,  $\mu_2$ で異なると、これに応じて駆動電流 $I_{ds}$ も $I_{ds1}$ ,  $I_{ds2}$ で大きく違ってしまう。これに対処するため移動度 $\mu_1$ ,  $\mu_2$ に対してそれぞれ適切な移動度補正パラメータ $V_1$ ,  $V_2$ をかけることで、駆動電流 $I_{ds}$ が $I_{ds\alpha}$ ,  $I_{ds\beta}$ となり、各移動度補正パラメータ $V_1$ ,  $V_2$ を最適値としてすることで、移動度補正後の駆動電流 $I_{ds\alpha}$ ,  $I_{ds\beta}$ を近づけることができ、最適状態では同レベルとすることができます。

20

#### 【0125】

移動度補正時には、図3Bのグラフから明らかなように、大きな移動度 $\mu_1$ に対しては移動度補正パラメータ $V_1$ が大きくなるようにする一方、小さい移動度 $\mu_2$ に対しては移動度補正パラメータ $V_2$ も小さくなるように負帰還をかけることになる。こう言った意味で、移動度補正パラメータ $V$ を負帰還量 $V$ とも称する。

#### 【0126】

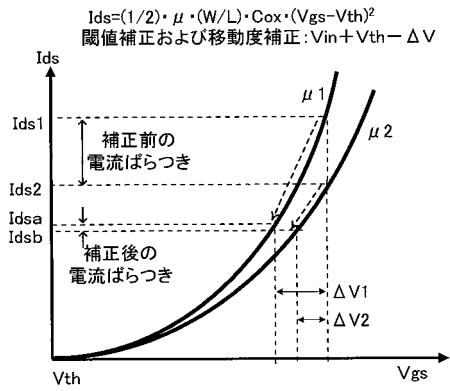

また、図3Cの各図は、閾値補正の観点から、信号電位 $V_{in}$ と駆動電流 $I_{ds}$ との関係を示している。たとえば、図3Cの各図においては、駆動トランジスタ121の電流電圧特性を、横軸に信号電位 $V_{in}$ をとり、縦軸に駆動電流 $I_{ds}$ をとって、閾値電圧 $V_{th}$ が比較的低く移動度 $\mu$ が比較的大きい駆動トランジスタ121で構成された画素回路P<sub>a</sub>（実線のカーブ）と、逆に閾値電圧 $V_{th}$ が比較的高く移動度 $\mu$ が比較的小さい駆動トランジスタ121で構成された画素回路P<sub>b</sub>（点線のカーブ）について、それぞれ特性カーブを挙げてある。

30

#### 【0127】

図3C(1)は、閾値補正および移動度補正ともに実行しない場合である。このときには画素回路P<sub>a</sub>および画素回路P<sub>b</sub>で閾値電圧 $V_{th}$ および移動度 $\mu$ の補正が全く実行されないため、閾値電圧 $V_{th}$ や移動度 $\mu$ の違いで $V_{in} - I_{ds}$ 特性に大きな違いが出てしまう。したがって、同じ信号電位 $V_{in}$ を与えても、駆動電流 $I_{ds}$ すなわち発光輝度が異なってしまい、画面輝度の均一性（ユニフォーミティ）が得られない。

#### 【0128】

図3C(2)は、閾値補正を実行する一方、移動度補正を実行しない場合である。このとき画素回路P<sub>a</sub>と画素回路P<sub>b</sub>で閾値電圧 $V_{th}$ の違いはキャンセルされる。しかしながら移動度 $\mu$ の相違はそのまま現れている。したがって信号電位 $V_{in}$ が高い領域（すなわち輝度が高い領域）で、移動度 $\mu$ の違いが顕著に現れ、同じ階調でも輝度が違ってしまう。具体的には、同じ階調（同じ信号電位 $V_{in}$ ）で、移動度 $\mu$ の大きい画素回路P<sub>a</sub>の輝度（駆動電流 $I_{ds}$ ）は高く、移動度 $\mu$ の小さい画素回路P<sub>b</sub>の輝度は低くなる。

40

#### 【0129】

図3C(3)は閾値補正および移動度補正ともに実行する場合である。閾値電圧 $V_{th}$ および移動度 $\mu$ の相違は完全に補正され、その結果、画素回路P<sub>a</sub>と画素回路P<sub>b</sub>の $V_{in} - I_{ds}$ 特性は一致する。したがって、全ての階調（信号電位 $V_{in}$ ）で輝度（ $I_{ds}$ ）が同一レベルとなり、画面輝度の均一性（ユニフォーミティ）が顕著に改善される。

50

## 【0130】

図3C(4)は、閾値補正および移動度補正ともに実行するものの、閾値電圧V<sub>th</sub>の補正が不十分な場合である。たとえば、1回の閾値補正動作では駆動トランジスタ121の閾値電圧V<sub>th</sub>に相当する電圧を十分に保持容量120へ保持させることができない場合がその一例である。このときには、閾値電圧V<sub>th</sub>の差が除去されないため、画素回路P<sub>a</sub>と画素回路P<sub>b</sub>では低階調の領域で輝度(駆動電流I<sub>ds</sub>)に差が出てしまう。よって、閾値電圧V<sub>th</sub>の補正が不十分な場合は低階調で輝度のムラが現れ画質を損なうことになる。

## 【0131】

<画素回路の動作；比較例>

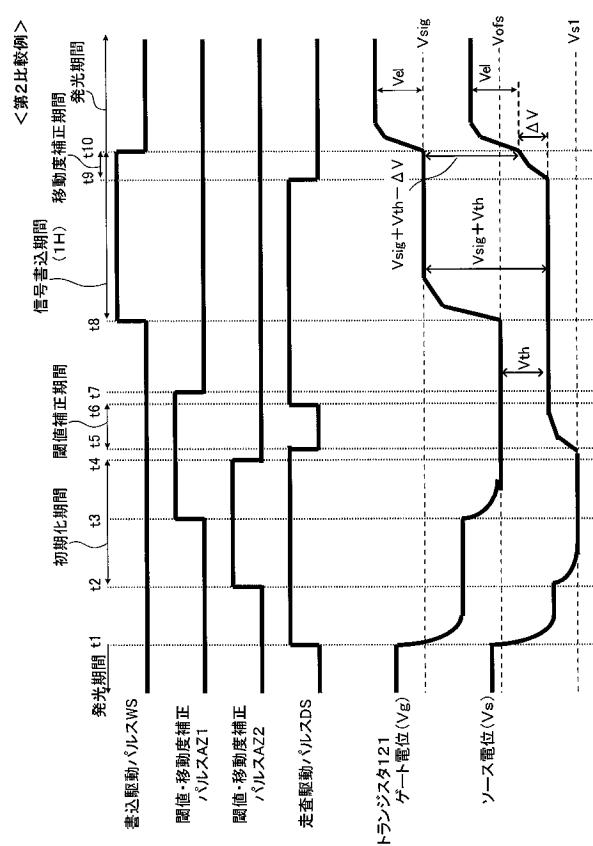

図4は、第2比較例の画素回路Pの動作を説明するタイミングチャートである。後述する本実施形態の駆動タイミングも、各駆動パルス自体は、基本的には、ここで示すタイミングチャートに示すものと同じであり、事実上、本実施形態の画素回路Pに関する駆動タイミングを示すタイミングチャートを包含している。

10

## 【0132】

図4では、時間軸tに沿って、書込駆動パルスWS、閾値&移動度補正パルスAZ1,AZ2、および走査駆動パルスDSの波形を表してある。前述の説明から理解されるように、スイッチングトランジスタ123,124,125はnチャネル型なので、各パルスWS,AZ1,AZ2がそれぞれハイ(H)レベルのときにオンし、ロー(L)レベルのときにはオフする。一方、発光制御トランジスタ122はpチャネル型なので、走査駆動パルスDSがハイレベルのときにオフし、ローレベルのときにオンする。なお、このタイミングチャートは、各パルスWS,AZ1,AZ2,DSの波形とともに、駆動トランジスタ121のゲート端Gの電位変化およびソース端Sの電位変化も表してある。

20

## 【0133】

比較例の画素回路Pにおいて、通常の発光状態では、駆動走査部105から出力される走査駆動パルスDSのみがアクティブLで、その他の書込走査部104および閾値&移動度補正走査部114,115からそれぞれ出力される書込駆動パルスWSおよび閾値&移動度補正パルスAZ1,AZ2がインアクティブLにあるため、発光制御トランジスタ122のみがオンした状態である。

## 【0134】

1フィールドの間に画素アレイ部102の各行が一回順次走査される。当該フィールドが始まる前の期間(t1以前)で、全てのパルスWS,AZ1,AZ2,DSがローレベルにある。したがって、nチャネル型のスイッチングトランジスタ123,124,125はオフ状態にある一方、pチャネル型の発光制御トランジスタ122のみがオン状態である。

30

## 【0135】

したがって、駆動トランジスタ121はオン状態の発光制御トランジスタ122を介して第1電源電位V<sub>c1</sub>に接続しているので、所定のゲート・ソース間電圧V<sub>gs</sub>に応じて駆動電流I<sub>ds</sub>を有機EL素子127に供給している。したがって、タイミングt1以前で有機EL素子127は発光している。このとき、駆動トランジスタ121に印加されるゲート・ソース間電圧V<sub>gs</sub>は、ゲート電位V<sub>g</sub>とソース電位V<sub>s</sub>の差で表される。

## 【0136】

このとき、駆動トランジスタ121は飽和領域で動作するように設定されているため、飽和領域で動作するトランジスタのドレイン端-ソース間に流れる電流をI<sub>ds</sub>、移動度をμ、チャネル幅をW、チャネル長をL、ゲート容量をC<sub>ox</sub>、トランジスタの閾値電圧をV<sub>th</sub>とすると、原理的には、駆動トランジスタ121は式(1)に示した値を持つ定電流源となる。

40

## 【0137】

新しいフィールドが始まるタイミングt1で、走査駆動パルスDSがローレベルからハイレベルに切り替わる(t1)。したがって、タイミングt1に入ると、全てのスイッチングトランジスタ122～125がオフ状態になる。これにより発光制御トランジスタ122がオフし、駆動トランジスタ121は第1電源電位V<sub>c1</sub>から切り離されるので、ゲート

50

電圧  $V_g$  やソース電圧  $V_s$  が低下して、有機EL素子127の発光が停止し非発光期間に入る。

#### 【0138】

次に、閾値 & 移動度補正パルスAZ1, AZ2を順にアクティブHにすることで、検知トランジスタ123, 124をオンする。なお検知トランジスタ123, 124はどちらが先にオンしてもよい。こうすることで、有機EL素子127には電流が流れないようにし、有機EL素子127を非発光状態とする。図示した例では、先ず閾値 & 移動度補正パルスAZ2をアクティブHにして検知トランジスタ124をオンさせてから( $t_2$ )、閾値 & 移動度補正パルスAZ1をアクティブHにして検知トランジスタ123をオンさせている( $t_3$ )。

10

#### 【0139】

このとき、駆動トランジスタ121は、ソース端Sには検知トランジスタ124を介して接地電位  $V_{s1}$  が供給されることで駆動トランジスタ121のソース電位  $V_s$  が初期化され( $t_2 \sim t_3$ )、さらにゲート端Gには検知トランジスタ123を介して接地電位  $V_{ofs}$  が供給されることで駆動トランジスタ121のゲート電位  $V_g$  が初期化される( $t_3 \sim t_4$ )。

#### 【0140】

これにより、駆動トランジスタ121のゲート・ソース間に接続された保持容量120の両端の電位差が駆動トランジスタ121の閾値電圧  $V_{th}$  以上に設定される。このとき、駆動トランジスタ121のゲート・ソース間電圧  $V_{gs}$  は “ $V_{ofs} - V_{s1}$ ” という値をとるが、“ $V_{s1} < V_{ofs} - V_{th}$ ” に設定されているので、駆動トランジスタ121はオン状態を維持し、それに応じた電流  $I_{ds1}$  が流れる。

20

#### 【0141】

ここで、有機EL素子127を非発光とするためには、 $V_{cath} + V_{thEL} > V_{s1} - V_{th}$  の関係にあること、つまり、有機EL素子127のアノード端Aにかかる電圧  $V_{el}$  ( $= V_{s1} - V_{th}$ ) を有機EL素子127の閾値電圧  $V_{thEL}$  とカソード電圧  $V_{cath}$  の和よりも小さくなるように接地電位  $V_{ofs}$  と接地電位  $V_{s1}$  の電圧を設定する必要がある。こうすれば、有機EL素子127は逆バイアス状態となり、電流は流れず、非発光状態になる。

#### 【0142】

よって、駆動トランジスタ121のドレイン電流  $I_{ds1}$  は第1電源電位  $V_{c1}$  からオン状態にある検知トランジスタ124を介して接地電位  $V_{s1}$  に流れる。また、 $V_{ofs} - V_{s1} = V_{gs} > V_{th}$  とすることで、その後のタイミング  $t_5$  で行なわれる閾値電圧  $V_{th}$  のばらつき補正の準備を行なう。換言すると、期間  $t_2 \sim t_5$  は、駆動トランジスタ121のリセット期間(初期化期間)や移動度補正の準備期間に相当する。

30

#### 【0143】

また、有機EL素子127の閾値電圧  $V_{thEL}$  に関しては、 $V_{thEL} > V_{s1}$  に設定されている。これにより、有機EL素子127にはマイナスバイアスが印加され、いわゆる逆バイアス状態となる。この逆バイアス状態は、後で行なう閾値電圧  $V_{th}$  のばらつき補正およびキャリア移動度  $\mu$  のばらつき補正の動作を正常に動作させるために必要である。

#### 【0144】

次に、閾値 & 移動度補正パルスAZ2をインアクティブLにし( $t_4$ )、それとほぼ同じくして(若干遅れて)走査駆動パルスDSをアクティブLにする( $t_5$ )。これにより、検知トランジスタ124がオフする一方、発光制御トランジスタ122がオンする。この結果、駆動電流  $I_{ds}$  が保持容量120に流れ込み、駆動トランジスタ121の閾値電圧  $V_{th}$  を補正(キャンセル)する閾値補正期間に入る。

40

#### 【0145】

駆動トランジスタ121のゲート端Gは接地電位  $V_{ofs}$  に保持されており、駆動トランジスタ121のソース電位  $V_s$  が上昇して駆動トランジスタ121がカットオフするまで駆動電流  $I_{ds}$  が流れる。カットオフすると駆動トランジスタ121のソース電位  $V_s$  は “ $V_{ofs} - V_{th}$ ” となる。

50

## 【0146】

すなわち、有機EL素子127の等価回路はダイオードと寄生容量C<sub>el</sub>の並列回路で表されるため、“V<sub>el</sub> - V<sub>cath</sub> + V<sub>thEL</sub>”である限り、つまり、有機EL素子127のリーフ電流が駆動トランジスタ121に流れる電流よりもかなり小さい限り、駆動トランジスタ121の電流は保持容量120と寄生容量C<sub>el</sub>を充電するために使われる。

## 【0147】

この結果、駆動トランジスタ121を流れるドレン電流I<sub>ds</sub>の電流路が遮断されると、有機EL素子127のアノード端Aの電圧V<sub>el</sub>つまりノードND121の電位は、時間とともに上昇してゆく。そして、ノードND121の電位(ソース電圧V<sub>s</sub>)とノードND122の電圧(ゲート電圧V<sub>g</sub>)との電位差がちょうど閾値電圧V<sub>th</sub>となったところで駆動トランジスタ121はオン状態からオフ状態となり、ドレン電流は流れなくなり、閾値補正期間が終了する。つまり、一定時間経過後、駆動トランジスタ121のゲート・ソース間電圧V<sub>gs</sub>は閾値電圧V<sub>th</sub>という値をとる。

10

## 【0148】

このとき、“V<sub>el</sub> = V<sub>ofs</sub> - V<sub>th</sub> - V<sub>cath</sub> + V<sub>thEL</sub>”となっている。つまり、ノードND121とノードND122の間に現われた電位差=閾値電圧V<sub>th</sub>は保持容量120に保持されることになる。このように、各検知トランジスタ123, 124は閾値&移動度補正走査線114AZ, 115AZによってそれぞれ適切なタイミングで選択されたとき動作し、駆動トランジスタ121の閾値電圧V<sub>th</sub>を検知し、これを保持容量120に保持する。

20

## 【0149】

走査駆動パルスDSをインアクティブHに(t6)、さらに閾値&移動度補正パルスAZ1をインアクティブLに(t7)、この順に切り替えることで、発光制御トランジスタ122と検知トランジスタ123を順にオフすることで、閾値キャンセル動作を終了させる。発光制御トランジスタ122を検知トランジスタ123よりも先にオフすることで、駆動トランジスタ121のゲート端Gの電圧V<sub>g</sub>の変動を抑えることが可能となる。

## 【0150】

なお、閾値キャンセル(V<sub>th</sub>補正期間)経過後も、検知した駆動トランジスタ121の閾値電圧V<sub>th</sub>を保持容量120に補正用電位として保持させる。

## 【0151】

このように、タイミングt5 ~ t6は、駆動トランジスタ121の閾値電圧V<sub>th</sub>を検出する期間である。ここでは、この検出期間t5 ~ t6を閾値補正期間と呼んでいる。

30

## 【0152】

次に、書き駆動パルスWSをアクティブHにしてサンプリングトランジスタ125をオンして、保持容量120への画素信号V<sub>sig</sub>を書き込む(サンプリングするととも称する)(t8 ~ t10)。このような映像信号V<sub>sig</sub>のサンプリングは、書き駆動パルスWSがインアクティブLに戻るタイミングt10まで行なわれる。すなわちタイミングt8 ~ t10が信号書き込み期間(以下サンプリング期間とも称する)と称する。通常、サンプリング期間は、1水平期間(1H)に設定される。

## 【0153】

このサンプリング期間(t8 ~ t10)では、駆動トランジスタ121のゲート端Gに画素信号V<sub>sig</sub>の信号電位V<sub>in</sub>を供給することで、ゲート電圧V<sub>g</sub>を信号電位V<sub>in</sub>に対応する駆動電位とする。信号電位V<sub>in</sub>に対応する保持容量120に書き込まれる情報の大きさの割合を、書き込みゲインG<sub>input</sub>と称する。この際、画素信号V<sub>sig</sub>は駆動トランジスタ121の閾値電圧V<sub>th</sub>に足し込む形で保持される。この結果、駆動トランジスタ121の閾値電圧V<sub>th</sub>の変動は常にキャンセルされる形となるので、閾値補正を行なっていることになる。

40

## 【0154】

駆動トランジスタ121のゲート・ソース間電圧V<sub>gs</sub>、つまり保持容量120に書き込まれる駆動電位は、保持容量120(容量値C<sub>s</sub>)と有機EL素子127の寄生容量C<sub>el</sub>(容量値C<sub>el</sub>)とゲート・ソース間の寄生容量(容量値C<sub>gs</sub>)によって、式(2)のよ

50

うに決定される。

【0155】

【数2】

$$V_{gs} = \frac{C_{el}}{C_{el} + C_s + C_{gs}} (V_{sig} - V_{ofs}) + V_{th} \dots (2)$$

【0156】

しかし、一般に寄生容量  $C_{el}$  は保持容量 120 の容量値  $C_s$  およびゲート・ソース間の寄生容量値  $C_{gs}$  に比べて遙かに大きい、つまり、有機 EL 素子 127 の寄生容量（等価容量） $C_{el}$  に比べて保持容量 120 は充分に小さい。この結果、映像信号  $V_{sig}$  の殆ど大部分が保持容量 120 に書き込まれる。正確には、 $V_{ofs}$  に対する、 $V_{sig}$  の差分 “ $V_{sig} - V_{ofs}$ ” が保持容量 120 に書き込まれる。

10

【0157】

したがって、駆動トランジスタ 121 のゲート・ソース間の電圧  $V_{gs}$  は、先に検出保持された閾値電圧  $V_{th}$  と今回サンプリングされた “ $V_{sig} - V_{ofs}$ ” を加えたレベル “ $V_{sig} - V_{ofs} + V_{th}$ ” に等しい。このとき、接地電位  $V_{ofs}$  を画素信号  $V_{sig}$  の黒レベル付近に設定しておけば、 $V_{ofs} = 0\text{V}$  とすることができ、結果的に、ゲート・ソース間電圧  $V_{gs}$  (= 駆動電位) は、ほぼ “ $V_{sig} + V_{th}$ ” と等しいことになる。

20

【0158】

信号書き込み期間の終了するタイミング  $t_{10}$  より前に走査駆動パルス DS をアクティブ L とし発光制御トランジスタ 122 をオンさせる ( $t_9$ )。これにより、駆動トランジスタ 121 のドレイン端 D が発光制御トランジスタ 122 を介して第 1 電源電位  $V_{c1}$  に接続されるので、画素回路 P は非発光期間から発光期間に進む。

20

【0159】

このように、サンプリングトランジスタ 125 がまだオン状態でかつ発光制御トランジスタ 122 がオン状態に入った期間  $t_9 \sim t_{10}$  で、駆動トランジスタ 121 の移動度補正を行なう。書き込み駆動パルス WS と走査駆動パルス DS のアクティブ期間のオーバーラップする期間（移動度補正期間と称する）を調整することにより、各画素の駆動トランジスタ 121 の移動度の補正を最適化するのである。すなわち、信号書き込み期間の後部分と発光期間の先頭部分とが重なる期間  $t_9 \sim t_{10}$  で移動度補正を適切に実行する。

30

【0160】

なお、この移動度補正を実行する発光期間の先頭では、有機 EL 素子 127 は實際には逆バイアス状態にあるので発光することはない。この移動度補正期間  $t_9 \sim t_{10}$  では、駆動トランジスタ 121 のゲート端 G が映像信号  $V_{sig}$ （詳しくは信号電位  $V_{in}$ ）に対応する電位に固定された状態で、駆動トランジスタ 121 に駆動電流  $I_{ds}$  が流れる。

30

【0161】

ここで、“ $V_{ofs} - V_{th} < V_{thEL}$ ” と設定しておくことで、有機 EL 素子 127 は逆バイアス状態におかれるため、ダイオード特性ではなく単純な容量特性を示すようになる。よって駆動トランジスタ 121 に流れる駆動電流  $I_{ds}$  は保持容量 120 の容量値  $C_s$  と有機 EL 素子 127 の寄生容量（等価容量） $C_{el}$  の容量値  $C_{el}$  の両者を結合した容量 “ $C = C_s + C_{el}$ ” に書き込まれていく。これにより駆動トランジスタ 121 のソース電位  $V_s$  は上昇していく。

40

【0162】

図 4 のタイミングチャートでは、この上昇分を  $\Delta V$  で表してある。この上昇分、すなわち移動度補正パラメータである負帰還量  $\Delta V$  は結局、保持容量 120 に保持されたゲート・ソース間電圧  $V_{gs}$  から差し引かれることになるので、負帰還をかけたことになる。このように、駆動トランジスタ 121 の駆動電流  $I_{ds}$  を同じく駆動トランジスタ 121 のゲート・ソース間電圧  $V_{gs}$  に負帰還することで、移動度  $\mu$  を補正することが可能である。なお

50

、負帰還量  $V$  は移動度補正期間  $t_9 \sim t_{10}$  の時間幅  $t$  を調整することで最適化可能である。

#### 【0163】

本例の場合、映像信号  $V_{sig}$  が高いほど駆動電流  $I_{ds}$  は大きくなり、 $V$  の絶対値も大きくなる。したがって発光輝度レベルに応じた移動度補正が行なえる。また、移動度が高い駆動トランジスタ 121 と低い駆動トランジスタ 121 を考えた場合、映像信号  $V_{sig}$  を一定とすると、駆動トランジスタ 121 の移動度  $\mu$  が大きいほど  $V$  の絶対値も大きくなる。

#### 【0164】

換言すると、移動度補正期間に移動度が高い駆動トランジスタ 121 は低い駆動トランジスタ 121 に対してソース電位が大きく上昇する。また、ソース電位が大きく上昇するほどゲートとソース間の電位差が小さくなり電流が流れ難くなるように負帰還が掛かる。移動度  $\mu$  が大きいほど負帰還量  $V$  が大きくなるので、画素ごとの移動度  $\mu$  のばらつきを取り除くことが可能である。移動度の違う駆動トランジスタ 121 であっても、同じ駆動電流  $I_{ds}$  を有機 EL 素子 127 に流すことができる。移動度補正期間を調整することで、その負帰還量  $V$  の大きさを最適な状態に設定できる。

10

#### 【0165】

次に、書込走査部 104 は、書込駆動パルス WS をインアクティブ L に切り替える ( $t_{10}$ )。これにより、サンプリングトランジスタ 125 が非導通（オフ）状態となり発光期間に進む。この後、次のフレーム（もしくはフィールド）に移って、再び、閾値補正準備動作、閾値補正動作、移動度補正動作、および発光動作が繰り返される。

20

#### 【0166】

この結果、駆動トランジスタ 121 のゲート端 G は映像信号線 106 HS から切り離される。駆動トランジスタ 121 のゲート端 G への信号電位  $V_{in}$  の印加が解除されるので、駆動トランジスタ 121 のゲート電位  $V_g$  は上昇可能となる。

#### 【0167】

このとき、駆動トランジスタ 121 に流れる駆動電流  $I_{ds}$  は有機 EL 素子 127 に流れ、有機 EL 素子 127 のアノード電位は駆動電流  $I_{ds}$  に応じて上昇する。この上昇分を  $V_{el}$  とする。このとき、駆動トランジスタ 121 のゲート・ソース間電圧  $V_{gs}$  は保持容量 120 による効果によって一定であるので、駆動トランジスタ 121 は、一定電流（駆動電流  $I_{ds}$ ）を有機 EL 素子 127 に流す。その結果、電圧降下が生じ、有機 EL 素子 127 のアノード端 A の電位  $V_{el}$  (= ノード N D 121 の電位) は、有機 EL 素子 127 に駆動電流  $I_{ds}$  という電流が流れ得る電圧まで上昇する。その間、保持容量 120 に保持されたゲート・ソース間電圧  $V_{gs}$  は “ $V_{sig} + V_{th} - V$ ” の値を維持する。

30

#### 【0168】

やがて、ソース電位  $V_s$  の上昇に伴い、有機 EL 素子 127 の逆バイアス状態は解消されるので、駆動電流  $I_{ds}$  の流入により有機 EL 素子 127 は実際に発光を開始する。このときの有機 EL 素子 127 のアノード電位の上昇 ( $V_{el}$ ) は、駆動トランジスタ 121 のソース電位  $V_s$  の上昇に他ならず、駆動トランジスタ 121 のソース電位  $V_s$  は、“ $-V_{th} + V + V_{el}$ ” となる。

40

#### 【0169】

発光時の駆動電流  $I_{ds}$  対ゲート電圧  $V_{gs}$  の関係は、先のトランジスタ特性を表わした式 (1) の  $V_{gs}$  に “ $V_{sig} + V_{th} - V$ ” を代入することで、式 (3) のように表わすことができる。

#### 【0170】

## 【数3】

$$I_{ds} = k \mu (V_{gs} - V_{th})^2 = k \mu (V_{sig} - \Delta V)^2 \cdots (3)$$

式(3)において、 $k = (1/2)(W/L)C_{ox}$ である。この式(3)から、閾値電圧 $V_{th}$ の項がキャンセルされており、有機EL素子127に供給される駆動電流 $I_{ds}$ は駆動トランジスタ121の閾値電圧 $V_{th}$ に依存しないことが分かる。基本的に駆動電流 $I_{ds}$ は映像信号の信号電圧 $V_{sig}$ によって決まる。換言すると、有機EL素子127は映像信号 $V_{sig}$ に応じた輝度で発光することになる。

10

## 【0171】

その際、信号電位 $V_{in}$ は帰還量 $V$ で補正されている。この補正量 $V$ はちょうど式(3)の係数部に位置する移動度 $\mu$ の効果を打ち消すように働く。したがって、駆動電流 $I_{ds}$ は実質的に信号電位 $V_{in}$ のみに依存することになる。駆動電流 $I_{ds}$ は閾値電圧 $V_{th}$ に依存しないので、閾値電圧 $V_{th}$ が製造プロセスにより変動しても、ドレイン・ソース間の駆動電流 $I_{ds}$ は変動せず、有機EL素子127の発光輝度も変動しない。

10

## 【0172】

また、駆動トランジスタ121のゲート端Gとソース端Sとの間には保持容量120が接続されており、その保持容量120による効果により、発光期間の最初でブートアップ動作が行なわれ、駆動トランジスタ121のゲート・ソース間電圧“ $V_{gs} = V_{in} - V + V_{th}$ ”を一定に維持したまま、駆動トランジスタ121のゲート電位 $V_g$ およびソース電位 $V_s$ が上昇する。駆動トランジスタ121のソース電位 $V_s$ が“ $-V_{th} + V + V_{el}$ ”となることで、ゲート電位 $V_g$ は“ $V_{in} + V_{el}$ ”となる。

20

## 【0173】

ここで、有機EL素子127は、発光時間が長くなるとそのI-V特性が変化してしまう。そのため、ノードND121の電位も変化する。しかしながら、保持容量120による効果のため、ノードND121の電位上昇に連動して、ノードND122の電位も上昇するので、駆動トランジスタ121のゲート・ソース間電位 $V_{gs}$ はノードND121の電位上昇に拘らず、常にほぼ“ $V_{sig} + V_{th} - V$ ”に維持されるので、有機EL素子127に流れる電流は変化しない。よって、有機EL素子127のI-V特性が劣化しても一定電流 $I_{ds}$ が常に流れ続けるため、有機EL素子127は画素信号 $V_{sig}$ に応じた輝度で発光を続けることになり、輝度が変化することはない。

30

## 【0174】

この後、次のフィールドのタイミングt1に至ると、走査駆動パルスDSがインアクティブHとなって発光制御トランジスタ122がオフし、発光が終了するとともに当該フィールドが終わる。この後、前述と同様にして、次のフィールドの動作に移って、再び閾値電圧補正動作、移動度補正動作、および発光動作が繰り返されることになる。

30

## 【0175】

このように、第2比較例の画素回路Pでは、ブートアップ回路130が、電気光学素子の一例である有機EL素子127の電流-電圧特性の変化を補正して駆動電流を一定に維持する駆動信号一定化回路として機能するようになっているのである。

40

## 【0176】

また、第2比較例の画素回路Pでは、閾値&移動度補正回路140を設けており、閾値補正期間における検知トランジスタ123, 124の作用により、駆動トランジスタ121の閾値電圧 $V_{th}$ をキャンセルし、当該閾値電圧 $V_{th}$ のばらつきの影響を受けない一定電流 $I_{ds}$ を流すことができるため、入力画素信号に対応する安定した階調で表示でき、高画質の画像を得ることができる。

## 【0177】

加えて、サンプリングトランジスタ125による映像信号 $V_{sig}$ の書き込み動作と連動し

50

た発光制御トランジスタ122による移動度補正期間における作用により、駆動トランジスタ121のキャリア移動度 $\mu$ を反映させたゲート・ソース間電位 $V_{gs}$ として、当該キャリア移動度 $\mu$ のばらつきの影響を受けない一定電流 $I_{ds}$ を流すことができるため、入力画素信号に対応する安定した階調で表示でき、高画質の画像を得ることができる。

## 【0178】

つまり、閾値 & 移動度補正回路140が、駆動トランジスタ121の特性ばらつき（本例では閾値電圧 $V_{th}$ およびキャリア移動度 $\mu$ のばらつき）による駆動電流 $I_{ds}$ に与える影響を防ぐために、閾値電圧 $V_{th}$ およびキャリア移動度 $\mu$ による影響を補正して駆動電流を一定に維持する駆動信号一定化回路として機能するようになっているのである。

## 【0179】

第2比較例において示したブートストラップ回路130や閾値 & 移動度補正回路140の回路構成は、駆動トランジスタ121としてnチャネル型を用いて有機EL素子127を駆動するための駆動信号を一定に維持する駆動信号一定化回路の一例に過ぎず、有機EL素子127の経時劣化やnチャネル型の駆動トランジスタ121の特性変動（たとえば閾値電圧や移動度などのばらつきや変動）による駆動電流 $I_{ds}$ に与える影響を防ぐための駆動信号一定化回路としては、その他の公知の様々な回路を適用することができる。

## 【0180】

## &lt;移動度補正の弊害について&gt;

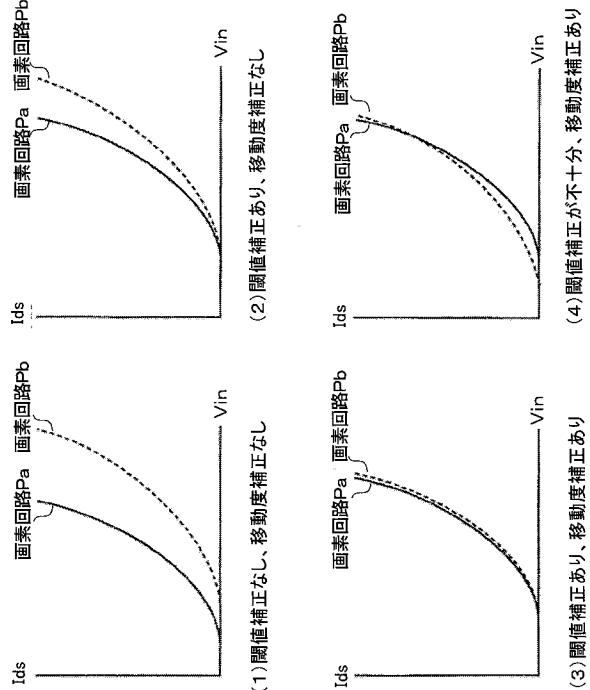

ここで、図3Bと図4を参照して、移動度補正の効果とこの移動度補正による弊害について考察してみる。図3Bを参照して説明したが、製造プロセスや経時における移動度 $\mu_1, \mu_2$ のばらつきに対して、発光時のゲート・ソース間電圧 $V_{gs}$ が“ $V_{in} + V_{th} - V$ ”で表されるようにする閾値補正および移動度補正をかけることで、移動度 $\mu$ の違いを抑制できる。移動度補正期間を調整してそれぞれの移動度補正パラメータ $V_1, V_2$ （ $V = I_{ds} \cdot C_{el} / t$ ）を最適化することで、移動度 $\mu$ の違いを除去できる。

## 【0181】

しかしながら、図4に示した駆動タイミングでは、書き込み駆動パルスWSをアクティブHにしてサンプリングトランジスタ125をオンさせて保持容量120に信号電位 $V_{in}$ に対応する情報（駆動電位）を書き込んだ後の、書き込み駆動パルスWSと走査駆動パルスDSの各アクティブ期間（つまり発光制御トランジスタ122とサンプリングトランジスタ125の各オン期間）のオーバーラップ期間を移動度補正期間（ $t_9 \sim t_{10}$ ）としている。この移動度補正期間では、駆動トランジスタ121に映像信号 $V_{sig}$ （信号電位 $V_{in}$ ）が供給されたままであり、ゲート電位 $V_g$ が固定されたままで、移動度補正分である移動度補正パラメータ $V$ の分だけ駆動トランジスタ121のソース電位 $V_s$ が上昇してしまう。

## 【0182】

この移動度補正期間中のソース電位 $V_s$ の上昇 $V$ は、その時点の駆動トランジスタ121のゲート・ソース間電圧 $V_{gs}$ （=  $V_{sig} + V_{th}$ ）に影響を与えてしまい、ソース電位 $V_s$ での $V$ の上昇分だけ、ゲート・ソース間電圧 $V_{gs}$ が減少してしまう。そのため、発光期間での駆動電流 $I_{ds}$ に資するゲート・ソース間電圧 $V_{gs}$ （つまり駆動電位）が小さくなってしまうので、発光輝度は移動度補正を行なわない場合に比べて低下する。

## 【0183】

この移動度補正に起因する発光輝度低下を防止する一手法として、たとえば、サンプリング期間（ $t_8 \sim t_9$ ）に、所望の輝度の発光に必要な映像信号 $V_{sig}$ （詳しくは信号電位 $V_{in}$ ）に $V$ を加えた電圧を書き込むことが考えられる。つまり、移動度補正によるゲート・ソース間電圧 $V_{gs}$ の減少分を補うように、より大きな映像信号 $V_{sig}$ を画素回路Pに供給して保持容量120により大きな駆動電位を書き込むことが考えられる。しかしながらこの手法では、移動度補正を行なわない場合に比べて信号電位 $V_{in}$ の振幅が大幅に上昇してしまう結果となり、電源電圧や書き込み駆動パルスWSを大きくしなければならず、消費電圧の増大へと繋がってしまう。

## 【0184】

そこで、本実施形態では、移動度補正に起因する発光輝度低下を防止するに当たり、映

10

20

30

40

50

像信号  $V_{sig}$  (詳しくは信号電位  $V_{in}$ ) に移動度補正パラメータ  $V$  の分を加えなくても、移動度補正に起因する発光輝度低下を防止することのできる仕組みにする。以下、具体的に説明する。

#### 【0185】

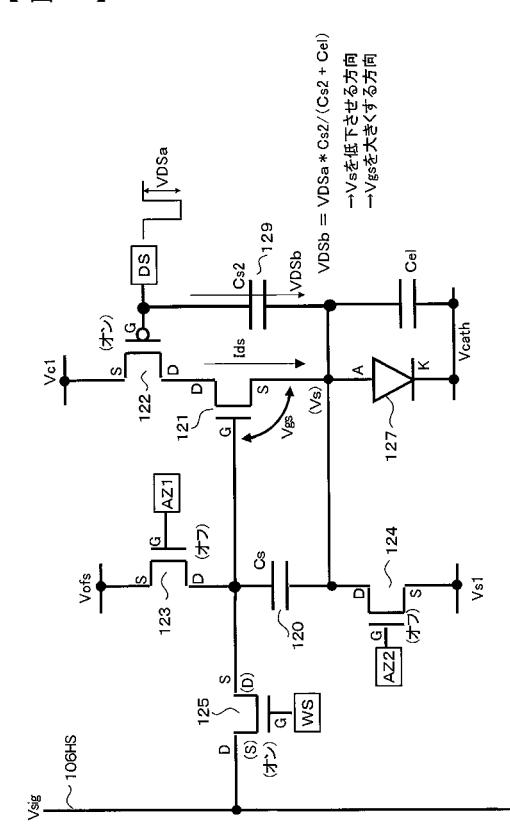

<画素回路：本実施形態>

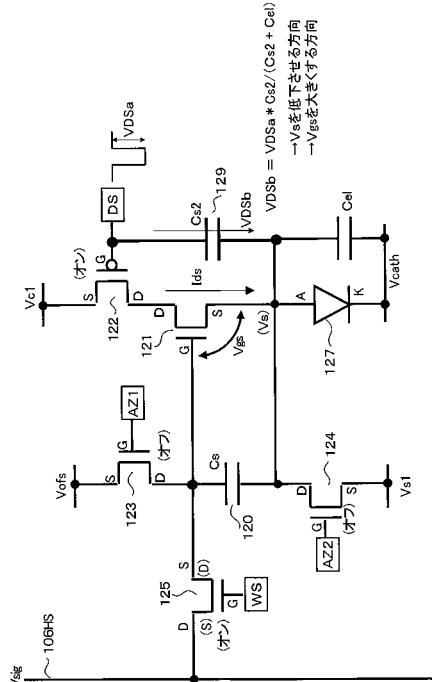

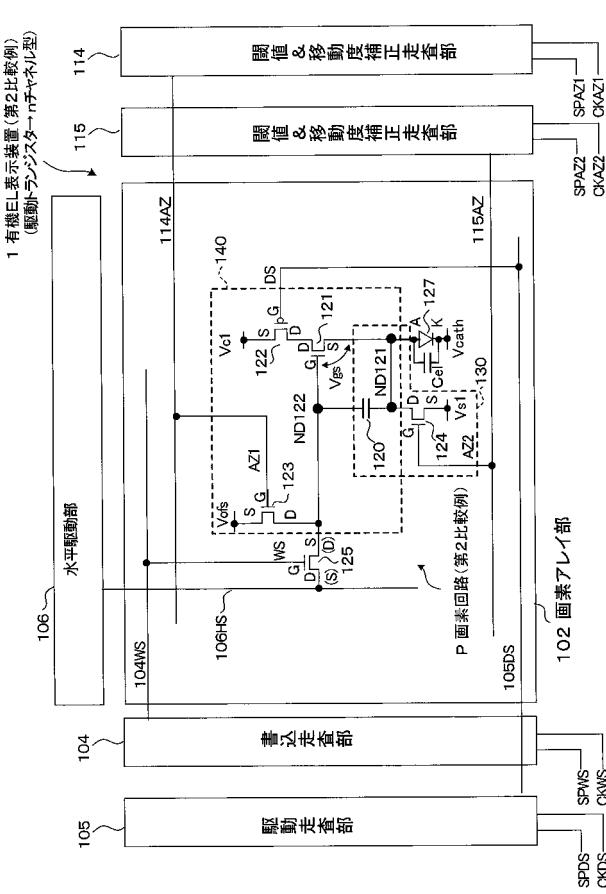

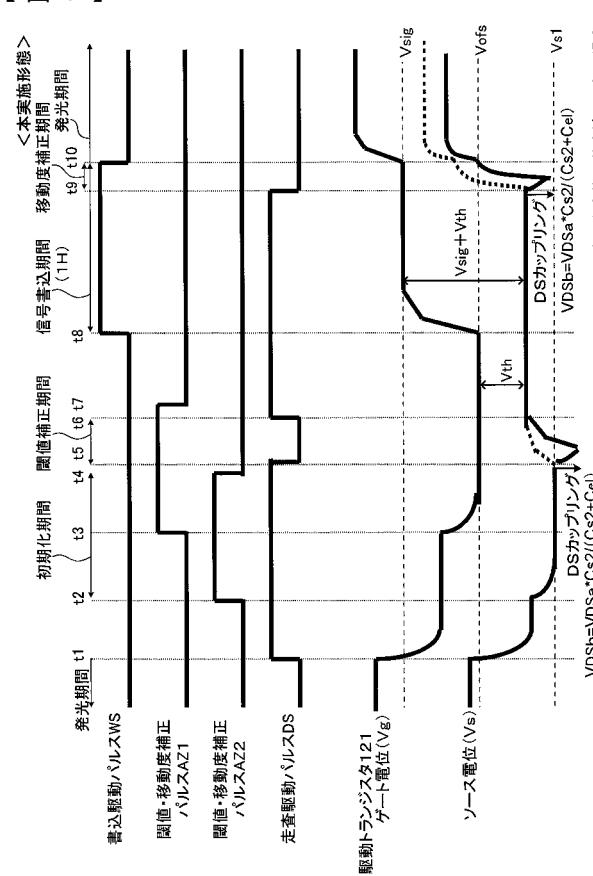

図5は、映像信号  $V_{sig}$  に移動度補正パラメータ  $V$  の分を加えずに移動度補正に起因する発光輝度低下を防止することを可能にする本実施形態の画素回路Pと、当該画素回路Pを備えた有機EL表示装置の一実施形態を示す図である。本実施形態の画素回路Pを画素アレイ部102に備える有機EL表示装置を本実施形態の有機EL表示装置1と称する。

10

#### 【0186】

本実施形態の有機EL表示装置1は、図2に示した第2比較例の画素回路Pと同様の機能要素を持つ複数の画素回路Pを行列状に配置した画素アレイ部102を備え、たとえば、有機EL素子127の経時劣化による駆動電流変動を防ぐ回路(ブートストラップ回路)を搭載し、また駆動トランジスタ121の特性変動(閾値電圧ばらつきや移動度ばらつき)による駆動電流変動を防ぐ駆動方式を採用する点に特徴を有する。そのため、駆動タイミングとしては、基本的には図4に示した第2比較例と同じものが適用される。

#### 【0187】

加えて、本実施形態の有機EL表示装置1においては、画素回路Pごとに、発光制御トランジスタ122のゲート端GとノードND121(駆動トランジスタ121のソース端Sおよび保持容量120の一方の端子と有機EL素子127のアノード端Aの接続点)に容量値Cs2の容量素子129を追加し、容量素子129を介して発光制御トランジスタ122のゲート端Gに供給される走査駆動パルスDSの遷移情報(特に移動度補正開始時のソース電位に対してゲート・ソース間電圧を広げる方向の情報)をノードND121に供給することで、発光期間におけるゲート・ソース間電圧Vgsを広げるようにした点に特徴を有する。

20

#### 【0188】

<画素回路の動作：本実施形態>

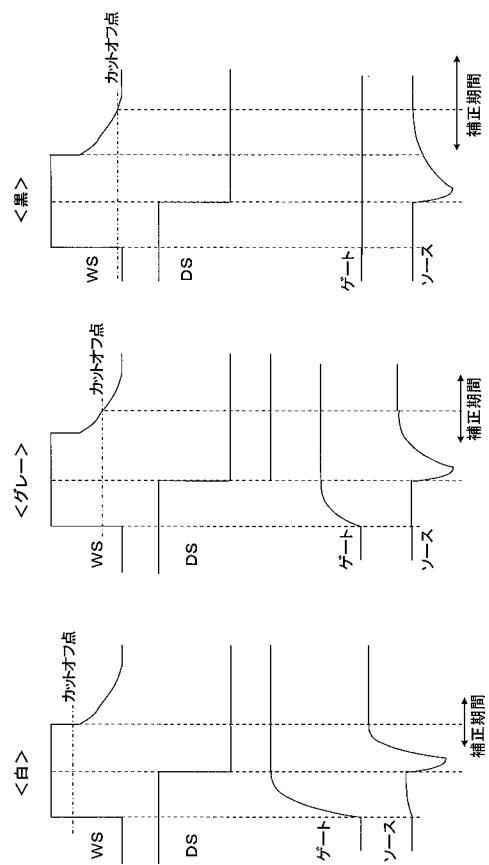

図6は、本実施形態の画素回路の動作を説明するタイミングチャートである。図7は、移動度補正によるゲート・ソース間電圧Vgsの減少分を補正する動作を説明する図ある。

30

#### 【0189】

図4に示した第2比較例の画素回路Pを駆動するタイミングチャートとの比較から推測されるように、各スイッチトランジスタ122, 123, 124, 125に対する駆動パルス自体には相違がない。

#### 【0190】

ただし、本実施形態の画素回路Pでは、pチャネル型の発光制御トランジスタ122のゲート端GとノードND122すなわち駆動トランジスタ121のソース端の間に、容量素子129を設けているので、走査駆動パルスDSの遷移情報がノードND121の電位(ソース電位Vs)に加わることになる。さらにはサンプリングトランジスタ125がオフしているときにはゲート電位Vgも保持容量120の効果により若干上昇する。

40

#### 【0191】

したがって、たとえば、走査駆動パルスDSがアクティブラインアクティブHに遷移する発光制御トランジスタ122のオフの動作時(タイミングt1, t6)には、発光制御トランジスタ122のゲート端Gの電圧変動が容量素子129を介して駆動トランジスタ121のソースにプラスのカッピングVDS( VDSは走査駆動パルスDSの振幅)が入るので、駆動トランジスタ121のソース電位Vsやゲート電位Vgが若干上昇する。

#### 【0192】

一方、走査駆動パルスDSがインアクティブHからアクティブラインに遷移する発光制御トランジスタ122のオンの動作時(タイミングt5, t9)には、発光制御トランジスタ122のゲート端Gの電圧変動が容量素子129を介して駆動トランジスタ121のソース

50

にマイナスのカップリングVDSが入るので、駆動トランジスタ121のソース電位Vsやゲート電位Vgが若干下降する。

【0193】

走査駆動パルスDSの振幅VDSがVDSa（V：ボルト）であるとすると、容量素子129を介して駆動トランジスタ121のソース端S側にカップリングする電圧VDSb（V：ボルト）は、式(4)で表される。

【0194】

【数4】

$$VDSb = VDSa * Cs2 / (Cs2 + Cel) \dots (4)$$

10

【0195】

たとえば、カップリングは発光制御トランジスタ122がオンになるタイミング(t9)であるため、駆動トランジスタ121のゲート・ソース間電圧Vgsは“Vth + VDSb”となる。その後、サンプリングトランジスタ125のオンにより所望の発光に必要な信号電位(映像信号Vsigに対応する値)を保持容量120に書き込み、“Vgs = Vth + VDSb + Vsig”とし、発光制御トランジスタ122がオンでサンプリングトランジスタ125のオンとオーバーラップさせることで移動度補正期間に入る。ここでVDSbのカップリング量=移動度補正で消費する電圧とすると、移動度補正後のゲート・ソース間電圧Vgsは“Vth + Vsig”となり、サンプリングトランジスタ125のオフ後に発光期間へと移行する。

20

【0196】

このように、本実施形態の仕組みでは、アクティブLの走査駆動パルスDSが供給されるpチャネル型の発光制御トランジスタ122のゲート端Gと駆動トランジスタ121のソース端S(ノードND121)との間に容量素子129を追加し、容量素子129を介して走査駆動パルスDSの遷移情報(特に移動度補正開始時のソース電位に対してゲート・ソース間電圧を広げる方向の情報)をノードND121に供給するようにした。

30

【0197】

移動度補正によるゲート・ソース間電圧Vgsの低下分Vを、移動度補正動作の開始時に(移動度補正前に)、走査駆動パルスDSによるカップリング電圧VDSbの分だけ広げておくことで、つまり、移動度補正時に消費される分の電圧Vを発光制御トランジスタ122に供給される走査駆動パルスDSによるカップリングにより電圧VDSbの分だけ上乗せし補うことで、発光期間におけるゲート・ソース間電圧Vgsを広げることができる。これにより、移動度補正に起因する発光輝度低下を防止でき、映像信号Vsig(信号電位Vin)の振幅を下げることができ、通常の映像信号Vsigのみを保持容量120に書き込むだけでも、低消費電力化に寄与することができる。

【0198】

移動度補正に起因する発光輝度低下を防止するに当たり、映像信号Vsig(詳しくは信号電位Vin)に移動度補正パラメータVの分を加えなくても、移動度補正に起因する発光輝度低下を防止できるので、パネルの低消費電力化に寄与することができる。

40

【0199】

加えて、付加的な効果として、映像信号Vsig(詳しくは信号電位Vin)の情報を保持容量120に書き込む際の書き込みゲインGinputの増大も期待できる。たとえば、駆動トランジスタ121のゲート端Gに形成される寄生容量を無視すると、保持容量120の容量値Csおよび有機EL素子127の寄生容量Celを用いて、図2に示した第2比較例の画素回路Pにおける書き込みゲインGinput0は式(5-1)のように表すことができ、一方、図5に示した本実施形態の画素回路Pにおける書き込みゲインGinput1は式(5-2)のように表すことができる。

【0200】

50

## 【数5】

$$G_{\text{input}0} = 1 - Cs / (Cs + Cel) \cdots (5-1)$$

$$G_{\text{input}1} = 1 - Cs / (Cs + Cs_2 + Cel) \cdots (5-2)$$

## 【0201】

式(5-1)と式(5-2)の比較から分かるように、本実施形態の画素回路Pをすることで、書き込みゲインG<sub>input</sub>の増加が見込まれる。これにより、発光輝度を従来と同じにすることを考えた場合、より小さな信号電位V<sub>in</sub>であってもよいと言うことになり、映像信号V<sub>sig</sub>の振幅を更に下げることが可能であり、低消費電力化を更に促進できる。

10

## 【0202】

このように、移動度補正時に消費される分(移動度補正パラメータV)の電圧を発光制御トランジスタ122のゲート端と駆動トランジスタ121のソース端の間に配した容量素子129を介して飛び込む、移動度補正期間開始を示す走査駆動パルスDSの立下り情報のカップリング効果により補うことで、信号振幅を大幅に削減し、低消費電力化に大きく寄与することができる。

20

## 【0203】

&lt;変形例&gt;

図8は、移動度補正によるゲート・ソース間電圧V<sub>gs</sub>の減少分を補正する変形例の動作を説明する図ある。図8では、書き込み駆動パルスWSを、立下りを鈍らせて階調ごとにカットオフ点を変化させる仕組みとDSカップリングとの組合せにおいて、白、グレー、黒の各表示時のDSカップリング時の、駆動パルスWS, DSと、駆動トランジスタ121のゲートおよびソースの各電圧を示したものである。

20

## 【0204】

前述の補正の仕組みでは、実際の所は、V<sub>gs</sub>補完完量に関しては、階調によらず一定となる。よって、たとえば、黒が浮いてしまうことが考えられる。一方、階調ごとに最適な移動度補正時間をとるために、書き込み駆動パルスWSを、立下りを鈍らせて階調ごとにカットオフ点を変化させる仕組みがある。この仕組みを用いることで、白信号付近ではDSカップリングによりゲート・ソース間電圧V<sub>gs</sub>を開き、信号電圧を低下させることができ、グレー～黒信号では書き込み駆動パルスWSの立下りをなまらせることで移動度補正量を多くし、所望の階調を実現できる。

30

## 【0205】

すなわち、DSカップリングにより“信号書き込み+”の電圧がゲート・ソース間電圧V<sub>gs</sub>に上乗せされる。この+は、信号電圧に依らず一定である。しかしながら、ここでの問題は低階調で所望の輝度より浮いてしまうことである。極端な例として黒を書く場合、閾値補正後、信号電圧は0V書きけば黒表示になるが、DSカップリングにより+が上乗せされてしまう。これを沈めるために、移動度補正時間を長く取る必要がある。移動度補正時間は低階調ほど長くする必要があるので、書き込み駆動パルスWSを、立下りを鈍らせて階調ごとにカットオフ点を変化させる仕組みの波形にし、移動度補正時間を信号電圧ごとに変える必要がある。

40

## 【0206】

以上、本発明について実施形態を用いて説明したが、本発明の技術的範囲は前記実施形態に記載の範囲には限定されない。発明の要旨を逸脱しない範囲で前記実施形態に多様な変更または改良を加えることができ、そのような変更または改良を加えた形態も本発明の技術的範囲に含まれる。

## 【0207】

また、前記の実施形態は、クレーム(請求項)にかかる発明を限定するものではなく、また実施形態の中で説明されている特徴の組合せの全てが発明の解決手段に必須であるとは限らない。前述した実施形態には種々の段階の発明が含まれており、開示される複数の

50

構成要件における適宜の組合せにより種々の発明を抽出できる。実施形態に示される全構成要件から幾つかの構成要件が削除されても、効果が得られる限りにおいて、この幾つかの構成要件が削除された構成が発明として抽出され得る。

### 【0208】

<画素回路および駆動タイミングの変形例>

たとえば、回路理論上は「双対の理」が成立するので、画素回路Pに対しては、この観点からの変形を加えることができる。この場合、図示を割愛するが、先ず、図5に示した5TR構成の画素回路Pがnチャネル型の駆動トランジスタ121を用いて構成しているのに対し、pチャネル型の駆動トランジスタ（以下p型駆動トランジスタ121pと称する）を用いて画素回路Pを構成する。これに合わせてpチャネル型の発光制御トランジスタ122をアクティブHの走査駆動パルスが供給されるnチャネル型の発光制御トランジスタ（以下n型発光制御トランジスタ122nと称する）に代え、また映像信号Vsigの信号電位Vinの極性や電源電圧の大小関係を逆転させるなど、双対の理に従った変更を加える。

10

### 【0209】

このような双対の理を適用してトランジスタをp型にした変形例の有機EL表示装置においても、前述のn型にした基本例の有機EL表示装置と同様に、容量素子129をn型発光制御トランジスタ122nのゲート端とp型駆動トランジスタ121pのソース端に接続することで、移動度補正開始時にp型駆動トランジスタ121pのゲート・ソース間電圧Vgsを予め広げておいてから移動度補正を行なうことができるので、移動度補正に伴うp型駆動トランジスタ121pのゲート・ソース間電圧Vgsの減少分を補うことができる。

20

### 【0210】

なお、ここで説明した変形例は、図5に示した5TR構成に対して「双対の理」に従った変更を加えたものであるが、回路変更の手法はこれに限定されるものではなく、5TR構成以外であってもよい。サンプリングトランジスタ125をオン状態にして信号電位Vinに応じた情報を保持容量120に保持させた後にサンプリングトランジスタ125をオン状態にしたままで移動度補正動作を行なう画素回路Pおよび駆動タイミングである限りにおいて、本実施形態の思想を適用することができる。

30

### 【図面の簡単な説明】

#### 【0211】

【図1】図1は、本発明に係る表示装置の一実施形態であるアクティブラトリクス型表示装置の構成の概略を示すブロック図である。

【図2】図1に示した有機EL表示装置を構成する本実施形態の画素回路に対する比較例を示す図である。

【図3】有機EL素子や駆動トランジスタの動作点を説明する図である。

【図3A】有機EL素子や駆動トランジスタの特性ばらつきが駆動電流Idsに与える影響を説明する図である。

【図3B】駆動トランジスタの特性ばらつきが駆動電流に与える影響の改善手法の概念を説明する図（その1）である。

40

【図3C】駆動トランジスタの特性ばらつきが駆動電流に与える影響の改善手法の概念を説明する図（その2）である。

【図4】第2比較例の画素回路の動作を説明するタイミングチャートである。

【図5】本実施形態の画素回路Pと有機EL表示装置の一実施形態を示す図である。

【図6】本実施形態の画素回路の動作を説明するタイミングチャートである。

【図7】移動度補正によるゲート・ソース間電圧Vgsの減少分を補正する動作を説明する図ある。

【図8】移動度補正によるゲート・ソース間電圧Vgsの減少分を補正する変形例の動作を説明する図ある。

### 【符号の説明】

50

## 【0212】

1...有機EL表示装置、101...基板、102...画素アレイ部、103...垂直駆動部、

104...書き込み走査部、104WS...書き込み走査線、105...駆動走査部、106...水平駆動部

、106HS...映像信号線、109...制御部、114, 115...閾値 & 移動度補正走査部、

114AZ, 115AZ...閾値 & 移動度補正走査線、120...保持容量、121...駆動トランジスタ、

122...発光制御トランジスタ、123, 124...検知トランジスタ、125...サンプリングトランジスタ、

127...有機EL素子、129...容量素子、130...ブートストラップ回路、140...閾値 & 移動度補正回路、

AZ1, AZ2...閾値 & 移動度補正パルス、Ce1...有機EL素子の寄生容量、DS...走査駆動パルス、P...画素回路、Vsig...映像信号、

WS...書き込み駆動パルス

10

【図1】

【図2】

【図3】

【図3A】

【図3B】

【図3C】

【 四 4 】

【 义 6 】

【図5】

【四七】

【図8】

---

フロントページの続き

(51)Int.Cl. F I テーマコード(参考)

H 05 B 33/14 A

F ターム(参考) 3K107 AA01 CC02 CC14 EE03 HH02 HH05

5C080 AA06 BB05 DD05 DD26 DD29 EE29 FF07 FF11 HH09 JJ02

JJ03 JJ04 JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路和显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2008233129A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2008-10-02 |

| 申请号            | JP2007068020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2007-03-16 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| [标]发明人         | 豊村直史<br>内野勝秀<br>飯田幸人                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 豊村 直史<br>内野 勝秀<br>飯田 幸人                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0819 G09G2300/0842 G09G2300/0861 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.641.A G09G3/20.611.H G09G3/20.611.A H05B33/14.A<br>G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/CC02 3K107/CC14 3K107/EE03 3K107/HH02 3K107/HH05 5C080/AA06 5C080/<br>/BB05 5C080/DD05 5C080/DD26 5C080/DD29 5C080/EE29 5C080/FF07 5C080/FF11 5C080/HH09<br>5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C380/AA01 5C380/AB06 5C380/AB18 5C380<br>/AB19 5C380/AB22 5C380/AB23 5C380/AB45 5C380/AC12 5C380/AC20 5C380/BA01 5C380/BA38<br>5C380/BA39 5C380/BB02 5C380/BB22 5C380/BD02 5C380/CA02 5C380/CA08 5C380/CA09 5C380<br>/CA12 5C380/CB01 5C380/CB16 5C380/CB18 5C380/CB26 5C380/CB27 5C380/CB31 5C380/CB37<br>5C380/CC03 5C380/CC04 5C380/CC06 5C380/CC07 5C380/CC26 5C380/CC27 5C380/CC30 5C380<br>/CC33 5C380/CC39 5C380/CC65 5C380/CC72 5C380/CC77 5C380/CD025 5C380/CD035 5C380<br>/DA02 5C380/DA06 5C380/DA32 5C380/DA47 5C380/HA05 |         |            |

| 代理人(译)         | 船桥 国则                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

### 摘要(译)

要解决的问题：即使在没有增加具有移动度校正功能的有机EL显示装置中的视频信号的幅度的情况下，也防止由于移动度校正而导致的发光亮度下降。

**解决方案：**电容元件129被添加到发光控制晶体管122的栅极端子G和驱动晶体管121的源极端子S。由于移动度校正引起的栅极 - 源极电压Vgs的下降电压 $\Delta V$ ，即在开始移动度校正操作时用于移动度校正所消耗的电压 $\Delta V$ 通过仅通过耦合提供给发光控制晶体管122的扫描驱动脉冲DS来增加电压VDSb来补偿以增加栅极 - 在发光期间的源电压Vgs。因此，可以防止由于移动度校正引起的发光亮度的下降；通过在存储容量120中仅写入正常视频信号Vsigt，可以减小视频信号Vsigt的幅度，并且可以有助于显示装置的低功耗。