(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-518473

(P2006-518473A)

(43) 公表日 平成18年8月10日(2006.8.10)

| (51) Int.C1.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | J 5C080     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 624B 5C094  |

| <b>G09F 9/30</b> (2006.01)  | G09G 3/20 | 641C        |

| <b>H01L 27/32</b> (2006.01) | G09G 3/20 | 670J        |

|                             | GO9F 9/30 | 338         |

審査請求 未請求 予備審査請求 未請求 (全 24 頁) 最終頁に続く

|               |                              |          |                                                                                                                                                                                            |

|---------------|------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2006-500309 (P2006-500309) | (71) 出願人 | 590000248<br>コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ<br>Koninklijke Philips Electronics N. V.<br>オランダ国 5621 ベーー アインドーフェン フルーネヴァウツウェッハ<br>1<br>Groenewoudseweg 1, 5621 BA Eindhoven, The Netherlands |

| (86) (22) 出願日 | 平成16年1月20日 (2004.1.20)       |          |                                                                                                                                                                                            |

| (85) 翻訳文提出日   | 平成17年7月22日 (2005.7.22)       |          |                                                                                                                                                                                            |

| (86) 國際出願番号   | PCT/IB2004/000158            |          |                                                                                                                                                                                            |

| (87) 國際公開番号   | W02004/066250                |          |                                                                                                                                                                                            |

| (87) 國際公開日    | 平成16年8月5日 (2004.8.5)         |          |                                                                                                                                                                                            |

| (31) 優先権主張番号  | 0301623.5                    |          |                                                                                                                                                                                            |

| (32) 優先日      | 平成15年1月24日 (2003.1.24)       |          |                                                                                                                                                                                            |

| (33) 優先権主張国   | 英國 (GB)                      |          |                                                                                                                                                                                            |

|               |                              | (74) 代理人 | 100070150<br>弁理士 伊東 忠彦                                                                                                                                                                     |

|               |                              | (74) 代理人 | 100091214<br>弁理士 大貫 進介                                                                                                                                                                     |

最終頁に続く

(54) 【発明の名称】アクティブマトリクス電界発光表示装置

## (57) 【要約】

アクティブマトリクス表示装置の夫々の画素は、断続的に表示素子に電流を流す第一のアモルファスシリコン・トランジスタ及び断続的に表示素子に電流を流す第二のアモルファスシリコン・トランジスタを有する。アモルファスシリコンTFTの経年変化の影響は、二つの駆動トランジスタ間の表示素子を共有することによって低減され得る。デューティーサイクルを設けることは夫々の駆動トランジスタのオン時間を減らすが、TFT特性を幾らか回復し得る期間をももたらす。

**【特許請求の範囲】****【請求項 1】**

複数の表示画素の配列を有し、夫々の画素は、

電界発光表示素子と、

該表示素子に断続的に電流を流す第一のアモルファスシリコン・駆動トランジスタと、

該表示素子に断続的に電流を流す第二のアモルファスシリコン・駆動トランジスタを有することを特徴とする、アクティブマトリクス電界発光表示装置。

**【請求項 2】**

該画素は行及び列で配置され、夫々の駆動トランジスタは夫々の列導電体に結合されることを特徴とする、請求項 1 記載の装置。

10

**【請求項 3】**

前記表示素子からの光出力は、前記第一及び第二の駆動トランジスタを照射することを特徴とする、請求項 1 又は 2 記載の装置。

**【請求項 4】**

アクティブ面及び該アクティブ面に結合される電界発光物質を有する、請求項 1 乃至 3 のうちいずれか一項記載の装置。

**【請求項 5】**

該アクティブ面は、前記表示素子の光から画素回路を遮蔽する黒マスク層を有し、前記第一及び第二の駆動トランジスタは該黒マスク層によって遮蔽されないことを特徴とする、請求項 4 記載の装置。

20

**【請求項 6】**

夫々の画素は、

前記第一の駆動トランジスタのゲート電圧を蓄えるための第一の蓄積容量及び前記第二の駆動トランジスタのゲート電圧を蓄えるための第二の蓄積容量と、

第一のデータラインから該第一の蓄積容量にデータ信号を印加する第一のアドレストランジスタ及び第二のデータラインから該第二の蓄積容量にデータ信号を印加する第二のアドレストランジスタと、を有することを特徴とする、

請求項 1 乃至 5 のうちいずれか一項記載の装置。

**【請求項 7】**

夫々の画素は、前記第一の駆動トランジスタのゲートとソース又はドレインとの間に直列に接続された第一及び第二の容量を有する第一の容量配置と、前記第二の駆動トランジスタのゲートとソース又はドレインとの間に直列に接続された第一及び第二の容量を有する第二の容量配置とを更に有し、

30

前記画素への第一のデータ入力は、該第一の容量配置の該第一及び第二の容量間の接続点に供給され、前記画素への第二のデータ入力は、該第二の容量配置の該第一及び第二の容量間の接続点に供給されることを特徴とする、

請求項 1 乃至 5 のうちいずれか一項記載の装置。

**【請求項 8】**

夫々の画素は、

第一の入力データラインと該第一の容量配置の該第一及び第二の容量間の該接続点との間に接続された第一の入力トランジスタと、

40

第二の入力データラインと該第二の容量配置の該第一及び第二の容量間の該接続点との間に接続された第二の入力トランジスタと、を更に有することを特徴とする、

請求項 7 記載の装置。

**【請求項 9】**

夫々の駆動トランジスタのドレインは、夫々の電力供給ラインに接続されることを特徴とする、請求項 7 又は 8 記載の装置。

**【請求項 10】**

夫々の画素は、

前記第一の駆動トランジスタの前記ゲート及びドレイン間に接続された第一の閾値サン

50

プリングトランジスタと、

前記第二の駆動トランジスタの前記ゲート及びドレイン間に接続された第二の閾値サンプリングトランジスタとを更に有することを特徴とする、

請求項 7 乃至 9 のうちいずれか一項記載の装置。

【請求項 1 1】

夫々の画素は、

前記第一の容量配置の前記第一及び第二の容量間の前記接続点と、前記表示素子との間に接続された第一の短絡トランジスタと、

前記第二の容量配置の前記第一及び第二の容量間の前記接続点と、前記表示装置との間に接続された第二の短絡トランジスタとを更に有することを特徴とする、

請求項 7 乃至 10 のうちいずれか一項記載の装置。

【請求項 1 2】

夫々の画素は、

前記第一の駆動トランジスタのソース及び接地電位ラインの間に接続された第一のバイパストランジスタと、

前記第二の駆動トランジスタのソース及び該接地電位ラインの間に接続された第二のバイパストランジスタと、を更に有することを特徴とする、

請求項 7 乃至 11 のうちいずれか一項記載の装置。

【請求項 1 3】

選択的に動かされ得るように、前記第一及び第二の容量配置の前記第一及び第二の容量は、夫々の前記駆動トランジスタの前記ゲート及びドレイン間に直列に接続され、

夫々の駆動トランジスタのドレインは、夫々異なる電力供給ラインに接続され、

これにより、夫々の駆動トランジスタが、前記表示素子に電流を供給するか、あるいは他のトランジスタからの電流に対してバイパス経路を供給することを特徴とする、

請求項 7 乃至 11 のうちいずれか一項記載の装置。

【請求項 1 4】

夫々の画素は、前記第一及び第二の駆動トランジスタのゲートと接地ラインとの間に直列に接続された第一及び第二の容量を有する容量配置を更に有し、

夫々の駆動トランジスタのソースは、夫々の制御ラインに接続され、

前記画素へのデータ入力は、該容量配置の該第一及び第二の容量間の前記接続点に供給されることを特徴とする、

請求項 1 乃至 5 のうちいずれか一項記載の装置。

【請求項 1 5】

夫々の画素は、前記第二の容量の端子間に接続された短絡トランジスタを更に有することを特徴とする、請求項 1 4 記載の装置。

【請求項 1 6】

夫々の画素は、電力供給ラインと第一及び第二の駆動トランジスタのドレインとの間に接続された充電トランジスタを更に有することを特徴とする、請求項 1 4 または 1 5 記載の装置。

【請求項 1 7】

夫々の画素は、前記第一及び第二の駆動トランジスタの前記ゲート及びドレイン間に接続された放電トランジスタを更に有することを特徴とする、請求項 1 4 乃至 1 6 のうちいずれか一項記載の装置。

【請求項 1 8】

夫々の駆動トランジスタは、NMOSトランジスタを有することを特徴とする、請求項 1 乃至 1 7 のうちいずれか一項記載の装置。

【請求項 1 9】

前記電界発光表示素子は、電界リン光性の有機電界発光表示素子であることを特徴とする、請求項 1 乃至 1 9 のうちいずれか一項記載の装置。

【請求項 2 0】

10

20

30

40

50

夫々の画素は、前記表示素子に断続的に電流を流す第三のアモルファスシリコン・駆動トランジスタを少なくとも更に有することを特徴とする、請求項1乃至19のうちいずれか一項記載の装置。

【請求項21】

複数の表示画素の配列を有し、夫々の画素は電界発光表示素子を有し、

交互に、第一及び第二のアモルファスシリコン・駆動トランジスタを用いて該表示素子に電流を流し、駆動トランジスタは該表示素子に電流が流れていらない時に停止されること、を特徴とするアクティブマトリクス電界発光表示装置を駆動する方法。

【請求項22】

該駆動トランジスタは、該表示素子によって照射されることを特徴とする、請求項21記載の方法。 10

【請求項23】

前記第一及び第二の駆動トランジスタの閾値電圧の時間に渡って変化を補償することを特徴とする、請求項21又は22記載の方法。

【請求項24】

補償のステップは、

前記駆動トランジスタの一つを介して接地に電流を流し、第一の容量に結果として生じるゲート・ソース間電圧まで充電し、

該一つの駆動トランジスタがオフとなるまで該第一の容量を放電し、それによって該第一の容量は閾値電圧を蓄え、 20

該駆動トランジスタの該ゲートとソース又はドレインとの間の該第一の容量に直列である第二の容量をデータ入力電圧まで充電し、

該第一及び第二の容量にかかる電圧の組み合わせを有するゲート・ソース間電圧又はゲート・ドレイン間電圧を用いて、前記表示素子に電流を流す前記駆動トランジスタを使用する、

ことを特徴とする請求項23記載の方法

【請求項25】

該駆動トランジスタの一つを介して接地に電流を流す該ステップは、他の該駆動トランジスタを介して接地に電流を流すことを特徴とする、請求項24記載の方法。

【発明の詳細な説明】 30

【技術分野】

【0001】

本発明は、電界発光表示装置、特に夫々の画素に結合される薄膜スイッチングトランジスタを有するアクティブマトリクス表示装置に関する。

【背景技術】

【0002】

電界発光、光放射、表示素子を用いるマトリクス表示装置が良く知られる。該装置は、有機薄膜電界発光素子、例えば高分子化合物質、又は従来のIII-V族半導体化合物を使用する発光ダイオード(LED)を有しても良い。有機電界発光物質、特に高分子化合物における最近の発展は、特に映像表示装置用に使用されるようなそれらの能力を実証している。一般的に、これらの物質は、一対の電極間に挟まれる半導体複合高分子化合物を一つ又はそれ以上有する。該電極の一つは透明であり、もう片方は空孔又は電子を高分子化合物層に入れるのに適した物質である。有機電界発光物質は、ダイオードのようなI-V特性を示す。故に、それらは表示機能及びスイッチング機能の両方をもたらすことができ、そのため受動型ディスプレイにおいて使われる。あるいは、これらの物質はアクティブマトリクス表示装置に対して用いられても良い。夫々の画素は、表示素子、及び該表示素子を流れる電流を制御する切り替え装置を有する。 40

【0003】

この形式の表示装置は、電流駆動表示素子を有する。従来のアナログ駆動の考えは、前記表示素子への制御電流の供給を有する。画素構造の部分として、前記表示素子を流れる

電流を決める電流形トランジスタに供給されるゲート電圧を有する電流形トランジスタを設けることが知られる。蓄積容量は、アドレス指定相の後にゲート電圧を保持する。

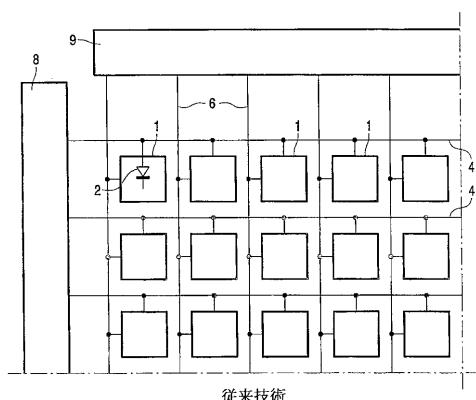

【0004】

図1は、電界発光表示素子をアドレス指定されるアクティブマトリクス用の既知の画素回路を示す。該表示素子は、規則正しく間隔を空けられた画素の行及び列のマトリクス配列を有するパネルを有する。該画素は、ブロック1によって表わされ、関連する切り替え手段と共に電界発光表示素子2を有し、行(選択)及び列(データ)のアドレス導電体4及び6の交差する集合間の共通部分に置かれる。数個の画素のみが簡単化のため図に示される。実際には、数百の行及び列の画素が存在する。画素1は、行、走査、駆動回路8、並びに列、データ、駆動回路9を有する周辺の駆動回路によって、行及び列のアドレス導電体の集合を介してアドレス指定される。該駆動回路は、導電体の夫々の集合の終端に結合される。

【0005】

電界発光表示素子2は、ここではダイオード素子(LED)として表わされ、一つ又はそれ以上の有機電界発光物質が挟まれる一対の電極を有する有機発光ダイオードを有する。前記配列の該表示素子は、絶縁支持材の片側で関連アクティブマトリクス回路と共に支えられる。表示素子のカソード又はアノードのどちらかは、透明な導電体物質で形成される。電界発光層によって発生する光は、これらの電極、及び支持材のもう一方の側で見る人に對して可視的であるような支持材を介して伝送されるように、前記支持材はガラスのような透明の物質から作られ、基材に近い表示素子2の電極はITOのような透明の導電体物質から成る。一般的に、有機電界発光物質層の厚さは、10nmから200nmの間である。素子2に対して使用される適切な有機電界発光物質の典型的な例は、EP-A-0717446で知られ、記述されている。W096/36959で記述されるような結合高分子化合物質も使用され得る。

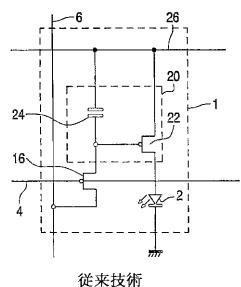

【0006】

図2は、電圧プログラム化動作を提供する既知の画素及び駆動回路の配置を、簡単な図解方式で示す。夫々の画素1は、EL表示素子2及び関連する駆動回路を有する。該駆動回路は、行導電体4で行アドレスパルスによってオンにされるアドレストランジスタ16を有する。該アドレストランジスタ16がオンにされる時、列導電体6での電圧は他の画素に移動する。特に、該アドレストランジスタ16は、駆動トランジスタ22及び蓄積容量24を有する電流源20に列導電体電圧を供給する。列電圧は駆動トランジスタ22のゲートに供給され、該ゲートは、前記行アドレスパルスが終了した後ですら蓄積容量24によってこの電圧で保持される。駆動トランジスタ22は、電力供給ライン26から電流を引き出す。

【0007】

この回路での駆動トランジスタ22は、蓄積容量24が一定のゲートソース間電圧を保持するように、PMOS TFTとして表わされる。これは、トランジスタを流れる一定のソースドレイン電流を生じる。従って、該トランジスタは画素の所望の電流源動作をもたらす。上述の基本的な画素回路は、電圧プログラム化画素であり、駆動電流をサンプリングする電流プログラム化画素も存在する。しかし、全ての画素構造は、夫々の画素に供給されるべき電流を必要とする。

【0008】

今まで、LED表示用アクティブマトリクス回路の大部分は、低温ポリシリコン(LTPS)TFTを使っていた。これらの素子の閾値電圧は時間で安定であるが、無作為な様態で画素から画素へ変化する。これは、画像において受け入れられない静的なノイズをもたらす。多くの回路は、この問題を克服するように提案されてきた。一つの例では、画素がアドレス指定される度に、画素回路は、画素から画素への変化を克服するように、電流形TFTの閾値電圧を測定する。この形式の回路は、LTPS TFTを対象としており、PMOS素子を用いる。このような回路は、現在のところNMOS素子に限られている水素化アモルファスシリコン(a-Si:H)素子では組み立てられ得ない。

【0009】

しかし、a-Si:Hの使用が考えられている。一般的に、a-Si:H TFTを使用する提案され

10

20

30

40

50

た回路は、電圧アドレス指定よりもむしろ電流アドレス指定を用いる。実際には、電流プログラム化画素は基材の中のトランジスタの変化の影響を減らしたり、あるいは除いたりすることが可能である。例えば、電流プログラム化画素は、所望の画素駆動電流が流されるサンプリングトランジスタでゲート ソース間電圧をサンプリングするように電流ミラーを使用する。サンプリングされたゲート ソース間電圧は、駆動トランジスタをアドレス指定するために用いられる。これは、サンプリングトランジスタ及び駆動トランジスタが基材上で夫々隣接し、より正確に夫々と適合され得るので、素子の均一性の問題を部分的に緩和する。他の電流サンプリング回路は、サンプリング及び駆動のために同じトランジスタを使用する。故に、トランジスタの整合は要求されないが、付加的なトランジスタ及びアドレスラインが要求される。

10

#### 【0010】

従来のLED素子を駆動するのに必要とされる電流は極めて大きく、これは、アクティブマトリクス有機LED表示用アモルファスシリコンの使用が可能ではないことを意味している。近年、有機LED及び溶液プロセスによる有機LEDは、リン光の使用によって極めて高い効率を示している。論文“電界リン光性有機発光ダイオード”、52.1 SID 02 要約、2002年5月発行、p.1357掲載、S・R・フォレストら著、及び“高効率溶液プロセスドンドリマーレ”、L-8 SID 02 要約、2002年5月発行、p.1032掲載、J・P・J・マーカム著が参考される。これら素子の所要の電流は、その時、アモルファスシリコンTFTの到達範囲内である。しかし、更なる問題が現われ始める。

20

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0011】

重大な問題は、TFTの閾値電圧の安定性（絶対値ではなくて）である。一定の偏りの下で、アモルファスシリコンTFTの閾値電圧は増加する。そのため、単なる一定の電流が短い時間の後に動作を終える。閾値電圧のドリフトは、一万時間以上又はそれ以上という表示の標準的な動作寿命に渡って、容易に5Vと同じ大きさであり得る。

#### 【0012】

従って、リン光性LED表示用ですら、アモルファスシリコンTFTを有する画素での使用に適したアドレス指定の考えを実行する際に困難が残る。

30

#### 【課題を解決するための手段】

#### 【0013】

本発明によれば、複数の表示画素の配列を有するアクティブマトリクス電界発光表示装置が設けられる。夫々の画素は、

電界発光（EL）表示素子と、

該表示素子に断続的に電流を流す第一のアモルファスシリコン・駆動トランジスタと、該表示素子に断続的に電流を流す第二のアモルファスシリコン・駆動トランジスタと、を有する。

#### 【0014】

本発明は、経年変化の影響が、二つの駆動トランジスタ間の表示素子の駆動を共有することによって低減されるという認識に基づかれる。デューティーサイクルを設けることは、夫々の駆動トランジスタのオン時間を減らすが、TFT特性をいくらか回復し得る期間をも提供する。

40

#### 【0015】

回復過程は、表示素子の出力で第一及び第二のトランジスタを照射することによって改善され得ることも見つけられている。ディスプレイが表示素子の光から画素回路を遮蔽する黒マスク層を有するアクティブ面である時、第一及び第二の駆動トランジスタは、黒マスク層によって遮蔽されないように配置され得る。

#### 【0016】

単純な画素回路において、夫々の画素は、前記第一の駆動トランジスタのゲート電圧を蓄えるための第一の蓄積容量及び前記第二の駆動トランジスタのゲート電圧を蓄えるため

50

の第二の蓄積容量と、第一のデータラインから該第一の蓄積容量にデータ信号を印加する第一のアドレストランジスタ及び第二のデータラインから該第二の蓄積容量にデータ信号を印加する第二のアドレストランジスタと、を有する。従って、画素回路は、二つのデータライン及び一つの行ラインを使用する。代わりに、一つのデータライン及び二つの行ラインで同様の動作を実行することが可能である。

【0017】

本発明のディスプレイは、アモルファスシリコン・駆動トランジスタの経年変化の影響を低減する。それにも関わらず、駆動トランジスタの閾値電圧における時間に渡る変化に対する補償を供給することは、望ましい。この目的のため、夫々の画素は、前記第一の駆動トランジスタのゲートとソース又はドレインとの間に直列に接続された第一及び第二の容量を有する第一の容量配置、並びに前記第二の駆動トランジスタのゲートとソース又はドレインとの間に直列に接続された第一及び第二の容量を有する第二の容量配置を有する。前記画素への第一のデータ入力は、該第一の容量配置の該第一及び第二の容量間の接続点と、該第二の容量配置の該第一及び第二の容量間の接続点に供給される。

【0018】

この画素配置は、駆動トランジスタの閾値電圧が夫々の第一の容量で蓄えられることを可能にし、これは画素が該駆動トランジスタでアドレス指定される度に成され得る。それによって、経年変化に伴う閾値電圧の変化を補償する。従って、アモルファスシリコン回路は、経年変化の影響を補償する特定のフレーム時間に関して電流形TFTの閾値電圧を測定し得るように設けられる。

【0019】

特に、本発明の画素配置は、大きな高解像度のアモルファス有機LED表示に対して十分に短い時間で画素の電圧プログラミング化が有効になっている間に、アモルファスシリコンTFTの閾値電圧の増大を克服する。

【0020】

更に、夫々の画素は、第一の入力データラインと、該第一の容量配置の該第一及び第二の容量間の該接続点との間に接続された第一の入力トランジスタと、第二の入力データラインと該第二の容量配置の該第一及び第二の容量間の該接続点との間に接続された第二の入力トランジスタと、を有する。前記入力トランジスタは、前記第二の容量への蓄積のため、画素へのデータ電圧の適用の時間を決める。

【0021】

更に、夫々の画素は、前記第一の駆動トランジスタの前記ゲート及びドレイン間に接続された第一の閾値サンプリングトランジスタと、前記第二の駆動トランジスタの前記ゲート及びドレイン間に接続された第二の閾値サンプリングトランジスタと、を有する。前記閾値サンプリングトランジスタは、ドレインから（電力供給ラインに接続されても良い）第一の容量への電流の供給を制御するために用いられる。従って、閾値サンプリングトランジスタをオンとすることによって、関連する第一の容量はゲート ソース間電圧まで充電され得る。

【0022】

更に、夫々の画素は、前記第一の容量配置の前記第一及び第二の容量間の前記接続点と前記表示素子との間に接続された第一の短絡トランジスタと、前記第二の容量配置の前記第一及び第二の容量間の前記接続点と前記表示素子との間に接続された第二の短絡トランジスタと、を有する。これらは、前記第一の容量が単独で前記駆動トランジスタのゲート ソース間電圧を蓄え得るように、前記第二の容量を短絡するために用いられる。

【0023】

更に、夫々の画素は、前記第一の駆動トランジスタのソース及び接地電位ラインの間に接続された第一のバイパストランジスタと、前記第二の駆動トランジスタのソース及び該接地電位ラインの間に接続された第二のバイパストランジスタと、を有する。これらは、表示素子を照射しないで、特に画素が系列をプログラミングする間に、駆動トランジスタからの電流に対して放出路として役割を果たすために用いられる。

10

20

30

40

50

## 【0024】

一つの望ましい配置において、第一及び第二の容量配置の第一及び第二の容量は、夫々の駆動トランジスタのゲート及びドレイン間に直列に接続され、夫々の駆動トランジスタのドレインは、異なる夫々の電力供給ラインに接続される。これは、高電圧ラインからのソース電流又は低電圧ラインへのドレイン電流に対する夫々の駆動トランジスタを可能にする。夫々の駆動トランジスタは、その時、選択的に、表示素子へ電流を供給するか、あるいは他の駆動トランジスタからの電流に対して放出経路を設けるように動かされ得る。この方法では、前記駆動トランジスタは、前記二つの駆動トランジスタに結合する回路構成要素の重複を減らす二つの機能を実行する。

## 【0025】

この補償配置において、前記二つの駆動トランジスタは夫々、閾値電圧及びデータ電圧を蓄えるための関連する容量配置を有する。他の実施例では、前記容量配置は共有され得る。この場合、更に夫々の画素は、前記第一及び第二の駆動トランジスタのゲートと接地ラインとの間に直列に接続された第一及び第二の容量を有する容量配置を有する。夫々の駆動トランジスタのソースは、夫々の制御ラインに接続され、前記画素へ入力されるデータは、該容量配置の該第一及び第二の容量間の前記接続点に供給される。

## 【0026】

その時、前記駆動トランジスタは独立な電源を有し、それらは電源制御ラインでオン又はオフとされ得る。望ましくは、更に、夫々の画素は、前記第二の容量の接続点に並列に接続された短絡トランジスタと、電力供給ラインと前記第一及び第二の駆動トランジスタのドレインとの間に接続された充電トランジスタと、を有する。更に、夫々の画素は、前記第一及び第二の駆動トランジスタのゲート及びドレイン間に接続された放電トランジスタを有しても良い。

## 【0027】

全ての実施例において、望ましくは、夫々の駆動トランジスタはNMOSトランジスタを有し、電界発光(EL)表示素子は電界リン光性の有機電界発光表示素子を有しても良い。

## 【0028】

本発明は、表示画素の配列を有するアクティブマトリクス電界発光表示装置を駆動する方法も提供し、それぞれの画素は、電界発光(EL)表示素子を有する。前記方法により、交互に、第一及び第二のアモルファスシリコン・駆動トランジスタを用いて該表示素子に電流を流し、駆動トランジスタは該表示素子に電流が流れていらない時に停止される。

## 【0029】

この方法は、二つの駆動トランジスタ間の表示素子の駆動を共有することによって経年変化の影響を減らす。

## 【0030】

望ましくは、駆動トランジスタは表示素子によって照射され、これがTFT特性の経年変化の影響を回復すると考えられる。

## 【0031】

更に経年変化の影響を減らすために、補償が前記第一及び第二の駆動トランジスタの閾値電圧の時間に渡る変化に対して実行される。

## 【0032】

この補償は、前記駆動トランジスタの一つを介して接地に電流を流し、第一の容量に結果として生じるゲート・ソース間電圧まで充電し、

該一つの駆動トランジスタがオフとなるまで該第一の容量を放電し、それによって該第一の容量は閾値電圧を蓄え、

該駆動トランジスタの該ゲートとソース又はドレインとの間の該第一の容量に直列である第二の容量をデータ入力電圧まで充電し、

該第一及び第二の容量にかかる電圧の組み合わせを有するゲート・ソース間電圧又はゲート・ドレイン間電圧を用いて、前記表示素子に電流を流す前記駆動トランジスタを使用

する、ことを特徴とする。

【0033】

駆動トランジスタの一つを介して接地に電流を流すステップは、他の駆動トランジスタを介して接地に電流を流すことを有し得る。この方法で、前記駆動トランジスタは二重機能を実行し得る。

【0034】

本発明を添付の図を参照して、例を用いて記述する。

【発明を実施するための最良の形態】

【0035】

同じ参照数字が異なる図で同じ構成要素に対して使われ、これら構成要素の記述は繰り返されない。 10

【0036】

本発明は、一つのTFTがLEDに電流を供給し、他のTFTがオフ状態であるように、一つ以上の現在供給中であるTFTを夫々の画素に設けることによって、アモルファスシリコンTFTの特性回復を提供する。それらTFTは、回復作用を高めるために照射されても良い。

【0037】

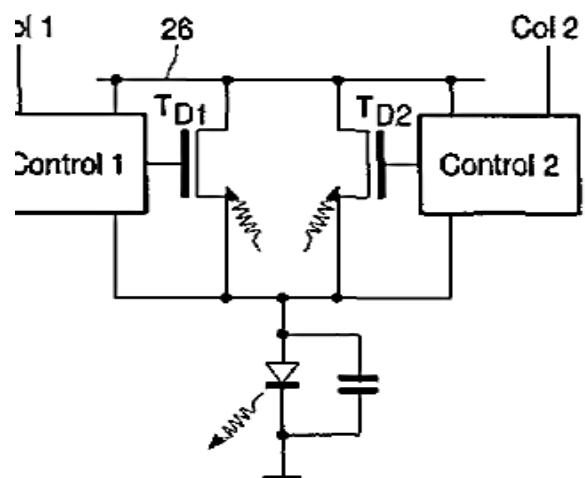

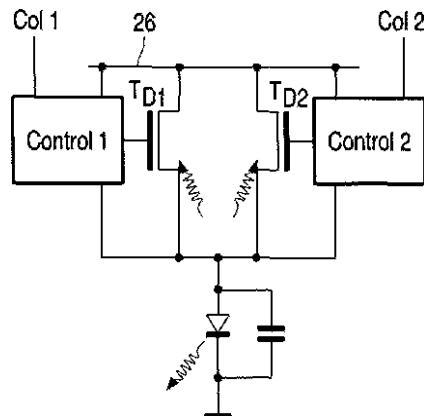

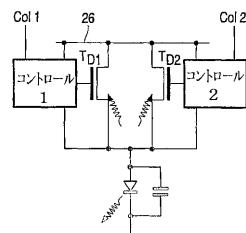

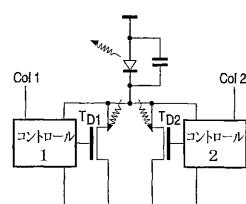

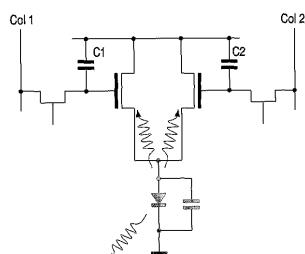

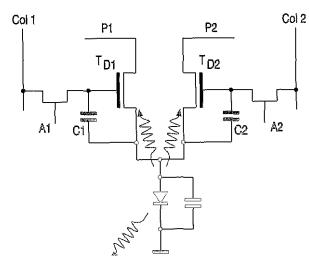

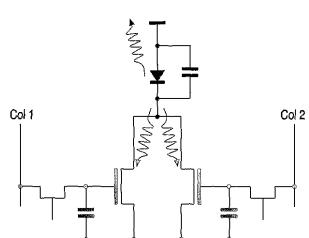

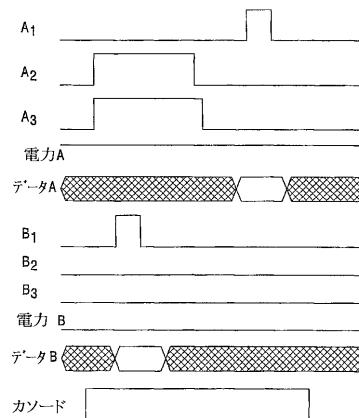

図3及び4は、本発明に基づく基本原理を図式的に説明する。

【0038】

図3は、LED表示素子のアノードを駆動する二つの駆動TFT( $T_{D1}$ 及び $T_{D2}$ )を示す。夫々の駆動トランジスタは、夫々の列ライン“Col1”及び“Col2”に沿ってデータ入力を受け取る夫々の制御回路“コントロール1”及び“コントロール2”によって制御される。図4はLED表示素子のカソードを駆動する二つの駆動TFT( $T_{D1}$ 及び $T_{D2}$ )を示す。これを実施するのは更に困難であるが、N型回路に更に適する。図3及び4は二つの駆動トランジスタを有する回路を図式的に示すが、二つ以上が使われ得る。 20

【0039】

図3において、夫々の制御回路は、共有の電力ライン26及び共用の表示素子2を駆動する夫々の回路を有する図2の標準的な画素配置の回路構成要素を単に有する。同様に、図4中の制御回路は、同じ画素回路に基づいても良い。

【0040】

図3及び4において、TFT  $T_{D1}$ がLEDに電流を流している時、TFT  $T_{D2}$ はスイッチを切られている。これらTFTの状態は、TFTのゲート、ドレイン及び共通のソースに接続された関連する回路によって制御される。 30

【0041】

好みい配置では、 $T_{D1}$ がLEDを光らせる時、その光の幾らかは駆動TFT  $T_{D1}$ 及び $T_{D2}$ 上に当たることが可能である。 $T_{D2}$ において、これは閾値電圧のドリフトの回復を可能にする。一つの時間期間後、制御は、 $T_{D2}$ が現在供給中であるTFTとなり、 $T_{D1}$ がオフされて回復することを許す。これは、ディスプレイの寿命の間中続く。結果として、二つの駆動TFTは、その時間のおおよそ半分で使用される。TFTが表示素子を駆動するために用いられない時、TFTは回復し得る。

【0042】

TFTの照射を供給することに代わって、あるいは同様に、負のゲートバイアスが、使用されていない駆動TFTに印加され得る。TFTをオフとするために必要とされるよりも大きい負のバイアスを供給することによって、TFT特性の回復率も高まり得る。 40

【0043】

上述の仕組みを実施するためには、閾値ゲート ソース間電圧以上の電圧が一つの駆動TFTに供給され、閾値ゲート ソース間電圧以下の電圧が他の駆動TFTに供給されるように、少なくとも夫々の駆動TFTのゲート又はソースを独立に制御することが可能でなければならない。

【0044】

図3及び4で示されるように、一つの可能な実施は、夫々の画素が二つのデータライン 50

を有するように、夫々の画素に付加的な列（データ）ラインを設ける。夫々の列ラインからのデータは、夫々一つの駆動TFTのゲートを駆動する。二つの駆動トランジスタの使用の所望の交代は、二つの列ラインの駆動信号を交互にすることによって達成される。

【0045】

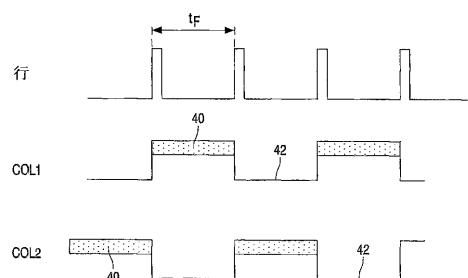

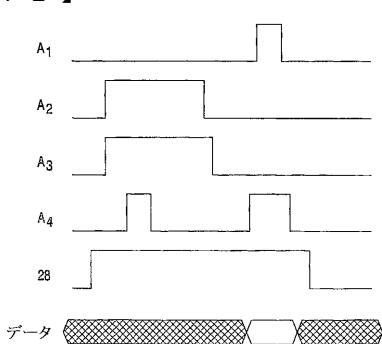

図5は、行ライン及び二つの列ラインに対する適切な駆動信号を示す。この例において、二つの駆動トランジスタの使用は交互表示フィールドで交互にされ、該フィールド期間は $t_F$ と示される。一つのフィールドで、 $T_{D1}$ はCol1のデータ信号によって駆動され、 $T_{D2}$ はオフ駆動レベルで駆動される。次のフィールドで、 $T_{D2}$ はCol2のデータ信号によって駆動され、 $T_{D1}$ はオフ駆動レベルで駆動される。その代わり、交代は一組のフィールド期間後であっても良い。

10

【0046】

領域40は、駆動TFTを制御するデータレベルの範囲を示し、電圧レベル42はトランジスタをオフとする。

【0047】

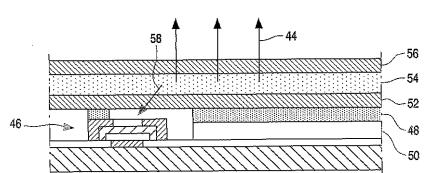

図3及び4は、表示素子による駆動トランジスタの照射を図式的に示す。これは、トップゲートTFT構造に対するITOゲートの使用によって、及び従来のボトムゲートから黒マスク層部分を移動させることによって達成される。画素での他の全てのTFTは、それらのゲートに結合する不透明の金属ゲート又は黒マスク層部分を有することによって、入射光から遮蔽されたままである。

20

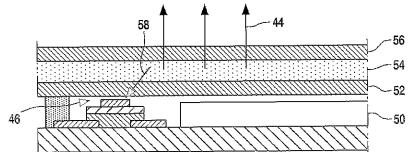

【0048】

図6は、ボトムゲートTFT46を有する表面放射構造（矢印44）を示す。黒マスク層48は、少なくとも夫々の駆動TFT（示されているうちの一つのみ）のゲートの上に開口を有する。黒マスク層は、画素の制御回路50の上に横たわっている。ITOアノード52、LED層54及びカソード56は、黒マスク層48の上に設けられる。矢印58は、駆動TFTの照射を表わす。

【0049】

図7は、トップゲートTFT46を有する表面放射構造を示す。夫々の駆動TFT（示されているうちの一つのみ）のゲートは透明であり、例えばITOから形成される。制御回路50の他のトランジスタは、不透明なゲート導電体を有する。ITOゲートが必要とされないように、光はゲート領域の外のアモルファスシリコン領域に十分に当たる。従って、ITOゲートは、照射されるべきTFTの一つの可能な実施である。

30

【0050】

底面放射構成も可能である。その中の開口は、光が入射し、基材を通り抜けるような回路にて形成される。

【0051】

照射されているアクティブ駆動TFTから生じる余分な漏れ電流は、電流がLSB電流の半分以下、例えば1nA以下に保たれるように設けられた表示レベルに影響を与えてはならない。

【0052】

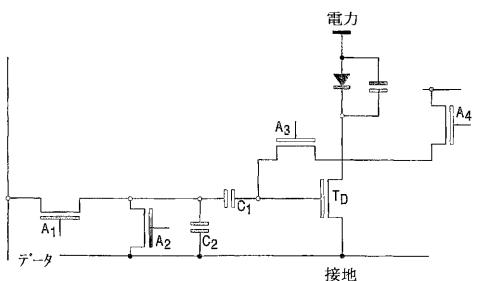

上述のように、夫々の制御回路は、図2の標準的な画素回路、又は実際にはNMOSトランジスタを用いる図2の変更されたものに対応可能である。図8は、NMOS画素回路を用いているが、本質的には図2の回路に対応する図3の配置を示す。

40

【0053】

図9は、代わりに、蓄積容量が、結合された駆動トランジスタのゲートと表示素子のアノードとの間に接続され得ることを示す。その時、夫々の駆動トランジスタは、夫々の電力ラインP1、P2によって供給される。

【0054】

この配置のアドレス指定系列は僅かに異なる。蓄積容量C1に電圧を蓄えるために、電力ラインP2は、接地に保たれ、P1はハイとなっている。容量C2は駆動トランジスタ $T_{D2}$ をオンとするような高い電圧まで充電され、それによって表示素子のアノードを低い電圧（電力ラインP2の電圧）で保持する。従って、 $T_{D1}$ のソース電圧は、データ電圧がC1に蓄えら

50

れる間、一定である。

【0055】

電圧がC1で蓄えられた後、アドレスラインA1は、容量C1からデータラインC0I1の接続を切るほど減じられる。その時、C2は、TD2をオフとするために、第二のアドレスラインA2によって零ボルトまで放電される。それから第二のアドレスラインは減じられ、二つのTFTのゲートは正確な動作レベルまで高くなる。動作は、回路の二つの側の間でやり取りされる。

【0056】

図10は、カソードが画素回路(図4で示されるような)に接続される画素に対して更なる可能な配置を示す。代わりに、容量は、TFTのゲートと共に表示素子のカソードの間に接続されても良い。

【0057】

閾値電圧のドリフトの回復に対する照射技術は完璧ではなく、閾値電圧でのドリフトが、十分により低いレベルでだが、依然起こることは非常にあり得る。従って、正確なグレースケールを達成することは、回路に含まれる閾値電圧の測定のための技術を必要とする。

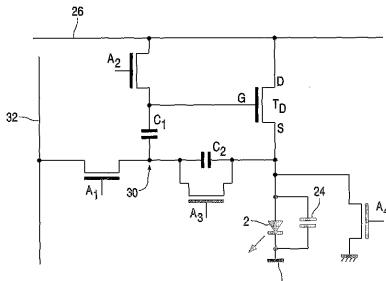

【0058】

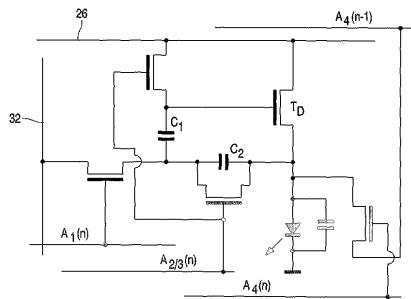

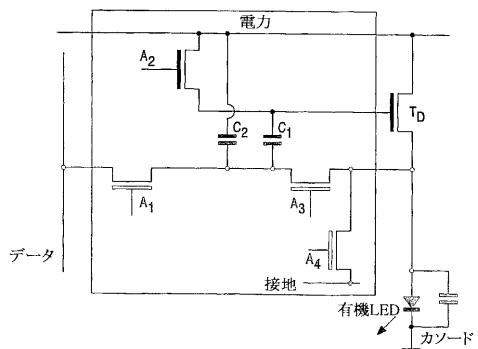

図11は、出願人によって提案された補償回路を示す。最初に、この回路の動作を記述する。次に、本発明によって二つ(又はそれ以上)の駆動トランジスタを有する単一な画素内で回路の重複を単純化するような回路の実施について検討する。夫々の画素は、電界発光(EL)表示素子2及び電力供給ライン26とカソードライン28との間に直列なアモルファスシリコン・駆動トランジスタTDを有する。駆動トランジスタTDは、表示素子2に電流を流す。

【0059】

第一及び第二の容量C1及びC2は、駆動トランジスタTDのゲートとソースとの間に直列に接続される。画素へのデータ入力は、第一及び第二の容量間の接続点30に供給され、以下で説明されるように、第二の容量C2を画素データ電圧まで充電する。第一の容量C1は、第一の容量C1に駆動トランジスタの閾値電圧を蓄える。

【0060】

入力トランジスタA1は、入力データライン32と第一及び第二の容量間の接続点30との間に接続される。この第一のトランジスタは、第二の容量C2への蓄積のため、画素に対するデータ電圧の適用の時間を決める。

【0061】

第二の入力トランジスタA2は、駆動トランジスタTDのゲート及びドレインの間に接続される。これは、電力供給ライン26から第一の容量C1への電流供給を制御するために使用される。従って、第二のトランジスタA2をオンとすることによって、第一の容量C1は駆動トランジスタTDのゲートソース間電圧を充電され得る。

【0062】

第三のトランジスタA3は、第二の容量C2の端子間に接続される。これは、第一の容量が単独で駆動トランジスタTDの閾値電圧を蓄え得るように、第二の容量を短絡するために用いられる。

【0063】

第四のトランジスタA4は、駆動トランジスタTDのソースと接地との間に接続される。これは、表示素子を照射しないで、特に画素が系列をプログラミングする間に、駆動トランジスタからの電流に対して放出路として役割を果たすために用いられる。

【0064】

容量24は、付加的な蓄積容量(図2の回路内のように)を有するか、あるいは、表示素子の自己静電容量を有しても良い。

【0065】

A1からA4のトランジスタは、それらのゲートに接続する夫々の行の導電体によって制御

10

20

30

40

50

される。更に以下で説明されるように、行の導電体の幾つかは共有されても良い。従って、複数の画素の配列のアドレス指定は画素の行のアドレス指定を有し、データライン32は、画素の全行が従来技術においてアドレス指定される行で同時にアドレス指定されるよう、列の導電体を有する。

【0066】

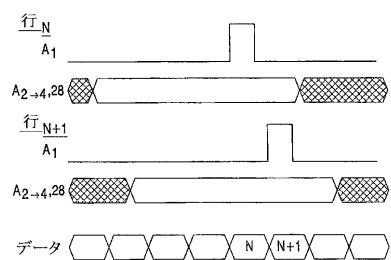

図11の回路は、多数の異なる方法で動作し得る。最初に基本的な動作を記述し、次にこれがパイプライン型のアドレス指定を提供するように拡張され得る方法を説明する。パイプライン型のアドレス指定手段には、隣接する行の制御信号間で重なり合うような、あるタイミングが存在する。

【0067】

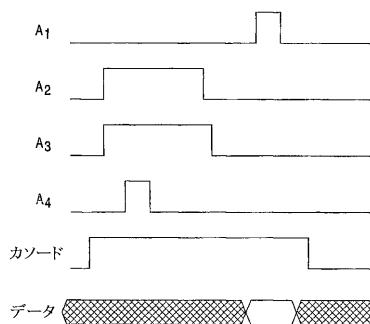

駆動トランジスタ $T_D$ のみが一定の電流状態で使用される。回路内の $A_1$ から $A_4$ の他の全てのTFTは、短いデューティーサイクルで動作するスイッチとして使用される。従って、これら素子の閾値電圧のドリフトは小さく、回路動作に影響を与えない。タイミング図が図12で示される。 $A_1$ から $A_4$ のプロットは、夫々のトランジスタに印加されるゲート電圧を表わす。プロット28は、カソードライン28に印加される電圧を表わし、プロット“データ”の透明部分はデータライン32でのデータ信号のタイミングを表わす。斜線領域は、データがデータライン32に存在しない時間を表わす。他の行の画素に対するデータは、データがデータライン32にほぼ連続的に印加され、パイプライン型の動作を与えるように、この時間の間印加され得ることが、以下の記述から明らかになる。

【0068】

回路動作は、駆動トランジスタ $T_D$ の閾値電圧を $C_1$ に蓄え、 $T_D$ のゲートソース間が閾値電圧を加えたデータ電圧であるように、データ電圧を $C_2$ に蓄えるべきである。

【0069】

該回路動作は、以下のステップを有する。

【0070】

ディスプレイの一つの行での画素のカソード（ライン28）は、アドレス指定系列の全体に渡って、LEDを逆バイアスに保つのに十分な電圧まで達する。これは、図12中のプロット“28”的正のパルスである。

【0071】

アドレスライン $A_2$ 及び $A_3$ は、関連するTFTをオンにするようにハイになる。これは、容量 $C_2$ を短絡し、容量 $C_1$ の一つの側を電力ライン及びLEDのアノード側の他のラインに接続する。

【0072】

アドレスライン $A_4$ は、そのTFTをオンとするようにハイになる。これは、LEDのアノードを接地に至らし、駆動TFT $T_D$ に大きなゲートソース間電圧を発生する。この方法で、 $C_1$ は充電されるが、 $C_2$ は短絡されたままで充電されない。

【0073】

アドレスライン $A_4$ はそのTFTをオフとするようにローになり、駆動TFT $T_D$ はその閾値電圧に到達するまで容量 $C_1$ を放電する。この方法で、駆動トランジスタ $T_D$ の閾値電圧は $C_1$ に蓄えられる。再び、第二の容量 $C_2$ には電圧がなくなる。

【0074】

$A_2$ は、第一の容量 $C_1$ で測定された閾値電圧を分離するようにローにされる。 $A_3$ は、第二の容量 $C_2$

がもはや短絡されないように、ローにされる。

【0075】

$A_4$ は、アノードを接地に接続するように再度ハイにされる。データ電圧は、入力トランジスタが $A_1$ での高いパルスによってオンとされる間、第二の容量 $C_2$ に印加される。

【0076】

最終的に、 $A_4$ は、接地まで下げられたカソードに引き続き、ローになる。LEDのアノードはその動作点まで上昇する。

10

20

30

40

50

## 【0077】

カソードは、 $A_2$ 及び $A_3$ がローにされた後、及び $A_4$ がハイにされる前に、交代に接地まで下げられ得る。

## 【0078】

アドレス指定系列は、画素の一つ以上の行がいずれか一つの時間でプログラミングされ得るように、パイプライン化され得る。従って、ライン $A_2$ から $A_4$ 及び行方向のカソードライン28でのアドレス指定信号は、異なる行に対して同じ信号で重なり得る。従って、アドレス指定系列の長さは長い画素のプログラミング時間を導かず、効率的なラインの時間は、アドレスライン $A_1$ がハイである時に第二の容量 $C_2$ を充電するのに必要とされる時間によってのみ制限される。この時間期間は、標準的なアクティブマトリクスのアドレス指定系列に対してと同じである。他の部分のアドレス指定は、フレーム時間全体がディスプレイの第一の少数の行を要求される状況によって僅かに長くされるに過ぎない。しかし、この状況はフレームが空白の期間内で容易に成されるので、閾値電圧の測定に対して必要とされる時間は問題ではない。

## 【0079】

パイプライン型アドレス指定は、図13のタイミング図で示される。トランジスタ $A_2$ から $A_4$ の制御信号は信号プロット内で組み合わされているが、動作は図11を参照して記述される通りである。図13中の“データ”的プロットは、データライン32が次の行にデータを供給するためにほぼ断続的に用いられる事を示す。

## 【0080】

図12及び13の方法で、閾値測定動作は、閾値測定及び表示が画素の各行に対して実行されるように、表示動作と組み合わされる。

## 【0081】

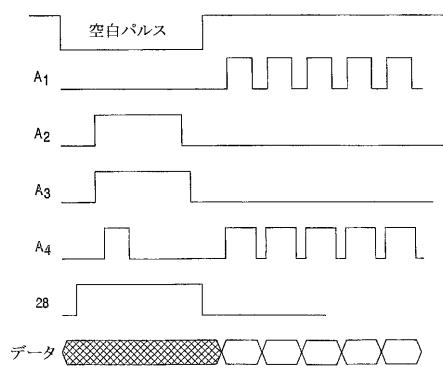

図14は、閾値電圧がディスプレイの全ての画素に対してフレームの始まりで測定される方法に関するタイミング図である。図14のプロットは、図12のそれらに対応する。このやり方の利点は、構造化されたカソード（即ち、図12及び13の方法の実施が必要とされるような異なる行に対する異なるライン28）が必要とされないことであるが、欠点は、漏れ電流が幾つかの不均一の結果として生じることである。この方法に関する回路図は、やはり図11のそれである。

## 【0082】

図14で示されるように、図14中の信号 $A_2$ 、 $A_3$ 、 $A_4$ 及びカソードライン28の信号は、閾値電圧の測定を実行する空白期間内で、ディスプレイの全ての画素に印加される。信号 $A_4$ は、 $A_2$ から $A_4$ の全ての信号が同時に全ての行に供給されるように、空白期間で同時にあらゆる画素に供給される。この時間の間、如何なるデータも画素に供給されず、故に図14の下のデータプロットの斜線部分となる。

## 【0083】

その後のアドレス指定期間において、データは、信号 $A_1$ であるように夫々の行に別々に供給される。図14中の $A_1$ でのパルスの系列は連続的な行に対するパルスを表わし、夫々のパルスはデータライン32へのデータの適用で決められる。

## 【0084】

図11の回路は、トランジスタの制御用及び構造カソードライン用（必要な場合）の多数の行を有する。図15は、必要とされる行の数を減らすような回路変更を示す。タイミング図は、信号 $A_2$ 及び $A_3$ が非常に相似であることを示す。シミュレーションは、実際には $A_2$ 及び $A_3$ は一つのアドレスラインのみが必要とされるように、作られ得ることを示す。更なる削減は、図11中のトランジスタ $A_4$ に結合されている接地ラインを前の行でアドレスライン $A_4$ に接続することによって実現され得る。図15の回路は行 $n$ 及び行 $n-1$ に対するアドレスラインを示す。

## 【0085】

複数の駆動TFTの補償と組み合わされる閾値電圧の回復を実行するために、補償回路があらゆる駆動TFTに対して繰り返される必要がある。制御回路の一つの部分が閾値電圧の

10

20

30

40

50

測定を実行するように構成され、加えられたデータを有する間、制御回路の他の部分は、駆動TFTがオフとされるように接続されることを確実にするように放電される容量を有する。

【0086】

上述される閾値補償回路は、多数の構成要素及び多数のアドレスラインを有し、そのため画素領域内に収まることが困難であり得る。

【0087】

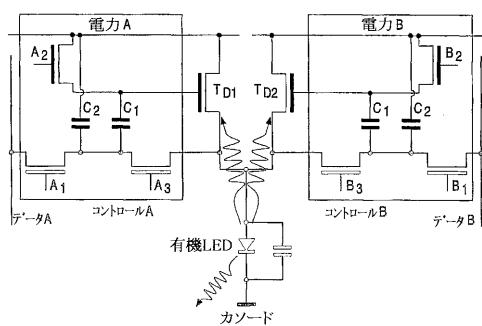

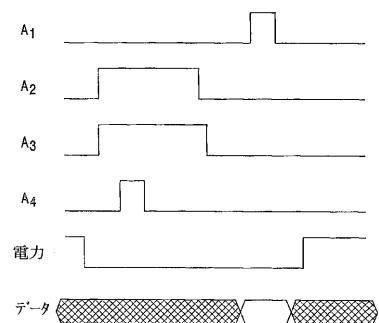

図16は、単一の画素内の回路の重複が単純化されるようにする、図11の回路に対する変更を示し、図18を参照して以下の記述から明らかになる。構成要素数は、TFTの幾つかが二重機能を有することを可能にすることによって減らされる。駆動TFTのソース又はゲートのどちらかの独立な制御が必要とされ、二つの駆動TFTの制御に用いられる全てのTFTは、これらTFTが幾つかの $V_T$ ドリフト補正自体を有していない場合、通常はオフ基準で動作しなければならない。即ち、低いデューティーサイクルを有していかなければならない。

10

【0088】

図11中でアドレスライン $A_4$ に接続されたTFTは、アドレス指定期間で駆動TFTによって供給される電流を流す必要があるので、大きい。従って、このTFTは、二重目的のTFTに対する理想的な候補、即ち駆動TFT及びアドレス指定TFTとして両方の動作をする一つのTFTである。残念ながら、図11で示される回路はこれを認めない。

20

【0089】

図16で、同じ参照数字は、図11の回路と同じ構成要素を示すために用いられるので、説明は繰り返さない。

【0090】

この回路において、第一及び第二の容量 $C_1$ 及び $C_2$ は、駆動トランジスタ $T_D$ のゲート及びドレインの間に直列に接続される。再び、画素への入力は、容量間の接続点に供給される。閾値電圧を蓄える第一の容量 $C_1$ は、駆動トランジスタのゲートと入力との間に接続される。データ入力電圧を蓄える第二の容量 $C_2$ は、画素入力と電力供給ライン（トランジスタのドレインは結合される）との間に直接的に結合される。制御ライン $A_3$ に接続されたトランジスタは、容量 $C_1$ が単独で閾値ゲート ソース間電圧を蓄えるために用いられるよう、再度、第二の容量 $C_2$ をバイパスする第一の容量 $C_1$ に充電経路を設ける。

30

【0091】

回路動作は図17で示され、以下のステップを有する。

【0092】

ディスプレイの一つの行での画素のカソードは、アドレス指定系列の全体に渡って、LEDを逆バイアスに保つのに十分な電圧に達する。

【0093】

アドレスライン $A_2$ 及び $A_3$ は、関連するTFTをオンとするようにハイになる。これは電力ラインに $C_1$ 及び $C_2$ の並列結合を接続する。

【0094】

アドレスライン $A_4$ は、そのTFTをオンとするようにハイになる。これは、LEDのアノードを接地に至らし、駆動TFT  $T_D$ で大きなゲート ソース間電圧を発生する。

40

【0095】

アドレスライン $A_4$ は、TFTをオフとするようにローになる。駆動TFT  $T_D$ は、その閾値電圧に到達するまで並列容量 $C_1 + C_2$ を放電する。

【0096】

$A_2$ 及び $A_3$ は、測定された閾値電圧を分離するようにローになる。

【0097】

$A_1$ はオンとされ、データ電圧は容量 $C_1$ に蓄えられる。

【0098】

最終的に、 $A_4$ は、接地に落とされたカソードに引き続いてローになる。

50

## 【0099】

再度、空白期間でのパイプライン型アドレス指定及び閾値の測定は、上記で説明されたように、この回路で実行され得る。

## 【0100】

電圧  $V_{data} - V_T$  は、このようにして駆動TFTのゲート - ドレイン間で蓄えられる。従って、以下の式

## 【0101】

## 【数1】

$$I = \frac{\beta}{2} (V_{gs} - V_T)^2 = \frac{\beta}{2} (V_{ds} - V_{dg} - V_T)^2 = \frac{\beta}{2} (V_{ds} - V_{data})^2$$

10

が成り立つ。

## 【0102】

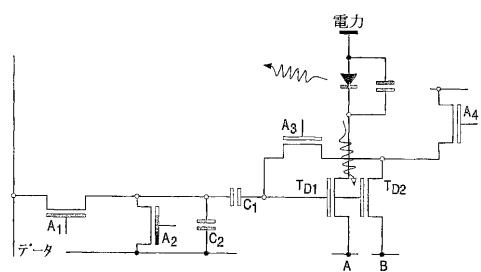

故に、閾値電圧依存は取り去られる。今は電流がLEDのアノード電圧に依存することがわかる。この回路に基づく照射による回復を有する閾値電圧測定回路は図18で示され、タイミング図は図19で示される。

## 【0103】

$T_{D1}$  が駆動し、 $T_{D2}$  が回復すると仮定すると、回路の左側は、既に述べたように機能し、回路の右側は、図16で  $A_4$  に接続されたTFTの機能、即ち、アノードを接地に引っ張るよう に機能しなければならない。これを達成するために、電力ラインBは接地でなければならず、アドレスライン  $B_2$  及び  $B_3$  はローでなければならず、 $B_1$  は、 $T_{D1}$  のアドレス指定相で必要とされる時、アノードを接地に接続するために  $T_{D2}$  のゲートをハイにするように、データラインBと共にハイにならなければならない。

20

## 【0104】

回路はLEDに関して対称であるから、信号は、 $T_{D1}$  が回復中で、 $T_{D2}$  が駆動中である時、回路の両側の間で、単純にやり取りされる。パイプライン型の信号は、空白期間内での  $V_T$  の測定のように、依然として可能である。

## 【0105】

上述の回路は、依然としてむしろ多数の構成要素（駆動TFTの独立なゲート及びソースによる）を有する。ただ一つの独立なノード、即ちソース又はゲートを有する回路は、構成要素の数を更に少なくする。以下で、回路は、LEDのカソード側での回路を使用し、回復を有する閾値電圧の測定回路を達成するために独立なソース電圧を使用することが記述される。最初に、单一な閾値電圧の測定回路を、図20を参照して記述し、図21でタイミング図を示す。

30

## 【0106】

図20の回路で、夫々の画素は、駆動トランジスタ  $T_D$  のゲート及び接地ラインの間に直列に接続された第一及び第二の容量  $C_1$ 、 $C_2$  を有する。駆動トランジスタのソースは、接地ラインに接続されるが、二つの回路が組み合わされる時、夫々の駆動トランジスタのソースは夫々の制御ラインに接続される。画素へ入力されるデータは、第一及び第二の容量の間の接続点に供給される。

40

## 【0107】

短絡トランジスタは、第二の容量  $C_2$  の端子間に接続され、ライン  $A_2$  によって制御される。前の回路と同じように、これは、ゲート - ソース間電圧が容量  $C_2$  をバイパスする容量  $C_1$  で蓄えられる。制御ライン  $A_4$  に結合されている充電トランジスタは、電力供給ライン50と駆動トランジスタ  $T_D$  のドレインとの間に接続される。これは、容量  $C_1$  に対する充電経路を設けられると共に、放電トランジスタは制御ライン  $A_3$  に結合され、駆動トランジスタのゲート及びドレインの間に接続される。

## 【0108】

回路は  $A_2$  及び  $A_3$  をハイに保つことによって動作し、その時  $A_4$  は、カソードをハイに引っ張り、容量  $C_1$  を高いゲート - ソース間電圧まで充電するように、絶えずハイに保たれる。

50

電力ラインは、LEDのバイアスを逆にするように接地の位置にある。 $T_D$ は、その閾値電圧まで放電し（ライン $A_3$ に結合されている放電トランジスタはオンにされる）、それは $C_1$ に蓄えられる。 $A_2$ 及び $A_3$ はローにされ、 $A_1$ はハイにされ、データは $C_2$ にアドレス指定される。電力ラインは、LEDを光らせるために再びハイにされる。

【0109】

再度、アドレス指定系列はパイプライン化され、閾値電圧はフィールド空白期間で測定される。

【0110】

独立なソースを有する回復回路の構成は、両方の駆動TFTがそれら自体の接地ラインを有することを必要とする。 $C_2$ に接続された余分な容量ラインもまた必要とされる。回復回路は図22で示される。

【0111】

この回路において、容量は両トランジスタ間で共有され、回路の他のトランジスタは重複される必要がない。夫々の駆動トランジスタは、カソードに接続された結合制御ラインA、Bを有する。

【0112】

動作は、上述された動作と非常に相似であり、図21で示される。しかし、ラインA又はBのどちらか一方は、関連する駆動TFTをそれが回復状態にある時にオフとするような電位である必要がある。駆動TFTが同様の閾値電圧を有すると仮定すると、ラインA及びBの電圧の差はデータ電圧範囲である必要があり、これは、夫々の駆動TFTの状態が駆動から回復まで変化するように明らかにやり取りする。

【0113】

回路は現在のところ利用可能なLED装置に対して用いられ得る。しかし、電界発光（EL）表示素子は、電界リン光性の有機電界発光表示素子を有する。本発明は、アクティブマトリクス有機LEDディスプレイに対するa-Si:Hの使用を可能にする。

【0114】

上述の回路は、NMOSトランジスタのみで実施されることが示されており、これらトランジスタは全てアモルファスシリコン素子である。NMOS素子の製造はアモルファスシリコンにおいて望ましく、他に取り得る回路は勿論PMOS素子で実行される。

【0115】

上述の好ましい実施例において、二つの駆動トランジスタが存在する。夫々の画素は三つ又はそれ以上の駆動トランジスタを有しても良く、補償回路は、可能であれば回路構成要素を共有しながら、夫々の駆動トランジスタに対して再び設けられても良いことが理解される。

【0116】

様々な他の変更は、当業者にとって明白である。

【図面の簡単な説明】

【0117】

【図1】既知のEL表示装置を示す。

【図2】入力駆動電圧を用いて、現在扱っているEL表示装置用の既知の画素回路の概略図である。

【図3】本発明に基づく基本原理を図式的に説明する図である。

【図4】本発明に基づく基本原理を図式的に説明する図である。

【図5】図3及び4の画素配置を動かすために適した駆動信号を示す。

【図6】駆動TFTの照射を示している表面放射構造のボトムゲートTFTを示す。

【図7】駆動TFTの照射を示している表面放射構造のトップゲートTFTを示す。

【図8】図3の配置を実施する第一の方法を更に詳細に示す。

【図9】図3の配置を実施する第二の方法を更に詳細に示す。

【図10】図4の配置を実施する第一の方法を更に詳細に示す。

【図11】本発明の閾値電圧の補償を有する画素配置の第一の例の概略図を示す。

10

20

30

40

50

【図12】図11の画素配置の第一の動作方法に関するタイミング図である。

【図13】図11の画素配置の第二の動作方法に関するタイミング図である。

【図14】図11の画素配置の第三の動作方法に関するタイミング図である。

【図15】図11の回路に対する変更を示す。

【図16】本発明の閾値電圧の補償を有する画素配置の第二の例の概略図を示す。

【図17】図16の画素配置の動作のタイミング図である。

【図18】図16の回路の二つが单一の画素内で結合される様子を示す。

【図19】図18の画素配置の動作のタイミング図である。

【図20】本発明の閾値電圧の補償を有する画素配置の第三の例の概略図を示す。

【図21】図20の画素配置の動作のタイミング図である。

【図22】図20の回路の二つが单一の画素内で結合される様子を示す。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

FIG.6

【図7】

FIG.7

【図8】

FIG.8

【図9】

FIG.9

【図11】

FIG.11

【図10】

FIG.10

【図12】

データ

【図13】

【図14】

【図15】

FIG.15

【図16】

【図17】

【図18】

【図19】

【図20】

【図2-1】

【図2-2】

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                        | PCT/IB2004/000158                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 G09G3/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                        |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                        |                                                                                |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 G09G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                        |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                        |                                                                                |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal, PAJ, WPI Data, INSPEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                        |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                        |                                                                                |

| Category                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                     | Relevant to claim No.                                                          |

| X<br>A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | US 2002/047555 A1 (INUKAI KAZUTAKA)<br>25 April 2002 (2002-04-25)<br><br>paragraph '0134!<br>paragraph '0142! – paragraph '0161!<br>paragraph '0367! – paragraph '0368!<br>figures 2-4 | 1,2,4,6,<br>18,19<br>21                                                        |

| X<br>A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | WO 02/17289 A (EMAGIN CORP)<br>28 February 2002 (2002-02-28)<br><br>page 6, line 3 – line 21<br>page 8, line 10 – line 24<br>figures 1-3                                               | 1,20<br>21                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                        | —/—                                                                            |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                        | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| <p>* Special categories of cited documents:</p> <p>*A* document defining the general state of the art which is not considered to be of particular relevance</p> <p>*E* earlier document but published on or after the International filing date</p> <p>*L* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)</p> <p>*O* document referring to an oral disclosure, use, exhibition or other means</p> <p>*P* document published prior to the International filing date but later than the priority date claimed</p> <p>*T* later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</p> <p>*X* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</p> <p>*Y* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.</p> <p>*&amp;* document member of the same patent family</p> |                                                                                                                                                                                        |                                                                                |

| Date of the actual completion of the international search<br><br>29 April 2004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                        | Date of mailing of the international search report<br><br>17/05/2004           |

| Name and mailing address of the ISA<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                        | Authorized officer<br><br>Farricella, L                                        |

## INTERNATIONAL SEARCH REPORT

PCT/IB2004/000158

## C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT

| Category * | Citation of document, with indication, where appropriate, of the relevant passages                                                    | Relevant to claim No. |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| P, X       | EP 1 296 310 A (SEMICONDUCTOR ENERGY LAB)<br>26 March 2003 (2003-03-26)<br>paragraph '0272! - paragraph '0276!<br>figure 24A<br>----- | 1                     |

| INTERNATIONAL SEARCH REPORT            |                  |                         |               | PCT/IB2004/000158 |  |

|----------------------------------------|------------------|-------------------------|---------------|-------------------|--|

| Patent document cited in search report | Publication date | Patent family member(s) |               | Publication date  |  |

| US 2002047555 A1                       | 25-04-2002       | CN                      | 1323023 A     | 21-11-2001        |  |

|                                        |                  | EP                      | 1111574 A2    | 27-06-2001        |  |

|                                        |                  | JP                      | 2001242827 A  | 07-09-2001        |  |

|                                        |                  | TW                      | 493152 B      | 01-07-2002        |  |

|                                        |                  | US                      | 2003146712 A1 | 07-08-2003        |  |

| WO 0217289 A                           | 28-02-2002       | AU                      | 8510101 A     | 04-03-2002        |  |

|                                        |                  | WO                      | 0217289 A1    | 28-02-2002        |  |

|                                        |                  | US                      | 2002044110 A1 | 18-04-2002        |  |

| EP 1296310 A                           | 26-03-2003       | CN                      | 1409289 A     | 09-04-2003        |  |

|                                        |                  | EP                      | 1296310 A2    | 26-03-2003        |  |

|                                        |                  | JP                      | 2004054200 A  | 19-02-2004        |  |

|                                        |                  | JP                      | 2004054203 A  | 19-02-2004        |  |

|                                        |                  | US                      | 2003058687 A1 | 27-03-2003        |  |

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 09 F 9/30 365Z

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NA,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(74)代理人 100107766

弁理士 伊東 忠重

(72)発明者 ディーン,スティーヴン シー

イギリス国,サリー アールエイチ1 5エイチエイ,レッドヒル,クロス・オーク・レーン,フィリップス インテレクチュアル プロパティ アンド スタンダーズ内(番地なし)

(72)発明者 フィッシュ,デイヴィッド エイ

イギリス国,サリー アールエイチ1 5エイチエイ,レッドヒル,クロス・オーク・レーン,フィリップス インテレクチュアル プロパティ アンド スタンダーズ内(番地なし)

(72)発明者 ナップ,アラン ジー

イギリス国,サリー アールエイチ1 5エイチエイ,レッドヒル,クロス・オーク・レーン,フィリップス インテレクチュアル プロパティ アンド スタンダーズ内(番地なし)

F ターム(参考) 5C080 AA06 BB05 DD05 DD29 EE29 FF11 HH09 JJ02 JJ03 JJ04

JJ06

5C094 AA04 AA23 BA03 BA27 DA20

|                |                                                                                                                                                                                         |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵电致发光显示装置                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP2006518473A</a>                                                                                                                                                           | 公开(公告)日 | 2006-08-10 |

| 申请号            | JP2006500309                                                                                                                                                                            | 申请日     | 2004-01-20 |

| [标]申请(专利权)人(译) | 皇家飞利浦电子股份有限公司                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 皇家飞利浦电子股份有限公司的Vie                                                                                                                                                                       |         |            |

| [标]发明人         | ディーンスティーヴンシー<br>フィッシュデイヴィッドエイ<br>ナップアランジー                                                                                                                                               |         |            |

| 发明人            | ディーン,スティーヴン シー<br>フィッシュ,デイヴィッド エイ<br>ナップ,アラン ジー                                                                                                                                         |         |            |

| IPC分类号         | G09G3/30 G09G3/20 G09F9/30 H01L27/32 G09G3/32                                                                                                                                           |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0417 G09G2300/0809 G09G2300/0819 G09G2300/0852 G09G2300/0861<br>G09G2300/0866 G09G2310/0251 G09G2310/0254 G09G2310/0256 G09G2310/063 G09G2320/043                   |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.641.C G09G3/20.670.J G09F9/30.338 G09F9/30.365.Z                                                                                                     |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD29 5C080/EE29 5C080/FF11 5C080/HH09 5C080/<br>/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C094/AA04 5C094/AA23 5C094/BA03 5C094/BA27<br>5C094/DA20 |         |            |

| 代理人(译)         | 伊藤忠彦                                                                                                                                                                                    |         |            |

| 优先权            | 2003001623 2003-01-24 GB                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                               |         |            |

## 摘要(译)

有源矩阵显示装置的每个像素具有用于间歇地将电流流到显示元件的第一非晶硅晶体管和用于间歇地使电流流过显示元件的第二非晶硅晶体管。通过在两个驱动晶体管之间共用显示元件，可以减小非晶硅TFT的长期变化的影响。提供占空比减少了每个驱动晶体管的导通时间，但也提供了一些可以在某种程度上恢复TFT特性的周期。