(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-126779

(P2006-126779A)

(43) 公開日 平成18年5月18日(2006.5.18)

(51) Int.CI.

**G09G 3/30 (2006.01)**

**G09G 3/20 (2006.01)**

**H01L 51/50 (2006.01)**

F 1

GO9G 3/30 K 3K007

GO9G 3/30 J 5C080

GO9G 3/20 612F

GO9G 3/20 624B

GO9G 3/20 641A

テーマコード(参考)

審査請求 有 請求項の数 9 O L (全 18 頁) 最終頁に続く

(21) 出願番号 特願2005-166024 (P2005-166024)

(22) 出願日 平成17年6月6日 (2005.6.6)

(31) 優先権主張番号 特願2004-288030 (P2004-288030)

(32) 優先日 平成16年9月30日 (2004.9.30)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2004-288039 (P2004-288039)

(32) 優先日 平成16年9月30日 (2004.9.30)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100079108

弁理士 稲葉 良幸

(74) 代理人 100080953

弁理士 田中 克郎

(74) 代理人 100093861

弁理士 大賀 真司

(72) 発明者 原 弘幸

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 3K007 AB17 AB18 BA06 DB03 GA00

GA04

最終頁に続く

(54) 【発明の名称】画素回路、画素駆動方法及び電子機器

## (57) 【要約】

【課題】制御動作や回路構成をより簡素に構成することを可能とする電気光学装置の駆動回路、駆動方法及び電子機器を提供する。

## 【解決手段】

本発明の画素回路は、電気光学素子OLEDを発光させる画素回路20において、電気光学素子の駆動電流路に挿入されるトランジスタTECTと、駆動電流路の電流値を設定する電流値設定回路21と、供給される画素信号のレベルを記憶するレベル保持手段CSDと、記憶された画素信号レベルと供給される傾斜レベル信号VREFとを比較し、比較結果に基づいてトランジスタTECTの動作を制御する比較回路23と、を備える。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

電気光学素子を発光させる画素回路であって、

前記電気光学素子の駆動電流路に挿入されるトランジスタと、

前記駆動電流路の電流値を設定する電流値設定回路と

供給される画素信号のレベルを記憶するレベル保持手段と、

記憶された画素信号レベルと供給される傾斜レベル信号とを比較し、比較結果に基づいて前記トランジスタの動作を制御する比較回路と、

を備える画素回路。

**【請求項 2】**

電気光学素子を発光させる画素回路であって、

前記電気光学素子の駆動電流路に挿入されるトランジスタと、

前記駆動電流路の電流値を設定する電流値設定回路と、

時間軸上において先行する一連の画素信号からなる画素列信号部分と、これに後続する傾斜レベル信号部分とを含む複合信号から、1つの画素信号を抽出してそのレベルと後続の傾斜レベル信号とをレベル比較し、比較結果に基づいて前記トランジスタの動作時間を制御する比較回路と、

を備える画素回路。

**【請求項 3】**

前記電流値設定回路は、前記駆動電流路に挿入される駆動トランジスタと、前記駆動トランジスタに所定値の電流を供給する電流供給源と、前記駆動トランジスタに前記所定値の電流を供給したときの該駆動トランジスタのゲート電圧を保持するキャパシタと、を含む請求項1又は2に記載の画素回路。

**【請求項 4】**

前記電気光学素子は有機EL発光素子である、請求項1乃至3のいずれかに記載の画素回路。

**【請求項 5】**

請求項1乃至4のいずれかに記載の画素回路を画像表示器に含む電子機器。

**【請求項 6】**

基板上に二次元に配置された複数の画素を発光させる画素駆動方法であって、

予め各画素に供給する電流レベルを設定する過程と、

各画素が表示すべき画素信号を各画素の領域に記憶する過程と、

供給される傾斜レベル信号と各画素の画素信号のレベルとを比較して前記電流レベルによる各画素の発光時間を制御する過程と、

を含む画素駆動方法。

**【請求項 7】**

画素を発光させる画素駆動方法であって、

予め画素に供給する電流レベルを設定する過程と、

前記画素が表示すべき画素信号を記憶する過程と、

供給される傾斜レベル信号と前記画素の画素信号とを比較して前記電流レベルによる前記画素の発光時間を制御する過程と、

を含む画素駆動方法。

**【請求項 8】**

基板上に二次元に配置された複数の電気光学素子を発光させる画素駆動方法であって、

予め各電気光学素子に供給する電流レベルを設定する過程と、

時間軸上において先行する一連の画素信号からなる画素列信号部分とこれに後続する傾斜レベル信号部分とを含む複合信号から各電気光学素子の配置領域に対応する画素信号を選択してそのレベルを記憶する過程と、

各電気光学素子の配置領域にそれぞれ対応付けられた各画素信号のレベルと供給される傾斜レベル信号とを比較して前記電流レベルによる各電気光学素子の発光時間を制御する

過程と、

を含む画素駆動方法。

【請求項 9】

電気光学素子を発光させる画素駆動方法であって、

予め前記電気光学素子に供給する電流レベルを設定する過程と、

時間軸上において先行する一連の画素信号からなる画素列信号部分と、これに後続する

傾斜レベル信号部分とを含む複合信号から、1つの画素信号を抽出してそのレベルを記憶

する過程と、

記憶された前記画素信号のレベルと前記傾斜レベル信号とをレベル比較して設定された

前記電流レベルによる前記電気光学素子の発光時間を制御する過程と、

を含む画素駆動方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像を形成する電気光学装置の画素回路、電気光学装置の画素回路の駆動方法及び電気光学装置を用いた電子機器に関する。

【背景技術】

【0002】

電気光学装置としては、液晶表示装置や有機EL（エレクトロルミネセンス）表示装置などが知られている。有機EL表示装置は、画素を構成する電気光学素子が有機EL材料からなり、自然光、広視野角、薄型、高速応答、低消費電力といった優れた特徴を備えると共に、ポリシリコン TFT（薄膜トランジスタ）を用いた周辺回路により、更なる小型化、軽量化が実現できることから注目されている。

【0003】

ところで、この種の有機EL表示装置は画素間の輝度のバラツキがあり、これを抑制するために、電流プログラム方式をはじめとする種々の駆動方式が提案されている（例えば、特許文献1）。

【特許文献1】米国特許第6229506B1号明細書

30

【発明の開示】

【発明が解決しようとする課題】

【0004】

電流プログラム方式は、TFTの飽和領域でTFTを動作させているため、TFT及び有機EL発光素子（以下、「OLED」という。）の特性のバラツキを補償出来るという特徴を持つ。

【0005】

しかしながら、従来の電流プログラム方式では、低階調領域における書きの不足や、駆動トランジスタの動作点の変動によるOLEDへの供給電流の変化によって階調ずれが発生するという不具合があった。

【0006】

そこで、本出願人は「電流プログラム型時間階調方式」（特願2003-367501号）を提案した。

【0007】

この技術は、保持キャパシタ、駆動トランジスタ、電気光学素子を有した画素に対してデータ電流を供給し、そのデータ電流の値に応じて駆動トランジスタから供給される駆動電流に基づいて電気光学素子が駆動される電気光学素子の駆動方法において、入力した階調データに関係なく、予め定められた一定の値のデータ電流を上記画素に供給して上記電気光学素子を駆動させるステップと、階調データに基づいて前記電気光学素子の駆動時間を設けたものである。それにより、書き不足、動作点変動は解消可能となる。

40

50

**【 0 0 0 8 】**

しかしながら、上記提案の技術を実際のOLED表示パネルに使用する場合、表示パネルを構成する、各画素に対して発光時間を個々の画素毎に制御しなければならず制御動作や回路構成が複雑である。

**【 0 0 0 9 】**

よって、本発明は制御動作や回路構成をより簡素に構成することを可能とする電気光学装置の駆動回路、駆動方法及び電子機器を提供することを目的とする。

**【課題を解決するための手段】****【 0 0 1 0 】**

上記目的を達成するため本発明の画素回路は、電気光学素子を発光させる画素回路において、上記電気光学素子の駆動電流路に挿入されるトランジスタと、上記駆動電流路の電流値を設定する電流値設定回路と、供給される画素信号のレベルを記憶するレベル保持手段と、記憶された画素信号レベルと供給される傾斜レベル信号とを比較し、比較結果に基づいて上記トランジスタの動作を制御する比較回路と、を備える。10

**【 0 0 1 1 】**

また、本発明の画素回路は、電気光学素子を発光させる画素回路において、上記電気光学素子の駆動電流路に挿入されるトランジスタと、上記駆動電流路の電流値を設定する電流値設定回路と、時間軸上において先行する一連の画素信号からなる画素列信号部分と、これに後続する傾斜レベル信号部分とを含む複合信号から、1つの画素信号を抽出してそのレベルと後続の傾斜レベル信号とをレベル比較し、比較結果に基づいて上記トランジスタの動作時間を制御する比較回路と、を備える。20

**【 0 0 1 2 】**

好ましくは、上記電流値設定回路は、上記駆動電流路に挿入される駆動トランジスタと、上記駆動トランジスタに所定値の電流を供給する電流供給源と、上記駆動トランジスタに上記所定値の電流を供給したときの該駆動トランジスタのゲート電圧を保持するキャパシタと、を含む。

**【 0 0 1 3 】**

好ましくは、上記電気光学素子は有機EL発光素子である。

**【 0 0 1 4 】**

また、本発明の電子機器は、上述した画素回路を画像表示器に含むことを特徴とする。30

**【 0 0 1 5 】**

本発明の画素駆動方法は、基板上に二次元に配置された複数の画素を発光させる画素駆動方法において、予め各画素に供給する電流レベルを設定する過程と、各画素が表示すべき画素信号を各画素の領域に記憶する過程と、供給される傾斜レベル信号と各画素の画素信号のレベルとを比較して上記電流レベルによる各画素の発光時間を制御する過程と、を含む。

**【 0 0 1 6 】**

また、本発明の画素駆動方法は、画素を発光させる画素駆動方法において、予め画素に供給する電流レベルを設定する過程と、上記画素が表示すべき画素信号を記憶する過程と、供給される傾斜レベル信号と上記画素の画素信号とを比較して上記電流レベルによる上記画素の発光時間を制御する過程と、を含む。40

**【 0 0 1 7 】**

また、本発明の画素駆動方法は、基板上に二次元に配置された複数の電気光学素子を発光させる画素駆動方法において、予め各電気光学素子に供給する電流レベルを設定する過程と、時間軸上において先行する一連の画素信号からなる画素列信号部分とこれに後続する傾斜レベル信号部分とを含む複合信号から各電気光学素子の配置領域に対応する画素信号を選択してそのレベルを記憶する過程と、各電気光学素子の配置領域にそれぞれ対応付けられた各画素信号のレベルと供給される傾斜レベル信号とを比較して上記電流レベルによる各電気光学素子の発光時間を制御する過程と、を含む。

**【 0 0 1 8 】**

10

20

30

40

50

また、本発明の画素駆動方法は、電気光学素子を発光させる画素駆動方法において、予め上記電気光学素子に供給する電流レベルを設定する過程と、時間軸上において先行する一連の画素信号からなる画素列信号部分と、これに後続する傾斜レベル信号部分とを含む複合信号から、1つの画素信号を抽出してそのレベルを記憶する過程と、記憶された上記画素信号のレベルと上記傾斜レベル信号とをレベル比較して設定された上記電流レベルによる上記電気光学素子の発光時間を制御する過程と、を含む。

【発明の効果】

【0019】

本発明では、電流プログラム方式を用いた時分割駆動方式において、画素の発光時間制御として比較手段（コンパレータ回路）を使用する構成としたので、煩雑な制御動作が回避可能となる。

【0020】

また、本発明では、電流プログラム方式を用いた時分割駆動方式において、画素の発光時間制御として一入力型の比較手段（コンパレータ回路）を使用する構成としたので、煩雑な制御動作が回避可能となる。また、画素回路を構成する素子数及び配線数を減少することが可能となる。

【発明を実施するための最良の形態】

【0021】

本発明においては、電気光学素子の画素を駆動するに際して、電流プログラム方式によって予め各画素に供給する電流レベルを設定し、更に、各画素が表示すべき画素信号を各画素の領域に記憶しておく。次に、全画素に傾斜レベル信号を供給し、各画素の画素信号のレベルと比較する。その結果に基づいて予め設定した電流レベルによる各画素の発光時間を制御する。それにより、比較的に簡素な制御手順によって作動する多階調の表示器を得ることが可能となる。

【実施例1】

【0022】

以下、本発明の実施例について図面を参照しつつ説明する。

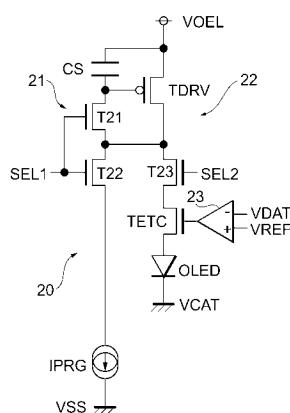

【0023】

図1は、本発明の電気光学装置の一例である有機EL表示装置の電気的接続を示すプロック回路図である。同図において、有機EL表示装置10はデータドライバ部11、走査ドライバ部12及びアクティブマトリクス部13を備えている。アクティブマトリクス部13は後述の画素回路20をマトリクス状に複数配置して構成されている。データドライバ部11は各画素回路20に画像の各画素の輝度に相当するアナログデータ信号VDATを供給する。走査ドライバ部12は各行の各画素回路20に書き込み選択信号SEL1及び発光時選択信号SEL2を供給する。また、各画素回路20は図示しない信号源から一定のプログラム電流IPRG及び参照電位VREFの供給を受け、電源からOLEDの電源電圧VOELの供給を受けている。

【0024】

後述のように、走査ドライバ部12によってアクティブマトリクス部13の各行の画素回路群が順次選択され、各行の画素回路群にデータドライバ部によって発光時間に相当する信号レベルVDATが書き込まれる。各画素回路に保持された信号レベルVDATと各画素回路に供給される傾斜電圧レベルVREFの比較によって画素であるOLEDの発光時間が決定される。

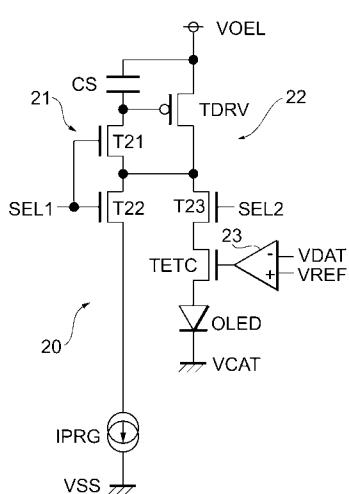

【0025】

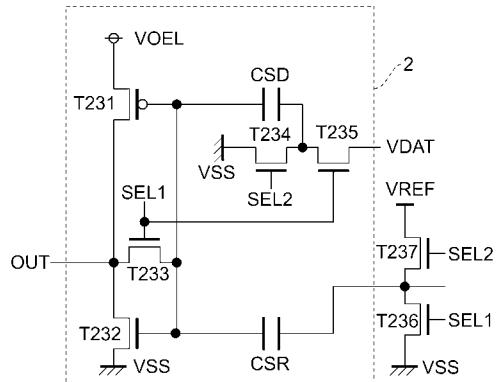

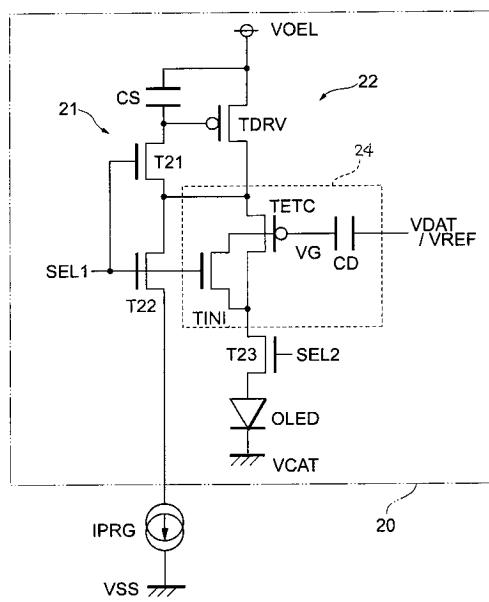

図2は、上述した画素回路20の構成例を示している。画素回路20は、電流プログラムを実現するための電流プログラム回路21、OLEDを駆動する駆動回路22、コンパレータ回路23によって構成されている。各回路で称されるトランジスタは薄膜トランジスタ(TFT)である。

【0026】

電流プログラム回路21は、有機EL電源電圧VOELとプログラム電流源IPRGと

10

20

30

40

50

の間に直列に接続された保持容量CS、NMOSトランジスタT21及びT22によって構成される。保持容量CSの両端は後述の駆動回路22の駆動トランジスタTDRVのゲート・ソース間に接続される。トランジスタT21及びT22の共通接続部はPMOSの駆動トランジスタTDRVのドレインに接続され、両トランジスタのゲートには書込時選択信号SEL1が供給される。

## 【0027】

駆動回路22は、有機ELの電源電圧源VOELと陰極電圧源VCATとの間に直列に接続された、PMOSトランジスタTDRV、ゲートに発光時選択信号SEL2が供給されるNMOSトランジスタT23、ゲートにコンパレータ回路23が供給されるNMOSの発光時間制御トランジスタTECT、OLEDによって構成される。

10

## 【0028】

電流プログラム回路21は、書込時選択信号SEL1がオン（レベルH）になり、発光時選択信号SEL2がオフ（レベルL）になると、トランジスタT21及びT22が導通し、駆動トランジスタTDRVをダイオード接続とする。プログラム電流源IPRGから駆動トランジスタTDRVにプログラム電流IPRを流すと、電流IPRが流れたトランジスタTDRVのゲート電圧が保持容量CSに記憶される。これにより、OLEDの発光時電流が設定可能となる。

## 【0029】

コンパレータ回路23には、発光時間に対応した当該画素のアナログデータ信号VDAT及び参照電位VREFが入力される。その出力端は発光時間制御トランジスタTECTのゲート端子に接続されている。コンパレータ回路23は、データ信号VDATが傾斜電圧の参照電位VREFを超える期間中、出力をレベルHとする。なお、トランジスタTECTをPMOSで構成した場合には、データ信号VDATが傾斜電圧の参照電位VREFを超える期間中、出力をレベルLとする。

20

## 【0030】

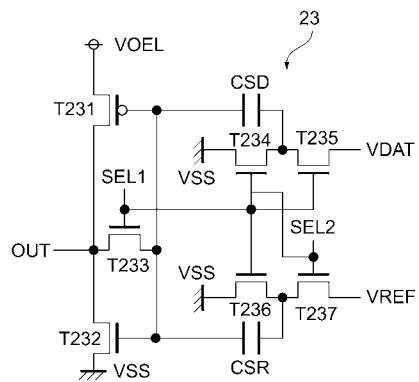

図3は、コンパレータ回路23の構成例を示している。同図に示す有機EL電源VOEL及び電源VSS（0ボルト）間にPMOSトランジスタT231及びNMOSトランジスタT232が出力端子OUTを介して直列に接続される。入力端子VDATと電源VSS間にNMOSトランジスタT234及びT235が直列に接続される。トランジスタT234及びT235の接続点とトランジスタT231のゲート間にデータ信号保持容量CSDが接続される。入力端子VREFと電源VSS間にNMOSトランジスタT237及びT236が直列に接続される。トランジスタT237及びT236の接続点とトランジスタT232のゲート間に参照電位保持容量CSRが接続される。トランジスタT231及びトランジスタT232の両ゲートは接続され、NMOSトランジスタT233を介して出力端子OUTに接続される。

30

## 【0031】

トランジスタT233、T235、T236の各ゲートには書込時選択信号SEL1が供給される。トランジスタT234及びT237のゲートには発光時選択信号SEL2が供給される。

40

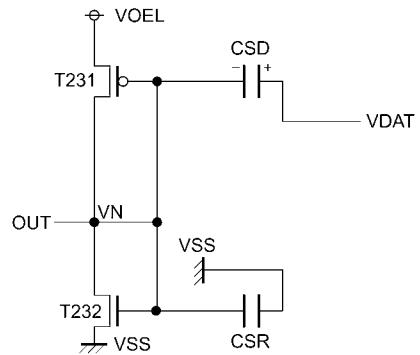

## 【0032】

コンパレータ回路23に供給される書込時選択信号SEL1がレベル「H」、発光時選択信号SEL2がレベル「L」の場合、コンパレータ回路23はトランジスタT233、T235及びT236の導通、T234及びT237の非導通によって図4に示すようになる。VDAT端子に供給されるアナログデータ信号VDATによってデータ保持容量CSDは充電され、当該データ信号のレベルを保持する。一方、参照電位保持容量CSRは一端が電源VSSに接続される。コンパレータ回路23の出力はCMOSインバータの特性により決まるインバータ中心VNとなる。

## 【0033】

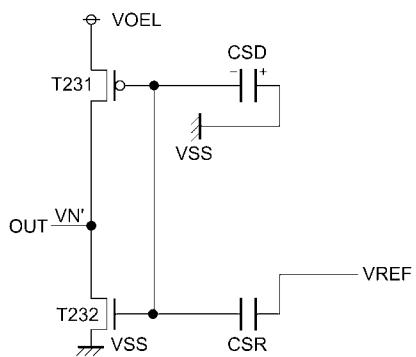

また、書込時選択信号SEL1がレベル「L」、発光時選択信号SEL2がレベル「H」の場合、コンパレータ回路23はトランジスタT233、T235及びT236の非導

50

通、T<sub>234</sub>及びT<sub>237</sub>の導通によって図5に示すようになる。入力端子VREF及び電源VSS間に参照電位保持容量CSR及びデータ保持容量CSDが直列に接続される。データ保持容量CSDの電荷の極性は反転して接続される。参照電位保持容量CSR及びデータ保持容量CSDの接続点はPMOSトランジスタT<sub>231</sub>及びNMOSトランジスタT<sub>232</sub>からなるCMOSインバータの入力端となっている。

#### 【0034】

初期の状態ではCMOSインバータの入力はインバータ中心VNとなっており、中間的な状態を維持している。その結果、OLEDの負荷電流回路が形成されて表示素子が発光する。

#### 【0035】

次に、入力端子に参照電位信号VREFが供給されると参照電位保持容量CSRが充電され、データ保持容量CSDの負電荷は相殺されて、CMOSインバータの入力は正方向に向かって変化する。データ保持容量CSDと参照電位保持容量CSRが等しいとき、CMOSインバータの入力VN'は、 $VN' = VN + 0.5 (VREF - VDAT)$ と与えられる。参照電位信号VREFのレベルがデータ保持容量CSDに保持されたレベルを超えると、CMOSインバータの入力は正電圧レベルとなり、トランジスタT<sub>231</sub>は非導通、トランジスタT<sub>232</sub>は導通となって出力端OUTは電源VSS(レベルL)を出力端OUTに出力する。出力端OUTにレベルLが出力されるとトランジスタTECTは非導通となり、OLEDの負荷電流回路が開放されて表示素子が消灯する。

#### 【0036】

このようにコンパレータ回路23は、アナログデータ信号VDATを保持容量CSDに蓄え、参照電位VREFを保持容量CSRに蓄える。そして、データ信号VDATが参照電位VREFよりも大きいとき、出力OUTはレベルHとなる。逆に、データ信号VDATが参照電位VREFよりも小さいとき、出力OUTはレベルLとなる。既述のようにコンパレータ回路23の出力OUTはトランジスタTECTのゲート入力となっている。従って、当該画素に供給するアナログデータ信号VDATのレベルに応じてOLEDの発光時間を制御することができる。

#### 【0037】

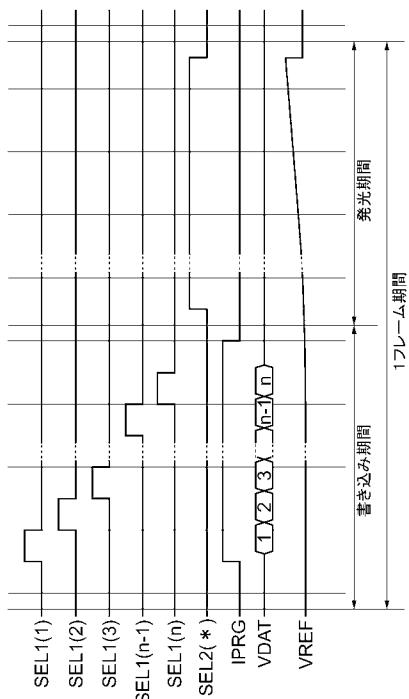

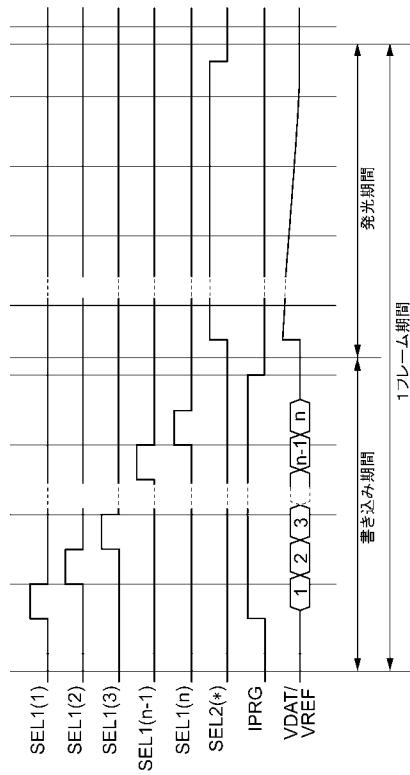

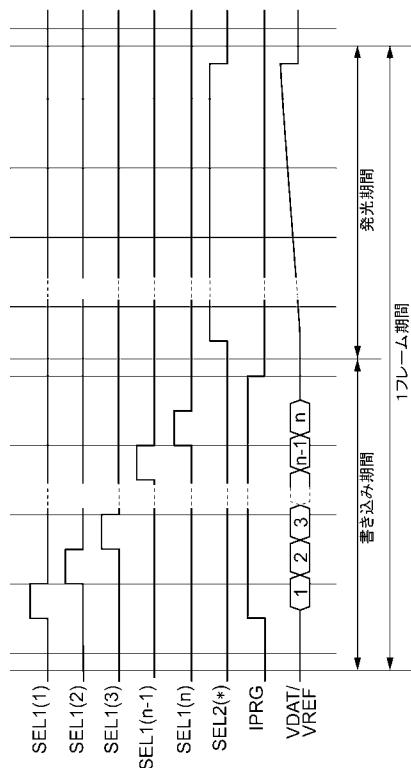

図6は、データ信号の書き込みから発光までの一連の動作を説明するタイミングチャートである。なお、書き込み時選択信号SEL1はアクティブマトリクス部13に対応してn行分設けられる。発光時選択信号SEL2もn行分設けられるが、1行分だけSEL2(\*)として示されている。データドライバ部11から出力されるアナログデータ信号VDATはアクティブマトリクス部13の1列分の信号だけ示されている。参照電位VREFは各画素に共通の波形であるので1つの信号のみが示されている。

#### 【0038】

同図に示されるように、画像の1画面の表示処理期間に相当する1フレーム期間は書き込み時間と発光時間に分けられる。前半の書き込み期間において、走査ドライバ部12は、各行の書き込み時選択信号SEL1(1)～SEL1(n)を順次レベルHに設定する。データドライバ部11は各行の画素に書き込み時選択信号SEL1(1)～SEL1(n)に同期してアナログデータ信号VDATを供給し、アナログデータ信号VDATの信号レベルを各画素の保持容量CSDに蓄えさせる。書き込み期間中において、各画素にはプログラム電流IPRGも供給されており、既述したように書き込み時選択信号SEL1及び発光時選択信号SEL2の供給に対応した駆動回路の動作によって駆動トランジスタTDRVがこのプログラム電流IPRGを流すために必要なゲート電圧が保持容量CSに蓄えられる。

#### 【0039】

後半の発光期間においては、各行の発光時選択信号SEL2(1)～SEL2(n)(図中には、SEL2(\*)として示されている)が一斉にレベルHとなり、全画素の発光時選択信号が一斉にレベルHとなり、参照電位VREFが保持容量CSRに供給される(図5参照)。この実施例では、参照電位VREFは時間経過と共にレベルが上昇するステップ信号である。コンパレータ回路23は先の書き込み期間で記憶されているアナログデータ

10

20

30

40

50

信号 VDAT と参照電位 VREF の比較を行う。

【0040】

データ信号 VDAT が参照電位 VREF よりも大きい場合には、コンパレータ回路の出力 OUT はレベル H となり、発光時間制御トランジスタ TETC はオン状態となる。その結果、OLED には書き期間にて記憶されたプログラム電流 IPRG が供給され発光状態となる。一方、データ信号 VDAT が参照電位 VREF よりも小さい場合には、コンパレータ回路の出力 OUT はオフ状態となる。その結果、OLED にはプログラム電流 IPRG が供給されず、非発光状態となる。参照電位 VREF をスイープ信号としていることから、書き期間に記憶されるデータ信号 VDAT の大小によって OLEDO の発光時間を制御することができる。

10

【実施例 2】

【0041】

コンパレータ回路の構成は図 2 に記載のものに限定されない。例えば、図 7 に示すように、一部のトランジスタ T236 及び T237 を複数の画素で共通化（共用）することもできる。同図において、図 3 と対応する部分には同一符号を付している。動作は図 3 のコンパレータ回路と同じであるので説明を省略する。コンパレータ回路は動作が同様であれば構成が異なってもよい。

【実施例 3】

【0042】

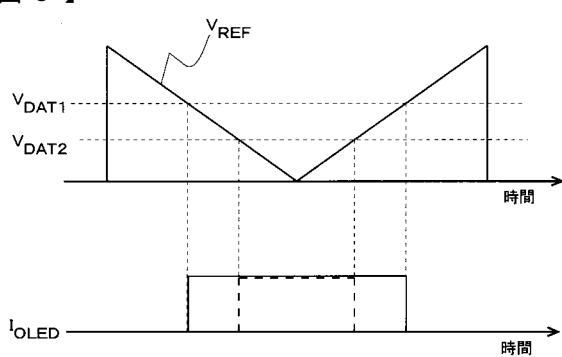

コンパレータ回路に供給される参照電位は、種々の態様のものを用いることが可能である。図 8 に示す例は、参照電位 VREF として、1 フレーム周期の中央部で信号レベルが最小値となる M 字状の信号波形を使用している。このようなスイープ信号であっても、データ保持容量 CSD に保持されたアナログデータ信号 VDAT の信号レベルに応じて OLEDO の発光電流 IOLED の供給時間（発光時間）を制御することができる。

20

【0043】

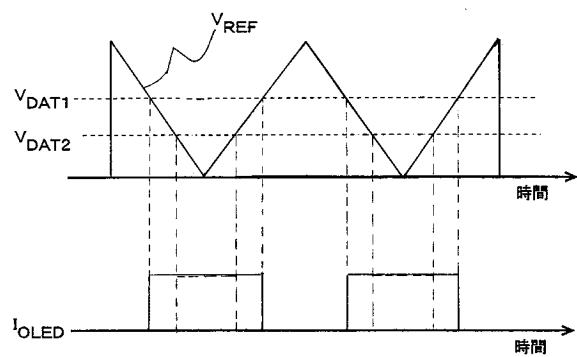

また、図 9 に示すコンパレータ回路に供給される参照電位の例は、参照電位 VREF として、1 フレーム周期で信号レベルが最小値となる箇所が 2 箇所ある W 字状の信号波形を使用している。このようなスイープ信号を用いることにより、OLED の発光電流 IOLED の供給時間（発光時間）をさらに細かく制御することができる。すなわち、OLED の発光時と非発光時の間隔をより短くできる。これにより、画像再生時に、視覚上より滑らかな画像表示を得ることができる。

30

【0044】

また、図示しないが、参照電位 VREF として鋸歯状の信号波形を使用してもよい。

【0045】

上述した実施例によれば、電流プログラムを用いた時分割階調方式によって OLEDO を駆動する際に、時間制御の手段としてコンパレータ回路を使用することによってアクティブマトリクスを構成する各画素の階調制御を同時に行うことができる。各画素の複雑な制御動作を回避しつつ、従来の電流プログラム方式に見られる階調ずれを抑制することが可能となって具合がよい。

40

【0046】

また、上述した実施例の画素の駆動回路を使用することで、予め各画素に供給する電流レベルを設定し、各画素が表示すべき画素信号を各画素の領域に記憶し、供給される傾斜レベル信号と各画素の画素信号のレベルとを比較し、電流レベルによる各画素の発光時間を制御し、基板上に二次元に配置された複数の画素を発光させる画素駆動方法が実行可能となる。

【実施例 4】

【0047】

本発明の第 5 の説明について図 10 乃至図 13 を参照して説明する。

この実施例においては、発光時間制御トランジスタ（TFT）を画素回路の電気光学素子の電流路に設ける。発光時間制御トランジスタのゲート・ドレイン間を短絡し、閾値を

50

記憶すると同時に発光時間に相当するアナログ信号を各画素回路に記憶する。参照電位(スイープ信号)を全画素回路に一斉に供給し、アナログ信号と参照電位の大小関係によって発光時間制御トランジスタのオンオフ動作が制御され、各画素回路の電気光学素子の発光時間が制御される。

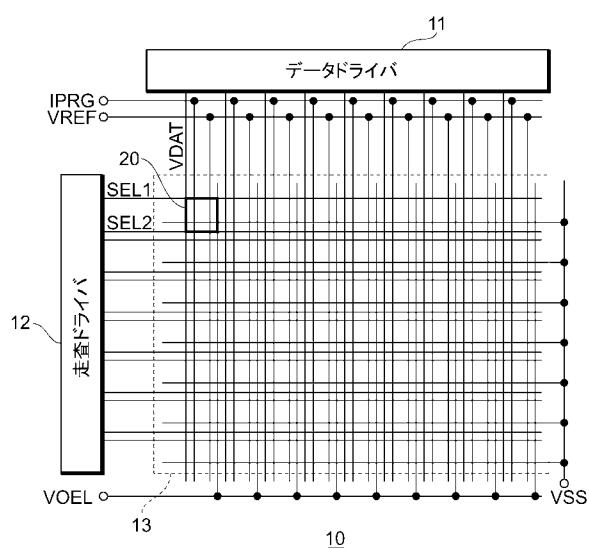

#### 【0048】

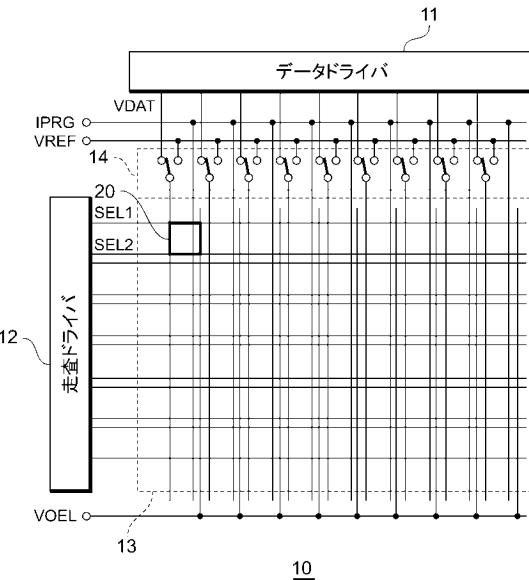

図10は、本発明の電気光学装置の一例である有機EL表示装置10の電気的接続を示すプロック回路図である。同図において、有機EL表示装置10はデータドライバ部11、走査ドライバ部12、アクティブマトリクス部13及び切替部14を備えている。アクティブマトリクス部13は後述の画素回路20をマトリクス状に複数配置して構成されている。データドライバ部11は画像の各画素の輝度に相当するアナログデータ信号VDATを出力する。切替部14は、アナログデータ信号VDAT及び図示しない信号源から出力される参照電位VREFを選択的に切替えて各画素回路20に供給する。走査ドライバ部12は各行の各画素回路20に書き時選択信号SEL1及び発光時選択信号SEL2を供給する。また、各画素回路20は後述の電流源から一定のプログラム電流IPRGの供給を受け、電源からOLEDの電源電圧VOELの供給を受けている。

#### 【0049】

走査ドライバ部12はアクティブマトリクス部13の各行の画素回路群を順次選択する。この間中、切替部14は、データドライバ部11の出力を選択し、各行の画素回路群に各画素の発光時間に相当する信号レベルVDATを書き込む。全画素回路20に画素データ(アナログデータ信号)の書きが終了すると、切替部14は参照電位VREFを選択して全画素回路20に供給する。各画素回路20に保持された信号レベルVDATと各画素回路20に供給される傾斜電圧レベルVREFの比較によって画素であるOLEDの発光時間が決定される。

#### 【0050】

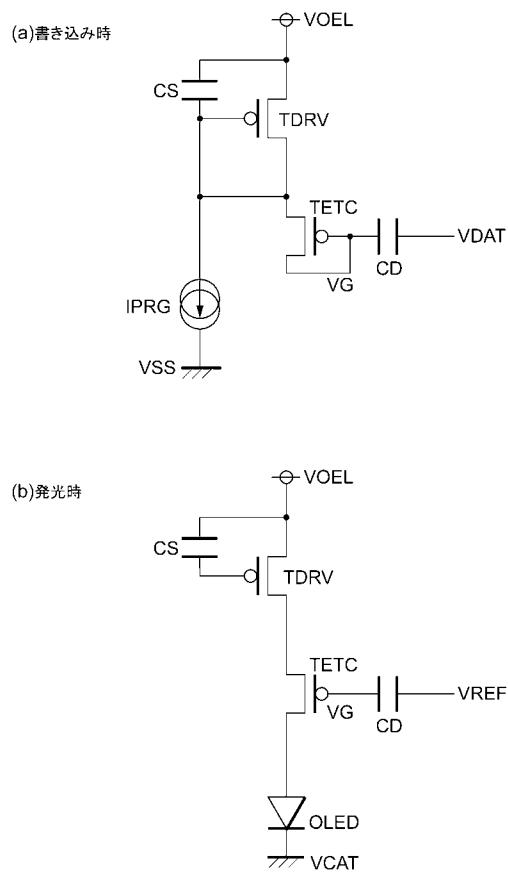

図11は、上述した画素回路20の構成例を示している。画素回路20は、電流プログラムを実現するための電流プログラム回路21、OLEDを駆動する駆動回路22、PMOSインバータ回路24によって構成されている。各回路で称されるトランジスタは薄膜トランジスタ(TFT)である。

#### 【0051】

電流プログラム回路21は、有機EL電源電圧VOELとプログラム電流源IPRGとの間に直列に接続された保持容量CS、NMOSトランジスタT21及びT22によって構成される。保持容量CSの両端は後述の駆動回路22の駆動トランジスタTDRVのゲート・ソース間に接続される。トランジスタT21及びT22の共通接続部はPMOSの駆動トランジスタTDRVのドレインに接続され、両トランジスタのゲートには書き時選択信号SEL1が供給される。

#### 【0052】

駆動回路22は、有機ELの電源電圧源VOELと陰極電圧源VCATとの間に直列に接続された、PMOSトランジスタTDRV、ゲートに発光時選択信号SEL2が供給されるNMOSトランジスタT23、OLEDによって構成される。

#### 【0053】

PMOSインバータ回路24は、OLEDの電流路に設けられた発光時間制御トランジスタTECT、発光時間制御トランジスタTECTのゲート・ドレン間に接続された閾値初期化トランジスタTINI及び発光時間制御トランジスタTECTのゲートに接続されたデータ信号保持容量CDによって構成される。データ信号保持容量CDを介して発光時間制御トランジスタTECTには複合信号VDAT/VREFが供給される。閾値初期化トランジスタTINIのゲートには書き時選択信号SEL1が供給される。

#### 【0054】

後述するように、PMOSインバータ回路24はアナログデータ信号VDATのレベルと参照電位VREFのレベルとを比較するレベル比較器として機能する。

#### 【0055】

10

20

30

40

50

複合信号 VDAT / VREF は、切替回路 14 の動作によって、1 フレーム周期の前半において画素列データを担うアナログデータ信号 (VDAT) 部分と、1 フレーム周期の後半において傾斜レベル信号 (スイープ信号) である参照電位 VREF 部分とに構成される (後述の図 12 参照)。

#### 【0056】

PMOS インバータ回路 24 は、アナログ信号 VDAT が参照電位 VREF よりも小さい場合、発光時間制御トランジスタ TETC は導通状態となる。アナログ信号 VDAT が参照電位 VREF よりも大きい場合、発光時間制御トランジスタ TETC は非導通状態となる。

#### 【0057】

電流プログラム回路 21 は、書込時選択信号 SEL1 がオン (レベル H) になり、発光時選択信号 SEL2 がオフ (レベル L) なると、トランジスタ T21 及び T22 が導通し、駆動トランジスタ TDRV をダイオード接続とする。プログラム電流源 IPRG から駆動トランジスタ TDRV にプログラム電流 IPR を流すと、電流 IPR が流れたトランジスタ TDRV のゲート電圧 (閾値電圧) が保持容量 CS に記憶される。これにより、有機 E-L 表示素子の発光時電流が設定可能となる。

#### 【0058】

図 12 は、データ信号の書込から発光までの一連の動作を説明するタイミングチャートである。走査ドライバ部 12 の出力である書込時選択信号 SEL1 はアクティブマトリクス部 13 に対応して n 行分設けられる。発光時選択信号 SEL2 も n 行分設けられるが、同図では 1 行分だけ SEL2 (\*) として示されている。切替部 14 から出力される複合信号 VDAT / VREF はアクティブマトリクス部 13 の 1 列分の信号だけ示されている。

#### 【0059】

同図に示されるように、画像の 1 画面の表示処理期間に相当する 1 フレーム期間は前半の書込時間と後半の発光時間に分けられる。書込期間において、走査ドライバ部 12 は、各行の書込時選択信号 SEL1(1) ~ SEL1(n) を順次レベル H に設定する。

#### 【0060】

図 13(a) に示すように、閾値初期化トランジスタ TINI が導通し、発光時間制御トランジスタ TETC のゲート・ドレイン間が短絡され、ダイオード接続となった発光時間制御トランジスタ TETC のゲート電圧 VG に閾値電圧が現れる。

#### 【0061】

また、切替部 14 は各行の画素に書込時選択信号 SEL1(1) ~ SEL1(n) に同期して複合信号のアナログデータ信号 VDAT を供給し、アナログデータ信号 VDAT の信号レベルを各画素の保持容量 CD に蓄えさせる。書込期間中において、各画素にはプログラム電流 IPRG も供給されている。既述したように書込時選択信号 SEL1 レベル H 及び発光時選択信号 SEL2 レベル L に対応してトランジスタ T21 及び T22 が導通、トランジスタ T23 の非導通によって駆動トランジスタ TDRV がこのプログラム電流 IPRG を流すために必要なゲート電圧が保持容量 CS に蓄えられる。

#### 【0062】

図 12 に示すように、後半の発光期間においては、各行の発光時選択信号 SEL2(1) ~ SEL2(n) (図中には、SEL2(\*) として示されている) が一斉にレベル H となり、全画素の発光時選択信号 SEL2 が一斉にレベル H となり、切替部 14 の切替動作によって複合信号 VDAT / VREF の参照電位 VREF が保持容量 CD に供給される。この実施例では、参照電位 VREF は時間経過と共にレベルが下降するスイープ信号である。

#### 【0063】

PMOS インバータ回路 24 は先の書込期間でデータ信号保持容量 CD に記憶されているアナログデータ信号 VDAT と参照電位 VREF の大小関係により、発光時間制御トランジスタ TETC の動作を決定する。

10

20

30

40

50

## 【0064】

データ信号V D A Tが参照電位V R E Fよりも小さい場合には、図13(b)に示すように、発光時間制御トランジスタT E T Cは導通状態となる。その結果、O L E Dには書き期間にて記憶されたプログラム電流I P R Gが供給されて発光状態となる。

## 【0065】

一方、データ信号V D A Tが参照電位V R E Fよりも大きい場合には、発光時間制御トランジスタT E T Cは非導通状態となる。その結果、O L E Dにはプログラム電流I P R Gが供給されず、非発光状態となる。

## 【0066】

実施例では参照電位V R E Fをスイープ信号としていることから、書き期間に記憶されるデータ信号V D A Tの大小によってO L E Dの発光時間を制御することができる。 10

## 【0067】

このように、実施例の画素駆動方法は、予め各電気光学素子に供給する電流レベルを設定し(プログラム電流方式)、時間軸上において先行する一連の画素信号からなる画素列信号部分とこれに後続する傾斜レベル信号部分とを含む複合信号から各電気光学素子の配置領域に対応する画素信号を選択してそのレベルを記憶し、各電気光学素子の配置領域にそれぞれ対応付けられた各画素信号のレベルと供給される傾斜レベル信号とを比較して電流レベルによる各電気光学素子の発光時間を制御する。

## 【実施例5】

## 【0068】

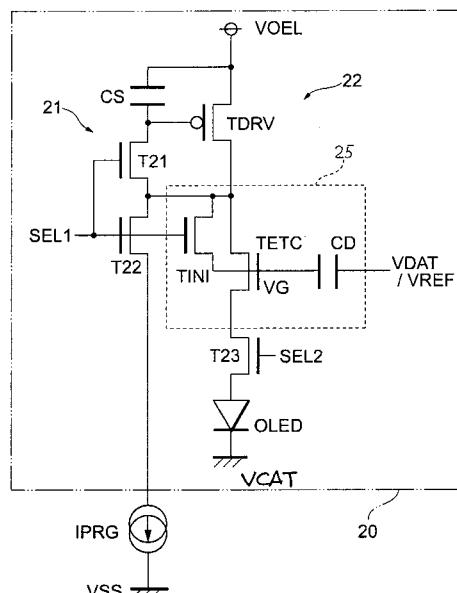

図14及び図15は、本発明の第5の実施例を示している。図14において、図11に示した画素回路20と対応する部分には同一符号を付し、かかる部分の説明は省略する。 20

## 【0069】

この実施例では、第4の実施例のP M O Sインバータ回路24をN M O Sインバータ回路25によって構成している。N M O Sインバータ回路25はN M O Sの発光時間制御トランジスタT E T C、発光時間制御トランジスタT E T Cのゲート・ドレイン間に接続される閾値初期化トランジスタT I N I及びデータ信号保持容量C Dによって構成されている。他の回路構成は図11に示した構成と同じである。

## 【0070】

このN M O Sインバータ回路25は、アナログ信号V D A Tが参照電位V R E Fよりも大きい場合、発光時間制御トランジスタT E T Cを導通状態とする。反対に、アナログ信号V D A Tが参照電位V R E Fよりも小さい場合、発光時間制御トランジスタT E T Cを非導通とする。 30

## 【0071】

そこで、図15のタイミングチャートに示すように、参照電位V R E Fのスイープの変化方向を第4の実施例の場合とは逆に(増加方向に)することで、N M O Sインバータ回路25を用いた場合にも第4の実施例の画素回路20と同じ動作が得られる。

## 【0072】

上述した実施例によれば、電流プログラムを用いた時分割階調方式によってO L E Dを駆動する際に、時間制御の手段として片チャンネルインバータを適用することによってアクティブマトリクスを構成する各画素の階調制御を同時にを行うことができる。各画素の複雑な制御動作を回避しつつ、従来の電流プログラム方式に見られる階調ずれを抑制することが可能となって具合がよい。また、発光時間の制御手段として2入力のコンパレータ回路を用いた場合に比べて素子数及び配線数を大幅に削減することができ、表示装置として重要な開口率の確保が容易となる。使用素子数の減少は信頼性の向上の観点からも好ましい。

## 【0073】

また、上述した実施例の画素駆動回路を使用することによって、予め各電気光学素子に供給する電流レベルを設定し、時間軸上において先行する一連の画素信号からなる画素列信号部分とこれに後続する傾斜レベル信号部分とを含む複合信号から各電気光学素子の配 40

置領域に対応する画素信号を選択してそのレベルを記憶し、各電気光学素子の配置領域にそれぞれ対応付けられた各画素信号のレベルと供給される傾斜レベル信号とを比較して電流レベルによる各電気光学素子の発光時間を制御する、基板上に二次元に配置された複数の電気光学素子を発光させる画素駆動方法を実現することが可能となる。

#### 【実施例 6】

##### 【0074】

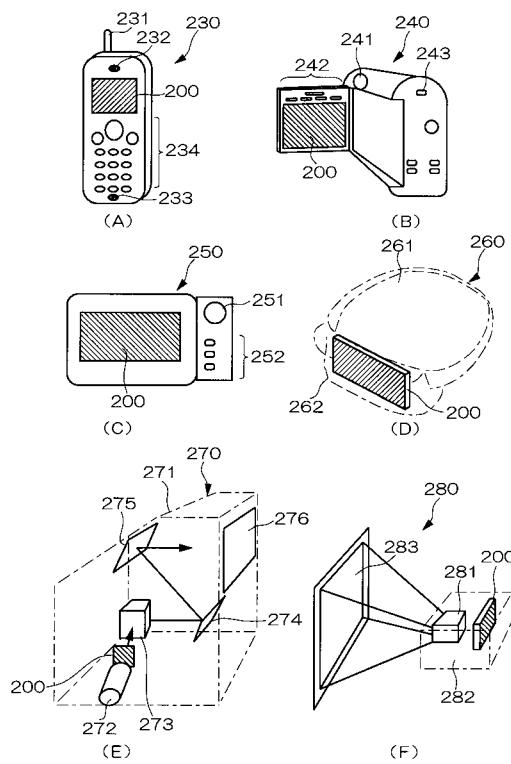

図16及び図17は、上述した電気光学装置（画像表示器）を適用可能な電子機器の例を示す図である。

図16（A）は携帯電話への適用例であり、当該携帯電話230はアンテナ部231、音声出力部232、音声入力部233、操作部234、および本発明の電気光学装置200を備えている。このように本発明に係る電気光学装置は表示部として利用可能である。

10

##### 【0075】

図16（B）はビデオカメラへの適用例であり、当該ビデオカメラ240は受像部241、操作部242、音声入力部243、および本発明の電気光学装置200を備えている。

。

##### 【0076】

図16（C）は携帯型パーソナルコンピュータ（いわゆるPDA）への適用例であり、当該コンピュータ250はカメラ部251、操作部252、および本発明に係る電気光学装置200を備えている。

##### 【0077】

図16（D）はヘッドマウントディスプレイへの適用例であり、当該ヘッドマウントディスプレイ260はバンド261、光学系収納部262および本発明に係る電気光学装置200を備えている。

20

##### 【0078】

図16（E）はリア型プロジェクターへの適用例であり、当該プロジェクター270は筐体271に、光源272、合成光学系273、ミラー274、275、スクリーン276、および本発明に係る電気光学装置200を備えている。

。

##### 【0079】

図16（F）はフロント型プロジェクターへの適用例であり、当該プロジェクター280は筐体282に光学系281および本発明に係る電気光学装置200を備え、画像をスクリーン283に表示可能になっている。

30

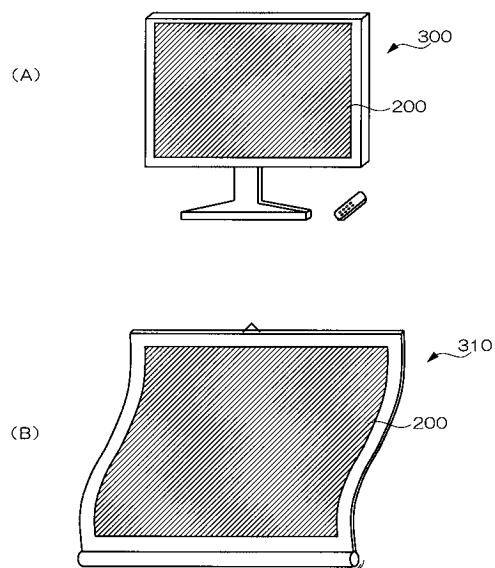

##### 【0080】

図17（A）はテレビジョンへの適用例であり、当該テレビジョン300は本発明に係る電気光学装置200を備えている。なお、パーソナルコンピュータ等に用いられるモニタ装置に対しても同様に本発明に係る電気光学装置を適用し得る。図17（B）はロールアップ式テレビジョンへの適用例であり、当該ロールアップ式テレビジョン310は本発明に係る電気光学装置200を備えている。

。

#### 【図面の簡単な説明】

##### 【0081】

【図1】図1は、有機EL表示装置の例を説明するブロック図である。

【図2】図2は、本発明の画素駆動回路の例を説明する回路図である。

40

【図3】図3は、図2の画素駆動回路に使用されるコンパレータ回路の例を説明する回路図である。

【図4】図4は、コンパレータ回路の動作（SEL1レベルH、SEL2レベルL）を説明する説明図である。

【図5】図5は、コンパレータ回路の動作（SEL1レベルL、SEL2レベルH）を説明する説明図である。

【図6】図6は、マトリクス状に配置された画素駆動回路の動作を説明するタイミングチャートである。

【図7】図7は、他のコンパレータ回路の例を説明する回路図である。

50

【図 8】図 8 は、VREF の他の信号波形例を説明するグラフである。

【図 9】図 9 は、VREF の他の信号波形例を説明するグラフである。

【図 10】図 10 は、電気光学装置（有機 EL 表示装置）の例を説明するブロック図である。

【図 11】図 11 は、本発明の第 1 の実施例の画素回路の例を説明する回路図である。

【図 12】図 12 は、図 11 の画素回路に供給される信号を説明するタイミングチャートである。

【図 13】図 13 は、画素回路の動作を説明する説明図であり、同図（a）は信号 SEL1 レベル「H」及び信号 SEL2 レベル「L」の場合、同図（b）は信号 SEL1 レベル「L」、信号 SEL2 レベル「H」の場合を示す。

10

【図 14】図 14 は、第 2 の実施例の画素回路を説明する回路図である。

【図 15】図 15 は、図 14 の画素回路に供給される信号を説明するタイミングチャートである。

【図 16】図 16 は、電気光学装置を適用可能な電子機器の例を示す図である。

【図 17】図 17 は、電気光学装置を適用可能な電子機器の例を示す図である。

#### 【符号の説明】

#### 【0082】

10 有機 EL 表示装置（電気光学装置） 11 データドライバ部、12 走査ドライバ部、13 アクティブマトリクス部、14 切替部、20 画素回路、23 コンパレータ回路、24 PMOS インバータ回路、25 NMOS インバータ回路、

20

20

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 4 1 D

H 0 5 B 33/14 AF ターム(参考) 5C080 AA06 BB05 DD22 EE28 EE29 FF11 JJ02 JJ03 JJ04 JJ06

KK43 KK47

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路，像素驱动方法和电子设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP2006126779A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2006-05-18 |

| 申请号            | JP2005166024                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2005-06-06 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 原弘幸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 原 弘幸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G09G3/325 G09G3/2014 G09G2300/0852 G09G2300/0861 G09G2310/0259 G09G2310/066                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/30.K G09G3/30.J G09G3/20.612.F G09G3/20.624.B G09G3/20.641.A G09G3/20.641.D H05B33/14.A G09G3/20.642.A G09G3/325 G09G3/3266 G09G3/3275 G09G3/3283 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/AB18 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 5C080/AA06 5C080 /BB05 5C080/DD22 5C080/EE28 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C080/KK43 5C080/KK47 3K107/AA01 3K107/BB01 3K107/CC02 3K107/CC33 3K107 /CC36 3K107/CC45 3K107/EE03 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB06 5C380/AC07 5C380/AC08 5C380/AC09 5C380/AC11 5C380/AC12 5C380/BB22 5C380/CA12 5C380/CA13 5C380 /CA53 5C380/CA54 5C380/CB01 5C380/CB18 5C380/CB29 5C380/CC13 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC50 5C380/CC52 5C380/CC57 5C380/CC58 5C380/CC63 5C380/CD015 5C380 /CD026 5C380/CF23 5C380/CF61 5C380/DA02 5C380/DA07 5C380/DA30 5C380/DA35 |         |            |

| 代理人(译)         | 田中 克郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 优先权            | 2004288030 2004-09-30 JP<br>2004288039 2004-09-30 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 其他公开文献         | JP4501785B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

#### 摘要(译)

为了提供一种驱动电路，驱动方法以及电光装置的电子设备，其能够使控制操作和电路结构更简单地构成。[解决方案] 本发明的像素电路包括：晶体管TETC，其插入到像素电路20中的电光元件的驱动电流路径中，该电光元件使电光元件OLED发光；以及电流值设置电路21，其设置驱动电流路径的电流值。比较电路23，用于将所存储的像素信号电平与所提供的斜率电平信号VREF进行比较，并基于比较结果来控制晶体管TETC的操作。 和 [选择图]图2