(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4610843号

(P4610843)

(45) 発行日 平成23年1月12日(2011.1.12)

(24) 登録日 平成22年10月22日(2010.10.22)

(51) Int.CI.

F 1

G09G 3/30 (2006.01)

G09G 3/20 (2006.01)G09G 3/30 J

G09G 3/30 K

G09G 3/20 611H

G09G 3/20 623H

G09G 3/20 623R

請求項の数 17 (全 33 頁) 最終頁に続く

(21) 出願番号

特願2002-180284 (P2002-180284)

(22) 出願日

平成14年6月20日 (2002.6.20)

(65) 公開番号

特開2004-21219 (P2004-21219A)

(43) 公開日

平成16年1月22日 (2004.1.22)

審査請求日

平成15年7月15日 (2003.7.15)

審判番号

不服2008-7959 (P2008-7959/J1)

審判請求日

平成20年4月2日 (2008.4.2)

(73) 特許権者 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(72) 発明者 佐藤 和仁

東京都八王子市石川町2951番地5 カ

シオ計算機株式会社 八王子研究所内

(72) 発明者 山田 裕康

東京都八王子市石川町2951番地5 カ

シオ計算機株式会社 八王子研究所内

合議体

審判長 下中 義之

審判官 後藤 亮治

審判官 江塚 政弘

最終頁に続く

(54) 【発明の名称】表示装置及び表示装置の駆動方法

(57) 【特許請求の範囲】

## 【請求項 1】

複数の行に配列された複数の走査線と複数の列に配列された複数の信号線との交差部にそれぞれ配置され、アノード電極及びカソード電極を有し、前記信号線からの階調電流に従って流れる駆動電流により発光する発光素子をそれぞれ有する複数の画素と、

前記階調電流により前記信号線にチャージされた電荷に応じた電圧を、リセット電圧に変位させるリセット手段と、

前記信号線に前記階調電流を流すデータドライバと、を備え、

前記複数の画素は、選択期間に前記信号線と導通し、非選択期間に前記信号線と非導通となり、それぞれ前記発光素子に前記駆動電流を供給する画素回路を有し、

前記リセット手段は、

所定行の前記選択期間に前記データドライバが前記画素回路を介して前記信号線に流す前記階調電流によって前記信号線に充電される電荷を、前記所定行の次の行の前記選択期間の前に、前記信号線に前記リセット電圧を印加してリセットする機能を有し、

前記画素回路は、

ドレイン電極が電源走査線に接続され、ソース電極が前記発光素子の前記アノード電極に接続された第1トランジスタと、

ゲート電極が前記走査線に接続され、ドレイン電極が前記電源走査線に接続され、ソース電極が前記第1トランジスタのゲート電極に接続された第2トランジスタと、

ゲート電極が前記走査線に接続され、ソース電極が前記信号線に接続され、ドレイン電

10

20

極が前記第1トランジスタの前記ソース電極に接続された第3トランジスタと、

前記第1トランジスタのゲート-ソース間に設けられたコンデンサと、を備え、

前記階調電流が最高輝度階調電流のときの前記信号線での最高輝度階調電圧は、前記階調電流が最低輝度階調電流のときの前記信号線での最低輝度階調電圧より低く、

前記リセット電圧は、前記最低階調電圧と、前記最高階調電圧と、の中間値となる中間電圧以上に設定され、

前記所定行の前記選択期間に、前記所定行の前記画素回路の前記第2トランジスタ及び前記第3トランジスタをオン状態とするとともに、前記電源走査線に前記発光素子の前記カソード電極の電位以下のチャージ電圧が印加され、前記データドライバが、前記所定行の前記画素の前記発光素子を介さずに、前記電源走査線から前記所定行の前記画素回路の前記第1トランジスタ及び前記第3トランジスタを介して前記信号線に前記階調電流を流して、前記所定行の前記画素回路の前記コンデンサに前記階調電流に応じた電荷がチャージされ、

前記所定行の前記選択期間後の前記非選択期間に、前記所定行の前記画素回路の前記第2トランジスタ及び前記第3トランジスタをオフ状態とするとともに、前記電源走査線に前記チャージ電圧より高い電源電圧が印加され、前記所定行の前記画素回路の前記コンデンサの電荷に応じて前記所定行の前記画素回路の前記第1トランジスタが前記所定行の前記画素の前記発光素子に前記駆動電流を流して、前記所定行の前記画素の前記発光素子が発光することを特徴とする表示装置。

**【請求項2】** 20

複数の行に配列された複数の走査線と複数の列に配列された複数の信号線との交差部にそれぞれ配置され、アノード電極及びカソード電極を有し、前記信号線からの階調電流に従って流れる駆動電流により発光する発光素子をそれぞれ有する複数の画素と、

前記階調電流により前記信号線にチャージされた電荷に応じた電圧を、リセット電圧に変位させるリセット手段と、

前記信号線に前記階調電流を流すデータドライバと、を備え、

前記複数の画素は、選択期間に前記信号線と導通し、非選択期間に前記信号線と非導通となり、それぞれ前記発光素子に前記駆動電流を供給する画素回路を有し、

前記リセット手段は、

所定行の前記選択期間後からその次の行の選択期間の前までの間に、前記所定行の前記選択期間に前記データドライバが前記画素回路を介して前記信号線に流す前記階調電流によって前記信号線に充電される電荷を、前記信号線に前記リセット電圧を印加してリセットする機能を有し、 30

前記画素回路は、

ドレン電極が電源走査線に接続され、ソース電極が前記発光素子の前記アノード電極に接続された第1トランジスタと、

ゲート電極が前記走査線に接続され、ドレン電極が前記電源走査線に接続され、ソース電極が前記第1トランジスタのゲート電極に接続された第2トランジスタと、

ゲート電極が前記走査線に接続され、ソース電極が前記信号線に接続され、ドレン電極が前記第1トランジスタの前記ソース電極に接続された第3トランジスタと、 40

前記第1トランジスタのゲート-ソース間に設けられたコンデンサと、を備え、

前記階調電流が最高輝度階調電流のときの前記信号線での最高輝度階調電圧は、前記階調電流が最低輝度階調電流のときの前記信号線での最低輝度階調電圧より低く、

前記リセット電圧は、前記最低階調電圧と、前記最高階調電圧と、の中間値となる中間電圧以上に設定され、

前記所定行の前記選択期間に、前記所定行の前記画素回路の前記第2トランジスタ及び前記第3トランジスタをオン状態とするとともに、前記電源走査線に前記発光素子の前記カソード電極の電位以下のチャージ電圧が印加され、前記データドライバが、前記所定行の前記画素の前記発光素子を介さずに、前記電源走査線から前記所定行の前記画素回路の前記第1トランジスタ及び前記第3トランジスタを介して前記信号線に前記階調電流を流

10

20

30

40

50

して、前記所定行の前記画素回路の前記コンデンサに前記階調電流に応じた電荷がチャージされ、

前記選択期間後の前記非選択期間に、前記所定行の前記画素回路の前記第2トランジスタ及び前記第3トランジスタをオフ状態とするとともに、前記電源走査線に前記チャージ電圧より高い電源電圧が印加され、前記所定行の前記画素回路の前記コンデンサの電荷に応じて前記所定行の前記画素回路の前記第1トランジスタが前記所定行の前記画素の前記発光素子に前記駆動電流を流して、前記所定行の前記画素の前記発光素子が発光することを特徴とする表示装置。

【請求項3】

前記リセット手段は、

10

前記信号線に前記階調電流を流す階調電流用トランジスタと、

前記信号線に前記リセット電圧を出力するリセット電圧用トランジスタと、

を有することを特徴とする請求項1又は2に記載の表示装置。

【請求項4】

前記リセット手段は、階調信号に応じた前記階調電流を生成するカレントミラー回路を備えることを特徴とする請求項1又は2に記載の表示装置。

【請求項5】

前記リセット手段は、シフトレジスタからの信号に応じて、各列に対応した前記カレントミラー回路に選択的に前記階調信号を供給する階調信号スイッチ手段を有することを特徴とする請求項4に記載の表示装置。

20

【請求項6】

前記リセット手段は、

データドライバからの前記階調電流を前記信号線に流す階調電流用トランジスタと、

前記リセット電圧を前記信号線に出力するリセット電圧用トランジスタと、

を有することを特徴とする請求項1又は2に記載の表示装置。

【請求項7】

前記リセット電圧は、前記発光素子が最高階調輝度で発光するときに前記発光素子に流れる最高階調駆動電流に等しい電流値となる前記最高輝度階調電流によって前記信号線にチャージされる電荷にしたがって定常化される前記最高階調電圧よりも高く設定されていることを特徴とする請求項1又は2に記載の表示装置。

30

【請求項8】

前記所定行の前記画素における前記画素回路は、

前記所定行の選択期間に、前記信号線に前記階調電流が流れることによって前記階調電流にしたがった電荷を保持する電荷保持手段を有し、

前記第1トランジスタは、前記所定行の発光期間に、前記電荷保持手段により保持された電荷に応じて前記階調電流と等しい電流値の駆動電流を前記発光素子に流し、

前記第2トランジスタ及び前記第3トランジスタは、前記第1トランジスタを介して前記信号線に流れる前記階調電流の流れを制御することを特徴とする請求項1又は2に記載の表示装置。

【請求項9】

前記所定行の前記画素における前記画素回路の前記第1トランジスタは、

40

前記所定行の選択期間に、前記第3トランジスタを介して前記信号線に流れる前記階調電流を流して、前記電荷保持手段に電荷を保持させる機能と、

前記所定行の発光期間に、前記第3トランジスタに前記階調電流を流すことを停止する機能と、

を有することを特徴とする請求項8に記載の表示装置。

【請求項10】

前記駆動電流の電流値は、前記階調電流の電流値に等しいことを特徴とする請求項1又は2に記載の表示装置。

【請求項11】

50

複数の行に配列された複数の走査線と複数の列に配列された複数の信号線との交差部にそれぞれ配置され、アノード電極及びカソード電極を有し、前記信号線からの階調電流に従って流れる駆動電流により発光する発光素子をそれぞれ有する複数の画素を備える表示装置の駆動方法であって、

前記複数の画素は、選択期間に前記信号線と導通し、非選択期間に前記信号線と非導通となり、それぞれ前記発光素子に前記駆動電流を供給する画素回路を有し、

前記画素回路は、

ドレン電極が電源走査線に接続され、ソース電極が前記発光素子の前記アノード電極に接続された第1トランジスタと、

ゲート電極が前記走査線に接続され、ドレン電極が前記電源走査線に接続され、ソース電極が前記第1トランジスタのゲート電極に接続された第2トランジスタと、

ゲート電極が前記走査線に接続され、ソース電極が前記信号線に接続され、ドレン電極が前記第1トランジスタの前記ソース電極に接続された第3トランジスタと、

前記第1トランジスタのゲート-ソース間に設けられたコンデンサと、を備え、

所定行の前記選択期間に、前記所定行の前記画素回路の前記第2トランジスタ及び前記第3トランジスタをオン状態とするとともに、前記電源走査線に前記発光素子の前記カソード電極の電位以下のチャージ電圧が印加され、前記所定行の前記画素の前記発光素子を介さずに、前記電源走査線から前記所定行の前記画素回路の前記第1トランジスタ及び前記第3トランジスタを介して前記信号線に前記階調電流を流して、前記所定行の前記画素回路の前記コンデンサに前記階調電流に応じた電荷がチャージされる階調電流ステップと、

前記所定行の前記選択期間後に、前記所定行の前記画素回路の前記第2トランジスタ及び前記第3トランジスタをオフ状態にさせて前記信号線と前記画素とを非導通にして、前記階調電流により前記信号線にチャージされた電荷に応じた電圧をリセット電圧に変位させるリセット電圧ステップと、

前記所定行の前記選択期間後に、前記電源走査線に前記チャージ電圧より高い電源電圧を印加し、前記所定行の前記画素回路の前記コンデンサの電荷に応じて前記所定行の前記画素回路の前記第1トランジスタが前記所定行の前記画素の前記発光素子に前記駆動電流を流して前記発光素子を発光する発光ステップと、

を有し、

前記階調電流が最高輝度階調電流のときの前記信号線での最高輝度階調電圧は、前記階調電流が最低輝度階調電流のときの前記信号線での最低輝度階調電圧より低く、

前記リセット電圧は、前記最低階調電圧と、前記最高階調電圧と、の中間値となる中間電圧以上に設定されていることを特徴とする表示装置の駆動方法。

#### 【請求項12】

前記発光素子は前記選択期間後に前記階調電流に従って流れる前記駆動電流により発光することを特徴とする請求項11に記載の表示装置の駆動方法。

#### 【請求項13】

前記リセット電圧ステップは、前記所定行の前記画素分の前記階調電流が前記信号線に流れた後から、次の行の前記画素分の前記階調電流が前記信号線に流れる前までに行われることを特徴とする請求項11又は請求項12に記載の表示装置の駆動方法。

#### 【請求項14】

前記所定行の前記画素における前記画素回路は、

前記所定行の選択期間に、前記信号線に前記階調電流が流れることによって前記階調電流にしたがった電荷を保持する電荷保持手段を有し、

前記第1トランジスタは、前記所定行の発光期間に、前記電荷保持手段により保持された電荷に応じて前記階調電流と等しい電流値の駆動電流を前記発光素子に流し、

前記第2トランジスタ及び前記第3トランジスタは、前記第1トランジスタを介して前記信号線に流れる前記階調電流の流れを制御することを特徴とする請求項11に記載の表示装置の駆動方法。

10

20

30

40

50

## 【請求項 15】

前記所定行の前記画素における前記画素回路の前記第1トランジスタは、前記所定行の選択期間に、前記第3トランジスタを介して前記信号線に流れる前記階調電流を流して、前記電荷保持手段に電荷を保持させる機能と、

前記所定行の発光期間に、前記第3トランジスタに前記階調電流を流すことを停止する機能と、

を有することを特徴とする請求項14に記載の表示装置の駆動方法。

## 【請求項 16】

前記リセット電圧は、前記発光素子が最高階調輝度で発光するときに前記発光素子に流れる最高階調駆動電流に等しい電流値となる前記最高輝度階調電流によって前記信号線にチャージされる電荷にしたがって定常化される前記最高階調電圧よりも高く設定されていることを特徴とする請求項11に記載の表示装置の駆動方法。

10

## 【請求項 17】

前記駆動電流の電流値は、前記階調電流の電流値に等しいことを特徴とする請求項11に記載の表示装置の駆動方法。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は、駆動電流のレベルによって輝度が制御される発光素子を画素ごとに備えた表示装置、及び発光素子に駆動電流を流すことで表示を行う表示装置の駆動方法に関する。

20

## 【0002】

## 【従来の技術】

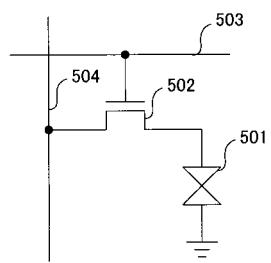

一般的に、表示装置には単純マトリクスのようなパッシブドライブ駆動方式と画素毎にスイッチングトランジスタを設けたアクティブマトリクス駆動方式のものがあり、アクティブマトリクス駆動方式の液晶ディスプレイでは、図11に示すように、コンデンサとしても機能する液晶を有する液晶素子501と、スイッチング素子として機能するTFT502とが、画素ごとに設けられている。アクティブマトリクス駆動方式では、選択期間中に走査ドライバによって走査線503にパルス信号が入力されて走査線503が選択されているときに、輝度を表すレベルの電圧がデータドライバによって信号線504に印加されると、TFT502を介して液晶素子501に電圧が印加される。選択期間後の非選択期間においてTFT502がオフ状態になっても、液晶素子501がコンデンサとして機能するため、次の選択期間まで電圧レベルが保持される。以上のように、選択期間において液晶素子501の光透過率が新たに更新されて、バックライトを光源として画素が電圧レベルに従った輝度で光を射出し、液晶ディスプレイの階調表現が行われる。

30

## 【0003】

一方、自発光素子である有機EL素子を用いた有機ELディスプレイは、液晶ディスプレイのようにバックライトを必要とせず、薄型化に最適であるとともに、液晶ディスプレイのような視野角の制限もないため、次世代の表示装置として実用化が大きく期待されている。

40

## 【0004】

高輝度、高コントラスト、高精細といった観点から、有機ELディスプレイも、液晶ディスプレイと同様にアクティブマトリクス駆動方式のものが特に望まれている。有機ELディスプレイは、パッシブ駆動方式では選択期間に流れる電流を増大しなければならないのに対してアクティブマトリクス駆動方式では非選択期間でも発光させるように、輝度を表す電圧レベルを保持しておくための素子を画素ごとに設けているため、単位時間当たりに流れる電流レベル（電流値）は小さくてよい。しかし、有機EL素子はコンデンサとしては極めて小さい容量しかないので、図11のような画素の回路において液晶素子501の代わりに有機EL素子を設けただけでは、非選択期間に有機EL素子が発光を維持することは困難になる。

## 【0005】

50

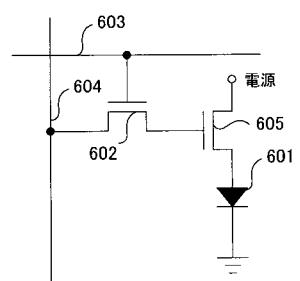

そこで、例えば図12に示すように、アクティブマトリクス駆動方式の有機ELディスプレイでは、有機EL素子601と、スイッチング素子として機能するTFT602と、輝度を表す電圧レベルを保持しておくとともに電圧レベルに従ったレベルの駆動電流を有機EL素子601に流すTFT605とが、画素ごとに設けられている。このディスプレイでは、選択期間中に走査ドライバによって走査線603にパルス信号が入力されて走査線603が選択されているときに、輝度を表すレベルの電圧がデータドライバによって信号線604に印加されると、TFT605のゲート電極にそのレベルの電圧が印加されて、TFT605がオン状態になり、ゲート電極の電圧レベルに応じたレベルの駆動電流が電源からTFT605を介して有機EL素子601に流れて、有機EL素子601が電流レベルに応じた輝度で発光する。選択期間後の非選択期間では、TFT602がオフ状態になっても、TFT605の容量等によりTFT605のゲート電極の電圧レベルが保持され続け、有機EL素子601が電圧レベルに従った輝度で発光する。以上のように、選択期間においてTFT605のゲート電圧が更新されることによって有機EL素子601の輝度が更新されて、有機ELディスプレイの階調表現が行われる。

#### 【0006】

ところで、一般的にTFTは、周囲の温度にチャネル抵抗が依存したり、長時間の使用によりチャネル抵抗が変化したりするために、ゲート閾値電圧が経時変化したり、同一表示領域内の個々のTFTのゲート閾値電圧がばらついたりする。従って、TFT605のゲート電極に印加する電圧のレベルを変化させることによって有機EL素子601に流れる電流のレベルを変化させること、換言すれば、TFT605のゲート電極に印加する電圧のレベルを変化させることによって有機EL素子601の輝度を変化させることを行っても、TFT605のゲート電圧レベルで有機EL素子601に流れる電流レベルを一義的に指定するには困難である。

#### 【0007】

そこで、輝度をTFTに印加される電圧のレベルで制御するのではなく、電流のレベルで制御する手法が研究されている。つまり、信号線にゲート電圧のレベルを指定する電圧指定方式ではなく、有機EL素子に流れる電流のレベルを直接信号線に指定する電流指定方式を有機ELディスプレイのアクティブマトリクス駆動方式に適用するというものである。

#### 【0008】

##### 【発明が解決しようとする課題】

しかしながら、電流指定方式の有機ELディスプレイでは、指定電流を流している選択期間内において指定電流レベル（電流値）は一定であるが、指定電流レベルが小さいと、指定電流により電圧が定常状態になるまでには時間を要する。そのため、有機EL素子が所望通りの輝度で発光しなくなり、有機ELディスプレイの表示品質の低下につながる。

#### 【0009】

一方、選択期間を長くすれば電圧が定常状態になるまでの時間より選択時間が長くなるが、選択時間が長くなれば表示画面がちらついて見えたりする等、有機ELディスプレイの表示品質の低下につながる。

#### 【0010】

そこで、本発明が解決しようとする課題は、高品質な表示を行うことである。

#### 【0011】

##### 【課題を解決するための手段】

以上の課題を解決するために、請求項1に記載の発明に係る表示装置は、複数の行に配列された複数の走査線と複数の列に配列された複数の信号線との交差部にそれぞれ配置され、アノード電極及びカソード電極を有し、前記信号線からの階調電流に従って流れる駆動電流により発光する発光素子をそれぞれ有する複数の画素と、前記階調電流により前記信号線にチャージされた電荷に応じた電圧を、リセット電圧に変位させるリセット手段と、

10

20

30

40

50

前記信号線に前記階調電流を流すデータドライバと、を備え、

前記複数の画素は、選択期間に前記信号線と導通し、非選択期間に前記信号線と非導通となり、それぞれ前記発光素子に前記駆動電流を供給する画素回路を有し、

前記リセット手段は、

所定行の前記選択期間に前記データドライバが前記画素回路を介して前記信号線に流す前記階調電流によって前記信号線に充電される電荷を、前記所定行の次の行の前記選択期間の前に、前記信号線に前記リセット電圧を印加してリセットする機能を有し、

前記画素回路は、

ドレイン電極が電源走査線に接続され、ソース電極が前記発光素子の前記アノード電極に接続された第1トランジスタと、

ゲート電極が前記走査線に接続され、ドレイン電極が前記電源走査線に接続され、ソース電極が前記第1トランジスタのゲート電極に接続された第2トランジスタと、

ゲート電極が前記走査線に接続され、ソース電極が前記信号線に接続され、ドレイン電極が前記第1トランジスタの前記ソース電極に接続された第3トランジスタと、

前記第1トランジスタのゲート - ソース間に設けられたコンデンサと、を備え、

前記階調電流が最高輝度階調電流のときの前記信号線での最高輝度階調電圧は、前記階調電流が最低輝度階調電流のときの前記信号線での最低輝度階調電圧より低く、

前記リセット電圧は、前記最低階調電圧と、前記最高階調電圧と、の中間値となる中間電圧以上に設定され、

前記所定行の前記選択期間に、前記所定行の前記画素回路の前記第2トランジスタ及び前記第3トランジスタをオン状態とするとともに、前記電源走査線に前記発光素子の前記カソード電極の電位以下のチャージ電圧が印加され、前記データドライバが、前記所定行の前記画素の前記発光素子を介さずに、前記電源走査線から前記所定行の前記画素回路の前記第1トランジスタ及び前記第3トランジスタを介して前記信号線に前記階調電流を流して、前記所定行の前記画素回路の前記コンデンサに前記階調電流に応じた電荷がチャージされ、

前記所定行の前記選択期間後の前記非選択期間に、前記所定行の前記画素回路の前記第2トランジスタ及び前記第3トランジスタをオフ状態とするとともに、前記電源走査線に前記チャージ電圧より高い電源電圧が印加され、前記所定行の前記画素回路の前記コンデンサの電荷に応じて前記所定行の前記画素回路の前記第1トランジスタが前記所定行の前記画素の前記発光素子に前記駆動電流を流して、前記所定行の前記画素の前記発光素子が発光することを特徴とする。

#### 【0012】

請求項2に記載の発明に係る表示装置は、

複数の行に配列された複数の走査線と複数の列に配列された複数の信号線との交差部にそれぞれ配置され、アノード電極及びカソード電極を有し、前記信号線からの階調電流に従って流れる駆動電流により発光する発光素子をそれぞれ有する複数の画素と、

前記階調電流により前記信号線にチャージされた電荷に応じた電圧を、リセット電圧に変位させるリセット手段と、

前記信号線に前記階調電流を流すデータドライバと、を備え、

前記複数の画素は、選択期間に前記信号線と導通し、非選択期間に前記信号線と非導通となり、それぞれ前記発光素子に前記駆動電流を供給する画素回路を有し、

前記リセット手段は、

所定行の前記選択期間後からその次の行の選択期間の前までの間に、前記所定行の前記選択期間に前記データドライバが前記画素回路を介して前記信号線に流す前記階調電流によって前記信号線に充電される電荷を、前記信号線に前記リセット電圧を印加してリセットする機能を有し、

前記画素回路は、

ドレイン電極が電源走査線に接続され、ソース電極が前記発光素子の前記アノード電極に接続された第1トランジスタと、

10

20

30

40

50

ゲート電極が前記走査線に接続され、ドレイン電極が前記電源走査線に接続され、ソース電極が前記第1トランジスタのゲート電極に接続された第2トランジスタと、

ゲート電極が前記走査線に接続され、ソース電極が前記信号線に接続され、ドレイン電極が前記第1トランジスタの前記ソース電極に接続された第3トランジスタと、

前記第1トランジスタのゲート-ソース間に設けられたコンデンサと、を備え、

前記階調電流が最高輝度階調電流のときの前記信号線での最高輝度階調電圧は、前記階調電流が最低輝度階調電流のときの前記信号線での最低輝度階調電圧より低く、

前記リセット電圧は、前記最低階調電圧と、前記最高階調電圧と、の中間値となる中間電圧以上に設定され、

前記所定行の前記選択期間に、前記所定行の前記画素回路の前記第2トランジスタ及び前記第3トランジスタをオン状態とするとともに、前記電源走査線に前記発光素子の前記カソード電極の電位以下のチャージ電圧が印加され、前記データドライバが、前記所定行の前記画素の前記発光素子を介さずに、前記電源走査線から前記所定行の前記画素回路の前記第1トランジスタ及び前記第3トランジスタを介して前記信号線に前記階調電流を流して、前記所定行の前記画素回路の前記コンデンサに前記階調電流に応じた電荷がチャージされ、

前記選択期間後の前記非選択期間に、前記所定行の前記画素回路の前記第2トランジスタ及び前記第3トランジスタをオフ状態とするとともに、前記電源走査線に前記チャージ電圧より高い電源電圧が印加され、前記所定行の前記画素回路の前記コンデンサの電荷に応じて前記所定行の前記画素回路の前記第1トランジスタが前記所定行の前記画素の前記発光素子に前記駆動電流を流して、前記所定行の前記画素の前記発光素子が発光することを特徴とする。

#### 【0013】

請求項3に記載の発明は、請求項1又は2に記載の表示装置において、

前記リセット手段は、

前記信号線に前記階調電流を流す階調電流用トランジスタと、

前記信号線に前記リセット電圧を出力するリセット電圧用トランジスタと、

を有することを特徴とする。

#### 【0014】

請求項4に記載の発明は、請求項1又は2に記載の表示装置において、

前記リセット手段は、階調信号に応じた前記階調電流を生成するカレントミラー回路を備えることを特徴とする。

#### 【0015】

請求項5に記載の発明は、請求項4に記載の表示装置において、

前記リセット手段は、シフトレジスタからの信号に応じて、各列に対応した前記カレントミラー回路に選択的に前記階調信号を供給する階調信号スイッチ手段を有することを特徴とする。

#### 【0016】

請求項6に記載の発明は、請求項1又は2に記載の表示装置において、

前記リセット手段は、

データドライバからの前記階調電流を前記信号線に流す階調電流用トランジスタと、

前記リセット電圧を前記信号線に出力するリセット電圧用トランジスタと、

を有することを特徴とする。

#### 【0017】

請求項7に記載の発明は、請求項1又は2に記載の表示装置において、

前記リセット電圧は、前記発光素子が最高階調輝度で発光するときに前記発光素子に流れる最高階調駆動電流に等しい電流値となる前記最高輝度階調電流によって前記信号線にチャージされる電荷にしたがって定常化される前記最高階調電圧よりも高く設定されていることを特徴とする。

#### 【0018】

10

20

30

40

50

請求項 8 に記載の発明は、請求項 1 又は 2 に記載の表示装置において、

前記所定行の前記画素における前記画素回路は、

前記所定行の選択期間に、前記信号線に前記階調電流が流れることによって前記階調電流にしたがった電荷を保持する電荷保持手段を有し、

前記第 1 ランジスタは、前記所定行の発光期間に、前記電荷保持手段により保持された電荷に応じて前記階調電流と等しい電流値の駆動電流を前記発光素子に流し、

前記第 2 ランジスタ及び前記第 3 ランジスタは、前記第 1 ランジスタを介して前記信号線に流れる前記階調電流の流れを制御することを特徴とする。

【 0 0 1 9 】

請求項 9 に記載の発明は、請求項 8 に記載の表示装置において、

10

前記所定行の前記画素における前記画素回路の前記第 1 ランジスタは、

前記所定行の選択期間に、前記第 3 ランジスタを介して前記信号線に流れる前記階調電流を流して、前記電荷保持手段に電荷を保持させる機能と、

前記所定行の発光期間に、前記第 3 ランジスタに前記階調電流を流すことを停止する機能と、

を有することを特徴とする。

【 0 0 2 0 】

請求項 10 に記載の発明は、請求項 1 又は 2 に記載の表示装置において、

20

前記駆動電流の電流値は、前記階調電流の電流値に等しいことを特徴とする。

【 0 0 2 1 】

請求項 11 に記載の発明は、

複数の行に配列された複数の走査線と複数の列に配列された複数の信号線との交差部にそれぞれ配置され、アノード電極及びカソード電極を有し、前記信号線からの階調電流に従って流れる駆動電流により発光する発光素子をそれぞれ有する複数の画素を備える表示装置の駆動方法であって、

前記複数の画素は、選択期間に前記信号線と導通し、非選択期間に前記信号線と非導通となり、それぞれ前記発光素子に前記駆動電流を供給する画素回路を有し、

前記画素回路は、

ドレイン電極が電源走査線に接続され、ソース電極が前記発光素子の前記アノード電極に接続された第 1 ランジスタと、

30

ゲート電極が前記走査線に接続され、ドレイン電極が前記電源走査線に接続され、ソース電極が前記第 1 ランジスタのゲート電極に接続された第 2 ランジスタと、

ゲート電極が前記走査線に接続され、ソース電極が前記信号線に接続され、ドレイン電極が前記第 1 ランジスタの前記ソース電極に接続された第 3 ランジスタと、

前記第 1 ランジスタのゲート - ソース間に設けられたコンデンサと、を備え、

所定行の前記選択期間に、前記所定行の前記画素回路の前記第 2 ランジスタ及び前記第 3 ランジスタをオン状態とするとともに、前記電源走査線に前記発光素子の前記カソード電極の電位以下のチャージ電圧が印加され、前記所定行の前記画素の前記発光素子を介さずに、前記電源走査線から前記所定行の前記画素回路の前記第 1 ランジスタ及び前記第 3 ランジスタを介して前記信号線に前記階調電流を流して、前記所定行の前記画素回路の前記コンデンサに前記階調電流に応じた電荷がチャージされる階調電流ステップと、

40

前記所定行の前記選択期間後に、前記所定行の前記画素回路の前記第 2 ランジスタ及び前記第 3 ランジスタをオフ状態にさせて前記信号線と前記画素とを非導通にして、前記階調電流により前記信号線にチャージされた電荷に応じた電圧をリセット電圧に変位させるリセット電圧ステップと、

前記所定行の前記選択期間後に、前記電源走査線に前記チャージ電圧より高い電源電圧を印加し、前記所定行の前記画素回路の前記コンデンサの電荷に応じて前記所定行の前記画素回路の前記第 1 ランジスタが前記所定行の前記画素の前記発光素子に前記駆動電流を流して前記発光素子を発光する発光ステップと、

50

を有し、

前記階調電流が最高輝度階調電流のときの前記信号線での最高輝度階調電圧は、前記階調電流が最低輝度階調電流のときの前記信号線での最低輝度階調電圧より低く、

前記リセット電圧は、前記最低階調電圧と、前記最高階調電圧と、の中間値となる中間電圧以上に設定されていることを特徴とする。

【0022】

請求項12に記載の発明は、請求項11に記載の表示装置の駆動方法において、

前記発光素子は前記選択期間後に前記階調電流に従って流れる前記駆動電流により発光することを特徴とする。

【0023】

請求項13に記載の発明は、請求項11又は請求項12に記載の表示装置の駆動方法において、

前記リセット電圧ステップは、前記所定行の前記画素分の前記階調電流が前記信号線に流れた後から、次の行の前記画素分の前記階調電流が前記信号線に流れる前までに行われる<sup>10</sup>ことを特徴とする。

【0024】

請求項14に記載の発明は、請求項11に記載の表示装置の駆動方法において、

前記所定行の前記画素における前記画素回路は、

前記所定行の選択期間に、前記信号線に前記階調電流が流れることによって前記階調電流にしたがった電荷を保持する電荷保持手段を有し、<sup>20</sup>

前記第1トランジスタは、前記所定行の発光期間に、前記電荷保持手段により保持された電荷に応じて前記階調電流と等しい電流値の駆動電流を前記発光素子に流し、

前記第2トランジスタ及び前記第3トランジスタは、前記第1トランジスタを介して前記信号線に流れる前記階調電流の流れを制御することを特徴とする。

【0025】

請求項15に記載の発明は、請求項14に記載の表示装置の駆動方法において、

前記所定行の前記画素における前記画素回路の前記第1トランジスタは、前記所定行の選択期間に、前記第3トランジスタを介して前記信号線に流れる前記階調電流を流して、前記電荷保持手段に電荷を保持させる機能と、<sup>30</sup>

前記所定行の発光期間に、前記第3トランジスタに前記階調電流を流すことを停止する機能と、

を有することを特徴とする。

請求項16に記載の発明は、請求項11に記載の表示装置の駆動方法において、

前記リセット電圧は、前記発光素子が最高階調輝度で発光するときに前記発光素子に流れる最高階調駆動電流に等しい電流値となる前記最高輝度階調電流によって前記信号線にチャージされる電荷にしたがって定常化される前記最高階調電圧よりも高く設定されていることを特徴とする。

請求項17に記載の発明は、請求項11に記載の表示装置の駆動方法において、

前記駆動電流の電流値は、前記階調電流の電流値に等しいことを特徴とする。

【0026】

【発明の実施の形態】

〔第一の実施の形態〕

以下に、図面を用いて本発明の具体的な態様について説明する。ただし、発明の範囲を図示例に限定するものではない。

【0027】

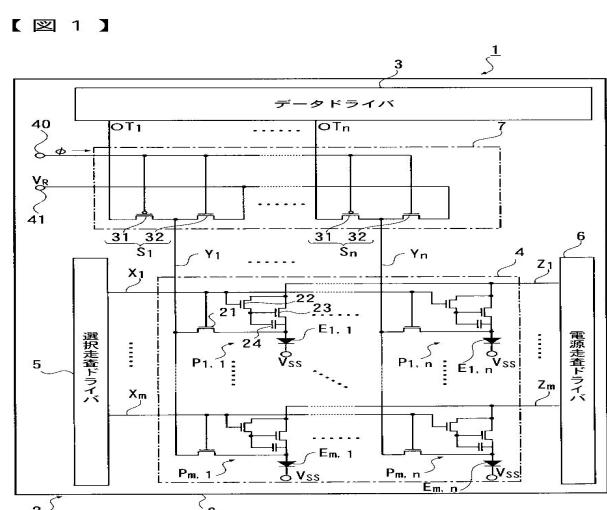

図1は、本発明の適用された有機ELディスプレイを示した図面である。図1に示すように、有機ELディスプレイ1は、基本構成として、アクティブマトリクス駆動方式によりカラー表示を行う有機EL表示パネル2と、有機EL表示パネル2に階調指定シンク電流（階調電流）を流させるデータドライバ3と、を備える。ここでシンク電流とは、後述する画素P<sub>1,1</sub>～P<sub>m,n</sub>のそれぞれから信号線Y<sub>1</sub>～Y<sub>n</sub>のそれぞれ方向へ流れる電流である。<sup>40</sup>

10

20

30

40

50

## 【0028】

有機EL表示パネル2は、透明基板8と、画像が実質的に表示される表示部4と、表示部4の周辺に設けられた選択走査ドライバ5、電源走査ドライバ6及び電流電圧切替部7とを基本構成としており、これらの回路4～7が透明基板8上に形成されている。

## 【0029】

表示部4においては、(m×n)個の画素P<sub>1,1</sub>～P<sub>m,n</sub>がマトリクス状に透明基板8上に設けられており、縦方向(列方向)にm個の画素P<sub>i,j</sub>が配列され、横方向(行方向)にn個の画素P<sub>i,j</sub>が配列されている。ここで、m, nは1以上の整数であり、iは1以上m以下の或る整数であり、jは1以上n以下の或る整数であり、縦にi番目(つまり、i行目)であって横にj番目(つまり、j列目)である画素を画素P<sub>i,j</sub>と記す。

10

## 【0030】

また、表示部4には、第一走査線としてのm本の選択走査線X<sub>1</sub>～X<sub>m</sub>と、第二走査線としてのm本の電源走査線Z<sub>1</sub>～Z<sub>m</sub>と、n本の信号線Y<sub>1</sub>～Y<sub>n</sub>とが配設されている。m本の選択走査線X<sub>1</sub>～X<sub>m</sub>は、横方向に延在し、透明基板8上に設けられている。電源走査線Z<sub>1</sub>～Z<sub>m</sub>が選択走査線X<sub>1</sub>～X<sub>m</sub>に対して交互に配列されている。また、信号線Y<sub>1</sub>～Y<sub>n</sub>は、縦方向に延在し、透明基板8上に設けられている。これら選択走査線X<sub>1</sub>～X<sub>m</sub>、電源走査線Z<sub>1</sub>～Z<sub>m</sub>及び信号線Y<sub>1</sub>～Y<sub>n</sub>間の交差している箇所は層間絶縁膜等によって互いに絶縁されている。選択走査線X<sub>i</sub>及び電源走査線Z<sub>i</sub>には、横方向に配列されたn個の画素P<sub>i,1</sub>～P<sub>i,n</sub>が接続されており、信号線Y<sub>j</sub>には、縦方向に配列されたm個の画素P<sub>1,j</sub>～P<sub>m,j</sub>が接続されており、選択走査線X<sub>i</sub>及び電源走査線Z<sub>i</sub>と信号線Y<sub>j</sub>との交差部に画素P<sub>i,j</sub>が配されている。

20

## 【0031】

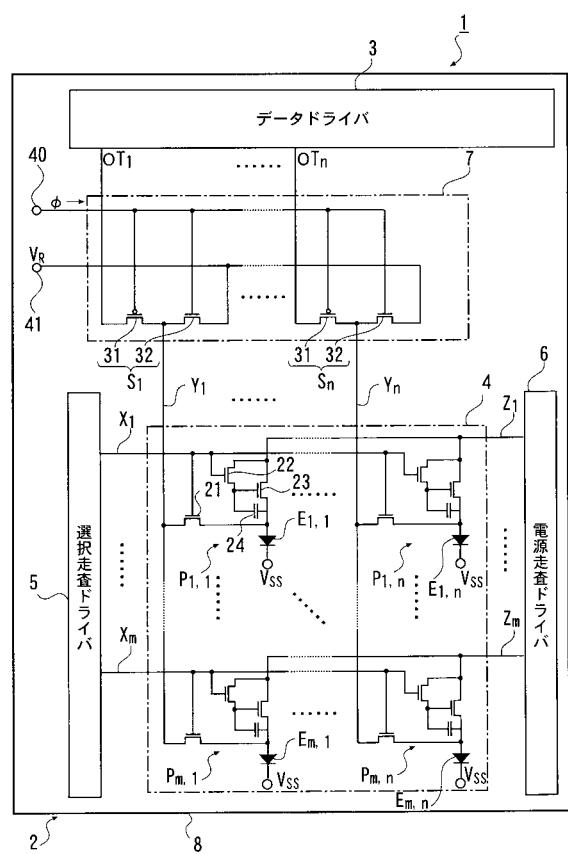

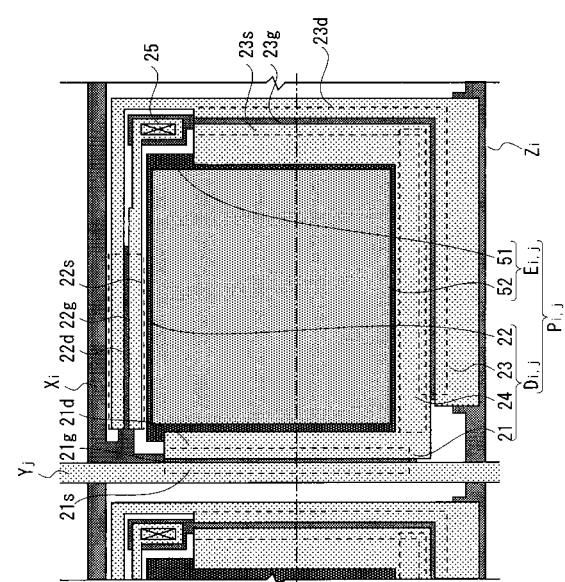

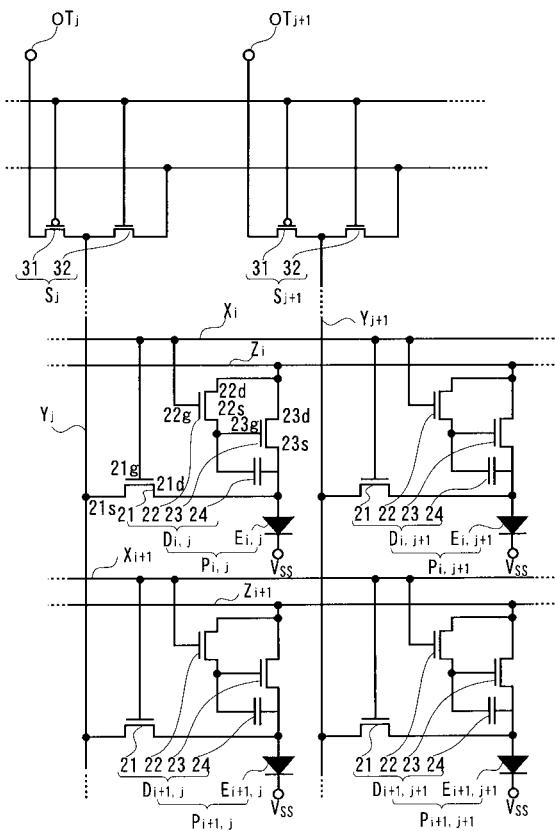

次に、図2及び図3を用いて各画素P<sub>i,j</sub>について説明する。図2は画素P<sub>i,j</sub>を示した平面図であり、図3は四つの画素P<sub>i,j</sub>, P<sub>i+1,j</sub>, P<sub>i,j+1</sub>, P<sub>i+1,j+1</sub>の等価回路図である。

## 【0032】

画素P<sub>i,j</sub>は、駆動電流のレベルに従った輝度で発光する有機EL素子E<sub>i,j</sub>と、有機EL素子E<sub>i,j</sub>の周辺に設けられているとともに有機EL素子E<sub>i,j</sub>を駆動する画素回路D<sub>i,j</sub>と、から構成されている。画素回路D<sub>i,j</sub>は、データドライバ3、選択走査ドライバ5及び電源走査ドライバ6から出力された信号に基づいて、有機EL素子E<sub>i,j</sub>の電流をオン・オフしたり、一定の発光期間中に駆動電流のレベルを保持することで有機EL素子E<sub>i,j</sub>の発光輝度を一定に保ったりするものである。

30

## 【0033】

有機EL素子E<sub>i,j</sub>は、透明基板8上にアノード電極51、有機EL層52、カソード電極(図示略)が順に積層した積層構造となっている。

## 【0034】

アノード電極51は画素P<sub>i,j</sub>ごとにパターニングされており、信号線Y<sub>1</sub>～Y<sub>n</sub>と選択走査線X<sub>1</sub>～X<sub>m</sub>に囲まれる各囲繞領域に形成されている。

## 【0035】

アノード電極51は、導電性を有しているとともに、可視光に対して透過性を有している。また、アノード電極51は、比較的仕事関数の高いものであり、有機EL層52へ正孔を効率よく注入するものが好ましい。例えば、アノード電極51としては、錫ドープ酸化インジウム(ITO)、亜鉛ドープ酸化インジウム(IZO)、酸化インジウム(In<sub>2</sub>O<sub>3</sub>)、酸化スズ(SnO<sub>2</sub>)又は酸化亜鉛(ZnO)を主成分としたものがある。

40

## 【0036】

各々のアノード電極51上に有機EL層52が成膜されている。有機EL層52も画素P<sub>i,j</sub>ごとにパターニングされている。有機EL層52は、例えば、アノード電極51から順に正孔輸送層、狭義の発光層、電子輸送層となる三層構造であっても良いし、アノード電極51から順に正孔輸送層、狭義の発光層となる二層構造であっても良いし、狭義の発光層からなる一層構造であっても良いし、これらの層構造において適切な層間に電子或い

50

は正孔の注入層が介在した積層構造であっても良いし、その他の層構造であっても良い。

【0037】

有機EL層52は、正孔及び電子を注入する機能、正孔及び電子を輸送する機能、正孔と電子の再結合により励起子を生成して赤色、緑色又は青色の何れかに発光する機能を有する広義の発光層である。つまり、画素 $P_{i,j}$ が赤である場合にはその画素 $P_{i,j}$ の有機EL層52は赤色に発光し、画素 $P_{i,j}$ が緑である場合にはその画素 $P_{i,j}$ の有機EL層52は緑色に発光し、画素 $P_{i,j}$ が青である場合にはその画素 $P_{i,j}$ の有機EL層52は青色に発光する。

【0038】

また、有機EL層52は、電子的に中立な有機化合物であることが望ましく、これにより正孔及び電子が有機EL層52でバランス良く注入及び輸送される。また、電子輸送性の物質が狭義の発光層に適宜混合されていても良いし、正孔輸送性の物質が狭義の発光層に適宜混合されても良いし、電子輸送性の物質及び正孔輸送性の物質が狭義の発光層に適宜混合されていても良い。

10

【0039】

有機EL層52上にカソード電極が形成されている。カソード電極は、全ての画素 $P_{1,1} \sim P_{m,n}$ に共通の層となる共通電極であっても良いし、画素電極として画素 $P_{i,j}$ ごとにパターニングさせて、アノード電極を共通電極としても良い。カソード電極は、仕事関数の低い材料で形成されており、例えば、インジウム、マグネシウム、カルシウム、リチウム若しくはバリウム又はこれらの少なくとも一種を含む合金若しくは混合物等で形成されている。また、カソード電極は、以上の各種材料の層が積層された積層構造となっていても良く、また、以上の各種材料の層上に例えばアルミニウム、クロム等といった高仕事関数で且つ低抵抗の材料が被覆された積層構造となっていても良い。また、カソード電極は、可視光に対して遮光性を有するとともに可視光に対して高い反射性を有することで、鏡面として作用するのが望ましいが、アノード電極が不透明電極の場合にはカソード電極を透明にすることで表示パネルとして利用することができる。

20

【0040】

以上のように積層構造となる有機EL素子 $E_{i,j}$ では、アノード電極51とカソード電極との間に順バイアス電圧が印加されると、正孔がアノード電極51から有機EL層52へ注入され、電子がカソード電極から有機EL層52に注入される。そして、有機EL層52で正孔及び電子が輸送されて、有機EL層52にて正孔及び電子が再結合することによって励起子が生成され、励起子が有機EL層52内の蛍光体を励起して、有機EL層52内にて光が発する。

30

【0041】

有機EL素子 $E_{i,j}$ の発光輝度は、有機EL素子 $E_{i,j}$ に流れる電流のレベル（電流値）に依存し、電流レベルの増大にしたがって発光輝度が増大する。有機EL素子 $E_{i,j}$ の発光期間中に有機EL素子 $E_{i,j}$ の発光輝度を一定に保ったり、データドライバ3を流れる階調指定シンク電流に従った発光輝度にしたりするために、有機EL素子 $E_{i,j}$ の電流レベル（電流値）を制御する画素回路 $D_{i,j}$ が画素 $P_{i,j}$ ごとに有機EL素子 $E_{i,j}$ の周囲に設けられている。

40

【0042】

各画素回路 $D_{i,j}$ は、三つの薄膜トランジスタ（以下、トランジスタと記述する。） $21, 22, 23$ と、コンデンサ $24$ とを備える。

【0043】

トランジスタ $21, 22, 23$ は、ゲート電極、ドレイン電極、ソース電極、半導体層、不純物半導体層、ゲート絶縁膜等から構成されたMOS型の電界効果トランジスタであり、特にアモルファスシリコンを半導体層としたa-Siトランジスタであるが、ポリシリコンを半導体層としたp-Siトランジスタであってもよい。また、トランジスタ $21, 22, 23$ の構造は逆スタガ型であっても良いし、コプラナ型であっても良い。なお、ゲート電極、ドレイン電極、ソース電極、半導体層、不純物半導体層、ゲート絶縁膜等の組

50

成はトランジスタ 21, 22, 23についてそれぞれ同じであり、トランジスタ 21, 22, 23は同一工程で同時に形成されるが、形状、大きさ、寸法、チャネル幅、チャネル長等はトランジスタ 21, 22, 23についてそれぞれ異なる。なお、以下では、トランジスタ 21, 22, 23の何れもがNチャネル型の電界効果トランジスタであるとして説明する。

【0044】

トランジスタ 22のゲート電極 22gは選択走査線  $X_i$  に接続されている。トランジスタ 22のドレイン電極 22dは、トランジスタ 23のドレイン電極 23dに接続されているとともに、電源走査線  $Z_i$  に接続されている。トランジスタ 22のソース電極 22sは、コンタクトホール 25を介してトランジスタ 23のゲート電極 23gに接続されているとともに、コンデンサ 24の一方の電極に接続されている。

10

【0045】

トランジスタ 23のソース電極 23sは、コンデンサ 24の他方の電極に接続されているとともにトランジスタ 21のドレイン電極 21dに接続されている。

【0046】

トランジスタ 21のゲート電極 21gは選択走査線  $X_i$  に接続されており、トランジスタ 21のソース電極 21sは信号線  $Y_j$  に接続されている。トランジスタ 23のソース電極 23s、コンデンサ 24の他方の電極、TF21のドレイン電極 21dは、有機EL素子  $E_{i,j}$  のアノード電極 51に接続されている。有機EL素子  $E_{i,j}$  のカソード電極の電位は、基準電位  $V_{SS}$  であり、本実施形態では、有機EL素子  $E_{i,j}$  のカソード電極が接地されて基準電位  $V_{SS}$  が 0 [V] となっている。

20

【0047】

また、図1、図3に示すように、選択走査線  $X_1 \sim X_m$  は選択走査ドライバ5に接続されており、電源走査線  $Z_1 \sim Z_m$  は電源走査ドライバ6に接続されている。

【0048】

選択走査ドライバ5はいわゆるシフトレジスタである。つまり、選択走査ドライバ5は、外部からのクロック信号に基づいて選択走査線  $X_1$  から選択走査線  $X_m$ への順（走査線  $X_m$  の次は走査線  $X_1$ ）に走査信号を順次出力することで、所定時間（詳細には後述するリセット期間  $T_{RESET}$ ）を空けて走査線  $X_1 \sim X_m$ を順次選択するものである。

【0049】

30

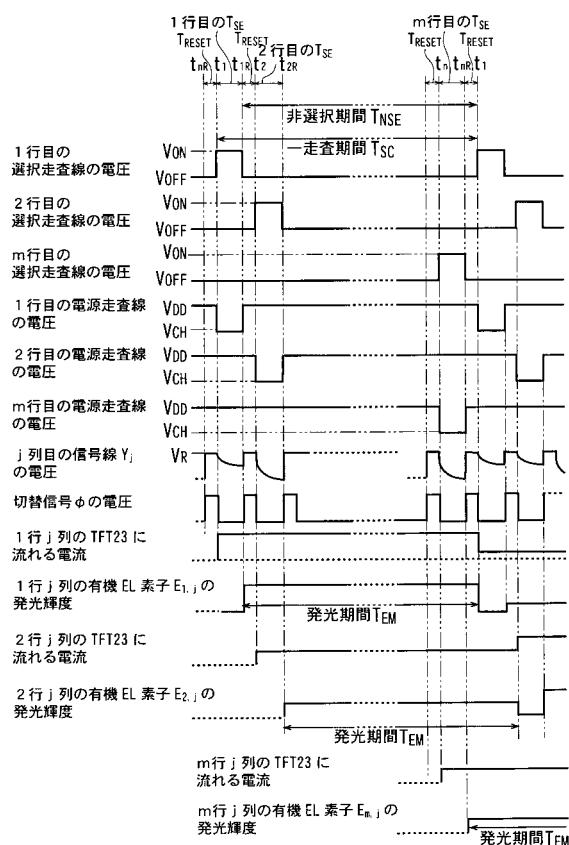

詳細には図5に示すように、選択走査ドライバ5は、ハイレベルのオン電圧  $V_{ON}$ （例えば基準電位  $V_{SS}$  より十分高い。）又はローレベルのオフ電圧  $V_{OFF}$ （例えば基準電位  $V_{SS}$  以下である。）の何れかのレベルの電圧を選択走査線  $X_1 \sim X_m$ に個別に印加することによって、所定周期で各選択走査線  $X_i$ を選択する。

【0050】

即ち、選択走査線  $X_i$  が選択される選択期間  $T_{SE}$  では、選択走査ドライバ5がオン電圧  $V_O$  のパルス信号を選択走査線  $X_i$  に出力することにより、選択走査線  $X_i$  に接続されたトランジスタ 21, 22（画素回路  $D_{i,1} \sim D_{i,n}$  全てのトランジスタ 21, 22である。）がオン状態になる。トランジスタ 21がオン状態になることによって信号線  $Y_j$  に流れる電流が画素回路  $D_{i,j}$  に流れ得るようになる。一方、選択期間  $T_{SE}$  以外の非選択期間  $T_{NSE}$  では、オフ電圧  $V_{OFF}$  を走査線  $X_i$  に印加することにより、トランジスタ 21, 22がオフ状態になる。トランジスタ 21がオフ状態になることで、信号線  $Y_j$  に流れる電流は画素回路  $D_{i,j}$  に流れ得ないようになる。

40

【0051】

ここで、 $T_{SE} + T_{NSE} = T_{SC}$  で表される期間が一走査期間であり、選択走査線  $X_1 \sim X_m$  の選択期間  $T_{SE}$  は互いに重ならない。また、 $i$  行目の選択期間  $T_{SE}$  から  $(i+1)$  行目の選択期間  $T_{SE}$  までは続いておらず、 $i$  行目の選択期間  $T_{SE}$  と  $(i+1)$  行目の選択期間  $T_{SE}$  との間には、選択期間  $T_{SE}$  より短い期間  $T_{RESET}$  が存する。つまり、選択走査ドライバ5は、 $i$  行目の選択走査線  $X_i$  にオン電圧  $V_{ON}$  のパルス信号を出力し終えてから期間  $T_{RESET}$  だけ経過したら、 $(i+1)$  行目の選択走査線  $X_{i+1}$  にオン電圧  $V_{ON}$  のパルス信号を出力

50

する。これにより、 $i$  行目の選択が終了してから期間  $T_{RESET}$  経過後に  $i + 1$  行目が選択される。以下では、期間  $T_{RESET}$  をリセット期間と述べる。

#### 【0052】

なお、詳細については後述するが、選択走査線  $X_1 \sim X_m$  が選択されている各々の選択期間  $T_{SE}$  の時に、データドライバ3が全ての出力端子  $OT_1 \sim OT_n$  へ階調指定シンク電流を流すことによって、全ての信号線  $Y_1 \sim Y_n$  に階調指定シンク電流が流れる。階調指定シンク電流とは、データドライバ3が信号線  $Y_1 \sim Y_n$  からそれぞれの出力端子  $OT_1 \sim OT_n$  へ流れる電流であり、画像データに従った輝度階調で発光するために各有機EL素子  $E_{1,1} \sim E_{m,n}$  に流れる電流のレベルに等しい。

#### 【0053】

図1、図3に示すように、電源走査ドライバ6は、いわゆるシフトレジスタである。電源走査ドライバ6は、選択走査ドライバ5に同期して電源走査線  $Z_1 \sim Z_m$  を順次選択するものである。つまり、電源走査ドライバ6は、上述の外部からのクロック信号に基づいて電源走査線  $Z_1$  から電源走査線  $Z_m$  への順（電源走査線  $Z_m$  の次は電源走査線  $Z_1$ ）にパルス信号を、選択走査ドライバ5の同一行のオン電圧  $V_{ON}$  のパルス信号に同期して順次出力することで、リセット期間  $T_{RESET}$  を空けて電源走査線  $Z_1 \sim Z_m$  を順次選択するものである。

10

#### 【0054】

詳細には図5に示すように、電源走査ドライバ6は、ローレベルのチャージ電圧  $V_{CH}$ （基準電位  $V_{SS}$  と等電圧、又は基準電位  $V_{SS}$  未満である。）を所定周期で各電源走査線  $Z_i$  に印加する。即ち、各選択走査線  $X_i$  が選択される選択期間  $T_{SE}$  では、電源走査ドライバ6がローレベルのチャージ電圧  $V_{CH}$  を電源走査線  $Z_i$  に印加する。一方、非選択期間  $T_{NSE}$  では、電源走査ドライバ6は、チャージ電圧  $V_{CH}$  より高いハイレベルの電源電圧  $V_{DD}$  を電源走査線  $Z_i$  に印加する。電源電圧  $V_{DD}$  は基準電位  $V_{SS}$  及びリセット電位  $V_R$  より高く、トランジスタ23がオン状態となっており、トランジスタ21がオフ状態となつていれば、電源走査線  $Z_i$  から有機EL素子  $E_{i,j}$  へと電流が流れる。

20

#### 【0055】

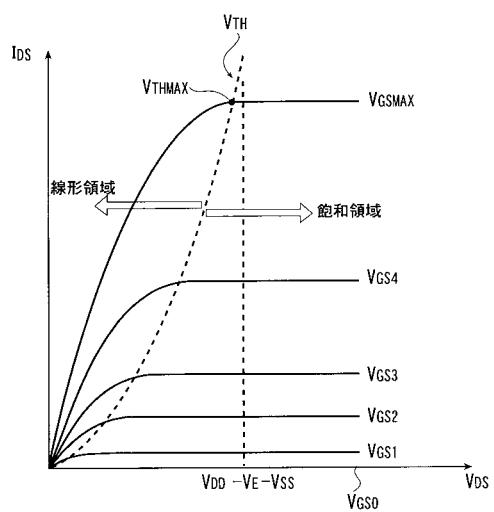

電源電圧  $V_{DD}$  について説明する。図4は、Nチャネル型の電界効果トランジスタ23の電流-電圧特性を表したグラフである。図4において、横軸はドレイン-ソース間の電圧レベル（電圧値）であり、縦軸はドレイン-ソース間の電流レベル（電流値）である。図中の線形領域（ソース-ドレイン間電圧レベル  $V_{DS} <$  ドレイン飽和閾電圧レベル  $V_{TH}$  : ドレイン飽和閾電圧レベル  $V_{TH}$  はゲート-ソース間電圧レベル  $V_{GS}$  に従っている。）では、ゲート-ソース間電圧レベル  $V_{GS}$  が一定であると、ソース-ドレイン間電圧レベル  $V_{DS}$  が大きくなるにつれてソース-ドレイン間電流レベル  $I_{DS}$  が大きくなる。更に、図中の飽和領域（ソース-ドレイン間電圧レベル  $V_{DS} >$  ドレイン飽和閾電圧レベル  $V_{TH}$  ）、ゲート-ソース間電圧レベル  $V_{GS}$  が一定であると、ソース-ドレイン間電圧レベル  $V_{DS}$  が大きくなつてもソース-ドレイン間電流レベル  $I_{DS}$  はほぼ一定となる。

30

#### 【0056】

また、図4において、ゲート-ソース間電圧レベル  $V_{GS0} \sim V_{GSMAX}$  は、 $V_{GS0} = 0 < V_{GS1} < V_{GS2} < V_{GS3} < V_{GS4} < V_{GSMAX}$  の関係となっている。つまり、図4から明らかなように、ドレイン-ソース間電圧レベル  $V_{DS}$  が一定の場合、ゲート-ソース間電圧レベル  $V_{GS}$  が大きくなるにつれて、線形領域、飽和領域のいずれであってもドレイン-ソース間電流レベル  $I_{DS}$  が大きくなる。更に、ゲート-ソース間電圧値  $V_{GS}$  が大きくなるにつれて、ドレイン飽和閾電圧レベル  $V_{TH}$  が大きくなる。

40

#### 【0057】

以上のことから、線形領域では、ソース-ドレイン間電圧レベル  $V_{DS}$  がわずかに変わるとソース-ドレイン間電流レベル  $I_{DS}$  が変わってしまうが、飽和領域では、ゲート-ソース間電圧レベル  $V_{GS}$  が定まれば、ソース-ドレイン間電圧レベル  $V_{DS}$  に関わらずドレイン-ソース間電流レベル  $I_{DS}$  が一義的に定まる。

#### 【0058】

ここで、トランジスタ23がゲート-ソース間最大電圧レベル  $V_{GSMAX}$  であるときのドレ

50

イン - ソース間電流レベル  $I_{DS}$  は、最高輝度で発光する有機 EL 素子  $E_{i,j}$  のアノード電極 51 とカソード電極との間に流れる電流レベルに設定されている。

また、トランジスタ 23 のゲート - ソース間電圧レベル  $V_{GS}$  が最大レベル  $V_{GSMAX}$  であつても、トランジスタ 23 が飽和領域を維持するように、下記に示す条件式を満たしている。

$$V_{DD} - V_E - V_{SS} \geq V_{THMAX}$$

ここで、 $V_E$  は、有機 EL 素子  $E_{i,j}$  の発光寿命期間中に有機 EL 素子  $E_{i,j}$  の高抵抗化のために徐々に高くなる、最高輝度時の有機 EL 素子  $E_{i,j}$  に分圧される予想最大の電圧レベルであり、 $V_{THMAX}$  は、 $V_{GSMAX}$  時のトランジスタ 23 のソース - ドレイン間の飽和閾電圧レベルである。以上の条件式を満たすように電源電圧  $V_{DD}$  を定める。

10

#### 【 0059 】

図 1、図 3 に示すように、信号線  $Y_1 \sim Y_n$  は電流電圧切替部 7 に接続されている。詳細には、電流電圧切替部 7 は、切替回路  $S_1 \sim S_n$  で構成されており、信号線  $Y_1 \sim Y_n$  が切替回路  $S_1 \sim S_n$  にそれぞれ接続されており、更にデータドライバ 3 の出力端子  $OT_1 \sim OT_n$  が切替回路  $S_1 \sim S_n$  にそれぞれ接続されている。切替回路  $S_1 \sim S_n$  に切替信号入力端子 40 が接続されており、切替信号 が切替回路  $S_1 \sim S_n$  に入力される。また、切替回路  $S_1 \sim S_n$  にリセット電圧入力端子 41 が接続されており、リセット電圧  $V_R$  が切替回路  $S_1 \sim S_n$  に印加される。

#### 【 0060 】

リセット電圧  $V_R$  は、選択期間  $T_{SE}$  に各有機 EL 素子  $E_{1,1} \sim E_{m,n}$  が最も明るい最高階調輝度  $L_{MAX}$  で発光するときに各有機 EL 素子  $E_{1,1} \sim E_{m,n}$  に流れる最高階調駆動電流  $I_{MAX}$  に等しい電流値となる階調指定シンク電流によって信号線  $Y_1 \sim Y_n$  にチャージされる電荷にしたがって定常化される最高階調電圧  $V_{hsb}$  より高い電圧に設定されている。リセット電圧  $V_R$  は、各有機 EL 素子  $E_{1,1} \sim E_{m,n}$  が最も暗い最低階調輝度  $L_{MIN}$  ( ただし電流レベルが 0 A を越える ) のときに各有機 EL 素子  $E_{1,1} \sim E_{m,n}$  に流れる最低階調駆動電流  $I_{MIN}$  に等しい電流値となる階調指定シンク電流によって信号線  $Y_1 \sim Y_n$  にチャージされる電荷にしたがって定常化される最低階調電圧  $V_{lsb}$  と、最高階調電圧  $V_{hsb}$  と、の中間値となる中間電圧以上が望ましく、最低階調電圧  $V_{lsb}$  と等しい値か或いは最低階調電圧  $V_{lsb}$  以上がさらに望ましい。

20

#### 【 0061 】

切替回路  $S_j$  ( 切替回路  $S_j$  は、 $j$  列目の信号線  $Y_j$  に接続されている。 ) は、データドライバ 3 の出力端子  $OT_j$  からの信号に応じた電流を信号線  $Y_j$  に流させることと、リセット電圧入力端子 41 から所定電圧レベルのリセット電圧  $V_R$  を信号線  $Y_j$  に出力することとの何れか一方に切り替えるものである。つまり、切替信号入力端子 40 から切替回路  $S_j$  へ入力する切替信号 がハイレベルの場合には、切替回路  $S_j$  は出力端子  $OT_j$  のシンク電流を遮断するとともにリセット電圧入力端子 41 からのリセット電圧を信号線  $Y_j$  に出力する。一方、切替信号入力端子 40 から切替回路  $S_j$  へ入力する切替信号 がローレベルの場合には、切替回路  $S_j$  は出力端子  $OT_j$  と信号線  $Y_j$  との間にシンク電流を流すとともにリセット電圧入力端子 41 からのリセット電圧  $V_R$  を遮断する。

30

#### 【 0062 】

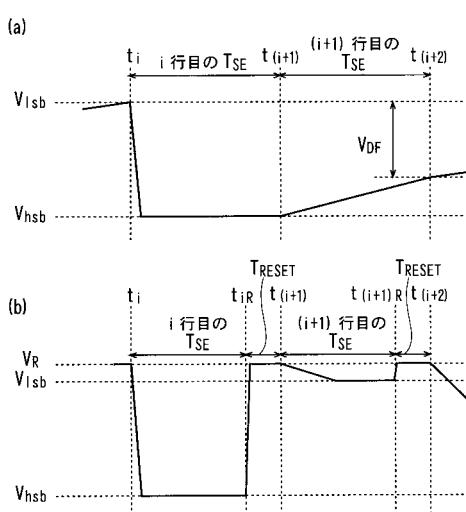

ここで、従来の電流シンク指定方式では、図 6 ( a ) に示すように、例えば  $i$  行目画素  $P_{i,j}$  を最高階調で発光するために、信号線  $Y_j$  に最大の電流レベル ( 電流値 ) のシンク電流を  $i$  行目の選択期間  $T_{SE}$  の間に流したとすると、この電流レベルに見合った電荷をコンデンサ 24 にチャージしたときの信号線  $Y_j$  にかかる最高階調電圧  $V_{hsb}$  は、基準電位  $V_{SS}$  やチャージ電圧  $V_{CH}$  よりも相対的に十分低くなっている。そして次の (  $i+1$  ) 行目の画素  $P_{i+1,j}$  をに最低階調輝度で発光させるために、信号線  $Y_j$  に最小の電流レベル ( 電流値 ) のシンク電流 ( ただし無電流ではない ) を流そうとすると、この電流レベルに見合った電荷をコンデンサ 24 にチャージしたときの信号線  $Y_j$  にかかる電圧をチャージ電圧  $V_{CH}$  に近似する程度に高くさせなければならないが、信号線  $Y_j$  に流れる電流レベルが極小のために信号線  $Y_j$  が単位時間に変位する電位差が小さくなってしまうので、信号線  $Y_j$  の電位

40

50

を最高階調電圧  $V_{hsb}$  から最低階調電圧  $V_{lsb}$  に定常化するまでに時間が掛かってしまう恐れがあり、また選択期間  $T_{SE}$  が短く設定されていると最低階調電圧  $V_{lsb}$  に達することなく電圧  $V_{DF}$  の差が生じてしまい画素  $P_{i+1,j}$  が正確な輝度で発光できなくなるが、本実施の形態では、図 6 (b) に示すように、リセット期間  $T_{RESET}$  に、切替回路  $S_j$  が信号線  $Y_j$  の電位を強制的に最高階調電圧  $V_{hsb}$  よりも十分高いリセット電圧  $V_R$  に切替えてしまうので、選択期間  $T_{SE}$  中に、容量となる信号線  $Y_j$  に蓄積された電荷が迅速に移動するような電流が流れ、信号線  $Y_j$  を速やかに高電位にすることが可能となる。

#### 【 0 0 6 3 】

切替回路  $S_j$  の一例について説明する。切替回路  $S_j$  は、P チャネル型の電界効果トランジスタであるトランジスタ 3 1 と、N チャネル型の電界効果トランジスタであるトランジスタ 3 2 とから構成される。トランジスタ 3 1 のゲート電極及びトランジスタ 3 2 のゲート電極は、切替信号入力端子 4 0 に接続されている。トランジスタ 3 1 のソース電極は信号線  $Y_j$  に接続されており、トランジスタ 3 1 のドレイン電極は出力端子  $OT_j$  に接続されている。トランジスタ 3 2 のドレイン電極は信号線  $Y_j$  に接続されており、トランジスタ 3 2 のソース電極はリセット電圧入力端子 4 1 に接続されている。この構成では、切替信号入力端子 4 0 からの切替信号  $V_{reset}$  がハイレベルの場合に、トランジスタ 3 2 がオン状態になり、トランジスタ 3 1 がオフ状態になる。一方、切替信号入力端子 4 0 からの切替信号  $V_{reset}$  がローレベルの場合に、トランジスタ 3 1 がオン状態になり、トランジスタ 3 2 がオフ状態になる。なお、トランジスタ 3 1 を P チャネル型としトランジスタ 3 2 を N チャネル型に設定して、切替信号  $V_{reset}$  のハイ・ローを逆位相にして切替回路  $S_j$  のスイッチングを切り替えるてもよい。

#### 【 0 0 6 4 】

ここで切替信号入力端子 4 0 に入力される切替信号  $V_{reset}$  の周期について説明する。図 5 に示すように、選択走査ドライバ 5 が選択走査線  $X_1 \sim X_m$  のうちの何れかに対してオン電圧  $V_{ON}$  を印加している時に、切替信号入力端子 4 0 に入力される切替信号  $V_{reset}$  がローレベルである。一方、選択走査ドライバ 5 が全ての選択走査線  $X_1 \sim X_m$  にオフ電圧  $V_{OFF}$  を印加している時に（つまり 1 行目から  $m$  行目のうちの何れのリセット期間  $T_{RESET}$  でも）、切替信号入力端子 4 0 に入力される切替信号  $V_{reset}$  がハイレベルである。例えば  $i$  行目分のシンク電流による信号線  $Y_1 \sim Y_n$  の電圧をリセット電圧  $V_R$  にするリセット期間  $T_{RESET}$  は、 $i$  行目の選択期間  $T_{SE}$  の終了時刻  $t_{iR}$  から次の（ $i+1$ ）行目の選択期間  $T_{SE}$  の開始時刻  $t_{i+1}$  までの間となる。つまり、切替信号入力端子 4 0 に入力される切替信号  $V_{reset}$  は、一走査期間  $T_{SC}$  中の  $n$  回のリセット期間  $T_{RESET}$  每にハイレベルになる信号である。なお、切替信号  $V_{reset}$  は、上述の外部から入力されるクロック信号と同周波数であっても良い。

#### 【 0 0 6 5 】

データドライバ 3 は、上述の外部からのクロック信号によって出力端子  $OT_1 \sim OT_n$  へ階調指定シンク電流（階調電流）を流すものである。切替信号入力端子 4 0 に入力される切替信号  $V_{reset}$  がローレベルの時、データドライバ 3 が全ての出力端子  $OT_1 \sim OT_n$  から階調指定シンク電流をパラで流し、切替信号入力端子 4 0 に入力される切替信号  $V_{reset}$  がハイレベルの時、データドライバ 3 がどの出力端子  $OT_1 \sim OT_n$  からも階調指定シンク電流を流さない。

#### 【 0 0 6 6 】

従って、各行の選択期間  $T_{SE}$  では、階調指定シンク電流がそれぞれ信号線  $Y_1 \sim Y_n$  からそれぞれ出力端子  $OT_1 \sim OT_n$  へ流れる。一方、各行のリセット期間  $T_{RESET}$  では、リセット電圧  $V_R$  が信号線  $Y_1 \sim Y_n$  に印加されて定常状態になる。

#### 【 0 0 6 7 】

データドライバ 3 の階調指定シンク電流について詳細に説明すると、データドライバ 3 は、各行の選択期間  $T_{SE}$  において、チャージ電圧  $V_{CH}$  を出力している各電源走査線  $Z_1 \sim Z_m$  からトランジスタ 2 3、トランジスタ 2 1、各信号線  $Y_1 \sim Y_n$ 、各切替回路  $S_1 \sim S_n$  を経てそれぞれの出力端子  $OT_1 \sim OT_n$  に向かう階調指定シンク電流を発生させるものである。階調指定シンク電流のレベルは画像データに従ったレベルである。つまり、階調指定シ

10

20

30

40

50

ンク電流のレベルは、画像データに従った輝度階調で発光するために各有機EL素子 $E_{1,1} \sim E_{m,n}$ に流れる電流のレベルに等しい。

【0068】

次に、以上のように構成される有機ELディスプレイ1の表示動作とその駆動方法について説明する。

【0069】

図5に示すように、選択走査ドライバ5が、入力したクロック信号に基づいて、1行目の選択走査線 $X_1$ から $m$ 行目の選択走査線 $X_m$ へと順次ハイレベル（オン電圧 $V_{ON}$ ）のパルス信号を出力する。同時に、電源走査ドライバ6が、入力したクロック信号に基づいて、1行目の電源走査線 $Z_1$ から $m$ 行目の電源走査線 $Z_m$ へと順次ローレベル（チャージ電圧 $V_{CH}$ ）のパルス信号を出力する。また、各行の選択期間 $T_{SE}$ 中に、データドライバ3が、クロック信号に基づいて、全ての出力端子 $OT_1 \sim OT_n$ からそれぞれの切替回路 $S_1 \sim S_n$ に階調指定シンク電流を出力する。

10

【0070】

また、各行の選択期間 $T_{SE}$ 中に切替信号入力端子40に入力される切替信号がローレベルなので、それぞれの切替回路 $S_1 \sim S_n$ のトランジスタ31がオン状態になるとともに、トランジスタ32がオフ状態になる。一方、各行のリセット期間 $T_{RESET}$ 中に切替信号入力端子に入力される切替信号がハイレベルなので、それぞれの切替回路 $S_1 \sim S_n$ のトランジスタ31がオフ状態になるとともに、トランジスタ32がオン状態になる。つまり、各行の選択期間 $T_{SE}$ では、電流電圧切替部7は、各々の信号線 $Y_1 \sim Y_n$ とリセット電圧入力端子41との間を遮断することで、画像データに従った輝度階調で発光するために各有機EL素子 $E_{1,1} \sim E_{m,n}$ に流れる電流のレベルに等しい階調指定シンク電流を流そうとするとともに各々の信号線 $Y_1 \sim Y_n$ にリセット電圧 $V_R$ に印加しないように機能する。一方、各行のリセット期間 $T_{RESET}$ では、電流電圧切替部7は、各々の信号線 $Y_1 \sim Y_n$ と出力端子 $OT_1 \sim OT_n$ を遮断するとともに、各々の信号線 $Y_1 \sim Y_n$ とリセット電圧入力端子41を接続することで、各々の信号線 $Y_1 \sim Y_n$ の電位を迅速にリセット電圧 $V_R$ にするよう20に機能する。

【0071】

ここで、ハイレベルのパルス信号が選択走査線 $X_i$ に出力されるタイミングは、ローレベルのパルス信号が電源走査線 $Z_i$ に出力されるタイミングにほぼ揃っており、ハイレベルのパルス信号とローレベルのパルス信号の時間的長さはほぼ同じであり、時刻 $t_i$ ～時刻 $t_{iR}$ の間（この期間が $i$ 行目の選択期間 $T_{SE}$ である。）にパルス信号が出力されている。つまり、選択走査ドライバ5から出力されるオンレベルのパルス信号がシフトしていく周期は、電源走査ドライバ6から出力されるチャージ電圧 $V_{CH}$ レベルのパルス信号がシフトしていく周期に同期している。また、オンレベルのパルス信号が選択走査線 $X_i$ に出力されている時に、切替信号入力端子40に入力される切替信号がローレベルになっているから、トランジスタ31がオン状態になる。

30

【0072】

このように、選択期間 $T_{SE}$ 中に電源走査線 $Z_i$ に出力される電圧は基準電位 $V_{SS}$ 以下となるために、各有機EL素子 $E_{i,1} \sim E_{i,n}$ には階調指定シンク電流が流れることがないので階調に見合った電流レベルの階調指定シンク電流が信号線 $Y_1 \sim Y_n$ からデータドライバ3へ流れ、発光期間 $T_{EM}$ にこれら階調指定シンク電流に等しい電流レベルの電流がトランジスタ23及び各有機EL素子 $E_{i,1} \sim E_{i,n}$ に流れるようにコンデンサ24に電荷がチャージされることが可能となる。これにより、1行目から $m$ 行目までのうち、選択走査ドライバ5からハイレベルのパルス信号が出力されている行が、所謂選択されている行であり、選択されている際にその行の各画素が所定の階調で表示されるようにコンデンサ24への階調電荷が更新される。

40

【0073】

以上のように選択走査ドライバ5及び電源走査ドライバ6が1行目から $m$ 行目へと線順次にパルス信号をシフトしていくことによって、1行目の画素 $P_{1,1} \sim P_{1,n}$ から $m$ 行目の画

50

素  $P_{m,1} \sim P_{m,n}$  へとデータドライバ 3 の階調指定シンク電流に基づいて順次更新されていく。このような線順次の走査が繰り返されることで、有機 EL 表示パネル 2 の表示部 4 で画像表示が為される。

【0074】

ここで、一走査期間  $T_{SC}$  における選択された  $i$  行目の画素  $P_{i,1} \sim P_{i,n}$  の更新、選択された  $i$  行目の画素  $P_{i,1} \sim P_{i,n}$  の階調表現について説明する。

【0075】

$i$  行目の選択期間  $T_{SE}$  では、選択走査ドライバ 5 から  $i$  行目の選択走査線  $X_i$  にハイレベルのパルス信号が出力されることで、選択走査線  $X_i$  に接続された全ての画素回路  $D_{i,1} \sim D_{i,n}$  のトランジスタ 21 及びトランジスタ 22 が選択期間  $T_{SE}$  の間オン状態となる。

10

更に、 $i$  行目の選択期間  $T_{SE}$  では、電源走査ドライバ 6 から  $i$  行目の電源走査線  $Z_i$  に、基準電位  $V_{SS}$  と同じ又はそれより低いチャージ電圧  $V_{CH}$  としてローレベルのパルス信号が印加される。そして、トランジスタ 22 がオン状態となっているので、トランジスタ 23 のゲート電極 23g にも電圧が印加され、トランジスタ 23 がオン状態となる。

【0076】

一方、 $i$  行目の選択期間  $T_{SE}$  中に切替信号入力端子 40 に入力される切替信号 がローレベルになっているから、全ての切替回路  $S_1 \sim S_n$  のトランジスタ 31 がオン状態となっており、トランジスタ 32 がオフ状態となっている。更に、 $i$  行目の選択期間中にデータドライバ 3 に入力される画像データにしたがって、 $i$  行目の全ての画素回路  $D_{i,1} \sim D_{i,n}$  では電源走査線  $Z_i$  トランジスタ 23 トランジスタ 21 トランジスタ 31 データドライバ 3 へと階調指定シンク電流が流れ、発光期間  $T_{EM}$  にトランジスタ 23 のソース - ドレイン間電流が階調指定シンク電流レベルになるようにコンデンサ 24 に電荷がチャージされるようになる。このとき 1 列目から  $n$  列目の何れの列においても、階調指定シンク電流のレベルは発光期間  $T_{EM}$  に各有機 EL 素子  $E$  に流れる電流のレベルである。

20

【0077】

$i$  行目の選択期間  $T_{SE}$  中に電源走査線  $Z_i$  トランジスタ 23 トランジスタ 21 信号線  $Y$  トランジスタ 31 データドライバ 3 へと一定レベルの階調指定シンク電流が流れることによって、 $i$  行目の選択期間  $T_{SE}$  中に電源走査線  $Z_i$  トランジスタ 23 トランジスタ 21 信号線  $Y$  トランジスタ 31 データドライバ 3 における電圧が定常状態になる。

30

【0078】

つまり、トランジスタ 23 に階調指定シンク電流が流れ電源走査線  $Z_i$  トランジスタ 23 トランジスタ 21 信号線  $Y$  トランジスタ 31 データドライバ 3 における電圧が定常状態になることによって、トランジスタ 23 に流れる階調指定シンク電流のレベルに従ったレベルの電圧がトランジスタ 23 のゲート電極 23g とソース電極 23s との間に印加され、トランジスタ 23 のゲート電極 23g とソース電極 23s との間の電圧のレベルに従った大きさの電荷がコンデンサ 24 にチャージされる。換言すれば、 $i$  行目の選択期間  $T_{SE}$  において  $i$  行目の各々の画素回路  $D_{i,1} \sim D_{i,n}$  では、トランジスタ 21 及びトランジスタ 22 が、信号線  $Y_i$  に流れる階調指定シンク電流をトランジスタ 23 に流すよう機能し、トランジスタ 23 が、階調指定シンク電流レベルをゲート - ソース間電圧のレベルに変換するように機能し、コンデンサ 24 が、変換されたゲート - ソース間電圧のレベルを保持するように機能する。

40

【0079】

ここで、信号線  $Y_j$  の静電容量を  $c$  とすると、電圧  $v$  で信号線  $Y_j$  に充電される電荷  $Q$  は、

$$Q = c v \quad \dots (1)$$

となり、

$dQ = c \cdot d v \quad \dots (2)$

となる。

【0080】

なお、所定の画素  $P_{i,j}$  の階調指定シンク電流のレベルを  $I_{data}$  とすると ( $I_{data}$  は選択

50

期間中  $T_{SE}$  では一定である。)、電源走査線  $Z_i$  ~ トランジスタ 23 ~ トランジスタ 21 ~ 信号線  $Y_j$  ~ トランジスタ 31 ~ データドライバ 3 における電圧が定常状態になるまでの時間  $d_t$  は、以下の式が成立する。

$$d_t = dQ / I_{data} \dots (3)$$

$dQ$  は時間  $d_t$  における信号線  $Y_j$  の電荷の変化量でもあり、電位差  $dV$  における信号線  $Y_j$  の電荷の変化量でもある。以上に表されるように、 $I_{data}$  が小さくなるに連れて  $d_t$  が長くなり、 $dQ$  が大きくなるに連れて  $d_t$  が長くなる。

#### 【0081】

以上のように、 $i$  行目の選択期間  $T_{SE}$  中において、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  のコンデンサ 24 にチャージされる電荷の大きさが前回の一走査期間  $T_{SC}$  から更新されるとともに、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  のトランジスタ 23 の電流レベルも前回の一走査期間  $T_{SC}$  から更新される。10

#### 【0082】

ここで、トランジスタ 23 トランジスタ 21 信号線  $Y_j$  までの間の任意の点での電位は、経時変化するトランジスタ 21, 22, 23 の内部抵抗等に因って変化してしまう。しかしながら、本実施形態では、トランジスタ 23 トランジスタ 21 信号線  $Y_j$  へと流れる階調指定シンク電流のレベルは、トランジスタ 21, 22, 23 の内部抵抗が経時変化しても、トランジスタ 23 トランジスタ 21 信号線  $Y_j$  へと流れる階調指定シンク電流のレベルは所望通りとなる。

#### 【0083】

また、 $i$  行目の選択期間  $T_{SE}$  では、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  のカソード電極は基準電位  $V_{SS}$  であり、電源走査線  $Z_i$  は基準電位  $V_{SS}$  と同じ又は基準電位  $V_{SS}$  より低いチャージ電圧  $V_{CH}$  であるため、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  には逆バイアス電圧が印加されるから、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  には電流が流れず、有機 EL 素子  $E_{i,1} \sim E_{i,n}$  は発光しない。そして信号線  $Y_1 \sim Y_n$  に流れる階調指定シンク電流により信号線  $Y_1 \sim Y_n$  はチャージ電圧  $V_{CH}$  よりも低くなつて定常化し、有機 EL 素子  $E_{i,1} \sim E_{i,n}$  に駆動電流を流すための各コンデンサ 24 へのチャージは、各信号線  $Y_1 \sim Y_n$  からデータドライバ 3 に流す階調指定シンク電流で一義的に決まる。20

#### 【0084】

続いて、 $i$  行目の選択期間  $T_{SE}$  の終了時刻  $t_{iR}$  (つまり  $i$  行目の非選択期間  $T_{NSE}$  の開始時刻) では、選択走査ドライバ 5 から選択走査線  $X_i$  に出力されるハイレベルのパルス信号が終了し、電源走査ドライバ 6 から電源走査線  $Z_i$  に出力されるローレベルのパルス信号が終了する。つまり、この終了時刻  $t_{iR}$  から次の  $i$  行目の選択期間  $T_{SE}$  の開始時刻  $t_{i+1}$  までの非選択期間  $T_{NSE}$  では、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  のトランジスタ 21 のゲート電極 21g 及びトランジスタ 22 のゲート電極 22g に対してオフ電圧  $V_{OFF}$  が選択走査ドライバ 5 によって印加されるとともに、電源電圧  $V_{DD}$  が電源走査ドライバ 6 によって電源走査線  $Z_i$  に印加される。30

#### 【0085】

このため、 $i$  行目の非選択期間  $T_{NSE}$  では、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  のトランジスタ 21 がオフ状態になり、電源走査線  $Z_i$  から信号線  $Y_1 \sim Y_n$  へ流れる階調指定シンク電流を遮断する。更に、 $i$  行目の非選択期間  $T_{NSE}$  では、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  に何れにおいても、トランジスタ 22 がオフ状態になつても、直前の  $i$  行目の選択期間  $T_{SE}$  においてコンデンサ 24 にチャージされた電荷がトランジスタ 22 によって閉じ込められ、トランジスタ 23 はオン状態を維持し続ける。つまり、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  の何れにおいても、非選択期間  $T_{NSE}$  と直前の選択期間  $T_{SE}$  とではトランジスタ 23 のゲート - ソース間電圧レベル  $V_{GS}$  が等しい。40

#### 【0086】

そのため、 $i$  行目の非選択期間  $T_{NSE}$  でも、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  のトランジスタ 23 は、直前の選択期間  $T_{SE}$  における階調指定シンク電流レベルと同レベルの電流を流し続ける。そして、 $i$  行目の非選択期間  $T_{NSE}$  では、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  50

のカソード電極が基準電位  $V_{SS}$  である上、電源走査線  $Z_i$  が基準電位  $V_{SS}$  より高い電源電圧  $V_{DD}$  であるため、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  には順バイアス電圧が印加されるから、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  に駆動電流がトランジスタ 23 の作用によって流れ、有機 EL 素子  $E_{i,1} \sim E_{i,n}$  は発光する。これにより、有機 EL 素子  $E_{i,1} \sim E_{i,n}$  の発光輝度が更新される。

#### 【0087】

つまり、非選択期間  $T_{SE}$  において各々の画素回路  $D_{i,1} \sim D_{i,n}$  では、トランジスタ 21 が、信号線  $Y_j$  に流れる階調指定シンク電流をトランジスタ 23 に流れないように信号線  $Y_j$  とトランジスタ 23 との間を電気的に遮断するように機能し、トランジスタ 21 及びトランジスタ 22 が、選択期間  $T_{SE}$  においてトランジスタ 23 のソース - ドレイン間に流れた階調指定シンク電流にしたがってチャージされたコンデンサ 24 の電荷を閉じ込めるこ<sup>10</sup>とによって、トランジスタ 23 のゲート - ソース間電圧のレベルを保持するように機能し、トランジスタ 23 が、保持されたゲート - ソース間電圧レベルに応じたレベルの駆動電流を有機 EL 素子  $E_{i,j}$  に流すように機能する。

#### 【0088】

ここで、画素回路  $D_{i,1} \sim D_{i,n}$  の各トランジスタ 23 のソース - ドレイン間では、図 4 に示す飽和領域になるような電圧が印加されているために各トランジスタ 23 のソース - ドレイン間を流れる電流  $I_{DS}$  は、各トランジスタ 23 のゲート - ソース間電圧のレベルで一義的に決まる。この電流  $I_{DS}$  の電流レベルは有機 EL 素子  $E_{i,1} \sim E_{i,n}$  に流れる駆動電流のレベルと等しくなり、各トランジスタ 23 のゲート - ソース間電圧のレベルは階調指定シンク電流にしたがってチャージされたコンデンサ 24 の電荷によって確定しているので<sup>20</sup>、駆動電流のレベルは直前の  $i$  行目の選択期間  $T_{SE}$  における画素回路  $D_{i,1} \sim D_{i,n}$  のトランジスタ 23 の各々に流れる階調指定シンク電流のレベルと同じである。 $i$  行目の発光期間  $T_{EM}$  (非選択期間  $T_{NSE}$ ) の間中、このようなレベルの駆動電流が有機 EL 素子  $E_{i,1} \sim$  有機 EL 素子  $E_{i,n}$  に流れ、有機 EL 素子  $E_{i,1} \sim$  有機 EL 素子  $E_{i,n}$  それぞれの駆動電流レベルに従った輝度階調で発光する。上述したように、 $i$  行目の選択期間  $T_{SE}$  では、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  のトランジスタ 23 の電流レベルは所望通りとなるから、有機 EL 素子  $E_{i,1} \sim$  有機 EL 素子  $E_{i,n}$  それぞれの駆動電流レベルも所望通りになり、有機 EL 素子  $E_{i,1} \sim$  有機 EL 素子  $E_{i,n}$  それぞれは所望の階調輝度で発光する。

#### 【0089】

アクティブマトリクス駆動有機 EL ディスプレイに電流指定方式を適用した場合、各有機 EL 素子に単位時間当たりに流れる電流レベル（電流値）は小さくし且つ非選択期間中にその電流レベルに応じた電圧を保持するため保持用容量に迅速に充電しなければならない<sup>30</sup>。

#### 【0090】

ここで最高階調輝度  $L_{hsb}$ 、最低階調輝度  $L_{lsb}$  (ただし微小電流は流れている) で発光するために有機 EL 素子に流す電流、つまり非選択期間に保持用容量に充電するために信号線  $Y_j$  に流す電流をそれぞれ、 $I_{hsb}$ 、 $I_{lsb}$  とすると、

$$I_{hsb} > I_{lsb} \dots (4)$$

となり、このような電流  $I_{hsb}$ 、 $I_{lsb}$  を定常状態とするための信号線  $Y_j$  にかかる電圧  $V_{hsb}$ 、 $V_{lsb}$  は、シンク電流階調指定方式のために、

$$V_{lsb} > V_{hsb} \dots (5)$$

となる。

#### 【0091】

最低輝度から最高輝度に変調するために蓄積される電荷量  $Q_1$  は、

$$Q_1 = c (V_{lsb} - V_{hsb}) \dots (6)$$

となり、この電荷量  $Q_1$  を蓄積するために信号線  $Y_j$  に流れる電流は最高輝度のための  $I_{hsb}$  となる。

#### 【0092】

ところで図 6 (a) に示すような従来のシンク電流階調指定方式では、最高階調輝度  $L_{hs}$

10

20

30

40

50

bから最低階調輝度  $L_{lsb}$  に変調するために蓄積される電荷量  $Q_2$  は電荷量  $Q_1$  の絶対値に等しいが、このとき信号線  $Y_j$  に流れる電流は  $I_{lsb}$  となる。つまり流れる電流  $I_{lsb}$  が極小なために定常状態の電圧  $V_{lsb}$  となるまでに時間が掛かってしまい高速応答できないため、特に動画のように画像データが変わりやすい画像をなめらかに表示することが困難になつてしまう。さらに有機EL素子の無発光無電流状態の電流  $I_{ne}$  ( $= 0$  A) と設定し、ある信号線が発光状態の電流から無発光無電流状態の電流  $I_{ne}$  に変調すると、信号線に電流自体が流れず直前の発光状態の電荷を保持したままになり正常に表示することが困難になつてしまう。

#### 【0093】

本実施の形態では、 $i$  行目の選択期間  $T_{SE}$  が終了する時刻  $t_{iR}$  から  $(i + 1)$  行目の選択期間  $T_{SE}$  が開始する時刻  $t_{i+1}$  までの間、つまり、 $(i + 1)$  行目のリセット期間  $T_{RESET}$  では、切替信号入力端子 40 に入力される切替信号  $Y_{i+1}$  がハイレベルであるから、トランジスタ 31 がオフ状態になり、トランジスタ 32 がオン状態になる。従って、図 6 (b) に示すように、 $(i + 1)$  行目のリセット期間  $T_{RESET}$  では、何れの信号線  $Y_1 \sim Y_n$  にも階調指定シンク電流が流れないが、リセット電圧  $V_R$  が全ての信号線  $Y_1 \sim Y_n$  に印加される。

#### 【0094】

リセット電圧  $V_R$  は、選択期間  $T_{SE}$  に各有機EL素子  $E_{1,1} \sim E_{m,n}$  が最も明るい最高階調輝度  $L_{MAX}$  で発光するときに各有機EL素子  $E_{1,1} \sim E_{m,n}$  に流れる最高階調駆動電流  $I_{MAX}$  に等しい電流値となる階調指定シンク電流によって信号線  $Y_1 \sim Y_n$  にチャージされる電荷にしたがって定常化される最高階調電圧  $V_{hsb}$  より高い電圧に設定され、望ましくは、各有機EL素子  $E_{1,1} \sim E_{m,n}$  が最も暗い最低階調輝度  $L_{MIN}$  (ただし電流レベルが 0 A を越える) のときに各有機EL素子  $E_{1,1} \sim E_{m,n}$  に流れる最低階調駆動電流  $I_{MIN}$  に等しい電流値となる階調指定シンク電流によって信号線  $Y_1 \sim Y_n$  にチャージされる電荷にしたがって定常化される最低階調電圧  $V_{lsb}$  と、最高階調電圧  $V_{hsb}$  と、の中間値となる中間電圧以上に設定され、さらに望ましくは、最低階調電圧  $V_{lsb}$  と等しい値か或いは最低階調電圧  $V_{lsb}$  以上に設定されている。

#### 【0095】

このようにリセット電圧  $V_R$  は、少なくとも最高階調電圧  $V_{hsb}$  より高いので、リセット期間  $T_{RESET}$  に信号線  $Y_1 \sim Y_n$  を流れる電流レベルは最低階調輝度  $L_{lsb}$  を発光させるための階調指定シンク電流レベルよりも十分大きく、その上、 $(i + 1)$  行目のリセット期間  $T_{RESET}$  では、どの行の選択期間  $T_{SE}$  でもないから全ての画素回路  $D_{1,1} \sim D_{m,n}$  のトランジスタ 21 がオフ状態となっていて信号線  $Y_1 \sim Y_n$  以外の容量にチャージを印加する必要がない。従って、迅速に信号線  $Y_1 \sim Y_n$  の寄生容量に電荷がチャージされ、信号線  $Y_1 \sim Y_n$  の電位が速やかにリセット電圧  $V_R$  で定常化される。

#### 【0096】

そして、 $(i + 1)$  行目の選択期間  $T_{SE}$  が開始すると、 $i$  行目の場合と同様に、 $(i + 1)$  行目の選択走査線  $X_{i+1}$  及び電源走査線  $V_{i+1}$  がそれぞれ選択走査ドライバ 5 及び電源走査ドライバ 6 によって選択されることによって、更にトランジスタ 31 がオン状態となることによって、それぞれの列において電源走査線  $Z_{i+1}$  トランジスタ 23 トランジスタ 21 信号線  $Y_{i+1}$  トランジスタ 31 データドライバ 3 へと階調指定シンク電流が流れる。その後、 $(i + 1)$  行目の非選択期間  $T_{NSE}$  となって、 $i$  行目の場合と同様に  $(i + 1)$  行目の有機EL素子  $E_{i+1,1} \sim E_{i+1,n}$  がそれぞれの駆動電流レベルに従つた輝度階調で発光する。

#### 【0097】

ここで、 $(i + 1)$  行目の選択期間  $T_{SE}$  中に電源走査線  $Z_{i+1} \sim$  トランジスタ 23 ~ トランジスタ 21 ~ トランジスタ 31 ~ データドライバ 3 における電圧が階調指定シンク電流によって定常状態になるまでの時間  $d_t$  は、上式 (1) ~ (3) で表される。もし  $i$  行目の選択期間  $T_{SE}$  に信号線  $Y_1 \sim Y_n$  に流れる階調指定シンク電流レベルが大きく、且つ  $(i + 1)$  行目の選択期間  $T_{SE}$  に信号線  $Y_1 \sim Y_n$  に流れる階調指定シンク電流のレベルが小さ

10

20

30

40

50

いと、信号線  $Y_1 \sim Y_n$  が ( $i + 1$ ) 行目の階調指定シンク電流になるための電圧を定常化させようとするとき、上式 (1) ~ (3) で表せるように  $d_t$  が長くなってしまい、 $d_t$  が選択期間  $T_{SE}$  より大きくなってしまう恐れがある。従って、もし上述のように ( $i + 1$ ) 行目の選択期間  $T_{SE}$  に階調指定シンク電流のレベルが小さいと、図 6 (a) に示すように、コンデンサ 24 に印加される電圧、トランジスタ 23 に印加される電圧等が定常状態になる前に、( $i + 1$ ) 行目の選択期間  $T_{SE}$  が終了してしまい、( $i + 1$ ) 行目の非選択期間  $T_{NSE}$  で ( $i + 1$ ) 行目の有機 EL 素子  $E_{i+1,1} \sim E_{i+1,n}$  の駆動電流のレベルが階調指定シンク電流のレベルと異なる恐れがある。

#### 【0098】

しかしながら、本実施の形態では、( $i + 1$ ) 行目の選択期間  $T_{SE}$  の直前にリセット期間  $T_{RESET}$  を設定し、信号線  $Y_1 \sim Y_n$  に最低輝度を発光するときの階調指定シンク電流レベルよりも迅速に電荷が放電されるような電流が流れるリセット電圧  $V_R$  が印加されて、速やかに信号線  $Y_1 \sim Y_n$  の電位が上がる。特にリセット電圧  $V_R$  が最低階調電圧  $V_{1sb}$  と等しい値かその近傍の値に設定されていると、( $i + 1$ ) 行目の選択期間  $T_{SE}$  に最低階調輝度  $L_{1sb}$  のための最低階調電流  $I_{1sb}$  のように低い輝度の電流を信号線  $Y_1 \sim Y_n$  に流した場合であっても、上式 (1) ~ (3) に表すように、リセット期間  $T_{RESET}$  時の信号線  $Y_1 \sim Y_n$  の電荷と、( $i + 1$ ) 行目の選択期間  $T_{SE}$  における信号線  $Y_1 \sim Y_n$  の電荷と、の変化量を最小限に抑えることができる。

#### 【0099】

従って、( $i + 1$ ) 行目の階調指定シンク電流が最低階調輝度  $L_{1sb}$  のための最低階調電流  $I_{1sb}$  であっても、信号線  $Y_1 \sim Y_n$  が ( $i + 1$ ) 行目の選択期間  $T_{SE}$  内に最低階調電圧  $V_{1sb}$  で定常状態になり、選択期間  $T_{SE}$  内に階調指定シンク電流レベルにしたがった電荷をコンデンサ 24 にチャージすることができ、速やかに画素の輝度階調を更新することができる。

#### 【0100】

同一画素  $P_{i,j}$  において、前の一走査期間  $T_{SC}$  (あるいは前の一発光期間  $T_{EM}$ ) で高い階調輝度になるようにコンデンサ 24 が大きい電荷量でチャージされている状態にあって、次のー走査期間  $T_{SC}$  で低い階調輝度に更新するためにコンデンサ 24 の電荷量を小さくする場合、つまり大きい階調指定シンク電流で制御された高階調低電圧から、微小階調指定シンク電流で制御された低階調高電圧に変位する場合に、直前に信号線  $Y_1 \sim Y_n$  にリセット電圧  $V_R$  による電流を流すことで信号線  $Y_1 \sim Y_n$  の電荷を、低階調高電圧側にシフトさせているので、信号線  $Y_1 \sim Y_n$  とコンデンサ 24 を 1 つのコンデンサとみなすと、このコンデンサの電荷量を、選択期間  $T_{SE}$  の前に、低い階調側に近づけることができるようになる。すなわち所望の階調指定シンク電流の電流レベルが小さくても階調指定シンク電流に従った電荷を速やかに各コンデンサ 24 にチャージできるようにコンデンサ 24 及び信号線  $Y_1 \sim Y_n$  の電圧を迅速に定常化することが可能となる。

#### 【0101】

従って、( $i + 1$ ) 行目の選択期間  $T_{SE}$  中における画素  $P_{i+1,1} \sim P_{i+1,n}$  の各コンデンサ 24 の一方の極の電圧及び信号線  $Y_1 \sim Y_n$  の電圧が、階調指定シンク電流レベルに依存することなく迅速に定常状態となるから、どのような階調であっても、発光期間  $T_{EM}$  (非選択期間  $T_{NSE}$ ) における駆動電流のレベルが直前の選択期間  $T_{SE}$  の指定電流のレベルが同じになり、有機 EL 素子  $E_{i+1,1} \sim E_{i+1,n}$  が所望の発光輝度で発光する。換言すれば、各々の行の選択期間  $T_{SE}$  を長くせずとも、有機 EL 素子  $E_{i,j}$  が所望通りの輝度で発光するから、表示画面がちらついて見えたりせず、有機 EL ディスプレイ 1 の表示品質を高くすることができる。

#### 【0102】

##### 〔第二の実施の形態〕

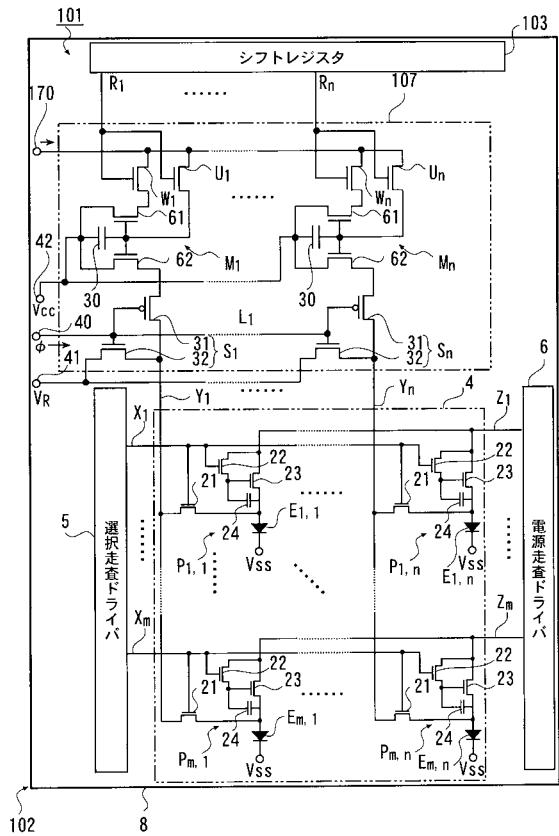

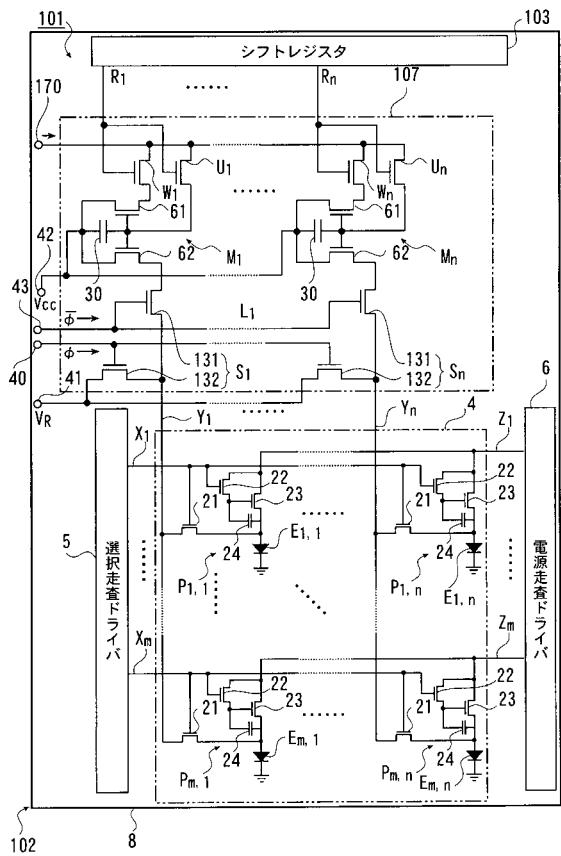

図 7 は、第一実施形態の有機 EL ディスプレイ 1 とは別の形態の有機 EL ディスプレイ 101 を示す図面である。図 7 に示すように、有機 EL ディスプレイ 101 は、基本構成として、アクティブマトリクス駆動方式によりカラー表示を行う有機 EL 表示パネル 102

10

20

30

40

50

と、シフトレジスタ103とを備える。

【0103】

有機EL表示パネル102は、透明基板8と、画像が実質的に表示される表示部4と、表示部4の周辺に設けられた選択走査ドライバ5、電源走査ドライバ6及び電流電圧変換部107とを基本構成としており、これらの回路4~6, 107が透明基板8上に形成されている。表示部4、選択走査ドライバ5、電源走査ドライバ6及び透明基板8は、第一実施形態の有機ELディスプレイ1の場合と同様である。従って、第二実施形態の有機EL表示ディスプレイ101の場合でも、選択走査ドライバ5による電圧印加タイミング、電源走査ドライバ6による電圧印加タイミング、画素 $P_{1,1} \sim P_{m,n}$ の更新、画素 $P_{1,1} \sim P_{m,n}$ ノ階調表現は第一実施形態の有機ELディスプレイ1の場合と同様である。

10

【0104】

電流電圧変換部107では、列ごとにトランジスタ31及びトランジスタ32で構成された切替回路 $S_j \sim S_n$ が設けられており、加えて、カレントミラー回路 $M_1 \sim M_n$ 並びにカレントミラー回路 $M_1 \sim M_n$ を制御するトランジスタ $U_1 \sim U_n$ 及びトランジスタ $W_1 \sim W_n$ が設けられている。電流電圧変換部107の一端にそれぞれ信号線 $Y_1 \sim Y_n$ が接続されており、他端はシフトレジスタ103に接続されている。

【0105】

カレントミラー回路 $M_j$ は、コンデンサ30と、二つのMOS型のトランジスタ61, 62とから構成されている。トランジスタ61, 62、トランジスタ31, 32、トランジスタ $U_1 \sim U_n$ 及びトランジスタ $W_1 \sim W_n$ は、MOS型の電界効果薄膜トランジスタであり、特にアモルファスシリコンを半導体層としたa-Siトランジスタであるが、ポリシリコンを半導体層としたp-Siトランジスタであってもよい。また、トランジスタ31、トランジスタ32, トランジスタ $U_1 \sim U_n$ 及びトランジスタ $W_1 \sim W_n$ の構造は、逆スタガ型であっても良いし、コプラナ型であっても良い。なお、以下では、トランジスタ61、62、トランジスタ32、トランジスタ $U_1 \sim U_n$ 及びトランジスタ $W_1 \sim W_n$ がNチャネル型の電界効果トランジスタであり、トランジスタ31がPチャネル型の電界効果トランジスタとして説明する。

20

【0106】

また、トランジスタ61のチャネル長とトランジスタ62のチャネル長は同じであり、トランジスタ61のチャネル幅はトランジスタ62のチャネル幅より長い。つまり、トランジスタ62のチャネル抵抗は、トランジスタ61のチャネル抵抗より高く、例えば、トランジスタ62のチャネル抵抗はトランジスタ61のチャネル抵抗の10倍である。なお、トランジスタ62のチャネル抵抗がトランジスタ61のチャネル抵抗より高ければ、トランジスタ61とトランジスタ62のチャネル長が同じでなくても良い。

30

【0107】

各々の列について説明すると、カレントミラー回路 $M_j$ は、トランジスタ61のドレイン電極がトランジスタ $W_j$ のソース電極に接続されており、トランジスタ61及びトランジスタ62のゲート電極がトランジスタ $U_j$ のソース電極に接続されているとともに、コンデンサ30の一方の極に接続され、トランジスタ62のドレイン電極がトランジスタ31のソース電極に接続され、トランジスタ61のソース電極及びトランジスタ62のソース電極は互いに接続されているとともに、コンデンサ30の他方の極に接続され、且つ一定レベルである低電位 $V_{CC}$ の低電圧入力端子42に接続されている。低電圧入力端子42の電位 $V_{CC}$ としては、基準電位 $V_{SS}$ より低く、更にチャージ電圧 $V_{CH}$ より低く、例えば、-20[V]である。

40

【0108】

j列目では、トランジスタ31のドレイン電極及びトランジスタ32のドレイン電極はともに信号線 $Y_j$ に接続され、トランジスタ31のゲート電極及びトランジスタ32のゲート電極はともに切替信号入力端子40に接続されている。そして、各列のトランジスタ32のソース電極はリセット電圧入力端子41に接続されている。

【0109】

50

トランジスタ  $U_j$  のゲート電極とトランジスタ  $W_j$  のゲート電極は、互いに接続されているとともに、シフトレジスタ 103 の出力端子  $R_j$  に接続されている。トランジスタ  $U_j$  のドレイン電極とトランジスタ  $W_j$  のドレイン電極は、互いに接続されているとともに、共通の階調信号入力端子 170 に接続されている。

【0110】

シフトレジスタ 103 は、外部からのクロック信号に基づいて、パルス信号をシフトしていく、出力端子  $R_1$  から出力端子  $R_n$  の順（出力端子  $R_n$  の次は出力端子  $R_1$ ）にオンレベルのパルス信号を順次出力し、これにより、カレントミラー回路  $M_1 \sim M_n$  を順次選択するものである。シフトレジスタ 103 の一シフト周期は、選択走査ドライバ 5 や電源走査ドライバ 6 の一シフト周期よりも短く、選択走査ドライバ 5 や電源走査ドライバ 6 が  $i$  行目から ( $i + 1$ ) 行目にパルス信号をシフトする間に、シフトレジスタ 103 は一行分のパルス信号を出力端子  $R_1$  から出力端子  $R_n$  へ順にシフトしていく、 $n$  回のオンレベルのパルス信号を出力する。

【0111】

階調信号入力端子 170 からは、外部のデータドライバの階調信号が出力され、この階調信号をシフトレジスタ 103 のパルス信号によって順次選択するカレントミラー回路  $M_1 \sim M_n$  が階調に応じた電流値の階調指定シンク電流を流すように設定されている。階調指定シンク電流により選択期間  $T_{SE}$  に有機 EL 素子  $E_{1,1} \sim E_{m,n}$  の輝度階調に応じた電流をトランジスタ 23 のソース - ドレイン間及び信号線  $Y_1 \sim Y_n$  に流させることにより非選択期間  $T_{NSE}$ （発光期間  $T_{EM}$ ）にトランジスタ 23 のソース - ドレイン間及び有機 EL 素子  $E_{1,1} \sim E_{m,n}$  に輝度階調に応じた電流を流れる。階調指定シンク電流は、アナログ信号でもデジタル信号であってもよく、シフトレジスタ 103 の出力端子  $R_1 \sim R_n$  からのオンレベルのパルス信号が入力されるタイミングでそれぞれトランジスタ  $U_1 \sim U_n$  のドレイン電極並びにトランジスタ  $W_1 \sim W_n$  のドレイン電極に入力される。階調指定シンク電流の一行分の周期は、選択走査ドライバ 5 や電源走査ドライバ 6 の一シフト周期よりも短く、選択走査ドライバ 5 や電源走査ドライバ 6 が  $i$  行目から ( $i + 1$ ) 行目にパルス信号をシフトする間に、 $n$  回の階調指定シンク電流が入力される。

【0112】

切替信号入力端子 40 には、外部から切替信号  $S$  が入力される。切替信号  $S$  の周期は、選択走査ドライバ 5 や電源走査ドライバ 6 の一シフト周期と同じであり、トランジスタ 31 のオンレベルの切替信号  $S$  が入力されるタイミングは、選択走査ドライバ 5 や電源走査ドライバ 6 がトランジスタ 21, 22 のオンレベルのパルス信号を出力している時である。従って、選択走査ドライバ 5 や電源走査ドライバ 6 が 1 行目から  $m$  行目までにシフトする間に、切替信号  $S$  のオンレベル電圧が  $m$  回入力される。

【0113】

階調信号が階調信号入力端子 170 から出力されることによって、トランジスタ 61 のドレイン電極及びゲート電極に電圧が印加されて、トランジスタ 61 のドレイン - ソース間に電流が流れる。このとき、トランジスタ 62 のドレイン - ソース間にも電流が流れる。ここで、トランジスタ 62 のチャネル抵抗がトランジスタ 61 のチャネル抵抗より高い上、トランジスタ 62 のゲート電極とトランジスタ 61 のゲート電極の電圧レベルが同じであるため、トランジスタ 62 のドレイン - ソース間の電流レベルは、トランジスタ 61 のドレイン - ソース間の電流レベルより小さい。具体的には、トランジスタ 62 のドレイン - ソース間の電流レベルは、実質的に、トランジスタ 61 のチャネル抵抗に対するトランジスタ 62 のチャネル抵抗の比率にトランジスタ 61 のドレイン - ソース間の電流レベルを乗じた値となり、トランジスタ 62 のドレイン - ソース間の電流レベルは、トランジスタ 61 のドレイン - ソース間の電流レベルより低い。このためトランジスタ 62 に流れる微小の階調指定シンク電流を容易に階調制御することができる。以下、トランジスタ 61 のチャネル抵抗に対するトランジスタ 62 のチャネル抵抗の比率を、電流減少率と述べる。

【0114】

10

20

30

40

50

次に、以上のように構成される有機ELディスプレイ101の動作について説明する。第一実施形態の場合と同様に、図5に示すように、選択走査ドライバ5及び電源走査ドライバ6が1行目からm行目へと線順次にパルス信号をシフトしていく。

【0115】

一方、図8に示すように、(i-1)行目の選択期間 $T_{SE}$ の終わりからi行目の選択期間 $T_{SE}$ の始めの間、つまりリセット期間 $T_{RESET}$ に、シフトレジスタ103は、トランジスタ $U_1 \sim U_n$ 及びトランジスタ $W_1 \sim W_n$ のオノレベルのパルス信号を出力端子 $R_1$ から出力端子 $R_n$ へとパルス信号をシフトする。シフトレジスタ103がパルス信号をシフトしている間、切替信号入力端子40の切替信号の電圧レベルはトランジスタ31のオフレベルであるとともにトランジスタ32のオノレベルのハイレベルHに維持されている。このため、リセット期間 $T_{RESET}$ では、信号線 $Y_1 \sim Y_n$ では速やかにリセット電圧入力端子41からのリセット電圧 $V_R$ に変位している。10

【0116】

ここで、シフトレジスタ103が出力端子 $R_j$ にオノレベルのパルス信号を出力しているとき、階調信号入力端子170からi行j列目の階調輝度用を示したレベルの階調信号が入力される。この時、j列目のトランジスタ $U_j$ 及びトランジスタ $W_j$ がオノ状態となっているので、i行j列目の階調輝度用を示した電流レベルの階調信号がカレントミラー回路 $M_j$ に入力され、トランジスタ61及びトランジスタ62がオノ状態となり、階調信号の電流レベルに従った大きさの電荷がコンデンサ30にチャージされる。つまり、トランジスタ $U_j$ 及びトランジスタ $W_j$ は、j列目の選択時に階調信号をカレントミラー回路 $M_j$ に取り込むように機能する。20

【0117】

トランジスタ61がオノ状態となることによって、カレントミラー回路 $M_j$ では階調信号入力端子170 トランジスタ61 低電圧入力端子42へと電流が流れようになる。階調信号入力端子170 トランジスタ61 低電圧入力端子42へと流れる電流のレベルは階調信号の電流レベルに従っている。

【0118】

この時、切替信号入力端子40のレベルがトランジスタ31のオフレベルであるから、j列目のトランジスタ31がオフ状態であり、カレントミラー回路 $M_j$ と信号線 $Y_j$ とに流れ 30

る階調指定シンク電流が流れないようになっている。

【0119】

続いて、シフトレジスタ103が出力端子 $R_{j+1}$ にパルス信号を出力しているとき、i行(j+1)列目の階調輝度用を示した電流レベルの階調信号が入力され、j列目の場合と同様に、階調信号の電流レベルに従った大きさの電荷が(j+1)列目のコンデンサ30にチャージされる。この時、j列目のトランジスタ $U_j$ ,  $W_j$ がオフ状態になつても、j列目のコンデンサ30にチャージされた電荷がトランジスタ $U_j$ によって閉じ込められるから、j列目のトランジスタ61及びトランジスタ62はオノ状態を維持し続ける。つまり、トランジスタ $U_j$ は、j列目の選択時に階調信号の電流のレベルに従ったゲート電圧レベルをj列目の非選択時でも保持するように機能する。

【0120】

以上のように、シフトレジスタ103がパルス信号をシフトしていくことによって、階調信号の電流レベルに従った大きさの電荷が1列目のコンデンサ30からn列目とコンデンサ30へと順次チャージされていく。

【0121】

そして、n列目のコンデンサ30へのチャージが終了したら、シフトレジスタ103のシフトは一旦終了し、切替信号入力端子40の切替信号がハイレベルからオフレベルに切り替わり、全てのトランジスタ31が同時にオノ状態になるとともに全てのトランジスタ32がオフ状態になる。この時、全ての列のコンデンサ30に電荷がチャージされているから、トランジスタ61, 62はオノ状態である。そして、この時はi行目の選択期間であるから、i行目の全ての画素回路 $D_{i,1} \sim D_{i,n}$ では電源走査線 $Z_i$  トランジスタ23 50

トランジスタ 21 信号線  $Y_1 \sim Y_n$  トランジスタ 62 低電圧入力端子 42 へと階調指定シンク電流が流れるようになる。このとき、1列目から  $n$ 列目の何れの列においても、カレントミラー回路  $M_j$  の機能によって、電源走査線  $Z_i$  トランジスタ 23 トランジスタ 21 信号線  $Y_1 \sim Y_n$  トランジスタ 62 低電圧入力端子 42 の向きに流れる階調指定シンク電流のレベルは、階調信号入力端子 170 トランジスタ 61 低電圧入力端子 42 の向きに流れる先ほどの電流のレベルにカレントミラー回路  $M_j$  の電流減少率を乗じたものとなる。

#### 【0122】

信号線  $Y_1 \sim Y_n$  の中のいずれかにおいて、前の行の選択期間  $T_{SE}$  で高い輝度の比較的大きい階調指定シンク電流を流したために信号線  $Y_1 \sim Y_n$  の配線容量に電荷が蓄積されて電位が低くなつた場合、その次の選択期間  $T_{SE}$  で流れる階調指定シンク電流のレベルが小さくても、その直前のリセット期間  $T_{RESET}$  に印加されたリセット電圧  $V_R$  により配線電位が高くなつてゐるので、信号線  $Y_1 \sim Y_n$  の電位を迅速に階調シンク電流に応じた電位に定常化することが可能となる。

10

#### 【0123】

続いて、選択走査ドライバ 5 及び電源走査ドライバ 6 のパルス信号が ( $i + 1$ ) 行目にシフトし、 $i$  行目の非選択期間  $T_{SE}$  となって、第一実施形態の場合と同様に  $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  の階調輝度が更新される。

#### 【0124】

そして、切替信号入力端子 40 がハイレベルになり、同様にシフトレジスタ 103 が一列目から  $n$ 列目へとパルス信号をシフトしていくことを繰り返すことによって、( $i + 1$ ) 行目の有機 EL 素子  $E_{i+1,1} \sim E_{i+1,n}$  の階調輝度を更新するために、一列目から  $n$ 列目のコンデンサ 30 に電荷が順次チャージされていく。

20

#### 【0125】

第二の実施の形態では、カレントミラー回路  $M_j$  が表示部 4 の外に設けられているから、画素毎に設けるトランジスタの数を必要最小限に抑えることができ、画素の開口率の低下を抑えることができる。また、カレントミラー回路  $M_j$  が設けられているため、階調信号入力端子 170 等において周囲のノイズや寄生容量等により階調信号が本来出力すべき電流レベルに対して多少ズレっていても、信号線  $Y_j$  の階調指定シンク電流レベルのズレは、電流減少率に則つて小さく抑えられ、ひいては有機 EL 素子  $E$  の輝度階調のズレを抑えることができる。

30

#### 【0126】

また上記各実施の形態では、切替回路  $S_1 \sim S_n$  が N チャネルトランジスタ及び P チャネルトランジスタの CMOS 構造であったが、図 9 に示すように、ともにカレントミラー回路  $M_1 \sim M_n$  と同じチャネル型トランジスタにして、電流電圧変換部 107 のトランジスタを单チャネル型トランジスタのみにすることが可能である。このようにすることで電流電圧変換部 107 の製造工程を簡易にすることが可能である。

#### 【0127】

さらに、電流電圧変換部 107 のトランジスタのチャネル型を表示部 4 内のトランジスタ 21 ~ 23 と同じチャネル型にすることで電流電圧変換部 107 内のトランジスタと表示部 4 内のトランジスタ 21 ~ 23 を一括して形成することも可能である。なお、仮に電流電圧変換部 107 内に部分的に表示部 4 のトランジスタ 21 ~ 23 と同一のチャネル型のトランジスタがあれば同時に形成することができるとはいうまでもない。

40

#### 【0128】

図 9 に示す有機 EL ディスプレイ 201 では、切替回路  $S_1 \sim S_n$  が、それぞれ切替信号が入力される切替信号入力端子 40 に接続された N チャネル型トランジスタ 132 及び切替信号  $\neg$  の反転信号である切替信号  $\neg$  ( $\neg$  は論理否定) が入力される切替信号入力端子 43 に接続された N チャネル型トランジスタ 131 で構成される。

#### 【0129】

トランジスタ 131 は、図 10 に示すように、切替信号  $\neg$  により選択期間  $T_{SE}$  にオン状

50

態になって電源走査線  $Z_1 \sim Z_m$ 、トランジスタ 2 3、トランジスタ 2 1、信号線  $Y_1 \sim Y_n$ 、トランジスタ 6 2、低電圧入力端子 4 2 へと微小の階調指定シンク電流を流すスイッチとして機能し、リセット期間  $T_{RESET}$  にオフ状態となる。トランジスタ 1 3 2 は、切替信号  $S$  により選択期間  $T_{SE}$  にオフ状態になり、リセット期間  $T_{RESET}$  にオン状態となって、信号線  $Y_1 \sim Y_n$  にリセット電圧  $V_R$  を印加するスイッチとして機能する。また図 1 に示す切替回路  $S_1 \sim S_n$  においても、互いに同一チャネル型のトランジスタ 1 3 1、1 3 2 を採用し、切替信号入力端子 4 3 に各トランジスタ 1 3 1 を接続し、切替信号入力端子 4 0 に各トランジスタ 1 3 2 を接続させても同様の効果を得ることができる。

#### 【0130】

なお、本発明は、上記各実施の形態に限定されることなく、本発明の趣旨を逸脱しない範囲において、種々の改良並びに設計の変更を行っても良い。

例えば、上記有機 E L ディスプレイ 1 では、画素  $P_{i,j}$  から引き抜かれたシンク電流のレベルによって階調輝度を画素  $P_{i,j}$  に指定している。しかしながら、逆に信号線  $Y_j$  から画素  $P_{i,j}$  へ電流を流し、この電流のレベルにしたがった階調輝度で画素  $P_{i,j}$  を発光させるようなアクティブマトリクス駆動方式の有機 E L ディスプレイの場合でも良い。

#### 【0131】

この場合も、切替回路が、各々の行の選択期間中にデータドライバの指定電流を信号線に流し、それぞれの選択期間の間のリセット期間中に一定レベルの定電圧を信号線に印加するが、輝度階調が高いほど信号線電圧が高く且つ信号線電流が大きく、輝度階調が低いほど信号線電圧が低く且つ信号線電流が小さい。したがって図 6 (b) での電圧  $V_R$ 、 $V_{lsb}$ 、 $V_{hsb}$  を上下に反転するような電位関係となり、リセット電圧  $V_R$  は、選択期間  $T_{SE}$  に各有機 E L 素子  $E_{1,1} \sim E_{m,n}$  が最も明るい最高階調輝度  $L_{MAX}$  で発光するときに各有機 E L 素子  $E_{1,1} \sim E_{m,n}$  に流れる最高階調駆動電流  $I_{MAX}$  に等しい電流値となる階調指定シンク電流によって信号線  $Y_1 \sim Y_n$  にチャージされる電荷にしたがって定常化される最高階調電圧  $V_{hsb}$  より少なくとも低い電圧に設定され、望ましくは、各有機 E L 素子  $E_{1,1} \sim E_{m,n}$  が最も暗い最低階調輝度  $L_{MIN}$  (ただし電流レベルが 0 A を越える) のときに各有機 E L 素子  $E_{1,1} \sim E_{m,n}$  に流れる最低階調駆動電流  $I_{MIN}$  に等しい電流値となる階調指定シンク電流によって信号線  $Y_1 \sim Y_n$  にチャージされる電荷にしたがって定常化される最低階調電圧  $V_{lsb}$  と、最高階調電圧  $V_{hsb}$  と、の中間値となる中間電圧以下であり、さらに望ましくは最低階調電圧  $V_{lsb}$  と等しい値か或いは最低階調電圧  $V_{lsb}$  以下である。

#### 【0132】

更にこの場合、画素  $P_{i,j}$  の回路は適宜変更しても良いが、走査線が選択されている時に信号線に流れる指定電流を画素回路に流すことで指定電流のレベルを電圧レベルに変換し、走査線が選択されていない時に信号線に流れる指定電流を遮断し、走査線が選択されていない時に変換された電圧レベルを保持するとともに、保持された電圧レベルに従ったレベルの駆動電流を有機 E L 素子に流す画素回路を、それぞれの有機 E L 素子の周囲に設けることが望ましい。

#### 【0133】

また、例えば、上記実施の形態では発光素子として有機 E L 素子を用いているが、逆バイアス電圧が印加された場合には電流が流れないとともに順バイアス電圧が印加された場合には電流が流れるような発光素子であって、流れる電流の大きさに従った輝度で発光する発光素子であっても良い。発光素子として、例えば L E D (Light Emitting Diode) 素子等でも良い。

#### 【0134】

##### 【発明の効果】

本発明によれば、所定の行の画素が選択されている時に、各々の信号線には階調電流が流れるが、前の行の画素のために信号線に流れる階調電流により定常化される電圧と、次の行の画素のために信号線に流す階調電流により定常化されるべき電圧との差が大きく、且つ当該次の画素のための階調電流の電流値が小さいときであっても、当該次の行の前に信号線にリセット電圧を印加することで迅速に信号線を当該次の行のための階調電流にした

10

20

30

40

50

がった電圧に定常化することができる。

従って、次の走査線が選択された後に、発光素子に流れる駆動電流のレベルは、指定電流のレベルと同じになり、発光素子が所望通りの輝度で発光する。つまり、各々の走査線が選択されている期間を長くせずとも、発光素子が所望通りの輝度で発光するから、表示画面がちらついて見えたりせず、表示装置の表示品質が高い。

【図面の簡単な説明】

【図 1】図 1 は、本発明が適用された有機 EL ディスプレイの具体的な態様を示したプロック図である。

【図 2】図 2 は、図 1 の有機 EL ディスプレイの画素を示した平面図である。

【図 3】図 3 は、図 1 の有機 EL ディスプレイの画素の等価回路を示した図面である。 10

【図 4】図 4 は、N チャネル型の電界効果トランジスタの電流 - 電圧特性を示した図面である。

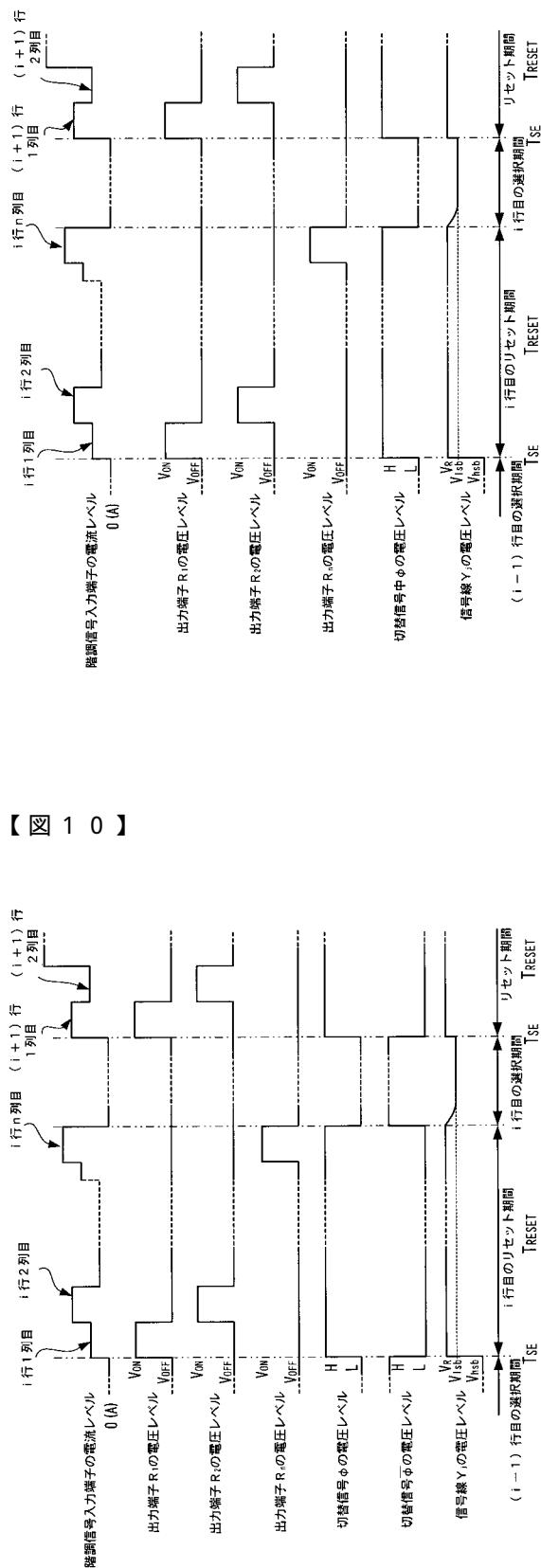

【図 5】図 5 は、図 1 の有機 EL ディスプレイにおける信号のレベルを示したタイミングチャートである。

【図 6】図 6 ( a ) は従来の電流指定型の有機 EL ディスプレイにおいて信号線に印加された電圧の変移を示す図面であり、図 6 ( b ) は本発明の有機 EL ディスプレイにおいて信号線に印加された電圧の変移を示す図面である。

【図 7】図 7 は、本発明が適用された他の有機 EL ディスプレイの具体的な態様を示したプロック図である。

【図 8】図 8 は、図 7 の有機 EL ディスプレイにおける信号のレベルを示したタイミングチャートである。 20

【図 9】図 9 は、本発明が適用された他の有機 EL ディスプレイの具体的な態様を示したプロック図である。

【図 10】図 10 は、図 9 の有機 EL ディスプレイにおける信号のレベルを示したタイミングチャートである。

【図 11】図 11 は、従来の液晶ディスプレイの画素の等価回路を示した図面である。

【図 12】図 12 は、従来の電圧指定型の有機 EL ディスプレイの画素の等価回路を示した図面である。

【符号の説明】

1 有機 EL ディスプレイ ( 表示装置 )

30

3 データドライバ

5 選択走査ドライバ

6 電源走査ドライバ

7, 107 電流電圧切替部 ( リセット手段 )

21, 22 トランジスタ ( 階調電流制御スイッチ手段 )

23 トランジスタ ( 駆動電流スイッチ手段 )

31, 131 トランジスタ ( 階調電流用トランジスタ )

32, 132 トランジスタ ( リセット電圧用トランジスタ )

61, 62 トランジスタ

24 コンデンサ ( 電圧保持手段 )

40

41 リセット電圧入力端子

101 シフトレジスタ

$E_{1,1} \sim E_{m,n}$  有機 EL 素子 ( 発光素子 )

$M_1 \sim M_n$  カレントミラー回路

$S_1 \sim S_n$  切替回路

$U_1 \sim U_n, W_1 \sim W_n$  トランジスタ ( 階調信号スイッチ手段 )

$Y_1 \sim Y_n$  信号線

$X_1 \sim X_m$  選択走査線

$Z_1 \sim Z_m$  電源走査線

$P_{1,1} \sim P_{m,n}$  画素

50

$D_{1,1} \sim D_{m,n}$  画素回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【圖 7】

〔 図 8 〕

【 四 9 】

【 図 1 0 】

【図11】

【図12】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 624 B

G 09 G 3/20 641 D

(56)参考文献 国際公開第01/06484 (WO, A1)

国際公開第02/39420 (WO, A1)

特表2002-517806 (JP, A)

特開2003-66908 (JP, A)

特開2002-149125 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/30

G09G 3/20

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置和显示装置的驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP4610843B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2011-01-12 |

| 申请号            | JP2002180284                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 申请日     | 2002-06-20 |

| [标]申请(专利权)人(译) | 卡西欧计算机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 卡西欧计算机有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 当前申请(专利权)人(译)  | 卡西欧计算机有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 佐藤和仁<br>山田裕康                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 佐藤 和仁<br>山田 裕康                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G09G3/30 G09G3/20 G09G3/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| CPC分类号         | G09G3/325 G09G3/2011 G09G3/32 G09G3/3283 G09G2300/043 G09G2300/0842 G09G2300/0861<br>G09G2300/0866 G09G2310/0251 G09G2310/06 G09G2310/061 G09G2310/066 G09G2320/02                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| FI分类号          | G09G3/30.J G09G3/30.K G09G3/20.611.H G09G3/20.623.H G09G3/20.623.R G09G3/20.624.B G09G3<br>/20.641.D G09G3/20.621.F G09G3/325 G09G3/3266 G09G3/3275 G09G3/3283                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD06 5C080/EE29 5C080/FF11 5C080/JJ03 5C080<br>/JJ04 5C080/JJ05 5C380/AA01 5C380/AA03 5C380/AB06 5C380/AB22 5C380/AB34 5C380/AB46<br>5C380/BA08 5C380/BA13 5C380/BA19 5C380/BB09 5C380/BC02 5C380/BC13 5C380/BC18 5C380<br>/CA08 5C380/CA13 5C380/CA25 5C380/CA30 5C380/CA54 5C380/CB01 5C380/CB20 5C380/CB26<br>5C380/CB33 5C380/CC13 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC41 5C380/CC52 5C380<br>/CC62 5C380/CD012 5C380/CD013 5C380/CE04 5C380/CF07 5C380/CF26 5C380/CF54 5C380/DA02<br>5C380/DA06 5C380/DA42 5C380/DA47 5C380/HA03 5C380/HA05 5C380/HA13 |         |            |

| 其他公开文献         | JP2004021219A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

## 摘要(译)

要解决的问题：通过解决未以所需亮度发光或者显示图像的问题来进行高质量的显示。SOLUTION：有机EL显示装置1具有以矩阵形状排列的像素P<sub>i</sub>和P<sub>j</sub>，并且像素P<sub>i</sub>和P<sub>j</sub>具有有机EL元件E<sub>i</sub>和E<sub>j</sub>和像素电路D<sub>i</sub>和D<sub>j</sub>。像素电路D<sub>i</sub>和D<sub>j</sub>保持与流向信号线Y<sub>j</sub>的灰度指定下沉电平相对应的电平电压，晶体管23在选择周期中产生与晶体管23的电压电平相应的电平的驱动电流流向有机EL元件E<sub>i</sub>和E<sub>j</sub>在非选择期间。电流/电压转换部分7使得由数据驱动器3产生的灰度指定吸收电流在选择时段中流到信号线Y<sub>1</sub>到Y<sub>n</sub>并且应用在复位周期中，信号线Y<sub>1</sub>到Y<sub>n</sub>的恒定电压。Z