(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4470960号

(P4470960)

(45) 発行日 平成22年6月2日(2010.6.2)

(24) 登録日 平成22年3月12日(2010.3.12)

(51) Int.Cl.

F 1

|             |              |                  |      |      |         |

|-------------|--------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | G09G | 3/30 | J       |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20 | 6 1 1 H |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 4 2 A |

|             |              |                  | G09G | 3/20 | 6 2 4 B |

|             |              |                  | G09G | 3/20 | 6 2 3 A |

請求項の数 4 (全 24 頁) 最終頁に続く

(21) 出願番号

特願2007-133862 (P2007-133862)

(22) 出願日

平成19年5月21日 (2007.5.21)

(65) 公開番号

特開2008-287139 (P2008-287139A)

(43) 公開日

平成20年11月27日 (2008.11.27)

審査請求日

平成20年6月25日 (2008.6.25)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100094363

弁理士 山本 幸久

(74) 代理人 100118290

弁理士 吉井 正明

(74) 代理人 100120640

弁理士 森 幸一

(72) 発明者 山下 淳一

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 内野 勝秀

東京都港区港南1丁目7番1号 ソニー株式会社内

最終頁に続く

(54) 【発明の名称】表示装置及びその駆動方法と電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

画素アレイ部とこれを駆動する駆動部とから成り、

画素アレイ部は、行状の走査線と、列状の信号線と、行列状の画素回路とから成り、

駆動部は、少なくとも、各走査線に制御信号を供給するライトスキャナと、各信号線に映像信号電位を供給する信号セレクタとを有し、

画素回路は、サンプリングトランジスタと、ドライブトランジスタと、保持容量と、発光素子とを含み、

サンプリングトランジスタの制御端は走査線に接続され、サンプリングトランジスタの一対の電流端の一方は信号線に接続され、他方はドライブトランジスタの制御端に接続され、

ドライブトランジスタの一対の電流端の一方は電源に接続され、他方は発光素子に接続され、

保持容量の一端はドライブトランジスタの制御端に接続され、他端はドライブトランジスタの電流端の他方に接続され、

サンプリングトランジスタは、制御信号に応じて導通し、映像信号電位を保持容量に書き込み、

ドライブトランジスタは、保持容量に書き込まれた映像信号電位に応じた駆動電流を発光素子に供給する表示装置であって、

画素回路は、1フィールド内において発光期間と非発光期間とに分かれて動作し、且つ

、非発光期間にドライブトランジスタの閾電圧補正動作、保持容量に対する映像信号の書き込み動作及びドライブトランジスタの移動度補正動作を行い、

信号セレクタは所定電位を信号線に供給し、サンプリングトランジスタは制御信号に応じて導通し、前記所定電位がドライブトランジスタの制御端に印加されることで、発光素子が消灯し、

サンプリングトランジスタを非導通状態とした状態で、電源の電位を高電位から前記所定電位より低い低電位とすることで、ドライブトランジスタの一対の電流端の他方の電位を該低電位とした後、

ドライブトランジスタの閾電圧補正動作において、信号セレクタは前記所定電位を信号線に供給し、サンプリングトランジスタは制御信号に応じて導通し、前記所定電位がドライブトランジスタの制御端に印加され、電源の電位が前記低電位から前記高電位とされることで、ドライブトランジスタの電流端の一方から他方に流れる電流によってドライブトランジスタの電流端の他方の電位を前記所定電位に近づける表示装置。

#### 【請求項 2】

ドライブトランジスタの移動度補正動作において、ドライブトランジスタに流れる電流が保持容量に負帰還される請求項 1 に記載の表示装置。

#### 【請求項 3】

請求項 1 に記載の表示装置を含む電子機器。

#### 【請求項 4】

画素アレイ部とこれを駆動する駆動部とから成り、

画素アレイ部は、行状の走査線と、列状の信号線と、行列状の画素回路とから成り、

駆動部は、少なくとも、各走査線に制御信号を供給するライトスキャナと、各信号線に映像信号電位を供給する信号セレクタとを有し、

画素回路は、サンプリングトランジスタと、ドライブトランジスタと、保持容量と、発光素子とを含み、

サンプリングトランジスタの制御端は走査線に接続され、サンプリングトランジスタの一対の電流端の一方は信号線に接続され、他方はドライブトランジスタの制御端に接続され、

ドライブトランジスタの一対の電流端の一方は電源に接続され、他方は発光素子に接続され、

保持容量の一端はドライブトランジスタの制御端に接続され、他端はドライブトランジスタの電流端の他方に接続され、

サンプリングトランジスタは、制御信号に応じて導通し、映像信号電位を保持容量に書き込み、

ドライブトランジスタは、保持容量に書き込まれた映像信号電位に応じた駆動電流を発光素子に供給する表示装置の駆動方法であって、

1 フィールド内において発光期間と非発光期間とに分かれて画素回路を動作させ、且つ、非発光期間にドライブトランジスタの閾電圧補正動作、保持容量に対する映像信号の書き込み動作及びドライブトランジスタの移動度補正動作を行い、

信号セレクタから所定電位を信号線に供給し、サンプリングトランジスタを制御信号に応じて導通させ、前記所定電位をドライブトランジスタの制御端に印加することで、発光素子を消灯し、

サンプリングトランジスタを非導通状態とした状態で、電源の電位を高電位から前記所定電位より低い低電位とすることで、ドライブトランジスタの一対の電流端の他方の電位を該低電位とした後、

ドライブトランジスタの閾電圧補正動作において、信号セレクタから前記所定電位を信号線に供給し、サンプリングトランジスタを制御信号に応じて導通させ、前記所定電位をドライブトランジスタの制御端に印加し、電源の電位を前記低電位から前記高電位とすることで、ドライブトランジスタの電流端の一方から他方に流れる電流によってドライブトランジスタの電流端の他方の電位を前記所定電位に近づける表示装置の駆動方法。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、各画素に設けた絶縁ゲート型電界効果トランジスタによって有機ELなどの発光素子に通電する電流量を制御する、いわゆるアクティブマトリクス型の表示装置及びその駆動方法に関する。また、この表示装置を備えた電子機器に関する。

**【背景技術】****【0002】**

画像表示装置、例えば液晶ディスプレイなどでは、多数の液晶画素をマトリクス状に並べ、表示すべき画像情報に応じて画素毎に入射光の透過強度又は反射強度を制御することによって画像を表示する。これは、有機EL素子を画素に用いた有機ELディスプレイなどにおいても同様であるが、液晶画素と異なり有機EL素子は自発光素子である。その為、有機ELディスプレイは液晶ディスプレイに比べて画像の視認性が高く、バックライトが不要であり、応答速度が高いなどの利点を有する。又、各発光素子の輝度レベル（階調）はそれに流れる電流値によって制御可能であり、いわゆる電流制御型であるという点で液晶ディスプレイなどの電圧制御型とは大きく異なる。

10

**【0003】**

有機ELディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として単純マトリクス方式とアクティブマトリクス方式がある。前者は構造が単純であるものの、大型且つ高精細のディスプレイの実現が難しいなどの問題がある為、現在はアクティブマトリクス方式の開発が盛んに行われている。この方式は、各画素回路内部の発光素子に流れる電流を、画素回路内部に設けた能動素子（一般には、薄膜トランジスタ、TFT）によって制御するものであり、以下の特許文献に記載がある。

20

**【0004】**

**【特許文献1】特開2003-255856**

**【特許文献2】特開2003-271095**

**【特許文献3】特開2004-133240**

**【特許文献4】特開2004-029791**

**【特許文献5】特開2004-093682**

**【特許文献6】特開2006-215213**

30

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

従来の画素回路は、制御信号を供給する行状の走査線と映像信号を供給する列状の信号線とが交差する部分に配され、少なくともサンプリングトランジスタと保持容量とドライブトランジスタと発光素子とを含む。サンプリングトランジスタは、走査線から供給される制御信号に応じて導通して、信号線から供給された映像信号をサンプリングする。保持容量は、サンプリングされた映像信号に応じた入力電圧を保持する。ドライブトランジスタは、保持容量に保持された入力電圧に応じて所定の発光期間に出力電流を供給する。尚、一般に、出力電流はドライブトランジスタのチャネル領域のキャリア移動度及び閾電圧に対して依存性を有する。発光素子は、ドライブトランジスタから供給された出力電流により映像信号に応じた輝度で発光する。

40

**【0006】**

ドライブトランジスタは、保持容量に保持された入力電圧をゲートに受けてソース／ドレイン間に電流を流し、発光素子に通電する。一般に、発光素子の発光輝度は通電量に比例している。更に、ドライブトランジスタの出力電流供給量は、ゲート電圧、すなわち保持容量に書き込まれた入力電圧によって制御される。従来の画素回路は、ドライブトランジスタのゲートに印加される入力電圧を入力映像信号に応じて変化させることで、発光素子に供給する電流量を制御している。

**【0007】**

50

ここでドライブトランジスタの動作特性は以下の式1で表される。

【0008】

$$I_{ds} = (1/2) \mu (W/L) C_{ox} (V_{gs} - V_{th})^2 \dots \text{式1}$$

【0009】

このトランジスタ特性式1において、 $I_{ds}$ はソース／ドレイン間に流れるドレン電流を表しており、画素回路では発光素子に供給される出力電流である。 $V_{gs}$ はソースを基準としてゲートに印加されるゲート電圧を表しており、画素回路では上述した入力電圧である。 $V_{th}$ はトランジスタの閾電圧である。又、 $\mu$ はトランジスタのチャネルを構成する半導体薄膜の移動度を表している。その他、 $W$ はチャネル幅を表し、 $L$ はチャネル長を表し、 $C_{ox}$ はゲート容量を表している。このトランジスタ特性式1から明らかなる様に、薄膜トランジスタは飽和領域で動作する時、ゲート／ソース間電圧 $V_{gs}$ が閾電圧 $V_{th}$ を超えて大きくなると、オン状態となってドレン電流 $I_{ds}$ が流れる。原理的に見ると、上記のトランジスタ特性式1が示す様に、ゲート／ソース間電圧 $V_{gs}$ が一定であれば、常に同じ量のドレン電流 $I_{ds}$ が発光素子に供給される。従って、画面を構成する各画素に全て同一のレベルの映像信号を供給すれば、全画素が同一輝度で発光し、画面の一様性（ユニフォーミティ）が得られるはずである。

【0010】

しかしながら、実際には、ポリシリコンなどの半導体膜で構成された薄膜トランジスタ（TFT）は、個々のデバイス特性にばらつきがある。例えば閾電圧 $V_{th}$ は必ずしも一定ではなく、デバイスごとにばらつきがある。前述のトランジスタ特性式1から明らかなる様に、ドライブトランジスタの閾電圧 $V_{th}$ がばらつくと、ゲート／ソース間電圧 $V_{gs}$ が一定であっても、ドレン電流 $I_{ds}$ にばらつきが生じ、画素毎に輝度がばらついてしまうため、画面のユニフォーミティを損なう。従来から、ドライブトランジスタの閾電圧のばらつきをキャンセルする機能（閾電圧補正機能）を組み込んだ画素回路が開発されており、例えば前記の特許文献3に開示がある。

【0011】

ドライブトランジスタは、閾電圧 $V_{th}$ に加え、移動度 $\mu$ もデバイスごとにばらつきがある。前述のトランジスタ特性式1から明らかなる様に、移動度 $\mu$ がばらつくと、ゲート／ソース間電圧 $V_{gs}$ が一定であっても、ドレン電流 $I_{ds}$ にばらつきが生じ、画素毎に移動度がばらついてしまうため、画面のユニフォーミティを損なう。従来からドライブトランジスタの移動度のばらつきをキャンセルする機能（移動度補正機能）を組み込んだ画素回路も開発されており、例えば前記の特許文献6に開示がある。

【0012】

従来の画素回路は、各フィールドで発光期間と非発光期間とに別れて動作し、且つ、非発光期間で上述したドライブトランジスタの閾電圧補正動作や移動度補正動作を行っている。

【0013】

従来の画素回路は、各フィールドで発光期間と非発光期間を切り換えるため、サンプリングトランジスタやドライブトランジスタに加えてスイッチングトランジスタを備えていた。このスイッチングトランジスタをオンオフ制御することで、画素の発光状態と非発光状態を切り換えている。

【0014】

かかる構成を有する画素回路をマトリクス状に配した画素アレイ部を駆動するため、周辺の駆動部はサンプリングトランジスタを線順次走査するためのライトスキャナに加え、スイッチングトランジスタをオンオフ制御して発光期間と非発光期間を切り換えるため別のスキャナを必要としていた。

【0015】

従来のアクティブマトリクス型表示装置は一枚のパネルで構成されている。パネルの中央部に画面を構成する画素アレイ部が配され、画面を囲む周辺部に駆動回路が配される。パネルの周辺部は中央の画面を額縁のように囲んでいるため、周辺部を額縁部と呼ぶ場合

がある。ここで駆動回路に必要とされるスキャナの数が多くなるほど、レイアウト的にパネル額縁部の面積が大きくなってしまう。パネルの額縁サイズが大きいほど、中央の画面領域を圧迫し、セット製品の形状やデザインの自由度が減少し、セットの設計を大きく制限している。周辺駆動回路の複雑化に伴う額縁部面積の肥大化は解決すべき課題となっている。

#### 【課題を解決するための手段】

##### 【0016】

上述した従来の技術の課題に鑑み、本発明は周辺の駆動部に含まれるスキャナの数を削減して額縁部の面積の縮小化（以下本明細書ではこれを狭額縁化と呼ぶ場合がある）を達成することを目的とする。かかる目的を達成するために以下の手段を講じた。即ち、本発明は、画素アレイ部とこれを駆動する駆動部とからなり、前記画素アレイ部は、行状の走査線と、列状の信号線と、各走査線と各信号線とが交差する部分に配された行列状の画素とからなり、前記駆動部は少なくとも、フィールド毎に走査線の順次走査を行って各走査線に制御信号を供給するライトスキャナと、該順次走査に合わせて各信号線に映像信号を供給する信号セレクタとを有し、各画素は少なくとも、サンプリングトランジスタと、ドライブトランジスタと、保持容量と、発光素子とを含み、前記サンプリングトランジスタは、その制御端が該走査線に接続し、その一対の電流端が該信号線と該ドライブトランジスタの制御端との間に接続し、前記ドライブトランジスタは、一対の電流端の一方が電源に接続し他方が該発光素子に接続し、前記保持容量は該ドライブトランジスタの制御端に接続し、前記サンプリングトランジスタは、該制御信号に応じてオンし該映像信号をサンプリングして該保持容量に書き込み、前記ドライブトランジスタは、該保持容量に書き込まれた映像信号に応じた駆動電流を該発光素子に供給する表示装置であって、各画素は、各フィールドで発光期間と非発光期間とに分かれて動作し、且つ非発光期間に該ドライブトランジスタの閾値電圧補正動作、保持容量に対する映像信号の書き動作及び該ドライブトランジスタの移動度補正動作を行い、前記信号セレクタは、各信号線に対して映像信号のほかに各発光素子を消灯するための所定電位を供給し、前記ライトスキャナは、信号線から映像信号を画素に取り込むための制御信号のほかに、信号線から所定電位を画素に取り込むための制御信号を各走査線に供給し、前記サンプリングトランジスタは、該ライトスキャナから供給された制御信号に応じて信号線から該所定電位を取り込んでドライブトランジスタの制御端に印加し、以って発光素子を消灯して発光期間から非発光期間への切り換えを行うことを特徴とする。

##### 【0017】

一態様では、前記画素は、該保持容量が該ドライブトランジスタの制御端と電流端との間に接続しており、該映像信号のサンプリングに先立って、該ドライブトランジスタがカットオフするまで電流を流し、カットオフした時現われるドライブトランジスタの制御端と電流端との間の電圧を該保持容量に書き込み、以って該ドライブトランジスタの閾電圧補正動作を行う。又、該サンプリングトランジスタがオンして映像信号を該保持容量に書き込む際、該ドライブトランジスタに流れる駆動電流を所定の補正期間該保持容量に負帰還し、以って該ドライブトランジスタの移動度補正動作を行う。

##### 【発明の効果】

##### 【0018】

本発明によれば、ライトスキャナは、信号線から映像信号を画素回路に取り込むための制御信号の他に、信号線から所定電位を画素回路に取り込むための制御信号を各走査線に供給している。サンプリングトランジスタは、ライトスキャナから供給されたこの制御信号に応じて信号線から所定電位を取り込んでドライブトランジスタをカットオフし、以て発光素子を消灯して発光期間から非発光期間への切り換えを行っている。かかる構成により、各画素回路は発光期間と非発光期間を切り換えるためのスイッチングトランジスタが不要になる。また、駆動部はこのスイッチングトランジスタを線順次走査するためのスキャナが不要になり、パネルの狭額縁化を達成することができる。

##### 【発明を実施するための最良の形態】

10

20

30

40

50

## 【0019】

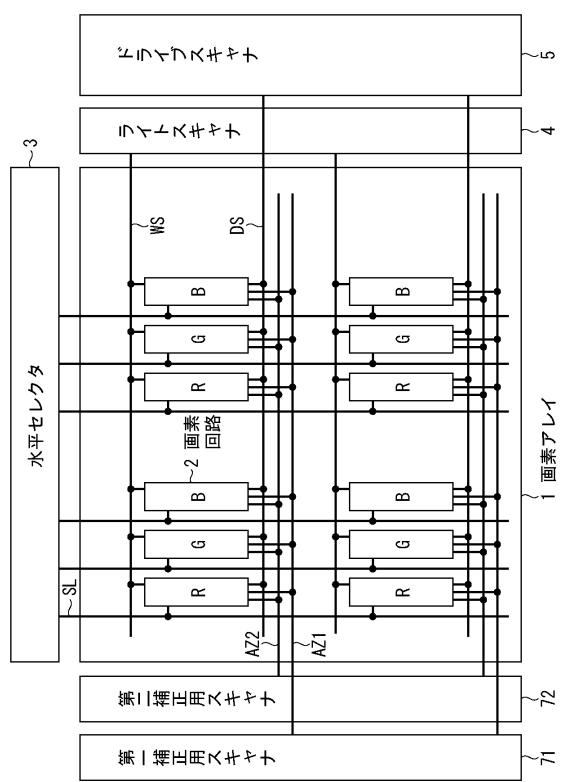

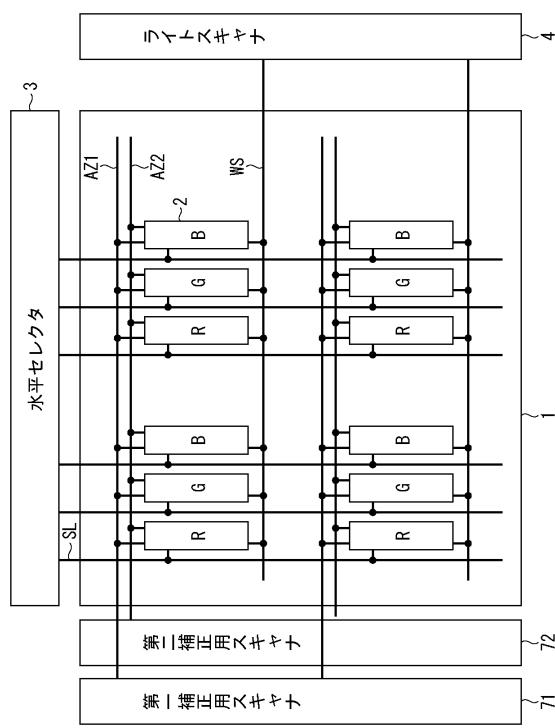

以下、図面を参照して、本発明の実施の形態を詳細に説明する。その前に、本発明の背景を明らかにするため、図1を参照してアクティブマトリクス型表示装置の参考例を説明する。図示する様に、アクティブマトリクス表示装置は、主要部となる画素アレイ部1と周辺の回路部とで構成されている。周辺の回路部は、水平セレクタ3、ライトスキャナ4、ドライブスキャナ5、補正用スキャナ71, 72などを含んでいる。画素アレイ部1は、行状の走査線WSと、列状の信号線SLと、両者の交差する部分にマトリクス状に配列した画素R, G, Bとで構成されている。カラー表示を可能とする為、RGBの三原色画素を用意しているが、本発明はこれに限られるものではない。各画素R, G, Bは、夫々、画素回路2で構成されている。信号線SLは水平セレクタ3によって駆動される。水平セレクタ3は信号部を構成し、信号線SLに映像信号を供給する。走査線WSはライトスキャナ4によって走査される。なお、走査線WSと並行に別の走査線DS, AZ1及びAZ2も配線されている。走査線DSはドライブスキャナ5によって走査される。走査線AZ1は第一補正用スキャナ71によって走査される。走査線AZ2は第二補正用スキャナ72によって走査される。ライトスキャナ4、ドライブスキャナ5、第一補正用スキャナ71及び第二補正用スキャナ72はスキャナ部を構成しており、1水平期間ごと画素回路の行を順次走査する。この参考例は合計4個のスキャナを備えているため、額縁部の面積が広くなり、狭額縁化の妨げとなっている。各画素回路2は、走査線WSによって選択されたとき、信号線SLから映像信号をサンプリングする。さらに、走査線DSによって選択されたとき、サンプリングされた映像信号によって画素回路2内に含まれている発光素子を駆動する。換言すると、走査線DSに制御信号を供給するドライブスキャナ5は、画素を発光期間と非発光期間とで切り換えている。加えて、画素回路2は、走査線AZ1及びAZ2によって走査されたとき、予め決められた補正動作を行う。

## 【0020】

上述した画素アレイ部1は通常ガラスなどの絶縁基板上に形成されており、フラットパネルとなっている。各画素回路2は低温ポリシリコン TFTで形成されている。低温ポリシリコン TFTの場合、信号部及びスキャナ部も同じ低温ポリシリコン TFTで形成できるので、フラットパネル上に画素アレイ部と信号部とスキャナ部を一体的に形成できる。信号部とスキャナ部とで周辺駆動部を構成している。

## 【0021】

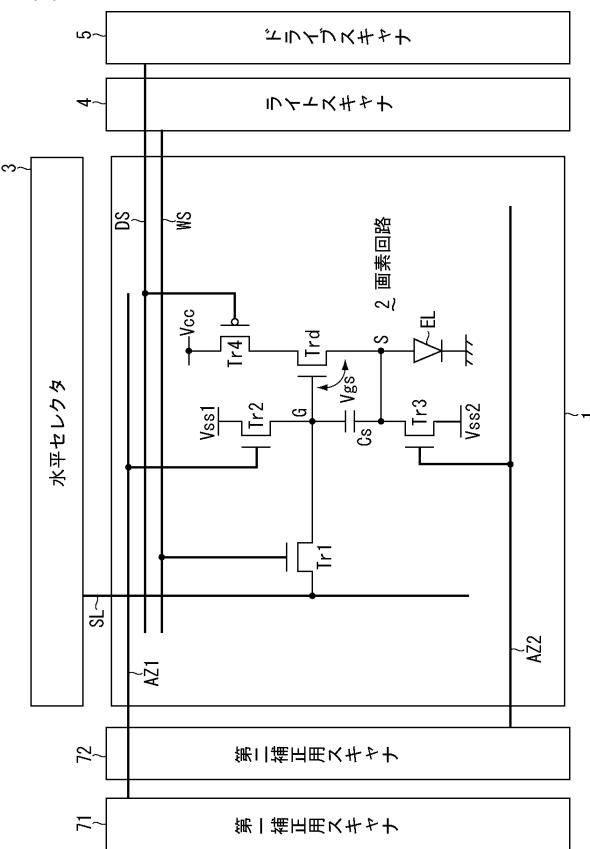

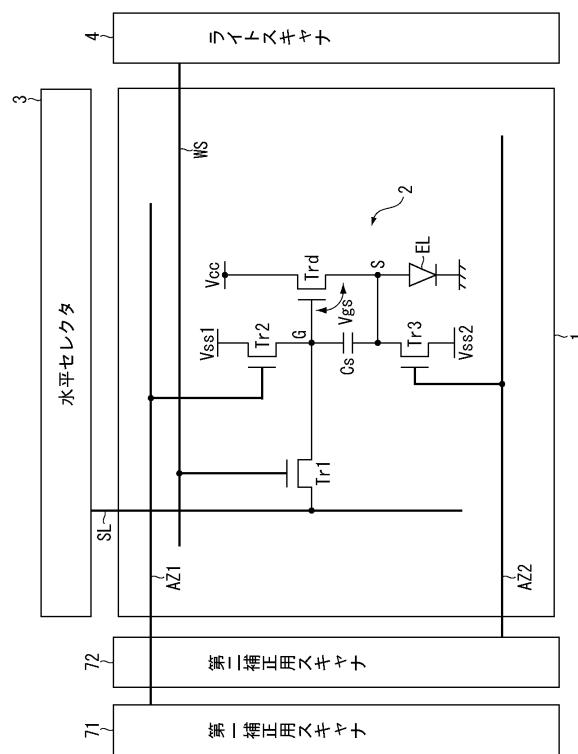

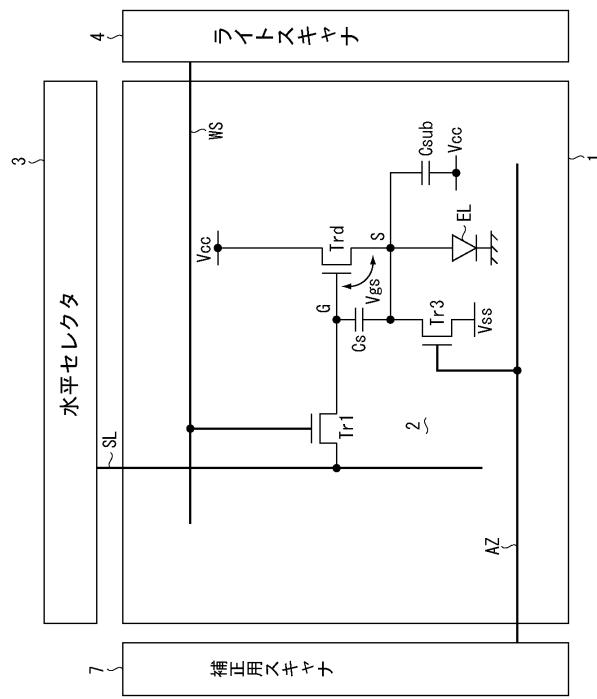

図2は、図1に示した参考例にかかる表示装置に含まれる画素回路の構成を示す回路図である。画素回路2は、5個の薄膜トランジスタTr1～Tr4及びTrdと1個の容量素子（保持容量）Csと1個の発光素子ELとで構成されている。トランジスタTr1～Tr3とTrdはNチャネル型のポリシリコン TFTである。トランジスタTr4のみPチャネル型のポリシリコン TFTである。1個の容量素子Csは本画素回路2の容量部を構成している。発光素子ELは、例えばアノード及びカソードを備えたダイオード型の有機EL素子である。

## 【0022】

画素回路2の中心となるドライブトランジスタTrdは、そのゲートGが保持容量Csの一端に接続され、そのソースSが同じく保持容量Csの他端に接続されている。また、ドライブトランジスタTrdのゲートGは、スイッチングトランジスタTr2を介して基準電位V<sub>ss1</sub>に接続されている。ドライブトランジスタTrdのドレインは、スイッチングトランジスタTr4を介して電源V<sub>cc</sub>に接続されている。このスイッチングトランジスタTr4のゲートは、走査線AZ1に接続されている。スイッチングトランジスタTr4のゲートは、走査線DSに接続されている。発光素子ELのアノードはドライブトランジスタTrdのソースSに接続され、カソードは接地されている。この接地電位はV<sub>cath</sub>で表される場合がある。また、ドライブトランジスタTrdのソースSと別の基準電位V<sub>ss2</sub>との間に、スイッチングトランジスタTr3が介在している。このトランジスタTr3のゲートは、走査線AZ2に接続されている。一方、サンプリングトランジスタTr1は、信号線SLとドライブトランジスタTrdのゲートGとの間に接続されている。サンプ

10

20

30

40

50

リングトランジスタ  $T_{r1}$  のゲートは、走査線  $W_S$  に接続されている。

#### 【0023】

かかる構成において、サンプリングトランジスタ  $T_{r1}$  は、所定のサンプリング期間に走査線  $W_S$  から供給される制御信号  $W_S$  に応じて導通して、信号線  $S_L$  から供給された映像信号  $V_{sig}$  を保持容量  $C_s$  にサンプリングする。保持容量  $C_s$  は、サンプリングされた映像信号  $V_{sig}$  に応じてドライブトランジスタのゲート  $G$  とソース  $S$  間に入力電圧  $V_{gs}$  を印加する。ドライブトランジスタ  $T_{rd}$  は、所定の発光期間中、入力電圧  $V_{gs}$  に応じた出力電流  $I_{ds}$  を発光素子  $E_L$  に供給する。なお、この出力電流（ドレン電流） $I_{ds}$  はドライブトランジスタ  $T_{rd}$  のチャネル領域のキャリア移動度  $\mu$  及び閾電圧  $V_{th}$  に対して依存性を有する。発光素子  $E_L$  は、ドライブトランジスタ  $T_{rd}$  から供給された出力電流  $I_{ds}$  により映像信号  $V_{sig}$  に応じた輝度で発光する。

10

#### 【0024】

画素回路 2 はスイッチングトランジスタ  $T_{r2} \sim T_{r4}$  で構成される補正手段を備えており、出力電流  $I_{ds}$  のキャリア移動度  $\mu$  に対する依存性を打ち消す為に、予め、発光期間の先頭で保持容量  $C_s$  に保持された入力電圧  $V_{gs}$  を補正する。具体的には、この補正手段（ $T_{r2} \sim T_{r4}$ ）は、走査線  $W_S$  及び  $D_S$  から供給される制御信号  $W_S, D_S$  に応じてサンプリング期間の一部で動作し、映像信号  $V_{sig}$  がサンプリングされている状態でドライブトランジスタ  $T_{rd}$  から出力電流  $I_{ds}$  を取り出し、これを保持容量  $C_s$  に負帰還して入力電圧  $V_{gs}$  を補正する。さらに、この補正手段（ $T_{r2} \sim T_{r4}$ ）は、出力電流  $I_{ds}$  の閾電圧  $V_{th}$  に対する依存性を打ち消すために、予め、サンプリング期間に先立ってドライブトランジスタ  $T_{rd}$  の閾電圧  $V_{th}$  を検出し、且つ、検出された閾電圧  $V_{th}$  を入力電圧  $V_{gs}$  に足し込む様にしている。

20

#### 【0025】

ドライブトランジスタ  $T_{rd}$  は N チャネル型トランジスタで、ドレンが電源  $V_{cc}$  側に接続される一方、ソース  $S$  が発光素子  $E_L$  側に接続されている。この場合、前述した補正手段は、サンプリング期間の後部分に重なる発光期間の先頭部分でドライブトランジスタ  $T_{rd}$  から出力電流  $I_{ds}$  を取り出して、保持容量  $C_s$  側に負帰還する。その際、補正手段は、発光期間の先頭部分でドライブトランジスタ  $T_{rd}$  のソース  $S$  側から取り出した出力電流  $I_{ds}$  が、発光素子  $E_L$  の有する容量に流れ込むようにしている。具体的には、発光素子  $E_L$  はアノード及びカソードを備えたダイオード型の発光素子から成り、アノード側がドライブトランジスタ  $T_{rd}$  のソース  $S$  に接続される一方、カソード側が接地されている。この構成で、補正手段（ $T_{r2} \sim T_{r4}$ ）は、予め、発光素子  $E_L$  のアノード / カソード間を逆バイアス状態にセットしておき、ドライブトランジスタ  $T_{rd}$  のソース  $S$  側から取り出した出力電流  $I_{ds}$  が発光素子  $E_L$  に流れ込む時、このダイオード型の発光素子  $E_L$  を容量性素子として機能させている。なお、補正手段は、サンプリング期間内でドライブトランジスタ  $T_{rd}$  から出力電流  $I_{ds}$  を取り出す時間幅  $t$  を調整可能であり、これにより、保持容量  $C_s$  に対する出力電流  $I_{ds}$  の負帰還量を最適化している。

30

#### 【0026】

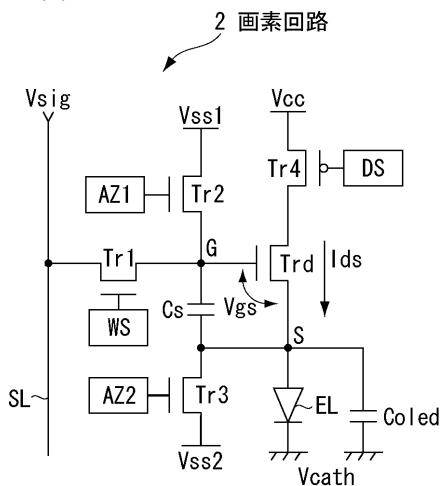

図 3 は、図 2 に示した表示装置から画素回路の部分を取り出した模式図である。理解を容易にする為、サンプリングトランジスタ  $T_{r1}$  によってサンプリングされる映像信号  $V_{sig}$  や、ドライブトランジスタ  $T_{rd}$  の入力電圧  $V_{gs}$  及び出力電流  $I_{ds}$ 、さらには、発光素子  $E_L$  が有する容量成分  $C_{oled}$ などを書き加えてある。以下、図 3 に基づいて、本画素回路 2 の基本的な動作を説明する。

40

#### 【0027】

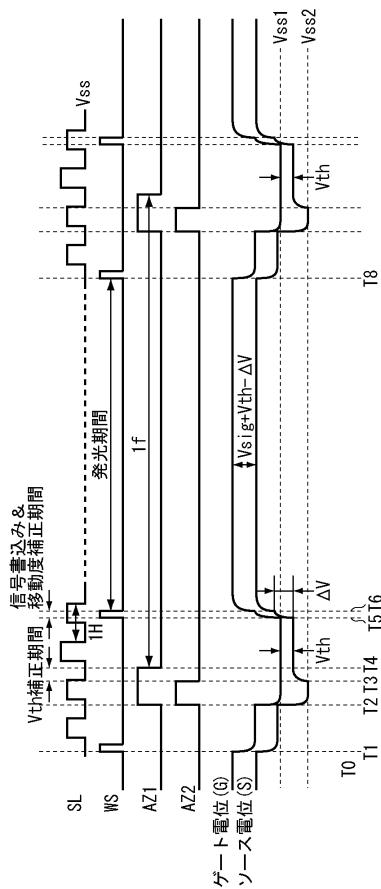

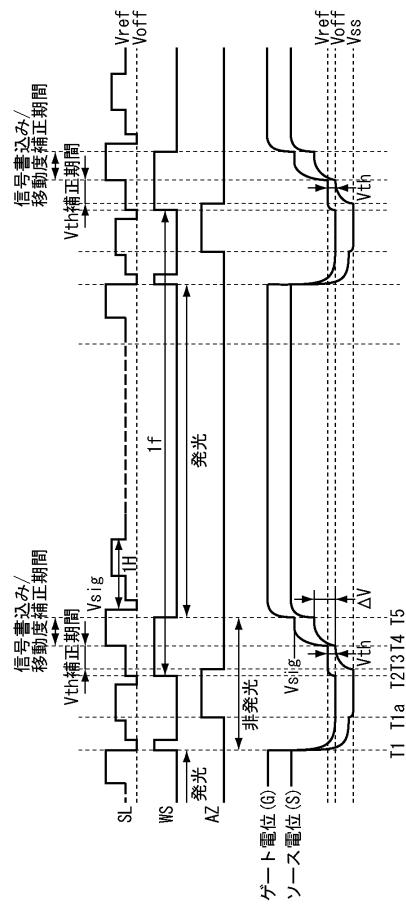

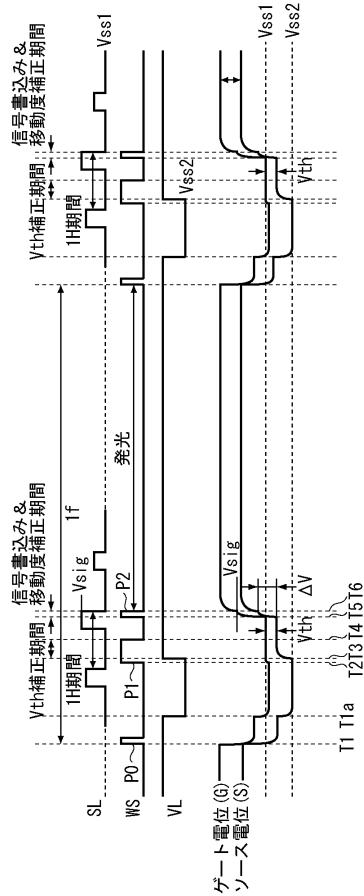

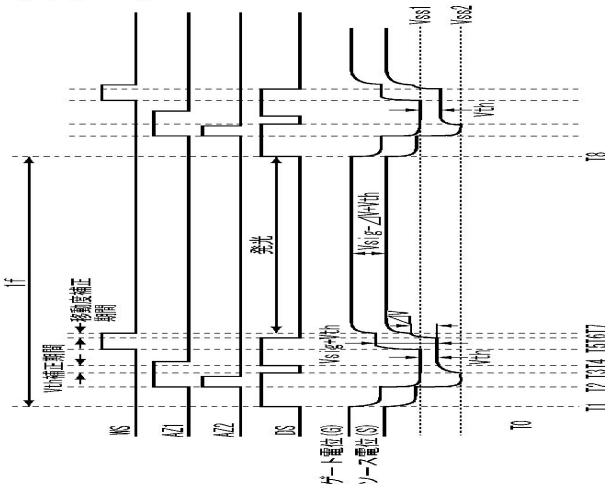

図 4 は、図 3 に示した画素回路のタイミングチャートである。図 4 を参照して、図 3 に示した画素回路の動作を、より具体的、且つ、詳細に説明する。図 4 は、時間軸  $T$  に沿って各走査線  $W_S, A_Z1, A_Z2$  及び  $D_S$  に印加される制御信号の波形を表してある。表記を簡略化する為、制御信号も対応する走査線の符号と同じ符号で表してある。トランジスタ  $T_{r1}, T_{r2}, T_{r3}$  は N チャネル型なので、走査線  $W_S, A_Z1, A_Z2$  がそれぞれハイレベルの時、オンし、ローレベルの時、オフする。一方、トランジスタ  $T_{r4}$  は

50

P チャネル型なので、走査線 D S がハイレベルの時、オフし、ローレベルの時、オンする。なお、このタイミングチャートは、各制御信号 W S , A Z 1 , A Z 2 , D S の波形と共に、ドライブトランジスタ T r d のゲート G の電位変化及びソース S の電位変化も表している。

#### 【 0 0 2 8 】

図 4 のタイミングチャートではタイミング T 1 ~ T 8 までを 1 フィールド ( 1 f ) としてある。1 フィールドの間に画素アレイ部の各行が一回順次走査される。タイミングチャートは、1 行分の画素回路に印加される各制御信号 W S , A Z 1 , A Z 2 , D S の波形を表してある。

#### 【 0 0 2 9 】

当該フィールドが始まる前のタイミング T 0 で、全ての制御信号 W S , A Z 1 , A Z 2 , D S がローレベルにある。したがって、N チャネル型のトランジスタ T r 1 , T r 2 , T r 3 はオフ状態にある一方、P チャネル型のトランジスタ T r 4 のみオン状態である。したがって、ドライブトランジスタ T r d はオン状態のトランジスタ T r 4 を介して電源 V cc に接続されているので、所定の入力電圧 V gs に応じて出力電流 I ds を発光素子 E L に供給している。したがって、タイミング T 0 で発光素子 E L は発光している。この時、ドライブトランジスタ T r d に印加される入力電圧 V gs は、ゲート電位 ( G ) とソース電位 ( S ) の差で表される。

#### 【 0 0 3 0 】

当該フィールドが始まるタイミング T 1 で、制御信号 D S がローレベルからハイレベルに切り替わる。これにより、トランジスタ T r 4 がオフし、ドライブトランジスタ T r d は電源 V cc から切り離されるので、発光が停止し、非発光期間に入る。したがって、タイミング T 1 に入ると、全てのトランジスタ T r 1 ~ T r 4 がオフ状態になる。

#### 【 0 0 3 1 】

続いてタイミング T 2 に進むと、制御信号 A Z 1 及び A Z 2 がハイレベルになるので、スイッチングトランジスタ T r 2 及び T r 3 がオンする。この結果、ドライブトランジスタ T r d のゲート G が基準電位 V ss1 に接続され、ソース S が基準電位 V ss2 に接続される。ここで  $V_{ss1} - V_{ss2} > V_{th}$  を満たしており、 $V_{ss1} - V_{ss2} = V_{gs} > V_{th}$  とする事で、その後タイミング T 3 で行われる V th 補正の準備を行う。換言すると、期間 T 2 ~ T 3 は、ドライブトランジスタ T r d のリセット期間に相当する。また、発光素子 E L の閾電圧を V thEL とすると、 $V_{thEL} > V_{ss2}$  に設定されている。これにより、発光素子 E L にはマイナスバイアスが印加され、いわゆる逆バイアス状態となる。この逆バイアス状態は、後で行う V th 補正動作及び移動度補正動作を正常に行うために必要である。

#### 【 0 0 3 2 】

タイミング T 3 では、制御信号 A Z 2 をローレベルにし、且つ、直後、制御信号 D S もローレベルにしている。これにより、トランジスタ T r 3 がオフする一方、トランジスタ T r 4 がオンする。この結果、ドレイン電流 I ds が保持容量 C s に流れ込み、V th 補正動作を開始する。この時、ドライブトランジスタ T r d のゲート G は V ss1 に保持されており、ドライブトランジスタ T r d がカットオフするまで電流 I ds が流れれる。カットオフすると、ドライブトランジスタ T r d のソース電位 ( S ) は  $V_{ss1} - V_{th}$  となる。ドレイン電流がカットオフした後のタイミング T 4 で制御信号 D S を再びハイレベルに戻し、スイッチングトランジスタ T r 4 をオフする。さらに、制御信号 A Z 1 もローレベルに戻し、スイッチングトランジスタ T r 2 もオフする。この結果、保持容量 C s に V th が保持固定される。この様にタイミング T 3 ~ T 4 はドライブトランジスタ T r d の閾電圧 V th を検出する期間である。ここでは、この検出期間 T 3 ~ T 4 を V th 補正期間と呼んでいる。

#### 【 0 0 3 3 】

この様に V th 補正を行った後、タイミング T 5 で制御信号 W S をハイレベルに切り替え、サンプリングトランジスタ T r 1 をオンして映像信号 V sig を保持容量 C s に書き込む。発光素子 E L の等価容量 C oled に比べて保持容量 C s は充分に小さい。この結果、映像信号 V sig のほとんど大部分が保持容量 C s に書き込まれる。正確には、V ss1 に対する V

10

20

30

40

50

<sub>sig</sub>の差分  $V_{sig} - V_{ss1}$  が保持容量  $C_s$  に書き込まれる。したがって、ドライブトランジスタ  $T_{rd}$  のゲート G とソース S 間の電圧  $V_{gs}$  は、先に検出保持された  $V_{th}$  と今回サンプリングされた  $V_{sig} - V_{ss1}$  を加えたレベル ( $V_{sig} - V_{ss1} + V_{th}$ ) となる。以降、説明簡易化の為、 $V_{ss1} = 0 \text{ V}$  とすると、ゲート / ソース間電圧  $V_{gs}$  は、図 4 のタイミングチャートに示すように、 $V_{sig} + V_{th}$  となる。かかる映像信号  $V_{sig}$  のサンプリングは、制御信号  $WS$  がローレベルに戻るタイミング  $T_7$  まで行われる。すなわち、タイミング  $T_5 \sim T_7$  がサンプリング期間に相当する。

## 【0034】

サンプリング期間の終了するタイミング  $T_7$  より前のタイミング  $T_6$  で制御信号  $DS$  がローレベルとなり、スイッチングトランジスタ  $T_{r4}$  がオンする。これにより、ドライブトランジスタ  $T_{rd}$  が電源  $V_{cc}$  に接続されるので、画素回路は非発光期間から発光期間に進む。この様に、サンプリングトランジスタ  $T_{r1}$  がまだオン状態で、且つ、スイッチングトランジスタ  $T_{r4}$  がオン状態に入った期間  $T_6 \sim T_7$  で、ドライブトランジスタ  $T_{rd}$  の移動度補正を行う。即ち、参考例では、サンプリング期間の後部分と発光期間の先頭部分とが重なる期間  $T_6 \sim T_7$  で移動度補正を行っている。なお、この移動度補正を行う発光期間の先頭では、発光素子  $EL$  は実際には逆バイアス状態にあるので、発光する事はない。この移動度補正期間  $T_6 \sim T_7$  では、ドライブトランジスタ  $T_{rd}$  のゲート G が映像信号  $V_{sig}$  のレベルに固定された状態で、ドライブトランジスタ  $T_{rd}$  にドレイン電流  $I_{ds}$  が流れる。ここで  $V_{ss1} - V_{th} < V_{thEL}$  と設定しておく事で、発光素子  $EL$  は逆バイアス状態におかれると、ダイオード特性ではなく、単純な容量特性を示すようになる。よって、ドライブトランジスタ  $T_{rd}$  に流れる電流  $I_{ds}$  は、保持容量  $C_s$  と発光素子  $EL$  の等価容量  $C_{oled}$  の両者を結合した容量  $C = C_s + C_{oled}$  に書き込まれていく。これにより、ドライブトランジスタ  $T_{rd}$  のソース電位 (S) は上昇していく。図 4 のタイミングチャートでは、この上昇分を  $V$  で表してある。この上昇分  $V$  は、結局、保持容量  $C_s$  に保持されたゲート / ソース間電圧  $V_{gs}$  から差し引かれる事になるので、負帰還をかけた事になる。この様に、ドライブトランジスタ  $T_{rd}$  の出力電流  $I_{ds}$  を同じくドライブトランジスタ  $T_{rd}$  の入力電圧  $V_{gs}$  に負帰還する事で、移動度  $\mu$  を補正する事が可能である。なお、負帰還量  $V$  は、移動度補正期間  $T_6 \sim T_7$  の時間幅  $t$  を調整する事で最適化可能である。

## 【0035】

タイミング  $T_7$  では、制御信号  $WS$  がローレベルとなり、サンプリングトランジスタ  $T_{r1}$  がオフする。この結果、ドライブトランジスタ  $T_{rd}$  のゲート G は信号線  $SL$  から切り離される。映像信号  $V_{sig}$  の印加が解除されるので、ドライブトランジスタ  $T_{rd}$  のゲート電位 (G) は上昇可能となり、ソース電位 (S) と共に上昇していく。その間、保持容量  $C_s$  に保持されたゲート / ソース間電圧  $V_{gs}$  は ( $V_{sig} - V + V_{th}$ ) の値を維持する。ソース電位 (S) の上昇に伴い、発光素子  $EL$  の逆バイアス状態は解消されるので、出力電流  $I_{ds}$  の流入により、発光素子  $EL$  は実際に発光を開始する。この時のドレイン電流  $I_{ds}$  対ゲート / ソース間電圧  $V_{gs}$  の関係は、先のトランジスタ特性式 1 の  $V_{gs}$  に  $V_{sig} - V + V_{th}$  を代入する事で、以下の式 2 のように与えられる。

## 【0036】

$$I_{ds} = k \mu (V_{gs} - V_{th})^2 = k \mu (V_{sig} - V)^2 \dots \text{式 2}$$

## 【0037】

上記式 2において、 $k = (1/2)(W/L)C_{ox}$  である。この特性式 2 から  $V_{th}$  の項がキャンセルされており、発光素子  $EL$  に供給される出力電流  $I_{ds}$  はドライブトランジスタ  $T_{rd}$  の閾電圧  $V_{th}$  に依存しない事が分かる。基本的に、ドレイン電流  $I_{ds}$  は映像信号の信号電圧  $V_{sig}$  によって決まる。換言すると、発光素子  $EL$  は映像信号  $V_{sig}$  に応じた輝度で発光する事になる。その際、 $V_{sig}$  は帰還量  $V$  で補正されている。この補正量  $V$  は、丁度、特性式 2 の係数部に位置する移動度  $\mu$  の効果を打ち消すように働く。したがって、ドレイン電流  $I_{ds}$  は、実質的に映像信号  $V_{sig}$  のみに依存する事になる。

## 【0038】

10

20

30

40

50

最後に、タイミング T 8に至ると、制御信号 D Sがハイレベルとなってスイッチングトランジスタ T r 4 がオフし、発光が終了すると共に、当該フィールドが終わる。この後、次のフィールドに移って、再び V<sub>th</sub>補正動作、移動度補正動作及び発光動作が繰り返される事になる。

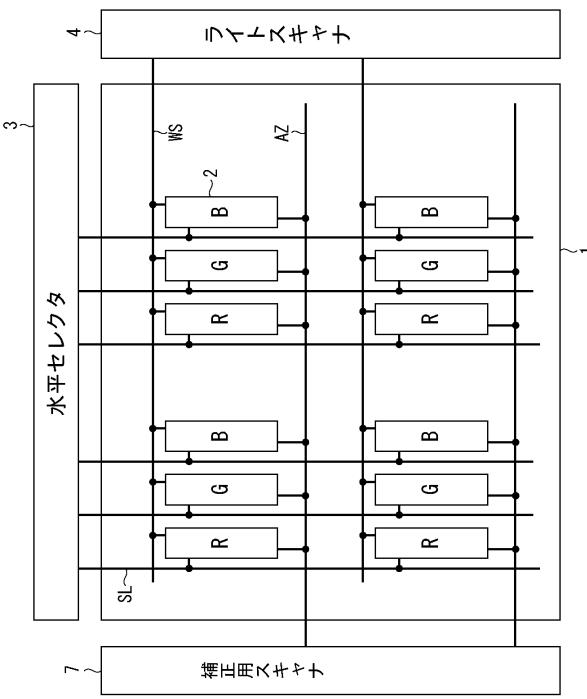

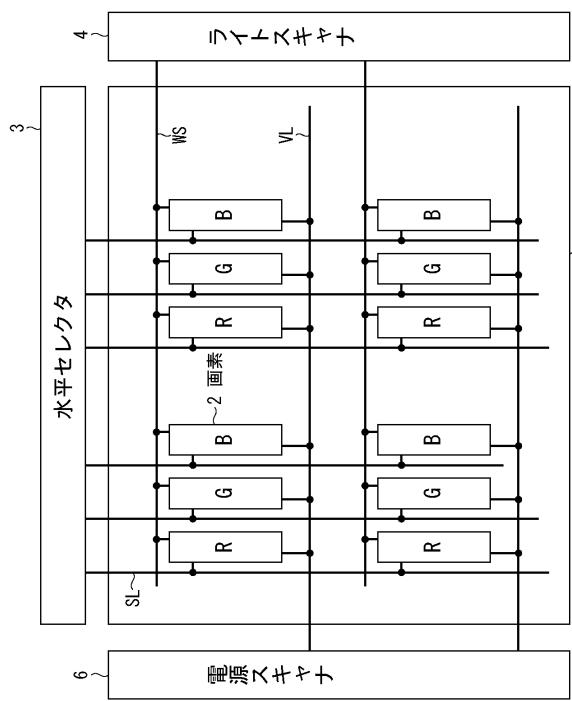

#### 【 0 0 3 9 】

上述のように、参考例にかかる表示装置は画素アレイ部を駆動するため 4 個のスキャナが必要であり、狭額縁化の妨げとなっている。図 5 は、本発明にかかる表示装置の第 1 実施形態を示しており、上述した参考例の問題点に対処したものである。図示するように、本アクティブマトリクス表示装置は、主要部となる画素アレイ部 1と周辺の駆動部とで構成されている。周辺の駆動部は、水平セレクタ 3、ライトスキャナ 4、第一補正用スキャナ 7 1及び第二補正用スキャナ 7 2を含んでいる。画素アレイ部 1 は、行状の走査線 W Sと、列状の信号線 S Lと、両者の交差する部分にマトリクス状に配列した画素回路 2で構成されている。信号線 S L は水平セレクタ 3 によって駆動される。水平セレクタ 3 は信号部を構成し、信号線 S L に映像信号となる信号電位と所定電位を時分割で供給する。この所定電位は、ドライブトランジスタをカットオフするための電位である。走査線 W S はライトスキャナ 4 によって走査される。なお、走査線 W Sと並行に別の走査線 A Z 1 及び A Z 2 も配線されている。走査線 A Z 1 は第一補正用スキャナ 7 1 によって走査される。走査線 A Z 2 は第二補正用スキャナ 7 2 によって走査される。ライトスキャナ 4、第一補正用スキャナ 7 1 及び第二補正用スキャナ 7 2 はスキャナ部を構成しており、1 水平期間ごと、画素回路の行を順次走査する。図 1 に示した参考例と比較すれば明らかのように、本実施形態の表示装置はスキャナ部が 3 個のスキャナから成り、参考例より 1 個少なく、狭額縁化を達成している。10

#### 【 0 0 4 0 】

各画素回路 2 は、走査線 W Sによって選択されたとき、信号線 S Lから映像信号の信号電位をサンプリングする。また、各画素回路 2は他のタイミングで走査線 W S によって選択されたとき、信号線 S Lから所定電位をサンプリングし、ドライブトランジスタをカットオフして、発光期間から非発光期間に切り換える。加えて、画素回路 2は走査線 A Z 1 及び A Z 2 によって走査されたとき、非発光期間で予め決められた補正動作を行う。20

#### 【 0 0 4 1 】

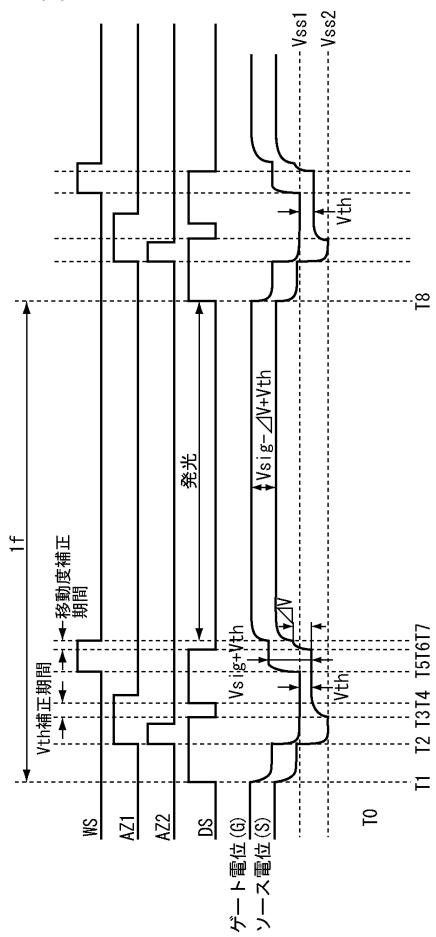

図 6 は、図 5 に示した第 1 実施形態にかかる表示装置に含まれる画素回路 2の構成を示す回路図である。図示するように画素回路 2 の中心となるドライブトランジスタ T r d は、そのゲート Gが保持容量 C s の一端に接続され、そのソース S が同じく保持容量 C s の他端に接続されている。また、ドライブトランジスタ T r dのゲート G は、スイッチングトランジスタ T r 2を介して基準電位 V<sub>ss1</sub>に接続されている。スイッチングトランジスタ T r 2 のゲートは走査線 A Z 1 に接続されている。ドライブトランジスタ T r d のドレンは電源 V<sub>cc</sub>に接続されている。発光素子 E L のアノードはドライブトランジスタ T r d のソース S に接続され、カソードは接地されている。また、ドライブトランジスタ T r dのソース S と所定の基準電位 V<sub>ss2</sub>との間に、スイッチングトランジスタ T r 3が介在している。このトランジスタ T r 3 のゲートは走査線 A Z 2 に接続されている。一方、サンプリングトランジスタ T r 1は、信号線 S Lとドライブトランジスタ T r d のゲート G との間に接続されている。サンプリングトランジスタ T r 1 のゲートは走査線 W S に接続されている。30

#### 【 0 0 4 2 】

図 7 は、図 5 及び図 6 に示した第 1 実施形態にかかる表示装置の動作説明に供するタイミングチャートである。理解を容易にするため、図 4 に示した参考例のタイミングチャートと同様の表記を採用している。図示するように、信号線 S Lには、1 水平期間(1 H 周期)で信号電位 V<sub>sig</sub>と所定電位 V<sub>ss</sub>とで切り換わる映像信号が供給されている。この所定電位 V<sub>ss</sub>はドライブトランジスタをカットオフできる程度の電位に予め設定されている。タイミング T 1 で信号線 S L に所定電位 V<sub>ss</sub>が供給されている時、走査線 W S に制御信号パルスを印加する。これにより、サンプリングトランジスタ T r 1がオンし、信号線 S40

L から所定電位  $V_{ss}$  が取り込まれ、ドライブトランジスタ Tr d のゲート G に印加される。これにより、ドライブトランジスタ Tr d がカットオフし、画素は発光期間から非発光期間に切り換わる。

#### 【 0 0 4 3 】

即ち、ドライブトランジスタ Tr d がカットオフすると、発光素子 EL に供給される電流が 0 になるため、発光素子 EL が点灯状態から消灯状態となる。この様に、本実施形態 は、参考例のようにスイッチングトランジスタのオンオフで発光期間と非発光期間を切り換えるのではなく、サンプリングトランジスタを制御してドライブトランジスタをカットオフすることで、発光期間と非発光期間を切り換えている。これにより、スイッチングトランジスタ とそのスキャナを削減することができる。

10

#### 【 0 0 4 4 】

タイミング T 2 になると、制御信号 AZ 1 及び AZ 2 がハイレベルに切り換わり、スイッチングトランジスタ Tr 2 及び Tr 3 が共にオンする。スイッチングトランジスタ Tr 2 がオンすることで、ドライブトランジスタ Tr d のゲート G に基準電位  $V_{ss1}$  が書き込まれる。また、スイッチングトランジスタ Tr 3 がオンすることで、ドライブトランジスタ Tr d のソース S に別の基準電位  $V_{ss2}$  が書き込まれる。これにより、ドライブトランジスタ Tr d のゲート G 及びソース S が所定の状態にリセットされ、閾電圧補正動作のための準備が整い、ドライブトランジスタ Tr d はオン状態に置かれる。

#### 【 0 0 4 5 】

タイミング T 3 で制御信号 AZ 2 がローレベルに戻り、スイッチングトランジスタ Tr 3 がオフして、ドライブトランジスタ Tr d のソース S が  $V_{ss2}$  から切り離され、閾電圧補正動作が行われる。これにより、ドライブトランジスタ Tr d のゲート G が  $V_{ss1}$  に固定された状態で、ドライブトランジスタ Tr d のソース S の電位が上昇して行き、両者の電位差が  $V_{th}$  に等しくなった所でドライブトランジスタ Tr d がカットオフし、閾電圧補正動作が終わる。この後、タイミング T 4 で制御信号 AZ 1 がローレベルに戻り、スイッチングトランジスタ Tr 2 もオフする。

20

#### 【 0 0 4 6 】

続いて、信号線 SL が所定電位  $V_{ss}$  から信号電位  $V_{sig}$  に切り換った後、タイミング T 6 で走査線 WS に再び制御信号パルスが印加され、サンプリングトランジスタ Tr 1 がオンする。これにより、信号線 SL から信号電位  $V_{sig}$  がサンプリングされ、保持容量 Cs に書き込まれる。このとき、同時に、移動度補正動作が行われ、補正分 V が保持容量 Cs に書き込まれる。タイミング T 5 で制御信号 WS がハイレベルに切り換わってからタイミング T 6 でローレベルに切り換わるまでの間が、信号書き込み期間及び移動度補正期間である。

30

#### 【 0 0 4 7 】

タイミング T 6 で制御信号 WS がローレベルに戻ると、サンプリングトランジスタ Tr 1 がオフし、ドライブトランジスタ Tr d のゲート G は信号線 SL から切り離される。これにより、ブートストラップ動作が可能となり、ドライブトランジスタ Tr d のソース S の電位が上昇し、発光素子 EL に駆動電流が流れ、発光期間となる。

#### 【 0 0 4 8 】

40

図 8 は、本発明にかかる表示装置の第 2 実施形態を示す全体ブロック図である。本表示装置は、基本的に、画素アレイ部 1 とこれを駆動する駆動部とで構成されている。画素アレイ部 1 は、行状の第 1 走査線 WS と、同じく行状の第 2 走査線 DS と、列状の信号線 SL と、各第 1 走査線 WS と各信号線 SL とが交差する部分に配された行列状の画素回路 2 とを備えている。これに対し、駆動部 は、ライトスキャナ 4、補正用スキャナ 7 及び水平セレクタ 3 を含んでいる。ライトスキャナ 4 は、各第 1 走査線 WS に制御信号を出力して、画素回路 2 を行単位で線順次走査する。補正用スキャナ 7 も、各第 2 走査線 AZ にそれぞれ制御信号を出力して、画素回路 2 を行単位で線順次走査する。但し、ライトスキャナ 4 と補正用スキャナ 7 は、制御信号を出力するタイミングが異なっている。一方、水平セレクタ 3 は、スキャナ 4, 7 側の線順次走査に合わせて、列状の信号線 SL に映像信号の

50

信号電位と基準電位とを供給する。

#### 【0049】

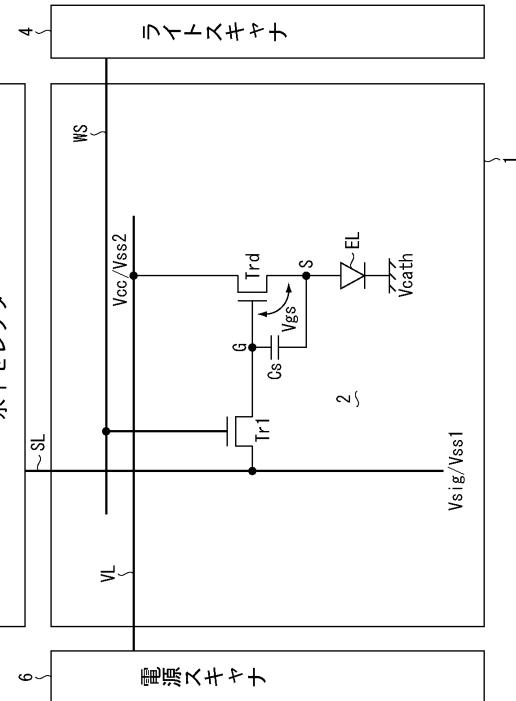

図9は、図8に示した表示装置に組み込まれる画素回路の構成を示す回路図である。図示するように本画素回路2は、基本的に、発光素子ELと、サンプリングトランジスタTr1と、ドライブトランジスタTrdと、スイッチングトランジスタTr3と、保持容量Csとを含む。サンプリングトランジスタTr1は、その制御端(ゲート)が走査線WSに接続され、一対の電流端(ソース及びドレイン)の一方が信号線SLに接続され、他方がドライブトランジスタTrdの制御端(ゲートG)に接続されている。ドライブトランジスタTrdは、一対の電流端(ソース及びドレイン)の一方(ドレイン)が電源ラインVccに接続され、他方(ソースS)が発光素子ELのアノードに接続されている。発光素子ELのカソードは所定のカソード電位Vcathに接続されている。スイッチングトランジスタTr3は、その制御端(ゲート)が走査線AZに接続され、一対の電流端(ソース及びドレイン)の一方が固定電位Vssに接続され、他方がドライブトランジスタTrdのソースSに接続されている。保持容量Csは、その一端がドライブトランジスタTrdの制御端(ゲートG)に接続され、その他端がドライブトランジスタTrdの他方の電流端(ソースS)に接続されている。このドライブトランジスタTrdの他方の電流端は、発光素子EL及び保持容量Csに対する出力電流端となっている。なお、本画素回路2においては、保持容量Csを補助する目的で、補助容量CsubがドライブトランジスタTrdのソースSと電源Vccとの間に接続されている。

#### 【0050】

かかる構成において、駆動部側のライトスキャナ4は、第1走査線WSにサンプリングトランジスタTr1を開閉制御するための制御信号を供給する。補正用スキャナ7は、第2走査線AZにスイッチングトランジスタTr3を開閉制御するための制御信号を出力する。水平セレクタ3は、信号線SLに信号電位Vsigと基準電位Vrefとの間で切り換わる映像信号(入力信号)を供給する。この様に、走査線WS、AZ及び信号線SLの電位が順次走査に合わせて変動するが、電源ラインはVccに固定されている。また、カソード電位Vcath及び固定電位Vssも一定である。

#### 【0051】

図10は、図8及び図9に示した第2実施形態にかかる表示装置の動作説明に供するタイミングチャートである。本実施形態では、信号線SLが1水平期間1Hで、信号電位Vsig、基準電位Vref及びオフ電位Voffの三電位で切り換っている。信号電位Vsigは基準電位Vrefより高く、オフ電位VoffはVrefより低く設定されている。このオフ電位Voffは、ドライブトランジスタTrdをカットオフするために必要な所定電位である。走査線WSには1フィールド(1f)で二発の制御信号パルスが供給されている。最初の制御信号パルスは、前フィールドの発光期間から当該フィールドの非発光期間に切り換えるために出力される。次の制御信号パルスは、当該フィールドの非発光期間で閾電圧補正動作と信号書き込み動作/移動度補正動作を行うときに供給されている。

#### 【0052】

まず、タイミングT1で走査線WSに1発目の制御信号パルスが印加される。このとき、信号線SLは所定のオフ電位Voffにある。サンプリングトランジスタTr1がオンし、このオフ電位VoffをサンプリングしてドライブトランジスタTrdのゲートGに印加する。これにより、ドライブトランジスタTrdのゲート電位が低下し、カットオフ状態となる。画素は発光期間から非発光期間に切り換わる。

#### 【0053】

続いてタイミングT1aで制御信号AZがローレベルからハイレベルに切り換わり、スイッチングトランジスタTr3がオンする。これにより、ドライブトランジスタTrdのソースSに固定電位Vssが書き込まれる。

#### 【0054】

この後、タイミングT2になると、再び走査線WSに制御信号パルスが印加され、サンプリングトランジスタTr1がオンする。このタイミングで、信号線SLには基準電位V

10

20

30

40

50

<sub>ref</sub>が現れている。基準電位 <sub>V<sub>ref</sub></sub> がドライブトランジスタ T<sub>r d</sub> のゲート G に書き込まれる。従って、ドライブトランジスタ T<sub>r d</sub> のゲート G / ソース S 間電圧 <sub>V<sub>gs</sub></sub> は <sub>V<sub>ref</sub></sub> - <sub>V<sub>s</sub></sub> という値を取る。ここで <sub>V<sub>gs</sub></sub> = <sub>V<sub>ref</sub></sub> - <sub>V<sub>ss</sub></sub> > <sub>V<sub>th</sub></sub> に設定されている。この <sub>V<sub>ref</sub></sub> - <sub>V<sub>ss</sub></sub> がドライブトランジスタ T<sub>r d</sub> の閾電圧 <sub>V<sub>th</sub></sub> よりも大きくないと、後続の閾電圧補正動作を正常に行うことができない。但し、<sub>V<sub>gs</sub></sub> = <sub>V<sub>ref</sub></sub> - <sub>V<sub>ss</sub></sub> > <sub>V<sub>th</sub></sub> であるため、ドライブトランジスタ T<sub>r d</sub> はこの時点でオン状態となり、貫通電流が電源ライン <sub>V<sub>cc</sub></sub> から固定電位 <sub>V<sub>ss</sub></sub> に向かって流れる。しかし、タイミング T<sub>2</sub> の後、ほとんど間を置かずにタイミング T<sub>3</sub> でスイッチングトランジスタ T<sub>r 3</sub> をオフすることで、この時流れる貫通電流はほとんど無視することができる。

## 【0055】

10

この後、タイミング T<sub>3</sub> になると、閾電圧補正期間に入り、スイッチングトランジスタ T<sub>r 3</sub> をオフしてドライブトランジスタ T<sub>r d</sub> のソース S を固定電位 <sub>V<sub>ss</sub></sub> から切り離す。ここで、ソース S の電位（即ち発光素子のアノード電位）がカソード電位 <sub>V<sub>cath</sub></sub> に発光素子 E<sub>L</sub> の閾電圧 <sub>V<sub>thEL</sub></sub> を足した値よりも低い限り、発光素子 E<sub>L</sub> は依然として逆バイアス状態に置かれ、わずかなリーク電流が流れるに過ぎない。よって、電源ライン <sub>V<sub>cc</sub></sub> からドライブトランジスタ T<sub>r d</sub> を通って供給された電流は、ほとんど保持容量 C<sub>s</sub> と補助容量 C<sub>s u b</sub> を充電するために使われる。この様に保持容量 C<sub>s</sub> が充電されるため、ドライブトランジスタ T<sub>r d</sub> のソース電位は時間の経過と共に固定電位 <sub>V<sub>ss</sub></sub> から上昇していく。一定期間後、ドライブトランジスタ T<sub>r d</sub> のソース電位は <sub>V<sub>ref</sub></sub> - <sub>V<sub>th</sub></sub> のレベルに達し、<sub>V<sub>g</sub></sub> が丁度 <sub>V<sub>th</sub></sub> になる。この時点でドライブトランジスタ T<sub>r d</sub> がカットオフし、<sub>V<sub>th</sub></sub> に相当する電圧がドライブトランジスタ T<sub>r d</sub> のソース S とゲート G との間に配されている保持容量 C<sub>s</sub> に書き込まれる。閾電圧補正動作が完了した時点でも、ソース電圧 <sub>V<sub>ref</sub></sub> - <sub>V<sub>t</sub></sub> はカソード電位 <sub>V<sub>cath</sub></sub> に発光素子の閾電圧 <sub>V<sub>thEL</sub></sub> を足した値よりも低くなっている。

20

## 【0056】

続いて、タイミング T<sub>4</sub> で、書込み期間 / 移動度補正期間に進む。タイミング T<sub>4</sub> では、信号線 S<sub>L</sub> を基準電位 <sub>V<sub>ref</sub></sub> から信号電位 <sub>V<sub>sig</sub></sub> に切り換える。信号電位 <sub>V<sub>sig</sub></sub> は階調に応じた電圧となっている。この時点でサンプリングトランジスタ T<sub>r 1</sub> はオンしているため、ドライブトランジスタ T<sub>r d</sub> のゲート G の電位は <sub>V<sub>sig</sub></sub> となる。これにより、ドライブトランジスタ T<sub>r d</sub> がオンし、電源ライン <sub>V<sub>cc</sub></sub> から電流が流れるため、ソース S の電位が時間と共に上昇していく。この時点で、依然としてソース S の電位が発光素子 E<sub>L</sub> の閾電圧 <sub>V<sub>thEL</sub></sub> とカソード電位 <sub>V<sub>cath</sub></sub> の和を超えていないので、発光素子 E<sub>L</sub> にはわずかなリーク電流が流れるだけであり、ドライブトランジスタ T<sub>r d</sub> から供給された電流は、そのほとんどが保持容量 C<sub>s</sub> と補助容量 C<sub>s u b</sub> の充電に使われる。この充電過程で、前述したようにソース S の電位が上昇していく。

30

## 【0057】

この書込み期間では既にドライブトランジスタ T<sub>r d</sub> の閾電圧補正動作は完了しているため、ドライブトランジスタ T<sub>r d</sub> が供給する電流はその移動度  $\mu$  を反映したものとなる。具体的に言うと、ドライブトランジスタ T<sub>r d</sub> の移動度  $\mu$  が大きい場合、ドライブトランジスタ T<sub>r d</sub> が供給する電流量が大きくなり、ソース S の電位上昇も速い。逆に、移動度  $\mu$  が小さいとき、ドライブトランジスタ T<sub>r d</sub> の電流供給量は小さく、ソース S の電位上昇は遅くなる。この様に、ドライブトランジスタ T<sub>r d</sub> の出力電流を保持容量 C<sub>s</sub> に負帰還することで、ドライブトランジスタ T<sub>r d</sub> のゲート G / ソース S 間電圧 <sub>V<sub>gs</sub></sub> は移動度  $\mu$  を反映した値となり、一定時間経過後には完全に移動度  $\mu$  を補正した <sub>V<sub>gs</sub></sub> の値となる。即ち、この書込み期間では、ドライブトランジスタ T<sub>r d</sub> から流れ出た電流を保持容量 C<sub>s</sub> に負帰還することで、ドライブトランジスタ T<sub>r d</sub> の移動度  $\mu$  の補正も同時に行っている。

40

## 【0058】

最後に、タイミング T<sub>5</sub> で当該フィールドの発光期間に入ると、サンプリングトランジスタ T<sub>r 1</sub> がオフし、ドライブトランジスタ T<sub>r d</sub> のゲート G が信号線 S<sub>L</sub> から切り離される。これにより、ゲート G の電位の上昇が可能となり、保持容量 C<sub>s</sub> に保持された <sub>V<sub>gs</sub></sub>

50

の値を一定に保ちつつ、ゲート G の電位上昇に連動してソース S の電位も上昇する。これにより、発光素子 E L の逆バイアス状態が解消され、ドライブトランジスタ T r d は  $V_{gs}$  に応じたドレイン電流  $I_{ds}$  を発光素子 E L に流す。ソース S の電位は発光素子 E L に電流が流れるまで上昇し、発光素子 E L が発光する。ここで、発光素子は発光時間が長くなると、その電流 / 電圧特性は変化する。このため、ソース S の電位も変化する。しかしながら、ドライブトランジスタ T r d のゲート / ソース間電圧  $V_{gs}$  はブートストラップ動作により一定値に保たれているので、発光素子 E L に流れる電流は変化しない。よって、発光素子 E L の電流 / 電圧特性が劣化しても、一定電流  $I_{ds}$  が常に流れ続け、発光素子 E L の輝度が変化することはない。

## 【0059】

10

図 11 は、本発明にかかる表示装置の第 3 実施形態を示す全体構成図である。この第 3 実施形態は、前述した第 2 実施形態と同じく、周辺の駆動部が 2 個のスキーナで構成されており、第 1 実施形態に比べて一段と狭額縁化を達成している。図示するように、本表示装置は、画素アレイ部 1 とこれを駆動する駆動部とから成る。画素アレイ部 1 は、行状の走査線 W S と、列状の信号線（信号ライン）S L と、両者が交差する部分に配された行列状の画素回路 2 と、各画素回路 2 の各行に対応して配された給電線（電源ライン）V L を備えている。なお、本例は、各画素回路 2 に R G B 三原色のいずれかが割り当てられており、カラー表示が可能である。但し、これに限られるものではなく、単色表示のデバイスも含む。駆動部は、各走査線 W S に順次制御信号を供給して画素回路 2 を行単位で線順次走査するライトスキーナ 4 と、この線順次走査に合わせて各給電線 V L に第 1 電位と第 2 電位で切り換わる電源電圧を供給する電源スキーナ 6 と、この線順次走査に合わせて列状の信号線 S L に駆動信号となる信号電位と基準電位を供給する信号セレクタ（水平セレクタ）3 とを備えている。

20

## 【0060】

図 12 は、図 11 に示した表示装置に含まれる画素回路 2 の具体的な構成及び結線関係を示す回路図である。図 9 に示した第 2 実施形態の画素回路と比較すると、トランジスタの個数が 3 個から 2 個に削減されており、画素の高精細化が可能になっている。図示するように、この画素回路 2 は、有機 E L デバイスなどで代表される発光素子 E L と、サンプリングトランジスタ T r 1 と、ドライブトランジスタ T r d と、保持容量 C s を含む。サンプリングトランジスタ T r 1 は、その制御端（ゲート）が対応する走査線 W S に接続され、一対の電流端（ソース及びドレイン）の片方が対応する信号線 S L に接続され、他方がドライブトランジスタ T r d の制御端（ゲート G）に接続される。ドライブトランジスタ T r d は、一対の電流端（ソース S 及びドレイン）の一方が発光素子 E L に接続され、他方が対応する給電線 V L に接続されている。本例では、ドライブトランジスタ T r d が N チャネル型であり、そのドレインが給電線 V L に接続される一方、ソース S が出力ノードとして発光素子 E L のアノードに接続されている。発光素子 E L のカソードは所定のカソード電位  $V_{cath}$  に接続されている。保持容量 C s は、ドライブトランジスタ T r d の片方の電流端であるソース S と制御端であるゲート G の間に接続されている。

30

## 【0061】

かかる構成において、サンプリングトランジスタ T r 1 は、走査線 W S から供給された制御信号に応じて導通し、信号線 S L から供給された信号電位をサンプリングして保持容量 C s に保持する。ドライブトランジスタ T r d は、第 1 電位（高電位  $V_{cc}$ ）にある給電線 V L から電流の供給を受け、保持容量 C s に保持された信号電位に応じて駆動電流を発光素子 E L に流す。ライトスキーナ 4 は、信号線 S L が信号電位にある時間帯にサンプリングトランジスタ T r 1 を導通状態にするため、所定のパルス幅の制御信号を制御線 W S に出力し、以て、保持容量 C s に信号電位を保持すると同時にドライブトランジスタ T r d の移動度  $\mu$  に対する補正を信号電位に加える。この後、ドライブトランジスタ T r d は、保持容量 C s に書き込まれた信号電位  $V_{sig}$  に応じた駆動電流を発光素子 E L に供給し、発光動作に入る。

40

## 【0062】

50

本画素回路 2 は、上述した移動度補正機能に加え、閾電圧補正機能も備えている。即ち、電源スキャナ 6は、サンプリングトランジスタ T r 1 が信号電位 V<sub>sig</sub> をサンプリングする前に、第 1 タイミングで給電線 V L を第 1 電位（高電位 V<sub>cc</sub>）から第 2 電位（低電位 V<sub>ss2</sub>）に切り換える。また、ライトスキャナ 4 は、同じく、サンプリングトランジスタ T r 1 が信号電位 V<sub>sig</sub> をサンプリングする前に、第 2 タイミングでサンプリングトランジスタ T r 1 を導通させて、信号線 S L から基準電位 V<sub>ss1</sub> をドライブトランジスタ T r d のゲート G に印加すると共に、ドライブトランジスタ T r d のソース S を第 2 電位（V<sub>ss2</sub>）にセットする。電源スキャナ 6 は、第 2 タイミングの後の第 3 タイミングで給電線 V L を第 2 電位 V<sub>ss2</sub> から第 1 電位 V<sub>cc</sub> に切り換えて、ドライブトランジスタ T r d の閾電圧 V<sub>th</sub> に相当する電圧を保持容量 C s に保持する。かかる閾電圧補正機能により、本表示装置は画素毎にばらつくドライブトランジスタ T r d の閾電圧 V<sub>th</sub> の影響をキャンセルすることができる。

10

## 【 0 0 6 3 】

本画素回路 2 は、さらにブートストラップ機能も備えている。即ち、ライトスキャナ 4 は、保持容量 C s に信号電位 V<sub>sig</sub> が保持された段階で走査線 W S に対する制御信号の印加を解除し、サンプリングトランジスタ T r 1 を非導通状態にして、ドライブトランジスタ T r d のゲート G を信号線 S L から電気的に切り離し、以て、ドライブトランジスタ T r d のソース S の電位変動にゲート G の電位が連動し、ゲート G とソース S 間の電圧 V<sub>gs</sub> を一定に維持することができる。

20

## 【 0 0 6 4 】

図 13 は、図 12 に示した画素回路 2 の動作説明に供するタイミングチャートである。時間軸を共通にして、走査線 W S の電位変化、給電線 V L の電位変化及び信号線 S L の電位変化を表している。また、これらの電位変化と並行に、ドライブトランジスタのゲート G 及びソース S の電位変化も表してある。

## 【 0 0 6 5 】

本発明の特徴として走査線 W S には、サンプリングトランジスタ T r 1 をオンするための制御信号パルスが印加される。この制御信号パルスは、画素アレイ部の線順次走査に合わせて 1 フィールド（1 f）周期で走査線 W S に印加される。この制御信号パルスは、1 フィールド（1 f）の間に三発のパルスを含んでいる。ここでは、最初のパルスを P 0 とし次のパルスを P 1 とし、後続のパルスを P 2 とする。給電線 V L は、1 フィールド周期（1 f）で高電位 V<sub>cc</sub> と低電位 V<sub>ss2</sub> の間で切り換わる。信号線 S L には、1 水平走査周期（1 H）内で信号電位 V<sub>sig</sub> と所定の基準電位 V<sub>ss1</sub> が切り換わる駆動信号が供給される。

30

## 【 0 0 6 6 】

図 13 のタイミングチャートに示すように、画素は前のフィールドの発光期間から当該フィールドの非発光期間に入り、その後、当該フィールドの発光期間となる。この非発光期間で、準備動作、閾電圧補正動作、信号書き込み動作、移動度補正動作などを行う。

## 【 0 0 6 7 】

前フィールドの発光期間では、給電線 V L が高電位 V<sub>cc</sub> にあり、ドライブトランジスタ T r d が駆動電流 I<sub>ds</sub> を発光素子 E L に供給している。駆動電流 I<sub>ds</sub> は高電位 V<sub>cc</sub> にある給電線 V L からドライブトランジスタ T r d を介して発光素子 E L を通り、カソードラインに流れ込んでいる。

40

## 【 0 0 6 8 】

続いて、当該フィールドの非発光期間に入ると、まず、タイミング T 1 で走査線 W S に最初の制御信号パルス P 0 が印加される。このとき、信号線 S L は所定電位（基準電位）V<sub>ss1</sub> にある。サンプリングトランジスタ T r 1 は制御信号パルス P 0 に応答してオンし、信号線 S L から V<sub>ss1</sub> を取り込む。これにより、ドライブトランジスタ T r d のゲート G の電位は急激に低下し、カットオフ状態となる。この結果、画素は発光期間から非発光期間に切り換わる。

## 【 0 0 6 9 】

続いて、タイミングT 1 aで、給電線V Lを高電位 $V_{cc}$ から低電位 $V_{ss2}$ に切り換える。これにより、給電線V Lは $V_{ss2}$ まで放電され、さらに、ドライブトランジスタTr dのソースSの電位も $V_{ss2}$ まで下降する。

#### 【0070】

続いて、タイミングT 2になると、走査線WSを低レベルから高レベルに切り換えることで、サンプリングトランジスタTr 1が導通状態になる。この時、信号線SLは基準電位 $V_{ss1}$ にある。よって、ドライブトランジスタTr dのゲートGの電位は、導通したサンプリングトランジスタTr 1を通じて信号線SLの基準電位 $V_{ss1}$ となる。この時、ドライブトランジスタTr dのソースSの電位は、 $V_{ss1}$ よりも十分低い電位 $V_{ss2}$ にある。この様にして、ドライブトランジスタTr dのゲートGとソースSとの間の電圧 $V_{gs}$ がドライブトランジスタTr dの閾電圧 $V_{th}$ より大きくなるように、初期化される。タイミングT 1からタイミングT 3までの期間T 1 ~ T 3は、ドライブトランジスタTr dのゲートG / ソースS間電圧 $V_{gs}$ を予め $V_{th}$ 以上に設定する準備期間である。10

#### 【0071】

この後、タイミングT 3になると、給電線V Lが低電位 $V_{ss2}$ から高電位 $V_{cc}$ に遷移し、ドライブトランジスタTr dのソースSの電位が上昇を開始する。やがて、ドライブトランジスタTr dのゲートG / ソースS間電圧 $V_{gs}$ が閾電圧 $V_{th}$ となった所で、電流がカットオフする。この様にして、ドライブトランジスタTr dの閾電圧 $V_{th}$ に相当する電圧が保持容量Csに書き込まれる。これが閾電圧補正動作である。この時、電流がもっぱら保持容量Cs側に流れ、発光素子ELには流れないようにするために、発光素子ELがカットオフとなるようにカソード電位 $V_{cath}$ を設定しておく。20

#### 【0072】

タイミングT 4では、走査線WSがハイレベルからローレベルに戻る。換言すると、走査線WSに印加されたパルスP 1が解除され、サンプリングトランジスタはオフ状態になる。以上の説明から明らかなように、パルスP 1は閾電圧補正動作を行うために、サンプリングトランジスタTr 1のゲートに印加される。

#### 【0073】

この後、信号線SLが基準電位 $V_{ss1}$ から信号電位 $V_{sig}$ に切り換わる。続いて、タイミングT 5で、走査線WSが再びローレベルからハイレベルに立上る。換言すると、パルスP 2がサンプリングトランジスタTr 1のゲートに印加される。これにより、サンプリングトランジスタTr 1は再びオンし、信号線SLから信号電位 $V_{sig}$ をサンプリングする。よって、ドライブトランジスタTr dのゲートGの電位は信号電位 $V_{sig}$ になる。ここで、発光素子ELは始めカットオフ状態(ハイインピーダンス状態)にあるため、ドライブトランジスタTr dのドレインとソースの間に流れる電流は専ら保持容量Csと発光素子ELの等価容量に流れ込み、充電を開始する。この後、サンプリングトランジスタTr 1がオフするタイミングT 6までに、ドライブトランジスタTr dのソースSの電位はVだけ上昇する。この様にして、映像信号の信号電位 $V_{sig}$ が $V_{th}$ に足し込まれる形で保持容量Csに書き込まれる共に、移動度補正用の電圧Vが保持容量Csに保持された電圧から差し引かれる。よって、タイミングT 5からタイミングT 6まで期間T 5 ~ T 6が信号書込期間及び移動度補正期間となる。換言すると、走査線WSにパルスP 2が印加されると、信号書込動作及び移動度補正動作が行われる。信号書込期間及び移動度補正期間T 5 ~ T 6は、パルスP 2のパルス幅に等しい。即ち、パルスP 2のパルス幅が移動度補正期間を規定している。30

#### 【0074】

この様に、信号書込期間T 5 ~ T 6では、信号電位 $V_{sig}$ の書き込みと補正量Vの調整が同時に行われる。 $V_{sig}$ が高いほど、ドライブトランジスタTr dが供給する電流I<sub>d</sub>は大きくなり、Vの絶対値も大きくなる。従って、発光輝度レベルに応じた移動度補正が行われる。 $V_{sig}$ を一定とした場合、ドライブトランジスタTr dの移動度μが大きいほど、Vの絶対値が大きくなる。換言すると、移動度μが大きいほど、保持容量Csに対する負帰還量Vが大きくなるので、画素毎の移動度μのばらつきを取り除くことが40

できる。

#### 【0075】

最後にタイミング T 6 になると、前述したように、走査線 W S が低レベル側に遷移し、サンプリングトランジスタ T r 1 はオフ状態となる。これにより、ドライブトランジスタ T r d のゲート G は信号線 S L から切り離される。同時に、ドレイン電流  $I_{ds}$  が発光素子 E L を流れ始める。これにより、発光素子 E L のアノード電位は駆動電流  $I_{ds}$  に応じて上昇する。発光素子 E L のアノード電位の上昇は、即ち、ドライブトランジスタ T r d のソース S の電位上昇に他ならない。ドライブトランジスタ T r d のソース S の電位が上昇すると、保持容量 C s のブートストラップ動作によりドライブトランジスタ T r d のゲート G の電位も連動して上昇する。ゲート電位の上昇量はソース電位の上昇量に等しくなる。ゆえに、発光期間中、ドライブトランジスタ T r d のゲート G / ソース S 間電圧  $V_{gs}$  は一定に保持される。この  $V_{gs}$  の値は、信号電位  $V_{sig}$  に閾電圧  $V_{th}$  及び移動量  $\mu$  の補正をかけたものとなっている。ドライブトランジスタ T r d は、飽和領域で動作する。即ち、ドライブトランジスタ T r d は、ゲート G / ソース S 間電圧  $V_{gs}$  に応じた駆動電流  $I_{ds}$  を供給する。この  $V_{gs}$  の値は、信号電位  $V_{sig}$  に閾電圧  $V_{th}$  及び移動量  $\mu$  の補正をかけたものとなっている。10

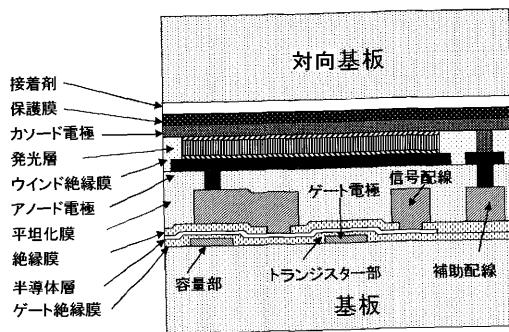

#### 【0076】

本発明にかかる表示装置は、図 14 に示すような薄膜デバイス構成を有する。本図は、絶縁性の基板に形成された画素回路の模式的な断面構造を表している。図示するように、画素回路は、複数の薄膜トランジスタを含むトランジスター部（図では 1 個の TFT を例示）、保持容量などの容量部及び有機 E L 素子などの発光部を含む。基板の上に TFT プロセスでトランジスター部や容量部が形成され、その上有機 E L 素子などの発光部が積層されている。その上に接着剤を介して透明な対向基板を貼り付けてフラットパネルとしている。20

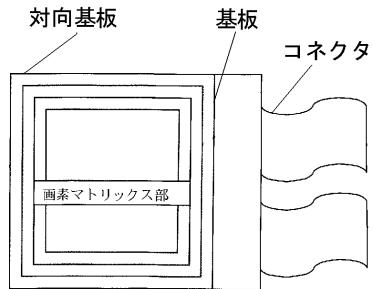

#### 【0077】

本発明にかかる表示装置は、図 15 に示すようにフラット型のモジュール形状のものを含む。例えば絶縁性の基板上に、有機 E L 素子、薄膜トランジスタ、薄膜容量等から成る画素回路をマトリックス状に集積形成した画素アレイ部を設ける。この画素アレイ部（画素マトリックス部）を囲むように接着剤を配し、ガラス等の対向基板を貼り付けて表示モジュールとする。この透明な対向基板には、必要に応じて、カラーフィルタ、保護膜、遮光膜等を設けてもよい。表示モジュールには、外部から画素アレイ部への信号等を入出力するためのコネクタとして、例えは FPC（フレキシブルプリントサーキット）を設けてもよい。30

#### 【0078】

以上に説明した本発明における表示装置は、フラットパネル形状を有し、様々な電子機器、例えば、デジタルカメラ、ノート型パソコンコンピューター、携帯電話、ビデオカメラなど、電子機器に入力された、若しくは、電子機器内で生成した映像信号を画像若しくは映像として表示するあらゆる分野の電子機器のディスプレイに適用することが可能である。以下、この様な表示装置が適用された電子機器の例を示す。

#### 【0079】

図 16 は本発明が適用されたテレビジョンセットであり、フロントパネル 12、フィルターガラス 13 等から構成される映像表示画面 11 を含み、本発明の表示装置をその映像表示画面 11 に用いることにより作製される。40

#### 【0080】

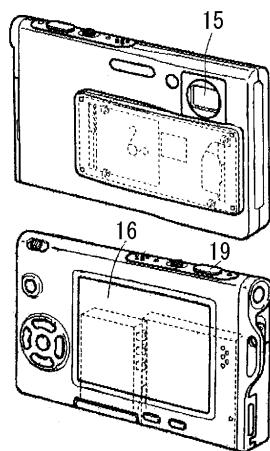

図 17 は本発明が適用されたデジタルカメラであり、上が正面図で下が背面図である。このデジタルカメラは、撮像レンズ、フラッシュ用の発光部 15、表示部 16、コントロールスイッチ、メニュー・スイッチ、シャッター 19 等を含み、本発明の表示装置をその表示部 16 に用いることにより作製される。

#### 【0081】

図 18 は本発明が適用されたノート型パソコンコンピューターであり、本体 20 には50

文字等を入力するとき操作されるキー<sup>21</sup>を含み、本体カバーには画像を表示する表示部<sup>22</sup>を含み、本発明の表示装置をその表示部<sup>22</sup>に用いることにより作製される。

#### 【0082】

図<sup>19</sup>は本発明が適用された携帯端末装置であり、左が開いた状態を表し、右が閉じた状態を表している。この携帯端末装置は、上側筐体<sup>23</sup>、下側筐体<sup>24</sup>、連結部（ここではヒンジ部）<sup>25</sup>、ディスプレイ<sup>26</sup>、サブディスプレイ<sup>27</sup>、ピクチャーライト<sup>28</sup>、カメラ<sup>29</sup>等を含み、本発明の表示装置をそのディスプレイ<sup>26</sup>やサブディスプレイ<sup>27</sup>に用いることにより作製される。

#### 【0083】

図<sup>20</sup>は本発明が適用されたビデオカメラであり、本体部<sup>30</sup>、前方を向いた側面に被写体撮影用のレンズ<sup>34</sup>、撮影時のスタート/ストップスイッチ<sup>35</sup>、モニター<sup>36</sup>等を含み、本発明の表示装置をそのモニター<sup>36</sup>に用いることにより作製される。

10

#### 【図面の簡単な説明】

#### 【0084】

【図1】参考例にかかる表示装置の全体構成を示すブロック図である。

【図2】図1に示した参考例にかかる表示装置に組み込まれる画素回路の構成例を示す回路図である。

【図3】図2に示した画素回路の動作説明に供する回路図である。

【図4】参考例にかかる表示装置の動作説明に供するタイミングチャートである。

【図5】本発明にかかる表示装置の第1実施形態を示す全体ブロック図である。

20

【図6】図5に示した第1実施形態に組み込まれる画素回路の構成を示す回路図である。

【図7】第1実施形態にかかる表示装置の動作説明に供するタイミングチャートである。

【図8】本発明にかかる表示装置の第2実施形態を示す全体構成図である。

【図9】第2実施形態に組み込まれる画素回路の構成を示す回路図である。

【図10】第2実施形態の動作説明に供するタイミングチャートである。

【図11】本発明にかかる表示装置の第3実施形態を示す全体構成図である。

【図12】図11に示した第3実施形態に組み込まれる画素回路の構成を示す回路図である。

【図13】第3実施形態の動作説明に供するタイミングチャートである。

【図14】本発明にかかる表示装置のデバイス構成を示す断面図である。

30

【図15】本発明にかかる表示装置のモジュール構成を示す平面図である。

【図16】本発明にかかる表示装置を備えたテレビジョンセットを示す斜視図である。

【図17】本発明にかかる表示装置を備えたデジタルスチルカメラを示す斜視図である。

【図18】本発明にかかる表示装置を備えたノート型パーソナルコンピューターを示す斜視図である。

【図19】本発明にかかる表示装置を備えた携帯端末装置を示す模式図である。

【図20】本発明にかかる表示装置を備えたビデオカメラを示す斜視図である。

#### 【符号の説明】

#### 【0085】

1・・・画素アレイ部、2・・・画素回路、3・・・水平セレクタ（信号セレクタ）、4

・・・ライトスキャナ、5・・・ドライブスキャナ、6・・・電源スキャナ、7・・・補正用スキャナ、71・・・第一補正用スキャナ、72・・・第二補正用スキャナ、Tr1

・・・サンプリングトランジスタ、Tr2・・・スイッチングトランジスタ、Tr3

・・・スイッチングトランジスタ、Tr4・・・スイッチングトランジスタ、Trd・・・ドライブトランジスタ、Cs・・・保持容量、EL・・・発光素子

40

【図1】

【図2】

【図3】

【図4】

【 四 5 】

【 图 6 】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図20】

【図19】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 6 1 2 L

G 09 G 3/20 6 1 1 Z

H 05 B 33/14 A

審査官 小川 浩史

(56)参考文献 特開2006-215213(JP, A)

特開2001-060076(JP, A)

特開2003-271095(JP, A)

特開2004-070293(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 2 0 , 3 / 3 0 - 3 / 3 2

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其驱动方法和电子设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP4470960B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2010-06-02 |

| 申请号            | JP2007133862                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2007-05-21 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 山下淳一<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 山下 淳一<br>内野 勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| CPC分类号         | H01L27/1255 G09G3/3233 G09G2300/0417 G09G2300/0819 G09G2310/0251 G09G2310/0262<br>G09G2320/0285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.H G09G3/20.642.A G09G3/20.624.B G09G3/20.623.A G09G3/20.612.L<br>G09G3/20.611.Z H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/CC43 3K107/EE03 3K107/HH00 3K107/HH04 3K107/<br>/HH05 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD22 5C080/FF11 5C080/JJ02 5C080/JJ03<br>5C080/JJ04 5C080/JJ06 5C080/KK02 5C080/KK07 5C080/KK43 5C380/AA01 5C380/AB06 5C380<br>/AB11 5C380/AB18 5C380/AB23 5C380/AB24 5C380/AB34 5C380/AB46 5C380/AC07 5C380/AC08<br>5C380/AC09 5C380/AC11 5C380/BA11 5C380/BA13 5C380/BA17 5C380/BA38 5C380/BA39 5C380<br>/BB02 5C380/BD05 5C380/CA08 5C380/CA12 5C380/CA53 5C380/CA54 5C380/CB01 5C380/CB16<br>5C380/CB20 5C380/CB26 5C380/CB31 5C380/CC02 5C380/CC05 5C380/CC06 5C380/CC07 5C380<br>/CC27 5C380/CC30 5C380/CC33 5C380/CC41 5C380/CC61 5C380/CC62 5C380/CC63 5C380/CC64<br>5C380/CC65 5C380/CD012 5C380/CD014 5C380/CD015 5C380/CD023 5C380/CD025 5C380/CE04<br>5C380/DA02 5C380/DA06 5C380/DA47 |         |            |

| 代理人(译)         | 山本隆久<br>吉井正明<br>森浩一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 审查员(译)         | 小川博                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 其他公开文献         | JP2008287139A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

**摘要(译)**

要解决的问题：通过减少外围驱动部分中包含的扫描仪的数量来减小面板框架部分的面积。像素2被操作分成发光期间和在每个字段中的非发光期间，和驱动晶体管Trd的所述非发光时段中的阈值电压校正操作，写入操作和视频信号的驱动器连接到保持电容Cs执行晶体管Trd的迁移率校正操作。除了视频信号之外，信号选择器3还向每条信号线SL提供用于关闭每个发光元件EL的预定电位。除了用于将视频信号从信号线SL取入像素的控制信号之外，写入扫描器4还将用于从信号线SL捕获预定电位的控制信号提供给每个像素到扫描线WS。采样晶体管Tr1从信号线SL施加到驱动晶体管Trd的栅极截取的预定电位，从断开切换到非发光时段来发光期间的发光元件EL。点域6

図 4

11 19734 15677