(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-352411

(P2005-352411A)

(43) 公開日 平成17年12月22日(2005.12.22)

(51) Int.Cl.<sup>7</sup>**G09G 3/30****G09G 3/20****H05B 33/14**

F 1

G09G 3/30

J

テーマコード(参考)

3K007

G09G 3/20

611H

5C080

G09G 3/20

621F

G09G 3/20

623R

G09G 3/20

624B

審査請求 未請求 請求項の数 5 O L (全 14 頁) 最終頁に続く

(21) 出願番号

特願2004-175882(P2004-175882)

(22) 出願日

平成16年6月14日(2004.6.14)

(71) 出願人 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100080034

弁理士 原 謙三

(74) 代理人 100113701

弁理士 木島 隆一

(74) 代理人 100116241

弁理士 金子 一郎

(72) 発明者 大場 敏弘

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

(72) 発明者 入江 一視

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

最終頁に続く

(54) 【発明の名称】電流駆動型表示素子の駆動回路およびそれを備えた表示装置

## (57) 【要約】

**【課題】** 画素内のコンデンサ数を削減し、画素の構成簡素化による高開口率の実現、これにより可能となる低電流駆動による長寿命化、或は高輝度化を図る。

**【解決手段】** トランジスタT4をOFFして、有機EL素子OLEDへ流入する電流を停止する。次に、トランジスタT1, T2, T5, T7をONし、閾値電圧Vpreをデータ線S<sub>i</sub>に印加することでトランジスタT3がONする。また、トランジスタT7をOFFして、トランジスタT3, T1, T2を介してコンデンサCsを放電すると、トランジスタT3がOFFする。そして、トランジスタT2のON状態を保ち、トランジスタT1, T5をOFFとして、トランジスタT6をONする。最後に、トランジスタT2, T6をOFFした後、トランジスタT4をONすることにより、トランジスタT3, T4を介して有機EL素子OLEDにデータ電圧Vdataで決められた駆動電流が流れる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

電流駆動型の表示素子を含むマトリックス状に配置された複数の画素と、該画素を選択する選択信号を供給する選択線と、選択された画素にデータを供給するデータ線とを備えた表示装置に設けられ、前記表示素子を駆動する電流駆動型表示素子の駆動回路において、

各画素は、

所望する電流を制御する第1のトランジスタと、

前記第1のトランジスタおよび前記表示素子と直列に接続され、前記表示素子への電流の供給または供給停止をする第2のトランジスタと、

前記第1のトランジスタの制御端子と入力端子との間に接続される第1のコンデンサと、

前記第1のトランジスタの制御端子と前記データ線との間を接続または遮断する第3のトランジスタと、

前記第1のトランジスタの出力端子と前記データ線との間を接続または遮断する第4のトランジスタとを有し、

前記駆動回路は、

前記第2のトランジスタがOFFしている期間に、前記第1のトランジスタがONするように前記第1のトランジスタの閾値電位を補正するための閾値補正電圧を前記データ線に印加すると共に前記第3のトランジスタと前記第4のトランジスタとをONした後、前記第1トランジスタの制御端子の電位が閾値電位に達するまで前記第1のコンデンサの蓄積電荷を放電させて、前記第1のトランジスタをOFFさせるように、前記閾値補正電圧の印加を停止し、発光・非発光を決定するデータ電圧を前記データ線に印加し前記第4のトランジスタをOFFすると共に前記第2のトランジスタをONする制御回路を備えていることを特徴とする電流駆動型表示素子の駆動回路。

**【請求項 2】**

前記画素の外部に設けられており、前記データ線に直列に接続される第2のコンデンサと、

前記第2のコンデンサの前記データ線側の一端子に前記閾値補正電圧を印加または印加停止する第1のスイッチと、

前記第2のコンデンサの他端子に一定電圧を印加または印加停止する第2のスイッチと、

前記第2のコンデンサの他端子に前記データ電圧を印加または印加停止する第3のスイッチとを有していることを特徴とする請求項1に記載の電流駆動型表示素子の駆動回路。

**【請求項 3】**

前記制御回路は、前記閾値補正電圧の印加停止後に前記データ線の浮遊容量を充電する充電電圧を印加し、前記浮遊容量の充電後に前記充電電圧の印加を停止することを特徴とする請求項1または2に記載の電流駆動型表示素子の駆動回路。

**【請求項 4】**

前記第2のコンデンサの他端子に前記充電電圧を印加または印加停止する第4のスイッチを有していることを特徴とする請求項3に記載の電流駆動型表示素子の駆動回路。

**【請求項 5】**

請求項1ないし4のいずれか1項に記載の駆動回路を備えていることを特徴とする表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、有機EL(Electro Luminescence)、FED(Field Emission Display)等の電流駆動型素子を駆動する駆動回路に関するものである。

**【背景技術】**

10

20

30

30

40

50

## 【0002】

電流駆動型表示素子である有機ELディスプレイ装置は、輝度が電流値に依存し、高輝度表示のために高電流で駆動すると寿命が短くなるという特性を有しており、このような特性はよく知られている。この有機ELディスプレイの大画面化や高精細化を図るためにアクティブマトリックス(AM)駆動が開発されている。従来のパッシブマトリックス駆動は、走査線数の増加により、高輝度化が難しいことや、電流値を増大させると寿命の低下をもたらすことなどの課題を有するために、大画面化や高精細化用途での実用には不向きである。

## 【0003】

ところで、AM駆動法では薄膜トランジスタ(TFT)の特性バラツキによる電流不均一性や閾値不均一性による表示輝度の不均一性が大きな課題である。更に別の課題として、有機ELの経時変化による輝度低下や、有機EL自身の発光(発熱)による輝度変化(温度が上昇すると輝度が上昇する)など不都合な特性を補償する機能が求められることが挙げられる。

## 【0004】

このような課題を解決するため、従来、様々な駆動回路方式が提案されている。そのような駆動回路方式としては、例えば、特許文献1に開示されている電圧プログラム方式や特許文献2に開示されている電流プログラム方式が挙げられる。

## 【0005】

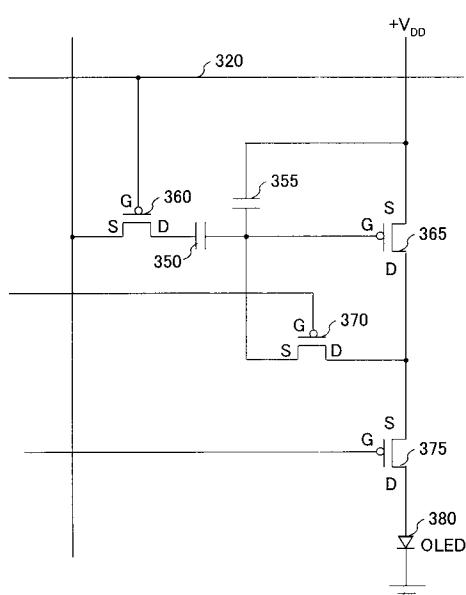

図7は、上記の電圧プログラム方式で駆動される画素回路の構成を示す回路図である。この図に示すように、画素回路は、有機EL素子であるOLED380と、TFTである4つのトランジスタ360, 365, 370, 375と、2つのコンデンサ350, 355とを備えている。

## 【0006】

この画素回路の駆動においては、まず、トランジスタ365がONする電圧をゲートに印加し、トランジスタ365, 370およびコンデンサ355において放電閉回路を形成する事により、ソース-ゲート間電圧をトランジスタ365の閾値電圧に自動的にセットする。次に、データ電圧をトランジスタ365のゲートに入力させ、その後にトランジスタ375をオンすると、トランジスタ365からOLED380にトランジスタ365の閾値電圧に依存しない電流が供給される。これにより、上記のAM駆動法の課題を克服できる。また、この電圧プログラム回路の利点は、データが電圧でトランジスタ365に書き込まれるため、データ線310の寄生容量に殆ど関係なく高速にデータ書き込みを行うことができる。このような駆動方法が走査線302の増加や大画面化を図る上で有利であることも知られている。

## 【0007】

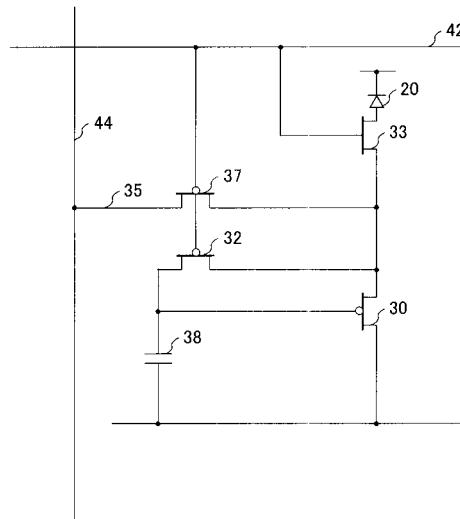

図8は、上記の電流プログラム方式で駆動される画素回路の構成を示す回路図である。この図に示すように、画素回路は、有機EL素子20と、TFTである4つのトランジスタ30, 32, 33, 37と、1つのコンデンサ38とを備えている。

## 【0008】

この画素回路の駆動において、具体的には、ゲート線42をLOWとして、トランジスタ33をオフに、トランジスタ32, 37をオンにすると、コンデンサ38、トランジスタ32, 37を介してデータ線44に流れた電流に従って決まるトランジスタ30のゲート-ソース電圧がコンデンサ38に蓄積される。コンデンサ38の両端電圧によりトランジスタ30がオン状態になり、トランジスタ30, 37を介した電流も定電流源であるデータ線44に流れ始める。やがて、トランジスタ30を介した電流のみがデータ線44に流れることになり、コンデンサ38にはトランジスタ30が所望の電流値を流す電圧が書き込まれた(プログラムされた)事になる。そして、トランジスタ33をオンすることにより、有機EL素子20をトランジスタ30に接続すると、トランジスタ30が電流源として動作して、データ線入力電流にほぼ等しい電流が表示素子20を通って駆動される。

## 【0009】

10

20

30

40

50

この回路の駆動電流は、データ線入力電流値にのみ依存し、トランジスタの閾値電圧のみならず、移動度、トランジスタのチャンネル幅、チャンネル長さ、および入力容量のバラツキに依存しない。このため、データ入力信号に応じて電圧プログラム回路と比べて正確に制御された駆動電流が有機EL素子20に供給され、輝度の経時変化や温度による変化を克服できる。

【特許文献1】特表2002-514320号公報(2002年5月14日公表)

【特許文献2】特表2003-529805号公報(2003年10月7日公表)

#### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0010】

しかし、上記の電流プログラム回路は、データが定電流で書き込まれることから、アナログ階調駆動、特に低電流(低輝度)領域ではデータ線が有する寄生容量への充電時間が長くなるために書き込み速度が遅くなるなどの不都合により、走査線の増加、大画面化に不利である事が知られている。また、上記の電流プログラム回路における時間分割デジタル階調駆動では、高電流(高輝度)領域で書き込みが行われるが、階調数に応じて1フレーム内での書き込み回数が多くなるなどの不都合から、走査線の増加、大画面化のみならず多階調表示に不利である事も知られている。

##### 【0011】

本発明は、上記の問題点に鑑みてなされたものであり、その目的は、画素回路内のコンデンサー数を削減し、画素回路の構成簡素化による高開口率の実現、これにより可能となる定電流駆動による長寿命化、或は商品性を高める高輝度化を実現できる画素回路構成とその駆動回路を提供することである。

##### 【課題を解決するための手段】

##### 【0012】

本発明に係る電流駆動型表示素子の駆動回路は、電流駆動型の表示素子を含むマトリックス状に配置された複数の画素と、該画素を選択する選択信号を供給する選択線と、選択された画素にデータを供給するデータ線とを備えた表示装置に設けられ、前記表示素子を駆動する電流駆動型表示素子の駆動回路において、上記課題を解決するために、各画素が、所望する電流を制御する第1のトランジスタと、前記第1のトランジスタおよび前記表示素子と直列に接続され、前記表示素子への電流の供給または供給停止をする第2のトランジスタと、前記第1のトランジスタの制御端子と入力端子との間に接続される第1のコンデンサと、前記第1のトランジスタの制御端子と前記データ線との間を接続または遮断する第3のトランジスタと、前記第1のトランジスタの出力端子と前記データ線との間を接続または遮断する第4のトランジスタとを有し、前記駆動回路が、前記第2のトランジスタがOFFしている期間に、前記第1のトランジスタがONするように前記第1のトランジスタの閾値電位を補正するための閾値補正電圧を前記データ線に印加すると共に前記第3のトランジスタと前記第4のトランジスタとをONした後、前記第1トランジスタの制御端子の電位が閾値電位に達するまで前記第1のコンデンサを放電させて、前記第1のトランジスタをOFFさせるように、前記閾値補正電圧の印加を停止し、発光・非発光を決定するデータ電圧を前記データ線に印加し、前記第4のトランジスタをOFFすると共に前記第2のトランジスタをONする制御回路を備えていることを特徴としている。

##### 【0013】

上記の構成では、制御回路によって、表示素子へ供給する電流が設定される。まず、第2のトランジスタをOFFしておき、表示素子への電流の流入を停止する。この状態で、閾値補正電圧をデータ線に印加することにより、閾値補正電圧印加期間前の第1のトランジスタのゲート電位に関わらず、第1のトランジスタのゲート電位を閾値電圧以下の電位にし、第1のトランジスタがON状態になる。このとき、第1のコンデンサは、第3のトランジスタからデータ線に流れる電流により充電されている。

##### 【0014】

次に、前記のように閾値補正電圧の印加を停止することにより、第1のトランジスタの

10

20

30

40

50

制御端子の電位が閾値電位に達するまで第1のコンデンサを放電するので、第1のトランジスタは自動的にOFF状態になる。そして、発光・非発光を決定するデータ電圧をデータ線に印加することにより、発光に応じたデータ電圧または非発光に応じたデータ電圧の大きさに応じて、第3のトランジスタからデータ線に電流が流れ込むことにより、第1のコンデンサには、第3のトランジスタの閾値電圧依存しない電流を第3のトランジスタが流す電圧が書き込まれる（充電される）。

#### 【0015】

さらに、第3のトランジスタをOFFさせ、発光・非発光を決定するデータ電圧の印加を停止させると共に、第2のトランジスタをONすることにより、第1のコンデンサから第1および第2のトランジスタを介して表示素子に前記データ電圧で決められた電流が流れ、表示素子は発光・非発光を開始する。駆動回路が上記の駆動手順を繰り返すことにより、任意の画像の表示が行われる。10

#### 【0016】

このような駆動構成により、画素内には、第1のコンデンサのみが設けられることになり、従来例では画素内に2個設けられていたコンデンサを1個に削減することができる。

#### 【0017】

前記の駆動回路は、より詳細には、前記画素の外部に設けられており、前記データ線に直列に接続される第2のコンデンサと、この第2のコンデンサの前記データ線側の一端子に前記閾値補正電圧を印加または印加停止する第1のスイッチと、前記第2のコンデンサの他端子に一定電圧を印加または印加停止する第2のスイッチと、前記第2のコンデンサの他端子に前記データ電圧を印加または印加停止する第3のスイッチとを有していることが好ましい。20

#### 【0018】

前記のように削減された1個のコンデンサは機能的には必要であり、前記の第1ないし第3のスイッチを用いて各電圧をデータ線に印加する構成を採用することにより、第2のコンデンサとして、画素外にデータ線毎に1個のみ設けられ、データ線に沿った多数の画素へのデータ書き込み時に使用される。具体的には、第2のコンデンサは、第1のコンデンサとの容量配分により第3のトランジスタの制御端子（ゲート）の電位を決定するために用いられる（後述の（7）式参照）。

#### 【0019】

また、前記の駆動回路において、前記制御回路は、前記閾値補正電圧の印加停止後に前記データ線の浮遊容量を充電する充電電圧を印加し、前記浮遊容量の充電後に前記充電電圧の印加を停止することが好ましい。このため、駆動回路は、前記第2のコンデンサの他端子に前記充電電圧を印加または印加停止する第4のスイッチを有する。30

#### 【0020】

上記の構成では、制御回路が、例えば第4のスイッチを制御することによって充電電圧を印加して浮遊容量の充電を行った後に充電電圧の印加を停止する。これにより、データ線に大きい寄生容量を持つ場合においても、この浮遊容量を素早く充放電することにより、第3のトランジスタの制御端子の電位がより速く閾値電位に達するので、高速駆動を実現することができる。40

#### 【0021】

本発明の表示装置は、前記のいずれかの構成の駆動回路を備えることにより、各駆動回路の前記の技術的優位性を有するようになる。

#### 【発明の効果】

#### 【0022】

本発明に係る表示装置の駆動回路は、前記制御回路を備えることによって、前記閾値補正電圧を前記データ線へ印加して第1のトランジスタをONさせた後、閾値補正電圧の印加を停止して第1のトランジスタをOFFさせ、さらに前記データ電圧を前記データ線に印加して、第1のコンデンサに第2のトランジスタに流す電流を第1のコンデンサに書き込む。この構成により、画素内のコンデンサが第1のコンデンサ1つになる。それゆえ、50

例えば 120 ppi 程度の解像度の表示装置の各画素の開口率はコンデンサ 1 個の減少に応じて約 10 % 程度改善でき、表示装置の高輝度化に寄与できる。また、前述の特許文献 2 の従来例と比べ、アナログ階調駆動時では、走査線の多い大画面化ディスプレイを実現することができ、時分割デジタル階調駆動では、走査線の増加や大画面化のみならず多階調表示を可能とする新規駆動回路を提供できる。

**【発明を実施するための最良の形態】**

**【0023】**

本発明の一実施形態について図 1ないし図 6 に基づいて説明すると以下の通りである。

**【0024】**

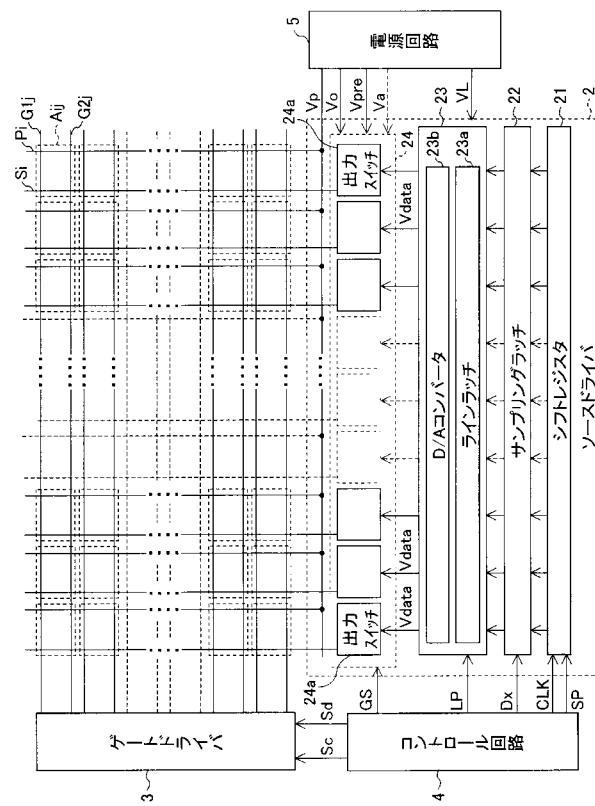

図 2 は、本実施形態の有機 EL ディスプレイ装置 1 の全体回路構成のブロックを示す。 10

**【0025】**

有機 EL ディスプレイ装置 1 は、図 2 に示すように、複数の画素  $A_{i,j}$  ( $i = 1 \sim m$ ,  $j = 1 \sim n$ ) と、ソースドライバ 2 と、ゲートドライバ 3 と、コントロール回路 4 と、電源回路 5 とを備えている。

**【0026】**

有機 EL ディスプレイ装置 1 には、複数の互いに平行に配されたデータ線  $S_i$  と、これらに直交する複数の互いに平行に配された走査線  $G_{1,j}$ ,  $G_{2,i}$  とが設けられ、それぞれの交点に画素  $A_{i,j}$  がマトリクス状に配置されている。データ線  $S_i$  はソースドライバ 2 に接続され、走査線  $G_{1,j}$ ,  $G_{2,j}$  はゲートドライバ 3 に接続されている。また、電源線  $P_i$  は、データ線  $S_i$  と同数だけデータ線  $S_i$  と平行に設けられており、電源電圧  $V_p$  を各画素  $A_{i,j}$  に印加する。 20

**【0027】**

両ドライバ 2, 3 は、表示装置全体の小型化および作製コストの低減を図るため、画素  $A_{i,j}$  が形成されている有機 EL ディスプレイ装置 1 と同じ基板上に、全部もしくは一部形成されることが好ましい。ただし、上記の効果は得られないが、両ドライバ 2, 3 の一部または全部を有機 EL ディスプレイ装置 1 と別の基板に IC として形成し、有機 EL ディスプレイ装置 1 と外部接続しても構わない。例えば、ガラス基板に IC を直接接合させる COG (Chip On Glass) でも構わない。また、フレキシブル基板上に IC を配置し、有機 EL ディスプレイ装置 1 の基板上の入出力端子に接合させることもできる。

**【0028】**

ソースドライバ 2 は、シフトレジスタ 21、サンプリングラッチ 22、出力ラッチ部 23 および出力スイッチ部 24 を有している。出力ラッチ部 23 は、ラインラッチ 23a と D/A コンバータ 23b とを有している。また、出力スイッチ部 24 は、各データ線  $S_i$  に 1 つずつ設けられる出力スイッチ 24a を有している。出力スイッチ 24a は、電源回路 5 からの後述する各電圧  $V_0$ ,  $V_{pre}$ ,  $V_a$  や D/A コンバータ 23b からの表示データ電圧  $V_{data}$  をデータ線  $S_i$  に印加するための複数のトランジスタ (図 1 のトランジスタ T5 ~ T7 または図 5 のトランジスタ T5 ~ T8) を有しており、これらのトランジスタの ON/OFF がコントロール回路 4 からのゲート信号 GS によって個々に制御される。 30

**【0029】**

このソースドライバ 2 において、シフトレジスタ 21 は、コントロール回路 4 より入力されるスタートパルス SP をクロック CLK に同期して転送し、各出力段からタイミング信号として出力する。サンプリングラッチ 22 は、複数のフリップフロップから構成されており、シフトレジスタ 21 からの対応するタイミング信号により、入力される複数ビットの画像データ信号  $D_x$  を個々のフリップフロップに保持する。ラインラッチ 23a は、サンプリングラッチ 22 に保持された 1 ライン分の画像データ信号  $D_x$  をラッチパルス LP により保持する。D/A コンバータ 23b は、ラインラッチ 23a で保持された画像信号データ  $D_x$  をアナログの表示データ電圧  $V_{data}$  に変換し、出力スイッチ 24 を介して各データ線  $S_i$  に印加する。 40

**【0030】**

コントロール回路 4 (制御回路) は、前記のスタートパルス SP、クロック CLK、画 50

像データ信号 D<sub>x</sub>、ラッチパルス L<sub>P</sub>およびゲート信号 G<sub>S</sub>（図 1 のトランジスタ T<sub>5</sub> ~ T<sub>7</sub> または図 5 のトランジスタ T<sub>5</sub> ~ T<sub>8</sub> のゲート信号）を出力する回路である。また、コントロール回路 4 は、スキャンデータ S<sub>d</sub> およびスキャンクロック S<sub>c</sub> を出力する。ゲートドライバ 3 は、シフトレジスタを含んでおり、シフトレジスタによって上記のスキャンデータ S<sub>d</sub> をスキャンクロック S<sub>d</sub> に同期して転送し、各出力段から走査線 G<sub>1j</sub>, G<sub>2j</sub> にそれぞれ異なる走査信号（図 4 の T<sub>1</sub> ゲート信号と T<sub>2</sub> ゲート信号）を出力する。これにより、各水平走査期間には、1 組の走査線 G<sub>1j</sub>, G<sub>2j</sub> が書き込み可能となるよう選択される。

## 【0031】

電源回路 5 は、電源線 P<sub>i</sub> に印加するための電源電圧 V<sub>p</sub>、後述する電圧 V<sub>0</sub>, V<sub>a</sub> および閾値補正電圧 V<sub>pre</sub> を出力する回路である。また、電源回路 5 は、ソースドライバ 2 に与える電源電圧 V<sub>L</sub> を出力する。10

## 【0032】

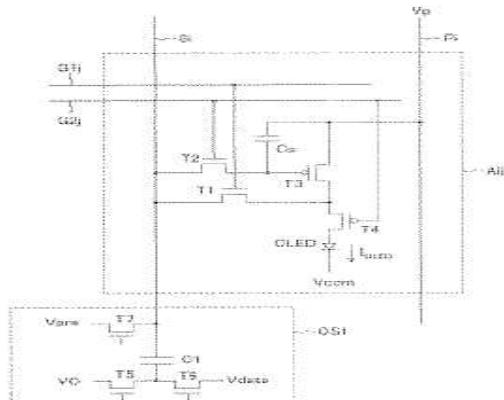

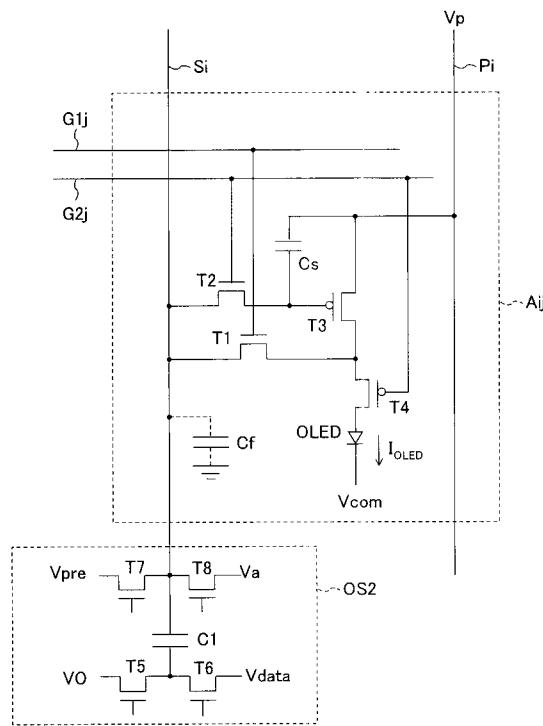

図 1 は、本実施形態の画素 A<sub>ij</sub> および出力スイッチ 24 の構成を示す回路図である。

## 【0033】

図 1 に示すように、画素 A<sub>ij</sub> は、有機 E L 素子 O L E D、多結晶シリコンまたは C G シリコンを用いた TFT からなるトランジスタ T<sub>1</sub> ~ T<sub>4</sub> およびコンデンサ C<sub>s</sub> を有している。

## 【0034】

電気光学素子としての有機 E L 素子 O L E D は、データ線 S<sub>i</sub> と走査線 G<sub>1j</sub>, G<sub>2j</sub> との交点付近に配置されており、そのアノードに共通電圧 V<sub>com</sub> が印加されている。トランジスタ T<sub>1</sub> は、データ線 S<sub>i</sub> とトランジスタ T<sub>3</sub> の出力端子との間に配置され、そのゲート端子が走査線 G<sub>1j</sub> に接続されている。トランジスタ T<sub>2</sub> は、データ線 S<sub>i</sub> とコンデンサ C<sub>s</sub> との間に配置され、そのゲート端子が走査線 G<sub>2j</sub> に接続されている。20

## 【0035】

トランジスタ T<sub>3</sub> は、電源ライン P<sub>i</sub> と有機 E L 素子 O L E D のカソードとの間に、トランジスタ T<sub>4</sub> と直列に配置され、そのゲート端子がコンデンサ C<sub>s</sub> の一端とトランジスタ T<sub>2</sub> に接続されている。コンデンサ C<sub>s</sub> の他端は、トランジスタ T<sub>3</sub> の入力端子および電源線 P<sub>i</sub> に接続されている。トランジスタ T<sub>4</sub> のゲート端子は、走査線 G<sub>2j</sub> に接続されている。30

## 【0036】

なお、画素 A<sub>ij</sub> のトランジスタ T<sub>1</sub>, T<sub>2</sub> とトランジスタ T<sub>3</sub>, T<sub>4</sub> とは、それぞれ図 1 においては n 型 TFT と p 型 TFT とであるが、適正な制御信号を供給できるのであればそれぞれ n 型 TFT と p 型 TFT とであってもよい。

## 【0037】

出力スイッチ 24 は、多結晶シリコンまたは C G シリコンを用いた TFT からなるトランジスタ T<sub>5</sub> ~ T<sub>7</sub> およびコンデンサ C<sub>1</sub> を有している。

## 【0038】

コンデンサ C<sub>1</sub> の一端は、データ線 S<sub>i</sub> とトランジスタ T<sub>7</sub> の出力端子に接続されている。トランジスタ T<sub>5</sub>, T<sub>6</sub> は、それぞれの出力端子で直列に接続され、その接続部にコンデンサ C<sub>1</sub> の他端が接続されている。トランジスタ T<sub>5</sub> ~ T<sub>7</sub> の入力端子には、それぞれ電圧 V<sub>0</sub>、データ電圧 V<sub>data</sub>、閾値補正電圧 V<sub>pre</sub> が入力される。40

## 【0039】

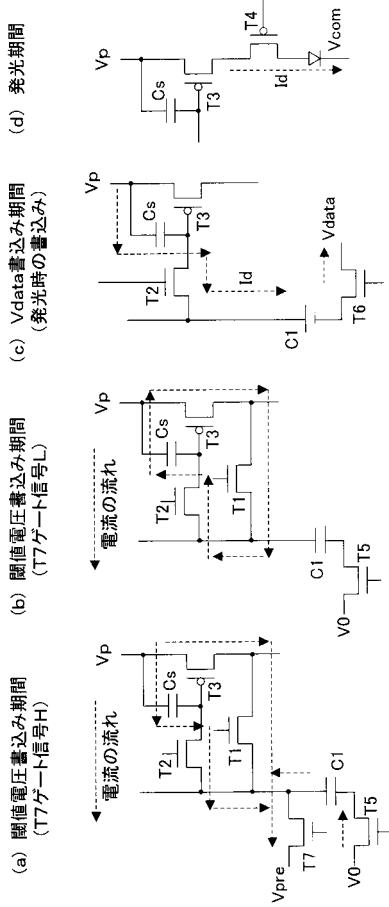

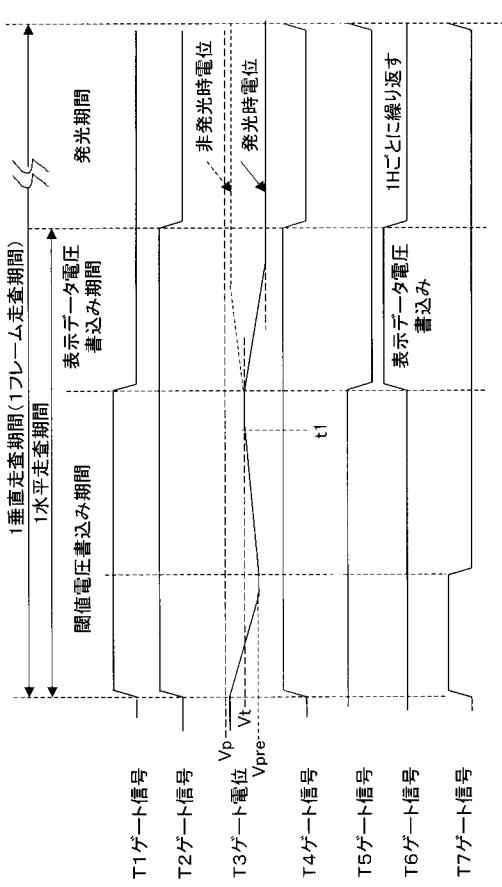

続いて、上記のように構成される有機 E L ディスプレイ装置 1 において、コントロール回路 4 の制御によって実行される電圧プログラム動作を説明する。図 3 (a) ないし (d) は、画素 A<sub>ij</sub> および出力スイッチ 24 の電圧プログラム動作における各部の電流の流れを示す図である。また、図 4 は、画素 A<sub>ij</sub> および出力スイッチ 24 の電圧プログラム動作を示すタイミングチャートである。

## 【0040】

電圧プログラム動作は、(1) 閾値電圧書き込み期間 (T<sub>7</sub> ゲート信号 H)、(2) 閾値電

圧書き込み期間（T7ゲート信号L）、（3）Vdata書き込み期間、および（4）発光期間の4つの駆動タイミング期間に分けられる。

#### 【0041】

##### 〔1〕閾値電圧書き込み期間（T7ゲート信号H）

この期間では、トランジスタT4をOFFしておき、閾値電圧書き込み期間およびデータ電圧書き込み期間に有機EL素子OLEDへ流入する電流を停止する。そして、図3(a)に示すように、トランジスタT1, T2, T5をONすると共に、トランジスタT7をONし、閾値補正電圧Vpreをデータ線Siに印加する。

#### 【0042】

ここで、電源電圧Vp=9V、共通電圧Vcom=0Vと設定し、閾値補正電圧Vpre=Vp-4V=5Vと設定する。この値は、トランジスタT3の閾値バラツキを考慮してONする値である。また、電圧V0=9Vに設定する。この値は電圧V0から表示データ電圧Vdataに切り変わるとき、すなわちトランジスタT3のゲート電位が閾値電位Vtから表示データ電圧Vdataの値により、ON或はOFFの状態にする必要があり、このため表示データ電圧Vdataとして、OFF時に9V、ON時に8.9~5Vの値が入力される。さらに、電圧VaはトランジスタT3のゲートに現れる閾値電位VtのTypical値程度に設定される。なお、上記の各電圧の値は一例であって、これらに限定されるものではない。

#### 【0043】

上記の動作により、閾値補正電圧印加期間前のトランジスタT3のゲート電位に関わらず、トランジスタT3を閾値電圧以下の電位にし、トランジスタT3をON状態にする。

#### 【0044】

〔1〕の期間において、トランジスタT3をONさせるために、閾値補正電圧Vpreは、トランジスタT3のゲートに現れる閾値電位Vtのバラツキを考慮した閾値電位Vtより低い電圧でよい。閾値電位Vtより低い電圧が印加され、トランジスタT2, T3, T1によりコンデンサCsに自動的に閾値電位Vtが蓄積され（逆に言えば閾値電位VtになるまでトランジスタT3はON状態を保つ）。

#### 【0045】

なお、図3(a)において、閾値電圧書き込み期間前の状態は非発光状態の場合の電流の流れを破線で示している。

#### 【0046】

##### 〔2〕閾値電圧書き込み期間（T7ゲート信号L）

トランジスタT7をOFFすると、コンデンサCs、トランジスタT3, T1, T2を介してコンデンサCsに蓄積された電荷が放出され、トランジスタT3のゲート電位が時刻t1で閾値電位Vtに達すると、トランジスタT3は自動的にOFF状態になる。このとき、データ線Siの電位はVtである。また、コンデンサC1の他端の電位はトランジスタT5がONであるため、任意で一定の電圧V0に保たれている。

#### 【0047】

したがって、このVt書き込み後、コンデンサQs, Q1に蓄積される電荷は次式で示される。

#### 【0048】

$$Q_s = C_s (V_p - V_t) \quad \dots (1)$$

$$Q_1 = C_1 (V_t - V_0) \quad \dots (2)$$

ここで、Vp, V0は、それぞれトランジスタT3, T5のソース電位である。

#### 【0049】

##### 〔3〕データ電圧書き込み期間

図3(c)に示すように、トランジスタT2はON状態を保ち、トランジスタT1, T5をOFFとし、トランジスタT6をONする。これにより、コンデンサC1の他端の電位を電圧V0から所望の表示情報である表示データ電圧Vdataに切り替える。

#### 【0050】

10

20

30

40

50

なお、図3(c)のデータ電圧書き込み期間は発光表示の電流の流れを破線で示す。非発光の場合は、トランジスタT3のゲート電位 $V_g$ が $V_g > V_t$ になる表示データ電圧 $V_{data}$ が印加され、電流の流れは逆方向になる。

#### 【0051】

データ電圧 $V_{data}$ (発光情報電圧)の書き込み完了時のコンデンサ $C_s$ ,  $C_1$ の蓄積電荷を次式に示す。

#### 【0052】

$$Q_s' = Q_s + Q_d \quad \dots (3)$$

$$= C_s (V_p - V_g) \quad \dots (4)$$

$$Q_1' = Q_1 + Q_d \quad \dots (5)$$

$$= C_1 (V_g - V_{data}) \quad \dots (6)$$

10

ここで、 $Q_d$ は、 $V_{data}$ の書き込み時にコンデンサ $C_s$ ,  $C_1$ に流れる電流の積分値を示す。コンデンサ $C_s$ ,  $C_1$ が直列に接続されていることから、コンデンサ $C_s$ ,  $C_1$ で増加する電荷量が同じであるため、その増加電荷量を $Q_d$ として電流の積分値を表現している。

#### 【0053】

(3)式 - (5)式 = (4)式 - (6)式により  $Q_d$ を消去し、次式を導出できる。

#### 【0054】

$$V_g = V_t + (V_{data} - V_0) C_1 / (C_s + C_1) \quad \dots (7)$$

このように、電圧 $V_0$ と表示データ電圧 $V_{data}$ との電圧差がコンデンサ $C_s$ とコンデンサ $C_1$ との容量値配分により、トランジスタT3のゲート電位を決定する。従って、トランジスタT3のゲートには、トランジスタT3の閾値電圧 $V_{th}$ に依存しない値のゲート電位 $V_g$ が書き込まれることになる。

20

#### 【0055】

ここで、トランジスタT3のゲート・ソース間電圧 $V_{gs}$ を $V_{gs} = V_p - V_g$ とし、トランジスタT3の閾値電圧 $V_{th}$ を $V_{th} = V_p - V_t$ とすると、(7)式は次のように表される。

#### 【0056】

$$V_{gs} = V_{th} - (V_{data} - V_0) C_1 / (C_s + C_1) \quad \dots (8)$$

TFTが飽和領域で動作する場合、駆動電流 $I_d$ は次式で示されることによく知られている。

30

#### 【0057】

$$I_d = A (V_{gs} - V_{th})^2 \quad \dots (9)$$

さらに、(8)式および(9)式から、次式が導出される。

#### 【0058】

$$I_d = A (V_{data} - V_0)^2 [C_1 / (C_1 + C_s)]^2 \quad \dots (10)$$

ここで、Aはトランジスタの移動度、チャンネル幅・長さ、および容量に関係した定数である。従って、コンデンサ $C_s$ には、閾値電圧 $V_{th}$ に依存しない駆動電流 $I_d$ をトランジスタT3が流す電圧が書き込まれることになる。

40

#### 【0059】

##### [4] 発光期間

この期間の開始に対し、トランジスタT2, T6をOFFする。次に、図3(d)に示すように、トランジスタT4をONすることにより、コンデンサ $C_s$ からトランジスタT3, T4を介して有機EL素子OLEDに式(10)で示される表示データ電圧 $V_{data}$ で決められた駆動電流 $I_d$ が流れ、有機EL素子OLEDは発光または非発光を開始する。

#### 【0060】

このように、本実施形態の有機ELディスプレイ装置1は、図1に示すように、電流駆動型表示素子に所望する駆動電流を与えるトランジスタT3、このトランジスタT3と直列に接続され、有機EL素子OLEDを直接ON, OFFするトランジスタT4、トランジスタT3の駆動電流を制御する2つのスイッチ用のトランジスタT1, T2、および所

50

望の駆動電流情報を電圧値として蓄積する1つのコンデンサC<sub>s</sub>を含む画素A<sub>i j</sub>と、データ線S<sub>i</sub>を介して画素A<sub>i j</sub>と接続され、データ線S<sub>i</sub>に接続される画素A<sub>i j</sub>群をゲート信号に応じて順次駆動する出力スイッチOS1(24a)とを備えている。この出力スイッチOS1は、画素A<sub>i j</sub>外、例えばソースドライバ2内に設けられており、トランジスタT3の閾値バラツキを補償すると共に、所望の駆動電流情報を電圧値として印加する機能を持つトランジスタT5～T7と、コンデンサC1とを有している。

#### 【0061】

これにより、電圧プログラム式で画素A<sub>i j</sub>を駆動する有機ELディスプレイ装置1において、画素A<sub>i j</sub>内に設けられるコンデンサとしては1つのコンデンサC<sub>s</sub>のみとなる。それゆえ、例えば120ppi程度の解像度の表示装置の各画素A<sub>i j</sub>の開口率は、従来の1画素当たり2個のコンデンサが必要であった電圧プログラム式の表示装置に対して、コンデンサ1個削減されることにより、輝度が約10%程度改善されるので、高輝度化に寄与できる。また、本有機ELディスプレイ装置1では、出力スイッチ24に1つずつ設けられるコンデンサC1が、同一のデータ線S<sub>i</sub>に接続される各画素A<sub>i j</sub>に共通に用いられるので、コンデンサC1も必要最小限ですむ。

10

#### 【0062】

続いて、本実施形態の変形例について説明する。

#### 【0063】

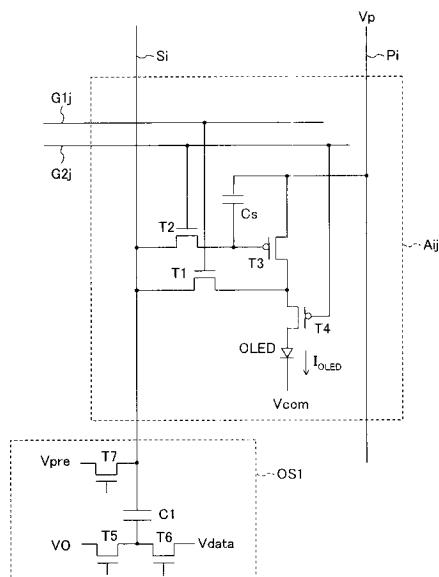

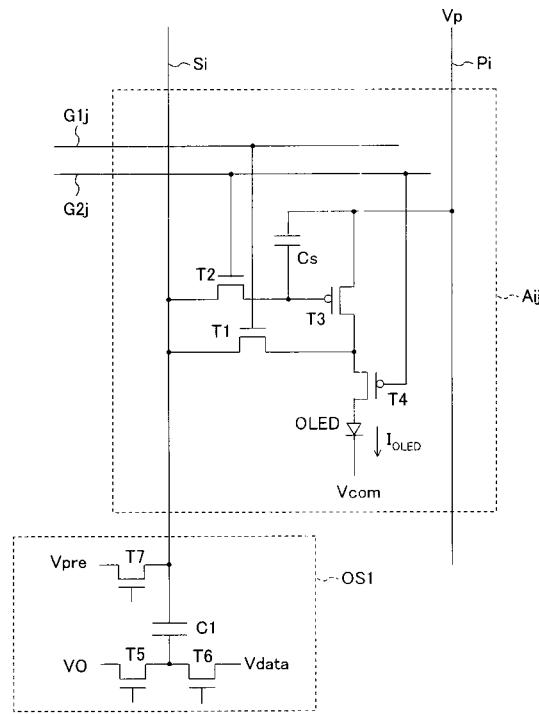

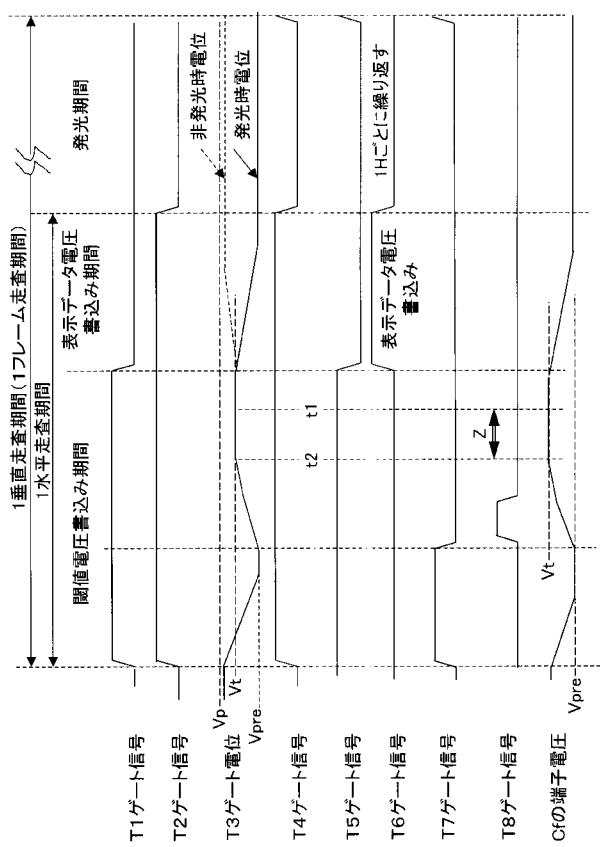

図5は、本変形例の画素A<sub>i j</sub>および出力スイッチ24の構成を示す回路図である。また、図6は、本変形例の画素A<sub>i j</sub>および出力スイッチ24の電圧プログラム動作を示すタイミングチャートである。

20

#### 【0064】

図5に示すように、この実施例の有機ELディスプレイ装置1では、データ線S<sub>i</sub>の浮遊容量C<sub>f</sub>が大きい場合を想定している。このため、出力スイッチ24は、トランジスタT8をデータライン駆動用にさらに追加している。TFTからなるトランジスタT8は、出力端子がデータ線S<sub>i</sub>に接続され、入力端子にトランジスタT3のゲートに現れる閾値電位V<sub>t</sub>近傍の電圧V<sub>a</sub>が入力される。

20

#### 【0065】

このような構成では、データ線S<sub>i</sub>にトランジスタT8をONすることにより、トランジスタT8を介して浮遊容量C<sub>f</sub>を充電するに足りる電圧V<sub>a</sub>が印加され、充電後には速やかにトランジスタT8をOFFする。これにより、図6に示すように、浮遊容量C<sub>f</sub>は期間Zで素早く充放電されるので、トランジスタT3のゲート電位が、図5のt1よりも早いt2で閾値電位に達する。それゆえ、書き込み速度をより速くすることができ、高速駆動に寄与する。

30

#### 【0066】

このような構成では、データ線S<sub>i</sub>にトランジスタT8をONすることにより、トランジスタT8を介して浮遊容量C<sub>f</sub>を充電する電圧V<sub>a</sub>がデータ線S<sub>i</sub>に印加され、充電後には速やかにトランジスタT8をOFFする。これにより、図6に示すように、浮遊容量C<sub>f</sub>は素早く充放電されるので、トランジスタT3のゲート電位が、図5のt1よりも期間Zで示した時間分早く時間t2で閾値電位に達する。それゆえ、書き込み速度をより速くすることができ、高速駆動に寄与する。

40

#### 【0067】

本発明は上述した実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能である。すなわち、請求項に示した範囲で適宜変更した技術的手段を組み合わせ得られる実施形態についても本発明の技術的範囲に含まれる。

#### 【産業上の利用可能性】

#### 【0068】

本発明の電流駆動型表示素子の駆動回路は、有機EL素子のアクティブマトリックス駆動において、階調制御を行うために時間分割などによるデジタル駆動とアナログ駆動に大別できる。駆動回路による電圧プログラムにより、駆動電流を制御できる駆動回路構成を

50

提供することができ、デジタル駆動或はアナログ駆動のいずれに適用されても、その本旨を損なわない。

【図面の簡単な説明】

【0069】

【図1】本発明の実施の一形態に係る有機ELディスプレイ装置における画素回路および出力スイッチの構成を示す回路図である。

【図2】上記有機ELディスプレイ装置の全体回路構成を示すブロック図である。

【図3】(a)ないし(d)は上記画素回路および出力スイッチの電圧プログラム動作における電流の流れを示す図である。

【図4】上記画素回路および出力スイッチの電圧プログラム動作を示すタイミングチャートである。 10

【図5】本発明の実施形態の変形例に係る有機ELディスプレイ装置における画素回路および出力スイッチの構成を示す回路図である。

【図6】図5の画素回路および出力スイッチの電圧プログラム動作を示すタイミングチャートである。

【図7】従来の有機ELディスプレイ装置における画素回路の構成を示す回路図である。

【図8】従来の他の有機ELディスプレイ装置における画素回路の構成を示す回路図である。

【符号の説明】

【0070】

|          |                |

|----------|----------------|

| 1        | 有機ELディスプレイ装置   |

| 2        | ゲートドライバ        |

| 3        | ソースドライバ        |

| 4        | コントロール回路(制御回路) |

| 5        | 電源回路           |

| 24a      | 出力スイッチ         |

| Aij      | 画素             |

| Gj       | 走査線            |

| Si       | データ線           |

| OLED     | 有機EL素子         |

| T1~T8    | トランジスタ         |

| Cs, C1   | コンデンサ          |

| OS1, OS2 | 出力スイッチ         |

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き(51)Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

H 05 B 33/14

A

F ターム(参考) 3K007 AB02 AB11 BA06 DB03 GA00

5C080 AA06 AA18 BB05 DD01 DD08 DD22 EE29 FF07 FF11 JJ02

JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于电流驱动的显示元件的驱动电路和具有该驱动电路的显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2005352411A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2005-12-22 |

| 申请号            | JP2004175882                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 申请日     | 2004-06-14 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人         | 大場 敏弘<br>入江一視                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 大場 敏弘<br>入江 一視                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| CPC分类号         | G09G2320/0295                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| FI分类号          | G09G3/30.J G09G3/20.611.H G09G3/20.621.F G09G3/20.623.R G09G3/20.624.B H05B33/14.A<br>G09G3/20.611.F G09G3/20.641.D G09G3/20.642.A G09G3/20.642.D G09G3/3233 G09G3/3266<br>G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 3K007/AB02 3K007/AB11 3K007/BA06 3K007/DB03 3K007/GA00 5C080/AA06 5C080/AA18 5C080<br>/BB05 5C080/DD01 5C080/DD08 5C080/DD22 5C080/EE29 5C080/FF07 5C080/FF11 5C080/JJ02<br>5C080/JJ03 5C080/JJ04 3K107/AA01 3K107/BB01 3K107/CC02 3K107/CC11 3K107/CC21 3K107<br>/CC36 3K107/CC42 3K107/CC45 3K107/EE03 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB06<br>5C380/AB21 5C380/AB23 5C380/BA13 5C380/BA19 5C380/BA38 5C380/BA39 5C380/BB22 5C380<br>/BC02 5C380/BC09 5C380/BC13 5C380/BD02 5C380/BD05 5C380/CA04 5C380/CA08 5C380/CA12<br>5C380/CA26 5C380/CA32 5C380/CA53 5C380/CB01 5C380/CB16 5C380/CB17 5C380/CB31 5C380<br>/CC04 5C380/CC07 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC53 5C380/CC62<br>5C380/CC63 5C380/CC64 5C380/CD014 5C380/CD024 5C380/CE04 5C380/CF07 5C380/CF09 5C380<br>/CF43 5C380/CF48 5C380/CF51 5C380/DA02 5C380/DA06 |         |            |

| 代理人(译)         | 木島 隆一<br>金子 一郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

### 摘要(译)

通过简化像素配置来减少像素中的电容器数量并实现高开口率，从而通过低电流驱动实现长寿命或高亮度。晶体管T4截止以停止电流流入有机EL元件OLED。接下来，晶体管T1，T2，T5，T7导通，并且阈值电压Vpre被施加到数据线Si以导通晶体管T3。当晶体管T7截止并且电容器Cs通过晶体管T3，T1，T2放电时，晶体管T3截止。然后，晶体管T2保持导通，晶体管T1和T5截止，并且晶体管T6导通。最后，在断开晶体管T2和T6之后，接通晶体管T4使由数据电压Vdata确定的驱动电流经由晶体管T3和T4流过有机EL元件OLED。[选型图]图1