# (19) 日本国特許庁(JP)

# (12) 公開特許公報(A)

(11)特許出願公開番号

特開2013-171153 (P2013-171153A)

(43) 公開日 平成25年9月2日(2013.9.2)

| (51) Int.Cl. |       |           | F 1    |      |                 |    | テーマコート    | ・ (参考) |

|--------------|-------|-----------|--------|------|-----------------|----|-----------|--------|

| G09G         | 3/30  | (2006.01) | G09G   | 3/30 | J               |    | 3 K 1 O 7 |        |

| G09G         | 3/20  | (2006.01) | GO9G   | 3/20 | 621M            |    | 5C080     |        |

| HO1L         | 51/50 | (2006.01) | GO9G   | 3/20 | 641D            |    | 5C38O     |        |

|              |       |           | GO9G   | 3/20 | $612\mathrm{U}$ |    |           |        |

|              |       |           | GO9G   | 3/20 | 624A            |    |           |        |

|              |       |           | 審査請求 未 | 請求   | 請求項の数 2         | ΟL | (全 11 頁)  | 最終頁に続く |

|              |       |           |        |      |                 |    |           |        |

(21) 出願番号 特願2012-34612 (P2012-34612) (22) 出願日 平成24年2月21日 (2012. 2. 21) (71) 出願人 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74)代理人 100109667

弁理士 内藤 浩樹

(74)代理人 100109151

弁理士 永野 大介

(74)代理人 100120156

弁理士 藤井 兼太郎

(72) 発明者 柘植 仁志

大阪府門真市大字門真1006番地 パナ

ソニック株式会社内

F ターム(参考) 3K107 AA01 BB01 CC14 CC33 CC42

CC45 EE03 HH01 HH04

最終頁に続く

# (54) 【発明の名称】画像表示装置

# (57)【要約】

【課題】EL表示パネルを用いた画像表示装置において、簡単な回路構成で大画面化を実現できるようにすることを目的とする。

【解決手段】有機 E L 素子に電流を流す駆動トランジスタとこの駆動トランジスタのゲート・ソース間に接続されたコンデンサとを有する画素回路を複数配列した E L 表示パネルを有し、前記画素回路に画像信号に応じた信号電圧を供給して前記コンデンサを充電する書込み期間と、前記駆動トランジスタのゲート・ソース間電圧に応じた電流を前記有機 E L 素子に流して発光させる発光期間とを有する画像表示装置であって、書込み期間中に減少する電圧減少量を画素回路に印加する電圧にあらかじめ加算して印加するとともに、 E L 表示パネルの中央部領域の画素回路に印加する電圧に比べて、端部領域の画素回路に印加する電圧が大きくなるように電圧減少量を設定した。

【選択図】図5

#### 【特許請求の範囲】

# 【請求項1】

有機EL素子に電流を流す駆動トランジスタとこの駆動トランジスタのゲート・ソース間に接続されたコンデンサとを有する画素回路を複数配列したEL表示パネルを有し、前記画素回路に画像信号に応じた信号電圧を供給して前記コンデンサを充電する書込み期間と、前記駆動トランジスタのゲート・ソース間電圧に応じた電流を前記有機EL素子に流して発光させる発光期間とを有する画像表示装置であって、前記書込み期間において、書込み期間中に減少する電圧減少量を画像信号に応じて画素回路に印加する電圧にあらかじめ加算して印加するとともに、前記EL表示パネルの中央部領域の画素回路に印加する電圧になるように電圧減少量を設定したに、端部領域の画素回路に印加する電圧が大きくなるように電圧減少量を設定したことを特徴とする画像表示装置。

【請求項2】

前記 E L 表示パネルの各画素回路における書込み時の電圧減少量の値を記憶した記憶手段を設け、入力される画像信号にガンマ補正を行った信号に、前記記憶手段から読み出した前記電圧減少量の値に基づく補正データを加算し、そのデータに基づく電圧を各画素回路に印加するように構成したことを特徴とする請求項1に記載の画像表示装置。

【発明の詳細な説明】

#### 【技術分野】

[0001]

本発明は、電流発光素子である有機 EL素子を用いたアクティブマトリックス型の画像表示装置に関する。

【背景技術】

[0002]

自ら発光する有機エレクトロルミネッセンス(EL)素子を用いた画像表示装置は、バックライトが不要で視野角にも制限がないため、次世代の画像表示装置として開発が進められている。

[0003]

有機EL素子は、流す電流量によって輝度を制御する電流発光素子である。近年は、画素回路毎に駆動トランジスタを備え有機EL素子を駆動するアクティブマトリックス型の有機EL表示装置が主流となってきている。

[0004]

駆動トランジスタおよびその周辺回路は、一般にポリシリコンやアモルファスシリコン等を用いた薄膜トランジスタで形成される。薄膜トランジスタは移動度および閾値電圧のばらつきが大きいという弱点があるものの、大型化が容易かつ安価であるために大型の有機 EL表示装置に適している。

[00005]

また、薄膜トランジスタの弱点である閾値電圧のばらつきおよび経時変化を画素回路の工夫により克服する方法についても検討されている。例えば特許文献1には、駆動トランジスタの閾値電圧を補正する機能を有する有機 EL表示装置とその駆動方法が開示されている。さらに特許文献2には、全画素の輝度 - 電圧特性のゲインとオフセットとを格納したメモリと、メモリのデータに基づき画像信号を補正する補正回路とを備え、画素間の輝度ばらつきに起因する輝度ムラを抑えた画像表示装置が開示されている。

【先行技術文献】

# 【特許文献】

[0006]

【特許文献1】特開2009-139125号公報

【特許文献 2 】特開 2 0 1 0 - 1 3 4 1 3 9 号公報

【発明の概要】

【発明が解決しようとする課題】

[0007]

20

10

30

40

有機EL素子は電流発光素子であるため、暗い画面での消費電力が非常に少ない画像表 示装置を構成することができる。特に、主に黒のバックグラウンドに文字等の表示を行う 場合には、バッテリーで長時間使用することができ、携帯用、移動用、野外用の画像表示 装置として有利である。

# [00008]

本発明はこのような現状に鑑みなされたものであり、簡単な回路構成で大画面化を実現 できるようにすることを目的とする。

# 【課題を解決するための手段】

# [0009]

上記目的を達成するために本発明は、有機EL素子に電流を流す駆動トランジスタとこ の駆動トランジスタのゲート・ソース間に接続されたコンデンサとを有する画素回路を複 数配列したEL表示パネルを有し、前記画素回路に画像信号に応じた信号電圧を供給して 前 記 コ ン デ ン サ を 充 電 す る 書 込 み 期 間 と 、 前 記 駆 動 ト ラ ン ジ ス タ の ゲ ー ト ・ ソ ー ス 間 電 圧 に応じた電流を前記有機EL素子に流して発光させる発光期間とを有する画像表示装置で あって、前記書込み期間において、書込み期間中に減少する電圧減少量を画像信号に応じ て画素回路に印加する電圧にあらかじめ加算して印加するとともに、前記EL表示パネル の中央部領域の画素回路に印加する電圧に比べて、端部領域の画素回路に印加する電圧が 大きくなるように電圧減少量を設定するように構成したことを特徴とする。

#### 【発明の効果】

# [ 0 0 1 0 ]

本発明によれば、書込み期間中に減少する電圧減少量を画像信号に応じて画素回路に印 加する電圧にあらかじめ加算して印加するとともに、パネルの中央部領域の画素回路に印 加する電圧に比べて、端部領域の画素回路に印加する電圧が大きくなるように電圧減少量 の値を設定することで、安定した書込みを行え、簡単な構成で大画面化を実現することが 可能となる。

# 【図面の簡単な説明】

#### [0011]

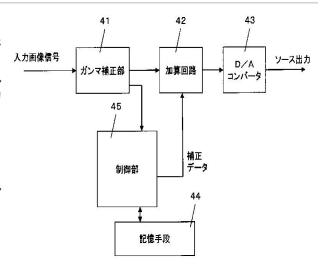

- 【図1】本発明の一実施の形態における画像表示装置の構成図

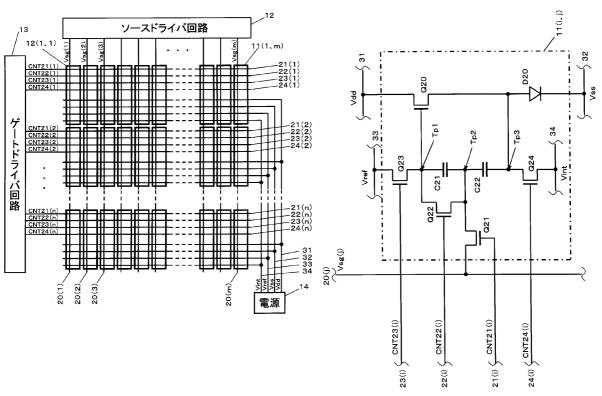

- 【図2】同画像表示装置の画像回路の一例を示す回路図

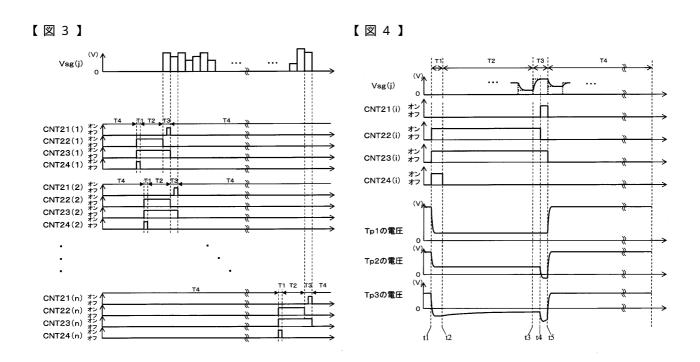

- 【 図 3 】 同 画 像 表 示 装 置 の 画 像 表 示 部 の 動 作 を 示 す タ イ ミ ン グ チ ャ ー ト

- 【 図 4 】 同 画 像 表 示 装 置 の 画 像 表 示 部 の 画 素 回 路 の 動 作 を 示 す タ イ ミ ン グ チ ャ ー ト

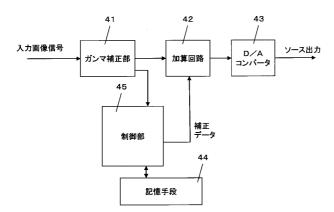

- 【図5】本発明の一実施の形態における画像表示装置の制御方法を実現するための構成の 一例を示すブロック図

# 【発明を実施するための形態】

# [0012]

以下、本発明の一実施の形態における画像表示装置について、図面を用いて説明する。 ここでは画像表示装置として、駆動トランジスタを用いて有機EL素子を発光させるアク ティブマトリックス型の有機EL表示装置について説明する。

# [ 0 0 1 3 ]

図1は、本発明の一実施の形態における有機EL表示装置の構成図である。

# [0014]

図 1 に示すように、有機 E L 表示装置は、 n 行 m 列 の マ ト リ ッ ク ス 状 に 複 数 配 列 さ れ た 多数の画素回路11(i、j)(ただし、1 i n、1 j mである)と、ソースド ライバ回路12と、ゲートドライバ回路13と、電源回路14とを備えている。

# [0015]

ソースドライバ回路12は、図1において列方向に配列された画素回路11(1、i) ~ 1 1 ( n 、 j ) に共通に接続されたデータ線 2 0 ( j ) にそれぞれ独立に信号電圧 V s g(j)を供給する。また、ゲートドライバ回路13は、図1において行方向に配列され た 画 素 回 路 1 1 ( i 、 1 ) ~ 1 1 ( i 、 m ) に 共 通 に 接 続 さ れ た ゲ ー ト 信 号 線 2 1 ( i ) ~ 2 4 ( i ) にそれぞれゲート信号CNT21( i ) ~ CNT24( i ) を供給する。本 10

20

30

40

10

20

30

40

50

実施の形態においては、1つの画素回路11(i、j)に4種類のゲート信号CNT21(i)~CNT24(i)を供給しているが、ゲート信号の数はこれに限定するものではなく、必要に応じた数のゲート信号を供給すればよい。

# [0016]

電源回路14は、全ての画素回路11(1、1)~11(n、m)に共通に接続された電源線31に高圧側電圧Vddを供給し、電源線32に低圧側電圧Vssを供給する。これら高圧側電圧Vddおよび低圧側電圧Vssの電源は、後述する有機EL素子を発光させるための電源である。また全ての画素回路11(i、j)に共通に接続された電圧線33に基準電圧Vrefを供給し、電圧線34に初期化電圧Vintを供給する。

# [0017]

図2は、有機 E L 表示装置の画素回路 1 1 ( i 、 j ) の回路図である。本実施の形態における画素回路 1 1 ( i 、 j ) は、電流発光素子である有機 E L 素子 D 2 0 と、駆動トランジスタ Q 2 0 と、第 1 コンデンサ C 2 1 と、第 2 コンデンサ C 2 2 と、スイッチとして動作するトランジスタ Q 2 1 ~ Q 2 4 とを備えている。

# [0018]

駆動トランジスタQ20は有機 E L 素子 D 20に電流を流す。第1コンデンサC21は画像信号に応じた信号電圧 V s g ( j ) を保持する。トランジスタQ23は第1コンデンサC21の一端に基準電圧 V r e f を印加するための第1のスイッチである。トランジスタQ21は信号電圧 V s g ( j ) を第1コンデンサC21に書込むための第2のスイッチであり、トランジスタQ22は第1コンデンサC21を短絡するスイッチである。第2コンデンサC22は駆動トランジスタQ20の閾値電圧 V t h を保持する。トランジスタQ24は第2コンデンサC22の一端に初期化電圧 V i n t を印加するための第3のスイッチである。

# [0019]

なお本実施の形態においては、駆動トランジスタQ20およびトランジスタQ21~Q24は全てNチャンネル薄膜トランジスタでありエンハンスメント型トランジスタであるものとして説明するが、本発明はこれに限定されるものではない。

#### [0020]

本実施の形態における画素回路11(i、j)は、電源線31と電源線32との間に駆動トランジスタQ20と有機EL素子D20とが接続されている。すなわち、駆動トランジスタQ20のドレインは電源線31に接続され、駆動トランジスタQ20のソースは有機EL素子D20のアノードに接続され、有機EL素子D20のカソードは電源線32に接続されている。

# [0021]

駆動トランジスタQ20のゲートとソースとの間には第1コンデンサC21と第2コンデンサC22とが直列に接続されている。すなわち、駆動トランジスタQ20のゲートには第1コンデンサC21の一方の端子が接続され、第1コンデンサC21の他方の端子は 第2コンデンサC22の一方の端子に接続され、第2コンデンサC22の他方の端子は駆動トランジスタQ20のソースに接続されている。以下では駆動トランジスタQ20のゲートと第1コンデンサC21とが接続されている節点を「節点Tp1」、第1コンデンサC21と第2コンデンサC22とが接続されている節点を「節点Tp2」、第2コンデンサC22と駆動トランジスタQ20のソースとが接続されている節点を「節点Tp3」とそれぞれ呼称する。

# [0022]

トランジスタQ23のドレイン(またはソース)は基準電圧Vrefが供給されている電圧線33に接続され、トランジスタQ23のソース(またはドレイン)は節点Tp1に接続され、トランジスタQ23のゲートはゲート信号線23(i)に接続されている。トランジスタQ21のドレイン(またはソース)は節点Tp2に接続され、トランジスタQ21のソース(またはドレイン)はデータ線20(j)に接続され、トランジスタQ21のゲートはゲート信号線21(i)に接続されている。

[0023]

トランジスタQ 2 2 のドレイン(またはソース)は節点Tp 1 に接続され、トランジスタQ 2 2 のソース(またはドレイン)は節点Tp 2 に接続され、トランジスタQ 2 2 のゲートはゲート信号線 2 2 ( i ) に接続されている。そしてトランジスタQ 2 4 のドレイン(またはソース)は節点Tp 3 に接続され、トランジスタQ 2 4 のソース(またはドレイン)は初期化電圧Vintが供給されている電圧線 3 4 に接続され、トランジスタQ 2 4 のゲートはゲート信号線 2 4 ( i ) に接続されている。

[0024]

データ線 2 0 ( j ) には画像信号に応じた信号電圧 V s g ( j ) が供給され、ゲート信号線 2 1 ( i ) ~ 2 4 ( i ) にはそれぞれゲート信号 C N T 2 1 ( i ) ~ C N T 2 4 ( i ) が供給されている。

[0025]

なお本実施の形態においては、有機EL素子D20に電流が流れ始めるときのアノード・カソード間電圧(以下、「電圧Vled」と称する)を1(V)、有機EL素子D20に電流が流れないときのアノード・カソード間容量を1(pF)程度と仮定する。また駆動トランジスタQ20の閾値電圧Vthを20(V)程度、第1コンデンサC21および第2コンデンサC22の静電容量を0.5(pF)と仮定する。駆動電圧については、高圧側電圧Vdd=10(V)、低圧側電圧Vss=0(V)、基準電圧Vref=1(V)、初期化電圧Vint=-1(V)であるとする。しかしこれらの数値は表示装置の仕様や各素子の特性に応じて変動し、駆動電圧は表示装置の仕様や各素子の特性に応じて最適に設定することが望ましい。

[0026]

次に、本実施の形態における画素回路11(i、j)の動作について説明する。

[ 0 0 2 7 ]

図3は、本発明の実施の形態における有機EL表示装置の動作を示すタイミングチャートである。このように1フレーム期間を初期化期間T1、閾値検出期間T2、書込み期間T3、発光期間T4の各期間に分割してそれぞれの画素回路11(i、j)の有機EL素子D20を駆動する。初期化期間T1では第2コンデンサC22を所定の電圧に充電する。閾値検出期間T2では駆動トランジスタQ20の閾値電圧Vthを検出して第2コンデンサC22に書込む。書込み期間T3では、画像信号に応じた信号電圧Vsg(j)を第1コンデンサC21に書込む。そして発光期間T4では、駆動トランジスタQ20のゲート・ソース間に第1コンデンサC21および第2コンデンサC22の端子間電圧の和を印加して、有機EL素子D20に電流を流し有機EL素子D20を発光させる。

[0028]

これらの4つの期間は、図1において行方向に配列されたm個の画素回路11(i、1)~11(i、m)で構成される画素行毎に共通するタイミングで設定し、かつ異なる画素行では互いに書込み期間T3が重ならないように設定している。このように1つの画素行で書込み動作を行う期間に他の画素行で書込み以外の動作を行うことで、駆動時間を有効に活用することができる。

[0029]

図4は、有機 E L 表示装置の画素回路 1 1 ( i 、 j )の動作を示すタイミングチャートである。また図4には、節点 T p 1 ~ T p 3 の電圧の変化も示している。以下、画素回路 1 1 ( i 、 j )の動作をそれぞれの期間における動作に分けて詳細に説明する。

[0030]

(初期化期間T1)

時刻 t 1 において、ゲート信号 C N T 2 1 ( i )をローレベルにしてトランジスタQ 2 1 をオフ状態とするとともに、ゲート信号 C N T 2 2 ( i )、 C N T 2 3 ( i )、 C N T 2 4 ( i )をハイレベルにしてトランジスタQ 2 2、 Q 2 3、 Q 2 4 をオン状態とする。するとトランジスタQ 2 3 を介して節点 T p 1 に基準電圧 V r e f が印加され、さらにトランジスタQ 2 2 を介して節点 T p 2 にも基準電圧 V r e f が印加される。また節点 T p

10

20

30

40

3にはトランジスタQ24を介して初期化電圧Vintが印加される。

#### [0031]

ここで基準電圧Vrefは、低圧側電圧Vssと有機EL素子D20の電圧Vledとの和よりも低い電圧に設定されている。すなわち、Vref<Vss+Vledである。これにより、駆動トランジスタQ20のソース電圧も電圧(Vss+Vled)よりも低くなるので、初期化期間T1で有機EL素子D20が発光することはない。

#### [0032]

また初期化電圧 Vintは、基準電圧 Vrefとの差が駆動トランジスタ Q20の閾値電圧 Vthよりも大きくなるように設定されている。すなわち、Vref-Vint>Vthである。これにより第2コンデンサ C22の端子間には閾値電圧 Vthよりも高い電圧 (Vref-Vint)に充電される。また駆動トランジスタ Q20のゲート・ソース間電圧も閾値電圧 Vthより高い電圧 (Vref-Vint)が印加されるので、高圧側電圧 Vddの電源から駆動トランジスタ Q20およびトランジスタ Q24を介して初期化電圧 Vintの電源に電流が流れる。なお本実施の形態において、初期化期間 T1は1μsに設定している。

# [0033]

# ( 閾値検出期間 T 2 )

時刻 t 2 においてゲート信号 C N T 2 4 (i)をローレベルにしてトランジスタ Q 2 4をオフ状態とする。このとき駆動トランジスタ Q 2 0 のゲート・ソース間には第 2 コンデンサ C 2 2 の端子間電圧が印加されているために駆動トランジスタ Q 2 0 には継続して電流が流れる。そしてこの電流により第 2 コンデンサ C 2 2 の電荷が放電され、第 2 コンデンサ C 2 2 の端子間電圧が低下しはじめる。しかし第 2 コンデンサ C 2 2 の端子間電圧は依然として閾値電圧 V t h より高いので駆動トランジスタ Q 2 0 には電流が減少しつつも流れ続ける。そのため第 2 コンデンサ C 2 2 の端子間電圧は歳々に低下し続ける。このようにして第 2 コンデンサ C 2 2 の端子間電圧の低下も止まる。2 0 に電流が流れなくなり、第 2 コンデンサ C 2 2 の端子間電圧の低下も止まる。

#### [ 0 0 3 4 ]

ここで駆動トランジスタQ 2 0 はゲート・ソース間電圧で制御される電流源として動作するので、第 2 コンデンサ C 2 2 の端子間電圧が低下するにともない駆動トランジスタQ 2 0 に流れる電流も減少する。そのため第 2 コンデンサ C 2 2 の端子間電圧が閾値電圧 V t h にほぼ等しくなるまでに非常に長い時間を要する。加えて有機 E L 素子 D 2 0 の大きな静電容量が第 2 コンデンサ C 2 2 の静電容量に加算されることも長い時間を要する要因となっている。実用的にはトランジスタをスイッチング動作させてコンデンサを充放電させる場合と比較して 1 0 ~ 1 0 0 倍の時間を要する。そのため本実施の形態においては閾値検出期間 T 2 を 1 0  $\mu$  s に設定している。

#### [0035]

# (書込み期間T3)

時刻 t 3 において、データ線 2 0 ( j ) には画素回路 1 1 ( i 、 j ) が表示すべき画像信号に応じた信号電圧 V s g ( j ) が供給される。しかしデータ線 2 0 ( j ) は比較的大きな等価容量を有し、またデータ線 2 0 ( j ) 自身もある程度のインピーダンスを有するので、図 4 に示すように、信号電圧 V s g ( j ) が確定するまでにある程度の時間を要する。

# [0036]

信号電圧Vsg(j)が確定した時刻t3において、ゲート信号CNT22(i)をローレベルにしてトランジスタQ22をオフ状態とする。その後、ゲート信号CNT21(i)をハイレベルにしてトランジスタQ21をオン状態とする。すると節点Tp2が信号電圧Vsg(j)となり、第1コンデンサC21の端子間は電圧(Vref-Vsg)に充電される。以下では、この電圧(Vref-Vsg)を信号電圧Vsg′と記載する。【0037】

# 10

20

30

本実施の形態においては、信号電圧 V s g ( j ) が確定するまでの時間、すなわちトランジスタ Q 2 1 をオン状態として第 1 コンデンサ C 2 1 を充電する時間を 1 μ s と設定している。

[0038]

( 発 光 期 間 T 4 )

時刻 t 5 において、ゲート信号 C N T 2 1 ( i ) をローレベルにしてトランジスタQ 2 1 をオフ状態とし、ゲート信号 C N T 2 3 ( i ) をローレベルにしてトランジスタQ 2 3 をオフ状態とする。すると節点 T p 1 ~ T p 3 は一旦フローティング状態となる。しかし、駆動トランジスタQ 2 0 のゲート・ソース間には電圧(V s g ' + V t h ) が印加されているので、ソース電圧が上昇して、駆動トランジスタQ 2 0 のゲート・ソース間電圧に応じた電流を有機 E L 素子 D 2 0 E に流す。

[0039]

このときの電流 I は、 I = K ・ ( V G S - V t h ) = K ・ V s g ' (ただし V G S はゲート・ソース間電圧、K は定数である。)となり、閾値電圧 V t h を含まない。

[0040]

このように、有機 E L 素子 D 2 0 に流れる電流には閾値電圧 V t h の影響が含まれない。従って有機 E L 素子 D 2 0 に流れる電流は、駆動トランジスタ Q 2 0 の閾値電圧 V t h のばらつきの影響を受けることがない。また閾値電圧 V t h が経時変化等により変動した場合であっても、画像信号に対応した輝度で有機 E L 素子 D 2 0 を発光させることができる。

[0041]

なお発光期間T4の後に、必要に応じて非発光期間を設けてもよい。非発光期間は、トランジスタQ22、Q23、Q24の少なくとも1つをオン状態とすることで実現できる

[0042]

また閾値検出期間T2において、トランジスタQ22をオン状態とすることが望ましいが、第1コンデンサC21のリーク電流を無視できればトランジスタQ22をオフ状態としてもよい。この場合にはゲート信号CNT22(i)とゲート信号CNT24(i)とを共用することができる。

[0043]

ところで、このような有機 E L 表示装置においては、画像信号の書き込みに伴い、駆動トランジスタQ 2 0 のゲート・ソース間には、第 1 コンデンサ C 2 1 の端子間電圧と第 2 コンデンサ C 2 2 の端子間電圧との和の電圧 ( V s g ' + V t h ) が印加されるが、このとき信号電圧 V s g ' > 0 であれば駆動トランジスタQ 2 0 に電流が流れ、有機 E L 素子D 2 0 の電圧が上昇し、第 1 コンデンサ C 2 1、第 2 コンデンサ C 2 2 の電荷が減少してしまうため、短時間の書込み期間で駆動している。

[0044]

しかしながら、大型の有機 E L 表示装置においては、パネルの中央部と端部とでは、ゲート線容量の違いにより書込み期間に差が発生し、これにより書込み終了時点での画像信号に応じた電荷量にばらつきが発生することから、所定の書込み期間内に十分な書込みを実現することができなくなる可能性がある。

[0045]

そこで、本発明は、短時間の書込み期間で十分な書込みが確保できるように、書込み期間中に減少する電圧減少量 Vを画像信号に応じて画素回路に印加する電圧にあらかじめ加算して印加するとともに、パネルの中央部領域の画素回路に印加する電圧に比べて、端部領域の画素回路に印加する電圧が大きくなるように Vの値を設定することで、安定した書込みを行えるようにしたものである。以下、本発明の構成について詳細に説明する。

[0046]

図 5 は本発明による制御方法を実現するための構成の一例を示すブロック図である。

[0047]

40

30

10

20

図 5 に示すように、入力された画像信号は、ガンマ補正部4 1 によりガンマ補正処理が行われ、加算回路4 2 を通して、デジタル・アナログ(D/A)コンバータ4 3 においてD/A変換され、ソース信号線を通して各画素に画像信号に基づく電圧が印加される。

#### [0048]

記憶手段44は、半導体メモリにより構成され、EL表示パネルの各画素回路における書込み時の電圧減少量 Vの値が記憶されている。この各画素回路の電圧減少量 Vは、EL表示パネルの製造時のプロセス条件などにより画素毎に変化するため、EL表示パネル作製後、各画素回路に電流を流して測定し、事前に決定した基準値との差分に基づき演算することによりあらかじめ設定している。なお、EL表示パネル作製後、実際にEL表示パネルを点灯させ、各画素回路の点灯時の輝度を測定し、事前に決定した輝度の基準値との差分に基づき演算して、記憶手段44に記憶する各画素回路の電圧減少量 Vの値を設定するようにしてもよい。

#### [0049]

制御部 4 5 は、ガンマ補正処理を施した画像信号に応じて、記憶手段 4 4 にあらかじめ記憶されている各画素回路の電圧減少量 Vの値を読み出し、電圧減少量 Vの値に基づく補正データを加算回路 4 2 に入力する。すなわち、ガンマ補正処理された画像信号に対して、各画素回路の電圧減少量 Vの値に基づく補正データが加算され、ソース信号線を通して各画素回路に電圧減少量 Vの値による補正データを加算したデータに基づく電圧が印加される。

# [0050]

上述したように、EL表示パネルの中央部と端部とでは、ゲート線容量の違いにより書込み期間に差が発生することから、本発明においては、このEL表示パネルの中央部と端部の間のゲート線容量による影響を考慮し、EL表示パネルの中央部領域の画素回路に印加する電圧に比べて、端部領域の画素回路に印加する電圧が大きくなるように、電圧減少量 Vの値を設定し、記憶手段44に記憶している。

# [0051]

以上のように本発明は、書込み期間中に減少する電圧減少量を画像信号に応じて画素回路に印加する電圧にあらかじめ加算して印加するとともに、EL表示パネルの中央部領域の画素回路に印加する電圧に比べて、端部領域の画素回路に印加する電圧が大きくなるように電圧減少量の値を設定することで、安定した書込みを行え、簡単な構成で大画面化を実現することが可能となる。

# 【産業上の利用可能性】

#### [0052]

本発明は、EL表示パネルを用いた画像表示装置の大画面化に有用な発明である。

# 【符号の説明】

# [0053]

- 1 1 画素回路

- 12 ソースドライバ回路

- 13 ゲートドライバ回路

- 14 電源回路

- D 2 0 有機 E L 素子

- Q20 駆動トランジスタ

- C 2 1 第1コンデンサ

- C 2 2 第 2 コンデンサ (補正コンデンサ)

- 4 1 ガンマ補正部

- 4 2 加算回路

- 4 3 D / A コンバータ

- 4 4 記憶手段

- 4 5 制御部

20

10

30

30

40

【図1】

# 【図5】

# フロントページの続き

| (51) Int.Cl. | FΙ            |         | テーマコード(参考) |

|--------------|---------------|---------|------------|

|              | G 0 9 G 3/20  | 6 3 1 V |            |

|              | G 0 9 G 3/20  | 6 4 1 Q |            |

|              | G 0 9 G 3/20  | 6 4 1 P |            |

|              | G 0 9 G 3/20  | 6 4 2 A |            |

|              | H 0 5 B 33/14 | Α       |            |

F ターム(参考) 5C080 AA06 BB05 CC06 DD05 JJ02 JJ03 JJ04 5C380 AA01 AB06 AB22 AB23 AC04 BA19 BA24 BA39 BA45 BB03 BB23 CA08 CA12 CB01 CC04 CC07 CC27 CC33 CC38 CC41 CC65 CD025 CF13 DA02 DA06 DA47 EA02

| 专利名称(译)        | 画像表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|

| 公开(公告)号        | <u>JP2013171153A</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2013-09-02 |  |  |

| 申请号            | JP2012034612                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2012-02-21 |  |  |

| [标]申请(专利权)人(译) | 松下电器产业株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |

| 申请(专利权)人(译)    | 松下电器产业株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |

| [标]发明人         | 柘植仁志                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |

| 发明人            | ·····································                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |  |  |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |  |  |

| FI分类号          | G09G3/30.J G09G3/20.621.M G09G3/20.641.D G09G3/20.612.U G09G3/20.624.A G09G3/20.631.V G09G3/20.641.Q G09G3/20.641.P G09G3/20.642.A H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                   |         |            |  |  |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC14 3K107/CC33 3K107/CC42 3K107/CC45 3K107/EE03 3K107 /HH01 3K107/HH04 5C080/AA06 5C080/BB05 5C080/CC06 5C080/DD05 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/AB22 5C380/AB23 5C380/AC04 5C380/BA19 5C380 /BA24 5C380/BA39 5C380/BA45 5C380/BB03 5C380/BB23 5C380/CA08 5C380/CA12 5C380/CB01 5C380/CC04 5C380/CC07 5C380/CC27 5C380/CC33 5C380/CC38 5C380/CC41 5C380/CC65 5C380 /CD025 5C380/CF13 5C380/DA02 5C380/DA06 5C380/DA47 5C380/EA02 |         |            |  |  |

| 代理人(译)         | 内藤裕树<br>长野大辅<br>藤井 兼太郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |  |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |  |  |

# 摘要(译)

摘要:要解决的问题:提供一种采用电致发光(EL)显示板的图像显示装置,其中可以用简单的电路结构实现大屏幕。解决方案:一种图像显示装置,包括EL显示面板,其中布置有多个像素电路,所述多个像素电路具有用于向有机EL元件提供电流的驱动晶体管和连接在驱动晶体管的栅极与其源极之间的电容器,并且被配置为具有用于根据图像信号向像素电路提供信号电压以对电容器充电的写入时间段以及用于根据栅极之间的电压向有机EL元件供应电流的发光时间段驱动晶体管及其源极发光。在其写入时段期间要降低的电压降低量被预先添加并施加到要施加到像素电路的电压,并且与要施加到EL显示面板的中心区域中的像素电路的电压相比,电压设定减小量使得施加到周边区域中的像素电路的电压更大。