(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-316454

(P2007-316454A)

(43) 公開日 平成19年12月6日(2007.12.6)

| (51) Int.CI.      | F 1                                                          | テーマコード (参考) |

|-------------------|--------------------------------------------------------------|-------------|

| <b>G09G 3/30</b>  | (2006.01) G09G 3/30 J 3K107                                  |             |

| <b>G09G 3/20</b>  | (2006.01) G09G 3/30 K 5C080                                  |             |

| <b>H01L 51/50</b> | (2006.01) G09G 3/20 624B<br>G09G 3/20 611H<br>G09G 3/20 622A |             |

審査請求 未請求 請求項の数 6 O L (全 18 頁) 最終頁に続く

|           |                              |          |                                                                                                            |

|-----------|------------------------------|----------|------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2006-147536 (P2006-147536) | (71) 出願人 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号                                                                     |

| (22) 出願日  | 平成18年5月29日 (2006.5.29)       | (74) 代理人 | 100092336<br>弁理士 鈴木 晴敏                                                                                     |

|           |                              | (72) 発明者 | 湯本 昭<br>東京都品川区北品川6丁目7番35号 ソニーブルーバード内                                                                       |

|           |                              |          | F ターム (参考) 3K107 AA01 BB01 CC33 CC45 HH04<br>HH05<br>5C080 AA06 BB05 DD05 DD22 EE29<br>FF11 JJ02 JJ03 JJ04 |

## (54) 【発明の名称】画像表示装置

## (57) 【要約】

【課題】ドライブトランジスタの閾電圧  $V_{th}$  のばらつきをキャンセルする機能を持たせつつ、スキャナの数を削減する。

【解決手段】画素回路2のサンプリングトランジスタT1は、サンプリング期間に走査線  $WS_n$  から供給される制御信号に応じ導通して信号線  $SL$  から供給された映像信号を画素容量  $C_s$  にサンプリングする。ドライブトランジスタ  $T_d$  は、サンプリングされた映像信号に応じた出力電流を発光素子  $OLED$  に供給する。更に画素回路2は、ドライブトランジスタ  $T_d$  のゲートに接続される閾電圧  $V_{th}$  キャンセル用のトランジスタ  $T_2$  を備えている。このトランジスタ  $T_2$  は、当該行よりも時間的に先行する行の走査線  $WS_n - k$  に印加される制御信号によってオンオフ動作して、映像信号のサンプリングに先立ってドライブトランジスタ  $T_d$  のゲートをあらかじめ基準の電位に設定する。

【選択図】図6

**【特許請求の範囲】****【請求項 1】**

制御信号を供給する行状の走査線と、映像信号を供給する列状の信号線と、該走査線と該信号線とが交差する部分に配された画素回路とを含み、

前記画素回路は、少なくともドライブトランジスタと、そのゲートに接続されるサンプリングトランジスタと、前記ドライブトランジスタのゲート・ソース間に接続される容量部と、前記ドライブトランジスタのソースに接続する発光素子とを含み、

前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、

前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、10

前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、

前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する画像表示装置であって、

前記画素回路は、前記ドライブトランジスタのゲートに接続される基準電位設定トランジスタを備えており、

前記基準電位設定トランジスタは、当該行よりも時間的に先行する行の走査線に印加される制御信号によってオンオフ動作して、映像信号のサンプリングに先立って前記ドライブトランジスタのゲートをあらかじめ基準の電位に設定することを特徴とする画像表示装置。20

**【請求項 2】**

制御信号を供給する行状の走査線と、映像信号を供給する列状の信号線と、該走査線と該信号線とが交差する部分に配された画素回路とを含み、

前記画素回路は、少なくともドライブトランジスタと、そのゲートに接続されるサンプリングトランジスタと、前記ドライブトランジスタのゲート・ソース間に接続される容量部と、前記ドライブトランジスタのソースに接続する発光素子とを含み、

前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、30

前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、

前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、

前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する画像表示装置であって、

前記画素回路は、前記ドライブトランジスタのソースに接続される初期化トランジスタを備えており、

前記初期化トランジスタは、当該行よりも時間的に先行する行の走査線に印加される制御信号によってオンオフ動作して、映像信号のサンプリングに先立って前記ドライブトランジスタのソースをあらかじめ所定の電位に初期化しておくことを特徴とする画像表示装置。40

**【請求項 3】**

制御信号を供給する行状の走査線と、映像信号を供給する列状の信号線と、該走査線と該信号線とが交差する部分に配された画素回路とを含み、

前記画素回路は、少なくともドライブトランジスタと、そのゲートに接続されるサンプリングトランジスタと、前記ドライブトランジスタのゲート・ソース間に接続される容量部と、前記ドライブトランジスタのソースに接続する発光素子とを含み、

前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、

前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲー50

トとソース間に入力電圧を印加し、

前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、

前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する画像表示装置であって、

前記画素回路は、前記ドライブトランジスタのソースに接続される初期化トランジスタと、前記ドライブトランジスタのゲートに接続される基準電位設定トランジスタとを備えており、

前記初期化トランジスタは、当該行よりも時間的に先行する行の走査線に印加される制御信号によってオンオフ動作して、映像信号のサンプリングに先立って前記ドライブトランジスタのソースをあらかじめ所定の電位に初期化し、10

前記基準電位設定トランジスタは、当該行よりも時間的に先行する行の走査線に印加される制御信号によってオンオフ動作して、前記ドライブトランジスタのソースの電位が初期化された時又はその後で且つ映像信号のサンプリングに先立ち、前記ドライブトランジスタのゲートをあらかじめ基準の電位に設定しておくことを特徴とする画像表示装置。

#### 【請求項 4】

前記初期化トランジスタが、走査線から印加される制御信号によってオンしている時間は、一水平走査期間よりも長いことを特徴とする請求項 3 に記載の画像表示装置。10

#### 【請求項 5】

前記行状の走査線と並行に、行状の電源駆動線が配されており、20

各電源駆動線は、各発光期間に電源電圧を供給し、

前記ドライブトランジスタは、そのドレインが対応する電源駆動線に接続されており、該電源電圧に応じて出力電流を発光素子に供給することを特徴とする請求項 3 に記載の画像表示装置。20

#### 【請求項 6】

前記画素回路は、前記ドライブトランジスタのドレインと所定の電源電位との間に接続されたスイッチングトランジスタを含み、発光期間中導通して、該ドライブトランジスタから発光素子に出力電流を流すようにしたことを特徴とする請求項 3 に記載の画像表示装置。30

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、画素毎に配した発光素子を電流駆動する画素回路を備えた画像表示装置に関する。より詳しくは、画素回路がマトリクス状（行列状）に配列された画像表示装置であって、特に画素回路内に設けた絶縁ゲート型電界効果トランジスタによって有機ELなどの発光素子に通電する電流量を制御する、いわゆるアクティブマトリクス型の画像表示装置に関する。30

#### 【背景技術】

#### 【0002】

画像表示装置、例えば液晶ディスプレイなどでは、多数の液晶画素をマトリクス状に並べ、表示すべき画像情報に応じて画素毎に入射光の透過強度又は反射強度を制御することによって画像を表示する。これは、有機EL素子を画素に用いた有機ELディスプレイなどにおいても同様であるが、液晶画素と異なり有機EL素子は自発光素子である。その為、有機ELディスプレイは液晶ディスプレイに比べて画像の視認性が高く、バックライトが不要であり、応答速度が高いなどの利点を有する。又、各発光素子の輝度レベル（階調）はそれに流れる電流値によって制御可能であり、いわゆる電流制御型であるという点で液晶ディスプレイなどの電圧制御型とは大きく異なる。40

#### 【0003】

有機ELディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として単純マトリクス方式とアクティブマトリクス方式とがある。前者は構造が単純であるものの、50

大型且つ高精細のディスプレイの実現が難しいなどの問題がある為、現在はアクティブマトリクス方式の開発が盛んに行なわれている。この方式は、各画素回路内部の発光素子に流れる電流を、画素回路内部に設けた能動素子（一般には薄膜トランジスタ、TFT）によって制御するものである。画素回路としては、例えば以下の特許文献1に開示がある。

【特許文献1】特開平8-234683号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

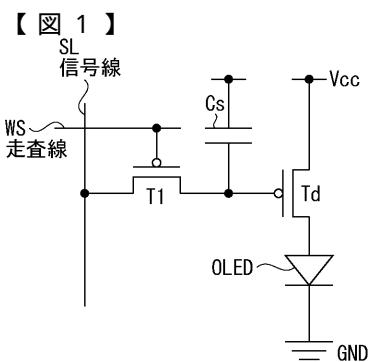

図1は、従来の画素回路の典型例を示す回路図である。図示する様に、従来の画素回路は、制御信号を供給する行状の走査線WSと映像信号を供給する列状の信号線SLとが交差する部分に配され、少なくともサンプリングトランジスタT1と容量部を構成する画素容量Csと、ドライブトランジスタTdと発光素子OLEDとを含む。サンプリングトランジスタT1は、走査線WSから供給される制御信号（選択パルス）に応じ導通して信号線SLから供給された映像信号をサンプリングする。画素容量Csは、サンプリングされた映像信号に応じた入力電圧を保持する。ドライブトランジスタTdは、電源ラインVccに接続されており、画素容量Csに保持された入力電圧に応じて出力電流を発光素子OLEDに供給する。発光素子OLEDは二端子型（ダイオード型）で、そのアノードがドライブトランジスタTdに接続され、カソードが接地ラインGNDに接続されている。発光素子OLEDはドライブトランジスタTdから供給された出力電流（ドレイン電流）により映像信号に応じた輝度で発光する。なお一般に、出力電流（ドレイン電流）はドライブトランジスタTdのチャネル領域のキャリア移動度及び閾電圧に対して依存性を有する。

【0005】

ドライブトランジスタTdは、画素容量（容量部）Csに保持された入力電圧をゲートに受けてソース／ドレイン間に出来た出力電流を流し、発光素子OLEDに通電する。発光素子OLEDは例えば有機ELデバイスからなり、その発光輝度は通電量に比例している。さらにドライブトランジスタTdの出力電流供給量はゲート電圧即ち画素容量Csに書き込まれた入力電圧によって制御される。従来の画素回路は、ドライブトランジスタTdのゲートに印加される入力電圧を入力映像信号に応じて変化させることで、発光素子OLEDに供給する電流量を制御している。

【0006】

ここでドライブトランジスタの動作特性は以下の式1で表わされる。

$$I_{ds} = (1/2) \mu (W/L) C_{ox} (V_{gs} - V_{th})^2 \dots \text{式1}$$

このトランジスタ特性式1において、 $I_{ds}$ はソース／ドレイン間に流れるドレイン電流を表わしており、画素回路では発光素子に供給される出力電流である。 $V_{gs}$ はソースを基準としてゲートに印加されるゲート電圧を表わしており、画素回路では上述した入力電圧である。 $V_{th}$ はトランジスタの閾電圧である。又 $\mu$ はトランジスタのチャネルを構成する半導体薄膜の移動度を表わしている。その他Wはチャネル幅を表わし、Lはチャネル長を表わし、 $C_{ox}$ はゲート容量を表わしている。このトランジスタ特性式1から明らかな様に、薄膜トランジスタは飽和領域で動作する時、ゲート電圧 $V_{gs}$ が閾電圧 $V_{th}$ を超えて大きくなると、オン状態となってドレイン電流 $I_{ds}$ が流れる。原理的に見ると上記のトランジスタ特性式1が示す様に、ゲート電圧 $V_{gs}$ が一定であれば常に同じ量のドレイン電流 $I_{ds}$ が発光素子に供給される。従って、画面を構成する各画素に全て同一のレベルの映像信号を供給すれば、全画素が同一輝度で発光し、画面の一様性（ユニフォーミティ）が得られるはずである。

【0007】

しかしながら実際には、ポリシリコンなどの半導体薄膜で構成された薄膜トランジスタ（TFT）は、個々のデバイス特性にはらつきがある。特に、閾電圧 $V_{th}$ は一定ではなく、画素毎にはらつきがある。前述のトランジスタ特性式1から明らかな様に、各ドライブトランジスタの閾電圧 $V_{th}$ がばらつくと、ゲート電圧 $V_{gs}$ が一定であっても、ド

10

20

30

40

50

レイン電流  $I_{ds}$  にばらつきが生じ、画素毎に輝度がばらついてしまう為、画面のユニフォーミティを損なう。

#### 【0008】

このため従来からドライブトランジスタの閾電圧のばらつきをキャンセルする機能を組み込んだ画素回路が開発されており、例えば以下の特許文献2に開示されている。

#### 【特許文献2】特開平2005-345722号公報

#### 【0009】

閾電圧  $V_{th}$  のばらつきをキャンセルする機能を組み込んだ画素回路は、画面のユニフォーミティや、閾電圧の経時変化による輝度変動を改善することが可能である。しかしながら、画素回路に閾電圧キャンセル機能を組み込むため、サンプリングトランジスタやドライブトランジスタの他に、少なくとも3個のトランジスタを追加する必要がある。しかも、これら追加されたトランジスタはサンプリングトランジスタとは別のタイミングで線順次走査する必要がある。従って、図1に示した単純な画素回路に比べると、1行分の画素に対して走査線が少なくとも4本必要となり、その分各走査線を異なるタイミングで線順次走査するためのスキャナが必要になる。即ち、図1に示した単純な画素回路に比べ、閾電圧キャンセル機能を組み込んだ画素を線順次走査するため、別途スキャナが3系統増加する。アモルファスシリコン TFT プロセスで画素回路を形成する場合、通常スキャナは外付け部品によって構成されるため、スキャナ数の増加は、直接製造コストの上昇につながる。また低温ポリシリコン TFT プロセスを用いて画素回路を形成する場合は、同時にスキャナもポリシリコン TFT で構成することが可能である。しかしそれの個数の増加は歩留り低下要因となるし、スキャナを配置するためのスペースが基板上に必要となることから、やはり製造コストの上昇につながる。

10

20

30

40

#### 【課題を解決するための手段】

#### 【0010】

上述した従来の技術の課題に鑑み、本発明はドライブトランジスタの閾電圧  $V_{th}$  のばらつきをキャンセルする機能を持たせつつ、スキャナの数を削減可能な画像表示装置を提供することを目的とする。かかる目的を達成するために以下の手段を講じた。即ち本発明は、制御信号を供給する行状の走査線と、映像信号を供給する列状の信号線と、該走査線と該信号線とが交差する部分に配された画素回路とを含み、前記画素回路は、少なくともドライブトランジスタと、そのゲートに接続されるサンプリングトランジスタと、前記ドライブトランジスタのゲート・ソース間に接続される容量部と、前記ドライブトランジスタのソースに接続する発光素子とを含み、前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する画像表示装置であって、前記画素回路は、前記ドライブトランジスタのゲートに接続される基準電位設定トランジスタを備えており、前記基準電位設定トランジスタは、当該行よりも時間的に先行する行の走査線に印加される制御信号によってオンオフ動作して、映像信号のサンプリングに先立って前記ドライブトランジスタのゲートをあらかじめ基準の電位に設定することを特徴とする。

#### 【0011】

又本発明は、制御信号を供給する行状の走査線と、映像信号を供給する列状の信号線と、該走査線と該信号線とが交差する部分に配された画素回路とを含み、前記画素回路は、少なくともドライブトランジスタと、そのゲートに接続されるサンプリングトランジスタと、前記ドライブトランジスタのゲート・ソース間に接続される容量部と、前記ドライブトランジスタのソースに接続する発光素子とを含み、前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、前記容量部は、該サンプリングされた映像

50

信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する画像表示装置であって、前記画素回路は、前記ドライブトランジスタのソースに接続される初期化トランジスタを備えており、前記初期化トランジスタは、当該行よりも時間的に先行する行の走査線に印加される制御信号によってオンオフ動作して、映像信号のサンプリングに先立って前記ドライブトランジスタのソースをあらかじめ所定の電位に初期化しておくことを特徴とする。

#### 【0012】

又本発明は、制御信号を供給する行状の走査線と、映像信号を供給する列状の信号線と、該走査線と該信号線とが交差する部分に配された画素回路とを含み、前記画素回路は、少なくともドライブトランジスタと、そのゲートに接続されるサンプリングトランジスタと、前記ドライブトランジスタのゲート・ソース間に接続される容量部と、前記ドライブトランジスタのソースに接続する発光素子とを含み、前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する画像表示装置であって、前記画素回路は、前記ドライブトランジスタのソースに接続される初期化トランジスタと、前記ドライブトランジスタのゲートに接続される基準電位設定トランジスタとを備えており、前記初期化トランジスタは、当該行よりも時間的に先行する行の走査線に印加される制御信号によってオンオフ動作して、映像信号のサンプリングに先立って前記ドライブトランジスタのソースをあらかじめ所定の電位に初期化し、前記基準電位設定トランジスタは、当該行よりも時間的に先行する行の走査線に印加される制御信号によってオンオフ動作して、前記ドライブトランジスタのソースの電位が初期化された時又はその後で且つ映像信号のサンプリングに先立ち、前記ドライブトランジスタのゲートをあらかじめ基準の電位に設定しておくことを特徴とする。

#### 【0013】

好ましくは、前記初期化トランジスタが、走査線から印加される制御信号によってオンしている時間は、一水平走査期間よりも長い。又前記行状の走査線と並行に、行状の電源駆動線が配されており、各電源駆動線は、各発光期間に電源電圧を供給し、前記ドライブトランジスタは、そのドレインが対応する電源駆動線に接続されており、該電源電圧に応じて出力電流を発光素子に供給する。又前記画素回路は、前記ドライブトランジスタのドレインと所定の電源電位との間に接続されたスイッチングトランジスタを含み、発光期間中導通して、該ドライブトランジスタから発光素子に出力電流を流す。

#### 【発明の効果】

#### 【0014】

本発明によれば、ドライブトランジスタの閾電圧のばらつきをキャンセルする機能を組み込むため、画素回路に初期化トランジスタや基準電位設定トランジスタを組み込んでいる。初期化トランジスタはドライブトランジスタのソース電位を初期化するものであり、基準電位設定トランジスタは同じくドライブトランジスタのゲートを基準電位に設定するものである。これらの初期化や基準電位設定を行うことで、閾電圧キャンセル機能を実現できる。本発明では特に、当該行よりも時間的に先行する行の走査線に印加される映像信号サンプリング用の制御信号を利用して、当該行の初期化トランジスタの初期化動作を実行している。これによりサンプリングトランジスタを線順次走査するスキーナを初期化トランジスタの線順次走査に利用できるため、初期化トランジスタ専用のスキーナを持つ必要がなくなる。また当該行よりも時間的に先行する行の走査線に印加されるサンプリング用制御信号を利用して、当該行の基準電位設定トランジスタの基準電位設定動作を制御し

10

20

30

40

50

ている。これにより同じくサンプリング用のスキャナを併用できるため、基準電位設定専用のスキャナを持つ必要がない。従って、画素回路に Vth シャンセル機能を有したまま、低コストの画像表示装置を提供することが出来る。

**【発明を実施するための最良の形態】**

**【0015】**

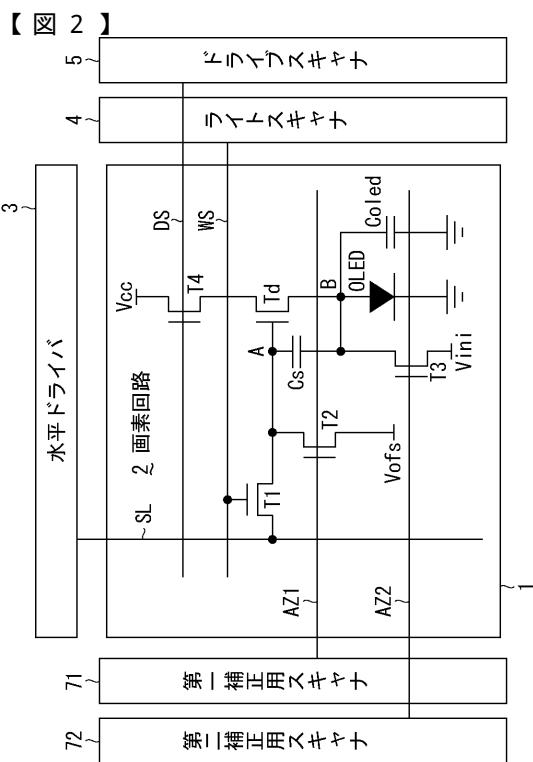

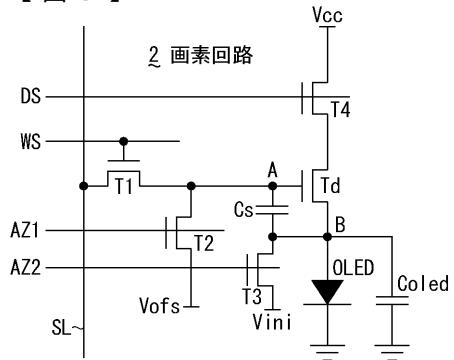

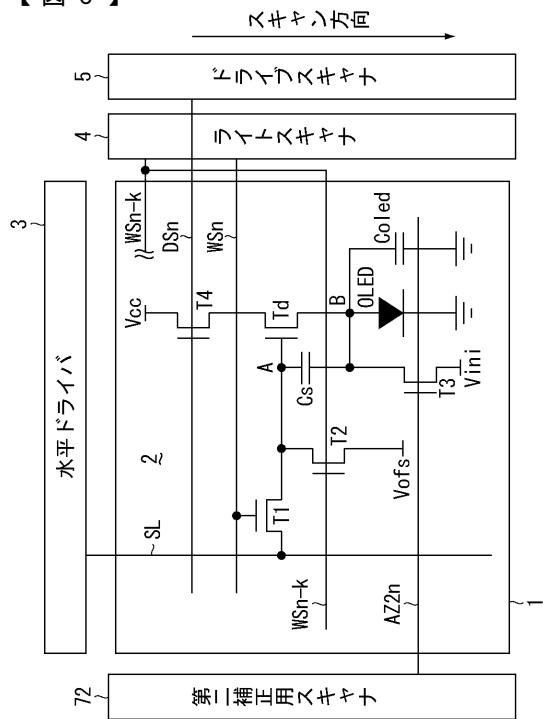

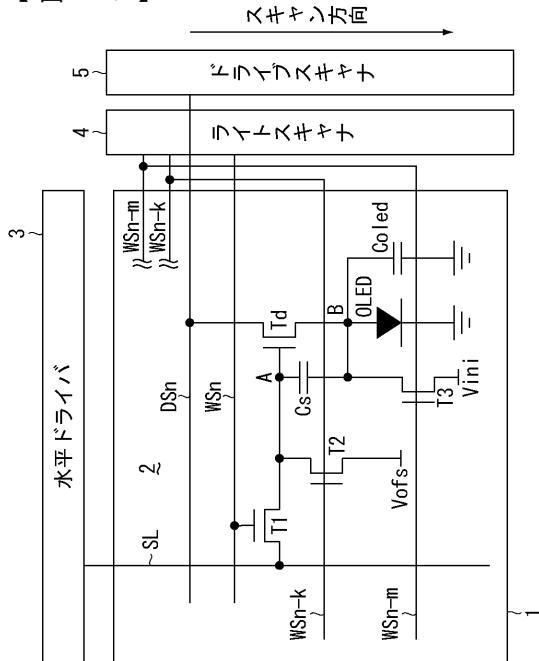

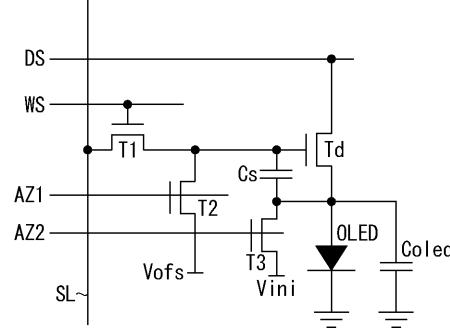

以下図面を参照して本発明の実施の形態を詳細に説明する。まず本発明の背景を明らかにするため、図2を参照して、本発明の元になった先行開発にかかる画像表示装置を説明する。この先行開発にかかる画像表示装置は、同一出願人にかかる特願2005-027028号に詳細な記載がある。先行開発にかかる画像表示装置は本発明にかかる画像表示装置と共に多くの部分が共通するため、ここに改めて本発明の一部として説明を行う。図示する様に、本画像表示装置は画素アレイ1と周辺の回路部からなる。画素アレイ1は画素回路2が行列状に配されており、画面を構成する。周辺の回路部は、画素アレイ1を線順次走査するための4系統のスキャナ4, 5, 71, 72を含んでいる。また画素アレイ1に映像信号を供給するため水平ドライバ3を含んでいる。

**【0016】**

各画素回路2は行状の走査線WSと列状の信号線SLとが交差する部分に配されている。図では理解を容易にするため、1個の画素回路2のみを示してある。信号線SLは水平ドライバ3に接続している。走査線WSはライトスキャナ4に接続している。本画像表示装置は、信号サンプリング用の走査線WSに加え、追加の走査線DS, AZ1, AZ2を含んでいる。これらの走査線DS, AZ1, AZ2はサンプリング用の走査線WSと並行に配されている。走査線DSはドライブスキャナ5に接続されており、発光期間を制御している。走査線AZ1は第一補正用スキャナ71に接続されており、基準電位設定動作に使われる。また走査線AZ2は第二補正用スキャナ72に接続されており、初期化動作に使われる。

**【0017】**

画素回路2は、5個のトランジスタT1, T2, T3, T4, Tdと、1個の画素容量Csと、1個の発光素子OLEDとで構成されている。本例は、全てのトランジスタがNチャネル型であるが、本発明はこれに限られるものではない。適宜Nチャネル型とPチャネル型を混ぜて画素回路を構成することが出来る。ドライブトランジスタTdは、そのゲートがノードAに接続されており、ソースがノードBに接続されており、ドレインがスイッチングトランジスタT4を介して電源ラインVccに接続されている。サンプリングトランジスタT1は信号線SLとノードAとの間に接続されている。サンプリングトランジスタT1のゲートは走査線WSに接続している。基準電位設定トランジスタT2はノードAと所定の基準電位Vofsとの間に接続されている。基準電位設定トランジスタT2のゲートは走査線AZ1に接続されている。初期化トランジスタT3はノードBと所定の初期化電位Vinjとの間に接続されている。初期化トランジスタT3のゲートは走査線AZ2に接続されている。スイッチングトランジスタT4は電源ラインVccとドライブトランジスタTdとの間に接続されている。そのゲートは走査線DSに接続している。画素容量CsはノードAとノードBとの間に接続されている。換言すると、画素容量CsはドライブトランジスタTdのゲートとソースとの間に接続されている。発光素子OLEDは例えば有機EL素子などの二端子型デバイスからなり、そのアノードはノードBに接続されており、カソードは接地されている。なお、発光素子OLEDの等価容量Coleoも図面に加えている。

**【0018】**

図示する様に、本画像表示装置は画素アレイ1を線順次走査するため、ライトスキャナ4、ドライブスキャナ5、第一補正用スキャナ71、第二補正用スキャナ72の合計4系統のスキャナを用いている。この分製造コストの増加を招いている。

**【0019】**

図3は、図2に示した画素アレイ1から特に画素回路2のみを切り取って模式的に示したものである。

10

20

30

40

50

## 【0020】

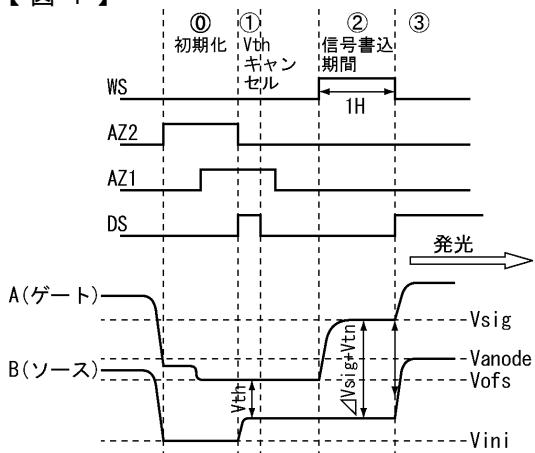

図4は、図2に示した画像表示装置の動作説明に供するタイミングチャートである。各スキャナ4, 5, 71, 72から線順次で出力される制御信号の波形をあらわしている。図では理解を容易にするため、各走査線に印加される制御信号（ゲート選択パルス）を走査線と同じ記号で表してある。即ちサンプリング用の走査線WSに印加されるサンプリング用制御信号をWSで表し、初期化用走査線AZ2に印加される初期化用制御信号をAZ2で表してある。また走査線AZ1に印加される基準電位設定用制御信号をAZ1で表してある。加えて走査線DSに印加される制御信号をDSで表してある。またこれら制御信号の波形と合わせて、ノードA及びノードBの電位変化も表してある。ノードAの電位変化は、ドライブトランジスタTdのゲート電位の変化を表している。またノードBの電位変化は、ドライブトランジスタTdのソースの電位変化を表している。

10

## 【0021】

図2に示した各スキャナ4, 5, 71, 72は時系列的に対応する制御信号を出力して、ステップ0ないし3の動作を順次行う。図4のタイミングチャートでは各ステップの番号を丸囲みで表している。最初にステップ0で初期化動作を行い、続いてステップ1でVthキャンセル動作を行い、さらにステップ2で信号書き込み動作（サンプリング動作）を行い、その後ステップ3で発光動作を行う。このステップ0ないし3を1フィールド毎に線順次で行い、画素アレイ1に1フィールド分の画像を表示する。

20

## 【0022】

初期化ステップ0では、制御信号AZ2が高レベルになる為Nチャネル型のトランジスタTdがオン状態となり、ドライブトランジスタTdのソース電位が初期化電位Vininiになる。続いてVthキャンセルステップ1では、制御信号AZ1及びDSが高レベルになる為、同じくNチャネル型のトランジスタT2, T4がオン状態となり、この結果ドライブトランジスタTdのゲート電位は基準電位Vofsになる。このときVofs - Vinini > Vthを満たすように設定されるため、ドライブトランジスタTdに電流が流れソース電位がVininiから上昇する。やがてドライブトランジスタTdのゲート・ソース間電位VgsがVthに等しくなるとドライブトランジスタTdにドレイン電流が流れなくなる為、Vthに等しい電圧が画素容量Csに保持されることになる。

20

## 【0023】

この後信号書き込みステップ2では制御信号WSが高レベルになる為サンプリングトランジスタT1がオン状態となり、信号線SLから映像信号電位Vsigがサンプリングされる。このとき発光素子OLEDの等価容量Coloredが画素容量Csに比べて十分大きいので、ドライブトランジスタTdのソース電位はステップ1の状態とほぼ変わらないから、画素容量CsにはVsig + Vthの電圧が保持されることになる。ここでVsig = Vsig - Vofsである。

30

## 【0024】

この後発光ステップ3の発光期間に入ると、制御信号DSが再び高レベルとなり、スイッチングトランジスタT4がオンする。これによりドライブトランジスタTdが電源ラインVccに接続され、ドレイン電流Idsが発光素子OLEDに流れ込む。この結果発光素子OLEDの内部抵抗のためそのアノード電位（即ちドライブトランジスタのソース電位）Vnodeは上昇する。その際ブートストラップ動作のため、画素容量Csに書き込まれた電圧はそのまま保持され、ドライブトランジスタTdのゲート電位もVnodeの上昇に伴って上昇する。つまり、発光期間中ドライブトランジスタTdのゲート・ソース間には一定の電圧Vsig + Vthが印加される。

40

## 【0025】

ステップ3の発光期間においてドライブトランジスタTdを流れるドレイン電流は前述した特性式1で与えられるため、以下の式2のように表される。この式2から明らかのように、ドレイン電流IdsはドライブトランジスタTdのVthに依存しないことが分かる。

$$I_{ds} = (1/2) \mu (W/L) C_o x (V_{gs} - V_{th})^2$$

50

$$\begin{aligned}

&= (1/2) \mu (W/L) C_o x (V_{sig} + V_{th} - V_{th})^2 \\

&= (1/2) \mu (W/L) C_o x \cdot V_{sig}^2 \cdots \text{式2}

\end{aligned}$$

## 【0026】

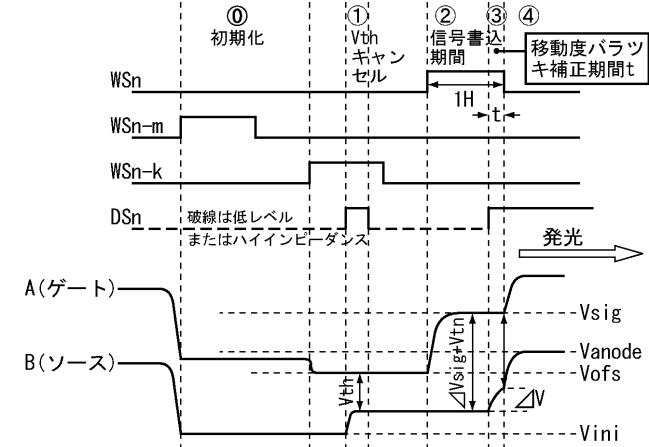

図5は、上述した閾電圧補正動作に加え、ドライブトランジスタの移動度 $\mu$ のばらつき補正動作を加えた例である。なお理解を容易にするため、図5のタイミングチャートは、図4のタイミングチャートと同様の表記を採用している。本例では、信号書き込みステップ2の後半で移動度補正ステップ3を行っている。その後発光ステップ4に進む。この移動度補正ステップ3では、制御信号WSが高レベルの状態で制御信号DSが高レベルとされるため、ドライブトランジスタTdにドレイン電流が流れ、そのソース電位がVだけ上昇する。一方ドライブトランジスタTdのゲート電位はVsigによって固定されるため、結果的にドライブトランジスタTdのVgsがVだけ減少する。この減少分Vの度合いは、ドライブトランジスタTdに流れる電流が大きいほど大きい。換言すると、前述のトランジスタ特性式1から明らかなように、ドライブトランジスタTdの移動度 $\mu$ が大きいほど、この減少分Vは大きくなる。この後制御信号WSがローレベルになり、ステップ4の発光動作に進むが、Vが大きいほど、発光素子OLEDに供給される出力電流のレベルが小さくなる。換言すると、Vだけ負帰還がかかるということである。このため、各画素回路間でドライブトランジスタTdの移動度 $\mu$ にばらつきがあった場合、各画素回路毎にこの負帰還をかけることで移動度のばらつきに起因する輝度むらを緩和することが可能である。

10

20

## 【0027】

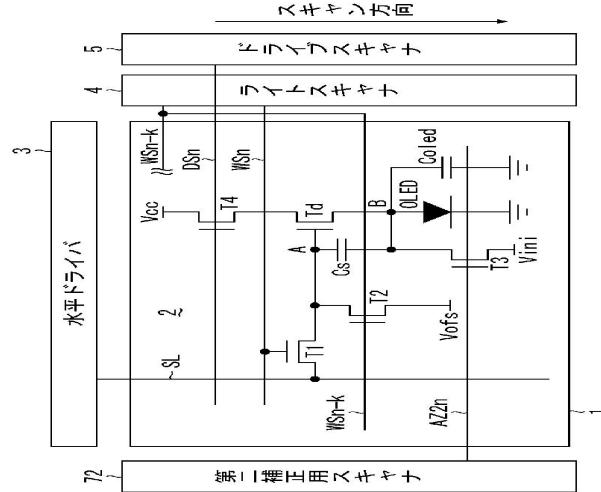

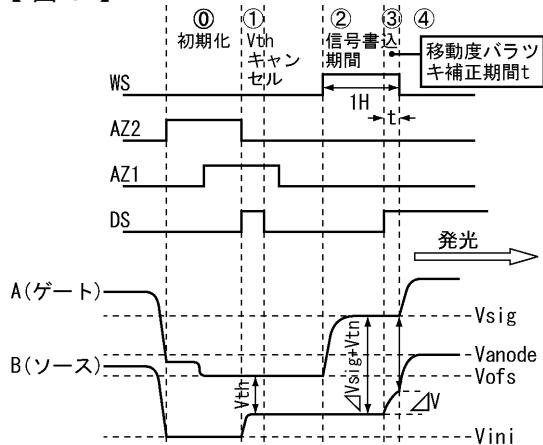

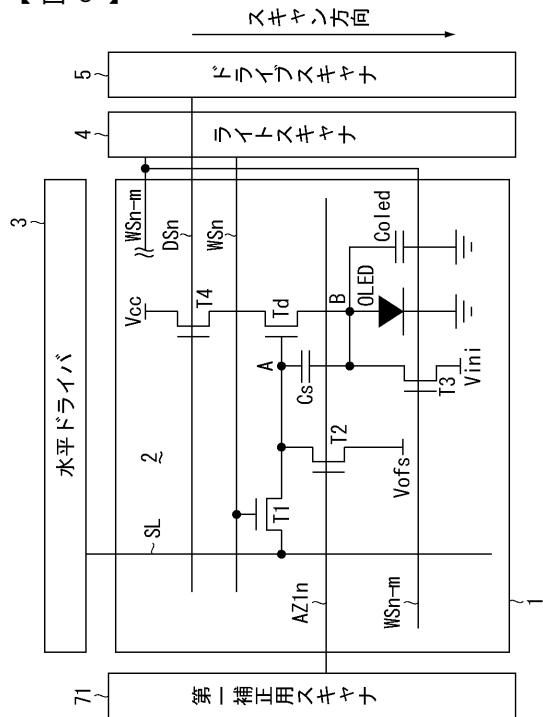

以上で本発明の元になった先行開発にかかる画像表示装置の説明を終わり、本発明にかかる画像表示装置の実施形態の説明に入る。図6は、本発明にかかる画像表示装置の第1実施形態を示すブロック図である。理解を容易にするため、図2に示した先行開発にかかる画像表示装置と対応する部分には対応する参照番号を付してある。図6は、特にn行目に位置する画素回路2を表しており、これを明記するためサンプリング用走査線WSに符号nを付けWSnと表している。同様に他の走査線についてもn行目であることを明示するため、nの符号をつけ、DSn及びAZ2nとしている。

30

## 【0028】

本実施形態の特徴として第1補正用スキャナ71が除かれており、これに対応する走査線AZ1nもない。その代わり、サンプリング用の走査線WSnと並行に走査線WSn-kが配されている。即ち基準電位設定トランジスタT2が、サンプリング用走査線WSn-kによって制御されている。WSn-kは、スキャン方向上からn-k行目のサンプリング用走査線WSから分岐していることを表している。ここでkは正の整数であり、走査方向は上から下と考えているので、サンプリング用走査線WSn-kは当該行のサンプリング用走査線WSnよりも時間的に早く高レベルになる。この様に本第一実施形態は、ライトスキャナ4をサンプリングトランジスタT1と基準電位設定トランジスタT2で併用することにより、第一補正用スキャナを不要とし、以って画素アレイ1の線順次走査に必要なスキャナの系統数を、先行開発例の4系統から3系統に削減している。

40

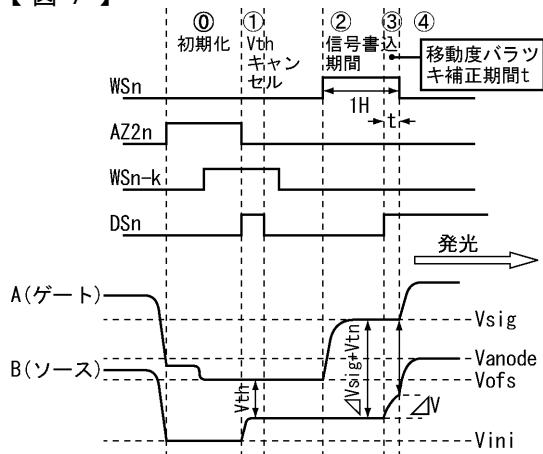

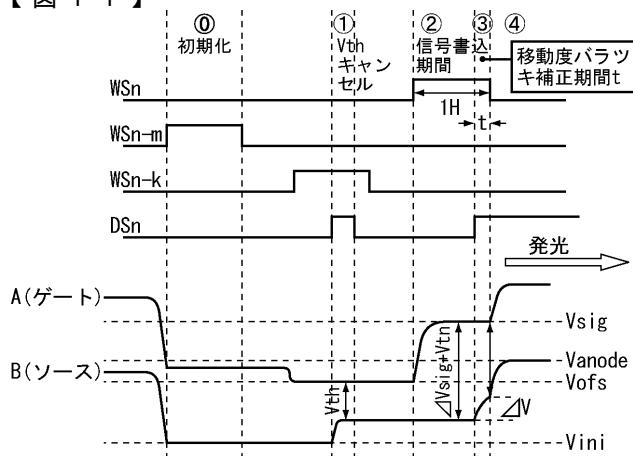

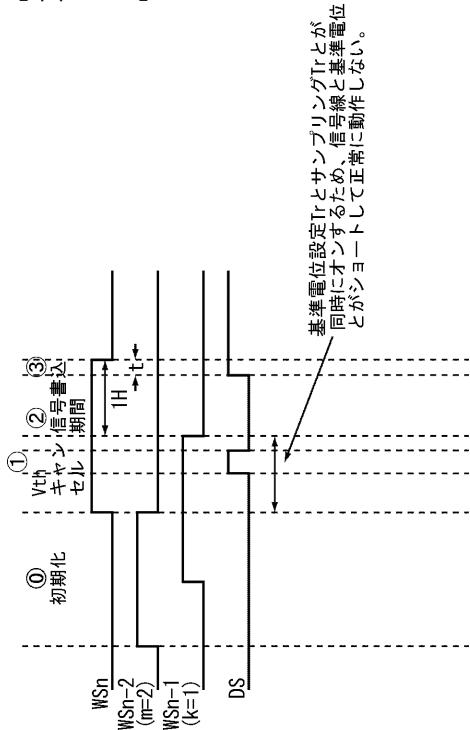

## 【0029】

図7は、図6に示した第一実施形態の動作説明に供するタイミングチャートである。理解を容易にするため図5に示した先行開発にかかる画像表示装置の動作説明に供したタイミングチャートと同様の表記を採用している。タイミングチャートから明らかなように、制御信号WSn-kは当該行の書き込み用制御信号WSnよりも先行して時間的に早く高レベルになる。よって信号書き込みステップ2よりも先行してVthキャンセルステップ1を行うことが出来る。これにより基準電位設定トランジスタT2専用のスキャナが不要になる為、画像表示装置の簡素化及び低コスト化が可能である。なお図7のタイミングチャートでは、ステップ3で移動度ばらつき補正を行っているが、このステップ3を行うか否かは任意であり、本発明はいずれの場合にも有効である。なお以下に説明する他の実施形態でも、移動度ばらつき補正ステップ3を行っているが、本発明は必ずしもこれに限られるものではなく、このステップ3を省略しても良い。

50

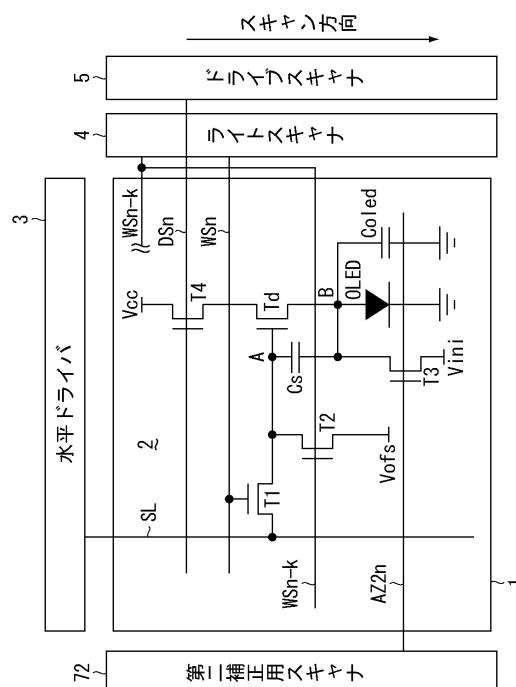

## 【 0 0 3 0 】

図 8 は本発明にかかる画像表示装置の第二実施形態を示すブロック図である。理解を容易にするため、図 6 に示した第一実施形態と対応する部分には対応する参照番号を付してある。第二実施形態において特徴的なのは、初期化トランジスタ T 3 が書き込み走査線 W S n - m によって、即ち上から n - m 行目の書き込み走査線 W S によって制御されていることである。これにより初期化トランジスタ T 3 を制御するための第二補正用スキャナが不要となり、合計のスキャナ系統数を 3 つにすることが出来る。

## 【 0 0 3 1 】

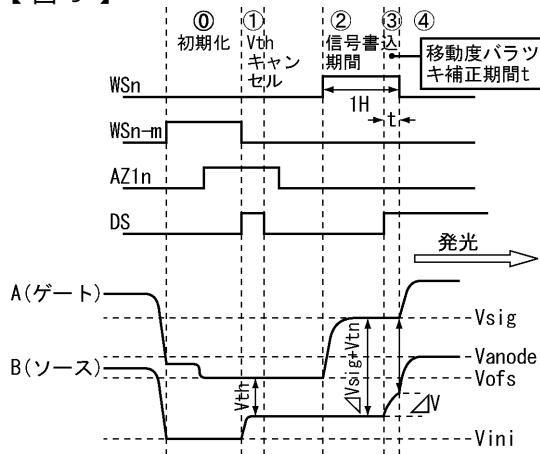

図 9 は、図 8 に示した第二実施形態にかかる画像表示装置の動作説明に供するタイミングチャートである。理解を容易にするため、第一実施形態のタイミングチャート図 7 と同様の表記を採用している。図示する様に、制御信号 W S n - m が最も先行しており、その後 A Z 1 n 、 D S n 、 W S n の順で高レベルとなり、ステップ 0 ないし 4 を順次実行する。ここで m は正の整数であり、走査方向は上から下と考えているので、タイミングチャートに示すように書き込み走査線 W S n - m は書き込み走査線 W S n よりも時間的に速く高レベルになる。初期化ステップ 0 はこの先行サンプリング用制御信号 W S n - m が高レベルとなることで実行され、ドライブトランジスタ T d のソースが V i n i に初期化される。初期化トランジスタ T 3 専用のスキャナが不要になる為、画像表示装置の簡素化及び低コスト化が可能である。

## 【 0 0 3 2 】

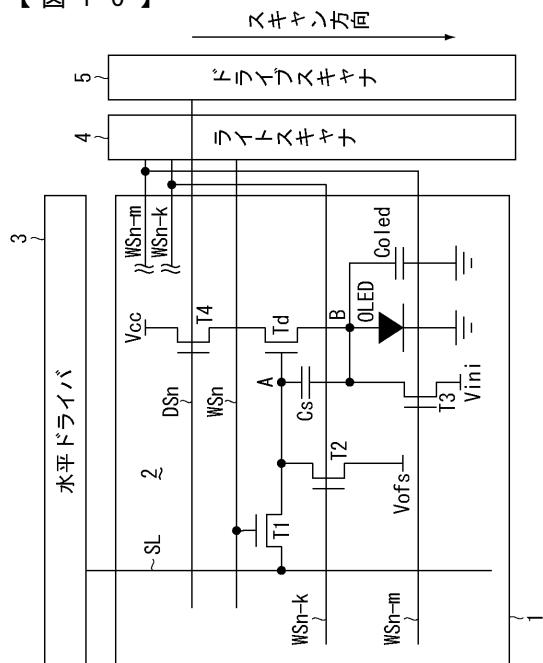

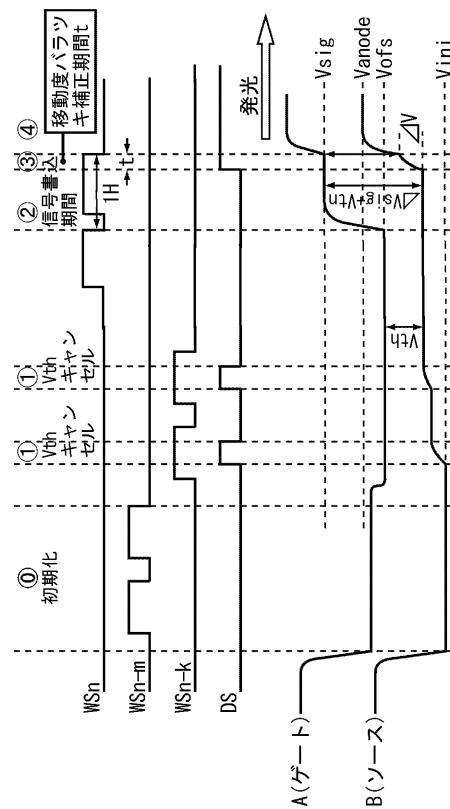

図 10 は、本発明にかかる画像表示装置の第三実施形態を示すブロック図である。理解を容易にするため、図 6 に示した第一実施形態と対応する部分には対応する参照番号を付してある。図 10 の実施形態において特徴的なのは、基準電位設定トランジスタ T 2 が、書き込み走査線 W S n - k によって、即ち上から n - k 行目の書き込み走査線 W S によって制御され、且つ初期化トランジスタ T 3 が、書き込み走査線 W S n - m によって、即ち上から n - m 行目の書き込み走査線 W S によって制御されている点である。これにより、スキャナの個数を 2 個削減できる。

## 【 0 0 3 3 】

図 11 は、図 10 に示した第三実施形態の動作説明に供するタイミングチャートである。理解を容易にするため、図 7 に示した第一実施形態のタイミングチャートと同じ表記を採用している。ライトスキャナ 4 から、順次制御信号 W S n - m 、 W S n - k 、 W S n が出力される。ここで k は正の整数、 m は k より大きい正の整数であり、走査方向は上から下と考えているので、書き込み走査線 W S n - k は当該行に割り当てられた書き込み走査線 W S n よりも時間的に早く高レベルになり、さらに書き込み走査線 W S n - m は書き込み走査線 W S n - k よりも時間的に早く高レベルになる。まず W S n - m が高レベルになったとき初期化ステップ 0 が行われ、ドライブトランジスタ T d のソースが V i n i に初期化される。続いて V t h キャンセルステップ 1 で、 W S n - k が高レベルとなり、ドライブトランジスタ T d のゲートが基準電位 V o f s に設定される。この状態で制御信号 D S n が高レベルとなる為、ドライブトランジスタ T d の閾電圧 V t h が画素容量 C s に書き込まれる。この後信号書き込みステップ 2 で当該行の走査線 W S n が高レベルとなるため、映像信号 V s i g が画素容量 C s に書き込まれる。この様に先行する書き込み用制御信号を利用することで V t h キャンセル動作を行うことが出来る。初期化トランジスタ用と基準電位設定トランジスタ用に専用のスキャナが不要となる為、画像表示装置の簡素化及び低コスト化が可能である。

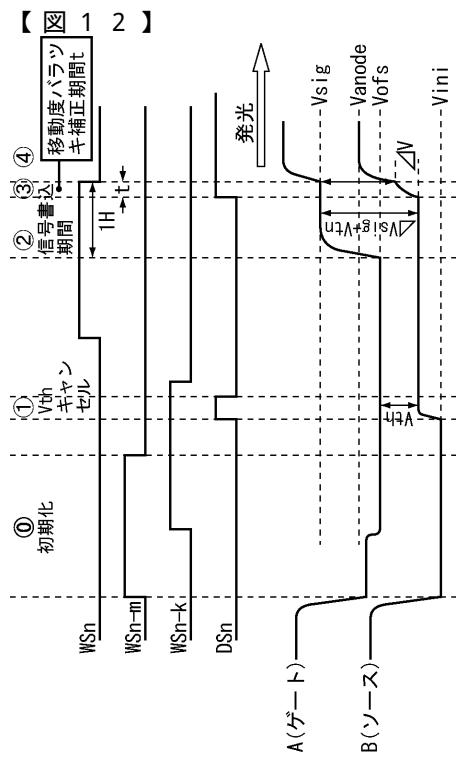

## 【 0 0 3 4 】

図 12 は、本発明にかかる画像表示装置の第四実施形態を示すタイミングチャートである。本実施形態の回路構成は第三実施形態と同じであり、図 10 に示した通りである。第三実施形態とは制御信号波形が異なっており、この点で図 12 のタイミングチャートが図 11 のタイミングチャートと相違している。図 11 に示した第三実施形態では書き込み走査線 W S の選択期間が 1 水平走査期間 ( 1 H ) に設定されているのに対し、本第四実施形態は書き込み走査線 W S の選択期間が 1 H よりも長く設定されていることである。即ちラ

10

20

30

40

50

イトスキャナから各書き込み走査線 WS に印加される制御信号（選択パルス）の幅は 1 H よりも長い。この結果初期化ステップ 0 で使われる初期化用制御信号 WS<sub>n-m</sub> のパルス幅も 1 H より長くなる。ドライブトランジスタ Td の初期化時間を 1 H よりも長く取ることが可能であり、より確実にドライブトランジスタ Td のソース電位を Vin に初期化できる。これにより Vth キャンセルステップ 1 における Vth キャンセル動作をより正確に行なうことが可能である。

なお、図 11 等のタイミングチャートにおいて、先に説明したように、m と k は、m > k を満たす正の整数であるべきである。典型的には m = 2、k = 1、すなわち基準電位設定トランジスタ T2 は当該行の前段の走査線 WS<sub>n-1</sub> によって制御され、初期化トランジスタ T3 は更にその前段の走査線 WS<sub>n-2</sub> によって制御されることが可能である。

10

しかるに図 12 のタイミングチャートにおいてはこの限りではないことに注意が必要である。すなわち図 12 では走査線の選択期間が 2 H であるため、m = 2、k = 1 とした場合、図 19 に示すように基準電位設定トランジスタ T2 とサンプリングトランジスタ T1 とが同時にオン状態となる期間が存在する。この場合基準電位 Vin と信号線とがショートして不正な貫通電流が流れ、正常な Vth キャンセル動作が行なわれない。

正しい動作が行なわれるためには基準電位設定トランジスタ T2 がオフ状態になった後にサンプリングトランジスタ T1 がオンする必要があるので、図 12 の実施例のように走査線の選択期間が 2 H である場合、k の値は 2 以上である必要がある。走査線の選択期間が 3 H 以上である場合はそれに応じて k の値を大きくする必要がある。

20

図 20 は図 12 の変形例である。この例では Vth キャンセルを 2 H に渡って行なっており、図 12 の例よりも確実な Vth キャンセル動作を行なうことが可能であるが、この場合も図 12 と同じ理由により、k の値は 2 以上である必要がある。実際には Vth キャンセルに長い時間を要しない場合もあるが、本例が示すように、k 及び m は大きな値とした方がタイミング設計の自由度が増大し、好ましい。

20

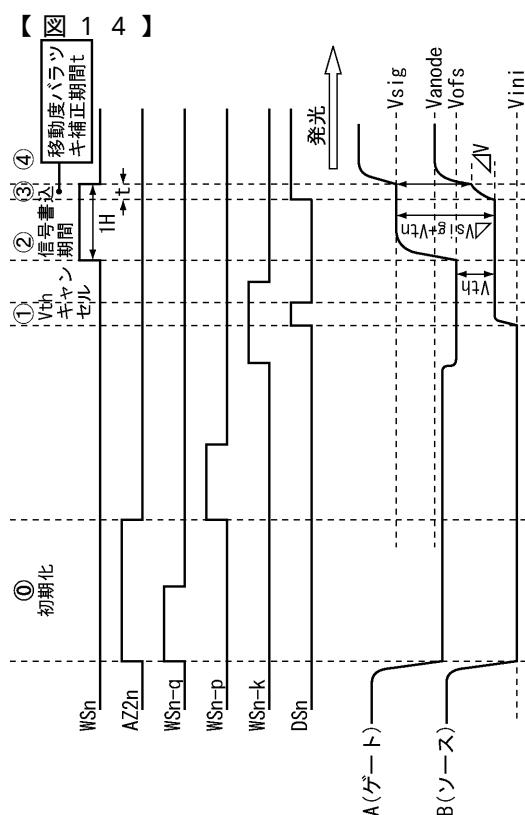

### 【0035】

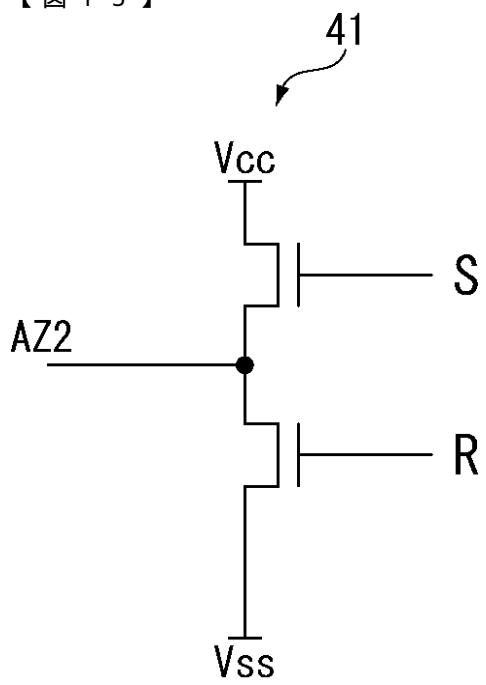

図 13 は、本発明にかかる画像表示装置の第五実施形態を示すブロック図である。基本的には図 10 に示した第三実施形態と類似しており、対応する部分には対応する参照番号を付して理解を容易にしている。第三実施形態と異なる点は、先行する行から分岐した走査線 WS<sub>n-m</sub> の代わりに、走査線 AZ<sub>2n</sub> を用いていることである。この AZ<sub>2n</sub> は SR フリップフロップ (SRFF) 41 を介してライトスキャナ 4 により制御されている。SR フリップフロップ 41 のセット端子 S には制御信号 WS<sub>n-q</sub> が供給され、リセット端子 R には同じく制御信号 WS<sub>n-p</sub> が供給されている。

30

### 【0036】

図 14 は、図 13 に示した第五実施形態の動作説明に供するタイミングチャートである。理解を容易にするため、第三実施形態のタイミングチャートである図 11 と同様の表記を用いている。図示する様に、ライトスキャナから、当該行の画素回路に対して、まず制御信号 WS<sub>n-q</sub> が出力され、次に WS<sub>n-p</sub> が出力され、続いて WS<sub>n-k</sub> が出力され、最後に当該行に割り当てられた WS<sub>n</sub> が出力される。ここで p は正の整数、q は p より大きな正の整数であり、走査方向は上から下と考えられるので、タイミングチャートに示すように、SR フリップフロップ 41 の出力、即ち、AZ<sub>2n</sub> は、書き込み走査線 WS<sub>n-q</sub> が高レベルとなった時点で高レベルになり、WS<sub>n-p</sub> が高レベルとなった時点で低レベルとなる。p と q の値の選び方によって、制御信号 AZ<sub>2n</sub> の高レベル期間（即ちパルス幅）は自在に設定することが出来る。従って初期化ステップ 0 における初期化時間を 1 H を超えて十分長く取ることが可能であり、より確実にドライブトランジスタ Td のソースの初期化動作を行なうことが出来る。

40

### 【0037】

図 15 は、図 13 の画像表示装置に含まれる SR フリップフロップ 41 の構成例を示す回路図である。この SR フリップフロップ 41 は一対の N チャネル型トランジスタを電源ライン Vcc と接地ライン Vss との間に直列接続したものであり、両トランジスタの接続点から出力信号 AZ<sub>2n</sub> が得られる。一方のトランジスタのゲートがセット端子 S となり

50

、制御信号 W S n - q が印加される。他方のトランジスタのゲートがリセット端子 R となり、ライトスキャナ 4 から制御信号 W S n - p が供給される。この S R フリップフロップ 4 1 は N チャネル型トランジスタのみで構成されるため、アモルファスシリコンプロセスでも形成可能である。

#### 【 0 0 3 8 】

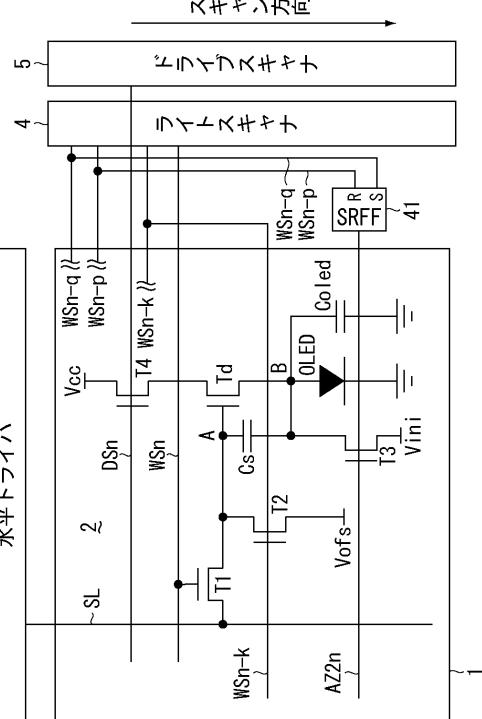

図 1 6 は、本発明にかかる画像表示装置の第六実施形態を示すブロック図である。基本的には図 1 0 に示した第三実施形態と類似しており、理解を容易にするため対応する部分には対応する参照符号を用いている。異なる点は、スイッチングトランジスタ T 4 が除かれており、画素回路 2 が合計 4 個のトランジスタ T 1 , T 2 , T 3 , T d で構成されていることである。構成トランジスタの個数が 5 個から 4 個に削減されており、その分歩留りの改善に寄与できる。スイッチングトランジスタ T 4 の削除に対応するため、単純な電源ライン V c c に代えて電源駆動線 D S n が画素回路 2 に配線されている。この電源駆動線 D S n はドライブスキャナ 5 によって走査線と同様に制御される。この電源駆動線 D S n は各発光期間に電源電圧 V c c を供給し、ドライブトランジスタ T d は、そのドレインが対応する電源駆動線 D S n に接続されており、電源電圧に応じて出力電流 I d s を発光素子 O L E D に供給する。なお第三実施形態で使われたスイッチングトランジスタ T 4 は、ドライブトランジスタ T d のドレインと所定の電源ライン V c c との間に接続され、発光期間中制御信号 D S に応答して導通し、ドライブトランジスタ T d を電源ライン V c c に接続することで発光素子 O L E D に出力電流 I d s を流す様にしている。

#### 【 0 0 3 9 】

図 1 7 は、図 1 6 に示した第六実施形態にかかる画像表示装置から、1 画素回路分を切り取って示した回路図である。

#### 【 0 0 4 0 】

図 1 8 は、図 1 6 に示した第六実施形態にかかる画像表示装置の動作説明に供するタイミングチャートである。理解を容易にするため、図 1 1 に示した第三実施形態のタイミングチャートと対応する表記を用いている。図示する様に V t h キャンセルステップ 1 、移動度ばらつき補正ステップ 3 及び発光ステップ 4 で、電源駆動線 D S が高レベルとなり、動作に必要な電源を供給する。それ以外のタイミングにおいて電源駆動線 D S は低レベルもしくはハイインピーダンス状態となって、ドライブトランジスタ T d に流れる電流を遮断する。これによりスイッチングトランジスタ T 4 が不要になる。その他の面では、前述した第三実施形態と同様、初期化トランジスタ用及び基準電位設定トランジスタ用の専用スキャナが不要となる為、画像表示装置の簡素化及び低コスト化が出来る。

#### 【 図面の簡単な説明 】

#### 【 0 0 4 1 】

【 図 1 】従来の画素回路の一例を示す回路図である。

【 図 2 】先行開発にかかる画像表示装置を示すブロック図である。

【 図 3 】図 2 に示した画像表示装置に含まれる画素回路の回路図である。

【 図 4 】図 2 に示した先行開発にかかる画像表示装置の動作説明に供するタイミングチャートである。

【 図 5 】同じく先行開発にかかる画像表示装置の動作説明に供する別のタイミングチャートである。

【 図 6 】本発明にかかる画像表示装置の第一実施形態を示すブロック図である。

【 図 7 】第一実施形態の動作説明に供するタイミングチャートである。

【 図 8 】本発明にかかる画像表示装置の第二実施形態を示すブロック図である。

【 図 9 】第二実施形態の動作説明に供するタイミングチャートである。

【 図 1 0 】本発明にかかる画像表示装置の第三実施形態を示すブロック図である。

【 図 1 1 】第三実施形態の動作説明に供するタイミングチャートである。

【 図 1 2 】第四実施形態の動作説明に供するタイミングチャートである。

【 図 1 3 】本発明にかかる画像表示装置の第五実施形態を示すブロック図である。

【 図 1 4 】第五実施形態の動作説明に供するタイミングチャートである。

10

20

30

40

50

【図15】第五実施形態に含まれるフリップフロップの構成例を示す回路図である。

【図16】本発明にかかる画像表示装置の第六実施形態を示すプロック図である。

【図17】同じく第六実施形態の画素回路図である。

【図18】第六実施形態の動作説明に供するタイミングチャートである。

【図19】第四実施形態に対比すべき参考例を示すタイミングチャートである。

【図20】第四実施形態の変形例を示すタイミングチャートである。

【符号の説明】

【0042】

1 . . . 画素アレイ、2 . . . 画素回路、3 . . . 水平ドライバ、4 . . . ライトスキャナ、5 . . . ドライブスキャナ、71 . . . 第一補正用スキャナ、72 . . . 第二補正用スキャナ、T1 . . . サンプリングトランジスタ、T2 . . . 基準電圧設定トランジスタ、T3 . . . 初期化トランジスタ、T4 . . . スイッチングトランジスタ、Td . . . ドライブトランジスタ、OLED . . . 発光素子、Cs . . . 画素容量

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【 図 1 3 】

【 図 1 5 】

【図16】

【 図 1 9 】

【 図 1 7 】

【図18

【 囮 2 0 】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 3 A |

| G 0 9 G | 3/20  | 6 2 2 C |

| H 0 5 B | 33/14 | A       |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 画像表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2007316454A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2007-12-06 |

| 申请号            | JP2006147536                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 申请日     | 2006-05-29 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 湯本昭                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 湯本 昭                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| CPC分类号         | G09G3/3233 G09G2300/043 G09G2300/0819 G09G2300/0861 G09G2300/0866 G09G2320/0233 G09G2320/043 G09G3/32 G09G3/3225 G09G5/18 G09G2300/0404 G09G2310/0267                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| FI分类号          | G09G3/30.J G09G3/30.K G09G3/20.624.B G09G3/20.611.H G09G3/20.622.A G09G3/20.623.A G09G3 /20.622.C H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/CC45 3K107/HH04 3K107/HH05 5C080/AA06 5C080 /BB05 5C080/DD05 5C080/DD22 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/AB22 5C380/AB24 5C380/BA13 5C380/BA28 5C380/BA29 5C380 /BA34 5C380/BA38 5C380/BA39 5C380/BB02 5C380/CA12 5C380/CB01 5C380/CB17 5C380/CB20 5C380/CB26 5C380/CB27 5C380/CC02 5C380/CC03 5C380/CC04 5C380/CC07 5C380/CC26 5C380 /CC27 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC41 5C380/CC55 5C380/CC61 5C380/CC62 5C380/CC64 5C380/CC65 5C380/CD012 5C380/CD024 5C380/CD025 5C380/CF10 5C380/DA02 5C380/DA06 5C380/DA47 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

### 摘要(译)

要解决的问题：减少扫描仪的数量，同时具有抵消驱动晶体管的阈值电压Vth的变化的功能。所述的像素电路2中，从导通到信号线SL，响应于从扫描线WSN采样周期用于采样像素电容器Cs提供的控制信号提供的视频信号的采样晶体管T1。驱动晶体管Td将与采样的视频信号对应的输出电流提供给发光元件OLED。此外，像素电路2包括晶体管T2，用于抵消连接到驱动晶体管Td的栅极的阈值电压Vth。晶体管T2是通过施加到扫描线WSN-k行时间上先行的控制信号接通和关断操作，推进驱动器晶体管的栅极的基准电位Td的之前的视频信号的采样它被设置为。点域6