(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-309924

(P2004-309924A)

(43) 公開日 平成16年11月4日(2004.11.4)

(51) Int.Cl.<sup>7</sup>**G09G 3/30****G09G 3/20****H05B 33/14**

F 1

G09G 3/30

J

テーマコード(参考)

3K007

G09G 3/30

K

5C080

G09G 3/20

611J

G09G 3/20

623C

G09G 3/20

623D

審査請求有 請求項の数 43 O L (全 44 頁) 最終頁に続く

(21) 出願番号

特願2003-105694(P2003-105694)

(22) 出願日

平成15年4月9日(2003.4.9)

(71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100094134

弁理士 小山 廣毅

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

最終頁に続く

(54) 【発明の名称】表示装置、ソース駆動回路、及び表示パネル

## (57) 【要約】

【課題】表示輝度の変化時にも画質を低下をきたさずに、高解像度の表示を可能にする電流駆動型の表示装置を提供する。

【解決手段】有機EL表示装置は、複数の画素5が形成された表示パネルと、画素5に駆動電流を流すための電流駆動部11と、データ信号をラッチするためのレジスタ7と、タイミング制御部9とを有する画素駆動部1が設けられているソース駆動回路と、電流駆動部11からの駆動電流を画素5に供給する信号線とを備えている。電流駆動部11は、電流設定時の所定の期間のみデータ信号によって設定された電流以上の電流を流すようにタイミング制御部9に制御されることにより、画素5に流れる電流の値を迅速に目標値に到達させることができる。

【選択図】

図1

**【特許請求の範囲】****【請求項 1】**

電流により駆動される発光素子を含む画素と、上記画素に接続された信号線とが設けられた表示パネルと、

上記信号線を介して上記画素に駆動電流を供給するためのソース駆動回路と

を備えている表示装置であって、

上記ソース駆動回路は、

Nビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、

制御信号を出力するためのタイミング制御部と、

上記制御信号に従って、電流設定時の所定の期間には任意に設定した上記駆動電流を流し

10

、上記所定の期間以外の動作時には上記レジスタからの表示データにより設定される上記

駆動電流を流す電流駆動部と

を有している、表示装置。

**【請求項 2】**

請求項 1 に記載の表示装置において、

電流設定時の所定の期間には、上記レジスタからの上記表示データにより設定される電流

値以上の上記駆動電流が上記電流駆動部から出力される、表示装置。

**【請求項 3】**

請求項 1 または 2 に記載の表示装置において、

上記電流駆動部は、

上記表示データのビットに応じた電流を出力するための N 個の電流源を有する電流加算型

の D / A コンバータと、

任意に設定した値の電流を出力するための付加電流源と、

上記制御信号を受けて、上記付加電流源と上記画素とを電流設定時の所定の期間のみ導通

させる第 1 のスイッチと

を有している、表示装置。

**【請求項 4】**

請求項 3 に記載の表示装置において、

上記 D / A コンバータ内の N 個の電流源は、それぞれ互いにカレントミラー回路を構成す

る M I S F E T からなっており、

上記付加電流源は、上記 N 個の電流源を構成する M I S トランジスタとカレントミラー回

路を構成する M I S F E T からなっている、表示装置。

**【請求項 5】**

請求項 3 または 4 に記載の表示装置において、

上記付加電流源は上記表示データを受けて、上記表示データのビットに応じた電流を出力

可能であることを特徴とする表示装置。

**【請求項 6】**

請求項 1 または 2 に記載の表示装置において、

上記駆動電流部は、

上記表示データのビットに応じた電流を出力するための N 個の電流源と、

上記 N 個の電流源を流れる電流の各出力経路上にそれぞれ介設された第 2 のスイッチと、

上記 N 個の電流源のそれぞれを流れる電流を上記第 2 のスイッチを迂回して出力するため

の N 本のバイパス経路と、

上記 N 本のバイパス経路のそれぞれの経路上に介設された第 3 のスイッチと

を有する電流加算型の D / A コンバータであり、

電流設定時の所定の期間中は、上記制御信号によって、上記第 3 のスイッチがオン状態に

設定され、上記所定の期間以外の動作時には上記第 3 のスイッチがオフ状態に設定される

、表示装置。

**【請求項 7】**

請求項 1 または 2 に記載の表示装置において、

10

20

30

40

50

電流設定時の所定の期間中、上記電流駆動部から出力される電流の値は、段階的に変化する、表示装置。

【請求項 8】

請求項 7 に記載の表示装置において、

上記駆動電流部は、

上記表示データのビットに応じた電流を出力するための N 個の電流源と、

上記 N 個の電流源を流れる電流の各出力経路上にそれぞれ介設された第 2 のスイッチと、上記 N 個の電流源のそれぞれを流れる電流を上記第 2 のスイッチを迂回して出力するための N 本のバイパス経路と、

上記 N 本のバイパス経路のそれぞれの経路上に介設された第 3 のスイッチとを有する電流加算型の D / A コンバータであり、10

電流設定時の所定の期間中は、上記制御信号によって上記第 3 のスイッチがオン状態に設定された後、上記 N 個の電流源のうち、上位ビット用の電流源に接続された上記第 3 のスイッチから段階的にオフ状態に切り替わるよう設定される、表示装置。

【請求項 9】

請求項 7 または 8 に記載の表示装置において、

電流設定時に上記タイミング制御部が上記第 3 のスイッチに出力する制御信号は、互いにタイミングをずらした複数の制御信号である、表示装置。

【請求項 10】

請求項 1 ~ 4 のうちいずれか 1 つに記載の表示装置において、20

ソース駆動回路は、

所定の電圧を出力するための電圧設定手段と、

上記電圧設定手段の出力電圧と上記電流駆動部の出力電圧とを比較し、比較結果を上記タイミング制御部に出力するための比較回路と

をさらに有し、

上記所定の期間中に上記電流駆動部から任意に設定した上記駆動電流が流れる際に、少なくとも上記電流駆動部の出力電圧が上記電圧設定手段の出力電圧と一致した時点で、上記駆動電流の値が上記表示データにより設定される電流値に切り替わるよう設定される、表示装置。

【請求項 11】

請求項 10 に記載の表示装置において、30

上記電圧設定手段が出力する上記所定の電圧は、

電流設定時に上記画素に流れる電流の値が目標値に到達する際の上記電流駆動部の出力電圧である安定出力電圧である、表示装置。

【請求項 12】

請求項 10 または 11 に記載の表示装置において、

上記電圧設定手段は、上記安定出力電圧を任意に設定するために設定データをラッチするレジスタを有している、表示装置。

【請求項 13】

請求項 10 または 11 に記載の表示装置において、40

上記電圧設定手段は、

上記表示パネル上に設けられ、TFT 及び容量を有し、画像表示に関係しないダミー画素と、上記表示パネル上に設けられ、上記ダミー画素に電流を供給するためのダミー信号線と、上記ソース駆動回路内に設けられると共に上記ダミー信号線及び上記比較回路に接続され、動作時を通して一定値の電流を出力するダミー電流駆動部を含むダミー画素駆動部とを有するダミー回路である、表示装置。

【請求項 14】

請求項 13 に記載の表示装置において、

上記ダミー回路は、複数個の上記電流駆動部に対して 1 つの割合で設けられている、表示装置。50

**【請求項 15】**

請求項 14 に記載の表示装置において、

上記ソース駆動回路は、互いに同一の構成を有する複数の半導体チップ上に分かれて設けられており、

上記複数の半導体チップのそれぞれには、上記ダミー画素駆動部が設けられている、表示装置。

**【請求項 16】**

請求項 13 ~ 15 のうちいずれか 1 つに記載の表示装置において、

上記ダミー回路は複数個存在し、複数の上記ダミー回路内のダミー電流駆動部同士は、少なくとも電流設定時の所定の期間互いに接続されている、表示装置。 10

**【請求項 17】**

請求項 10 ~ 16 のうちいずれか 1 つに記載の表示装置において、

上記比較回路は差動増幅回路を有するコンパレータである、表示装置。

**【請求項 18】**

電流により駆動される発光素子を含む画素と、上記画素に接続された信号線とが設けられた表示パネルと、

上記信号線を介して上記画素を流れる駆動電流を設定するためのソース駆動回路とを備えている表示装置であって、

上記信号線は、上記画素に流れる駆動電流を設定するための駆動電圧用信号線と、上記画素の駆動電流を伝達するための駆動電流用信号線とに分かれており、 20

上記ソース駆動回路は、上記駆動電圧用信号線を介して上記画素に駆動電圧を供給するための電圧駆動部と、上記駆動電流用信号線を介して上記画素の駆動電流を流すための電流供給手段とを有している、表示装置。

**【請求項 19】**

請求項 18 に記載の表示装置において、

上記電流供給手段は、上記画素から流れる駆動電流の値を検出し、検出結果を上記電圧駆動部にフィードバックするための電流値検出部であり、

上記ソース駆動回路には、表示データをラッチし、且つ上記表示データを上記電流値検出部へ入力するためのレジスタがさらに設けられている、表示装置。 30

**【請求項 20】**

請求項 19 に記載の表示装置において、

上記電流値検出部は、上記駆動電流用信号線に接続され、上記表示データに応じて出力電流の値を変更可能な電流駆動部と、上記電流駆動部と上記駆動電流用信号線との接続経路上に介設された抵抗素子とを有し、

上記電流駆動部と上記抵抗素子との間に生じる電圧が、上記検出結果として上記電圧駆動部に入力される、表示装置。

**【請求項 21】**

請求項 18 ~ 20 のうちいずれか 1 つに記載の表示装置において、

上記電圧駆動部と上記電流供給手段とを電流設定時の所定の期間のみ短絡させるための短絡手段をさらに備えている、表示装置。 40

**【請求項 22】**

請求項 18 ~ 21 のうちいずれか 1 つに記載の表示装置において、

上記画素は、

上記発光素子と、

ゲート電極が上記駆動電圧用信号線に一時的に接続され、ドレインが上記駆動電流用信号線に一時的に接続され、上記発光素子に電流を供給するための電流源として機能する M I S F E T と、

上記駆動電圧用信号線に一時的に接続され、且つ上記 M I S F E T のゲート電極に接続される画素入力容量と、

上記画素入力容量と上記 M I S F E T のゲート電極との接続点と上記駆動電圧用信号線と 50

の接続経路上に介設された電圧用スイッチと、

上記M I S F E Tと上記発光素子との間に介設され、上記駆動電流用信号線に一時的に接続されるスイッチと、

上記スイッチと上記M I S F E Tとの接続点と上記駆動電流用信号線との間に介設された電流用スイッチとを備え、

上記電圧用スイッチ及び上記電流用スイッチは、電流設定時にオンになり、表示時にはオフになるように制御され、

上記スイッチは、電流設定時にオフとなり、表示時にはオンとなるよう制御されている、表示装置。

**【請求項 2 3】**

電流により駆動される発光素子を含む画素と、上記画素に接続された信号線とが設けられた表示パネルと、

上記信号線を介して上記画素を流れる駆動電流を設定するためのソース駆動回路とを備えている表示装置であって、

上記画素は、

上記発光素子と、

ゲート電極が上記駆動電圧用信号線に一時的に接続され、ドレインが上記駆動電流用信号線に一時的に接続され、上記発光素子に電流を供給するための電流源として機能するM I S F E Tと、

上記駆動電圧用信号線に一時的に接続され、且つ上記M I S F E Tのゲート電極に接続される画素入力容量と、

上記画素入力容量と上記M I S F E Tのゲート電極との接続点と上記駆動電圧用信号線との接続経路上に介設された電圧用スイッチと、

上記M I S F E Tと上記発光素子との間に介設され、上記駆動電流用信号線に一時的に接続されるスイッチと、

上記スイッチと上記M I S F E Tとの接続点と上記駆動電流用信号線との間に介設された電流用スイッチとを備えており、

上記電圧用スイッチ及び上記電流用スイッチは、電流設定時にオンになり、表示時にはオフになるように制御され、

上記スイッチは、電流設定時にオフとなり、表示時にはオンとなるよう制御されている、表示装置。

**【請求項 2 4】**

電流により駆動される発光素子を含む画素と、上記画素に接続された信号線とが設けられた表示パネルと、

上記信号線を介して上記画素に駆動電流を供給するためのソース駆動回路とを備えている表示装置であって、

上記ソース駆動回路は、

Nビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、上記レジスタから入力される上記表示データに応じた上記駆動電流を出力するための電流駆動部と、

上記電流駆動部よりも出力インピーダンスの低い電圧供給手段と、

上記信号線と上記電圧供給手段とを接続するための配線と、

制御信号を出力するためのタイミング制御部と、

上記配線上に設けられ、上記制御信号に従って、電流設定時の所定の期間のみ上記信号線と上記電圧供給手段とを導通させる短絡用スイッチと

を有している、表示装置。

**【請求項 2 5】**

請求項 2 4 に記載の表示装置において、

上記電圧供給手段は、

上記表示パネル上に設けられ、TFT 及び容量を有し、画像表示に関係しないダミー画素

10

20

30

40

50

と、上記表示パネル上に設けられ、上記ダミー画素に電流を供給するためのダミー信号線と、上記ソース駆動回路内に設けられ、且つ上記ダミー信号線に接続され、動作時を通して一定値の電流を出力するダミー電流駆動部を含むダミー画素駆動部とを有するダミー回路と、

上記ダミー電流駆動部に接続され、上記ダミー電流駆動部からの出力電圧を上記信号線に出力するための電流増幅用バッファと

から構成されている、表示装置。

#### 【請求項 26】

請求項 24 または 25 に記載の表示装置において、

上記電圧供給手段は、複数個の上記電流駆動部に対して 1 つの割合で設けられている、表示装置。 10

#### 【請求項 27】

請求項 24 に記載の表示装置において、

上記電圧供給手段は、上記電流駆動部毎に設けられ、上記レジスタから出力される表示データに応じて出力電圧を変えることができる電圧出力型の D / A コンバータである、表示装置。

#### 【請求項 28】

請求項 27 に記載の表示装置において、

上記電圧出力型の D / A コンバータは、上記表示データのうち上位 1 または 2 ビットに応じて出力電圧を変える、表示装置。 20

#### 【請求項 29】

請求項 24 または 25 に記載の表示装置において、

上記電圧供給手段は、外部電源に接続された配線である、表示装置。

#### 【請求項 30】

電流により駆動される発光素子を含む画素と、上記画素に接続された信号線とが設けられた表示パネルと、

上記信号線を介して上記画素に駆動電流を供給するためのソース駆動回路と

を備えている表示装置であって、

上記ソース駆動回路は、

N ビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、

電流設定時の所定の期間に上記レジスタから入力された上記表示データに M ビットを加算

して ( N + M ) ビットの表示データを出力するためのビットデータ加算手段と、

制御信号を出力するためのタイミング制御部と、 30

上記制御信号に従って、電流設定時の所定の期間には上記 ( N + M ) ビットの表示データ

により設定される上記駆動電流を流し、上記所定の期間以外の動作時には N ビットの上記

表示データにより設定される上記駆動電流を流す電流駆動部と

を有している、表示装置。

#### 【請求項 31】

請求項 30 に記載の表示装置において、

上記 M ビットは 1 または 2 ビットである、表示装置。 40

#### 【請求項 32】

電流により駆動される発光素子を含む画素と、上記画素に接続された信号線とが設けられた表示パネルと、

N ビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、上

記表示データのビットに応じた駆動電流を上記信号線に出力する電流駆動部と、上記電流

駆動部に基準電流を供給するための基準電流生成部とを有するソース駆動回路と

を備えている表示装置であって、

上記電流駆動部は、それぞれ互いにカレントミラー回路を構成する M I S F E T から構成

される N 個の電流源を有し、

上記基準電流生成部は、ソースに電源電圧が供給され、上記基準電流を流すための第 1 の 50

MISFETと、上記第1のMISFETのドレインに接続され、上記表示データが入力された際には、上記表示データにより抵抗値が変化する可変抵抗と、上記第1のMISFETとカレントミラー回路を構成する第2のMISFETと、上記第2のMISFETに接続され、上記N個の電流源のそれぞれにカレントミラーを介して上記基準電流を供給するための第3のMISFETとを有し、

上記レジスタから出力される上記表示データは、電流設定時の所定の期間に上記可変抵抗に入力される、表示装置。

**【請求項33】**

Nビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、制御信号を出力するためのタイミング制御部と、

上記制御信号に従って、電流設定時の所定の期間には上記表示データにより設定される電流以上の上記駆動電流を流し、上記所定の期間以外の動作時には上記レジスタからの表示データにより設定される上記駆動電流を流す電流駆動部と

を備えているソース駆動回路。

**【請求項34】**

請求項33に記載のソース駆動回路において、

所定の電圧を出力するための電圧設定手段と、

上記電圧設定手段の出力電圧と上記電流駆動部の出力電圧とを比較し、比較結果を上記タイミング制御部に出力するための比較回路と

をさらに有し、

上記所定の期間中に、上記表示データにより設定される電流値以上の上記駆動電流が上記電流駆動部から流れる際に、少なくとも上記電流駆動部の出力電圧が上記電圧設定手段の出力電圧と一致した時点で、上記駆動電流の値が上記表示データにより設定される電流値に切り替わるよう設定される、ソース駆動回路。

**【請求項35】**

電圧を供給するための電圧駆動部と、

表示データをラッチし、且つ出力するためのレジスタと、

上記レジスタから出力される上記表示データが入力され、上記表示データに応じた電流を流すための電流供給手段と

を備えているソース駆動回路。

**【請求項36】**

請求項35に記載のソース駆動回路において、

上記電流供給手段は、

出力電流の値を検出し、検出結果を上記電圧駆動部にフィードバックするための電流値検出部である、ソース駆動回路。

**【請求項37】**

請求項35または36に記載のソース駆動回路において、

上記電圧駆動部と上記電流供給手段とを電流設定時の所定の期間のみ短絡させるための短絡手段をさらに備えている、ソース駆動回路。

**【請求項38】**

Nビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、

上記レジスタから入力される上記表示データに応じた上記駆動電流を出力するための出力部を有する電流駆動部と、

上記電流駆動部よりも出力インピーダンスの低い電圧供給手段と、

上記電流駆動部の出力部と上記電圧供給手段とを接続するための配線と、

制御信号を出力するためのタイミング制御部と、

上記配線上に設けられ、上記制御信号に従って、電流設定時の所定の期間のみ上記信号線と上記電圧供給手段とを導通させる短絡用スイッチと

を備えているソース駆動回路。

**【請求項39】**

10

20

30

40

50

Nビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、電流設定時の所定の期間に上記レジスタから入力された上記表示データにMビットを加算して(N+M)ビットの表示データを出力するためのビットデータ加算手段と、制御信号を出力するためのタイミング制御部と、

上記制御信号に従って、電流設定時の所定の期間には上記(N+M)ビットの表示データにより設定される電流を流し、上記所定の期間以外の動作時にはNビットの上記表示データにより設定される電流を流す電流駆動部と

を備えているソース駆動回路。

## 【請求項40】

Nビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、

上記表示データのビットに応じた駆動電流を上記信号線に出力する電流駆動部と、

上記電流駆動部に基準電流を供給するための基準電流生成部とを備えているソース駆動回路であって、

上記電流駆動部は、それぞれ互いにカレントミラー回路を構成するMISFETから構成されるN個の電流源を有し、

上記基準電流生成部は、ソースに電源電圧が供給され、上記基準電流を流すための第1のMISFETと、上記第1のMISFETのドレインに接続され、上記表示データが入力された際には、上記表示データにより抵抗値が変化する可変抵抗と、上記第1のMISFETとカレントミラー回路を構成する第2のMISFETと、上記第2のMISFETに接続され、上記N個の電流源のそれぞれにカレントミラーを介して上記基準電流を供給するための第3のMISFETとを有し、

上記レジスタから出力される上記表示データは、電流設定時の所定の期間に上記可変抵抗に入力される、ソース駆動回路。

## 【請求項41】

電流により駆動される発光素子を含む画素と、

上記画素に接続された信号線と、

画像表示に関係しないダミー画素と、

上記ダミー画素に接続されたダミー信号線と

を備えている表示パネル。

## 【請求項42】

電流により駆動される発光素子を含み、電圧及び電流によって駆動される画素と、

上記画素に駆動電圧を供給するための駆動電圧用信号線と、

上記画素の駆動電流を出力するための駆動電流用信号線と

を備えている表示パネル。

## 【請求項43】

請求項42に記載の表示パネルにおいて、

ゲート電極が上記駆動電圧用信号線に一時的に接続され、ドレインが上記駆動電流用信号線に一時的に接続され、上記発光素子に電流を供給するための電流源として機能するMISFETと、

上記駆動電圧用信号線に一時的に接続され、且つ上記MISFETのゲート電極に接続される画素入力容量と、

上記画素入力容量と上記MISFETのゲート電極との接続点と上記駆動電圧用信号線との接続経路上に介設された電圧用スイッチと、

上記MISFETと上記発光素子との間に介設され、上記駆動電流用信号線に一時的に接続されるスイッチと、

上記スイッチと上記MISFETとの接続点と上記駆動電流用信号線との間に介設された電流用スイッチと

をさらに備え、

上記スイッチは、電流設定時にオフとなり、表示時にはオンとなるよう制御されている、

表示パネル。

10

20

30

40

50

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は、有機EL( Electro luminescence )などの電流駆動型の発光素子を有する表示装置と、該表示装置に用いられるソース駆動回路、及び表示パネルに関する。

## 【0002】

## 【従来の技術】

一般に、アクティブマトリクス型の画像表示装置では、多数の画素をマトリクス状に並べ、与えられた輝度情報に応じて画素ごとに光の強度を制御することによって画像を表示する。そのため、例えば長方形形状のディスプレイパネルは、マトリクス状に並べられ、液晶または光学物質の状態を制御するTFT(Thin-Film-Transistor)と、パネルの上下辺に沿って設けられたソース駆動回路と、パネルの側端部に設けられたゲートドライバとを有している。

## 【0003】

従来、ディスプレイパネル等の画像表示装置では、光学物質として液晶を用いたものが主流であった。これらの画像表示装置では、ソース駆動回路である液晶ドライバが電圧の形で表示情報を各画素に供給し、この表示情報に応じて画素の透過率を変化させていた。

## 【0004】

これに対し、近年、有機EL( Electro Luminescence )を発光素子として用いた画像表示装置の開発が活発に行われている。有機ELは、液晶とは異なりそれ自体が発光するので、これを用いたディスプレイパネルは視認性が高い上、バックライトが不要になるという利点がある。ディスプレイパネルに用いられる有機ELはダイオードの機能を有し、電流を与えられることで発光する。

## 【0005】

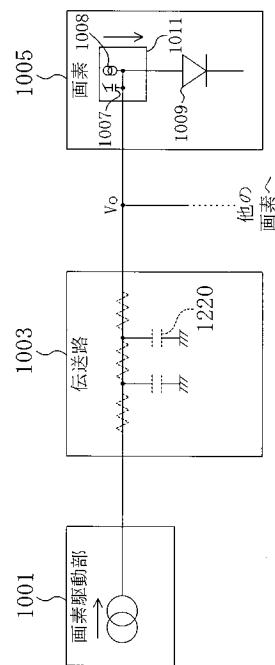

図23は、従来の有機EL表示装置の構成を概略的に示すブロック回路図である。

## 【0006】

同図に示すように、従来の有機EL表示装置は、表示パネルと、表示パネル上に設けられた画素1005と、画素1005に接続された伝送路1003と、ソース駆動回路に含まれ、伝送路1003を介して画素1005に駆動電流を供給するための画素駆動部1001とを備えている。ここで、伝送路1003には、ソース駆動回路と表示パネルとを接続する配線と、表示パネル上に設けられた信号線とが含まれる。図23の伝送路1005中には抵抗や容量が示されているが、これは配線抵抗や浮遊容量を示したものである。

## 【0007】

また、画素駆動部1001は複数の電流源を有しており、これら電流源のうち、導通状態にあるものからの電流の合計が、出力電流として各信号線に接続された画素1005に供給される。

## 【0008】

画素1005は、画素入力容量1007及び電流源1008を有する電流発生部1011と、電流源1008に接続された有機EL素子1009とを有している。なお、図23で示す「画素」は、実際にはR(赤)、G(緑)、B(青)をそれぞれ表示する3つのサブピクセルから構成されている。

## 【0009】

次に、画素駆動部と画素の構成と、有機EL表示装置の黑白表示について説明する。

## 【0010】

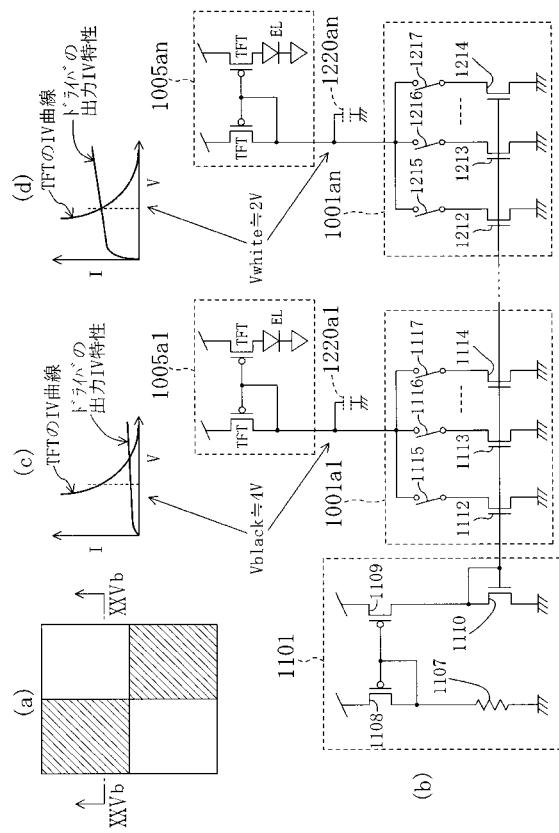

図24(a)は、従来の有機EL表示装置において、黑白表示をした場合の表示パネルの拡大図であり、(b)は、(a)に示す表示パネルのXXVb-XXVb線上に配置された画素と、該画素に接続された画素駆動部とを示す回路図である。また、図24(c)は、黒表示時におけるTFTの動作点を示すグラフ図であり、(d)は、白表示時におけるTFTの動作点を示すグラフ図である。

## 【0011】

図24(b)に示すように、ソース駆動回路には、図23に示す画素駆動部が複数配置されている。すなわち、従来のソース駆動回路は、第1の画素駆動部1001a<sub>1</sub>、第2の画素駆動部1001a<sub>2</sub>、…第nの1001a<sub>n</sub>と、各画素駆動部1001に供給する電流を生成する基準電流生成部1101とを有している。

## 【0012】

基準電流生成部1101は、ソースに電源電圧が供給されたPチャネル型の第1のMOSFET1108と、一端が第1のMOSFET1108に接続され、他端が接地された抵抗1107と、第1のMOSFET1108とカレントミラーを構成するPチャネル型の第2のMOSFET1109と、ドレインが第2のMOSFETのドレインに接続され、ソースが接地に接続されたNチャネル型の第3のMOSFET1110とを有している。

10

## 【0013】

また、画素駆動部1001のそれぞれは第3のMOSFET1110とカレントミラーを構成する複数の電流源と、この複数の電流源のそれぞれに接続されたスイッチとから構成されている。例えば、64階調の表示装置の場合、第1の画素駆動部1001a<sub>1</sub>は、電流I<sub>1</sub>を出力する第1の電流源1112と、電流2I<sub>1</sub>を出力する第2の電流源1113と、電流4I<sub>1</sub>、8I<sub>1</sub>、16I<sub>1</sub>をそれぞれ出力する第3の電流源、第4の電流源及び第5の電流源(図示せず)と、電流32I<sub>1</sub>を出力する第6の電流源1114と、各電流源に接続されたスイッチ1115、1116、1117とを有している。各電流源は第3のMOSFET1110とカレントミラーを構成するNチャネル型MOSFETから構成されている。

20

## 【0014】

また、簡略化して示された画素1005のうち、各サブピクセルは、有機EL素子1009と、画素駆動部1001に接続された第1のTFTと、第1のTFTとカレントミラーを構成し、第1のTFTに入力された電流を有機EL素子1009に供給するための第2のTFTとを有している。なお、この例ではパネル側のTFTはPチャネル型MOSFETであるので、実際の駆動時には画素側から画素駆動部側へ電流が引き込まれこととなる。

## 【0015】

図24(a)に示すような黑白表示を行なう場合、黒表示を行なう画素1005a<sub>1</sub>では、画素駆動部1001a<sub>1</sub>内のスイッチはすべてオフ状態に制御されており、画素1005a<sub>1</sub>は電源電圧によって充電される。この場合、図24(c)に示すように、ソース駆動回路の出力端子電圧が高くなつても流れる電流は非常に小さくなっている。TFTのIV(電流・電圧)曲線とソース駆動回路出力のIV特性の交点がTFTの動作点となる。

30

## 【0016】

一方、白表示を行なう画素1005a<sub>n</sub>では、画素駆動部1001a<sub>n</sub>内のスイッチはすべてオン状態に制御されており、画素1005a<sub>n</sub>から画素駆動部1001a<sub>n</sub>へと電荷が引き込まれる。この場合、図24(d)に示すように、TFTの動作点は黒表示時に比べて低電位側にシフトしている。なお、ここで「黒表示」とは、「低輝度の表示」と言い換えてよく、「白表示」とは、「高輝度の表示」と言い換えてよい。

## 【0017】

次に、図23に示す電流発生部1011の具体的な構成例を説明する。

40

## 【0018】

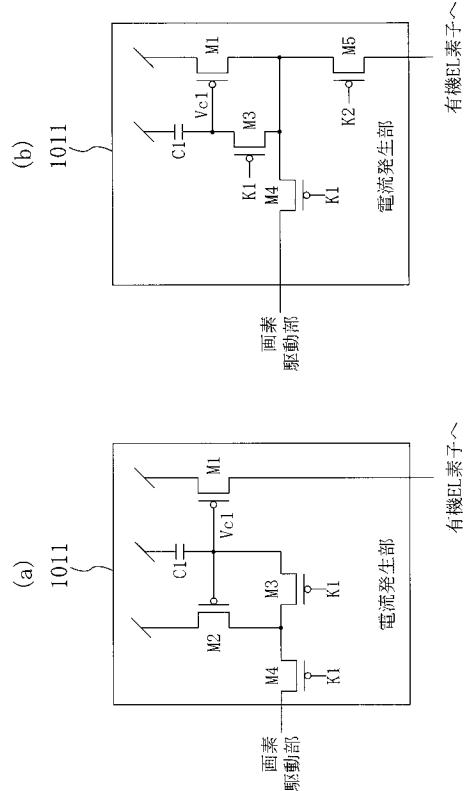

図25(a)、(b)は、それぞれ一般的な有機EL画素における電流発生部の構成例を示す回路図である。

## 【0019】

図25(a)に示す電流発生部1011は、一端が画素駆動部に接続された第1のスイッチ用トランジスタM4と、第1のスイッチ用トランジスタM4と直列に接続された第2のスイッチ用トランジスタM3と、第1のスイッチ用トランジスタM4及び第2のスイッチ用トランジスタM3と直列に接続され、一端に電源電圧が供給された容量C1と、第1のスイッチ用トランジスタM4-第2のスイッチ用トランジスタM3間を接続する配線にド

50

レインが接続され、ソースに電源電圧が供給されたPチャネル型の第1のTFTM2と、第1のTFTM2とカレントミラーを構成し、ドレンが有機EL素子1009に接続された第2のTFTM1とを有している。また、容量C1と第2のスイッチ用トランジスタM3とを接続する配線と第1のTFTM2と第2のTFTM1の両ゲート電極間を接続する配線とは互いに接続されている。そして、第1のスイッチ用トランジスタM4及び第2のスイッチ用トランジスタM3は、この例では共にPチャネル型MOSFETであり、共に制御信号K1によって動作制御されている。

#### 【0020】

ここで示す電流発生部1011において、電流設定時には、制御信号K1によって第1のスイッチ用トランジスタM4及び第2のスイッチ用トランジスタM3が共にオン状態に制御されており、画素駆動部1001へ電流が流れるとともにゲート電圧Vc1によって容量C1が充電される。そして、容量C1が充電されると、第1のTFTM2と第2のTFTM1にはそれぞれ一定の電流が流れ。なお、本明細書中で「電流設定時」とは、水平走査期間の開始後、画素1005に流れる電流が目標値に達するまでの期間のことを意味する。

10

#### 【0021】

また、表示時には制御信号K1により第1のスイッチ用トランジスタM4及び第2のスイッチ用トランジスタM3が共にオフ状態に制御される。このとき、容量C1によってゲート電圧Vc1が保持されるので、電流設定時と同じ電流が第2のTFTM1から有機EL素子1009へと流れ続ける。

20

#### 【0022】

また、図25(b)に示す電流発生部1011は、一端が画素駆動部に接続された第1のスイッチ用トランジスタM4と、一端に電源電圧が供給され、他端が第1のスイッチ用トランジスタM4に接続された容量C1と、第1のスイッチ用トランジスタM4と容量C1との間に介設された第2のスイッチ用トランジスタM3と、ゲート電極が容量C1及び第2のスイッチ用トランジスタM3に接続され、ソースに電源電圧が供給され、ドレンに有機EL素子1009が接続されたTFTM1と、TFTM1と有機EL素子1009との間に介設された第3のスイッチ用トランジスタM5とを有している。TFTM1のドレンは、第1のスイッチ用トランジスタM4及び第2のスイッチ用トランジスタM3にも接続されている。そして、第1のスイッチ用トランジスタM4及び第2のスイッチ用トランジスタM3は共に第1の制御信号K1により動作が制御されており、第3のスイッチ用トランジスタM5は、第1の制御信号の逆相信号である第2の制御信号K2によって動作が制御されている。

30

#### 【0023】

この電流発生部1011において、電流設定時には、第1の制御信号K1によって第1のスイッチ用トランジスタM4及び第2のスイッチ用トランジスタM3は共にオン状態となり、第2の制御信号K2によって第3のスイッチ用トランジスタM5はオフ状態となる。このとき、電流発生部1011から画素駆動部へと電流が流れるとともにゲート電圧Vc1によって容量C1が充電される。そして、容量C1が充電されると、TFTM1に一定の電流が流れ。

40

#### 【0024】

次に、表示時には、第1のスイッチ用トランジスタM4及び第2のスイッチ用トランジスタM3は共にオフ状態となり、第3のスイッチ用トランジスタM5はオン状態となる。このとき、容量C1によってゲート電圧Vc1が保持されるので、電流設定時と同じ電流がTFTM1から有機EL素子1009へと流れ続ける。

#### 【0025】

#### 【特許文献1】

特開2002-215095

#### 【0026】

#### 【発明が解決しようとする課題】

50

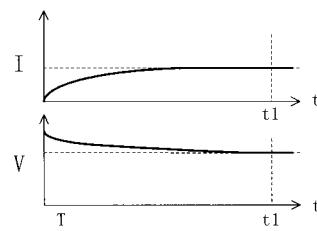

図26は、従来の有機EL表示装置において、黒表示を行なう際の画素1005に流れる電流値、及び画素1005にかかる電圧値の変化を示すグラフ図である。同図において、横軸は時間( $t$ )であり、縦軸は電流( $I$ )または電圧( $V$ )である。

#### 【0027】

有機EL表示装置は、図23に示すように、配線上に生じる浮遊容量1220や画素入力容量1007を有している。そのため、従来の有機EL表示装置では、黒表示を行なう際に、電荷が浮遊容量1220や画素入力容量1007の充電に用いられてしまい、設定通り有機EL素子1009に伝達されない場合があった。その結果、図26に示すように、有機EL素子1009に流れる電流が目標電流値に達するまでの時間 $t_1$ が長くなっていた。10

#### 【0028】

黒表示を行なう際の充電時間は、通常、フレーム周期を水平ライン数で割った時間より少ない時間内に行われる。フレーム周期としては、70Hz前後の値がよく用いられるが、表示画素数の多いパネルを作製しようとすると、水平ライン数が増加して1ラインあたりの充電時間が短くなる。そのため、従来の有機EL表示パネルで高解像度の表示を実現しようとすると、充電時間を短くせざる得ず、画質が低下してしまうという不具合が生じていた。

#### 【0029】

また、白表示を行なう場合には、黒表示の場合とは逆に、浮遊容量1220や画素入力容量1007などに充電された電荷を画素駆動部側に放出する必要がある。そのため、従来の有機EL表示装置で解像度を高めようとすると放電時間を短くせざる得ず、画質の低下を招くことがあった。なお、ここでいう「画質の低下」とは、正しい輝度にならないことによる色再現性の低下、という意味である。20

#### 【0030】

本発明の目的は、低輝度表示から高輝度表示への変化時、または高輝度表示から低輝度表示への変化時にも画質を低下をきたさずに、高解像度の表示を可能にする表示装置、及びこれを実現するためのドライバIC、表示パネルを提供することにある。

#### 【0031】

##### 【課題を解決するための手段】

本発明の第1の表示装置は、電流により駆動される発光素子を含む画素と、上記画素に接続された信号線とが設けられた表示パネルと、上記信号線を介して上記画素に駆動電流を供給するためのソース駆動回路とを備えている表示装置であって、上記ソース駆動回路は、Nビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、制御信号を出力するためのタイミング制御部と、上記制御信号に従って、電流設定時の所定の期間には任意に設定した上記駆動電流を流し、上記所定の期間以外の動作時には上記レジスタからの表示データにより設定される上記駆動電流を流す電流駆動部とを有している。30

#### 【0032】

この構成により、電流設定時の所定の期間に、電流駆動部を流れる電流を最適な値に設定することができるので、画素に流れる電流の値を目標値に到達させるのに要する時間を従来よりも短縮することができる。特に、高輝度表示から低輝度表示に切り替える際には、表示パネル側に蓄積した電荷を速やかにソース駆動回路側に引き込むことができるので、高い時間短縮効果が得られる。この結果、画質を低下させることなく水平ライン数を増加させることができるので、表示の解像度を高めることができる。40

#### 【0033】

特に、電流設定時の所定の期間には、上記レジスタからの上記表示データにより設定される電流値以上の上記駆動電流が上記電流駆動部から出力されると、画素に流れる電流の値を目標値に到達させるのに要する時間を従来よりも短縮することができるので、好ましい。50

#### 【0034】

上記電流駆動部は、上記表示データのビットに応じた電流を出力するためのN個の電流源を有する電流加算型のD/Aコンバータと、任意に設定した値の電流を出力するための付加電流源と、上記制御信号を受けて、上記付加電流源と上記画素とを電流設定時の所定の期間のみ導通させる第1のスイッチとを有していることにより、電流設定時の所定の期間だけ付加電流源から適宜最適な電流を流すことができるので、画素に流れる電流の値を目標値に到達させるのに要する時間を従来よりも短縮することができる。

## 【0035】

上記D/Aコンバータ内のN個の電流源は、それぞれ互いにカレントミラー回路を構成するMISFETからなっており、上記付加電流源は、上記N個の電流源を構成するMISトランジスタとカレントミラー回路を構成するMISFETからなっていてもよい。 10

## 【0036】

上記付加電流源は上記表示データを受けて、上記表示データのビットに応じた電流を出力可能であることにより、付加電流源から表示データごとに適した電流を流すことができるので、画素に流れる電流の値を目標値に到達させるのに要する時間をより効果的に短縮することができる。

## 【0037】

上記駆動電流部は、上記表示データのビットに応じた電流を出力するためのN個の電流源と、上記N個の電流源を流れる電流の各出力経路上にそれぞれ介設された第2のスイッチと、上記N個の電流源のそれぞれを流れる電流を上記第2のスイッチを迂回して出力するためのN本のバイパス経路と、上記N本のバイパス経路のそれぞれの経路上に介設された第3のスイッチとを有する電流加算型のD/Aコンバータであり、電流設定時の所定の期間中は、上記制御信号によって、上記第3のスイッチがオン状態に設定され、上記所定の期間以外の動作時には上記第3のスイッチがオフ状態に設定されることによっても画素に流れる電流の値を目標値に到達させるのに要する時間をより効果的に短縮することができる。 20

## 【0038】

電流設定時の所定の期間中、上記電流駆動部から出力される電流の値が、段階的に変化することによって、電流設定時に画素に印加される電圧のオーバーシュート量を低減することができるので、画素に流れる電流の値を目標値に到達させるのに要する時間をより効果的に短縮することができる。 30

## 【0039】

上記駆動電流部は、上記表示データのビットに応じた電流を出力するためのN個の電流源と、上記N個の電流源を流れる電流の各出力経路上にそれぞれ介設された第2のスイッチと、上記N個の電流源のそれぞれを流れる電流を上記第2のスイッチを迂回して出力するためのN本のバイパス経路と、上記N本のバイパス経路のそれぞれの経路上に介設された第3のスイッチとを有する電流加算型のD/Aコンバータであり、電流設定時の所定の期間中は、上記制御信号によって上記第3のスイッチがオン状態に設定された後、上記N個の電流源のうち、上位ビット用の電流源に接続された上記第3のスイッチから段階的にオフ状態に切り替わるよう設定されることが好ましい。

## 【0040】

ソース駆動回路は、所定の電圧を出力するための電圧設定手段と、上記電圧設定手段の出力電圧と上記電流駆動部の出力電圧とを比較し、比較結果を上記タイミング制御部に出力するための比較回路とをさらに有し、上記所定の期間中に上記電流駆動部から任意に設定した上記駆動電流が流れる際に、少なくとも上記電流駆動部の出力電圧が上記電圧設定手段の出力電圧と一致した時点で、上記駆動電流の値が上記表示データにより設定される電流値に切り替わるよう設定されることが好ましい。これにより、画素に流れる電流を目標電流に到達させるまでの時間（以後この時間を「電流設定時間」と呼ぶ）を短縮するために適した電圧が電圧設定手段により設定されるので、電流設定時間を効果的に短縮させることができる。 40

## 【0041】

上記電圧設定手段が出力する上記所定の電圧は、電流設定時に上記画素に流れる電流の値が目標値に到達する際の上記電流駆動部の出力電圧である安定出力電圧であれば、電流設定時間を効果的に短縮させることができる。

#### 【0042】

上記電圧設定手段は、上記表示パネル上に設けられ、TFT及び容量を有し、画像表示に関係しないダミー画素と、上記表示パネル上に設けられ、上記ダミー画素に電流を供給するためのダミー信号線と、上記ソース駆動回路内に設けられると共に上記ダミー信号線及び上記比較回路に接続され、動作時を通して一定値の電流を出力するダミー電流駆動部を含むダミー画素駆動部とを有するダミー回路であることにより、安定出力電圧に近い電圧に到達しているダミー画素駆動部の出力電圧を基準として電流駆動部の出力電流を適切な値に設定できるので、流設定時間を効果的に短縮させることができる。10

#### 【0043】

上記ダミー回路は、複数個の上記電流駆動部に対して1つの割合で設けられていることにより、回路面積の増加を抑えることができるので、小面積化が要求される場合には特に好ましい。

#### 【0044】

また、上記ソース駆動回路は、互いに同一の構成を有する複数の半導体チップ上に分かれ設けられており、上記複数の半導体チップのそれぞれには、上記ダミー画素駆動部が設けられている場合、ソース駆動回路として、複数種類の半導体チップを準備する必要がないので好ましい。また、表示パネルへの入出力構成を簡単にすることができる。加えて、自ずとダミー回路同士が所定の間隔で配置されることになるので、表示パネルの位置によって生じる時間短縮効果のばらつきを抑えることができる。20

#### 【0045】

上記ダミー回路は複数個存在し、複数の上記ダミー回路内のダミー電流駆動部同士は、少なくとも電流設定時の所定の期間互いに接続されることによって、表示パネルの位置による特性ばらつきの影響を抑えることができる。

#### 【0046】

本発明の第2の表示装置は、電流により駆動される発光素子を含む画素と、上記画素に接続された信号線とが設けられた表示パネルと、上記信号線を介して上記画素に流れる駆動電流を設定するためのソース駆動回路とを備えている表示装置であって、上記信号線は、上記画素に駆動電圧を伝達するための駆動電圧用信号線と、上記画素の駆動電流を伝達するための駆動電流用信号線とに分かれており、上記ソース駆動回路は、上記駆動電圧用信号線を介して上記画素に駆動電圧を供給するための電圧駆動部と、上記駆動電流用信号線を介して上記画素の駆動電流を流すための電流供給手段とを有している。30

#### 【0047】

この構成により、第1の表示装置で用いられた電流駆動部よりも出力インピーダンスの低い電圧駆動部により画素を駆動することができるので、低輝度表示から高輝度表示へ切り替わる際と高輝度表示から低輝度表示へ切り替わる際のいずれの場合でも、電流設定時間を効果的に短縮させることができる。なお、画素の構成は電流と電圧の両方で駆動できる回路構成であればどのような回路構成であってもよい。

#### 【0048】

上記電流供給手段は、上記画素から流れる駆動電流の値を検出し、検出結果を上記電圧駆動部にフィードバックするための電流値検出部であり、上記ソース駆動回路には、表示データをラッチし、且つ上記表示データを上記電流値検出部へ入力するためのレジスタがさらに設けられることにより、例えば、画素から電流検出部へ流れる電流値が設定された値を越える場合には、画素から流れる電流値を低減する方向に上記電圧駆動部からの出力電圧が制御される。このようなフィードバック制御を実現できるので、外部から特別な制御を加えることなく、電流設定時間を効果的に短縮させることができる。40

#### 【0049】

上記電流値検出部は、上記駆動電流用信号線に接続され、上記表示データに応じて出力電50

流の値を変更可能な電流駆動部と、上記電流駆動部と上記駆動電流用信号線との接続経路上に介設された抵抗素子とを有し、上記電流駆動部と上記抵抗素子との間に生じる電圧が、上記検出結果として上記電圧駆動部に入力されていてもよい。

#### 【0050】

上記電圧駆動部と上記電流供給手段とを電流設定時の所定の期間のみ短絡させるための短絡手段をさらに備えていることによっても電流設定時間を短縮させることができる。

#### 【0051】

本発明の第3の表示装置は、電流により駆動される発光素子を含む画素と、上記画素に接続された信号線とが設けられた表示パネルと、上記信号線を介して上記画素に駆動電流を供給するためのソース駆動回路とを備えている表示装置であって、上記ソース駆動回路は、Nビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、上記レジスタから入力される上記表示データに応じた上記駆動電流を出力するための電流駆動部と、上記電流駆動部よりも出力インピーダンスの低い電圧供給手段と、上記信号線と上記電圧供給手段とを接続するための配線と、制御信号を出力するためのタイミング制御部と、上記配線上に設けられ、上記制御信号に従って、電流設定時の所定の期間のみ上記信号線と上記電圧供給手段とを導通させる短絡用スイッチとを有している。10

#### 【0052】

この構成により、電流設定時の所定の期間中に電流駆動部よりも出力インピーダンスの低い電圧供給手段からの電圧で画素を駆動することができるので、高輝度表示を行なう際には、ソース駆動回路側に速やかに電荷を引き込むことができ、低輝度表示を行なう際には、表示パネル側の容量を速やかに充電することができる。従って、従来の表示装置に比べて電流設定時間を著しく短縮させることができる。20

#### 【0053】

上記電圧供給手段は、上記表示パネル上に設けられ、TFT及び容量を有し、画像表示に関係しないダミー画素と、上記表示パネル上に設けられ、上記ダミー画素に電流を供給するためのダミー信号線と、上記ソース駆動回路内に設けられ、且つ上記ダミー信号線に接続され、動作時を通して一定値の電流を出力するダミー電流駆動部を含むダミー画素駆動部とを有するダミー回路と、上記ダミー電流駆動部に接続され、上記ダミー電流駆動部からの出力電圧を上記信号線に出力するための電流增幅用バッファとから構成されていることにより、定常状態に達しているダミー電流駆動部の出力電圧を画素に供給することができるので、電流設定時間を効果的に短縮させることができる。30

#### 【0054】

上記電圧供給手段は、複数個の上記電流駆動部に対して1つの割合で設けられていることにより、電流設定時間を短縮させつつ、回路面積の著しい増加を抑えることができる。

#### 【0055】

上記電圧供給手段は、上記電流駆動部毎に設けられ、上記レジスタから出力される表示データに応じて出力電圧を変えることができる電圧出力型のD/Aコンバータであれば、半導体チップ内で出力電圧を発生させることができ、好ましい。

#### 【0056】

上記電圧出力型のD/Aコンバータは、上記表示データのうち上位1または2ビットに応じて出力電圧を変えることにより、電流設定時間を短縮させつつ回路面積の増加を抑えることができる。40

#### 【0057】

上記電圧供給手段は、外部電源に接続された配線であってよい。

#### 【0058】

本発明の第4の表示装置は、電流により駆動される発光素子を含む画素と、上記画素に接続された信号線とが設けられた表示パネルと、上記信号線を介して上記画素に駆動電流を供給するためのソース駆動回路とを備えている表示装置であって、上記ソース駆動回路は、Nビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、電流設定時の所定の期間に上記レジスタから入力された上記表示データにMビットを加算50

して(  $N + M$  )ビットの表示データを出力するためのビットデータ加算手段と、制御信号を出力するためのタイミング制御部と、上記制御信号に従って、電流設定時の所定の期間には上記(  $N + M$  )ビットの表示データにより設定される上記駆動電流を流し、上記所定の期間以外の動作時には $N$ ビットの上記表示データにより設定される上記駆動電流を流す電流駆動部とを有している。

## 【 0 0 5 9 】

この構成により、電流設定時の所定の期間中には電流駆動部から本来出力されるべき電流以上の電流が一時的に出力されるので、電流設定時間を短縮させることができる。

## 【 0 0 6 0 】

上記 $M$ ビットは1または2ビットである場合、回路面積の著しい増加を抑えることができるので、好ましい。 10

## 【 0 0 6 1 】

本発明の第5の表示装置は、電流により駆動される発光素子を含む画素と、上記画素に接続された信号線とが設けられた表示パネルと、 $N$ ビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、上記表示データのビットに応じた駆動電流を上記信号線に出力する電流駆動部と、上記電流駆動部に基準電流を供給するための基準電流生成部とを有するソース駆動回路とを備えている表示装置であって、上記電流駆動部は、それぞれ互いにカレントミラー回路を構成するM I S F E Tから構成される $N$ 個の電流源を有し、上記基準電流生成部は、ソースに電源電圧が供給され、上記基準電流を流すための第1のM I S F E Tと、上記第1のM I S F E Tのドレインに接続され、上記表示データが入力された際には、上記表示データにより抵抗値が変化する可変抵抗と、上記第1のM I S F E Tとカレントミラー回路を構成する第2のM I S F E Tと、上記第2のM I S F E Tに接続され、上記 $N$ 個の電流源のそれぞれにカレントミラーを介して上記基準電流を供給するための第3のM I S F E Tとを有し、上記レジスタから出力される上記表示データは、電流設定時の所定の期間に上記可変抵抗に入力される。 20

## 【 0 0 6 2 】

この構成により、電流設定時には可変抵抗の抵抗値が表示データに応じて変化することにより、電流駆動部を流れる電流の値を適切な値に調節することができる、従来に比べて効果的に電流設定時間を短縮させることができる。

## 【 0 0 6 3 】

本発明の第1のソース駆動回路は、 $N$ ビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、制御信号を出力するためのタイミング制御部と、上記制御信号に従って、電流設定時の所定の期間には上記表示データにより設定される電流以上の上記駆動電流を流し、上記所定の期間以外の動作時には上記レジスタからの表示データにより設定される上記駆動電流を流す電流駆動部とを備えている。 30

## 【 0 0 6 4 】

これにより、本ソース駆動回路を用いた表示装置では、電流設定時に画素に流れる電流を従来よりも短時間で目標電流に到達させることができる。すなわち、本ソース駆動回路を用いれば、従来よりも解像度の高い電流駆動型の表示装置を実現することができる。

## 【 0 0 6 5 】

また、所定の電圧を出力するための電圧設定手段と、上記電圧設定手段の出力電圧と上記電流駆動部の出力電圧とを比較し、比較結果を上記タイミング制御部に出力するための比較回路とをさらに有し、上記所定の期間中に、上記表示データにより設定される電流値以上の上記駆動電流が上記電流駆動部から流れる際に、少なくとも上記電流駆動部の出力電圧が上記電圧設定手段の出力電圧と一致した時点で、上記駆動電流の値が上記表示データにより設定される電流値に切り替わるよう設定されることにより、本ソース駆動回路を用いた表示装置では、電流設定時に画素に流れる電流を従来よりも短時間で目標電流に到達させることができるようになる。 40

## 【 0 0 6 6 】

本発明の第2のソース駆動回路は、電圧を供給するための電圧駆動部と、表示データをラ 50

ツチし、且つ出力するためのレジスタと、上記レジスタから出力される上記表示データが入力され、上記表示データに応じた電流を流すための電流供給手段とを備えている。

【0067】

これにより、従来よりも電流設定時間が短縮された表示装置を実現することができる。

【0068】

本発明の第3のソース駆動回路は、Nビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、上記レジスタから入力される上記表示データに応じた上記駆動電流を出力するための出力部を有する電流駆動部と、上記電流駆動部よりも出力インピーダンスの低い電圧供給手段と、上記電流駆動部の出力部と上記電圧供給手段とを接続するための配線と、制御信号を出力するためのタイミング制御部と、上記配線上に設けられ、上記制御信号に従って、電流設定時の所定の期間のみ上記信号線と上記電圧供給手段とを導通させる短絡用スイッチとを備えている。10

【0069】

これにより、従来よりも電流設定時間が短縮された表示装置を実現することができる。

【0070】

本発明の第4のソース駆動回路は、Nビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、電流設定時の所定の期間に上記レジスタから入力された上記表示データにMビットを加算して(N+M)ビットの表示データを出力するためのビットデータ加算手段と、制御信号を出力するためのタイミング制御部と、上記制御信号に従って、電流設定時の所定の期間には上記(N+M)ビットの表示データにより設定される電流を流し、上記所定の期間以外の動作時にはNビットの上記表示データにより設定される電流を流す電流駆動部とを備えている。20

【0071】

これにより、従来よりも電流設定時間が短縮された表示装置を実現することができる。

【0072】

本発明の第5のソース駆動回路は、Nビットの表示データをラッチし、且つ上記表示データを出力するためのレジスタと、上記表示データのビットに応じた駆動電流を上記信号線に出力する電流駆動部と、上記電流駆動部に基準電流を供給するための基準電流生成部とを備えているソース駆動回路であって、上記電流駆動部は、それぞれ互いにカレントミラー回路を構成するMISFETから構成されるN個の電流源を有し、上記基準電流生成部は、ソースに電源電圧が供給され、上記基準電流を流すための第1のMISFETと、上記第1のMISFETのドレンに接続され、上記表示データが入力された際には、上記表示データにより抵抗値が変化する可変抵抗と、上記第1のMISFETとカレントミラー回路を構成する第2のMISFETと、上記第2のMISFETに接続され、上記N個の電流源のそれぞれにカレントミラーを介して上記基準電流を供給するための第3のMISFETとを有し、上記レジスタから出力される上記表示データは、電流設定時の所定の期間に上記可変抵抗に入力される。30

【0073】

これにより、従来よりも電流設定時間が短縮された表示装置を実現することができる。

【0074】

本発明の第1の表示パネルは、電流により駆動される発光素子を含む画素と、上記画素に接続された信号線と、画像表示に関係しないダミー画素と、上記ダミー画素に接続されたダミー信号線とを備えている。40

【0075】

これにより、本表示パネルを用いて従来よりも電流設定時間が短縮された表示装置を実現することができる。

【0076】

本発明の第2の表示パネルは、電流により駆動される発光素子を含み、電圧及び電流によって駆動される画素と、上記画素に駆動電圧を供給するための駆動電圧用信号線と、上記画素の駆動電流を出力するための駆動電流用信号線とを備えている。50

## 【0077】

これにより、本表示パネルを用いて従来よりも電流設定時間が短縮された表示装置を実現することができる。

## 【0078】

## 【発明の実施の形態】

## (第1の実施形態)

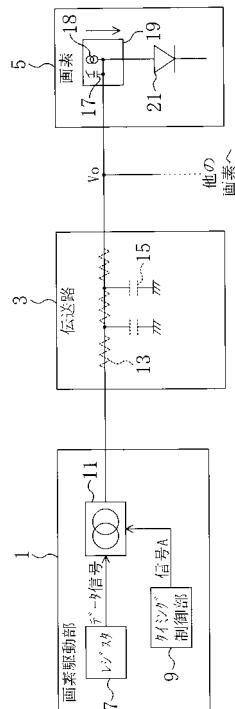

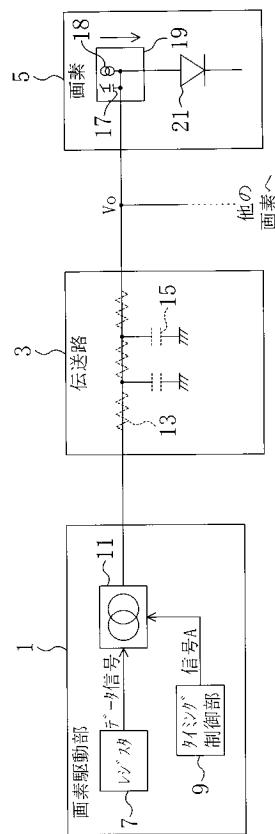

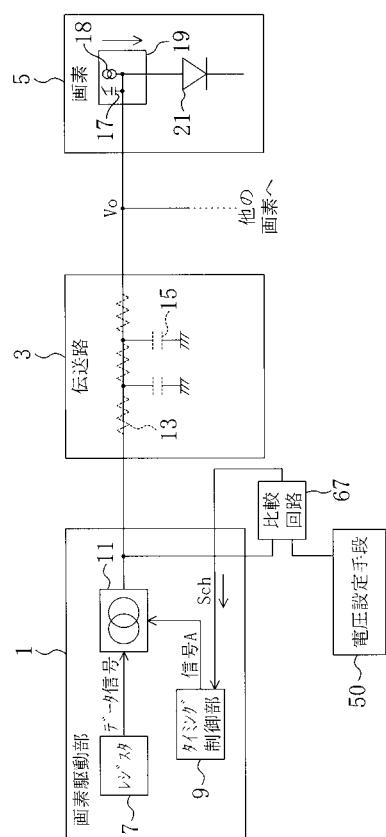

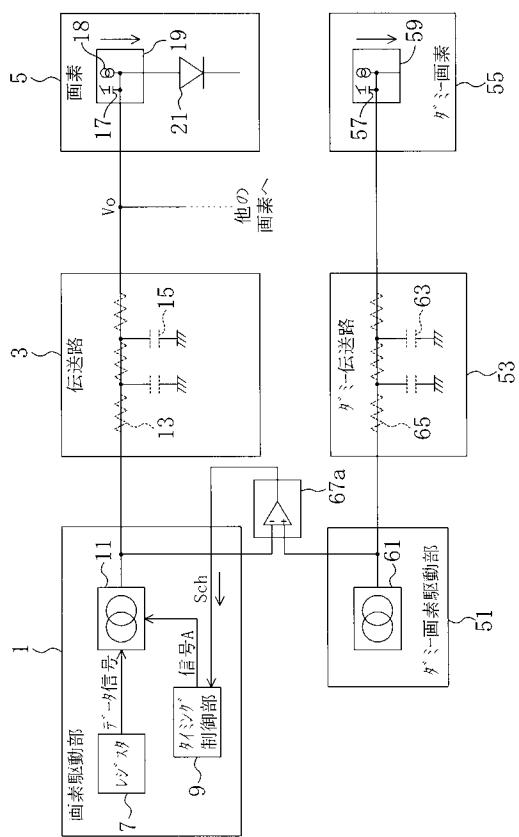

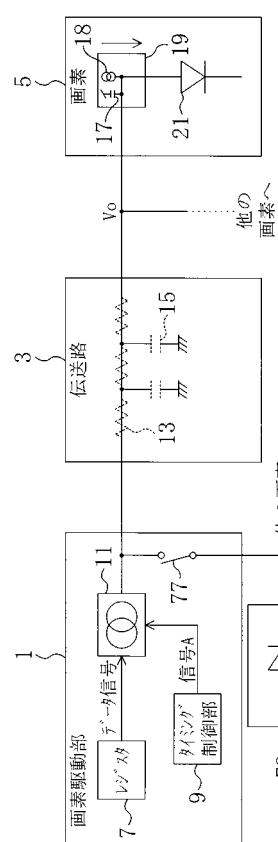

図1は、本発明の第1の実施形態に係る有機EL表示装置の構成を概略的に示すプロック回路図である。本実施形態の有機EL表示装置は、電流設定時に画素駆動部1から所定の電流を一定期間流した後、設定された電流値が画素駆動部1から出力されることが特徴である。

10

## 【0079】

図1に示すように、本実施形態の有機EL表示装置は、表示パネルと、表示パネル上に設けられ、画像を表示するための画素5と、画素5に接続された伝送路3と、ソース駆動回路に含まれ、伝送路3を介して画素5に駆動電流を供給するための画素駆動部1とを備えている。ここで、伝送路3には、画素駆動部1と表示パネルとを接続する配線と、表示パネル上に設けられた信号線とが含まれる。図1の伝送路3中には抵抗や容量が示されているが、これは配線抵抗や浮遊容量を示したものである。なお、信号線は、信号線の延びる方向に配置された他の画素にも接続される。

## 【0080】

画素駆動部1は、画素5に駆動電流を供給するための電流駆動部11と、表示データであるデータ信号をラッチし、該データ信号を電流駆動部11に出力するレジスタ7と、電流駆動部11からの出力電流を制御するための信号Aを出力するタイミング制御部9とを有している。電流駆動部11に信号Aが入力されることにより、電流駆動部11は、電流設定時のうち所定の期間だけ任意に設定した値の電流を出力し、それ以外の動作期間にはデータ信号によって設定された電流値を出力するよう制御されている。ここで、電流駆動部11から所定の期間だけ出力される電流の値は、データ信号により設定される電流の値以上であることが好ましい。

20

## 【0081】

なお、画素5の構成は従来と同様である。すなわち、画素5は、信号線に接続され、画素入力容量17と電流源とを有する電流発生部19と、電流発生部19からの出力電流によって駆動される有機EL素子21とを有している。

30

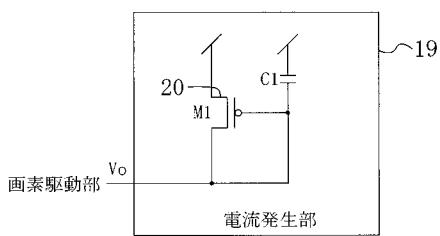

## 【0082】

図2は、本実施形態の有機EL表示装置のうち、電流設定時における電流発生部19のモデル例を示す回路図である。電流発生部19の構成は、図25(a)、(b)に示すような従来と同様の構成であってもよいし、TFTを用いた他の一般的な構成であってもよい。図2に示す例では、ソースに電源電圧が供給され、ドラインが画素駆動部及び自身のゲート電極に接続されたPチャネル型のTFT20と、TFT20のゲート電極及び画素駆動部に接続されたゲート電圧保持用の容量C1(図1に示す画素入力容量17に相当)とを有している。なお、図2では、有機EL素子21に電流を供給するためのTFT(例えば図25(a)に示す第2のTFTM1)は省略している。

40

## 【0083】

本実施形態の有機EL表示装置によれば、例えば黒表示から白表示に変化する際の電流設定時に、所定の期間大きい電流をパネル側から画素駆動部1側へ流すことによって、浮遊容量15や画素入力容量17に充電された電荷を速やかに引き抜くことが可能となる。その結果、電流駆動部11から画素5に入力される電流値、及び電圧値が従来よりも短時間で目標値に到達できるようになるので、本実施形態の有機EL表示装置では、解像度の高い表示が可能となる。

## 【0084】

また、有機EL表示装置では、動画の表示切替えを滑らかに見せるために一旦黒表示をしてから所定の表示を行なう場合がある。この場合、本実施形態の有機EL表示装置では、

50

画素 5 に流れる電流を従来よりも速やかに目標電流に到達させることができるので、各画素の動作の統一を図ることができる。

#### 【 0 0 8 5 】

次に、本実施形態の有機 E L 表示装置に用いられる電流駆動部の具体的な構成例を説明する。

#### 【 0 0 8 6 】

##### - 第 1 の具体例 -

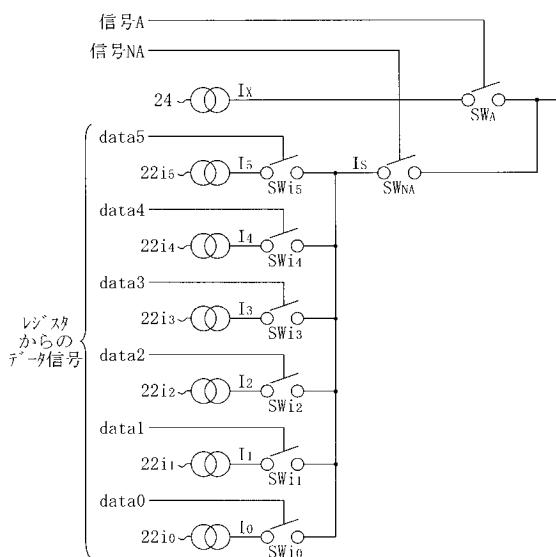

図 3 は、第 1 の実施形態に係る有機 E L 表示装置について、電流駆動部の第 1 の具体例を示す回路図である。ここでは、6 ビット、すなわち 6 4 階調表示の有機 E L 表示装置の例を示す。

10

#### 【 0 0 8 7 】

図 3 に示す本具体例に係る電流駆動部は、固定電流  $I_x$  を流すための付加電流源 2 4 と、レジスタ 7 から出力されたデータ信号を受けてデータ信号に応じた電流を出力するための電流加算型 D / A コンバータと、付加電流源 2 4 に流れる電流をオンまたはオフに切り替えるためのスイッチ  $S_{W_A}$  と、電流加算型 D / A コンバータの出力電流（引き込み電流）をオンまたはオフに切り替えるためのスイッチ  $S_{W_{NA}}$  とを有している。そして、スイッチ  $S_{W_A}$  は信号 A によって動作を制御され、スイッチ  $S_{W_{NA}}$  は信号 A の逆相信号である信号 N A によって動作を制御される。

#### 【 0 0 8 8 】

また、電流加算型 D / A コンバータは、最小電流単位の電流  $I_0$  を流すための第 1 の電流源 2 2  $i_0$  と、 $I_0$  の 2 倍の電流  $I_1$  を流すための第 2 の電流源 2 2  $i_1$  と、 $I_0$  の  $2^2$  倍の電流  $I_2$  を流すための第 3 の電流源 2 2  $i_2$  と、 $I_0$  の  $2^3$  倍の電流  $I_3$  を流すための第 4 の電流源 2 2  $i_3$  と、 $I_0$  の  $2^4$  倍の電流  $I_4$  を流すための第 5 の電流源 2 2  $i_4$  と、 $I_0$  の  $2^5$  倍の電流  $I_5$  を流すための第 6 の電流源 2 2  $i_5$  と、第 1 ~ 第 6 の電流源の各々を流れる電流をオンまたはオフに制御するための第 1 のスイッチ  $S_{Wi_0}$  、第 2 のスイッチ  $S_{Wi_1}$  、第 3 のスイッチ  $S_{Wi_2}$  、第 4 のスイッチ  $S_{Wi_3}$  、第 5 のスイッチ  $S_{Wi_4}$  及び第 6 のスイッチ  $S_{Wi_5}$  とを有している。第 1 ~ 第 6 のスイッチはそれぞれデータ 0 ~ データ 5 までのデータ信号によってオンまたはオフが決定され、導通状態となった各電流源を流れる電流の合計が、電流  $I_s$  としてこの D / A コンバータに引き込まれる。なお、ここではデータ信号が 6 ビットの例を示しているが、ビット数はこれに限られない。また、D / A コンバータは、表示輝度に比例した出力電流を出力する場合もあるが、有機 E L 素子の特性を補正するために、表示輝度に比例しない出力電流を出力する場合もある。以上のこととは、他の実施形態に係る有機 E L 表示装置についても同じである。

20

#### 【 0 0 8 9 】

本具体例の有機 E L 表示装置において、N ビット（N は 2 以上の整数）の場合には電流源の数は N 個となり、M S B（最上位ビット）の電流源は L S B（最下位ビット）の電流源の  $2^{N-1}$  倍の電流を引き込む。この D / A コンバータの構成は図 2 4 に示す従来の電流駆動部と同様であり、例えば各電流源は、互いにカレントミラーを構成する M O S F E T から構成されている。

30

#### 【 0 0 9 0 】

なお、付加電流源 2 4 に流れる電流  $I_x$  は、少なくとも最小電流単位の電流  $I_0$  より大きい任意の値とする。

40

#### 【 0 0 9 1 】

以上のような構成の本具体例に係る電流駆動部では、電流設定時の所定の期間にスイッチ  $S_{W_A}$  がオンになり、スイッチ  $S_{W_{NA}}$  がオフとなる。そして、表示時など、該所定の期間以外の期間にはスイッチ  $S_{W_A}$  がオフになり、スイッチ  $S_{W_{NA}}$  がオンとなっている。このような制御によって、高輝度表示から低輝度表示に変化する際に、所定の期間付加電流源 2 4 に電流が引き込まれるので、画素 5 に流れる電流の値を迅速に目標値に到達させることができる。よって、電流発生部（図 1 参照）から有機 E L 素子 2 1 に流れる電流の値を、迅速に目標値に到達させることが可能となる。

50

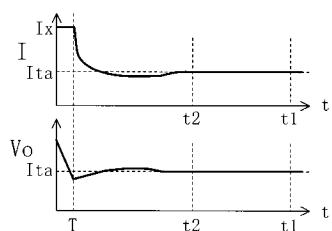

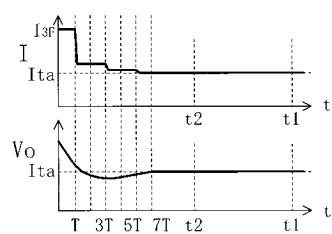

## 【0092】

図4は、本具体例の有機EL表示装置において、電流設定時における画素5に流れる電流Iの変化、及び画素5の入力部に印加される電圧V<sub>o</sub>の変化を示すグラフ図である。同図は、黒表示から白表示に切り替える際の変化を示している。

## 【0093】

図4に示すように、本具体例の有機EL表示装置において、電流設定時の時間0から時間Tまでの間に、図26に示す従来例よりも大きい電流I<sub>x</sub>が電流発生部19から流れる。これに伴って画素5の入力部に印加される電圧V<sub>o</sub>は急激に低下し、時間Tでは安定電圧V<sub>ta</sub>に近づく。このため、時間Tで電流駆動部11に流れる電流が本来の設定電流(図3に示す電流I<sub>s</sub>)に切り替わった後、目標電流I<sub>ta</sub>に到達する時間が従来の時間t<sub>1</sub>よりも早い時間t<sub>2</sub>となっている。すなわち、本具体例の有機EL表示装置では、所定の電流を一定期間流すための付加電流源24を設けることで、低輝度表示(黒表示)から高輝度表示(白表示)への変化時に、電流駆動部11から画素5に流れる電流の値が目標値に到達するまでの時間を、従来の有機EL表示装置よりも短縮することができる。従って、本具体例の有機EL表示装置によれば、表示品質の低下を來すことなく高解像度化を達成することができる。

## 【0094】

なお、図4に示す目標電流値は、表示時における画素の輝度によってそれぞれ異なっている。そのため、電流駆動部11が電流I<sub>x</sub>を出力する期間Tの長さを画素の輝度に応じて変えることがより好ましい。この場合、図1に示すタイミング制御部9によって信号Aが図3に示すスイッチSW<sub>A</sub>をオンにする時間やタイミングを適宜制御してもよい。

## 【0095】

なお、本具体例では画素内の発光素子として有機EL素子を用いているが、これに代えて発光ダイオードなど、電流により駆動される素子を用いてもよい。これは、以下の実施形態についても同様である。また、本実施形態の有機EL表示装置に用いられる画素駆動部の構成は、プリンタヘッドにも応用することができる。

## 【0096】

また、本具体例に係る有機EL表示装置において、信号Aを出力するタイミング制御部9は、電流駆動部ごとに設けてもよいが、複数の電流駆動部につき1つ設けてもよい。タイミング制御部9を複数の電流駆動部で共用する構成にすれば、回路面積を低減することができる。

## 【0097】

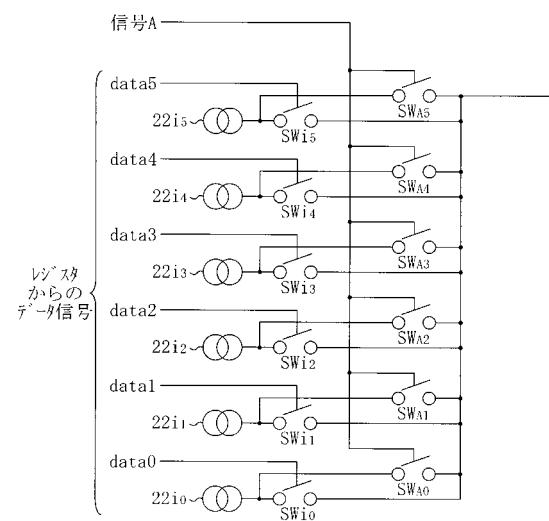

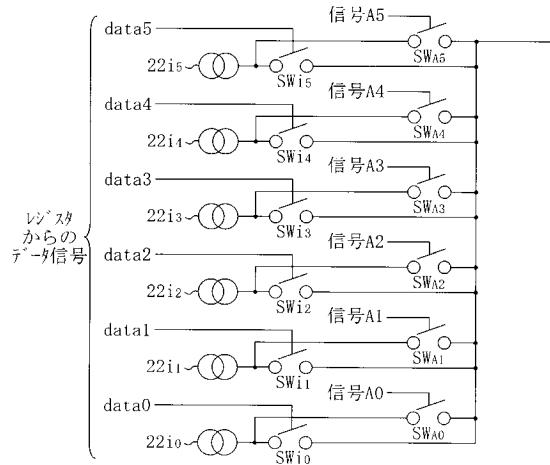

## - 第2の具体例 -

図5は、第1の実施形態に係る有機EL表示装置について、電流駆動部の第2の具体例を示す回路図である。本具体例では、付加電流源を設けずに、電流加算型D/Aコンバータの第1～第6の電流源を用いて電流設定時の所定の期間だけ最大出力電流を流す電流駆動部について説明する。

## 【0098】

図5に示すように、本具体例に係る電流駆動部は、第1の具体例と同一構成のD/Aコンバータに加え、第1～第6の電流源のそれぞれとD/Aコンバータの出力部とを接続するバイパス経路と、このバイパス経路上にそれぞれ設けられた、第1の電流源22i<sub>0</sub>とD/Aコンバータの出力部の間に設けられたスイッチSW<sub>A</sub><sub>0</sub>、第2の電流源22i<sub>1</sub>とD/Aコンバータの出力部の間に設けられたスイッチSW<sub>A</sub><sub>1</sub>、第3の電流源22i<sub>2</sub>とD/Aコンバータの出力部の間に設けられたスイッチSW<sub>A</sub><sub>2</sub>、第4の電流源22i<sub>3</sub>とD/Aコンバータの出力部の間に設けられたスイッチSW<sub>A</sub><sub>3</sub>、第5の電流源22i<sub>4</sub>とD/Aコンバータの出力部の間に設けられたスイッチSW<sub>A</sub><sub>4</sub>、及び第6の電流源22i<sub>5</sub>とD/Aコンバータの出力部の間に設けられたスイッチSW<sub>A</sub><sub>5</sub>とを有している。このスイッチSW<sub>A</sub><sub>0</sub>～SW<sub>A</sub><sub>5</sub>のそれぞれは、図1に示すタイミング制御部9から出力される信号Aによって電流設定時の所定の期間のみオン状態になり、その他の期間はオフ状態になるよう制御されている。

## 【0099】

また、第1のスイッチSW<sub>i0</sub>、第2のスイッチSW<sub>i1</sub>、第3のスイッチSW<sub>i2</sub>、第4のスイッチSW<sub>i3</sub>、第5のスイッチSW<sub>i4</sub>及び第6のスイッチSW<sub>i5</sub>のそれぞれは、スイッチSW<sub>A0</sub>～SW<sub>A5</sub>がオン状態にあるときはオフ状態となっている。

## 【0100】

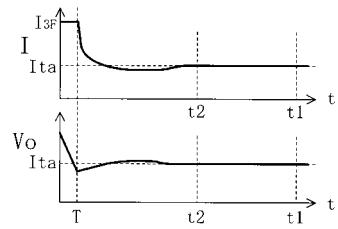

以上の構成により、本具体例の電流駆動部には、第1～第6の全ての電流源により生じる電流の合計電流が電流設定時の所定の期間だけ流れることとなる。この合計電流は、64階調表示の場合、データ3Fの電流I<sub>3F</sub>、すなわち最小電流単位の63倍の電流となる。

## 【0101】

図6は、本具体例に係る有機EL表示装置において、電流設定時の電流駆動部11から画素5に流れる電流Iの変化、及び画素5に印加される電圧V<sub>o</sub>の変化を示すグラフ図である。ここでは、黒表示後の電流I及び電圧V<sub>o</sub>の変化を示している。

## 【0102】

図6に示すように、本具体例の有機EL表示装置においては、電流設定時の時間0から時間Tまでの間に、64階調表示の最大電流である電流I<sub>3F</sub>が電流駆動部11から出力される。これに伴って画素5に印加される電圧V<sub>o</sub>は急激に低下し、時間Tでは安定電圧V<sub>ta</sub>に近づく。このため、第1の具体例と同様に、時間Tで電流駆動部11に引き込まれる電流が本来の設定電流（図3に示す電流I<sub>s</sub>）に切り替わった後、目標電流I<sub>ta</sub>に到達する時間が従来の時間t<sub>1</sub>よりも早い時間t<sub>2</sub>となっている。すなわち、本具体例の有機EL表示装置では、D/Aコンバータの最大設定電流を一定期間流することで、低輝度表示（黒表示）から高輝度表示（白表示）への変化時に、画素5の入力部に流れる電流の値が目標値に到達するまでの時間を、従来の有機EL表示装置よりも短縮することができる。

## 【0103】

特に、本具体例に係る電流駆動部では、付加電流源を設けていないので、第1の具体例に比べて電流駆動部の面積を小さくすることができる。

## 【0104】

なお、本具体例の電流駆動部においては、第1～第6の電流源全てに出力部と接続するためのバイパス経路が設けられていたが、例えば第5の電流源22i<sub>4</sub>と第6の電流源22i<sub>5</sub>のみにバイパス経路を設けるなど、表示装置の設計によっては一部の電流源にのみバイパス経路を設けてもよい。すなわち、D/Aコンバータから一時的に出力される電流は、必ずしも設定値の最大電流でなくてもよい。

## 【0105】

また、本具体例では、各ビットの電流源に電流を流すためのスイッチSW<sub>A0</sub>～SW<sub>A5</sub>の動作を共通の信号Aによって制御しているが、スイッチSW<sub>A0</sub>～SW<sub>A5</sub>がそれぞれ独立した信号A<sub>0</sub>～A<sub>5</sub>によって制御されるように設計してもよい。この上で、他の信号線に接続される複数の電流駆動部に、1つのタイミング制御部9から共通の信号A<sub>0</sub>～A<sub>5</sub>を出力するように設定することもできる。この際に、電流設定時にオン状態にする電流源の組み合わせを最適化するようにタイミング制御部9の動作をプログラムしておくこともできる。これにより、図6に示す電圧のオーバーシュート（一時的に設定電圧より下がること）を小さくすることができるので、電流駆動部及び電流発生部を流れる電流値をより速く目標値に到達させることができるとなる。

## 【0106】

## - 第3の具体例 -

図7は、第1の実施形態に係る有機EL表示装置における、電流駆動部の第3の具体例を示す回路図である。本具体例の電流駆動部では、電流加算型D/Aコンバータの第1～第6の電流源を用いて電流設定時の所定の期間に設定電流以上の電流を流す点は第2の具体例と同じであるが、設定電流以上の電流を流した後、段階的にD/Aコンバータに流れる電流値を低減させる点が異なる。

10

20

30

40

50

## 【0107】

図7に示すように、本具体例に係る電流駆動部は、第1の具体例と同一構成のD/Aコンバータに加え、第1の電流源 $22i_0$ 、第2の電流源 $22i_1$ 、第3の電流源 $22i_2$ 、第4の電流源 $22i_3$ 、第5の電流源 $22i_4$ 、第6の電流源 $22i_5$ とD/Aコンバータの出力部とをそれぞれ結ぶバイパス経路と、このバイパス経路上にそれぞれ設けられた、第1の電流源 $22i_0$ とD/Aコンバータの出力部の間に設けられたスイッチ $SW_{A_0}$ 、第2の電流源 $22i_1$ とD/Aコンバータの出力部の間に設けられたスイッチ $SW_{A_1}$ 、第3の電流源 $22i_2$ とD/Aコンバータの出力部の間に設けられたスイッチ $SW_{A_2}$ 、第4の電流源 $22i_3$ とD/Aコンバータの出力部の間に設けられたスイッチ $SW_{A_3}$ 、第5の電流源 $22i_4$ とD/Aコンバータの出力部の間に設けられたスイッチ $SW_{A_4}$ 、及び第6の電流源 $22i_5$ とD/Aコンバータの出力部の間に設けられたスイッチ $SW_{A_5}$ とを有している。10

## 【0108】

本具体例と第2の具体例との違いは、スイッチ $SW_{A_0} \sim SW_{A_5}$ がそれぞれ互いに独立した信号 $A_0 \sim A_5$ によって、電流設定期間中にオン状態からオフ状態へと段階的に切り替えられる点である。この信号 $A_0 \sim A_5$ は、図1に示すタイミング制御部9から所定のタイミングで出力される。

## 【0109】

次に、本具体例に係る電流駆動部の電流設定期間中の動作を図を用いて説明する。

## 【0110】

図8は、本具体例に係る有機EL表示装置において、電流設定時の電流発生部から有機EL素子に流れる電流Iの変化、及び画素5に印加される電圧 $V_o$ の変化を示すグラフ図である。20

## 【0111】

同図に示すように、本具体例の有機EL表示装置においては、電流設定時の時間0から時間Tまでの間に、電流駆動部11からデータ3F（「3F」は16進数表記）に応じた64階調での最大電流 $I_{3F}$ が流れる。この期間、画素5の入力部に印加される電圧 $V_o$ は急激に低下し、目標電圧 $V_{ta}$ に近づく。

## 【0112】

次に、時間Tでは、例えば、スイッチ $SW_{A_4}$ 及びスイッチ $SW_{A_5}$ を共にオフ状態に切替え、上位2ビット分を表示すべき正しいデータに置き換える。この状態を時間Tから時間3Tまで続く。この期間中に画素5に流れる電流は、より目標電流に近づく。この間、画素5の入力部に印加される電圧は徐々に低下し、時間3Tでは安定電圧 $V_{ta}$ をわずかに下回る。30

## 【0113】

次に、時間3Tの時点で、例えば、スイッチ $SW_{A_2}$ 及びスイッチ $SW_{A_3}$ をさらにオフ状態に切替え、さらに2ビット分を表示すべき正しいデータに置き換える。この状態が時間3Tから時間5Tまで続く。これに伴って、時間3Tから時間5Tまでの間に、画素5に印加される電圧はさらに安定電位に近づく。

## 【0114】

次いで、時間5Tの時点で、例えば、スイッチ $SW_{A_0}$ 及びスイッチ $SW_{A_1}$ をさらにオフ状態に切替え、電流駆動部の出力電流を、レジスタに設定された6ビットすべてのデータ信号に従った設定電流とする。40

## 【0115】

以上のように、本具体例に係る電流駆動部の出力電流の値を段階的に変化させることにより、画素5に印加される電圧のオーバーシュート量を低減することができ、第2の具体例と比べてもより迅速に画素5に流れる電流を目標電流に到達させることができる。

## 【0116】

なお、この例では、時間Tの後、一定の間隔（2T間隔）で電流駆動部に流れる電流量を変化させたが、任意のタイミング及び期間で変化させてもよい。例えば、最初に所定の期50

間に電流駆動部に最大設定量の電流を流して画素 5 に流れる電流の値を目標値に近づけた後、電流駆動部に流れる電流値を短時間ずつ変化させていき、最終的にレジスタに設定されたデータ信号に応じた電流を流してもよい。この場合にも、目標電流に到達するのに必要な時間を従来の電流駆動部よりも短くできる。あるいは、最大設定量の電流を流す時間を含め、一定の時間 T ごとに電流駆動部に流れる電流量を変化させててもよい。

#### 【 0 1 1 7 】

なお、このような制御は図 1 に示すタイミング制御部 9 から出力される信号 A 0 ~ A 5 によって行われる。

#### 【 0 1 1 8 】

また、本具体例の電流駆動部において、最大電流またはそれに近い電流を流した後、上位ビットから順に 2 ビット分ずつ設定電流に切替えていったが、一度に設定通りに戻すビット数を 3 ビット以上または 1 ビットにしてもよい。設定電流に戻す順番は、本具体例のように上位ビットから下位ビットへ順次行なうことが好ましいが、任意の順序で行うこともできる。

#### 【 0 1 1 9 】

- 第 4 の具体例 -

本具体例では、第 3 の具体例に係る有機 E L 表示装置を実現するためのタイミング制御部の構成を説明する。すなわち、本具体例のタイミング制御部は、電流駆動部を流れる電流値を段階的に変化させるような信号 A 0 ~ A 5 を出力する。

#### 【 0 1 2 0 】

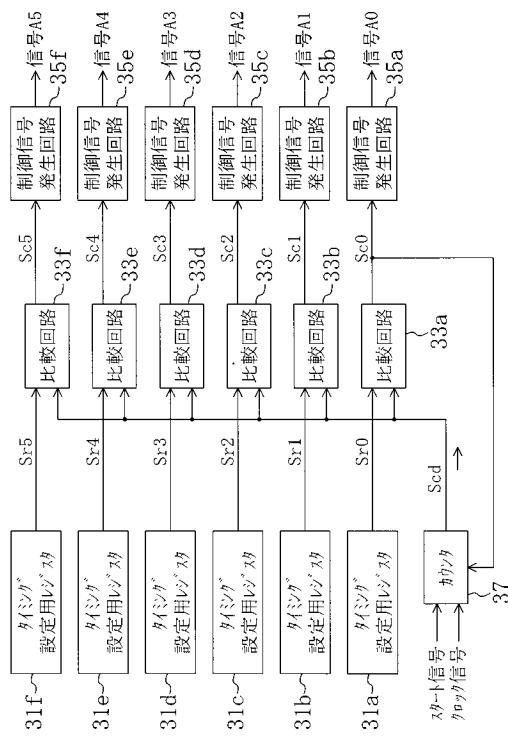

図 9 は、第 1 の実施形態の第 4 の具体例に係るタイミング制御部の構成例を示すブロック図である。

#### 【 0 1 2 1 】

同図に示すように、本具体例のタイミング制御部は、それぞれレジスタデータ信号 S r 0 、 S r 1 、 S r 2 、 S r 3 、 S r 4 及び S r 5 をそれぞれ出力するためのタイミング設定用レジスタ 3 1 a 、 3 1 b 、 3 1 c 、 3 1 d 、 3 1 e 及び 3 1 f と、スタート信号とクロック信号とを受けてカウント動作を行い、カウントした値をカウントデータ信号 S c d として出力するカウンタ 3 7 と、カウンタデータ信号 S c d とレジスタデータ信号 S r 0 ~ S r 5 とをそれぞれ比較し、これらが互いに一致する場合に一致信号 S c 0 ~ S c 5 をそれぞれ出力する比較回路 3 3 a 、 3 3 b 、 3 3 c 、 3 3 d 、 3 3 e 、 3 3 f と、一致信号 S c 0 ~ S c 5 をそれぞれ受けて信号 A 0 ~ A 5 をそれぞれ出力する制御信号発生回路 3 5 a 、 3 5 b 、 3 5 c 、 3 5 d 、 3 5 e 及び 3 5 f とを有している。

#### 【 0 1 2 2 】

例えば、電流設定時において、上位ビットから 1 ビットずつ正しいデータに置き換えてゆく場合、タイミング設定用レジスタ 3 1 f 、 3 1 e 、 3 1 d 、 3 1 c 、 3 1 b 及び 3 1 a にはそれぞれデータ " 1 " 、 " 2 " 、 " 3 " 、 " 4 " 、 " 5 " 、 " 6 " があらかじめ設定されており、これらのレジスタデータ信号が比較回路 3 3 f 、 3 3 e 、 3 3 d 、 3 3 c 、 3 3 b 及び 3 3 a に出力される。

#### 【 0 1 2 3 】

また、カウンタ 3 7 では、スタート信号の入力とともに、クロック信号に同期したカウント動作が開始される。そして、各比較回路に出力されるカウンタデータ信号が " 1 " 、 " 2 " ... と一定の時間で順に変化するのに従って、比較回路 3 3 f 、 3 3 e ... からは順次一致信号 S c 5 、 S c 4 ... が制御信号発生回路 3 5 f 、 3 5 e ... に出力される。このとき、最後に出力された一致信号 S c 0 がカウンタ 3 7 にフィードバックされると、カウンタ 3 7 の動作はリセットされる。

#### 【 0 1 2 4 】

そして、制御信号発生回路 3 5 f 、 3 5 e 、 3 5 d ... 、 3 5 a からは、一定の時間をおいてそれぞれ信号 A 5 、 A 4 、 A 3 ... 、 A 0 が電流駆動部へ出力される。なお、一度出力された信号 A 5 、 A 4 、 A 3 ... 、 A 0 は、電流設定時が終了するまで継続して出力される。

#### 【 0 1 2 5 】

10

20

30

40

50

以上のような回路動作により、電流設定時の電流駆動部に流す電流を段階的に変化させることができる。

【0126】

本具体例では、信号A5～A0が一定の時間間隔で出力される例を説明したが、タイミング設定用レジスタに設定させておくデータを変えれば、信号A5～A0が出力されるタイミングを変えることができる。

【0127】

また、本具体例では、第3の具体例に係る有機EL表示装置を実現するためのタイミング制御部の一例を示したが、上述の制御を行なう回路構成は図9に示す構成に限られない。

【0128】

なお、本具体例に係るタイミング制御部は、電流駆動部ごとに設けられていてもよいし、複数の電流駆動部に共用されて、LSIにつき1つのみ設けられていてもよい。特に、信号A0～A5の各信号が表示パネル上で共通に用いられる場合には、タイミング制御部はパネルにつき1つであってもよい。このように、タイミング制御部が複数の電流駆動部に共用される場合では、回路面積の増加を抑えることができる。

【0129】

(第2の実施形態)

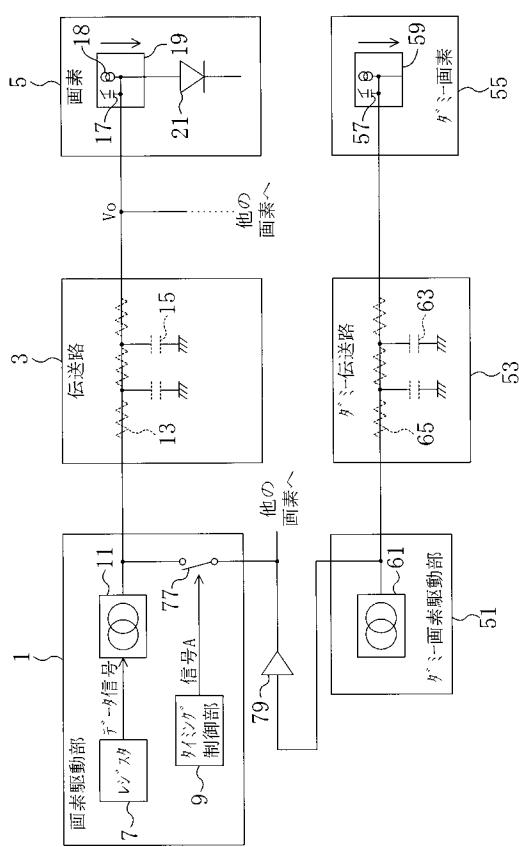

図10は、本発明の第2の実施形態に係る有機EL表示装置の構成を概略的に示すブロック回路図である。同図において、図1に示した部分と同一部分については同じ符号を付し、説明を省略する。

【0130】

図10に示すように、本実施形態の有機EL表示装置の特徴は、第1の実施形態に係る有機EL表示装置に、電流設定時における電流駆動部11の安定出力電圧を設定するための電圧設定手段50と、電流駆動部11からの出力電圧と電圧設定手段50からの出力電圧とを比較し、その比較結果をタイミング制御部9に出力する比較回路67とが付加されていることである。ここで、「電流駆動部の安定出力電圧」とは、電流設定時において、画素5の入力部に印加される電圧が安定電圧(図4に示すVta)にある時の電流駆動部の出力電圧のことを意味するものとする。

【0131】

電圧設定手段50は、ソース駆動回路と同じチップ上に設けられる場合と、ソース駆動回路から表示パネル側にまたがって設けられる場合とがある。後者については後の具体例で説明する。

【0132】

ソース駆動回路内に設けられる場合の電圧設定手段50は、データ信号に応じた電流駆動部11についての安定出力電圧があらかじめ設定されたレジスタを有している。この安定出力電圧は、例えば、異なる輝度表示を行なう際の電流駆動部11の出力電圧を測定するなどして求められる。そして、電流設定時には、レジスタに設定された安定出力電圧が比較回路に出力される。

【0133】

一方、比較回路67は、電圧設定手段50から出力された安定出力電圧と電流駆動部11からの出力電圧とを比較する。そして、低輝度表示から高輝度表示に切り替わる際の電流設定時においては、電流駆動部11からの出力電圧が電圧設定手段50の出力電圧と同等またはそれ以下になる場合には、比較回路67からタイミング制御部9に切替え信号Schが outputされる。これに対し、高輝度表示から低輝度表示に切り替わる際の電流設定時においては、電流駆動部11からの出力電圧が電圧設定手段50の出力電圧と同等またはそれ以上になる場合には、比較回路67からタイミング制御部9に切替え信号Schが outputされる。ただし、表示動作では一度低輝度表示を行ってから画像表示を行なう制御が行われることが多いので、低輝度表示から高輝度表示の変化時と高輝度表示から低輝度表示の変化時とで比較回路67の設定を変えることは、必ずしも必要ではない。

【0134】

10

20

20

30

40

50

電流設定時において、タイミング制御部 9 に切替え信号 S c h が入力されると、タイミング制御部 9 の動作がリセットされて、電流駆動部 11 からの出力電流は、データ信号に応じた設定電流に切り替わる。この際に、本実施形態では、タイミング制御部 9 が出力する信号 A によって電流駆動部 11 の出力電流がデータ信号通りの設定電流になる。

#### 【 0 1 3 5 】

以上のような電圧設定手段 50 と、比較回路 67 を設けたことにより、電流駆動部 11 の出力電流を適切なタイミングで切り替えることができるので、従来に比べてより短時間で電流発生部 19 からの出力電流を目標電流に到達させることができるとなる。従って、本実施形態の有機 E L 表示装置は、従来は困難であった高精細、高解像度の画像表示を、画質の低下を来すことなく実現することができる。10

#### 【 0 1 3 6 】

なお、本実施形態で説明した電圧設定手段 50 と比較回路 67 とは、第 1 の実施形態の全ての具体例に適用することができる。

#### 【 0 1 3 7 】

また、本実施形態の有機 E L 表示装置において、上述のように、電圧設定手段 50 をソース駆動回路と同一チップ内に設けた場合には、電圧設定手段 50 をパネル側にまたがって設ける場合に比べ既存の表示パネルを使用できるという利点がある。

#### 【 0 1 3 8 】

また、比較回路 67 は、パネル側に設けてもよいが、ソース駆動回路内に設ける方がより好ましい。なお、この比較回路 67 の一例として、差動増幅回路を用いたコンパレータがある。20

#### 【 0 1 3 9 】

なお、電圧設定手段 50 は、電流駆動部 11 ごとに設けられてもよいし、複数の電流駆動部 11 に共用されていてもよい。ソース駆動回路及び表示パネルを小面積化する場合には、電圧設定手段 50 が複数の電流駆動部 11 に共用される方が好ましい。この際に、ソース駆動回路が設けられた半導体チップ毎に 1 つ以上の電圧設定手段 50 を設けておくとさらに好ましい。これにより、表示パネルを複数のチップ上に設けられたソース駆動回路で駆動する際に、同一規格のチップを用いることができる。ソース駆動回路の入出力構成を簡易にすることができる。加えて、電圧設定手段 50 がソース駆動回路の一部に固めて配置されている場合に比べ、チップ間のばらつきやパネル側の位置によるばらつきの影響を低減することができる。30

#### 【 0 1 4 0 】

なお、以上の説明では、ソース駆動回路が表示パネルの外部に設けられていることを前提としていたが、表示パネルの内部にソース駆動回路が作り込まれている場合もある。これは、他の具体例および実施形態でも共通である。

#### 【 0 1 4 1 】

##### - 第 2 の実施形態の具体例 -

本発明の第 2 の実施形態の一具体例として、電圧設定手段 50 が、ソース駆動回路のチップ上と表示パネル上にまたがって設けられている場合の有機 E L 表示装置について説明する。40

#### 【 0 1 4 2 】

図 11 は、第 2 の実施形態の具体例に係る有機 E L 表示装置の構成を概略的に示すブロック回路図である。同図において、図 10 と同一の部分については同一の符号を付している。

#### 【 0 1 4 3 】

図 11 に示すように、本具体例に係る有機 E L 表示装置では、図 10 に示す電圧設定手段 50 が、ダミー電流駆動部 61 を有するダミー画素駆動部 51 と、表示パネル上に設けられたダミー画素 55 と、ダミー電流駆動部 61 からの出力電流をダミー画素 55 に伝達するダミー伝送路 53 とで構成されている。なお、ここでいう「ダミー」とは、画像表示に直接関わっていない、という意味である。50

## 【 0 1 4 4 】

ダミー電流駆動部 6 1 は、電流駆動部 1 1 と同様の構成を有しており、例えば 6 4 階調表示の表示装置の場合、6 ビットの電流加算型 D / A コンバータを有している。

## 【 0 1 4 5 】

また、ダミー伝送路 5 3 は、伝送路 3 とほぼ同一の構成を有しており、ソース駆動回路と表示パネルとを接続する配線や、パネル上に設けられた信号線を有している。図 1 1 には、ダミー伝送路における配線抵抗 6 5 及び浮遊容量 6 3 も示している。

## 【 0 1 4 6 】

ダミー画素 5 5 は、ダミー画素入力容量 5 7 及び電流源を有し、電流発生部 1 9 と同一構成を有するダミー電流発生部 5 9 を有している。ただし、有機 E L 素子 2 1 は必ずしも設けられている必要はない。

## 【 0 1 4 7 】

本具体例に係る有機 E L 表示装置では、ダミー電流駆動部 6 1 からの出力電圧はコンパレータ 6 7 a の(+)側入力部に入力される。一方、コンパレータ 6 7 a の(-)側入力部には電流駆動部 1 1 からの出力電圧が入力される。そして、コンパレータ 6 7 a は電流駆動部 1 1 の出力電圧とダミー電流駆動部 6 1 の出力電圧とを比較し、その比較結果をタイミング制御部 9 に出力する。なお、図 1 1 には、比較回路の一例として差動増幅回路を有するコンパレータを示すが、他の構成を有する比較回路を用いてもよい。

## 【 0 1 4 8 】

本具体例では、ダミー画素駆動部 5 1 から非表示時を除く期間を通して任意の固定電流が流れれる。

## 【 0 1 4 9 】

例えば、図 3 に示す第 1 の実施形態の第 1 の具体例に係る有機 E L 表示装置に本具体例のダミー画素駆動部 5 1 、ダミー伝送路 5 3 及びダミー画素 5 5 を付加する場合には、付加電流源 2 4 を流れる電流  $I_x$  に等しい電流をダミー電流駆動部 6 1 に引き込む。これによって、ダミー電流駆動部 6 1 からの出力電圧は、出力電流  $I_x$  における安定出力電圧となる。

## 【 0 1 5 0 】

本具体例の有機 E L 表示装置では、コンパレータ 6 7 a が、この安定出力電圧と電流駆動部 1 1 の出力電圧とを比較する。この際に、低輝度表示から高輝度表示に切り替わる際の電流設定時においては、電流駆動部 1 1 からの出力電圧がダミー電流駆動部 6 1 からの出力電圧と同等またはそれ以下になる場合には、コンパレータ 6 7 a からタイミング制御部 9 に切替え信号 S ch が出力される。これに対し、高輝度表示から低輝度表示に切り替わる際の電流設定時においては、電流駆動部 1 1 からの出力電圧が電圧設定手段 5 0 の出力電圧と同等またはそれ以上になる場合には、コンパレータ 6 7 a からタイミング制御部 9 に切替え信号 S ch が出力される。

## 【 0 1 5 1 】

また、コンパレータ 6 7 a が動作するのは電圧が変化する過渡期であるので、電流駆動部 1 1 からの出力電圧を V 1 、ダミー電流駆動部 6 1 の出力電圧を V 2 とすると、V 1 と V 2 ( k は正の任意の値 ) とを比較するようにしてもよい。

## 【 0 1 5 2 】

タイミング制御部 9 に切替え信号 S ch が入力されると、タイミング制御部 9 の動作がリセットされて、電流駆動部 1 1 からの出力電流は、データ信号に応じた設定電流に切り替わる。

## 【 0 1 5 3 】

以上のように駆動することで、電流駆動部 1 1 の出力電流を適切なタイミングで切り替えることができるので、従来に比べてより短時間で画素 5 を流れる電流の値を目標電流に到達させることが可能となる。

## 【 0 1 5 4 】

なお、この例ではダミー電流駆動部 6 1 に流れる電流を  $I_x$  に設定したが、ダミー電流駆

10

30

40

50

動部 6 1 の安定出力電圧を、電流駆動部 1 1 本来の安定出力電圧よりも低くする、あるいは高くするような電流値に設定してもよい。つまり、本具体例のダミー画素駆動部 5 1 では、ダミー電流駆動部 6 1 に流れる電流値を任意に設定することで、高輝度表示から低輝度表示に切り替わる際の充電時間、または低輝度表示から高輝度表示に切り替わる際の放電時間を最短にすることができる。

#### 【 0 1 5 5 】

実際の表示装置では、表示パネルの特性を実測することなどによって、最適なダミー電流駆動部 6 1 の出力電流値を求める。

#### 【 0 1 5 6 】

なお、本具体例の有機 E L 表示装置において、1組のダミー画素駆動部 5 1 及びダミー伝送路 5 3 及びダミー画素 5 5 は、面積の増加を抑えるために、複数の電流駆動部 1 1 の動作制御に共通に用いられることが好ましい。10

#### 【 0 1 5 7 】

なお、有機 E L 表示装置の表示パネルが比較的大きい場合、ソース駆動回路を設けた複数の半導体チップで駆動することも多い。この場合には、ソース駆動回路とダミー画素駆動部 5 1 とが併せて作り込まれた同じ半導体チップを、表示パネルの額縁部分に複数枚並べることが好ましい。これにより、表示パネル上のダミー伝送路 5 3 同士及びダミー画素 5 5 同士の間隔を所定の間隔（例えば、互いに等間隔など）に設定することとなるので、有機 E L 画素や伝送路の特性ばらつきの影響を低減することができるようになる。また、使用するソース駆動回路のチップが1種類で済むので、ソース駆動回路の入出力構成を簡単にすることができる。20

#### 【 0 1 5 8 】

この例に限らず、表示パネル上に複数のダミー伝送路 5 3 及びダミー画素 5 5 を形成する場合には、ダミー伝送路 5 3 及びダミー画素 5 5 を均等に配置することが好ましい。

#### 【 0 1 5 9 】

このように、ダミー伝送路 5 3 及びダミー画素 5 5 を表示パネルの複数箇所に設ける場合には、それぞれのダミー伝送路 5 3 に接続されたダミー画素駆動部 5 1 の出力部（またはダミー電流駆動部 6 1 の出力部）同士を互いに接続することもできる。これにより、表示パネル上での有機 E L 画素や伝送路のばらつきを平均化することができる。また、複数のダミー画素駆動部 5 1 、複数のダミー伝送路 5 3 及び複数のダミー画素 5 5 のうち一部の部材に不具合が生じても残りの部分で動作が補償されるので、動作に不具合を生じにくくすることができる。30

#### 【 0 1 6 0 】

##### （第 3 の実施形態）

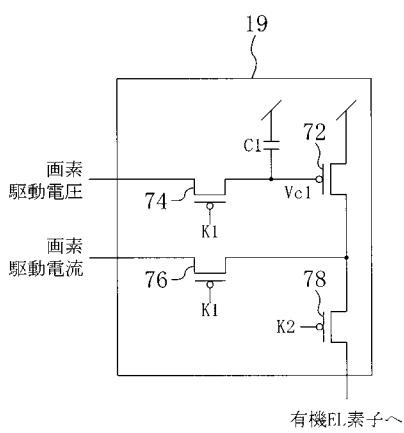

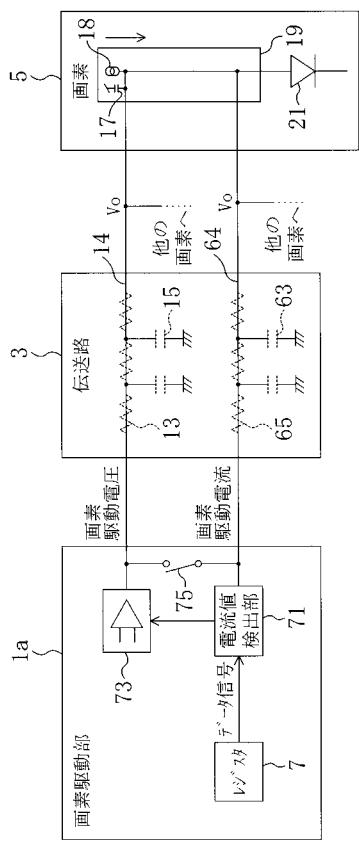

図 1 2 は、本発明の第 3 の実施形態に係る電流発生部の構成を示す回路図であり、図 1 3 は、図 1 2 に示す電流発生部を用いた第 3 の実施形態に係る有機 E L 表示装置の一例を概略的に示すブロック回路図である。

#### 【 0 1 6 1 】

図 1 3 に示すように、本実施形態の有機 E L 表示装置の特徴は、画素 5 に駆動電圧を供給するための電圧供給手段と、画素 5 に駆動電流を供給するための電流供給手段とを備えていることである。この電流検出手段は、電圧供給手段の出力電圧をフィードバック制御するために設けられている。40

#### 【 0 1 6 2 】

以下、本実施形態の有機 E L 表示装置の具体的な構成を説明する。

#### 【 0 1 6 3 】

図 1 3 に示すように、本実施形態の有機 E L 表示装置は、表示パネル（図示せず）と、表示パネル上に設けられた画素 5 と、画素 5 に接続された伝送路 3 と、ソース駆動回路に含まれ、伝送路 3 を介して画素 5 に駆動電圧及び駆動電流を供給するための画素駆動部 1 を備えている。

#### 【 0 1 6 4 】

10

20

30

40

50

画素駆動部 1 a は、画素 5 に駆動電圧を供給するための電圧駆動部 7 3 と、画素 5 に流れる駆動電流を設定すると共に、該駆動電流の電流値を検出して検出結果を電圧駆動部 7 3 へ出力する電流値検出部 7 1 と、画像データであるデータ信号をラッチし、該データ信号を電流値検出部 7 1 に出力するレジスタ 7 とを有している。

#### 【 0 1 6 5 】

また、伝送路 3 は、画素 5 に駆動電圧を伝達するための配線及び駆動電圧用信号線 1 4 と、画素 5 に駆動電流を伝達するための配線及び駆動電流用信号線 6 4 とを有している。

#### 【 0 1 6 6 】

そして、画素 5 は、入力電流に応じて発光する有機 E L 素子 2 1 と、伝送路 3 を介して電圧駆動部 7 3 及び電流値検出部 7 1 に接続され、有機 E L 素子 2 1 に駆動電流を供給するため電流発生部 1 9 とを有している。

#### 【 0 1 6 7 】

そして、図 1 2 に示すように、電流発生部 1 9 は、ゲート電極に駆動電圧用信号線 1 4 に接続され、ソースに電源電圧が供給された、有機 E L 素子 2 1 に駆動電流を供給するための P チャネル型の T F T 7 2 と、一端が T F T 7 2 のゲート電極に接続され、ゲート電圧 V c 1 を保持するための容量 C 1 と、容量 C 1 及び T F T 7 2 のゲート電極と駆動電圧用信号線 1 4 との接続経路上に介設され、第 1 の制御信号 K 1 によって動作制御された第 1 のスイッチ用トランジスタ 7 4 ( 電圧用スイッチ ) と、T F T 7 2 と有機 E L 素子 2 1 との間に介設され、第 1 の制御信号の逆相信号である第 2 の制御信号 K 2 によって動作制御された第 2 のスイッチ用トランジスタ 7 8 とを有している。また、電流発生部 1 9 では、T F T 7 2 と第 2 のスイッチ用トランジスタ 7 8 との接続点は、駆動電流用信号線 6 4 に接続されており、T F T 7 2 及び第 2 のスイッチ用トランジスタ 7 8 と駆動電流用信号線 6 4 との間には、制御信号 K 1 によって動作制御された第 3 のスイッチ用トランジスタ 7 6 ( 電流用スイッチ ) が介設されている。ここで、各スイッチ用 M O S トランジスタは、すべて P チャネル型の T F T であるが、これに限らず、スイッチ動作が可能な素子であれば用いることができる。なお、図 1 2 に示す容量 C 1 及び T F T 7 2 は、それぞれ図 1 3 に示す画素入力容量 1 7 と電流源 1 8 に相当する。

#### 【 0 1 6 8 】

次に、電流発生部 1 9 の動作を説明する。

#### 【 0 1 6 9 】

まず、電流設定時には、制御信号 K 1 及び制御信号 K 2 によって第 1 のスイッチ用トランジスタ 7 4 及び第 3 のスイッチ用トランジスタ 7 6 が共にオン状態、第 2 のスイッチ用トランジスタ 7 8 がオフ状態に設定される。これにより、電圧駆動部 7 3 からの画素駆動電圧が第 1 のスイッチ用トランジスタ 7 4 を介して容量 C 1 及び T F T 7 2 のゲート電極に供給され、第 3 のスイッチ用トランジスタ 7 6 を介して画素駆動電流が T F T 7 2 に流れれる。そして、この電流設定時に容量 C 1 にゲート電圧 V c 1 分の電荷が充電されると、T F T 7 2 には一定電流 ( 目標電流 I t a ) が流れれるようになる。

#### 【 0 1 7 0 】

続いて、表示時には、制御信号 K 1 及び制御信号 K 2 によって第 1 のスイッチ用トランジスタ 7 4 及び第 3 のスイッチ用トランジスタ 7 6 が共にオフ状態、第 2 のスイッチ用トランジスタ 7 8 がオン状態に設定される。このとき、充電された容量 C 1 によってゲート電極 V c 1 が保持されるので、目標電流 I t a が T F T 7 2 から有機 E L 素子 2 1 に流れ続ける。

#### 【 0 1 7 1 】

次に、本実施形態の画素駆動部 1 a の動作及び特徴について簡単に説明する。

#### 【 0 1 7 2 】

従来の有機 E L 表示装置では、低輝度表示から高輝度表示に切り替わる際に、画素 5 内の T F T を介した電源電圧によって充電されていた。しかし、T F T の出力インピーダンスが高かったため、従来は画素入力容量 1 7 を高速に充電することができなかつた。

#### 【 0 1 7 3 】

10

20

30

40

50

これに対し、本実施形態の有機EL表示装置では、電流設定時において、電圧駆動部73から駆動電圧用信号線14を介して画素5に画素駆動電圧が供給される。このとき、電圧駆動部73の出力インピーダンスは、従来の有機EL表示装置における電流駆動部よりも低くなっている。そのため、本実施形態の有機EL表示装置では、従来の有機EL表示装置より高速に画素入力容量17(容量C1)を充電することができる。

#### 【0174】

また、電流設定時における電流値検出部71では、画素5から駆動電流用信号線64を介して流れる電流値を検出し、その検出結果を電圧駆動部73にフィードバックする。

#### 【0175】

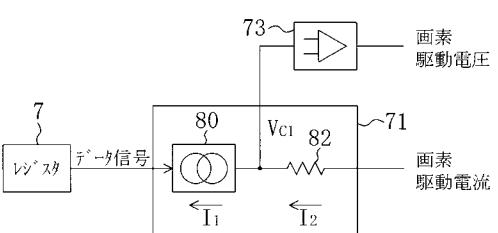

図14は、本実施形態の有機EL表示装置に用いられる電流値検出部71の構成例を示す10

プロック回路図である。

#### 【0176】

同図に示す電流値検出部71は、レジスタ7から出力されるデータ信号を受けて画素5の駆動電流を流すための電流駆動部80と、画素5と電流駆動部80との間に設けられた抵抗82とを有している。そして、電流駆動部80と抵抗82とを接続する配線は、電圧駆動部73に接続されている。

#### 【0177】

この電流値検出部71において、レジスタからのデータ信号によって設定された駆動電流を $I_1$ 、画素5がら流れ込む画素駆動電流を $I_2$ とすると、電流値検出部71から電圧駆動部73に出力される電圧 $V_{c1}$ は、駆動電流 $I_1$ と画素駆動電流 $I_2$ とが一致するときに安定する。また、画素駆動電流 $I_2$ が駆動電流 $I_1$ よりも大きい場合には電圧 $V_{c1}$ が上昇して画素駆動電流 $I_2$ が減少し、駆動電流 $I_1$ が画素駆動電流 $I_2$ よりも大きい場合には、電圧 $V_{c1}$ が低下して画素駆動電流 $I_2$ が増加するようにフィードバックがかかる。その結果、電圧駆動部73から出力される画素駆動電圧は、適切な値で安定化する。ここで、画素駆動電流 $I_2$ の伝達経路には画素入力容量17が存在しないので、伝達経路全体での浮遊容量は小さくなっている。高速に電流値の検出を行なうことができる。従って、本実施形態の有機EL表示装置においては、従来に比べて、画素5に供給する電流及び電圧の値を迅速に目標値に到達させることができるので、より高精度の表示が可能となっている。

#### 【0178】

なお、電流値検出部71は、画素5からの画素駆動電流を検出して電圧駆動部73にフィードバックできる構成であれば、図14に示す構成に限られない。

#### 【0179】

また、本実施形態の電流値検出部71は、表示パネル上の電流源18がPチャネル型のTFTの場合に用いられる。電流源18がNチャネル型のTFTで構成される場合には、画素駆動電流が大きくなるほど電圧駆動部73への出力電圧が低くなるように、電流値検出部71を構成すればよい。

#### 【0180】

なお、本実施形態では電流発生部19が図12に示すような構成を有する例について説明したが、画素駆動電圧と画素駆動電流とが入力されることによって有機EL素子21に駆動電流を出力できる構成であれば図12に示す構成に限られない。

#### 【0181】

##### (第4の実施形態)

図15は、本発明の第4の実施形態に係る有機EL表示装置の一例を概略的に示すプロック回路図である。

#### 【0182】

同図に示すように、第4の実施形態に係る有機EL表示装置は、第3の実施形態に係る有機EL表示装置において、電圧駆動部73の出力部と電流値検出部71の出力部とを所定の期間だけ短絡するための短絡手段をさらに設けたものである。なお、短絡手段以外の部分は、第3の実施形態の有機EL表示装置と同一であるので、説明を省略する。

10

20

30

40

50

**【 0 1 8 3 】**

図15に示す例では、スイッチ75によって、画素駆動電圧及び画素駆動電流の出力開始時（電流設定時の開始時）に所定の期間だけ電圧駆動部73の出力部と電流値検出部71の出力部とが電気的に接続される。このスイッチ75としては、例えばNチャネル型MOSFETとPチャネル型MOSFETなどで構成されるトランスマニアゲートなどが用いられるが、それ以外の構成でもよい。また、このスイッチ75は、表示パネル上の信号線間に配置されていてもよいが、ソース駆動回路と同一のチップ上に設けられている方が好ましい。

**【 0 1 8 4 】**

本実施形態の有機EL表示装置では、第3の実施形態の有機EL表示装置と同様に、電圧駆動部73からの出力インピーダンスは低くなっているので、高速に画素入力容量17を充電することができる。また、画素入力容量17が画素駆動電流の伝達経路にないため、電流値検出部71では高速に電流値を検出することができる。

**【 0 1 8 5 】**

特に、本実施形態の有機EL表示装置では、電流値検出部71の出力部が、出力インピーダンスの低い電圧駆動部73の出力部と所定の期間短絡するので、電流の検出をより高速に行うことができる。このため、本実施形態の有機EL表示装置では、電流設定時に、第3の実施形態の有機EL表示装置と比べて画素駆動電流及び画素駆動電圧の値をより迅速に目標電流に到達させることができる。

**【 0 1 8 6 】****( 第5の実施形態 )**

図16は、本発明の第5の実施形態に係る有機EL表示装置の構成を概略的に示すブロック回路図である。

**【 0 1 8 7 】**

本実施形態の有機EL表示装置は、図1に示す第1の実施形態の有機EL表示装置に出力インピーダンスの低い低インピーダンス手段、例えば電圧駆動部79などの電圧供給手段を附加したものである。この電圧駆動部79は、他の電圧源に接続された電流増幅用のバッファであってもよい。なお、第1の実施形態の有機EL表示装置と同一の部分については説明を省略する。

**【 0 1 8 8 】**

図16に示すように、本実施形態の有機EL表示装置が第1の実施形態に係る有機EL表示装置と異なるのは、任意の一定電圧を出力するための電圧駆動部79と、電圧駆動部79の出力部と電流駆動部11の出力部とを接続する配線上に介設されたスイッチ77を備えている点と、タイミング制御部9から出力される信号Aがスイッチ77の動作を制御している点である。

**【 0 1 8 9 】**

電流設定時に、スイッチ77は、信号Aによって電流設定時に所定の期間だけオン状態となるように制御されている。そして、スイッチ77がオフ状態になると、データ信号に応じた設定電流が電流駆動部11から出力される。

**【 0 1 9 0 】**

このため、本実施形態の有機EL表示装置では、高輝度（白）表示から低輝度（黒）表示に切り替わる際の電流設定時の開始後に、出力インピーダンスの低い電圧駆動部79を用いて浮遊容量15や画素入力容量17を迅速に充電できるので、画素5に流れる電流を従来よりも短時間で目標電流に到達させることができる。

**【 0 1 9 1 】**

また、低輝度表示から高輝度表示に切り替わる際の電流設定時にも、浮遊容量15や画素入力容量17に保持された電荷を速やかに引き抜くことができるので、画素5に流れる電流を従来よりも短時間で目標電流に到達させることができる。

**【 0 1 9 2 】**

従って、本実施形態の有機EL表示装置では、高輝度表示から低輝度表示に切り替わる際

10

20

30

40

50

と低輝度表示から高輝度表示に切り替わる際のいずれの場合にも、画素に流れる電流の値を短時間で目標値に到達させることができるので、従来よりも高解像度の表示が実現されている。

### 【0193】

なお、以上で説明した電圧駆動部79は、画素駆動部1毎に設けられていてもよいし、複数の画素駆動部1に対して1つの電圧駆動部79が共通に接続されていてもよい。小面積化が優先される場合には、複数の画素駆動部1に対して1つの電圧駆動部79が設けられている方がより好ましい。

### 【0194】

(第6の実施形態)

図17は、本発明の第6の実施形態に係る有機EL表示装置の構成を概略的に示すプロック回路図である。

### 【0195】

同図に示すように、本実施形態の有機EL表示装置は、第5の実施形態の有機EL表示装置に、図11に示すダミー画素駆動部51、ダミー伝送路53及びダミー画素55を付加した表示装置である。そして、ダミー画素駆動部51の出力部は電圧駆動部79の入力部に接続されている。電圧駆動部79は例えば電流增幅用のバッファであり、スイッチ77の導通時にはダミー画素駆動部51の出力電圧を供給する。また、スイッチ77は、電流設定時の所定の期間のみオン状態になるよう設定されている。

### 【0196】

これにより、電流設定時の所定の期間中、ダミー画素駆動部51からの出力電圧が伝送路3を介して画素5に供給される。この際に、電圧駆動部79の出力インピーダンスは低くなっているので、浮遊容量15及び画素入力容量17への充電または浮遊容量15及び画素入力容量17からの放電が迅速に完了することができる。その後、スイッチ77がオフ状態となるので、電流駆動部11からはデータ信号に応じた設定電流が流れる。

### 【0197】

本実施形態の有機EL表示装置においては、画像表示に直接関係しないダミー画素駆動部51、ダミー伝送路53及びダミー画素55を用いることで、用いる表示パネルの特性によらず実際の安定出力電圧に近い出力電圧を供給することができる。言い換えれば、表示パネルごとに電圧駆動部79の出力電圧を設定し直す必要がなくなる。

### 【0198】

また、このダミー画素駆動部51からは複数の信号線に接続された画素へ電圧を供給することができるので、画素駆動部1ごとに設ける場合に比べて回路面積の増加を抑えることができる。

### 【0199】

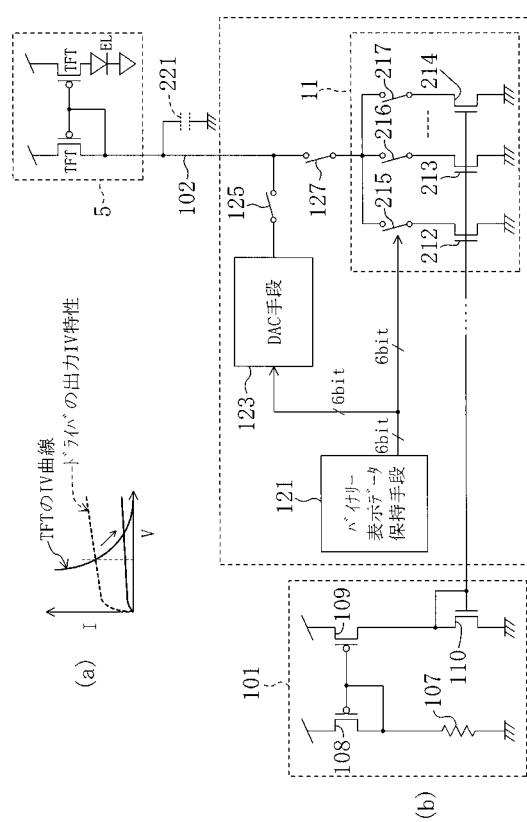

(第7の実施形態)

本発明の第7の実施形態に係る有機EL表示装置は、図16に示す第5の実施形態の有機EL表示装置において、電圧駆動部79としてDAC手段123を用い、このDAC手段123を画素駆動部1毎に設けたものである。

### 【0200】

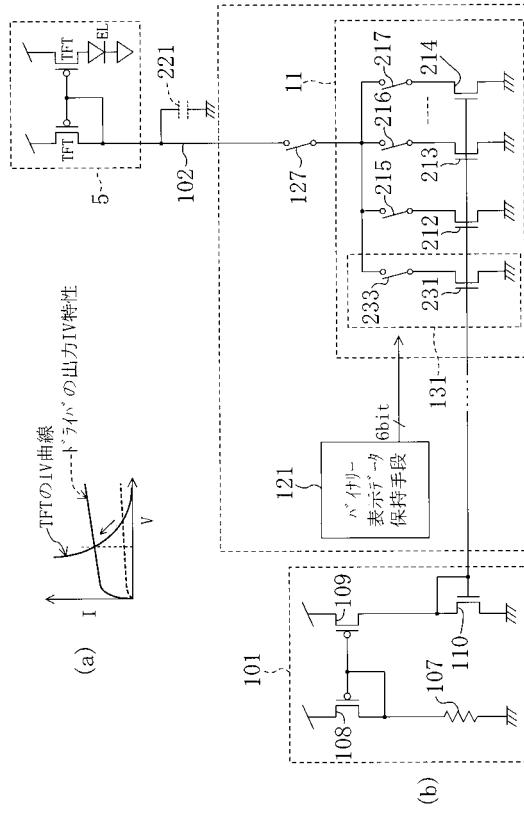

図18(a)は、本発明の第7の実施形態に係る有機EL表示装置において、白表示時(高輝度表示時)のTFTの動作点を示すグラフ図であり、(b)は、第7の実施形態に係る有機EL表示装置の構成を示すプロック回路図である。

### 【0201】

図18(b)に示すように、第7の実施形態の有機EL表示装置は、TFTと有機EL素子とを含む画素5と、画素5に接続された信号線102とが設けられた表示パネルと、信号線102に接続され、画素5に駆動電流を供給するためのソース駆動回路(図示せず)とを備えている。

### 【0202】

ソース駆動回路は、画素5に駆動電流を流すための電流駆動部11と、電流駆動部11か

10

20

30

40

50

らの駆動電流をオンまたはオフにするスイッチ 127 と、出力部が電流駆動部 11 と画素 5 との接続経路に接続された電圧出力型の D A C 手段 123 と、画像信号であるデータ信号をラッピングするバイナリー表示データ保持手段 121 と、D A C 手段 123 の出力電圧をオンまたはオフにするためのスイッチ 125 と、基準電流生成部 101 とを備えている。ここで、バイナリー表示データ保持手段 121 は、図 16 におけるレジスタ 7 に相当する。

#### 【 0203 】

n ビットの階調表示を行なう場合、電流駆動部 11 は、n 個の電流源を有している。本実施形態の例では 6 ビットの階調表示を行なうので、電流駆動部 11 は、第 1 の電流源 212、第 2 の電流源 213、…第 6 の電流源 214 と、第 1 の電流源 212、第 2 の電流源 213、…第 6 の電流源 214 の出力をそれぞれオンまたはオフにするための第 1 のスイッチ 215、第 2 のスイッチ 216、…第 6 のスイッチ 217 を有している。10

#### 【 0204 】

また、バイナリー表示データ保持手段 121 は、D A C 手段 123 及び第 1 のスイッチ 215、第 2 のスイッチ 216、…第 6 のスイッチ 217 に 6 ビットのデータ信号を出力する。

#### 【 0205 】

基準電流生成部 101 は、P チャネル型の第 1 の M O S F E T 108 と、第 1 の M O S F E T に接続され、基準電流を発生させるための抵抗 107 と、第 1 の M O S F E T とカレントミラーを構成する第 2 の M O S F E T 109 と、第 2 の M O S F E T に流れる電流を第 1 の電流源 212、第 2 の電流源 213、…第 6 の電流源 214 にそれぞれ伝達するための N チャネル型の第 3 の M O S F E T 110 を有している。第 1 の電流源 212、第 2 の電流源 213、…第 6 の電流源 214 のそれを構成する N チャネル型 M O S F E T は、第 3 の M O S F E T 110 とカレントミラーハウジングを構成している。20

#### 【 0206 】

本実施形態の有機 E L 表示装置の特徴は、ソース駆動回路の最終動作点付近に配置され、6 ビット分のデータ信号に応じた電圧を出力する D A C 手段 123 を備えていることである。そして、スイッチ 125 は電流設定時の所定の期間だけオンとなり、その期間に D A C 手段 123 からの出力電圧は画素 5 に供給される。この所定の期間は、画素 5 に流れる電流が目標電流付近になるように設定される。30

#### 【 0207 】

D A C 手段 123 の出力は電流駆動部 11 に比べて著しく低インピーダンスであるので、高輝度表示から低輝度表示の切替え時に伝送路上の浮遊容量 221 ( 図 16 の浮遊容量 15 ) 及び画素入力容量は従来よりも短時間で充電される。このとき、ソース駆動回路出力の電流・電圧特性は、図 18 ( a ) の点線に示す曲線から実線に示す曲線へと移動し、画素 5 内の T F T の動作点が高電圧側に移動する。このため、短時間の間に高輝度表示に切り替えることが可能となっている。従って、本実施形態の有機 E L 表示装置においては、高解像度のパネルを用いた場合にも良好に画像表示を行なうことができるようになっている。

#### 【 0208 】

また、本実施形態の D A C 手段 123 は、64 階調の表示データの各々に応じた電圧を出力することができるので、画素 5 に流れる電流の値をより迅速に目標電流値に到達させることができる。ここで、64 階調の表示データの各々に応じた電圧の例としては、例えば該表示データについての安定出力電圧が挙げられる。40

#### 【 0209 】

なお、本実施形態の有機 E L 表示装置では、ソース駆動回路と同一チップ上に形成された D A C 手段 123 を低インピーダンス手段として用いたが、外部の電源電圧を電流設定時の所定の期間のみ画素 5 に供給するような構成をとってもよい。

#### 【 0210 】

( 第 8 の実施形態 )

10

20

30

40

50

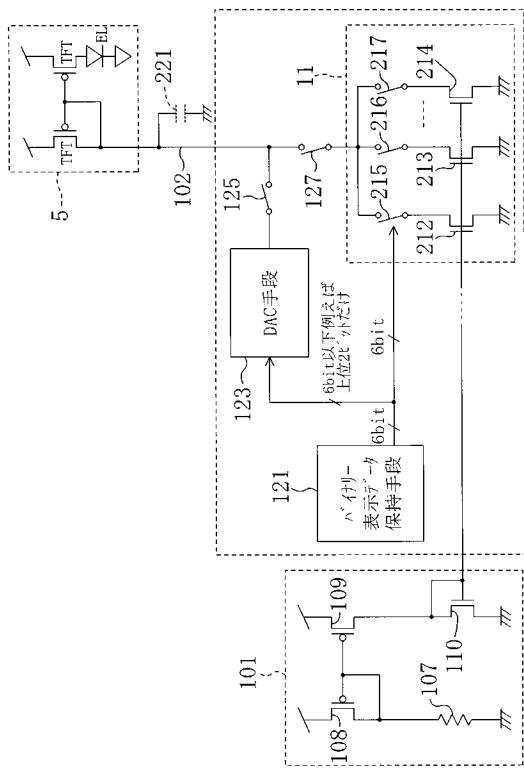

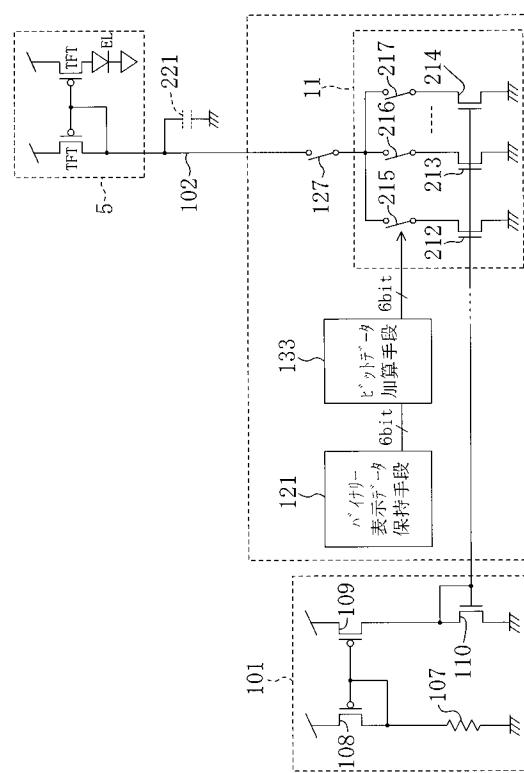

図19は、本発明の第8の実施形態に係る有機EL表示装置の構成を示すブロック回路図である。

【0211】

図19に示すように、本実施形態の有機EL表示装置は、バイナリー表示データ保持手段121から6ビットのデータ信号のうち、一部のビットのデータ信号のみがDAC手段123へ出力される点が第7の実施形態の有機EL表示装置と異なる。その他の回路構成は第7の実施形態の有機EL表示装置と同様であるので、説明は省略する。

【0212】

本実施形態のDAC手段123においては、例えば上位2ビットのみに応じた電圧がDAC手段から出力されるので、高輝度表示から低輝度表示に切り替わる際の電流設定時間を従来よりも短縮することができる。特に、本実施形態のDAC手段123は、第7の実施形態で説明したDAC手段よりも回路面積が小さくなっているので、表示装置の小面積化が要求される場合に好ましく用いられる。ただし、第7の実施形態で用いられるDAC手段は、すべての階調のデータ信号に対して最適な電圧を出力できるので、小面積化よりも解像度の向上が重視される場合には好ましく用いられる。

【0213】

なお、本実施形態のDAC手段123に入力されるデータ信号は、下位ビットの信号よりも上位ビットの信号である方がより適切な電圧を出力できるので好ましい。

【0214】

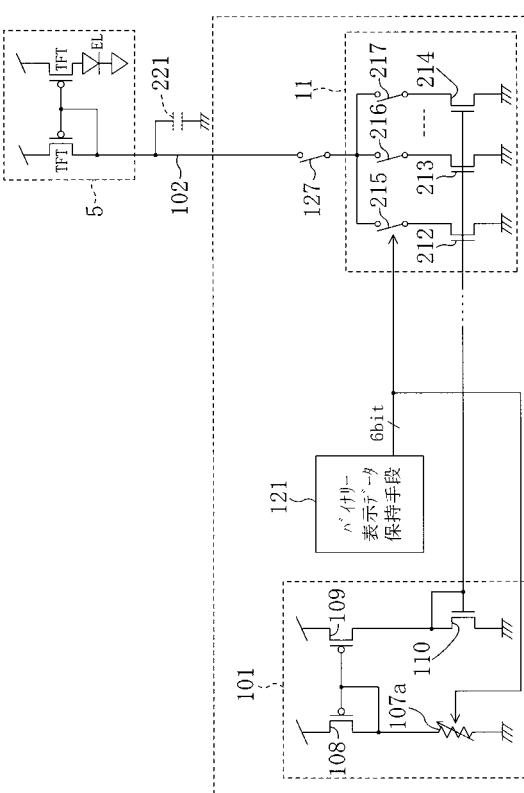

(第9の実施形態)

図20(a)は、本発明の第9の実施形態に係る有機EL表示装置において、黒表示(低輝度表示)の際のTFTの動作点を示すグラフ図であり、(b)は、第9の実施形態に係る有機EL表示装置の構成を示すブロック回路図である。

【0215】

本実施形態の有機EL表示装置の特徴は、電流駆動部11に電流 $I_x$ を出力するための冗長ビット131が付加されていることである。この冗長ビット131は、第1の電流源212、第2の電流源213、...第6の電流源214及び第3のMOSFET110とカレントミラー回路を構成する付加電流源231と、付加電流源231からの出力電流を電流設定時の所定期間に導通させるスイッチ233とを有している。

【0216】

本実施形態の有機EL表示装置は、図1及び図3に示した第1の実施形態の第1の具体例の変形例である。

【0217】

すなわち、図20(b)に示す冗長ビット131のうち、付加電流源231は図3に示す付加電流源24に相当し、スイッチ233はスイッチSW<sub>A</sub>に相当する。そして、スイッチSW<sub>A</sub>は、図20(b)では図示しないタイミング制御部9によって、電流設定時の所定期間のみオン状態になるように制御されている。このスイッチSW<sub>A</sub>がオン状態の間に付加電流源231を流れる電流の値は、少なくとも最小電流単位より大きくなっている。特に、データ信号によって本来設定される電流値以上に設定されている。

【0218】

これにより、低輝度表示から高輝度表示に切り替わる際の電流設定時に、パネル側から見た出力インピーダンスを低下させることができるので、画素5に流れる電流の値を従来よりも短時間に目標値に到達させることができる。なお、低輝度表示の際に、画素5内のTFTの動作点は、図20(a)に示すように、低電位側へ移動することになる。

【0219】

また、本実施形態の冗長ビット131は、バイナリー表示データ保持手段121から出力される6ビットのデータ信号に応じて電流の引き込み量を変えることができる。ただし、電流の引き込み量をデータ信号と無関係とすることもできる。

【0220】

これにより、本実施形態の有機EL表示装置は、第1の実施形態の第1の具体例と比べて

10

20

30

40

50

も画素 5 に流れる電流の値を短時間に目標値に到達させることができる。このため、本実施形態の有機 E L 表示装置によれば、高解像度の画像表示が実現される。

【 0 2 2 1 】

( 第 1 0 の実施形態 )

図 2 1 は、本発明の第 1 0 の実施形態に係る有機 E L 表示装置の構成を示すブロック回路図である。

【 0 2 2 2 】

本実施形態の有機 E L 表示装置は、図 2 4 に示す従来の有機 E L 表示装置に、表示データであるデータ信号をラッチすると共に出力するためのバイナリー表示データ保持手段 1 2 1 と、データ信号を受けて、該データ信号にビットを加算して出力するためのビットデータ加算手段 1 3 3 を付加した表示装置である。図 2 1 では、バイナリー表示データ保持手段 1 2 1 が output するデータ信号が 6 ビットである例を示している。

【 0 2 2 3 】

本実施形態のビットデータ加算手段 1 3 3 がデータ信号に加算するビット数は任意に設定できるが、消費電力の増加及び回路面積の増加を抑えるために、1 または 2 ビットであることが好ましい。

【 0 2 2 4 】

また、電流駆動部 1 1 は、かさ上げされた分の電流を出力可能な構成を有している。その一例として、ビットデータ加算手段 1 3 3 がデータ信号に 2 ビット加算する場合、電流駆動部 1 1 には、下位 2 ビット分の電流源及びスイッチが付加される。.

【 0 2 2 5 】

本実施形態の有機 E L 表示装置において、電流設定時にバイナリー表示データ保持手段 1 2 1 が 6 ビット分のデータ信号に 2 ビットを加算して電流駆動部 1 1 に出力すると、電流駆動部 1 1 に一時的に 2 ビット分かさ上げされた電流が引き込まれる。これによって、低輝度表示から高輝度表示に切り替わる際に、パネル側の浮遊容量及び画素入力容量に充電された電荷を速やかに放電させることができる。その結果、画素 5 に流れる電流の値を従来よりも短時間に目標値に到達させることができる。

【 0 2 2 6 】

なお、図 2 1 には示さないが、本実施形態のビットデータ加算手段 1 3 3 は、例えば図 9 に示すようなタイミング制御部によって、電流設定時の所定の期間のみ駆動されている。

【 0 2 2 7 】

( 第 1 1 の実施形態 )

図 2 2 は、本発明の第 1 1 の実施形態に係る有機 E L 表示装置の構成を示すブロック回路図である。

【 0 2 2 8 】

同図に示すように、本実施形態の有機 E L 表示装置においては、基準電流生成部 1 0 1 のうち、基準電流を発生させるための抵抗 1 0 7 ( 図 1 8 ~ 2 1 参照 ) が、可変抵抗 1 0 7 a に置き換えられている。そして、電流設定時の所定の期間には、バイナリー表示データ保持手段 1 2 1 からのデータ信号が、電流駆動部 1 1 だけでなく可変抵抗 1 0 7 a にも伝達される。これ以外の期間には、バイナリー表示データ保持手段 1 2 1 からのデータ信号は、可変抵抗 1 0 7 a に伝達されない。

【 0 2 2 9 】

可変抵抗 1 0 7 a は、高輝度表示のデータ信号が入力されると自身の抵抗値を下げて基準電流を大きくさせ、低輝度表示のデータ信号が入力されると自身の抵抗値を上げて基準電流を減少させる。このため、本実施形態の有機 E L 表示装置では、高輝度表示を行なう際には一時的に電流駆動部 1 1 への引き込み電流が増大し、画素 5 に流れる電流の値を迅速に目標値に到達できるようになっている。また、低輝度表示の場合には、電流駆動部 1 1 の引き込み電流が減少するように制御される。

【 0 2 3 0 】

従って、本実施形態の有機 E L 表示装置によれば、低輝度表示から高輝度表示に切り替わ

10

20

30

40

50

る際に、画素 5 に流れる電流の値を従来よりも短時間に目標値に到達させることができるので、画質を低下させることなく高解像度の表示を行なうことができる。

【0231】

なお、本実施形態の有機 EL 表示装置において、バイナリー表示データ保持手段 121 から可変抵抗 107a に伝達されるデータ信号は、6 ビットのうち一部、例えば上位 1 または 2 ビットのみであってもよい。この場合、回路面積の増加は抑えられる。

【0232】

なお、図 22 に示す例では、画素 5 内の TFT が P チャネル型で、電流駆動部 11 内の電流源を構成する MOSFET が N チャネル型であったが、TFT が N チャネル型で、電流源を構成する MOSFET が P チャネル型であってもよい。この場合、基準電流生成部 101 を構成する MOSFET の導電型も入れ替わる。これは、本実施形態のみならず、ここまで説明した他の実施形態に係る有機 EL 表示装置においても同じである。10

【0233】

【発明の効果】

本発明の有機 EL 表示装置によれば、電流設定時の所定の期間のみパネル側の出力インピーダンスを低減させる手段を講じることによって、黒表示から白表示に切り替わる際に画素に流れる電流の値を迅速に目標値に到達させることができるので、画質を低下させずに高解像度の表示を実現させることができる。

【0234】

また、ソース駆動回路が、電流設定時の所定の期間のみ画素に電圧を駆動するための電圧駆動部を有していることによっても、パネル側の寄生容量を迅速に充放電させることができるので、画素に流れる電流の値を迅速に目標値に到達させることができ、画質を低下させずに高解像度の表示を実現させることができる。20

【0235】

また、本発明の有機 EL 表示装置において、ソース駆動回路が画素を駆動するための電圧を供給する電圧駆動部と、画素から流れる駆動電流の値を検出して検出結果を電圧駆動部にフィードバックする電流値検出部とを有していることにより、画素に流れる電流の値を従来よりも迅速に目標値に到達させることができる。

【図面の簡単な説明】

【図 1】本発明の第 1 の実施形態に係る有機 EL 表示装置の構成を概略的に示すブロック回路図である。30

【図 2】第 1 の実施形態に係る有機 EL 表示装置のうち、電流設定時における電流発生部のモデル例を示す回路図である。

【図 3】第 1 の実施形態に係る有機 EL 表示装置について、電流駆動部の第 1 の具体例を示す回路図である。

【図 4】第 1 の実施形態の第 1 の具体例に係る有機 EL 表示装置において、電流設定時の画素 5 に流れる電流 I の変化、及び画素 5 の入力部に印加される電圧 V<sub>o</sub> の変化を示すグラフ図である。

【図 5】第 1 の実施形態に係る有機 EL 表示装置について、電流駆動部の第 2 の具体例を示す回路図である。

【図 6】第 1 の実施形態の第 2 の具体例に係る有機 EL 表示装置において、電流設定時の電流駆動部から画素に流れる電流 I の変化、及び画素に印加される電圧 V<sub>o</sub> の変化を示すグラフ図である。40

【図 7】第 1 の実施形態に係る有機 EL 表示装置における、電流駆動部の第 3 の具体例を示す回路図である。

【図 8】第 1 の実施形態の第 3 の具体例に係る有機 EL 表示装置において、電流設定時の電流発生部から有機 EL 素子に流れる電流 I の変化、及び画素に印加される電圧 V<sub>o</sub> の変化を示すグラフ図である。

【図 9】第 1 の実施形態の第 4 の具体例に係るタイミング制御部の構成例を示すブロック図である。50

【図10】本発明の第2の実施形態に係る有機EL表示装置の構成を概略的に示すブロック回路図である。

【図11】第2の実施形態の具体例に係る有機EL表示装置の構成を概略的に示すブロック回路図である。

【図12】本発明の第3の実施形態に係る有機EL表示装置のうち、電流発生部の構成を示す回路図である。

【図13】図12に示す電流発生部を用いた第3の実施形態に係る有機EL表示装置の一例を概略的に示すブロック回路図である。

【図14】第3の実施形態に係る有機EL表示装置のうち、電流値検出部の構成例を示すブロック回路図である。

【図15】本発明の第4の実施形態に係る有機EL表示装置の一例を概略的に示すブロック回路図である。

【図16】本発明の第5の実施形態に係る有機EL表示装置の構成を概略的に示すブロック回路図である。

【図17】本発明の第6の実施形態に係る有機EL表示装置の構成を概略的に示すブロック回路図である。

【図18】(a)は、本発明の第7の実施形態に係る有機EL表示装置において、白表示時(高輝度表示時)のTFTの動作点を示すグラフ図であり、(b)は、第7の実施形態に係る有機EL表示装置の構成を示すブロック回路図である。

【図19】本発明の第8の実施形態に係る有機EL表示装置の構成を示すブロック回路図である。

【図20】(a)は、本発明の第9の実施形態に係る有機EL表示装置において、黒表示の際のTFTの動作点を示すグラフ図であり、(b)は、第9の実施形態に係る有機EL表示装置の構成を示すブロック回路図である。

【図21】本発明の第10の実施形態に係る有機EL表示装置の構成を示すブロック回路図である。

【図22】本発明の第11の実施形態に係る有機EL表示装置の構成を示すブロック回路図である。

【図23】従来の有機EL表示装置の構成を概略的に示すブロック回路図である。

【図24】(a)は、従来の有機EL表示装置において、黑白表示をした場合の表示パネルの拡大図、(b)は、(a)に示す表示パネルのXXVb-XXVb線上に配置された画素と、該画素に接続された画素駆動部とを示す回路図、(c)は、黒表示時におけるTFTの動作点を示すグラフ図、(d)は、白表示時におけるTFTの動作点を示すグラフ図である。

【図25】(a)、(b)は、それぞれ一般的な有機EL画素における電流発生部の構成例を示す回路図である。

【図26】従来の有機EL表示装置において、黒表示を行なう際の画素に流れる電流値及び画素にかかる電圧値の変化を示すグラフ図である。

#### 【符号の説明】

|                   |          |

|-------------------|----------|

| 1 , 1 a           | 画素駆動部    |

| 3                 | 伝送路      |

| 5                 | 画素       |

| 7                 | レジスタ     |

| 9                 | タイミング制御部 |

| 1 1 、 8 0         | 電流駆動部    |

| 1 4               | 駆動電圧用信号線 |

| 1 5 、 6 3 、 2 2 1 | 浮遊容量     |

| 1 7               | 画素入力容量   |

| 1 8               | 電流源      |

| 1 9               | 電流発生部    |

10

20

30

40

50

|                                               |                   |    |

|-----------------------------------------------|-------------------|----|

| 2 0 、 7 2                                     | T F T             |    |

| 2 1                                           | 有機 E L 素子         |    |

| 2 2 i 0                                       | 第 1 の電流源          |    |

| 2 2 i 1                                       | 第 2 の電流源          |    |

| 2 2 i 2                                       | 第 3 の電流源          |    |

| 2 2 i 3                                       | 第 4 の電流源          |    |

| 2 2 i 4                                       | 第 5 の電流源          |    |

| 2 2 i 5                                       | 第 6 の電流源          |    |

| 2 4 、 2 3 1                                   | 付加電流源             |    |

| 3 1 a 、 3 1 b 、 3 1 c 、 3 1 d 、 3 1 e 、 3 1 f | タイミング設定用レジスタ      | 10 |

| 3 3 a 、 3 3 b 、 3 3 c 、 3 3 d 、 3 3 e 、 3 3 f | 比較回路              |    |

| 3 5 a 、 3 5 b 、 3 5 c 、 3 5 d 、 3 5 e 、 3 5 f | 制御信号発生回路          |    |

| 3 7                                           | カウンタ              |    |

| 5 0                                           | 電圧設定手段            |    |

| 5 1                                           | ダミー画素駆動部          |    |

| 5 3                                           | ダミー伝送路            |    |

| 5 5                                           | ダミー画素             |    |

| 5 7                                           | ダミー画素入力容量         |    |

| 5 9                                           | ダミー電流発生部          |    |

| 6 1                                           | ダミー電流駆動部          | 20 |

| 6 4                                           | 駆動電流用信号線          |    |

| 6 5                                           | 配線抵抗              |    |

| 6 7                                           | 比較回路              |    |

| 6 7 a                                         | コンパレータ            |    |

| 7 1                                           | 電流値検出部            |    |

| 7 3 、 7 9                                     | 電圧駆動部             |    |

| 7 4                                           | 第 1 のスイッチ用トランジスタ  |    |

| 7 5 、 7 7 、 S W A 0 ~ S W A 5                 | スイッチ              |    |

| 7 6                                           | 第 3 のスイッチ用トランジスタ  |    |

| 7 8                                           | 第 2 のスイッチ用トランジスタ  | 30 |

| 8 2 、 1 0 7                                   | 抵抗                |    |

| 1 0 1                                         | 基準電流生成部           |    |

| 1 0 2                                         | 信号線               |    |

| 1 0 7 a                                       | 可変抵抗              |    |

| 1 0 8                                         | 第 1 の M O S F E T |    |

| 1 0 9                                         | 第 2 の M O S F E T |    |

| 1 1 0                                         | 第 3 の M O S F E T |    |

| 1 2 1                                         | バイナリー表示データ保持手段    |    |

| 1 2 3                                         | D A C 手段          |    |

| 1 2 5 、 1 2 7 、 2 3 3                         | スイッチ              | 40 |

| 1 3 1                                         | 冗長ビット             |    |

| 1 3 3                                         | ビットデータ加算手段        |    |

| 2 1 2                                         | 第 1 の電流源          |    |

| 2 1 3                                         | 第 2 の電流源          |    |

| 2 1 4                                         | 第 6 の電流源          |    |

| 2 1 5                                         | 第 1 のスイッチ         |    |

| 2 1 6                                         | 第 2 のスイッチ         |    |

| 2 1 7                                         | 第 6 のスイッチ         |    |

| S c 0 ~ S c 5                                 | 一致信号              |    |

| S r 0 ~ S r 5                                 | レジスタデータ信号         | 50 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図7】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 7】

【図 1 8】

【図 19】

【図 20】

【図 21】

【図 22】

【図23】

【図25】

【図24】

【図26】

## フロントページの続き

| (51) Int.Cl. <sup>7</sup> | F I           | テーマコード(参考) |

|---------------------------|---------------|------------|

|                           | G 0 9 G 3/20  | 6 2 3 F    |

|                           | G 0 9 G 3/20  | 6 2 3 G    |

|                           | G 0 9 G 3/20  | 6 2 3 R    |

|                           | G 0 9 G 3/20  | 6 4 1 D    |

|                           | G 0 9 G 3/20  | 6 4 2 P    |

|                           | H 0 5 B 33/14 | A          |

(74)代理人 100115691

弁理士 藤田 篤史

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121500

弁理士 後藤 高志

(74)代理人 100121728

弁理士 井関 勝守

(72)発明者 大森 哲郎

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 伊達 義人

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ターム(参考) 3K007 AB02 AB03 AB17 DB03 GA04

5C080 AA06 BB05 DD04 DD05 DD07 DD08 DD28 EE28 FF11 JJ02

JJ03 JJ04 JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置，源极驱动电路，显示面板                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP2004309924A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2004-11-04 |

| 申请号            | JP2003105694                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 申请日     | 2003-04-09 |

| [标]申请(专利权)人(译) | 松下电器产业株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | 松下电器产业有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| [标]发明人         | 大森哲郎<br>伊達義人                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 大森 哲郎<br>伊達 義人                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 G09G3/32 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | G09G3/325 G09G3/3241 G09G3/3283 G09G3/3291 G09G2300/0842 G09G2310/0248 G09G2310/0251 G09G2310/027 G09G2320/0223 G09G2320/0252                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| FI分类号          | G09G3/30.J G09G3/30.K G09G3/20.611.J G09G3/20.623.C G09G3/20.623.D G09G3/20.623.F G09G3/20.623.G G09G3/20.623.R G09G3/20.641.D G09G3/20.642.P H05B33/14.A G09G3/20.621.F G09G3/3241 G09G3/325 G09G3/3266 G09G3/3275 G09G3/3283                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |