(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4747565号

(P4747565)

(45) 発行日 平成23年8月17日(2011.8.17)

(24) 登録日 平成23年5月27日(2011.5.27)

(51) Int.Cl.

F 1

G09G 3/30 (2006.01)

G09G 3/20 (2006.01)

H01L 51/50 (2006.01)G09G 3/30 K

G09G 3/30 J

G09G 3/20 611D

G09G 3/20 612E

G09G 3/20 612U

請求項の数 3 (全 33 頁) 最終頁に続く

(21) 出願番号

特願2004-347283 (P2004-347283)

(22) 出願日

平成16年11月30日(2004.11.30)

(65) 公開番号

特開2006-154521 (P2006-154521A)

(43) 公開日

平成18年6月15日(2006.6.15)

審査請求日

平成18年1月27日(2006.1.27)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100094363

弁理士 山本 幸久

(74) 代理人 100118290

弁理士 吉井 正明

(74) 代理人 100120640

弁理士 森 幸一

(72) 発明者 山下 淳一

東京都品川区北品川6丁目7番35号 ソニー株式会社内

(72) 発明者 内野 勝秀

東京都品川区北品川6丁目7番35号 ソニー株式会社内

最終頁に続く

(54) 【発明の名称】 画素回路及びその駆動方法

(57) 【特許請求の範囲】

【請求項 1】

信号電流が流れる信号線と制御信号を供給する走査線とが交差する部分に配された画素回路であって、

第1スイッチングトランジスタ、第2スイッチングトランジスタ、第3スイッチングトランジスタ、第4スイッチングトランジスタ、第5スイッチングトランジスタ、駆動トランジスタ、第1画素容量、第2画素容量、及び、発光素子から成り、

駆動トランジスタのソースは、電源に接続されており、

駆動トランジスタのドレインは、第5スイッチングトランジスタの一方のソース／ドレイン、及び、第4スイッチングトランジスタの一方のソース／ドレインに接続されており

、駆動トランジスタのゲートは、第2画素容量の一端、第2スイッチングトランジスタの一方のソース／ドレイン、第1スイッチングトランジスタの他方のソース／ドレイン、及び、第4スイッチングトランジスタの他方のソース／ドレインに接続されており、

第1スイッチングトランジスタの一方のソース／ドレインは、信号線に接続されており

、第1スイッチングトランジスタのゲートは、走査線の内の第1走査線に接続されており

、第1画素容量の一端は、第2スイッチングトランジスタの他方のソース／ドレイン、及び、第3スイッチングトランジスタの他方のソース／ドレインに接続されており、

10

20

第 1 画素容量の他端は、電源に接続されており、

第 2 スイッチングトランジスタのゲートは、走査線の内の第 2 走査線に接続されており

、

第 3 スイッチングトランジスタの一方のソース / ドレインは、第 2 画素容量の他端に接続されており、

第 3 スイッチングトランジスタのゲートは、走査線の内の第 3 走査線に接続されており

、

第 4 スイッチングトランジスタのゲートは、走査線の内の第 4 走査線に接続されており

、

第 5 スイッチングトランジスタの他方のソース / ドレインは、発光素子の一端に接続され

ており、

第 5 スイッチングトランジスタのゲートは、走査線の内の第 5 走査線に接続されており

、

第 3 スイッチングトランジスタ及び第 4 スイッチングトランジスタがオン状態、第 5 ス

イッチングトランジスタがオフ状態とされ、信号線に基準電流が流れている状態で、第 1

スイッチングトランジスタ及び第 2 スイッチングトランジスタがオン状態とされることで

、基準電流が第 1 画素容量にサンプリングされた後、

第 2 スイッチングトランジスタがオフ状態とされ、信号線に流れる信号電流が第 1 画素

容量及び第 2 画素容量にサンプリングされることで、サンプリングされた信号電流の平方

根と基準電流の平方根との差分に応じた制御電圧が第 2 画素容量に保持された後、

第 1 スイッチングトランジスタ及び第 3 スイッチングトランジスタがオフ状態とされ、

第 2 スイッチングトランジスタがオン状態とされることで、駆動トランジスタの閾電圧が

検出され、駆動トランジスタの閾電圧の影響を駆動電流からキャンセルするための閾電圧

が第 1 画素容量に保持された後、

第 2 スイッチングトランジスタ及び第 4 スイッチングトランジスタがオフ状態とされ、

第 3 スイッチングトランジスタ及び第 5 スイッチングトランジスタがオン状態とされることで、駆動トランジスタのゲート・ソース間に前記閾電圧と前記制御電圧との和が印加され、駆動トランジスタは駆動電流を発光素子に供給して発光を行わせる画素回路。

【請求項 2】

第 1 画素容量及び第 2 画素容量は同一の容量値を有する請求項 1 に記載の画素回路。

【請求項 3】

信号電流が流れる信号線と制御信号を供給する走査線とが交差する部分に配されており

、

第 1 スイッチングトランジスタ、第 2 スイッチングトランジスタ、第 3 スイッチングト

ランジスタ、第 4 スイッチングトランジスタ、第 5 スイッチングトランジスタ、駆動ト

ランジスタ、第 1 画素容量、第 2 画素容量、及び、発光素子から成り、

駆動トランジスタのソースは、電源に接続されており、

駆動トランジスタのドレインは、第 5 スイッチングトランジスタの一方のソース / ドレ

イン、及び、第 4 スイッチングトランジスタの一方のソース / ドレインに接続されており

、

駆動トランジスタのゲートは、第 2 画素容量の一端、第 2 スイッチングトランジスタの

一方のソース / ドレイン、第 1 スイッチングトランジスタの他方のソース / ドレイン、及

び、第 4 スイッチングトランジスタの他方のソース / ドレインに接続されており、

第 1 スイッチングトランジスタの一方のソース / ドレインは、信号線に接続されており

、

第 1 スイッチングトランジスタのゲートは、走査線の内の第 1 走査線に接続されており

、

第 1 画素容量の一端は、第 2 スイッチングトランジスタの他方のソース / ドレイン、及

び、第 3 スイッチングトランジスタの他方のソース / ドレインに接続されており、

第 1 画素容量の他端は、電源に接続されており、

10

20

30

40

50

第 2 スイッチングトランジスタのゲートは、走査線の内の第 2 走査線に接続されており、

第 3 スイッチングトランジスタの一方のソース / ドレインは、第 2 画素容量の他端に接続されており、

第 3 スイッチングトランジスタのゲートは、走査線の内の第 3 走査線に接続されており、

第 4 スイッチングトランジスタのゲートは、走査線の内の第 4 走査線に接続されており、

第 5 スイッチングトランジスタの他方のソース / ドレインは、発光素子の一端に接続されており、

第 5 スイッチングトランジスタのゲートは、走査線の内の第 5 走査線に接続されている画素回路の駆動方法であって、

第 3 スイッチングトランジスタ及び第 4 スイッチングトランジスタをオン状態、第 5 スイッチングトランジスタをオフ状態とし、信号線に基準電流を流した状態で、第 1 スイッチングトランジスタ及び第 2 スイッチングトランジスタをオン状態とすることで、基準電流を第 1 画素容量にサンプリングした後、

第 2 スイッチングトランジスタをオフ状態とし、信号線に流れる信号電流を第 1 画素容量及び第 2 画素容量にサンプリングすることで、サンプリングされた信号電流の平方根と基準電流の平方根との差分に応じた制御電圧を第 2 画素容量に保持した後、

第 1 スイッチングトランジスタ及び第 3 スイッチングトランジスタをオフ状態とし、第 2 スイッチングトランジスタをオン状態とすることで、駆動トランジスタの閾電圧を検出し、駆動トランジスタの閾電圧の影響を駆動電流からキャンセルするための閾電圧を第 1 画素容量に保持した後、

第 2 スイッチングトランジスタ及び第 4 スイッチングトランジスタをオフ状態とし、第 3 スイッチングトランジスタ及び第 5 スイッチングトランジスタをオン状態とすることで、駆動トランジスタのゲート・ソース間に前記閾電圧と前記制御電圧との和を印加し、駆動トランジスタによって駆動電流を発光素子に供給して発光させる画素回路の駆動方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、画素毎に配した発光素子を電流駆動する画素回路及びその駆動方法に関する。また、この画素回路をマトリクス状（行列状）に配列した表示装置であって、特に、各画素回路内に設けた絶縁ゲート型電界効果トランジスタによって、有機ELなどの発光素子に通電する電流量を制御する、いわゆるアクティブマトリクス型の表示装置及びその駆動方法に関する。

##### 【背景技術】

##### 【0002】

画像表示装置、例えば液晶ディスプレイなどでは、多数の液晶画素をマトリクス状に並べ、表示すべき画像情報を応じて画素毎に入射光の透過強度または反射強度を制御する事によって画像を表示する。これは、有機EL素子を画素に用いた有機ELディスプレイなどにおいても同様であるが、液晶画素と異なり、有機EL素子は自発光素子である。その為、有機ELディスプレイは、液晶ディスプレイに比べて画像の視認性が高く、バックライトが不要であり、応答速度が高いなどの利点を有する。また、各発光素子の輝度レベル（階調）は、それに流れる電流値によって制御可能であり、いわゆる電流制御型であるという点で液晶ディスプレイなどの電圧制御型とは大きく異なる。

##### 【0003】

有機ELディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として、単純マトリクス方式とアクティブマトリクス方式がある。前者は構造が単純であるものの、大型、且つ、高精細のディスプレイの実現が難しいなどの問題がある為、現在は、アクティブマトリクス方式の開発が盛んに行われている。この方式は、各画素回路内部の発光

素子に流れる電流を、画素回路内部に設けた能動素子（一般には薄膜トランジスタ TFT）によって制御するものであり、以下の特許文献に記載がある。

【0004】

【特許文献1】特開2003-255856公報

【特許文献2】特開2003-271095公報

【特許文献3】特開2004-133240公報

【特許文献4】特開2004-029791公報

【特許文献5】特開2004-093682公報

【0005】

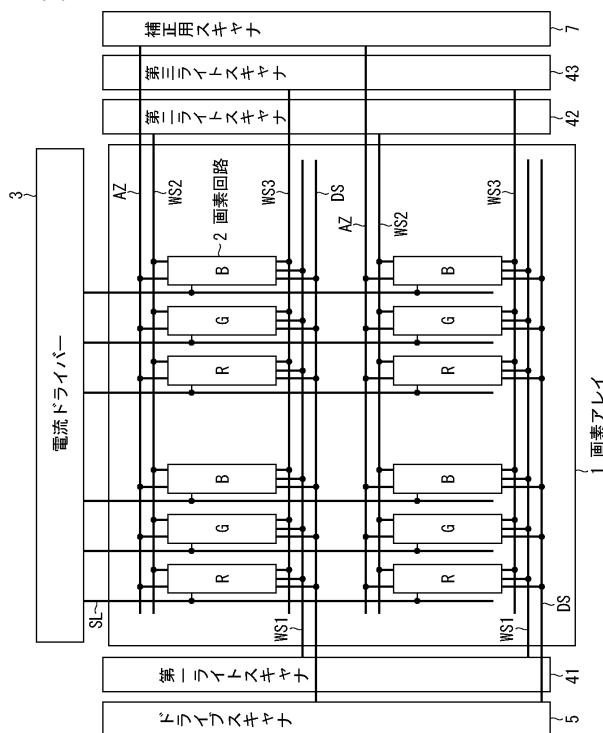

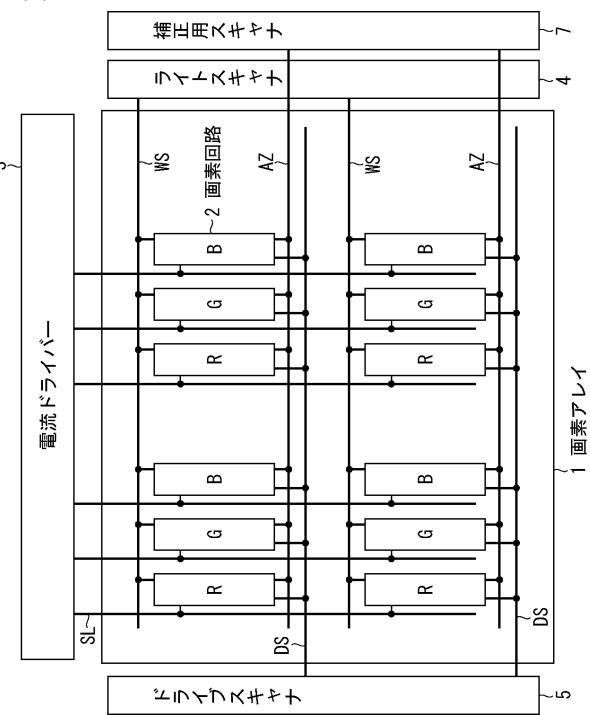

図22は、従来のアクティブマトリクス方式の有機ELディスプレイを示す模式的なブロック図である。図示するように、この表示装置は、主要部となる画素アレイ1と周辺の回路部とで構成されている。周辺の回路部は、電流ドライバー3、ライトスキャナ4、ドライブスキャナ5、補正用スキャナ7などを含んでいる。画素アレイ1は、行状の走査線WSと列状の信号線SLと両者の交差する部分にマトリクス状に配列した画素R, G, Bとで構成されている。カラー表示を可能とする為、RGBの三原色画素を用意しているが、これに代えて、白黒表示の単色画素を用いる事もある。各画素R, G, Bは、それぞれ画素回路2で構成されている。信号線SLは電流ドライバー3によって駆動され、信号電流が流れるようになっている。走査線WSはライトスキャナ4によって走査される。なお、走査線WSと平行に、別の走査線DS及びAZも配線されている。走査線DSはドライブスキャナ5によって走査される。ドライブスキャナ5は、各画素に含まれる発光素子の発光期間を制御するものである。走査線AZは補正用スキャナ7によって走査される。ライトスキャナ4、ドライブスキャナ5及び補正用スキャナ7は、全体としてスキャナ部を構成しており、1水平期間毎に画素の行を順次走査する。

【0006】

図23は、図22に示した画素回路の構成例を示す回路図である。図示するように、画素回路2は、4個のトランジスタTr1, Tr4, Tr5, Trdと、1個の画素容量Csと、1個の発光素子ELとで構成されている。4個のトランジスタは、いずれも薄膜トランジスタである。この内、トランジスタTr1, Tr4及びTr5は制御用のスイッチングトランジスタであり、いずれもNチャネル型を用いている。これに対し、トランジスタTrdは、発光素子ELを駆動する為の駆動トランジスタであり、Pチャネル型を用いている。また、発光素子ELは、アノード及びカソードを備えた二端子型の自発光素子であり、例えば、有機EL素子を用いる事ができる。

【0007】

駆動トランジスタTrdのソースSは電源Vccに接続されている。ドレインDは発光素子ELのアノード側に位置する。発光素子ELのカソード側は接地されている。駆動トランジスタTrdのゲートGは画素容量Csの一端に接続されている。画素容量Csの他端は電源Vccに接続されている。

【0008】

スイッチングトランジスタTr1のソース/ドレインは、信号線SLと駆動トランジスタTrdのゲートGとの間に接続されている。スイッチングトランジスタTr1のゲートは走査線WSに接続されている。スイッチングトランジスタTr4のソース/ドレインは、駆動トランジスタTrdのゲートGとドレインDとの間に接続されている。このトランジスタTr4のゲートは走査線AZに接続されている。スイッチングトランジスタTr5のソース/ドレインは、駆動トランジスタTrdのドレインDと発光素子ELのアノードとの間に接続されている。このトランジスタTr5のゲートは走査線DSに接続されている。

【0009】

駆動トランジスタTrdは飽和領域で動作し、その特性は以下の式(1)で表される。

【0010】

式(1)

10

20

30

40

50

$$I_{ds} = \frac{k\mu}{2} (V_{gs} - V_{th})^2$$

## 【0011】

式(1)において、 $V_{gs}$ はゲート電圧であり、駆動トランジスタTrdのソースSとゲートGとの間の電圧を表している。 $I_{ds}$ はドレイン電流であり、駆動トランジスタTrdのソースSとドレインDとの間を流れて発光素子ELに供給される。 $V_{th}$ は駆動トランジスタTrdの閾電圧を表している。 $\mu$ は、駆動トランジスタTrdのキャリア移動度を表している。また、kは定数であり、 $(C_{ox} \cdot W / L)$ で与えられる。ここで、 $C_{ox}$ は駆動トランジスタTrdのゲート容量、Wはチャネル幅、Lはチャネル長である。定数kは、サイズファクタと呼ばれる場合がある。駆動トランジスタTrdが飽和領域で動作する時、式(1)から明らかのように、ゲート電圧 $V_{gs}$ が閾電圧 $V_{th}$ を越えた時点からドレイン電流 $I_{ds}$ が流れ始める。ドレイン電流 $I_{ds}$ の大きさはゲート電圧 $V_{gs}$ の2乗に比例して増大する。なお、本明細書では、駆動トランジスタの閾電圧 $V_{th}$ は、駆動トランジスタの閾電圧の絶対値をとったものとする。ちなみに、Pチャネル型のトランジスタでは閾電圧は負の値を持つので、その値をそのまま式(1)に入れてしまうと正しくないことになる。その為、本明細書では絶対値をとり、閾電圧 $V_{th}$ は正の値にて取り扱うことにする。

## 【0012】

駆動トランジスタTrdは、例えば、多結晶シリコン薄膜を活性層とするTFTである。多結晶シリコン薄膜としては、レーザーアニールで結晶化された低温ポリシリコンが多用されている。一般に、低温ポリシリコンTFTは、デバイス毎に閾電圧 $V_{th}$ やキャリア移動度 $\mu$ がばらつく傾向にある。換言すると、個々の画素回路2毎に駆動トランジスタTrdの閾電圧 $V_{th}$ やキャリア移動度 $\mu$ が異なっている。

## 【0013】

画素回路2は、大別してサンプリング動作と発光動作を行う。始めのサンプリング動作では、トランジスタTr5をオフする一方、トランジスタTr1及びTr4をオンする。この状態で信号線SLを電流ドライバー3で駆動すると、信号電流 $I_{sig}$ が電源Vccから駆動トランジスタTrd及びスイッチングトランジスタTr4, Tr1を通って信号線SLに流れる。この時の駆動トランジスタTrdの動作特性は、以下の式(2)で表される。

## 【0014】

式(2)

$$I_{sig} = \frac{k\mu}{2} (V_{gs} - V_{th})^2$$

## 【0015】

式(2)は、式(1)のドレイン電流 $I_{ds}$ を信号電流 $I_{sig}$ で置き換えたものとなっている。

## 【0016】

信号電流 $I_{sig}$ が流れたとき駆動トランジスタTrdのゲートGとソースSとの間に現れるゲート電圧 $V_{gs}$ は、式(2)を $V_{gs}$ で解くことによって、以下の式(3)の様に表される。

## 【0017】

式(3)

$$V_{gs} = \sqrt{\frac{2I_{sig}}{k\mu}} + V_{th}$$

## 【0018】

式(3)で表されるゲート電圧  $V_{gs}$  は画素容量  $C_s$  に保持される。この様にして、サンプリング動作では、電流ドライバー3によって供給される信号電流  $I_{sig}$  のレベルに応じたゲート電圧  $V_{gs}$  が、画素容量  $C_s$  に書き込まれる。簡略的に言うと、信号電流  $I_{sig}$  が駆動トランジスタ  $T_{rd}$  のゲートに書き込まれた事になる。

## 【0019】

続いて発光動作では、トランジスタ  $T_{r1}$  及び  $T_{r4}$  がオフする一方、 $T_{r5}$  がオンになる。これにより、駆動トランジスタ  $T_{rd}$  から駆動電流  $I_{ds}$  が発光素子  $EL$  に流れ、所定の輝度で発光する事になる。このとき駆動トランジスタ  $T_{rd}$  に流れる駆動電流  $I_{ds}$  は以下の式(4)で表される。

## 【0020】

## 式(4)

$$I_{ds} = \frac{k\mu}{2} (V_{gs} - V_{th})^2$$

$$= \frac{k\mu}{2} \left( \sqrt{\frac{2I_{sig}}{k\mu}} + V_{th} - V_{th} \right)^2$$

$$= I_{sig}$$

## 【0021】

式(3)で求めた  $V_{gs}$  を式(4)の  $V_{gs}$  に代入して整理すると、結局、移動度  $\mu$  及び閾電圧  $V_{th}$  の項がキャンセルされ、 $I_{ds} = I_{sig}$  となる。したがって、駆動トランジスタ  $T_{rd}$  の移動度  $\mu$  や閾電圧  $V_{th}$  が画素毎にばらついていても、上述の信号電流書き込み動作を行うことで全てキャンセルされ、画面のユニフォーミティを維持する事ができる。

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0022】

図23に示した従来の画素回路は、駆動トランジスタの移動度  $\mu$  や閾電圧  $V_{th}$  のばらつきに拘わらず、信号電流  $I_{sig}$  と同じ駆動電流  $I_{ds}$  を発光素子  $EL$  に供給する事ができるという利点がある。電流ドライバー3は、信号電流  $I_{sig}$  のレベルを階調制御する事で、発光素子  $EL$  の輝度を黒レベルから中間のグレーレベルを通って白レベルまで変化させ事ができる。黒レベルのとき、信号電流  $I_{sig}$  は微弱となって0に近づく一方、白レベルでは大きな電流値となる。しかしながら、信号線  $SL$  の寄生容量は数十pFと比較的大きく、図23に示した従来の構成では、電流値の微弱な黒レベルの信号電流  $I_{sig}$  を、サンプリング動作に割り当てられた1水平映像期間(1H)内で、充分に書き込む事ができないという課題があった。

10

20

30

40

50

## 【0023】

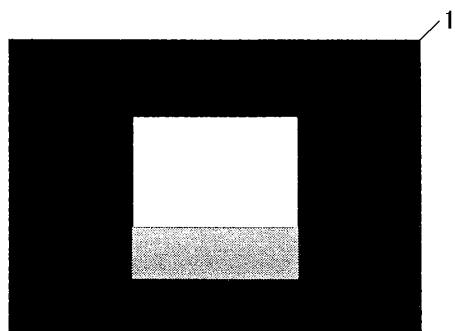

図24は、この問題を模式的に表したものである。画素アレイ1は画面を構成しており、黒の背景に白のウインドウを表示させた場合である。白いウインドウの下方にグレーの部分が現れている。本来、このグレーの部分は背景に属し、黒色でなければならない。しかしながら、図23に示した従来の画素回路構成では、白いウインドウの下方に位置する画素に黒レベルの信号電流を書き込むことができず、図示のような黒浮きや縦クロストークなどが発生する為、解決すべき課題となっている。

## 【課題を解決するための手段】

## 【0024】

上述した従来の技術の課題に鑑み、本発明は黒レベルの信号電流も充分書き込み可能な画素回路及び表示装置とこれらの駆動方法を提供することを目的とする。かかる目的を達成するために以下の手段を講じた。即ち、本発明は、信号電流が流れる信号線と制御信号を供給する走査線とが交差する部分に配され、発光素子と、該発光素子に駆動電流を供給する駆動トランジスタと、該制御信号に応じて動作し該信号電流に基づいて該駆動トランジスタの駆動電流を制御する制御部とからなる画素回路であって、前記制御部は該信号線に流れる信号電流をサンプリングする第1サンプリング手段と、該信号電流に前後して該信号線に流れる所定の基準電流をサンプリングする第2サンプリング手段と、サンプリングされた該信号電流と該基準電流の差分に応じた制御電圧を生成する差分手段とを含み、前記駆動トランジスタは該制御電圧をゲートに受けてソース・ドレイン間に流れる駆動電流を該発光素子に供給して発光を行わせることを特徴とする。

10

## 【0025】

具体的に、前記第1及び第2サンプリング手段が各々サンプリングする信号電流及び基準電流は、両者の相対的な差分が小さい時該発光素子の発光量が少なくなり且つ差分が大きい時発光量が多くなる一方、両者の相対的な差分が小さい時でも該信号電流及び基準電流の絶対的なレベルはサンプリングを可能とする様に大きく設定されている。好ましくは、前記制御部は、該駆動トランジスタの閾電圧を検出してこれを該制御電圧に加える補正手段を有しており、該閾電圧の影響を該駆動電流からキャンセルする。一態様では、前記第1サンプリング手段は該信号電流を該駆動トランジスタに流してその時ゲートに発生する信号電圧をサンプリングし、前記第2サンプリング手段は該駆動トランジスタに該基準電流を流してその時ゲートに発生する基準電圧をサンプリングし、前記差分手段は容量を介して該信号電圧と該基準電圧をカップリングさせ両者の差分を求めて該制御電圧を生成する。この場合、前記第1サンプリング手段はサンプリングした信号電圧を保持する第1の容量を有し、前記第2サンプリング手段はサンプリングした基準電圧を保持し且つ該信号電圧にカップリングする為の第2の容量を有し、前記第1及び第2の容量は同一の容量値を有する。

20

## 【0026】

本発明は又、画素アレイ部とドライバー部とスキャナ部とからなり、前記画素アレイ部は、列状の信号線と、行状の走査線と、両者の交差する部分に配された行列状の画素回路とからなり、前記ドライバー部は、各信号線に信号電流を流し、前記スキャナ部は、各走査線に制御信号を供給し、各画素回路は、発光素子と、該発光素子に駆動電流を供給する駆動トランジスタと、該制御信号に応じて動作し該信号電流に基づいて該駆動トランジスタの駆動電流を制御する画素内制御部とからなる表示装置であって、前記画素内制御部は、該信号線に流れる信号電流をサンプリングする第1サンプリング手段と、該信号電流に前後して該信号線に流れる所定の基準電流をサンプリングする第2サンプリング手段と、サンプリングされた該信号電流と該基準電流の差分に応じた制御電圧を生成する差分手段とを含み、前記駆動トランジスタは該制御電圧をゲートに受けてソース・ドレイン間に流れる駆動電流を該発光素子に供給して発光を行わせることを特徴とする。

30

## 【0027】

具体的に、前記第1及び第2サンプリング手段が各々サンプリングする信号電流及び基準電流は、両者の相対的な差分が小さい時該発光素子の発光量が少なくなり且つ差分が大

40

50

きい時発光量が多くなる一方、両者の相対的な差分が小さい時でも該信号電流及び基準電流の絶対的なレベルはサンプリングを可能とする様に大きく設定されている。このM市区は、好ましくは、前記画素内制御部は、該駆動トランジスタの閾電圧を検出してこれを該制御電圧に加える補正手段を有しており、該閾電圧の影響を該駆動電流からキャンセルする。

【0028】

本発明は更に、信号電流が流れる信号線と制御信号を供給する走査線とが交差する部分に配され、発光素子と、該発光素子に駆動電流を供給する駆動トランジスタと、該制御信号に応じて動作し該信号電流に基づいて該駆動トランジスタの駆動電流を制御する制御部とからなる画素回路の駆動方法であって、該信号線に流れる信号電流をサンプリングする第1サンプリング手順と、該信号電流に前後して該信号線に流れる所定の基準電流をサンプリングする第2サンプリング手順と、サンプリングされた該信号電流と該基準電流の差分に応じた制御電圧を生成する差分手順と、該制御電圧を前記駆動トランジスタのゲートに印加しソース・ドレイン間に流れる駆動電流を該発光素子に供給する発光手順とを行なうことを特徴とする。

【0029】

加えて本発明は、画素アレイ部とドライバー部とスキャナ部とからなり、前記画素アレイ部は、列状の信号線と、行状の走査線と、両者の交差する部分に配された行列状の画素回路とからなり、前記ドライバー部は各信号線に信号電流を流し、前記スキャナ部は各走査線に制御信号を供給し、各画素回路は、発光素子と、該発光素子に駆動電流を供給する駆動トランジスタと、該制御信号に応じて動作し該信号電流に基づいて該駆動トランジスタの駆動電流を制御する画素内制御部とからなる表示装置の駆動方法であって、該信号線に流れる信号電流をサンプリングする第1サンプリング手順と、該信号電流に前後して該信号線に流れる所定の基準電流をサンプリングする第2サンプリング手順と、サンプリングされた該信号電流と該基準電流の差分に応じた制御電圧を生成する差分手順と、該制御電圧を前記駆動トランジスタのゲートに印加しソース・ドレイン間に流れる駆動電流を該発光素子に供給する発光手順とを行なうことを特徴とする。

【発明の効果】

【0030】

本発明にかかる表示装置は、電流ドライバー側から信号電流ばかりでなく、基準電流も供給している。画素回路は、前後して信号電流及び基準電流をサンプリングし、さらに、両者の差分を求めて駆動トランジスタのゲート制御電圧としている。これにより、駆動トランジスタは、基準電流に対する信号電流の差分に応じて発光素子を駆動する事ができる。その際、黒レベルの発光輝度では差分が0に近くなり、信号電流が基準電流と略同じになる。この様な状態でも、信号電流及び基準電流の絶対値は、信号線の寄生容量に対して充分高く設定する事ができる。したがって、黒レベルの電流でも各画素に充分高速で書き込むことができ、従来問題となっていた黒浮きや縦クロストークを防ぐ事ができる。表示すべき輝度階調に依存することなく、信号電流及び基準電流のレベルを高く設定できるので、黒表示の電流であっても1水平期間内に充分画素に書き込むことができ、輝度が充分沈んだ黒色を表現でき、高いコントラスト特性を得ることが可能である。また、駆動トランジスタの閾電圧や移動度に依存することなく、信号電流と基準電流の差分を求めて発光素子に対する駆動電流を制御する為、駆動トランジスタの特性ばらつきに影響を受けることなく、高いユニフォーミティの画像を表示する事ができる。特に、移動度や閾電圧が大きくばらつく低温ポリシリコンTFTを用いた画素回路で、本発明の効果が大きい。

【発明を実施するための最良の形態】

【0031】

以下、図面を参照して本発明の実施の形態を詳細に説明する。

【0032】

図1は、本発明にかかる表示装置の実施形態の全体的な構成を示すブロック図である。図示するように、本表示装置はアクティブマトリクス型であり、主要部となる画素アレイ

10

20

30

40

50

1と周辺の回路部とで構成されている。周辺の回路部は、電流ドライバー3、第一ライトスキャナ41、第二ライトスキャナ42、第三ライトスキャナ43、ドライブスキャナ5、及び、補正用スキャナ7などを含んでいる。画素アレイ1は、行状の走査線WSと列状の信号線SLと両者の交差する部分に、マトリクス状に配列された画素R、G、Bから構成されている。各画素R、G、Bは、それぞれ、画素回路2で構成されている。信号線SLは、電流ドライバー3によって駆動される。換言すると、電流ドライバー3は、信号線SLに信号電流及び基準電流を流す。走査線WSは、実際には、3本の走査線WS1、WS2、WS3に分かれている。最初の走査線(第1走査線)WS1は、第一ライトスキャナ41によって走査される。次の走査線(第2走査線)WS2は、第二ライトスキャナ42によって走査される。残る走査線(第3走査線)WS3は、第三ライトスキャナ43によって走査される。これらの走査線WS1乃至WS3に供給される制御信号は、それぞれ、タイミングが異なっている。また、走査線WS1、WS2、WS3と平行に、別の走査線DS及びAZも配線されている。走査線(第5走査線)DSは、ドライブスキャナ5によって走査される。ドライブスキャナ5は、各画素に含まれる発光素子の発光期間を制御するものである。走査線(第4走査線)AZは、補正用スキャナ7によって走査される。ライトスキャナ41、42、43、ドライブスキャナ5及び補正用スキャナ7は、全体としてスキャナ部を構成しており、1水平期間ごと画素の行を順次走査する。

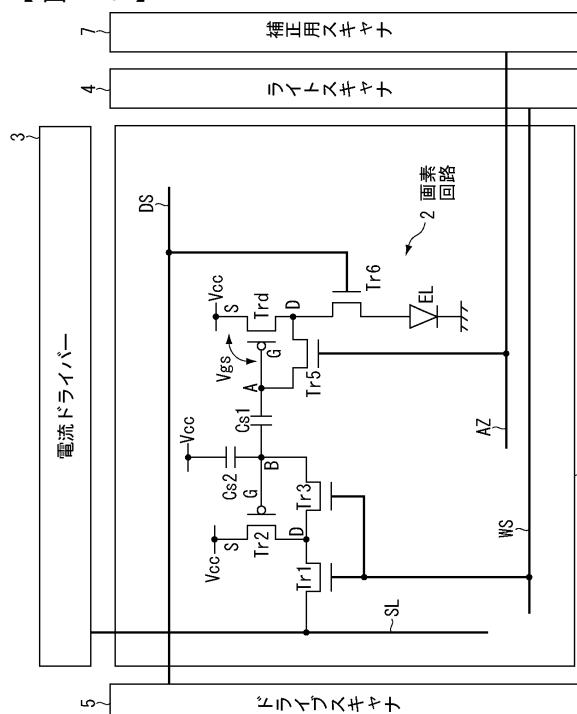

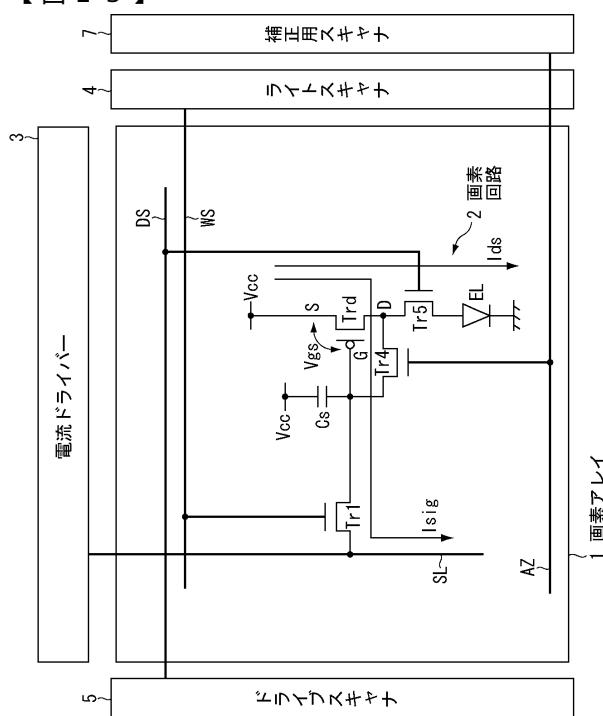

#### 【0033】

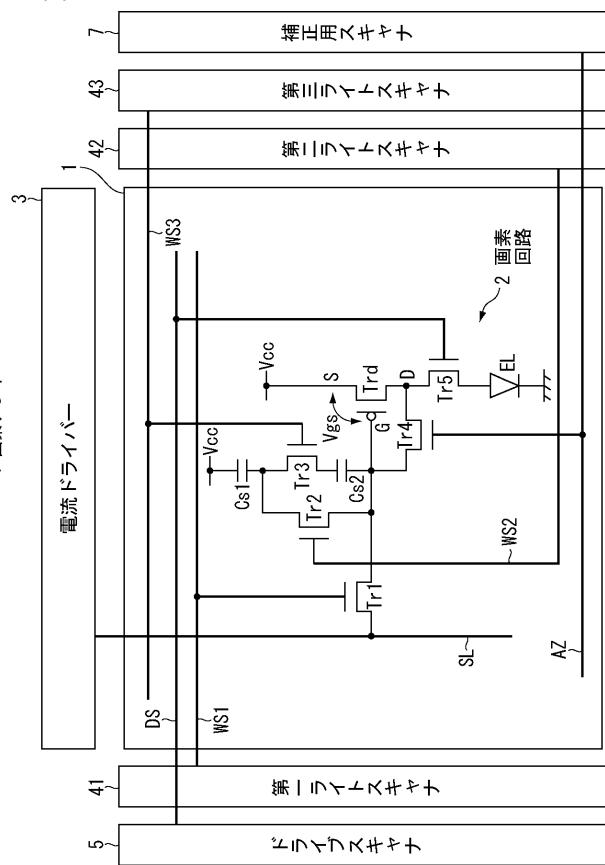

図2は、図1に示した画素回路2の構成を示す回路図である。本画素回路2は、6個の薄膜トランジスタ(第1スイッチングトランジスタTr1、第2スイッチングトランジスタTr2、第3スイッチングトランジスタTr3、第4スイッチングトランジスタTr4、第5スイッチングトランジスタTr5、及び、駆動トランジスタTrd)と、2個の画素容量(第1画素容量Cs1及び第2画素容量Cs2)と、1個の発光素子ELとで構成されている。6個の薄膜トランジスタの内、スイッチング制御用のトランジスタTr1乃至Tr5はNチャネル型である。残るトランジスタTrdは、発光素子ELを駆動する為の駆動トランジスタである。駆動トランジスタTrdはPチャネル型となっている。本実施形態では、これら6個の薄膜トランジスタは、低温ポリシリコン薄膜をチャネル領域としている。発光素子ELは、アノード及びカソードを備えた二端子型デバイスであり、例えば、有機EL発光素子を用いる事ができる。なお、上記実施例では、トランジスタTr1～Tr5は全てNチャネル型としているが、これらは、全てPチャネル型、もしくは、Nチャネル型とPチャネル型が混在していても構わない。

#### 【0034】

駆動トランジスタTrdのソースSは、電源Vccに接続されている。駆動トランジスタTrdのドレインDは、発光素子ELのアノード側に接続されている。発光素子ELのカソードは接地されている。なお、発光素子ELのカソード接地電位は、V<sub>cathode</sub>で表される場合がある。駆動トランジスタTrdのゲートGは、第2画素容量Cs2の一端に接続されている。この第2画素容量Cs2の他端は、第1画素容量Cs1の一端に接続されている。第1画素容量Cs1の他端は、電源Vccに接続されている。

#### 【0035】

スイッチングトランジスタTr1のソース/ドレインは、信号線SLと駆動トランジスタTrdのゲートGに接続されており、そのゲートは、走査線WS1を介して第一ライトスキャナ41に接続されている。スイッチングトランジスタTr2は、そのソース/ドレインが、駆動トランジスタTrdのゲートGと第1画素容量Cs1の一端との間に接続され、ゲートが、走査線WS2を介して第二ライトスキャナ42に接続されている。スイッチングトランジスタTr3は、ソース/ドレインが、第1画素容量Cs1と第2画素容量Cs2との間に接続され、このゲートが、走査線WS3を介して第三ライトスキャナ43に接続されている。スイッチングトランジスタTr4は、そのソース/ドレインが、駆動トランジスタTrdのゲートGとドレインDとの間に接続されており、そのゲートが、走査線AZを介して補正用スキャナ7に接続されている。スイッチングトランジスタTr5は、そのソース/ドレインが、駆動トランジスタTrdのドレインDと発光素子ELのア

10

20

30

40

50

ノードとの間に接続され、そのゲートが、走査線 D S を介してドライブスキャナ 5 に接続されている。

【 0 0 3 6 】

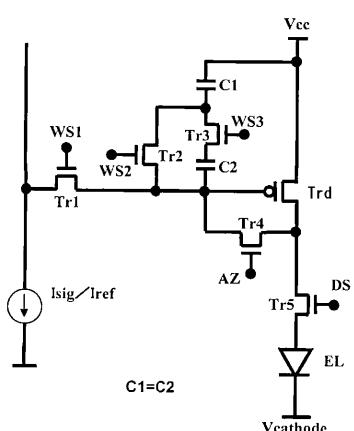

図 3 は、図 2 に示した画素回路の動作説明に供する模式図である。図示するように、信号線には、電流ドライバーから信号電流  $I_{sig}$  及び基準電流  $I_{ref}$  が交互に流れる。また、各スイッチングトランジスタ T r のゲートには、対応する走査線を介して、各スキャナから制御信号が供給される。図では、理解を容易にする為、走査線と同じ符号を用いて制御信号を表している。例えば、スイッチングトランジスタ T r 1 のゲートに印加される制御信号は W S 1 で表してある。同様に、トランジスタ T r 2 のゲートに印加される制御信号は W S 2 で表され、トランジスタ T r 3 の制御信号は W S 3 で表され、トランジスタ T r 4 の制御信号は A Z で表され、トランジスタ T r 5 の制御信号は D S で表されている。また、第 1 画素容量 C s 1 及び第 2 画素容量 C s 2 は、その容量値  $C_1, C_2$  で図示してある。本実施形態では、第 1 画素容量 C s 1 と第 2 画素容量 C s 2 の容量値  $C_1$  と  $C_2$  が等しくなるように設定されている。

【 0 0 3 7 】

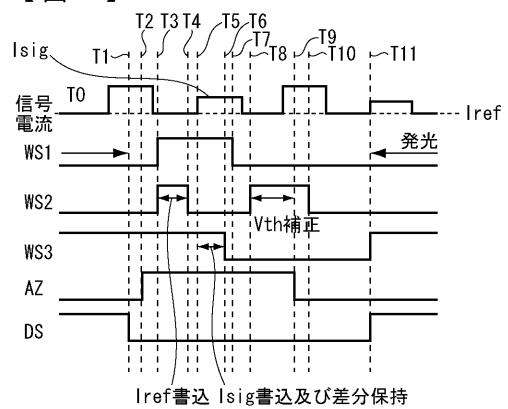

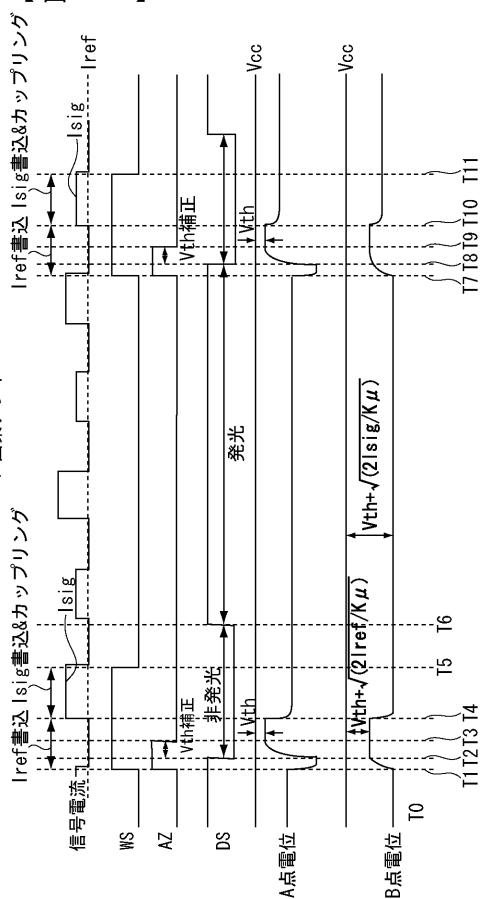

図 4 は、図 3 に示した画素回路の動作説明に供するタイミングチャートである。時間軸 T に沿って、信号電流、基準電流及び各制御信号 W S 1, W S 2, W S 3, A Z, D S の波形を表してある。信号電流  $I_{sig}$  は 1 水平期間 ( 1 H ) 毎に変化しており、それぞれ、対応する行の画素に割り当てられる。1 H 内で、電流レベルは、信号電流  $I_{sig}$  と基準電流  $I_{ref}$  との間を切り替わる。基準電流  $I_{ref}$  は、予め所定のレベルに設定されている。信号電流  $I_{sig}$  は、この基準電流  $I_{ref}$  を基準として、1 H 毎に変化している。信号電流  $I_{sig}$  のレベルが高くなる程、発光輝度は大きくなる。

【 0 0 3 8 】

タイミング T 0 で制御信号 W S 1, W S 2 及び A Z はローレベルにある一方、制御信号 W S 3 及び D S はハイレベルにある。各スイッチングトランジスタは N チャネル型であるので、対応する制御信号がハイレベルにある時、オン状態となり、ローレベルにある時、オフ状態となる。タイミング T 0 では、制御信号 D S がハイレベルである為、スイッチングトランジスタ T r 5 はオンとなっており、駆動トランジスタ T r d から発光素子 E L に駆動電流が流れるので、画素回路は発光状態である。

【 0 0 3 9 】

ここからタイミング T 1 になると、制御信号 D S がローレベルになり、発光素子 E L は非発光状態に切り替わる。タイミング T 2 で制御信号 A Z がハイレベルになる。さらに、タイミング T 3 で制御信号 W S 1 及び W S 2 もハイレベルとなる。このとき、信号線には基準電流  $I_{ref}$  が流れている。タイミング T 4 に進むと制御信号 W S 2 がローレベルに戻る。このタイミング T 3 ~ T 4 までの期間で、基準電流  $I_{ref}$  を第 1 画素容量 C s 1 に書き込む。

【 0 0 4 0 】

続いてタイミング T 5 になると、信号線側が基準電流  $I_{ref}$  から信号電流  $I_{sig}$  に切り替わる。さらにタイミング T 6 で、制御信号 W S 3 がローレベルになる。このタイミング T 5 ~ T 6 の間で、信号電流書き込み動作及び基準電流  $I_{ref}$  と信号電流  $I_{sig}$  の電流差分保持動作が行われる。

【 0 0 4 1 】

この後、タイミング T 7 で、制御信号 W S 1 が立ち下がる。さらに、タイミング T 8 で、制御信号 W S 2 が再びハイレベルになる。続いてタイミング T 9 で、制御信号 A Z がローレベルに戻る。このタイミング T 8 ~ T 9 の間で、駆動トランジスタの閾電圧  $V_{th}$  の補正動作 ( 閾電圧補正動作 ) が行われる。

【 0 0 4 2 】

さらにタイミング T 10 に進むと、制御信号 W S 2 がローレベルに戻る。タイミング T 11 になると、制御信号 W S 3 がハイレベルになるとと共に、制御信号 D S がハイレベルになる。これにより発光動作が行われる。

10

20

30

40

50

## 【0043】

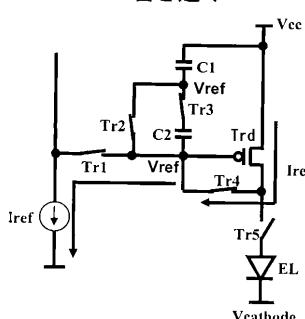

図5は、図4のタイミングチャートに示した期間T3-T4で行われる基準電流書き込み動作を示す模式図である。この期間T3-T4では、信号線に基準電流 $I_{ref}$ が流れている。スイッチングトランジスタは、Tr1乃至Tr4がオンで、Tr5がオフとなっている。したがって、基準電流 $I_{ref}$ が、電源Vccから駆動トランジスタTrd、スイッチングトランジスタTr4及びTr1を通って信号線側に流れる。この結果、基準電流 $I_{ref}$ に応じた基準電圧 $V_{ref}$ が駆動トランジスタTrdのゲートに現れる。この時、駆動トランジスタTrdのゲート電圧 $V_{gs}$ は以下の式(5)によって表される。

## 【0044】

式(5)

$$V_{gs} = V_{cc} - V_{ref}$$

10

## 【0045】

したがって、基準電流 $I_{ref}$ が駆動トランジスタTrdを流れた時の特性式は、以下の式(6)で表される。

## 【0046】

式(6)

$$\begin{aligned} I_{ref} &= \frac{k\mu}{2} (V_{gs} - V_{th})^2 \\ &= \frac{k\mu}{2} (V_{cc} - V_{ref} - V_{th})^2 \end{aligned}$$

20

## 【0047】

式(6)では $V_{gs}$ に式(5)の( $V_{cc} - V_{ref}$ )を代入する事で、基準電流 $I_{ref}$ と基準電圧 $V_{ref}$ の関係が求められている。

30

## 【0048】

ここで式(6)を $V_{ref}$ について整理すると、以下の式(7)の様になる。

## 【0049】

式(7)

$$V_{ref} = V_{cc} - V_{th} - \sqrt{\frac{2I_{ref}}{k\mu}}$$

40

## 【0050】

この様にして得られた基準電圧 $V_{ref}$ は、オン状態にあるトランジスタTr2を介して第1画素容量 $C_{s1}$ に書き込まれる。

## 【0051】

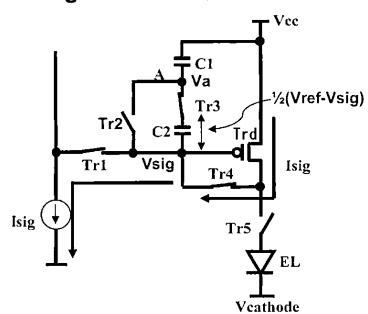

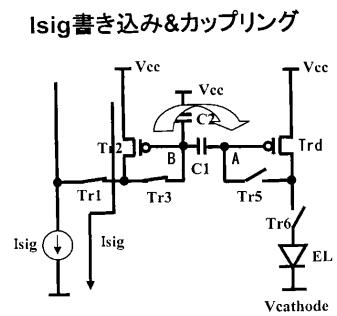

図6は、図4に示したタイミングチャートの期間T5-T6で行われる信号電流書き込み及び電流差分保持動作を示す模式図である。期間T5-T6では、信号線に信号電流 $I_{sig}$ が流れる。スイッチングトランジスタは、Tr1、Tr3及びTr4がオンにある一方、Tr2及びTr5がオフになっている。この状態で、信号電流 $I_{sig}$ が電源Vccから駆動トランジスタTrd、スイッチングトランジスタTr4及びTr1を通って信号線

50

に流れる。この結果、駆動トランジスタ T r d のゲート電位は基準電圧  $V_{ref}$  から信号電圧  $V_{sig}$  に変化する。この信号電圧  $V_{sig}$  は、式(7)で基準電圧  $V_{ref}$  を求めた時と同様にして、以下の式(8)によって求められる。

【0052】

式(8)

$$V_{sig} = V_{cc} - V_{th} - \sqrt{\frac{2I_{sig}}{k\mu}}$$

10

【0053】

駆動トランジスタ T r d のゲートに現れた電位変化 ( $V_{sig} - V_{ref}$ ) は、第2画素容量  $C_{s2}$  を介してノードAにカップリングされる。ノードAは、第1画素容量  $C_{s1}$  と第2画素容量  $C_{s2}$  との接続点であり、その電位を  $V_a$  で表してある。ゲート電位の変化の容量カップリング分は、

$$(\frac{V_{sig} - V_{ref}}{V_{ref}}) C_2 / (C_1 + C_2)$$

で表される。元々、電位  $V_{ref}$  にあったA点にこの容量カップリング分が加わる為、ノードAの電位  $V_a$  は、以下の式(9)で表される事になる。

【0054】

式(9)

20

$$V_a = V_{ref} + \frac{C_2}{C_1 + C_2} (V_{sig} - V_{ref}) = \frac{V_{sig} + V_{ref}}{2}$$

【0055】

なお、式(9)では、 $C_1 = C_2$  を仮定しているので、

$$V_a = (\frac{V_{sig} + V_{ref}}{2}) / 2$$

となっている。

【0056】

ノードAの電位  $V_a$  から駆動トランジスタ T r d のゲート電位  $V_{sig}$  を引いたものが、第2画素容量  $C_{s2}$  に保持された電位である。式(9)の結果から、この第2画素容量  $C_{s2}$  の両端に保持された電圧 ( $V_a - V_{sig}$ ) は  $(V_{ref} - V_{sig}) / 2$  で表される。さらに、この基準電圧  $V_{ref}$  及び信号電圧  $V_{sig}$  に、式(7)及び式(8)で得られた結果を代入すると、結局、以下の式(10)が得られる。

30

【0057】

式(10)

$$V_a - V_{sig} = \frac{V_{ref} - V_{sig}}{2} = \frac{\sqrt{I_{sig}} - \sqrt{I_{ref}}}{\sqrt{2k\mu}}$$

40

【0058】

式(10)から明らかなように、第2画素容量  $C_{s2}$  の両端には、信号電流  $I_{sig}$  と基準電流  $I_{ref}$  の差分に応じた電圧が保持された事になる。以上の動作により、信号電流  $I_{sig}$  の書き込みと、基準電流  $I_{ref}$  及び信号電流  $I_{sig}$  の電流差分が求められ、且つ、電流差分に応じた電圧が式(10)で表される形によって第2画素容量  $C_{s2}$  に保持される。

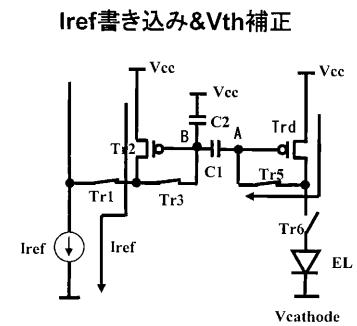

【0059】

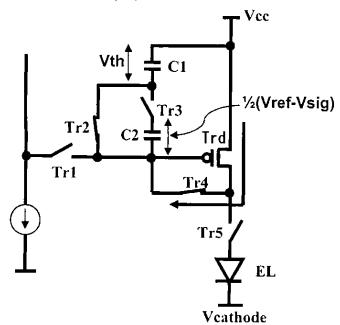

図7は、図4に示したタイミングチャートの期間 T8 - T9 で行われる閾電圧補正動作 ( $V_{th}$  キャンセル動作) を示す模式図である。この期間 T8 - T9 では、スイッチングト

50

ランジスタ Tr 1, Tr 3 及び Tr 5 がオフにある一方、スイッチングトランジスタ Tr 2 及び Tr 4 がオンしている。これにより、電源 Vcc、駆動トランジスタ Tr d、スイッチングトランジスタ Tr 4、スイッチングトランジスタ Tr 2 及び第 1 画素容量 Cs 1 により、閉ループが構成される。この閉ループに電源 Vcc から電流が流れ、第 1 画素容量 Cs 1 を充電して、駆動トランジスタ Tr d のゲート電位を上昇させる。駆動トランジスタ Tr d のゲート電圧  $V_{gs}$  が、丁度、閾電圧  $V_{th}$  に到達した段階で、過渡電流は流れなくなる。この時のゲート電圧  $V_{gs}$  が、閾電圧  $V_{th}$  として、第 1 画素容量 Cs 1 に書き込まれる事になる。この様にして、駆動トランジスタ Tr d の閾電圧  $V_{th}$  のキャンセルに必要な電位  $V_{th}$  が、第 1 画素容量 Cs 1 に保持される。

【0060】

10

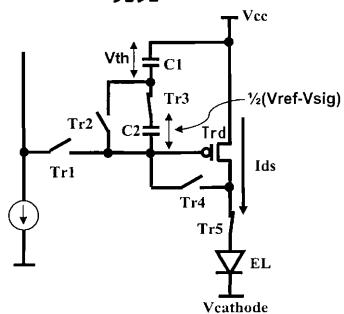

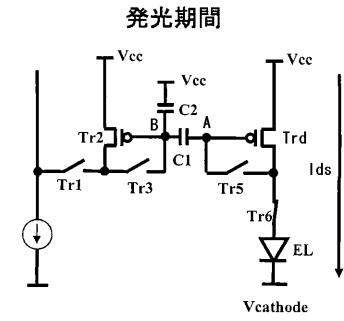

図 8 は、図 4 のタイミングチャートに示した期間 T11 以降で行われる発光動作を示す模式図である。図示するように、タイミング T11 以降の発光期間では、スイッチングトランジスタ Tr 1, Tr 2 及び Tr 4 がオフする一方、Tr 3 及び Tr 5 がオンしている。この結果、駆動電流  $I_{ds}$  が電源 Vcc から駆動トランジスタ Tr d 及びスイッチングトランジスタ Tr 5 を通って発光素子 EL に流れ、所定の輝度で発光が行われる。この発光期間における駆動トランジスタ Tr d のゲート電圧  $V_{gs}$  は、スイッチングトランジスタ Tr 3 がオンしている為、第 1 画素容量 Cs 1 に保持された電圧と第 2 画素容量 Cs 2 に保持された電圧の和となる。トランジスタ Tr 3 をオンして第 1 画素容量 Cs 1 と第 2 画素容量 Cs 2 を接続した時、駆動トランジスタ Tr d のゲート寄生容量に比べて第 1 画素容量 Cs 1 の容量値  $C_1$  及び第 2 画素容量 Cs 2 の容量値  $C_2$  の値が大きいので、第 1 画素容量 Cs 1 と第 2 画素容量 Cs 2 は電荷を保持したまま接続される。よって、駆動トランジスタ Tr d のゲート電圧  $V_{gs}$  は第 1 画素容量 Cs 1 に保持された電圧  $V_{th}$  と第 2 画素容量 Cs 2 に保持された電圧  $(V_{ref} - V_{sig}) / 2$  の和となり、以下の式(11)で表される。

20

【0061】

式(11)

$$V_{gs} = V_{th} + \frac{1}{2} (V_{ref} - V_{sig})$$

30

【0062】

一方、発光期間に流れる駆動電流  $I_{ds}$  は、以下の式(12)によって表される。なお、この式(12)は、トランジスタの基本特性を示す式(1)と同じである。

【0063】

式(12)

$$I_{ds} = \frac{k \mu}{2} (V_{gs} - V_{th})^2$$

40

【0064】

式(12)に含まれる  $V_{gs}$  に式(11)で求めた結果を代入すると、以下の式(13)が得られる。

【0065】

式(13)

$$I_{ds} = \frac{1}{2} k \mu \left( V_{th} + \frac{V_{ref} - V_{sig}}{2} - V_{th} \right)^2$$

## 【0066】

式(13)から明らかなように、元々のトランジスタ特性式に含まれていた閾電圧 $V_{th}$ の項は、第1画素容量 $C_s 1$ に保持された閾電圧 $V_{th}$ の項によってキャンセルされる。これにより、駆動トランジスタ $T_{rd}$ の閾電圧 $V_{th}$ のばらつきの影響が除かれる。さらに、式(13)で残された( $V_{ref}$  -  $V_{sig}$ ) / 2の項に式(10)で求めた結果を代入すると、以下の式(14)が得られる。

## 【0067】

式(14)

$$I_{ds} = \frac{1}{2} k \mu \left( \frac{\sqrt{I_{sig}} - \sqrt{I_{ref}}}{\sqrt{2k\mu}} \right)^2$$

## 【0068】

式(14)に含まれている移動度 $\mu$ の項は、結局、分子と分母でキャンセルされるので、最終的な駆動電流 $I_{ds}$ の式は、以下の式(15)のようになる。

## 【0069】

式(15)

$$I_{ds} = \frac{1}{4} (\sqrt{I_{sig}} - \sqrt{I_{ref}})^2$$

## 【0070】

式(15)から明らかなように、駆動電流 $I_{ds}$ は信号電流 $I_{sig}$ と基準電流 $I_{ref}$ の差分に応じて決まり、駆動トランジスタに固有の移動度 $\mu$ や閾電圧 $V_{th}$ は含まれていない。この様にして、本発明の画素回路では、信号電流 $I_{sig}$ と基準電流 $I_{ref}$ の電流差分値により発光電流が決定され、閾電圧 $V_{th}$ と移動度 $\mu$ のばらつきによらない、ユニフォーミティの高い画質を得ることができる。さらに、本画素回路で、黒表示は、 $I_{sig} = I_{ref}$ にて表される。そして、基準電流 $I_{ref}$ 及び信号電流 $I_{sig}$ の値は、書き込みに充分な電流値に設定している。このため、黒表示の信号電流でも、1水平期間内に充分画素容量に書き込む事ができ、黒浮きや縦クロストークなどの発生を抑制できる。

## 【0071】

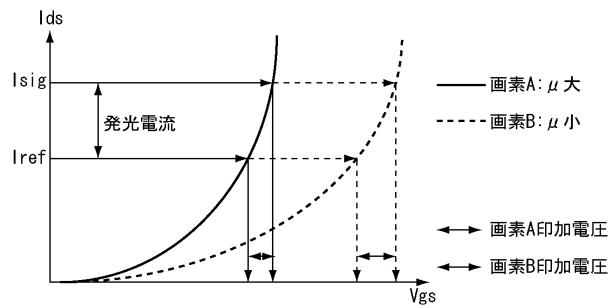

図9は、本発明にかかる画素回路に含まれる駆動トランジスタの動作を模式的に表したグラフである。このグラフは、横軸にゲート電圧 $V_{gs}$ を取り、縦軸にドレイン電流 $I_{ds}$ を取って、駆動トランジスタの動作特性を模式的に表している。実線は、画素Aに含まれる駆動トランジスタの特性であって、移動度 $\mu$ が大きい場合である。点線のカーブは、画素Bに含まれる駆動トランジスタの特性であって、移動度 $\mu$ が小さい場合である。移動度 $\mu$ が小さいほど特性カーブは傾斜が緩やかになっており、各画素で特性にばらつきがある。この様な特性のばらつきは、低温ポリシリコン薄膜を用いたトランジスタに顕著である。この様に特性のばらつきがある駆動トランジスタ $T_{rd}$ であっても、本発明では、信号電流 $I_{sig}$ と基準電流 $I_{ref}$ の差分に応じて発光電流が定まるように駆動トランジスタ $T_{rd}$ を制御している。したがって、移動度 $\mu$ がばらついても、常に、各画素で電流差分に応じた発光電流制御が行われる為、高ユニフォーミティの画面品質が得られる。

## 【0072】

10

20

30

40

50

以上に説明したように、図2に示した本発明の実施形態にかかる画素回路は、信号電流  $I_{sig}$  が流れる信号線  $S_L$  と、制御信号を供給する走査線  $WS_1, WS_2, WS_3, AZ, DS$  とが交差する部分に配されている。この画素回路2は、発光素子  $EL$  と、発光素子  $EL$  に駆動電流  $I_{ds}$  を供給する駆動トランジスタ  $Tr_d$  と、制御信号  $WS_1, WS_2, WS_3, AZ, DS$  に応じて動作し、信号電流  $I_{sig}$  に基づいて駆動トランジスタ  $Tr_d$  の駆動電流  $I_{ds}$  を制御する制御部とで構成されている。この制御部は、第1サンプリング手段と第2サンプリング手段と差分手段とを含んでいる。第1サンプリング手段は、トランジスタ  $Tr_1, Tr_3, Tr_4$  と第2画素容量  $C_s 2$  とで構成されており、信号線  $S_L$  に流れる信号電流  $I_{sig}$  をサンプリングする。第2サンプリング手段は、トランジスタ  $Tr_1, Tr_2, Tr_3, Tr_4$  と第1画素容量  $C_s 1$  とで構成され、信号電流  $I_{sig}$  に前後して信号線  $S_L$  に流れる所定の基準電流  $I_{ref}$  をサンプリングする。差分手段は、トランジスタ  $Tr_1, Tr_3, Tr_4$  と、第1画素容量  $C_s 1$  及び第2画素容量  $C_s 2$  で構成されており、サンプリングされた基準電流  $I_{ref}$  に対するサンプリングされた信号電流  $I_{sig}$  の差分に応じた制御電圧 ( $V_{ref} - V_{sig}$ ) / 2 を生成する。駆動トランジスタ  $Tr_d$  は、この制御電圧 ( $V_{ref} - V_{sig}$ ) / 2 をゲートGに受けて、ソースS / ドレインD間に流れる駆動電流  $I_{ds}$  を発光素子  $EL$  に供給して発光を行わせる。

## 【0073】

第1サンプリング手段及び第2サンプリング手段が各々サンプリングする信号電流  $I_{sig}$  及び基準電流  $I_{ref}$  は、両者の相対的な差分が小さいとき、発光素子  $EL$  の発光量が小さくなり、差分が大きいとき、発光量が大きくなる一方、相対的な差分が小さいときでも、信号電流  $I_{sig}$  及び基準電流  $I_{ref}$  の絶対的なレベルは、サンプリングを可能とするよう大きく設定されている。

## 【0074】

画素回路2の制御部は、上述した第1サンプリング手段及び第2サンプリング手段と差分手段に加え、補正手段を有している。この補正手段は、トランジスタ  $Tr_2, Tr_4$  と第1画素容量  $C_s 1$  とで構成されており、駆動トランジスタ  $Tr_d$  の閾電圧  $V_{th}$  を検出して、これを、前述した制御電圧 ( $V_{ref} - V_{sig}$ ) / 2 に加える事ができる様にしている。これにより、閾電圧  $V_{th}$  の影響を、駆動電流  $I_{ds}$  からキャンセルする事ができる。

## 【0075】

本実施形態では、第1サンプリング手段は信号電流  $I_{sig}$  を駆動トランジスタ  $Tr_d$  に流して、その時ゲートGに発生する信号電圧  $V_{sig}$  をサンプリングする。同様に、第2サンプリング手段は駆動トランジスタ  $Tr_d$  に基準電流  $I_{ref}$  を流して、その時ゲートGに発生する基準電圧  $V_{ref}$  をサンプリングする。このとき、差分手段は、第2画素容量  $C_s 2$  を介して信号電圧  $V_{sig}$  と基準電圧  $V_{ref}$  をカップリングさせ、両者の差分を求めて制御電圧 ( $V_{ref} - V_{sig}$ ) / 2 を生成している。なお、第1サンプリング手段は、サンプリングした信号電圧  $V_{sig}$  を保持する第2画素容量  $C_s 2$  を有し、第2サンプリング手段は、サンプリングした基準電圧  $V_{ref}$  を保持し、且つ、信号電圧  $V_{sig}$  にカップリングする為の第1画素容量  $C_s 1$  を有する。この場合、第1画素容量  $C_s 1$  及び第2画素容量  $C_s 2$  は同一の容量値を有する。

## 【0076】

図10は、本発明にかかる画素回路、及び、これを組み込んだ表示装置の他の実施形態を示す回路図である。図示するように、本表示装置は、主要部を構成する画素アレイ1と、その周辺に位置する回路部とで構成されている。周辺回路部は、ドライバーパー部を構成する電流ドライバー3、スキャナ部を構成するライトスキャナ4、ドライブスキャナ5、補正用スキャナ7で構成されている。画素アレイ1には、列状に信号線  $S_L$  が形成されている。この信号線  $S_L$  は電流ドライバー3によって駆動され、所定の基準電流及び信号電流が交互に流れる様になっている。画素アレイ1には、走査線  $WS, DS, AZ$  が行状に配されている。走査線(第1走査線)  $WS$  は、ライトスキャナ4に接続されており、信号電流や基準電流のサンプリング用の制御信号  $WS$  が供給される。走査線(第3走査線)  $DS$  には、ドライブスキャナ5が接続されており、発光制御用の制御信号  $DS$  が供給される。

走査線（第2走査線）AZには、補正用スキャナ7が接続されており、闇電圧補正用の制御信号AZが供給される。

#### 【0077】

列状の信号線SLと行状の走査線WS, DS, AZが交差する部分に、各画素回路2が集積形成されている。図10は、図示を簡略化するため1個の画素回路2のみを表示している。図示するように、画素回路2は、6個のトランジスタ（第1スイッチングトランジスタTr1、第2スイッチングトランジスタTr2、第3スイッチングトランジスタTr3、第4スイッチングトランジスタTr5、第5スイッチングトランジスタTr6、及び、駆動トランジスタTrd）と、2個の画素容量（第1画素容量Cs1と第2画素容量Cs2）と、1個の発光素子ELとで構成されている。6個のトランジスタのうち、Tr1, Tr3, Tr5及びTr6はNチャネル型の薄膜トランジスタである。これに対し、トランジスタTr2とTrdはPチャネル型の薄膜トランジスタである。一対のPチャネル型トランジスタTr2, Trdは、第1画素容量Cs1を介してゲートが互いに接続されており、カレントミラー構成となっている。トランジスタTr2はカレントミラー回路の入力側に位置し、トランジスタTrdは出力側に位置する。この出力側に位置するトランジスタTrdは、発光素子ELを駆動する為の駆動トランジスタである。発光素子ELはアノード及びカソードを備えた二端子型（ダイオード型）であり、例えば、有機EL発光素子を用いる事ができる。駆動トランジスタTrdのソースSは、電源Vccに接続されている。駆動トランジスタTrdのドレインDは、トランジスタTr6を介して発光素子ELのアノードに接続されている。発光素子ELのカソードは接地されている。駆動トランジスタTrdのゲートGは第1画素容量Cs1の一端に接続されている。図では、第1画素容量Cs1の一端をA点で表してある。トランジスタTr5のソース/ドレインは、駆動トランジスタTrdのゲートGとドレインDとの間に接続されている。このトランジスタTr5のゲートには、走査線AZを介して補正用スキャナ7から制御パルスAZが供給される。本明細書では、理解と表記を容易にする為、走査線と対応する制御信号は同じ表記を用いている。トランジスタTr6のソース/ドレインは、駆動トランジスタTrdのドレインDと発光素子ELのアノードとの間に接続され、そのゲートには、走査線DSを介してドライブスキャナ5から発光制御用の制御信号DSが供給される。カレントミラー回路の入力側を構成するトランジスタTr2は、そのソースSが電源Vccに接続され、ドレインDがトランジスタTr1を介して信号線SLに接続され、ゲートGが第1画素容量Cs1の他端に接続されている。図では、第1画素容量Cs1の他端をB点で表してある。トランジスタTr2は、駆動トランジスタTrdのミラーであって、基本的に、移動度μは等しい値となっている。トランジスタTr1のソース/ドレインは、信号線SLとトランジスタTr2のドレインDとの間に接続され、そのゲートは、走査線WSを介してライトスキャナ4から信号サンプリング用の制御信号WSを受け入れる。トランジスタTr3のソース/ドレインは、トランジスタTr2のドレインDとB点との間に接続されており、そのゲートは、走査線WSに接続されている。B点と電源Vccとの間に、別の画素容量（第2画素容量Cs2）が接続されている。

#### 【0078】

図11は、図10に示した画素回路の動作説明に供するタイミングチャートである。時間軸Tに沿って、信号電流、基準電流の波形及び各制御信号WS, AZ, DSの波形の変化を表している。合わせて、A点及びB点における電位の変化も表示してある。前述したように、A点は、カレントミラー回路を構成するペアトランジスタTr2, Trdの内、出力側に位置する駆動トランジスタTrdのゲートGである。またB点は、ペアトランジスタTr2, Trdの内、入力側に位置するミラートランジスタTr2のゲートGである。図示のタイミングチャートは、タイミングT1で1フィールドがスタートし、タイミングT7で1フィールドが終わる様になっている。1フィールドで1画面を表示する。このフィールド動作を繰り返すことで、連続的に画面を画素アレイに表示する。

#### 【0079】

信号線に流れる信号電流は、1水平期間（1H）毎に変化している。各水平期間では、

10

20

30

40

50

前半で所定の基準電流  $I_{ref}$  が流れ、後半で信号電流  $I_{sig}$  が流れる。基準電流  $I_{ref}$  は固定されている一方、信号電流  $I_{sig}$  は映像信号に応じたレベルを有する。

#### 【0080】

当該フィールドが開始する前のタイミング T 0 で、制御信号 W S 及び A Z はローレベルにある一方、制御信号 D S はハイレベルにある。制御信号 D S がハイレベルなので、スイッチングトランジスタ T r 6 がオンしており、発光素子 E L には駆動トランジスタ T r d から駆動電流が供給される。したがって、タイミング T 0 では、発光素子 E L が発光状態にある。

#### 【0081】

タイミング T 1 で当該フィールドがスタートすると、制御信号 W S 及び A Z が立ち上がり、全てのスイッチングトランジスタ T r 1, T r 3, T r 5, T r 6 がオン状態になる。このとき、略同時に信号線側が信号電流  $I_{sig}$  から基準電流  $I_{ref}$  に切り替わる。これにより、電源 V c c から入力側トランジスタ T r 2 及びスイッチングトランジスタ T r 1 を通って信号線 S L に基準電流  $I_{ref}$  が流れる。これに応じて、入力側トランジスタ T r 2 のゲート G に接続された B 点の電位が、基準電流  $I_{ref}$  に対応したレベルになる。換言すると、第2画素容量 C s 2 に基準電流  $I_{ref}$  に応じた基準電圧が書き込まれる事になる。この動作は、タイミング T 4 まで続く。すなわち、タイミング T 1 ~ タイミング T 4 までの期間 T 1 - T 4 で、基準電流  $I_{ref}$  の書き込みが行われる。

#### 【0082】

一方、A 点側では、タイミング T 1 で一旦駆動トランジスタ T r d に電流を流した後、タイミング T 2 でスイッチングトランジスタ T r 6 を遮断する。これにより、駆動トランジスタ T r d は電流路を遮断されるので、ゲート電位 (A 点電位) は上昇していく。A 点電位が駆動トランジスタ T r d の閾電圧  $V_{th}$  に達した時点で、駆動トランジスタ T r d はカットオフする。この動作で、駆動トランジスタ T r d の閾電圧  $V_{th}$  が検出され、第1画素容量 C s 1 に保持される。この保持された  $V_{th}$  は、後の発光動作で、駆動トランジスタ T r d の閾電圧のばらつきをキャンセルする 为に用いられる。駆動トランジスタ T r d がカットオフした後のタイミング T 3 で、制御信号 A Z はローレベルとなり、スイッチングトランジスタ T r 5 がオフする。これにより、第1画素容量 C s 1 に書き込まれた閾電圧  $V_{th}$  が固定される。この様にして、駆動トランジスタ T r d の閾電圧  $V_{th}$  を検出保持する処理が、タイミング T 2 ~ タイミング T 3 の間で行われる。この期間 T 2 - T 3 を、本明細書では、閾電圧補正期間あるいは  $V_{th}$  キャンセル期間 という。以上の説明から明らかのように、期間 T 1 - T 4 の間で、カレントミラー回路の入力側トランジスタ T r 2 側では基準電流書き込みが行われる一方、駆動トランジスタ (出力側トランジスタ T r d) では閾電圧キャンセルが行われる。

#### 【0083】

タイミング T 4 で、信号線に流れる電流が基準電流  $I_{ref}$  から信号電流  $I_{sig}$  に切り替わる。この結果、入力側トランジスタ T r 2 には、電源 V c c から信号線 S L に向かって信号電流  $I_{sig}$  が流れる。よって、B 点の電位は、先の基準電流  $I_{ref}$  に応じたレベルから信号電流  $I_{sig}$  に応じたレベルに変化する。この変化は、カレントミラー動作により第1画素容量 C s 1 を介して A 点側にカップリングされる。この後、タイミング T 5 で制御信号 W S がローレベルになり、トランジスタ T r 1 及び T r 3 がオフする。この様にして、タイミング T 4 ~ タイミング T 5 までの期間 T 4 - T 5 で、信号電流  $I_{sig}$  がサンプリングされ、且つ、基準電流  $I_{ref}$  と信号電流  $I_{sig}$  の差分に応じた電位変化が、B 点側から A 点側にカップリングされる。

#### 【0084】

タイミング T 6 に至ると制御信号 D S が再びハイレベルとなり、スイッチングトランジスタ T r 6 がオンする。これにより、駆動トランジスタ T r d と発光素子 E L が直結し、駆動トランジスタ T r d から発光素子 E L に駆動電流が供給され、発光状態となる。このとき、駆動トランジスタ T r d から供給される駆動電流は、A 点に書き込まれた電位に応じたものとなる。A 点電位は先に説明したように、基準電流と信号電流の差分に応じたも

10

20

30

40

50

のとなっている。

【0085】

この後、タイミングT7に至ると、当該フィールドが終了すると共に、次のフィールドが開始する。前のフィールドと同じようにタイミングT7で基準電流書き込みが始まると共に、次のタイミングT8で閾電圧キャンセル動作が始まる。

【0086】

図12は、図11のタイミングチャートに示した期間T1-T4で行われる基準電流書き込み及び閾電圧補正動作を示す模式図である。理解を容易にする為、この模式図では各スイッチングトランジスタTr1, Tr3, Tr5, Tr6をスイッチシンボルで置き換え、また、第1画素容量Cs1と第2画素容量Cs2を容量値C1, C2で表してある。カレントミラー構成の画素回路の出力側で閾電圧補正動作が行われる。すなわち、トランジスタTr6をオン状態からオフ状態に切り替えることで駆動トランジスタTrdの電流路が遮断され、スイッチングトランジスタTr5を介して第1画素容量Cs1を充電し始める。その充電により、A点電位が駆動トランジスタTrdの閾電圧Vthまで上昇すると、駆動トランジスタTrdがカットオフする。この後、トランジスタTr5をオフすることで、第1画素容量Cs1に保持された閾電圧Vthが固定される。

【0087】

一方、カレントミラー回路の入力側で基準電流書き込みが行われる。トランジスタTr1及びTr3がオンしているので、電源Vccから入力側トランジスタTr2及びスイッチングトランジスタTr1を通って基準電流Irefが信号線に流れる。このとき、入力側トランジスタTr2のゲートに接続したB点に現れる電位を基準電圧Vrefとする。この基準電圧Vrefは基準電流Irefに応じたレベルとなる。入力側トランジスタTr2のソースSとゲートGとの間に現れるゲート電圧Vgsは、(Vcc - Vref)で表される。ここで、入力側トランジスタTr2は、トランジスタTr3がオンなので、飽和領域で動作しており、ドレイン電流Irefとゲート電圧Vgsとの関係は、以下の式(16)で表される。

【0088】

式(16)

$$I_{ref} = \frac{k\mu}{2} (V_{gs} - V_{th})^2$$

$$= \frac{k\mu}{2} (V_{cc} - V_{ref} - V_{th})^2$$

【0089】

式(16)において、Vgsは(Vcc - Vref)で置き換えられている。したがって、式(16)は、IrefとVrefの関係を表したものとなる。

【0090】

式(16)をVrefについて整理すると、以下の式(17)が得られる。

【0091】

式(17)

$$V_{ref} = V_{cc} - V_{th} - \sqrt{\frac{2I_{ref}}{k\mu}}$$

【0092】

式(17)から明らかなように、B点の電位Vrefは、基準電流Irefの関数となってい

10

20

30

40

50

る。なお、式(17)中、 $\mu$ は入力側トランジスタTr2の移動度を表し、 $k$ はトランジスタTr2のサイズを表し、 $V_{th}$ はトランジスタTr2の閾電圧を表している。

【0093】

図13は、図11に示したタイミングチャートの期間T4-T5で行われる基準電流書き込み及びカップリング動作を示す模式図である。この期間T4-T5では、トランジスタTr5及びTr6がオフすると共に、信号線を流れる電流が、基準電流 $I_{ref}$ から信号電流 $I_{sig}$ に切り替わる。これにより、電源 $V_{cc}$ から、入力側トランジスタTr2及びスイッチングトランジスタTr1を通って、信号線に信号電流 $I_{sig}$ が流れる。換言すると、この信号電流 $I_{sig}$ は、入力側トランジスタTr2を流れるドレイン電流となっている。このドレイン電流 $I_{sig}$ が流れる事で、B点の電位は先の基準電圧 $V_{ref}$ から信号電圧 $V_{sig}$ に変化する。基準電圧 $V_{ref}$ を表す式(17)と同じ計算で、信号電圧 $V_{sig}$ が、以下の式(18)により表される。

【0094】

式(18)

$$V_{sig} = V_{cc} - V_{th} - \sqrt{\frac{2I_{sig}}{k\mu}}$$

【0095】

式(18)から明らかなように、B点の電位 $V_{sig}$ は信号電流 $I_{sig}$ の関数となっている。

【0096】

B点に現れる電位変化は、 $V_b = V_{sig} - V_{ref}$ となる。これに式(17)及び式(18)を代入すると、以下の式(19)が得られる。

【0097】

式(19)

$$\Delta V_b = \sqrt{\frac{2}{k\mu}} (\sqrt{I_{ref}} - \sqrt{I_{sig}})$$

【0098】

式(19)から明らかなように、B点の電位変化 $V_b$ は、基準電流 $I_{ref}$ の平方根と信号電流 $I_{sig}$ の平方根との差分となっている。

【0099】

このB点の電位変化 $V$ は、カレントミラー動作により、第1画素容量 $C_{s1}$ を介してA点側にカップリングされる。カップリング量は、第1画素容量 $C_{s1}$ の容量値 $C_1$ と駆動トランジスタTrdのゲート容量 $C_g$ との容量分割にて決定される。したがって、A点の電位変化 $V_a$ は、以下の式(20)により表される。

【0100】

式(20)

$$\Delta V_a = \frac{C_1}{C_1 + C_g} \Delta V_b$$

【0101】

式(20)の $V_b$ に式(19)を代入すると、結局、A点の電位変化 $V_a$ は、以下の式(21)で表される事になる。

【0102】

式(21)

10

20

30

40

50

$$\Delta V_a = \frac{C1}{C1 + Cg} \sqrt{\frac{2}{k \mu}} (\sqrt{I_{ref}} - \sqrt{I_{sig}})$$

## 【0103】

式(21)において、第1画素容量  $C_s 1$  の容量  $C_1$  は駆動トランジスタ  $T_{rd}$  のゲート容量  $C_g$  に比べて大きい。したがって、式(21)の右辺の係数  $C_1 / (C_1 + C_g)$  は 1 に近い値となっている。換言すると、カレントミラー回路の入力側の電位変化  $V_b$  は、略そのまま出力側の電位変化  $V_a$  にミラーリングされる。

## 【0104】

図14は、図11に示したタイミングチャートの期間  $T_6 - T_8$  で行われる発光動作を示す模式図である。発光期間では、スイッチングトランジスタ  $T_{r1}, T_{r3}, T_{r5}$  がオフする一方、 $T_{r6}$  がオンする。これにより、駆動トランジスタ  $T_{rd}$  と発光素子  $EL$  が直結され、駆動電流  $I_{ds}$  が流れ発光素子  $EL$  が発光する。このとき流れる駆動電流  $I_{ds}$  は、駆動トランジスタ  $T_{rd}$  のゲート電圧  $V_{gs}$  により規定される。ゲート電圧  $V_{gs}$  は、電源電位  $V_{cc}$  から A 点電位  $V_a$  を引いたものである。A 点電位  $V_a$  は、闘電圧 キャンセル動作で書き込まれた電位  $(V_{cc} - V_{th})$  に式(21)で求めた電位変化  $\Delta V_a$  を足したものである。したがって、 $V_a = V_{cc} - V_{th} + \Delta V_a$  となる。この様にして求めた  $V_{gs}$  を先の式(1)で表したトランジスタの基本特性式に代入すると、駆動電流  $I_{ds}$  が、以下の式(22)の様に求められる事になる。

## 【0105】

式(22)

$$I_{ds} = \frac{1}{2} k' \mu \{ V_{cc} - (V_{cc} - V_{th} + \Delta V_a) - V_{th} \}^2$$

$$= \left( \frac{C1}{C1 + Cg} \right)^2 \frac{k'}{k} (\sqrt{I_{sig}} - \sqrt{I_{ref}})^2$$

10

20

30

## 【0106】

式(22)中で、 $\mu$  は駆動トランジスタ  $T_{rd}$  の移動度を表している。これは、ペアトランジスタの他方を構成するトランジスタ  $T_{r2}$  の移動度  $\mu$  と同じである。また、 $k'$  は駆動トランジスタ  $T_{rd}$  のサイズファクタを表している。式(22)を整理すると、結局、駆動電流  $I_{ds}$  は、信号電流  $I_{sig}$  と基準電流  $I_{ref}$  の差分に応じた値となっており、闘電圧  $V_{th}$  及び移動度  $\mu$  の影響はキャンセルされている。式(22)で表された駆動電流  $I_{ds}$  には、闘電圧  $V_{th}$  や移動度  $\mu$  の項が含まれない事が分かる。これにより、本発明にかかる画素回路は、闘電圧  $V_{th}$  や移動度  $\mu$  のばらつきに依存しない、ユニフォーミティの高い画質を得る事ができる。また、駆動電流  $I_{ds}$  の値は  $k$  と  $k'$  の比、つまりペアトランジスタ  $T_{r2}, T_{rd}$  のサイズ比によって決められる。さらに、本発明の画素回路では、黒表示は、 $I_{sig} = I_{ref}$  に設定する事で得られる。式(22)から明らかのように、 $I_{sig} = I_{ref}$  とすれば、 $I_{ds} = 0$  となり、発光素子には駆動電流が流れないので、完全な黒表示が得られる。黒表示の場合であっても、信号電流  $I_{sig}$  及び基準電流  $I_{ref}$  の絶対値は書き込みに充分な電流値としている。この為、黒信号でも、1 水平期間 (1H) 内に充分書き込む事ができ、黒浮きや縦クロストークなどの発生を抑制できる。なお、本画素回路において駆動トランジスタ  $T_{rd}$  とミラートランジスタ  $T_{r2}$  以外のスイッチングトランジスタ  $T_{r1}, T_{r3}, T_{r5}$  及び  $T_{r6}$  は N チャネル型を用いているが、これに限られるものではなく、P チャネル型であっても良い。あるいは、N チャネル型と P チャネル型とを混

40

50

在させても良い。

【0107】

以上の説明から明らかなように、本発明にかかる画素回路2は、信号電流 $I_{sig}$ が流れる信号線 $S_L$ と制御信号を供給する走査線 $WS$ ,  $DS$ ,  $AZ$ とが交差する部分に配されている。画素回路2は、発光素子 $EL$ と、これに駆動電流 $I_{ds}$ を供給する駆動トランジスタ $Tr_d$ と、各制御信号 $WS$ ,  $AZ$ ,  $DS$ に応じて動作し、信号電流 $I_{sig}$ に基づいて駆動トランジスタ $Tr_d$ の駆動電流 $I_{ds}$ を制御する制御部とで構成されている。制御部は、基本的に、第1サンプリング手段と第2サンプリング手段と差分手段とを含む。第1サンプリング手段は、スイッチングトランジスタ $Tr_1$ ,  $Tr_3$ と第2画素容量 $C_s2$ とミラートランジスタ $Tr_2$ とで構成され、信号線 $S_L$ に流れる信号電流 $I_{sig}$ をサンプリングする。第2サンプリング手段は、スイッチングトランジスタ $Tr_1$ ,  $Tr_3$ と第2画素容量 $C_s2$ とミラートランジスタ $Tr_2$ とで構成され、信号電流 $I_{sig}$ に前後して信号線 $S_L$ に流れる所定の基準電流 $I_{ref}$ をサンプリングする。差分手段は、第1画素容量 $C_s1$ を含んでおり、サンプリングされた基準電流 $I_{ref}$ に対するサンプリングされた信号電流 $I_{sig}$ の差分に応じた制御電圧を生成する。駆動トランジスタ $Tr_d$ は、この制御電圧をゲートGに受けて、ソースS/ドレインD間に流れる駆動電流 $I_{ds}$ を発光素子 $EL$ に供給して発光を行わせる。

10

【0108】

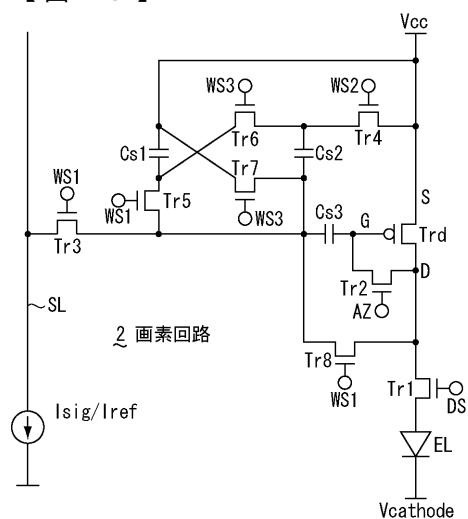

図15は、本発明にかかる画素回路の別の実施形態を示す模式的な回路図である。画素回路2は、列状の信号線 $S_L$ と行状の走査線 $WS_1$ ,  $WS_2$ ,  $WS_3$ ,  $AZ$ ,  $DS$ とが交差する部分に配されている。信号線 $S_L$ には、図示しない電流ドライバーから信号電流 $I_{sig}$ と基準電流 $I_{ref}$ が前後して流される。走査線(第1走査線) $WS_1$ 、走査線(第2走査線) $WS_2$ 、走査線(第3走査線) $WS_3$ 、走査線(第5走査線) $AZ$ 、走査線(第4走査線) $DS$ には、それぞれ、対応するスキャナから、制御信号 $WS_1$ ,  $WS_2$ ,  $WS_3$ ,  $AZ$ ,  $DS$ を供給される。本明細書では表記を簡略化する為、走査線とこれに対応する制御信号は同じ参照符号を用いてある。

20

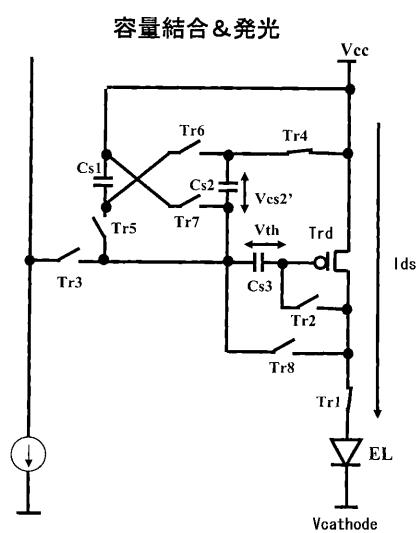

【0109】

画素回路2は、8個のスイッチングトランジスタ $Tr_1$ 乃至 $Tr_8$ (第1スイッチングトランジスタ $Tr_1$ 、第2スイッチングトランジスタ $Tr_2$ 、第3スイッチングトランジスタ $Tr_3$ 、第4スイッチングトランジスタ $Tr_4$ 、第5スイッチングトランジスタ $Tr_5$ 、第6スイッチングトランジスタ $Tr_6$ 、第7スイッチングトランジスタ $Tr_7$ 、及び、第8スイッチングトランジスタ $Tr_8$ )と、1個の駆動トランジスタ $Tr_d$ と、3個の画素容量 $C_s1$ 乃至 $C_s3$ と、発光素子 $EL$ とで構成されている。スイッチングトランジスタ $Tr_1$ 乃至 $Tr_8$ は、全て、Nチャネル型の薄膜トランジスタである。駆動トランジスタ $Tr_d$ はPチャネル型の薄膜トランジスタである。発光素子 $EL$ はアノード及びカソードを備えた二端子型(ダイオード型)の発光素子であり、例えば、有機EL素子を用いる事ができる。なお、上記実施例では、トランジスタ $Tr_1$ ～ $Tr_8$ は全てNチャネル型としているが、これらは、全てPチャネル型、もしくは、Nチャネル型とPチャネル型が混在していても構わない。

30

【0110】

駆動トランジスタ $Tr_d$ は、そのソースSが電源 $V_{cc}$ に接続されており、ドレインDがスイッチングトランジスタ $Tr_1$ を介して発光素子 $EL$ のアノード側に接続され、そのゲートGは第3画素容量 $C_s3$ の一端に接続されている。駆動トランジスタ $Tr_d$ と発光素子 $EL$ の間に介在するスイッチングトランジスタ $Tr_1$ のゲートには、走査線 $DS$ から制御信号 $DS$ が印加される。駆動トランジスタ $Tr_d$ のゲートGとドレインDとの間に、スイッチングトランジスタ $Tr_2$ が接続されている。このトランジスタ $Tr_2$ のゲートは走査線 $AZ$ に接続されている。

40

【0111】

スイッチングトランジスタ $Tr_3$ のソース/ドレインは、信号線 $S_L$ と第3画素容量 $C_s3$ の他端との間に接続されている。このトランジスタ $Tr_3$ のゲートは走査線 $WS_1$ に

50

接続されている。スイッチングトランジスタ  $T_{r5}$  は、第3画素容量  $C_{s3}$  の他端と第1画素容量  $C_{s1}$  の一端との間に接続されている。このスイッチングトランジスタ  $T_{r5}$  のゲートは、トランジスタ  $T_{r3}$  と同じく、走査線  $WS_1$  に接続されている。第1画素容量  $C_{s1}$  の他端は電源  $V_{cc}$  に接続されている。スイッチングトランジスタ  $T_{r4}$  は、電源  $V_{cc}$  と第2画素容量  $C_{s2}$  の一端との間に接続されている。このスイッチングトランジスタ  $T_{r4}$  のゲートは、走査線  $WS_2$  に接続されている。第2画素容量  $C_{s2}$  の他端は、第3画素容量  $C_{s3}$  の他端に接続されている。スイッチングトランジスタ  $T_{r6}$  は、第1画素容量  $C_{s1}$  の一端と第2画素容量  $C_{s2}$  の一端との間に接続されている。このトランジスタ  $T_{r6}$  のゲートは、走査線  $WS_3$  に接続されている。また、トランジスタ  $T_{r7}$  は、第1画素容量  $C_{s1}$  の他端と第2画素容量  $C_{s2}$  の他端との間に接続されている。このスイッチングトランジスタ  $T_{r7}$  のゲートは、トランジスタ  $T_{r6}$  と同じく、走査線  $WS_3$  に接続されている。最後に、スイッチングトランジスタ  $T_{r8}$  は、駆動トランジスタ  $T_{rd}$  のドレイン  $D$  と第3画素容量  $C_{s3}$  の他端との間に接続されている。このトランジスタ  $T_{r8}$  のゲートは、スイッチングトランジスタ  $T_{r3}$  及び  $T_{r5}$  と同じく、走査線  $WS_1$  に接続されている。10

#### 【0112】

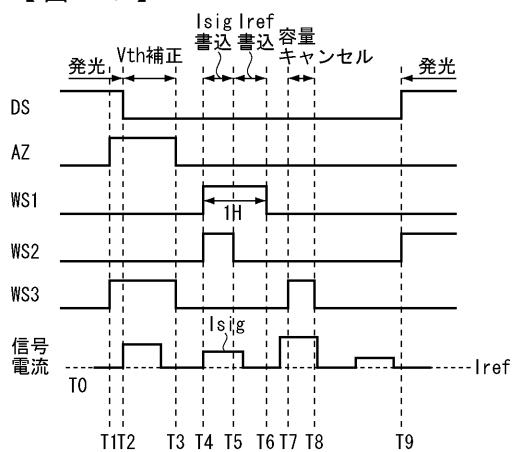

図16は、図15に示した画素回路2の動作説明に供するタイミングチャートである。時間軸  $T$  に沿って、制御信号  $DS$ ,  $AZ$ ,  $WS_1$ ,  $WS_2$ ,  $WS_3$  の波形変化を表している。同時に、信号電流  $I_{sig}$ 、基準電流の波形変化も表してある。この信号電流  $I_{sig}$  は、1水平期間 (1H) 毎に信号レベルが変化する。また、各水平期間内で、前半に信号電流  $I_{sig}$  が流れた後、後半は所定の基準電流  $I_{ref}$  に切り替わる。基準電流  $I_{ref}$  は固定されているのに対し、信号電流  $I_{sig}$  は映像信号に応じて変化する。本表示装置は、1フィールドで1画面を画素アレイに書き込む。図16のタイミングチャートでは、1フィールドがタイミング  $T_1$  から始まるように記載されている。20

#### 【0113】

当該フィールドが開始するタイミング  $T_1$  の前の期間  $T_0$  で、制御信号  $DS$  がハイレベルにある一方、残りの制御信号  $AZ$ ,  $WS_1$ ,  $WS_2$ ,  $WS_3$  はローレベルにある。制御信号  $DS$  がハイレベルなので、スイッチングトランジスタ  $T_{r1}$  がオンしており、発光素子  $EL$  は、駆動トランジスタ  $T_{rd}$  によって駆動されており、発光状態にある。30

#### 【0114】

タイミング  $T_1$  で当該フィールドが開始すると、制御信号  $AZ$  及び  $WS_3$  がローレベルからハイレベルに切り替わる。これにより、駆動トランジスタ  $T_{rd}$  の閾電圧  $V_{th}$  を検出する準備状態に入る。続いてタイミング  $T_2$  で制御信号  $DS$  がハイレベルからローレベルに切り替わり、発光素子  $EL$  が発光状態から非発光状態になると共に、駆動トランジスタ  $T_{rd}$  の閾電圧  $V_{th}$  の検出が行われる。続いてタイミング  $T_3$  で、制御信号  $AZ$  及び  $WS_3$  がローレベルになり、検出された閾電圧が保持、固定される。この保持、固定された閾電圧  $V_{th}$  は、後の発光段階で、駆動トランジスタ  $T_{rd}$  の閾電圧のばらつきのキャンセルもしくは補正に用いられる。そこで、タイミング  $T_2$  ~ タイミング  $T_3$  までの期間  $T_2$  ~  $T_3$  を、閾電圧補正期間と呼ぶ場合がある。40

#### 【0115】

タイミング  $T_4$  に進むと、制御信号  $WS_1$  及び  $WS_2$  がハイレベルに切り替わる。この時、信号線  $SL$  には信号電流  $I_{sig}$  が流れている。この信号電流  $I_{sig}$  がサンプリングされて、画素回路2 に書き込まれる。続いてタイミング  $T_5$  で、制御信号  $WS_2$  がローレベルに切り替わると、信号電流  $I_{sig}$  の書き込みが終了する。タイミング  $T_4$  ~ タイミング  $T_5$  まで、信号電流  $I_{sig}$  がサンプリングされる期間を、信号電流書き込み期間と呼ぶ場合がある。50

#### 【0116】

続いてタイミング  $T_5$  の後、信号線  $SL$  に流れる電流が信号電流  $I_{sig}$  から基準電流  $I_{ref}$  に切り替わると、この基準電流  $I_{ref}$  のサンプリングが行われる。タイミング  $T_6$  で制御信号  $WS_1$  がローレベルに戻ると、基準電流  $I_{ref}$  の書き込みが終了する。タイミング 50

T 5 ~ タイミング T 6までの期間 T 5 - T 6は、基準電流書き込み期間と呼ばれる。以上の説明から明らかなように、タイミング T 4 ~ T 6まで制御信号 W S 1がハイレベルの間に、信号電流書き込みと基準電流書き込みが順次行われる。制御信号 W S 1がハイレベルの期間 T 4 - T 6は、丁度、1水平期間 (1H)となっている。当該画素回路 2に割り当てられた1水平期間 1Hで、順次、信号電流  $I_{sig}$  及び基準電流  $I_{ref}$ をサンプリングする事ができる。

【0117】

この後、タイミング T 7で、制御信号 W S 3が立ち上がり、タイミング T 8で、制御信号 W S 3が立ち下がる。この制御信号 W S 3がハイレベルにある期間 T 7 - T 8で、信号電流  $I_{sig}$  と基準電流  $I_{ref}$ の差分が求められる。この差分は、第1画素容量 C s 1と第2画素容量 C s 2のキャンセル動作によって行われる。そこで、この期間 T 7 - T 8を、容量キャンセル期間と呼ぶ場合がある。

【0118】

タイミング T 9になると、制御信号 D Sがハイレベルになると共に、制御信号 W S 2もハイレベルになる。これにより、第2画素容量 C s 2と第3画素容量 C s 3が結合されると共に、駆動電流  $I_{ds}$ が駆動トランジスタ T r d から発光素子 E Lに供給され、発光動作が行われる。

【0119】

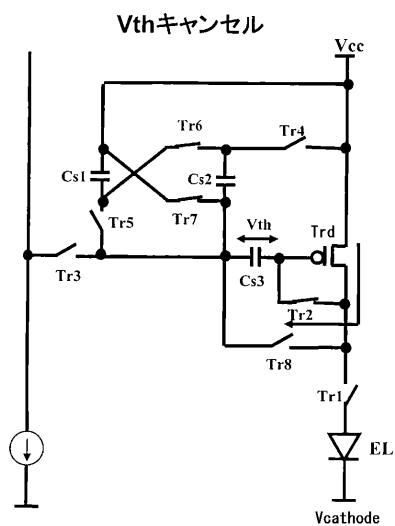

図 17は、図 16に示した閾電圧補正期間 T 2 - T 3で行われる  $V_{th}$  キャンセル動作を示す模式図である。この期間 T 2 - T 3で、スイッチングトランジスタ T r 1、T r 3、T r 4、T r 5、T r 8がオフしている一方、T r 2、T r 6及びT r 7がオンしている。この結果、第3画素容量 C s 3の一端は駆動トランジスタ T r dのゲートに接続される一方、他端はトランジスタ T r 7を介して電源  $V_{cc}$ に接続されている。電源  $V_{cc}$ から発光素子 E Lに向かって電流が流れている状態でスイッチングトランジスタ T r 1をオフすると、電流路が遮断される為、トランジスタ T r 2を介して第3画素容量 C s 3を充電していく。この充電に伴い、駆動トランジスタ T r dのゲート電位は上昇していく。丁度、ゲート電位が駆動トランジスタ T r dの閾電圧  $V_{th}$ となつたところで、駆動トランジスタ T r dがカットオフする。この時点で検出された駆動トランジスタ T r dの閾電圧  $V_{th}$ が、第3画素容量 C s 3の両端に保持される。この後、トランジスタ T r 2がオフして、第3画素容量 C s 3に保持された閾電圧  $V_{th}$ が固定される。この様にして、保持、固定された  $V_{th}$ は、後の発光動作で、駆動トランジスタ T r dの閾電圧のばらつきのキャンセルもしくは補正に用いられる。

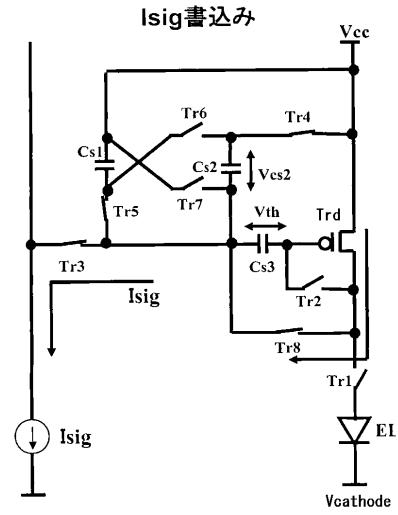

【0120】

図 18は、図 16のタイミングチャートに示した期間 T 4 - T 5で行われる信号電流書き込み動作を示す模式図である。この期間では、信号線に信号電流  $I_{sig}$  が流れている。また、トランジスタ T r 1、T r 2、T r 6、T r 7がオフしている一方、トランジスタ T r 3、T r 4、T r 5、T r 8がオンしている。この結果、信号電流  $I_{sig}$  が電源  $V_{cc}$ から駆動トランジスタ T r d、スイッチングトランジスタ T r 8、スイッチングトランジスタ T r 3を通って信号線側に流れる。換言すると、信号電流  $I_{sig}$ がドレイン電流として駆動トランジスタ T r dを流れた事になる。よって、式(1)で示したトランジスタの基本特性に従い、ドレイン電流  $I_{sig}$ は以下の式(23)で表される。

【0121】

式(23)

$$I_{sig} = \frac{k\mu}{2} \left( V_{gs} - V_{th} \right)^2$$

【0122】

式(23)において、 $V_{gs}$ は駆動トランジスタ T r dのゲート - ソース間に現れるゲート電圧を表し、 $V_{th}$ は駆動トランジスタ T r dの閾電圧を表し、kは駆動トランジスタ T

10

20

30

40

50

$r_d$  のサイズファクタを表し、 $\mu$  は駆動トランジスタ  $T_{rd}$  の移動度を表している。

【0123】

ここで式(23)を  $V_{gs}$  について整理すると、以下の式(24)が得られる。

【0124】

式(24)

$$V_{gs} = \sqrt{\frac{2I_{sig}}{k\mu}} + V_{th}$$

10

【0125】

ここで、図18を参照すると、駆動トランジスタ  $T_{rd}$  のソースとゲートとの間には第2画素容量  $C_{s2}$  と第3画素容量  $C_{s3}$  が直列接続されている。ここで、第2画素容量  $C_{s2}$  の両端に保持された電圧を  $V_{cs2}$  とし、第3画素容量  $C_{s3}$  に保持された電圧を  $V_{cs3}$  とすると、ゲート電圧  $V_{gs} = V_{cs2} + V_{cs3}$  で与えられる。ここで、先の  $V_{th}$  キャンセル動作により、 $V_{cs3}$  は  $V_{th}$  に設定されている。したがって、 $V_{gs} = V_{cs2} + V_{th}$  となる。この式の  $V_{gs}$  に式(24)で与えられた  $V_{gs}$  を代入してまとめると、第2画素容量  $C_{s2}$  に保持された電圧  $V_{cs2}$  が、以下の式(25)により与えられる

20

【0126】

式(25)

$$V_{cs2} = \sqrt{\frac{2I_{sig}}{k\mu}}$$

【0127】

式(25)から明らかなように、第2画素容量  $C_{s2}$  に保持された電圧  $V_{cs2}$  は、信号電流  $I_{sig}$  の平方根に比例している。換言すると、期間  $T4 - T5$  の信号電流書き込み動作により、第2画素容量  $C_{s2}$  に信号電流  $I_{sig}$  に対応した電圧  $V_{cs2}$  がサンプリング保持された事になる。

30

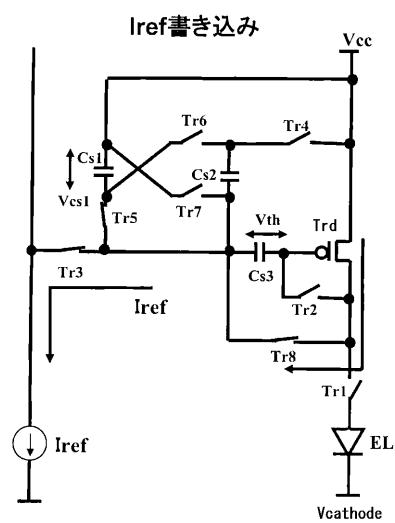

【0128】

図19は、図16に示した期間  $T5 - T6$  で行われる基準電流書き込み動作を示す模式図である。図18に示した信号電流書き込み動作から本図の基準電流の書き込み動作に進むと、走査線  $WS2$  がローレベルになる結果、トランジスタ  $T_{r4}$  がオフする。その他のスイッチングトランジスタの状態は、そのまま維持されている。したがって、図18と図19を比較すれば明らかなように、第2画素容量  $C_{s2}$  が第1画素容量  $C_{s1}$  に切り替わった関係となっている。より具体的には、図18の信号電流書き込み動作では、駆動トランジスタ  $T_{rd}$  のソース / ゲート間に第2画素容量  $C_{s2}$  及び第3画素容量  $C_{s3}$  が直列に接続されていたのに対し、本図の基準電流書き込み動作では、駆動トランジスタ  $T_{rd}$  のソースとゲートとの間に第1画素容量  $C_{s1}$  と第3画素容量  $C_{s3}$  が直列に接続されている。すなわち、回路動作としては、単に、第2画素容量  $C_{s2}$  が第1画素容量  $C_{s1}$  に入れ代わっているに過ぎない。このとき、信号線には、先の信号電流  $I_{sig}$  に代わって、基準電流  $I_{ref}$  が流れている。より具体的には、基準電流  $I_{ref}$  は電源  $V_{cc}$  から駆動トランジスタ  $T_{rd}$  を通り、さらに、スイッチングトランジスタ  $T_{r8}$  及び  $T_{r3}$  を介して信号線側に流れる。このとき、駆動トランジスタ  $T_{rd}$  のソースとゲートとの間に生じるゲート電圧  $V_{gs}$  の一部が、第1画素容量  $C_{s1}$  に保持される。この電圧を  $V_{cs1}$  とすると、式(25)の場合と全く同様にして、以下の式(26)のように表される。

40

【0129】

50

式 ( 2 6 )

$$V_{cs1} = \sqrt{\frac{2I_{ref}}{k\mu}}$$

【 0 1 3 0 】

ここで式 ( 2 5 ) と式 ( 2 6 ) を比較すれば明らかなように、式の左辺が  $V_{cs2}$  から  $V_{cs1}$  に置き換わる一方、式の右辺は信号電流  $I_{sig}$  から基準電流  $I_{ref}$  に置き換わっている。式 ( 2 6 ) から明らかなように、第 1 画素容量  $C_{s1}$  に保持された電圧  $V_{cs1}$  は、基準電流  $I_{ref}$  の平方根に対応している。換言すると、この基準電流書き込み動作で、第 1 画素容量  $C_{s1}$  に、基準電流  $I_{ref}$  に対応した電圧がサンプリングされた事になる。

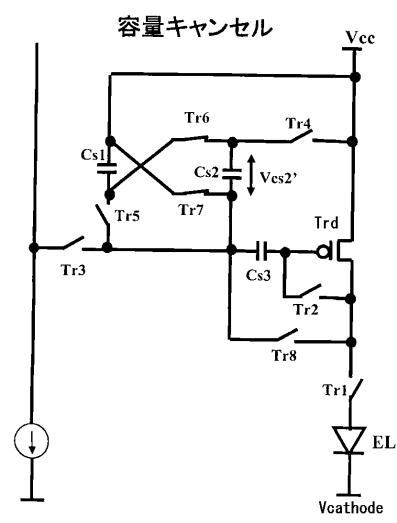

【 0 1 3 1 】

図 2 0 は、図 1 6 に示したタイミングチャートの期間 T 7 - T 8 で行われる容量キャンセル動作を示す模式図である。この動作では、スイッチングトランジスタ T r 3, T r 5 及び T r 8 がオフする一方、T r 6 及び T r 7 がオンする。これにより、第 1 画素容量  $C_{s1}$  のマイナス側端子と第 2 画素容量  $C_{s2}$  のプラス側端子が接続され、且つ、第 1 画素容量  $C_{s1}$  のプラス側端子と第 2 画素容量  $C_{s2}$  のマイナス側端子が接続される。これにより、第 1 画素容量  $C_{s1}$  と第 2 画素容量  $C_{s2}$  の容量キャンセルが、電圧  $V_{cs1}$  と電圧  $V_{cs2}$  との間で行われる。つまり、第 1 画素容量  $C_{s1}$  に保持された電圧  $V_{cs1}$  と第 2 画素容量  $C_{s2}$  に保持された電圧  $V_{cs2}$  の差分が得られ、且つ、この差分が、第 2 画素容量  $C_{s2}$  の両端に保持される。ここで、第 1 画素容量  $C_{s1}$  と第 2 画素容量  $C_{s2}$  の容量値が等しい場合、容量キャンセル後の第 2 画素容量  $C_{s2}$  に保持された電位  $V_{cs2}'$  は以下の式 ( 2 7 ) で与えられる。

【 0 1 3 2 】

式 ( 2 7 )

$$V_{cs2}' = \frac{V_{cs2} - V_{cs1}}{2} = \frac{\sqrt{I_{sig}} - \sqrt{I_{ref}}}{\sqrt{2k\mu}}$$

10

20

30

【 0 1 3 3 】

式 ( 2 7 ) から明らかなように、 $V_{cs2}'$  は信号電流  $I_{sig}$  と基準電流  $I_{ref}$  との差分に応じた値となっている。正確には、信号電流  $I_{sig}$  の平方根と基準電流  $I_{ref}$  の平方根との差に応じた電圧が、第 2 画素容量  $C_{s2}$  に  $V_{cs2}'$  として保持される事になる。

【 0 1 3 4 】

図 2 1 は、図 1 6 に示したタイミング T 9 以降に行われる発光期間における容量結合及び発光動作を示す模式図である。タイミング T 9 に至ると、制御信号 D S と W S 2 がハイレベルになる一方、他の制御信号は全てローレベルである。したがって、スイッチングトランジスタ T r 4 及び T r 1 がオン状態になる一方、残りのスイッチングトランジスタ T r 3, T r 5, T r 6, T r 7, T r 2, T r 8 はオフ状態である。T r 4 がオンになる為、駆動トランジスタ T r d のソースとゲートとの間で第 2 画素容量  $C_{s2}$  と第 3 画素容量  $C_{s3}$  が結合される。このとき、駆動トランジスタ T r d のゲート容量  $C_g$  が充分小さいので、第 2 画素容量  $C_{s2}$  と第 3 画素容量  $C_{s3}$  は、互いの電荷を保持した状態で結合される。つまり、発光時における駆動トランジスタ T r d のゲート電圧  $V_{gs}$  は、 $V_{gs} = V_{cs3} + V_{cs2}' = V_{th} + V_{cs2}'$  となる。

【 0 1 3 5 】

この様にして得られた  $V_{gs}$  を、先の式 ( 1 ) で示したトランジスタの基本特性式に入れると、以下の式 ( 2 8 ) に示すような駆動電流  $I_{ds}$  が得られる。

【 0 1 3 6 】

40

50

式(28)

$$\begin{aligned}

I_{ds} &= \frac{1}{2} k \mu (V_{gs} - V_{th})^2 = \frac{1}{2} k \mu (V_{cs2}')^2 \\

&= \frac{1}{2} k \mu \left( \frac{\sqrt{I_{sig}} - \sqrt{I_{ref}}}{\sqrt{2k\mu}} \right)^2 \\

&= \frac{1}{4} (\sqrt{I_{sig}} - \sqrt{I_{ref}})^2

\end{aligned}$$

10

**【0137】**

式(28)の一段目で、 $V_{gs}$ に $V_{th} + V_{cs2}'$ を代入している。これにより、 $V_{th}$ がキャンセルされ、駆動電流 $I_{ds}$ は $V_{cs2}'$ の2乗に比例した形となる。さらに、式(28)の二段目に示すように、 $V_{cs2}'$ に式(27)を代入する。このあと、分母に現れる移動度 $\mu$ と係数部の移動度 $\mu$ がキャンセルされ、最終的に、式(28)の三段目で表す形となる。この式から明らかのように、信号電流 $I_{sig}$ と基準電流 $I_{ref}$ の電流差分値により駆動電流(発光電流) $I_{ds}$ が決定され、駆動トランジスタの閾電圧 $V_{th}$ や移動度 $\mu$ のばらつきによらない、ユニフォーミティの高い画質を得る事ができる。さらに、本発明の画素回路では、黒表示時、 $I_{sig} = I_{ref}$ に設定する。式(28)から明らかのように、 $I_{sig} = I_{ref}$ にすると、 $I_{ds} = 0$ となり、発光電流はなくなる。この結果、完全な黒表示となる。一方、黒表示でも、基準電流 $I_{ref}$ の絶対値は充分に高いレベルに設定する事ができ、1水平期間(1H)内で、充分に黒信号を書き込む事ができる事になる。これにより、黒浮きや縦クロストークなどの発生を抑制でき、完全に沈んだ黒を表現でき高いコントラスト特性を得る事ができる。

20

**【0138】**

以上に説明したように、図15に示した本発明の実施形態にかかる画素回路は、信号電流 $I_{sig}$ が流れる信号線SLと、制御信号を供給する走査線WS1, WS2, WS3, AZ, DSとが交差する部分に配されている。この画素回路2は、発光素子ELと、発光素子ELに駆動電流 $I_{ds}$ を供給する駆動トランジスタTrdと、制御信号WS1, WS2, WS3, AZ, DSに応じて動作し、信号電流 $I_{sig}$ に基づいて駆動トランジスタTrdの駆動電流 $I_{ds}$ を制御する制御部とで構成されている。この制御部は、第1サンプリング手段と第2サンプリング手段と差分手段とを含んでいる。第1サンプリング手段は、トランジスタTr3, Tr4, Tr8と第2画素容量Cs2とで構成されており、信号線SLに流れる信号電流 $I_{sig}$ をサンプリングする。第2サンプリング手段はトランジスタTr3, Tr5, Tr8と第1画素容量Cs1とで構成され、信号電流 $I_{sig}$ に前後して信号線SLに流れる所定の基準電流 $I_{ref}$ をサンプリングする。差分手段は、トランジスタTr6, Tr7と一対の画素容量(第1画素容量Cs1と第2画素容量Cs2)で構成されており、サンプリングされた基準電流 $I_{ref}$ に対するサンプリングされた信号電流 $I_{sig}$ の差分に応じた制御電圧 $V_{cs2}'$ を生成する。駆動トランジスタTrdは、この制御電圧をゲートGに受けて、ソース/ドレイン間に流れる駆動電流 $I_{ds}$ を発光素子ELに供給して発光を行わせる。

30

**【0139】**

第1サンプリング手段及び第2サンプリング手段が各々サンプリングする信号電流 $I_{sig}$ 及び基準電流 $I_{ref}$ は、両者の相対的な差分が小さいとき、発光素子ELの発光量が小さくなり、差分が大きいとき、発光量が大きくなる一方、相対的な差分が小さいときでも、信号電流 $I_{sig}$ 及び基準電流 $I_{ref}$ の絶対的なレベルは、サンプリングを可能とするように大きく設定されている。

40

**【0140】**

50

画素回路 2 の制御部は、上述した第 1 サンプリング手段及び第 2 サンプリング手段と差分手段に加え、補正手段を有している。この補正手段は、トランジスタ  $T_{r1}, T_{r2}, T_{r7}$  と第 3 画素容量  $C_{s3}$  とで構成されており、駆動トランジスタ  $T_{rd}$  の閾電圧  $V_{th}$  を検出して、これを、前述した制御電圧  $V_{cs2}$  に加える事ができる様にしている。これにより、閾電圧  $V_{th}$  の影響を駆動電流  $I_{ds}$  からキャンセルする事ができる。

【図面の簡単な説明】

【0141】

【図 1】本発明にかかる画素回路及び表示装置の実施形態を示す模式的な全体ブロック図である。

【図 2】図 1 に示した表示装置に含まれる画素回路の構成を示す回路図である。 10

【図 3】図 2 に示した画素回路の動作説明に供する模式図である。

【図 4】同じく動作説明に供するタイミングチャートである。

【図 5】同じく動作説明に供する模式図である。

【図 6】同じく動作説明に供する模式図である。

【図 7】同じく動作説明に供する模式図である。

【図 8】同じく動作説明に供する模式図である。

【図 9】駆動トランジスタの電流電圧特性を示すグラフである。

【図 10】本発明にかかる画素回路及び表示装置の他の実施形態を示す回路図である。

【図 11】図 10 に示した画素回路の動作説明に供するタイミングチャートである。 20

【図 12】同じく動作説明に供する模式図である。

【図 13】同じく動作説明に供する模式図である。

【図 14】同じく動作説明に供する模式図である。

【図 15】本発明にかかる画素回路の別の実施形態を示す回路図である。

【図 16】図 15 に示した画素回路の動作説明に供するタイミングチャートである。

【図 17】同じく動作説明に供する模式図である。

【図 18】同じく動作説明に供する模式図である。

【図 19】同じく動作説明に供する模式図である。

【図 20】同じく動作説明に供する模式図である。

【図 21】同じく動作説明に供する模式図である。

【図 22】従来の表示装置の一例を示す全体ブロック図である。 30

【図 23】図 22 に示した従来の表示装置に含まれる画素回路の構成を示す回路図である。

【図 24】図 22 に示した従来の表示装置の画面の一例を示す模式図である。

【符号の説明】

【0142】

1 . . . 画素アレイ、 2 . . . 画素回路、 3 . . . 電流ドライバー、 4 . . . ライトスキャナ、 5 . . . ドライブスキャナ、 7 . . . 補正用スキャナ、 41 . . . 第一ライトスキャナ、 42 . . . 第二ライトスキャナ、 43 . . . 第三ライトスキャナ、  $T_{rd}$  . . . 駆動トランジスタ、  $T_{r1}$  . . . スイッチングトランジスタ、  $T_{r2}$  . . . スイッチングトランジスタ、  $T_{r3}$  . . . スイッチングトランジスタ、  $T_{r4}$  . . . スイッチングトランジスタ、  $T_{r5}$  . . . スイッチングトランジスタ、  $T_{r6}$  . . . スイッチングトランジスタ、  $T_{r7}$  . . . スイッチングトランジスタ、  $T_{r8}$  . . . スイッチングトランジスタ、  $E_L$  . . . 発光素子、  $C_{s1}$  . . . 第 1 画素容量、  $C_{s2}$  . . . 第 2 画素容量、  $C_{s3}$  . . . 第 3 画素容量 40

【図1】

【図2】

【図3】

【図4】

【図5】

Iref書き込み

【図6】

Isig書き込み&amp;電流差分保持

【図7】

Vthキャンセル

【図8】

発光

【図9】

【図10】

【図11】

【図12】

【図14】

【図13】

【図15】

【図16】

【図17】

【 図 1 8 】

【 19 】

【 図 2 0 】

【図 2 1】

【図 2 2】

【図 2 3】

【図 2 4】

---

フロントページの続き

(51)Int.Cl.

F I

|        |       |         |

|--------|-------|---------|

| G 09 G | 3/20  | 6 2 1 A |

| G 09 G | 3/20  | 6 2 1 F |

| G 09 G | 3/20  | 6 2 3 L |

| G 09 G | 3/20  | 6 2 4 B |

| G 09 G | 3/20  | 6 4 1 D |

| G 09 G | 3/20  | 6 4 1 P |

| H 05 B | 33/14 | A       |

審査官 奈良田 新一

(56)参考文献 特開2003-150116 (JP, A)

特開2004-341023 (JP, A)

特開2004-354883 (JP, A)

特開2005-157347 (JP, A)

特開2004-093777 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 2 0 , 3 / 3 0 - 3 / 3 2

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP4747565B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2011-08-17 |

| 申请号            | JP2004347283                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2004-11-30 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 山下淳一<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 山下 淳一<br>内野 勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | G09G3/3241 G09G3/3233 G09G3/325 G09G2300/0417 G09G2300/0819 G09G2300/0852 G09G2300/0861 G09G2310/0262 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/30.K G09G3/30.J G09G3/20.611.D G09G3/20.612.E G09G3/20.612.U G09G3/20.621.A G09G3/20.621.F G09G3/20.623.L G09G3/20.624.B G09G3/20.641.D G09G3/20.641.P H05B33/14.A G09G3/20.611.H G09G3/20.642.A G09G3/3241 G09G3/325 G09G3/3266 G09G3/3275 G09G3/3283                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH02 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD10 5C080/EE28 5C080/EE29 5C080/EE30 5C080/FF11 5C080/JJ01 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C380/AA01 5C380/AB06 5C380/AB24 5C380/AB31 5C380/AB34 5C380/AC04 5C380/BA12 5C380/BA19 5C380/BA20 5C380/BA38 5C380/BA39 5C380/BB02 5C380/BB08 5C380/BB23 5C380/BC03 5C380/BC14 5C380/CA13 5C380/CA29 5C380/CA53 5C380/CA54 5C380/CB01 5C380/CB16 5C380/CB17 5C380/CB26 5C380/CC11 5C380/CC13 5C380/CC14 5C380/CC15 5C380/CC18 5C380/CC19 5C380/CC26 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC61 5C380/CC64 5C380/CC66 5C380/CC72 5C380/CD014 5C380/CD026 5C380/CD038 5C380/CE04 5C380/CE20 5C380/DA02 5C380/DA06 5C380/DA47 5C380/HA03 5C380/HA06 5C380/HA13 |         |            |

| 代理人(译)         | 山本隆久<br>吉井正明<br>森浩一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | JP2006154521A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

**摘要(译)**

还提供了一种能够充分写入黑电平的弱信号电流的像素电路。像素电路2的第一采样装置包括晶体管Tr1，Tr3，Tr4和像素电容器Cs2，并对流过信号线SL的信号电流Isig进行采样。第二采样装置包括晶体管Tr1，Tr2，Tr3，Tr4和像素电容器Cs1，并对在信号电流Isig之前和之后流过信号线SL的预定参考电流Iref进行采样。差分装置包括晶体管Tr1，Tr3，Tr4和一对像素电容Cs1，Cs2，并根据采样信号电流Isig和参考电流Iref之间的差值产生控制电压。驱动晶体管Trd接收栅极G处的控制电压，并将在源极S和漏极D之间流动的驱动电流Ids提供给发光元件EL。.The

$$I_{\rm sig} = \frac{k\mu}{2} \bigg( V_{\rm gs} - V_{\rm th} \bigg)^2$$