(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4725577号

(P4725577)

(45) 発行日 平成23年7月13日(2011.7.13)

(24) 登録日 平成23年4月22日(2011.4.22)

(51) Int.CI.

F 1

|                   |                  |            |   |

|-------------------|------------------|------------|---|

| <b>H01L 51/50</b> | <b>(2006.01)</b> | H05B 33/22 | C |

| <b>H05B 33/10</b> | <b>(2006.01)</b> | H05B 33/10 |   |

| <b>H05B 33/12</b> | <b>(2006.01)</b> | H05B 33/12 | B |

|                   |                  | H05B 33/14 | A |

|                   |                  | H05B 33/22 | A |

請求項の数 7 (全 32 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2007-340226 (P2007-340226)  |

| (22) 出願日  | 平成19年12月28日 (2007.12.28)      |

| (65) 公開番号 | 特開2009-164236 (P2009-164236A) |

| (43) 公開日  | 平成21年7月23日 (2009.7.23)        |

| 審査請求日     | 平成21年6月17日 (2009.6.17)        |

前置審査

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 000001443<br>カシオ計算機株式会社<br>東京都渋谷区本町1丁目6番2号           |

| (72) 発明者  | 木津 貴志<br>東京都八王子市石川町2951番地の5<br>カシオ計算機株式会社 八王子技術センター内 |

| (72) 発明者  | 田野 朋子<br>東京都八王子市石川町2951番地の5<br>カシオ計算機株式会社 八王子技術センター内 |

| 審査官       | 東松 修太郎                                               |

最終頁に続く

(54) 【発明の名称】表示装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

表示パネルの基板上に設けられた互いに直交する複数の行及び複数の列に沿って複数の表示画素が配列され、複数の発光色を発光してカラー表示を行う表示装置の製造方法であつて、

前記列毎に異なる発光色の前記発光素子を有する前記各表示画素が配列され、同じ発光色の発光素子を有する前記表示画素が、前記基板上の前記複数の列における、1又は複数の列を隔てて離間した列群の各列に、列方向に沿って配列され、

前記発光素子は、少なくとも、第1の電極と、前記第1の電極に対向して設けられた第2の電極と、前記第1の電極と前記第2の電極との間に設けられた担体輸送層を有する発光機能層と、を具備し、

前記表示パネルの前記同じ発光色の発光素子に対応する前記列群の前記発光素子が形成される領域に対して、当該発光色に対応した膜厚の前記担体輸送層を形成する担体輸送性材料溶液を塗布する塗布工程を、前記各発光色の発光素子に対応する前記各列群に対して順次実行し、前記各発光色の発光素子に応じて異なる膜厚を有する前記発光機能層を形成する工程を含み、

前記担体輸送性材料溶液が塗布された所定の列と、前記所定の列への前記担体輸送性材料溶液の塗布後に引き続き塗布処理が実行される列と、が互いに隣接せず、かつ、前記担体輸送性材料溶液が塗布された所定の列に隣接する列への前記担体輸送性材料溶液の塗布時には、前記所定の列に前記担体輸送性材料溶液が堆積されていることを特徴とする表示

装置の製造方法。

**【請求項 2】**

前記各発光色の発光素子を有する前記各表示画素は、前記基板上の行方向に沿って一定の周期で配列され、前記同じ発光色の発光素子を有する前記各表示画素は、前記複数の列における一定の数の列を隔てた列群の各列に配列され、

前記塗布工程は、前記同じ発光色の発光素子に対応する前記列群の各列に、前記担体輸送性材料溶液を順次塗布することを特徴とする請求項1記載の表示装置の製造方法。

**【請求項 3】**

前記担体輸送層は、正孔輸送性又は電子輸送性の層であることを特徴とする請求項1又は2記載の表示装置の製造方法。

10

**【請求項 4】**

前記担体輸送層を形成する工程は、第1の発光色の発光素子を有する前記表示画素が配列される第1の列群の各列に対して、該第1の発光色に対応した前記発光材料溶液を塗布する前記塗布工程が終了した後に、前記第1の発光色と異なる第2の発光色の発光素子を有する前記表示画素が配列される、前記第1の列群と異なる第2の列群の各列に対して、該第2の発光色に対応した前記発光材料溶液を塗布する前記塗布工程を実行する工程を、前記複数の発光色の全てに対して繰り返して実行することを特徴とする請求項1乃至3のいずれかに記載の表示装置の製造方法。

**【請求項 5】**

前記担体輸送層を形成する工程は、前記各列の前記発光素子が形成される領域に対して塗布する前記担体輸送性材料溶液の流量を前記各発光色に応じて異なる値に制御することにより、前記各発光色に応じて前記担体輸送層の膜厚を異なる値に設定することを特徴とする請求項1乃至4のいずれか記載の表示装置の製造方法。

20

**【請求項 6】**

前記担体輸送層を形成する工程は、前記各列の前記発光素子が形成される領域に対して前記担体輸送性材料溶液を塗布する際の塗布速度を前記各発光色に応じて異なる値に制御することにより、前記各発光色に応じて前記担体輸送層の膜厚を異なる値に設定することを特徴とする請求項1乃至4のいずれかに記載の表示装置の製造方法。

**【請求項 7】**

前記担体輸送層を形成する工程は、前記各列の前記発光素子が形成される領域に対して前記担体輸送性材料溶液を塗布する際の塗布回数を前記各発光色に応じて異なる値に制御することにより、前記各発光色に応じて前記担体輸送層の膜厚を異なる値に設定することを特徴とする請求項1乃至4のいずれかに記載の表示装置の製造方法。

30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、表示装置及びその製造方法に関し、特に、有機エレクトロルミネッセンス素子等の発光素子を有する表示画素を備えた表示装置の製造方法に関する。

**【背景技術】**

**【0002】**

40

近年、携帯電話や携帯音楽プレーヤ等の電子機器の表示デバイスとして、有機エレクトロルミネッセンス素子（以下、「有機EL素子」と略記する）を2次元配列した表示パネル（有機EL表示パネル）を適用したものが知られている。特に、アクティブマトリクス駆動方式を適用した有機EL表示パネルにおいては、広く普及している液晶表示装置に比較して、表示応答速度が速く、視野角依存性も小さいという優れた表示特性を有しているとともに、液晶表示装置のようにバックライトや導光板を必要としないという装置構成上の特徴を有している。そのため、今後様々な電子機器への適用が期待されている。

**【0003】**

有機EL素子は、周知のように、概略、ガラス基板等の基板の一面側に、アノード（陽極）電極と、有機EL層（発光機能層）と、カソード（陰極）電極と、を順次積層した素

50

子構造を有し、有機EL層に発光しきい値を越えるようにアノード電極に正電圧、カソード電極に負電圧を印加することにより、有機EL層内で注入されたホールと電子が再結合する際に生じるエネルギーに基づいて光（励起光）が放射されるものである。

#### 【0004】

ここで、基板の一面側に有機EL素子（発光素子）が形成された表示パネルにおいては、上記有機EL層を介して対向して形成された一対の電極（アノード電極、カソード電極）のいずれか一方を、光透過性を有する電極材料により形成し、他方を、光反射性を有する電極材料により形成することにより、基板の一面側に光を放射するトップエミッション型と、基板の他面側に光を放射するボトムエミッション型の発光構造が知られている。例えば特許文献1等に記載されているように、トップエミッション型の表示パネルにおいては、一面側に設けられた発光素子において発光した光が基板を透過することなく反射して一面側に放射され、一方、ボトムエミッション型の表示パネルにおいては、発光素子において発光した光が基板を透過して他面側に放射される発光構造を有している。10

#### 【0005】

【特許文献1】特開2005-222759号公報（第3頁、第5頁～第7頁、図1、図4）

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0006】

しかしながら、上述したような発光構造を有する表示パネルにおいては、発光層で発光した光が光透過性を有する電極を介して直接視野側（基板の一面側又は他面側）に放射されるとともに、光反射特性を有する電極で反射した光が発光層及び光透過性を有する電極を介して上記視野側に放射されることにより、放射光に膜厚分の光路差が生じ、干渉効果に起因する色度ずれや発光輝度（発光強度）のばらつきを招き、画像のにじみやぼけ等の表示特性の劣化を生じるという問題を有していた。特に、発光素子として、有機EL層を高分子系の有機材料を用いて形成した高分子系の有機EL素子を適用した場合には、上述したような特性の劣化が顕著になるという問題を有していた。20

#### 【0007】

そこで、本発明は、上述した問題点に鑑み、色度ずれや発光輝度（発光強度）のばらつきを抑制して、画像のにじみやぼけのない表示特性に優れた表示装置の製造方法を提供することを目的とする。30

#### 【課題を解決するための手段】

#### 【0010】

請求項1記載の発明は、表示パネルの基板上に設けられた互いに直交する複数の行及び複数の列に沿って複数の表示画素が配列され、複数の発光色を発光してカラー表示を行う表示装置の製造方法であって、前記列毎に異なる発光色の前記発光素子を有する前記各表示画素が配列され、同じ発光色の発光素子を有する前記表示画素が、前記基板上の前記複数の列における、1又は複数の列を隔てて離間した列群の各列に、列方向に沿って配列され、前記発光素子は、少なくとも、第1の電極と、前記第1の電極に対向して設けられた第2の電極と、前記第1の電極と前記第2の電極との間に設けられた担体輸送層を有する発光機能層と、を具備し、前記表示パネルの前記同じ発光色の発光素子に対応する前記列群の前記発光素子が形成される領域に対して、当該発光色に対応した膜厚の前記担体輸送層を形成する担体輸送性材料溶液を塗布する塗布工程を、前記各発光色の発光素子に対応する前記各列群に対して順次実行し、前記各発光色の発光素子に応じて異なる膜厚を有する前記発光機能層を形成する工程を含み、前記担体輸送性材料溶液が塗布された所定の列と、前記所定の列への前記担体輸送性材料溶液の塗布後に引き続き塗布処理が実行される列と、が互いに隣接せず、かつ、前記担体輸送性材料溶液が塗布された所定の列に隣接する列への前記担体輸送性材料溶液の塗布時には、前記所定の列に前記担体輸送性材料溶液が堆積されていることを特徴とする。40

請求項2記載の発明は、請求項1記載の表示装置の製造方法において、前記各発光色の

発光素子を有する前記各表示画素は、前記基板上の行方向に沿って一定の周期で配列され、前記同じ発光色の発光素子を有する前記各表示画素は、前記複数の列における一定の数の列を隔てた列群の各列に配列され、前記塗布工程は、前記同じ発光色の発光素子に対応する前記列群の各列に、前記担体輸送性材料溶液を順次塗布することを特徴とする。

請求項 3 記載の発明は、請求項 1 又は 2 記載の表示装置の製造方法において、前記担体輸送層は、正孔輸送性又は電子輸送性の層であることを特徴とする。

請求項 4 記載の発明は、請求項 1 乃至 3 のいずれかに記載の表示装置の製造方法において、前記担体輸送層を形成する工程は、第 1 の発光色の発光素子を有する前記表示画素が配列される第 1 の列群の各列に対して、該第 1 の発光色に対応した前記発光材料溶液を塗布する前記塗布工程が終了した後に、前記第 1 の発光色と異なる第 2 の発光色の発光素子を有する前記表示画素が配列される、前記第 1 の列群と異なる第 2 の列群の各列に対して、該第 2 の発光色に対応した前記発光材料溶液を塗布する前記塗布工程を実行する工程を、前記複数の発光色の全てに対して繰り返して実行することを特徴とする。10

請求項 5 記載の発明は、請求項 1 乃至 4 のいずれか記載の表示装置の製造方法において、前記担体輸送層を形成する工程は、前記各列の前記発光素子が形成される領域に対して塗布する前記担体輸送性材料溶液の流量を前記各発光色に応じて異なる値に制御することにより、前記各発光色に応じて前記担体輸送層の膜厚を異なる値に設定することを特徴とする。

請求項 6 記載の発明は、請求項 1 乃至 4 のいずれかに記載の表示装置の製造方法において、前記担体輸送層を形成する工程は、前記各列の前記発光素子が形成される領域に対して前記担体輸送性材料溶液を塗布する際の塗布速度を前記各発光色に応じて異なる値に制御することにより、前記各発光色に応じて前記担体輸送層の膜厚を異なる値に設定することを特徴とする。20

請求項 7 記載の発明は、請求項 1 乃至 4 のいずれかに記載の表示装置の製造方法において、前記担体輸送層を形成する工程は、前記各列の前記発光素子が形成される領域に対して前記担体輸送性材料溶液を塗布する際の塗布回数を前記各発光色に応じて異なる値に制御することにより、前記各発光色に応じて前記担体輸送層の膜厚を異なる値に設定することを特徴とする。

#### 【発明の効果】

#### 【0012】

本発明に係る表示装置及びその製造方法によれば、色度ずれや発光輝度（発光強度）のばらつきを抑制して、画像のにじみやぼけのない優れた表示特性を実現することができる。

#### 【発明を実施するための最良の形態】

#### 【0013】

以下、本発明に係る表示装置及びその製造方法について、実施の形態を示して詳しく説明する。

##### <表示パネル>

まず、本発明に係る表示装置に適用される表示パネル（有機 E L 表示パネル）及び表示画素について説明する。40

#### 【0014】

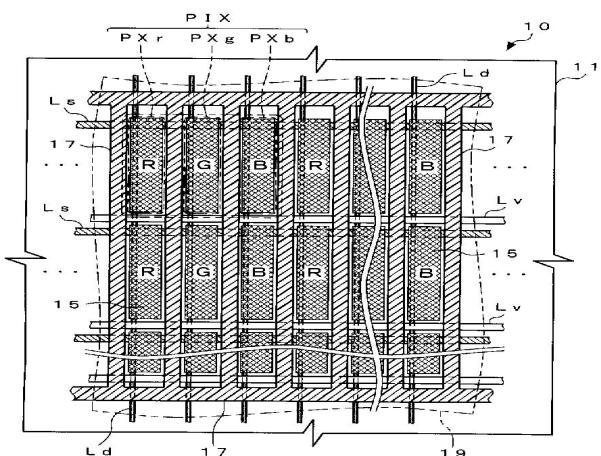

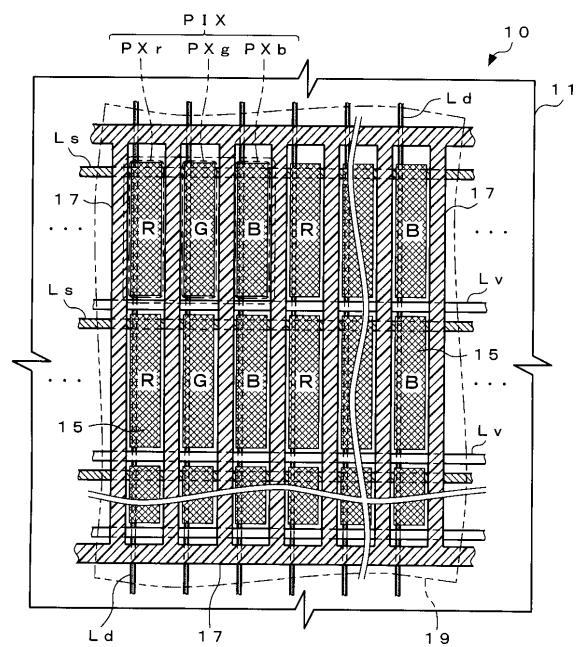

図 1 は、本発明に係る表示装置に適用される表示パネルの画素配列状態の一例を示す概略平面図であり、図 2 は、本発明に係る表示装置の表示パネルに 2 次元配列される各表示画素（発光素子及び画素駆動回路）の回路構成例を示す等価回路図である。なお、図 1 に示す平面図においては、説明の都合上、表示パネルを視野側（一面側；有機 E L 素子の形成側）から見た、各表示画素に設けられる画素電極の配置と各配線層の配設構造との関係、及び、各表示画素の形成領域を画定するバンク（隔壁）との配置関係のみを示し、各表示画素の有機 E L 素子を発光駆動するために、各表示画素に設けられる図 2 に示す画素駆動回路内のトランジスタ等の表示を省略した。また、図 1 においては、画素電極及び各配線層、バンクの配置を明瞭にするために、便宜的にハッチングを施して示した。50

## 【0015】

図1に示すように、本発明に係る表示装置（表示パネル10）は、ガラス基板等の絶縁性基板11の一面側に、行方向（図面左右方向）に配設された複数の選択ラインL<sub>s</sub>と、該選択ラインL<sub>s</sub>に並行に行方向に配設された複数の電源電圧ライン（例えばアノードライン）L<sub>v</sub>と、選択ラインL<sub>s</sub>及び電源電圧ラインL<sub>v</sub>に直交する列方向（図面上下方向）に配設された複数のデータラインL<sub>d</sub>と、を備え、選択ラインL<sub>s</sub>とデータラインL<sub>d</sub>の各交点を含む領域に各表示画素PIX（サブ画素P<sub>Xr</sub>、P<sub>Xg</sub>、P<sub>Xb</sub>）が配置されている。

## 【0016】

ここで、上記表示パネル10を備えた表示装置が、図1に示すように、カラー表示に対応している場合には、例えば赤（R）、緑（G）、青（B）の3色それぞれのサブ画素（以下、便宜的に「色画素」と記す）P<sub>Xr</sub>、P<sub>Xg</sub>、P<sub>Xb</sub>が行方向（図面左右方向）に繰り返し配列されるとともに、列方向（図面上下方向）に同一色の色画素P<sub>Xr</sub>、P<sub>Xg</sub>、P<sub>Xb</sub>が複数配列される。この場合には、行方向（図面左右方向）に隣接するRGB3色の色画素P<sub>Xr</sub>、P<sub>Xg</sub>、P<sub>Xb</sub>を一組として1つの表示画素PIXとなる。

## 【0017】

また、図1に示した表示パネル10においては、絶縁性基板11の一面側から突出し、柵状又は格子状の平面パターンを有して配設されたバンク（隔壁）17により、列方向に配列された同一色の複数の色画素P<sub>Xr</sub>、P<sub>Xg</sub>、又は、P<sub>Xb</sub>の画素形成領域（より具体的には、各色画素の有機EL素子の形成領域）が画定される。また、各色画素P<sub>Xr</sub>、P<sub>Xg</sub>、又は、P<sub>Xb</sub>の画素形成領域には、画素電極（例えばアノード電極；第1の電極）15が形成されている。

## 【0018】

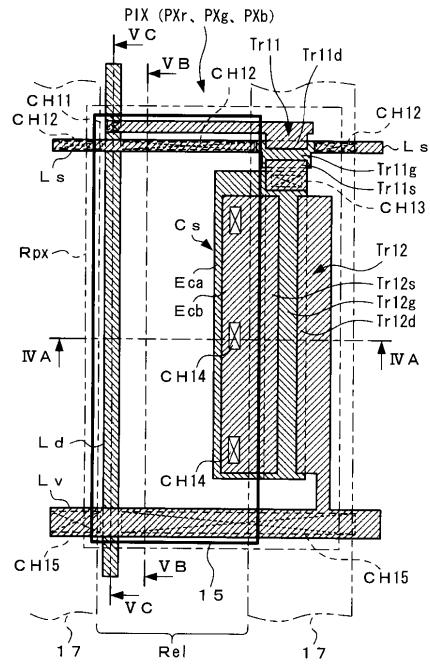

表示画素PIXの各色画素P<sub>Xr</sub>、P<sub>Xg</sub>、P<sub>Xb</sub>は、例えば図2に示すように、絶縁性基板11上に複数のトランジスタ（例えばアモルファスシリコン薄膜トランジスタ等）を有する画素駆動回路DCと、当該画素駆動回路DCにより生成される発光駆動電流が、上記画素電極15に供給されることにより発光動作する有機EL素子（発光素子）OLEDと、を備えた回路構成を有している。

## 【0019】

画素駆動回路DCは、具体的には、例えば図2に示すように、ゲート端子が選択ラインL<sub>s</sub>に、ドレイン端子がデータラインL<sub>d</sub>に、ソース端子が接点N<sub>11</sub>に各々接続されたトランジスタ（選択トランジスタ）Tr<sub>11</sub>と、ゲート端子が接点N<sub>11</sub>に、ドレイン端子が電源電圧ラインL<sub>v</sub>に、ソース端子が接点N<sub>12</sub>に各々接続されたトランジスタ（駆動トランジスタ）Tr<sub>12</sub>と、トランジスタTr<sub>12</sub>のゲート端子及びソース端子間に接続されたキャパシタCsと、を備えている。

## 【0020】

ここでは、トランジスタTr<sub>11</sub>、Tr<sub>12</sub>はいずれもnチャネル型の電界効果型トランジスタ（薄膜トランジスタ）が適用されている。トランジスタTr<sub>11</sub>、Tr<sub>12</sub>がpチャネル型であれば、ソース端子及びドレイン端子が互いに逆になる。また、キャパシタCsはトランジスタTr<sub>12</sub>のゲート-ソース間に形成される寄生容量、又は、該ゲート-ソース間に付加的に設けられた補助容量、もしくは、これらの寄生容量と補助容量からなる容量成分である。よって、トランジスタTr<sub>12</sub>がpチャネル型であれば、キャパシタCsの一方は、有機EL素子OLED側（接点N<sub>12</sub>側）ではなく、電源電圧ラインL<sub>v</sub>側に接続される。

## 【0021】

有機EL素子OLEDは、アノード端子（アノード電極となる画素電極15）が上記画素駆動回路DCの接点N<sub>12</sub>に接続され、カソード端子（カソード電極）が対向電極19と一体的に形成され、所定の基準電圧V<sub>com</sub>（例えば接地電位V<sub>gnd</sub>）に直接又は間接的に接続されている。ここで、対向電極19は、絶縁性基板11上に2次元配列された複数の表示画素PIXの画素電極15に対して共通に対向するように、单一の電極層（べた電極

10

20

30

40

50

)により形成されている。これにより、複数の表示画素 PIX に上記基準電圧 Vcom が共通に印加される。

#### 【0022】

なお、図1、図2に示した選択ライン Ls は、図示を省略した選択ドライバに接続され、所定のタイミングで表示パネル10の行方向に配列された複数の表示画素 PIX (色画素 PXr、PXg、PXb) を選択状態に設定するための選択信号 Ssel が印加される。また、データライン Ld は、図示を省略したデータドライバに接続され、上記表示画素 PIX の選択状態に同期するタイミングで表示データに応じた階調信号 Vpix が印加される。ここで、階調信号 Vpix は、有機EL素子 OLEd の発光輝度階調を設定する電圧信号である。

10

#### 【0023】

また、電源電圧ライン Lv は、例えば所定の高電位電源に直接又は間接的に接続され、各表示画素 PIX (色画素 PXr、PXg、PXb) に設けられる有機EL素子 OLEd の画素電極15に表示データに応じた発光駆動電流を流すために、有機EL素子 OLEd の対向電極19に印加される基準電圧 Vcom より電位の高い、所定の高電圧 (電源電圧 Vdd) が印加される。

#### 【0024】

すなわち、図2に示す画素駆動回路DCにおいては、各表示画素 PIX において直列に接続されたトランジスタ Tr12 と有機EL素子 OLEd の組の両端 (トランジスタ Tr12 のドレイン端子と有機EL素子 OLEd のカソード端子) にそれぞれ電源電圧 Vdd と基準電圧 Vcom を印加して、有機EL素子 OLEd に順バイアスを付与し、有機EL素子 OLEd が発光可能な状態とし、さらに、階調信号 Vpix に応じて有機EL素子 OLEd に流れる発光駆動電流の電流値を制御している。

20

#### 【0025】

そして、このような回路構成を有する表示画素 PIX における駆動制御動作は、まず、図示を省略した選択ドライバから選択ライン Ls に対して、所定の選択期間に、選択レベル (オンレベル; 例えばハイレベル) の選択信号 Ssel を印加することにより、トランジスタ Tr11 がオン動作して選択状態に設定される。このタイミングに同期して、図示を省略したデータドライバから表示データに応じた電圧値を有する階調信号 Vpix をデータライン Ld に印加するように制御する。これにより、トランジスタ Tr11 を介して、階調信号 Vpix に応じた電位が接点 N11 (すなわち、トランジスタ Tr12 のゲート端子) に印加される。

30

#### 【0026】

図2に示した回路構成を有する画素駆動回路DCにおいては、トランジスタ Tr12 のドレイン - ソース間電流 (すなわち、有機EL素子 OLEd に流れる発光駆動電流) の電流値は、ドレイン - ソース間の電位差及びゲート - ソース間の電位差によって決定される。ここで、トランジスタ Tr12 のドレイン端子 (ドレイン電極) に印加される電源電圧 Vdd と、有機EL素子 OLEd のカソード端子 (カソード電極) に印加される基準電圧 Vcom は固定値であるので、トランジスタ Tr12 のドレイン - ソース間の電位差は、電源電圧 Vdd と基準電圧 Vcom によって予め固定されている。そして、トランジスタ Tr12 のゲート - ソース間の電位差は、階調信号 Vpix の電位によって一義的に決定されるので、トランジスタ Tr12 のドレイン - ソース間に流れる電流の電流値は、階調信号 Vpix によって制御することができる。

40

#### 【0027】

このように、トランジスタ Tr12 が接点 N11 の電位に応じた導通状態 (すなわち、階調信号 Vpix に応じた導通状態) でオン動作して、高電位側の電源電圧 Vdd からトランジスタ Tr12 及び有機EL素子 OLEd を介して低電位側の基準電圧 Vcom (接地電位 Vgnd) に、所定の電流値を有する発光駆動電流が流れるので、有機EL素子 OLEd が階調信号 Vpix (すなわち表示データ) に応じた輝度階調で発光動作する。また、このとき、接点 N11 に印加された階調信号 Vpix に基づいて、トランジスタ Tr12 のゲート

50

- ソース間のキャパシタ C<sub>s</sub> に電荷が蓄積（充電）される。

#### 【 0 0 2 8 】

次いで、上記選択期間終了後の非選択期間において、選択ライン L<sub>s</sub> に非選択レベル（オフレベル；例えばローレベル）の選択信号 S<sub>sel</sub> を印加することにより、表示画素 P<sub>I</sub> X のトランジスタ T<sub>r 1 1</sub> がオフ動作して非選択状態に設定され、データライン L<sub>d</sub> と画素駆動回路 D<sub>C</sub>（具体的には接点 N<sub>1 1</sub>）とが電気的に遮断される。このとき、上記キャパシタ C<sub>s</sub> に蓄積された電荷が保持されることにより、トランジスタ T<sub>r 1 2</sub> のゲート端子に階調信号 V<sub>pix</sub> に相当する電圧が保持された（すなわち、ゲート - ソース間の電位差が保持された）状態となる。

#### 【 0 0 2 9 】

10

したがって、上記選択状態における発光動作と同様に、電源電圧 V<sub>dd</sub> からトランジスタ T<sub>r 1 2</sub> を介して、有機 E<sub>L</sub> 素子 O<sub>L</sub> E<sub>D</sub> に所定の発光駆動電流が流れ、発光動作状態が継続される。この発光動作状態は、次の階調信号 V<sub>pix</sub> が印加される（書き込まれる）まで、例えば、1 フレーム期間継続するように制御される。そして、このような駆動制御動作を、表示パネル 1 0 に 2 次元配列された全ての表示画素 P<sub>I</sub> X（各色画素 P<sub>X r</sub>、P<sub>X g</sub>、P<sub>X b</sub>）について、例えば各行ごとに順次実行することにより、所望の画像情報を表示する画像表示動作を実行することができる。

#### 【 0 0 3 0 】

20

なお、図 2 においては、表示画素 P<sub>I</sub> X に設けられる画素駆動回路 D<sub>C</sub> として、表示データに応じて各表示画素 P<sub>I</sub> X（具体的には、画素駆動回路 D<sub>C</sub> のトランジスタ T<sub>r 1 2</sub> のゲート端子；接点 N<sub>1 1</sub>）に書き込む階調信号 V<sub>pix</sub> の電圧値を調整（指定）することにより、有機 E<sub>L</sub> 素子 O<sub>L</sub> E<sub>D</sub> に流す発光駆動電流の電流値を制御して、所望の輝度階調で発光動作させる電圧指定型の階調制御方式に対応した回路構成を示したが、表示データに応じて各表示画素 P<sub>I</sub> X に供給する（書き込む）電流の電流値を調整（指定）することにより、有機 E<sub>L</sub> 素子 O<sub>L</sub> E<sub>D</sub> に流す発光駆動電流の電流値を制御して、所望の輝度階調で発光動作させる電流指定型の階調制御方式の回路構成を有するものであってもよい。

#### 【 0 0 3 1 】

また、図 2 に示した画素駆動回路 D<sub>C</sub> においては、2 個の n チャネル型のトランジスタ T<sub>r 1 1</sub>、T<sub>r 1 2</sub> を適用した回路構成を示したが、本発明に係る表示パネルはこれに限定されるものではなく、3 個以上のトランジスタを適用した他の回路構成を有するものであってもよいし、回路素子として p チャネル型のトランジスタのみを適用したもの、あるいは、n チャネル型及び p チャネル型の双方のチャネル極性を有するトランジスタが混在するものであってもよい。ここで、図 2 に示したように、画素駆動回路 D<sub>C</sub> として n チャネル型のトランジスタのみを適用した場合には、既に製造技術が確立されたアモルファスシリコン半導体製造技術を用いて、動作特性が安定したトランジスタを簡易に製造することができ、上記表示画素の発光特性のバラツキを抑制した画素駆動回路を実現することができる。

30

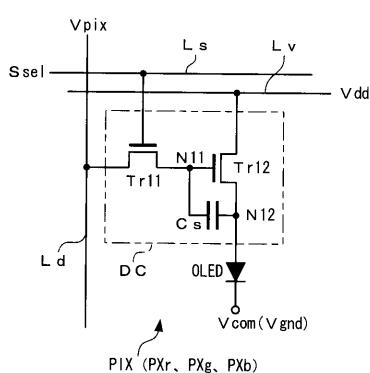

#### 【 0 0 3 2 】

< 表示画素のデバイス構造 >

次に、上述したような回路構成を有する表示画素（画素駆動回路及び有機 E<sub>L</sub> 素子）の具体的なデバイス構造（平面レイアウト及び断面構造）について説明する。ここでは、トップエミッション型の発光構造を有する有機 E<sub>L</sub> 素子を適用した場合のデバイス構造について説明する。

40

#### 【 0 0 3 3 】

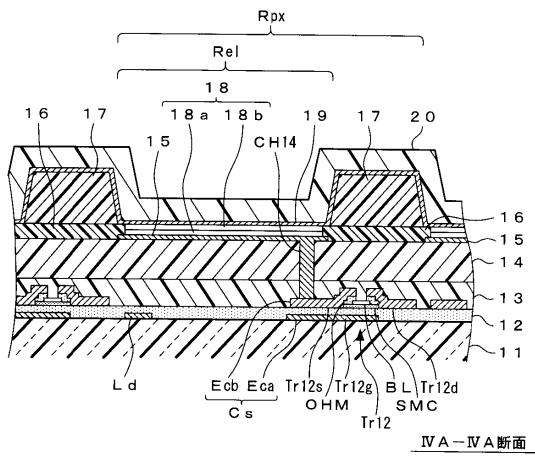

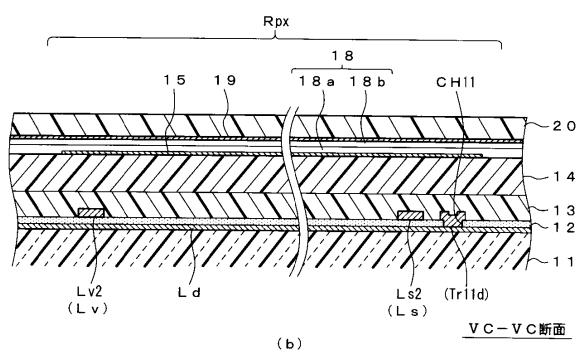

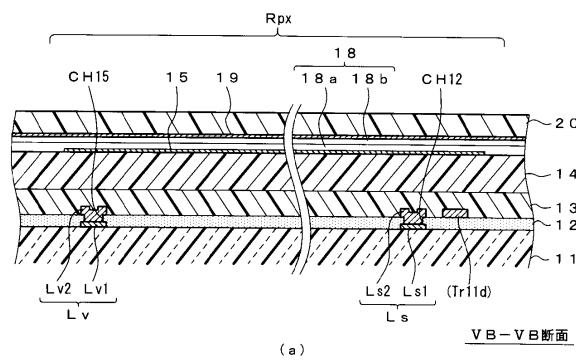

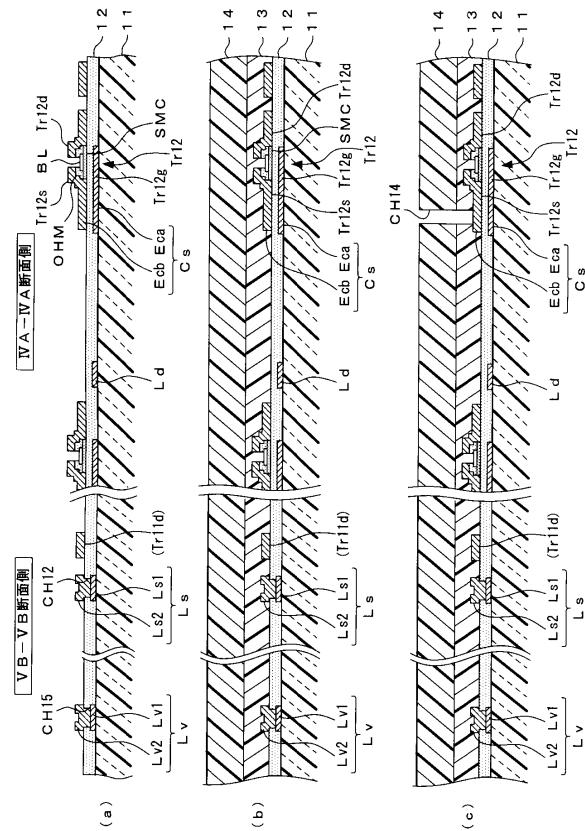

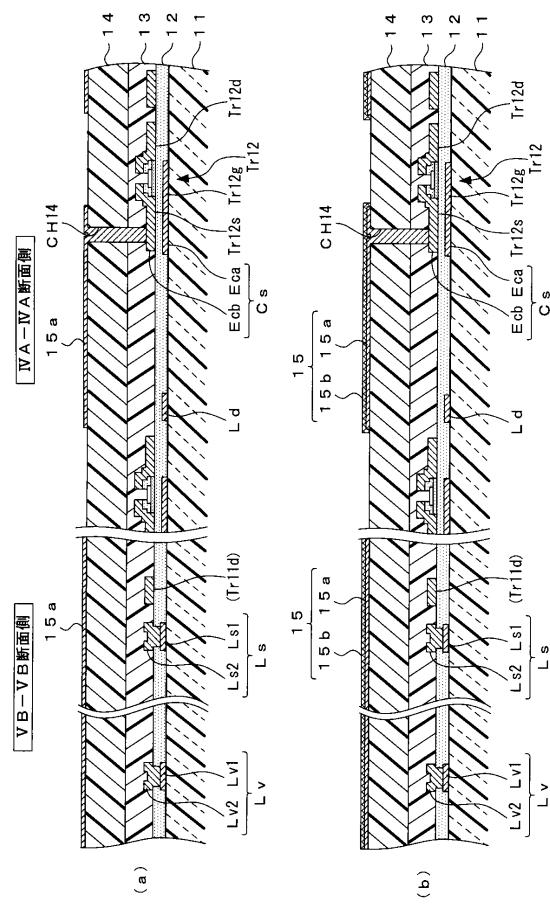

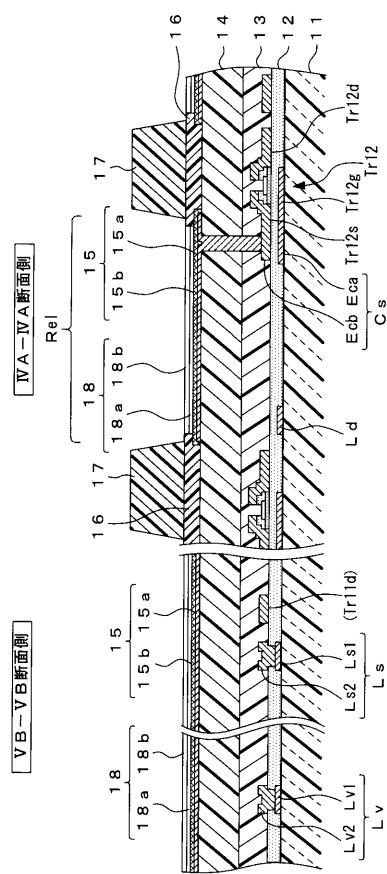

図 3 は、本発明に係る表示装置（表示パネル）に適用可能な表示画素の一例を示す平面レイアウト図である。ここでは、図 1 に示した表示画素 P<sub>I</sub> X の赤（R）、緑（G）、青（B）の各色画素 P<sub>X r</sub>、P<sub>X g</sub>、P<sub>X b</sub> のうちの、特定の一の色画素の平面レイアウトを示す。なお、図 3 においては、画素駆動回路 D<sub>C</sub> の各トランジスタ及び配線層等が形成された層を中心に示し、各配線層及び各電極の配置や平面形状を明瞭にするために、便宜的にハッチングを施して示した。また、図 4 は、図 3 に示した平面レイアウトを有する表

50

示画素におけるIVA - IVA線（本明細書においては図3中に示したローマ数字の「4」に対応する記号として便宜的に「IV」を用いる）に沿った断面を示す概略断面図である。図5(a)及び図5(b)は、それぞれ図3に示した平面レイアウトを有する表示画素におけるVB - VB線（本明細書においては図3中に示したローマ数字の「5」に対応する記号として便宜的に「V」を用いる）、VC - VC線に沿った断面を示す概略断面図である。

#### 【0034】

図2に示した表示画素（色画素）PIXは、具体的には、例えば図3に示すように、絶縁性基板11の一面側に設定された画素形成領域Rpxにおいて、図面上方及び下方の縁辺領域に行方向（図面左右方向）に延在するように選択ラインLs及び電源電圧ラインLvが各々配設されるとともに、これらのラインLs、Lvに直交するように、上記図面左方の縁辺領域に列方向（図面上下方向）に延在するようにデータラインLdが配設されている。また、上記平面レイアウトの右方の縁辺領域には右側に隣接する表示画素（色画素）にまたがって列方向（図面上下方向）に延在するようにバンク17が配設されている。

10

#### 【0035】

ここで、例えば図3～図5に示すように、データラインLdは、選択ラインLs及び電源電圧ラインLvよりも下層側（絶縁性基板11側）に設けられ、トランジスタTr11、Tr12のゲート電極Tr11g、Tr12gを形成するためのゲートメタル層をパターニングすることによって当該ゲート電極Tr11g、Tr12gと同じ工程で形成される。また、データラインLdは、その上に被覆形成されたゲート絶縁膜12に設けられたコンタクトホールCH11を介して、トランジスタTr11のドレイン電極Tr11dに接続されている。

20

#### 【0036】

選択ラインLs及び電源電圧ラインLvは、データラインLdやゲート電極Tr11g、Tr12gよりも上層側に設けられ、トランジスタTr11、Tr12のソース電極Tr11s、Tr12s、ドレイン電極Tr11d、Tr12dを形成するためのソース、ドレインメタル層をパターニングすることによって当該ソース電極Tr11s、Tr12s、ドレイン電極Tr11d、Tr12dと同じ工程で形成される。ここで、電源電圧ラインLvが延在されている線方向において、データラインLdと平面的に（平面視して）重なる領域を除いてゲート絶縁膜12にコンタクトホールCH15が設けられている。

30

#### 【0037】

選択ラインLsは、トランジスタTr11のゲート電極Tr11gの両端に位置するゲート絶縁膜12に設けられたコンタクトホールCH12を介してゲート電極Tr11gに接続されている。また、電源電圧ラインLvは、トランジスタTr12のドレイン電極Tr12dと一体的に形成されている。

#### 【0038】

ここで、選択ラインLs及び電源電圧ラインLvは、例えば図5(a)、(b)に示すように、低抵抗化を図るために、下層配線層Ls1、Lv1と上層配線層Ls2、Lv2を積層した配線構造を有しているものであってもよい。例えば下層配線層Ls1、Lv1は、トランジスタTr11、Tr12のゲート電極Tr11g、Tr12gと同層であって、かつ、当該ゲート電極Tr11g、Tr12gを形成するためのゲートメタル層をパターニングすることによって当該ゲート電極Tr11g、Tr12gと同じ工程で形成される。また、上層配線層Ls2、Lv2は、上述したように、いずれもトランジスタTr11、Tr12のソース電極Tr11s、Tr12s及びドレイン電極Tr11d、Tr12dと同層であって、かつ、当該ソース電極Tr11s、Tr12s及びドレイン電極Tr11d、Tr12dを形成するためのソース、ドレインメタル層をパターニングすることによって当該ソース電極Tr11s、Tr12s及びドレイン電極Tr11d、Tr12dと同じ工程で形成される。

40

#### 【0039】

なお、下層配線層Ls1、Lv1は、アルミニウム単体(A1)やアルミニウム・チタン(

50

A1Ti)、アルミニウム-ネオジウム-チタン(A1NdTi)等のアルミニウム合金、銅(Cu)等の配線抵抗を低減するための低抵抗金属の単層や合金層により形成するものであってもよいし、クロム(Cr)やチタン(Ti)等のマイグレーションを低減するための遷移金属層が上記低抵抗金属層の下層に設けられた積層構造を有するものであってもよい。また、上層配線層Ls2、Lv2は、クロム(Cr)やチタン(Ti)等のマイグレーションを低減するための遷移金属層と、当該遷移金属層の下層にアルミニウム単体やアルミニウム合金等の配線抵抗を低減するための低抵抗金属層が設けられた積層構造を有しているものであってもよい。

#### 【0040】

そして、画素駆動回路DCは、より具体的には、例えば図3に示すように、図2に示したトランジスタTr11が行方向に延在するように配置され、また、トランジスタTr12が列方向に沿って延在するように配置されている。ここで、各トランジスタTr11、Tr12は、周知の電界効果型の薄膜トランジスタ構造を有し、各々、例えば絶縁性基板11上に形成されたゲート電極Tr11g、Tr12gと、該ゲート電極Tr11g、Tr12g上に被覆形成されたゲート絶縁膜12を介して各ゲート電極Tr11g、Tr12gに対応する領域に形成された半導体層SMCと、該半導体層SMCのチャネルの両側部に延在するように形成されたソース電極Tr11s、Tr12s及びドレイン電極Tr11d、Tr12dと、を有する逆スタガ構造を有している。

#### 【0041】

なお、各トランジスタTr11、Tr12のソース電極Tr11s、Tr12sとドレイン電極Tr11d、Tr12dが両端部に対向して配置された半導体層SMCのチャネル上には、製造プロセスにおいて当該半導体層SMCへのエッティングダメージを防止するための酸化シリコン又は窒化シリコン等のチャネル保護層(ブロック層)BLが形成され、また、ソース電極Tr11s、Tr12s及びドレイン電極Tr11d、Tr12dが接觸する半導体層SMCのチャネルの両端部上には、当該半導体層SMCとソース電極Tr11s、Tr12s及びドレイン電極Tr11d、Tr12dとのオーミック接続を実現するための不純物層OHMが形成されている。

#### 【0042】

そして、図2に示した画素駆動回路DCの回路構成に対応するように、トランジスタTr11は、図3に示すように、ゲート電極Tr11gがゲート絶縁膜12に設けられたコンタクトホールCH12を介して選択ラインLsに接続され、同ドレイン電極Tr11dがゲート絶縁膜12に設けられたコンタクトホールCH11を介してデータラインLdに接続されている。

#### 【0043】

トランジスタTr12は、図3、図4に示すように、ゲート電極Tr12gがゲート絶縁膜12に設けられたコンタクトホールCH13を介して上記トランジスタTr11のソース電極Tr11sに接続され、同ドレイン電極Tr12dが電源電圧ラインLvと一体的に形成され、同ソース電極Tr12sが保護絶縁膜13及び平坦化膜14に設けられたコンタクトホールCH14を介して有機EL素子OLEDの画素電極15に接続されている。

#### 【0044】

また、キャパシタCsは、図3、図4に示すように、絶縁性基板11上にトランジスタTr12のゲート電極Tr12gと一体的に形成された電極Ecaと、ゲート絶縁膜12上にトランジスタTr12のソース電極Tr12sと一体的に形成された電極Ecbと、がゲート絶縁膜12を介して対向するように設けられている。また、上述したように、電極Ecb上の保護絶縁膜13及び平坦化膜14にはコンタクトホールCH14が設けられ、当該コンタクトホールCH14を介して有機EL素子OLEDの画素電極15に接続されている。

#### 【0045】

有機EL素子OLEDは、図3～図5に示すように、上記トランジスタTr11、Tr12を被覆するように形成された保護絶縁膜13及び平坦化膜14の上面に設けられるとともに、保護絶縁膜13及び平坦化膜14を貫通して設けられたコンタクトホールCH14

10

20

30

40

50

を介して、トランジスタ Tr 1 2 のソース電極 Tr 1 2 s に接続され、所定の発光駆動電流が供給される光反射特性を有する画素電極（例えばアノード電極）1 5 と、上記平坦化膜 1 4 上であって、隣接する表示画素 PIX の画素電極 1 5 との間の領域（境界領域）に形成された層間絶縁膜 1 6 、及び、該層間絶縁膜 1 6 上に連続的に突出して配設されたバンク 1 7 により画定された（バンク 1 7 に取り囲まれた領域である）EL 素子形成領域 Rel に形成された、例えば正孔輸送層 1 8 a 及び電子輸送性発光層 1 8 b を有する有機 EL 層（発光機能層）1 8 と、絶縁性基板 1 1 上に 2 次元配列された各表示画素 PIX の画素電極 1 5 に共通して対向するように設けられた光透過特性を有する单一の電極層（べた電極）からなる対向電極（例えばカソード電極）1 9 と、を順次積層することにより形成される。

10

#### 【 0 0 4 6 】

ここで、対向電極 1 9 は、各 EL 素子形成領域 Rel だけでなく、当該 EL 素子形成領域 Rel を画定するバンク 1 7 上にも延在するように設けられている。また、EL 素子形成領域 Rel の周囲は、図 3 に示した平面レイアウトの左右方向に隣接する表示画素（色画素）PIX の EL 素子形成領域 Rel との境界領域にバンク 1 7 が形成されているので、選択ライン L s 及び電源電圧ライン L v の一部、並びに、トランジスタ Tr 1 1 、Tr 1 2 は、バンク 1 7 と平面的に（平面視して）重なっている。そのため、バンク 1 7 は、当該バンク 1 7 上に形成された上記対向電極 1 9 による寄生容量の影響を緩和している。ここで、データライン L d についても、同様の目的でバンク 1 7 の下方に配置させるものであってもよい。

20

#### 【 0 0 4 7 】

また、図 3 ~ 図 5 に示したパネル構造においては、選択ライン L s 及び電源電圧ライン L v を積層配線構造として、上層配線層 L s2 、 L v2 をトランジスタ Tr 1 1 、 Tr 1 2 のソース電極 Tr 1 1 s 、 Tr 1 2 s 及びドレイン電極 Tr 1 1 d 、 Tr 1 2 d を形成するためのソース、ドレインメタル層をパターニングすることによって形成し、選択ライン L s をコンタクトホール CH12 を介してトランジスタ Tr 1 1 のゲート電極 Tr 1 1 g に接続し、電源電圧ライン L v をトランジスタ Tr 1 2 のドレイン電極 Tr 1 2 d と一緒に形成し、また、データライン L d をトランジスタ Tr 1 1 、 Tr 1 2 のゲート電極 Tr 1 1 g 、 Tr 1 2 g を形成するためのゲートメタル層をパターニングすることによって形成し、コンタクトホール CH11 を介してトランジスタ Tr 1 1 のドレイン電極 Tr 1 1 d に接続している。

30

#### 【 0 0 4 8 】

ここで、コンタクトホール CH12 は、選択ライン L s の延在方向において、トランジスタ Tr 1 1 のゲート電極 Tr 1 1 g が設けられている領域及びデータライン L d が設けられている領域を除いて設けられている。したがって、選択ライン L s は、図 5 ( a ) 、図 5 ( b ) に示すように、コンタクトホール CH12 のある領域において下層配線層 L s1 及び上層配線層 L s2 で構成され、データライン L d と重なる領域において上層配線層 L s2 のみで構成され、ゲート電極 Tr 1 1 g が設けられている領域では形成されておらず、且つトランジスタ Tr 1 1 のゲート電極 Tr 1 1 g の両端に接続されている。そして、コンタクトホール CH15 は、電源電圧ライン L v の延在方向において、データライン L d が設けられている領域を除いて設けられている。したがって、電源電圧ライン L v は、図 5 ( a ) 、図 5 ( b ) に示すように、コンタクトホール CH15 のある領域において下層配線層 L v1 及び上層配線層 L v2 で構成され、データライン L d と重なる領域において上層配線層 L v2 のみで構成されている。

40

#### 【 0 0 4 9 】

なお、選択ライン L s 及び電源電圧ライン L v の配線構造は、上記構成に限定される必要はなく、上記ゲートメタル層をパターニングすることによってゲート絶縁膜 1 2 の下層に形成し、データライン L d を上記ソース、ドレインメタル層をパターニングすることによってゲート絶縁膜 1 2 の上層に形成することでコンタクトホール CH11 及び CH12 を設けることなく、選択ライン L s をゲート電極 Tr 1 1 g と一緒に、また、データライン

50

L d をドレイン電極 T r 1 1 d と一緒に設けるようにしてもよい。

#### 【 0 0 5 0 】

また、画素電極 1 5 と画素駆動回路 D C のトランジスタ T r 1 2 のソース電極 T r 1 2 s (又は、キャパシタ C s の他方側の電極 E cb ) とを電気的に接続する構造としては、図 4 に示すように、保護絶縁膜 1 3 及び平坦化膜 1 4 を貫通して設けられたコンタクトホール C H 14 に画素電極 1 5 を形成する電極材料を埋め込んで、画素電極 1 5 とソース電極 T r 1 2 s とを直接接続するものであってもよいし、コンタクトホール C H 14 に画素電極 1 5 とは異なる導電性材料からなるコンタクトメタル ( 図示を省略 ) を埋め込んで、画素電極 1 5 とソース電極 T r 1 2 s とを当該コンタクトメタルを介して接続するものであってもよい。

10

#### 【 0 0 5 1 】

バンク 1 7 は、表示パネル 1 0 に 2 次元配列される複数の表示画素 ( 色画素 ) P I X 相互の境界領域 ( 具体的には、各画素電極 1 5 間の領域 ) であって、表示パネル 1 0 の列方向に ( 表示パネル 1 0 全体では図 1 に示すように複数の画素電極 1 5 を取り囲む柵状、又は、各画素電極 1 5 を取り囲む格子状の平面パターンを有するように ) 配設されている。

#### 【 0 0 5 2 】

ここで、図 3 、図 4 に示すように、上記境界領域のうち、表示パネル 1 0 ( 絶縁性基板 1 1 ) の列方向には上記トランジスタ T r 1 2 が延在して形成されており、バンク 1 7 は、例えば当該トランジスタ T r 1 2 を略被覆し、各画素形成領域 R px の画素電極 1 5 間に形成される層間絶縁膜 1 6 上に、絶縁性基板 1 1 表面から高さ方向に連続的に突出するよう 20 に形成されている。これにより、バンク 1 7 により囲まれた領域、すなわち、列方向 ( 図 1 の上下方向 ) に配列された複数の表示画素 P I X の画素電極 1 5 を含む領域が、後述する製造方法において、有機 E L 層 1 8 ( 例えば正孔輸送層 1 8 a 及び電子輸送性発光層 1 8 b ) を形成する際の有機化合物材料を含む溶液或いは懸濁液の溶媒 ( 有機化合物含有液 ) の塗布領域 ( すなわち、E L 素子形成領域 R e l ) として規定される。

20

#### 【 0 0 5 3 】

また、バンク 1 7 は、例えば感光性の樹脂材料を用いて形成され、上記有機 E L 層 1 8 の形成時において、少なくともその表面 ( 側面及び上面 ) が、E L 素子形成領域 R e l に塗布される有機化合物含有液に対して撥液性を有するように表面処理が施されている。

そして、上記画素駆動回路 D C 、有機 E L 素子 O L E D 及びバンク 1 7 が形成された絶縁性基板 1 1 の一面側全域には、例えば図 4 、図 5 に示すように、保護絶縁膜 ( パッシベーション膜 ) としての機能を有する封止層 2 0 が被覆形成されている。さらには、絶縁性基板 1 1 に対向するように図示を省略したガラス基板等からなる封止基板が接合されているものであってもよい。

30

#### 【 0 0 5 4 】

そして、本実施形態に係る表示パネルにおいては、特に、E L 素子形成領域 R e l の画素電極 1 5 上に形成される有機 E L 層 1 8 のうち、正孔輸送層 1 8 a の膜厚を、R 、 G 、 B の各色画素 P X r 、 P X g 、 P X b ごとに、異なる特定の膜厚になるように形成したことを特徴としている。具体的には、有機 E L 層 ( 発光機能層 ) 1 8 として、上述した正孔輸送層 1 8 a と電子輸送性発光層 1 8 b に加え、正孔輸送層 1 8 a と電子輸送性発光層 1 8 b との間にインターレイヤ層を介在させた層構造において、各色画素 P X r 、 P X g 、 P X b に共通の層構造としてインターレイヤ層を 1 0 n m 、電子輸送性発光層 1 8 b を 7 0 n m の膜厚で形成した場合、赤 ( R ) 色の発光色を有する色画素 P X r では正孔輸送層 1 8 a の膜厚を概ね 1 5 n m ± 1 0 n m に設定し、緑 ( G ) 色の発光色を有する色画素 P X g では正孔輸送層 1 8 a の膜厚を概ね 9 5 n m ± 2 0 n m に設定し、青 ( B ) 色の発光色を有する色画素 P X b では正孔輸送層 1 8 a の膜厚を概ね 9 0 n m ± 2 0 n m に設定する。

40

#### 【 0 0 5 5 】

このような表示パネル 1 0 ( 表示画素 P I X ) においては、データライン L d を介して供給される表示データに応じた階調信号 V pix に基づいて、所定の電流値を有する発光駆

50

動電流がトランジスタ Tr 1 2 のソース - ドレイン間に流れ、有機 EL 素子 OLED の画素電極 1 5 に供給されることにより、各表示画素（色画素）PIX の有機 EL 素子 OLED が上記表示データに応じた所望の輝度階調で発光動作する。

#### 【 0 0 5 6 】

ここで、本実施形態に係る表示パネル 1 0 においては、画素電極 1 5 が光反射特性（可視光に対して高い反射率）を有し、かつ、対向電極 1 9 が光透過特性（可視光に対して高い透過率）を有することにより、各表示画素 PIX の有機 EL 層 1 8 において発光した光が、光透過特性を有する対向電極 1 9 を介して視野側（図 4、図 5 の上方）に直接射出されるとともに、光反射特性を有する画素電極 1 5 で反射し、対向電極 1 9 を介して視野側に出射されるトップエミッション型の発光構造を実現することができる。 10

#### 【 0 0 5 7 】

このとき、上述したように、R、G、B の各色画素 Px r、Px g、Px b の EL 素子形成領域 Rel に形成される有機 EL 層 1 8（正孔輸送層 1 8 a）の膜厚を、R、G、B の各色に対応させて異なる特定の膜厚になるように設定したことにより、電子輸送性発光層 1 8 b において発光した光が、対向電極 1 9 を介して直接視野側に出射されるとともに、インターレイヤ層及び特定の膜厚を有する正孔輸送層 1 8 a を介して光反射特性を有する画素電極 1 5 表面で反射し、再び上記正孔輸送層 1 8 a 及びインターレイヤ層、さらに電子輸送性発光層 1 8 b、対向電極 1 9 を介して視野側に出射されるので、光の干渉効果を利用して色度や発光強度を調節することができ、色度ずれや輝度のばらつきを抑制して、画像のにじみやぼけ等のない良好な表示特性を実現することができる。 20

#### 【 0 0 5 8 】

また、本実施形態に係る表示パネル 1 0 においては、トップエミッション型の発光構造を有しているので、絶縁性基板 1 1 上に形成された画素駆動回路 DC の各回路素子や配線層を、保護絶縁膜 1 3 及び平坦化膜 1 4 上に形成された有機 EL 素子 OLED と平面的に重なるように配置することができ、画素開口率を高くして、消費電力の低減やパネル寿命の長期化を図ることができるとともに、画素回路のレイアウト設計の自由度を高めることができる。 20

#### 【 0 0 5 9 】

##### （表示パネルの製造方法）

次に、本実施形態に係る表示パネルの製造方法について説明する。 30

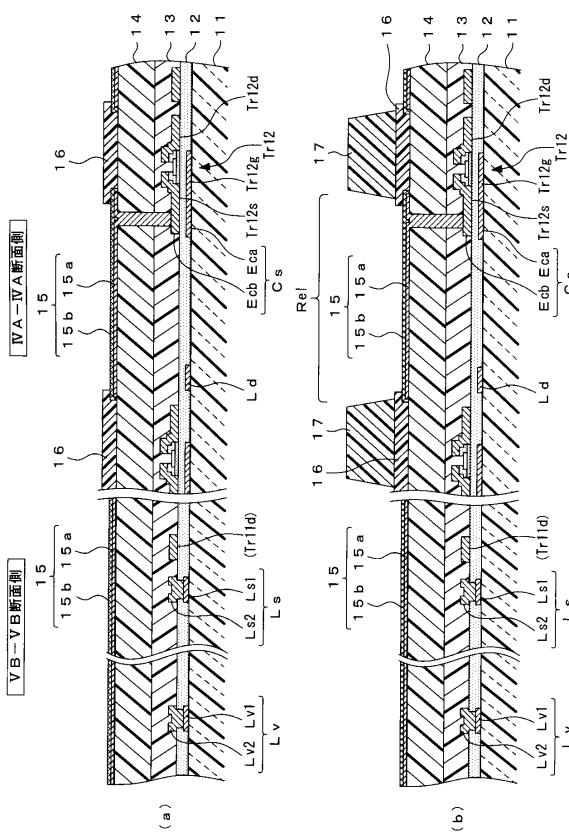

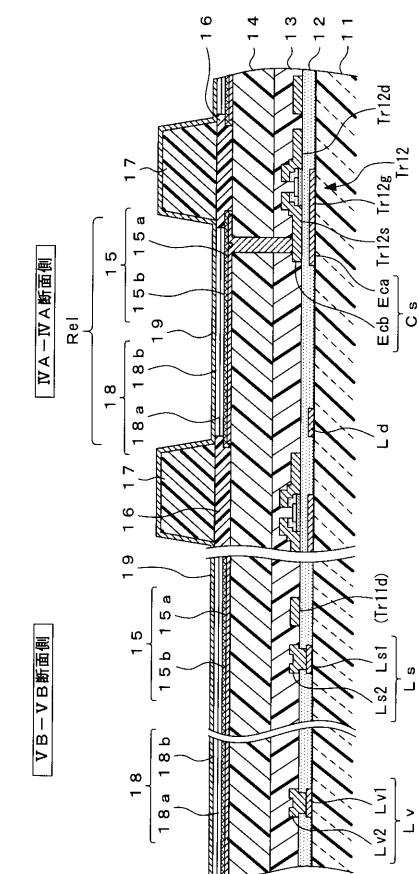

図 6 乃至図 1 0 は、本実施形態に係る表示装置（表示パネル）の製造方法の一例を示す工程断面図である。ここでは、図 4、図 5 ( a ) に示した IVA - IVA 線及び VB - VB 線に沿った表示パネルの断面構造のうち、各一部分（トランジスタ Tr 1 2、キャパシタ Cs、有機 EL 素子 OLED、選択ライン L s、電源電圧ライン L v 等）を便宜的に抜き出した構造を示して、上述した表示パネルの製造方法の概略を説明する。

#### 【 0 0 6 0 】

上述した表示パネルの製造方法は、まず、図 6 ( a ) に示すように、ガラス基板等の絶縁性基板 1 1 の一面側（図面上面側）に設定された表示画素（色画素）PIX の画素形成領域 R px に、画素駆動回路 DC のトランジスタ Tr 1 1、Tr 1 2 やキャパシタ Cs、データライン L d や選択ライン L s、電源電圧ライン L v 等の配線層を形成する（図 3 ~ 図 5 参照）。 40

#### 【 0 0 6 1 】

具体的には、絶縁性基板 1 1 上に、ゲート電極 Tr 1 1 g、Tr 1 2 g、及び、当該ゲート電極 Tr 1 2 g と一体的に形成されるキャパシタ Cs の一方側の電極 E ca、データライン L d、選択ライン L s の下層配線層 L s1、電源電圧ライン L v の下層配線層 L v1 を、同一のゲートメタル層をパターニングすることによって同時に形成し、その後、絶縁性基板 1 1 の全域にゲート絶縁膜 1 2 を被覆形成する。なお、図 3 に示したように、データライン L d と選択ライン L s 及び電源電圧ライン L v が交差する領域においては、例えば選択ライン L s の下層配線層 L s1 及び電源電圧ライン L v の下層配線層 L v1 を形成しないようにして、相互に電気的に接続されない（絶縁される）ようにする。 50

**【 0 0 6 2 】**

次いで、上記データライン L d 上のゲート絶縁膜 1 2 の所定の領域にコンタクトホール C H11を、また、選択ライン L s の下層配線層 L s1上のゲート絶縁膜 1 2 にコンタクトホール C H12を、電源電圧ライン L v の下層配線層 L v1上のゲート絶縁膜 1 2 にコンタクトホール C H15を、トランジスタ T r 1 2 のゲート電極 T r 1 2 g 上のゲート絶縁膜 1 2 の所定の領域にコンタクトホール C H13をそれぞれ形成する。

**【 0 0 6 3 】**

次いで、ゲート絶縁膜 1 2 上の各ゲート電極 T r 1 1 g、T r 1 2 g に対応する領域に、例えは、アモルファスシリコンやポリシリコン等からなる半導体層 S M C、及び、窒化シリコン等からなるチャネル保護層 B L を形成し、当該半導体層 S M C（チャネル）の両端部にオーミック接続のための不純物層 O H M を介してソース電極 T r 1 1 s、T r 1 2 s 及びドレイン電極 T r 1 1 d、T r 1 2 d を形成する。10

**【 0 0 6 4 】**

ここで、図 2、図 3 に示したように、トランジスタ T r 1 1 のドレイン電極 T r 1 1 d がゲート絶縁膜 1 2 に形成されたコンタクトホール C H11を介してデータライン L d に接続され、同ソース電極 T r 1 1 s がゲート絶縁膜 1 2 に形成されたコンタクトホール C H13を介してトランジスタ T r 1 2 のゲート電極 T r 1 2 g に接続される。

**【 0 0 6 5 】**

また、このとき、同一のソース、ドレインメタル層をパターニングすることによってソース電極 T r 1 2 s に接続されたキャパシタ C s の他方側の電極 E cb を形成するとともに、上記選択ライン L s の上層配線層 L s2、及び、電源電圧ライン L v の上層配線層 L v2 を同時に形成する。20

**【 0 0 6 6 】**

ここで、選択ライン L s の上層配線層 L s2 は、ゲート絶縁膜 1 2 に形成された溝状のコンタクトホール（開口部）C H12を介して、上記選択ライン L s の下層配線層 L s1 に電気的に接続されるように形成され、また、電源電圧ライン L v の上層配線層 L v2 は、ゲート絶縁膜 1 2 に形成された溝状のコンタクトホール（開口部）C H15を介して、上記電源電圧ライン L v の下層配線層 L v1 に電気的に接続されるように形成される。これにより、上層配線層 L s2 及び下層配線層 L s1 からなる積層配線構造を有する選択ライン L s、及び、上層配線層 L v2 及び下層配線層 L v1 からなる積層配線構造を有する電源電圧ライン L v が形成される。30

**【 0 0 6 7 】**

なお、上述したトランジスタ T r 1 1、T r 1 2 のソース電極 T r 1 1 s、T r 1 2 s 及びドレイン電極 T r 1 1 d、T r 1 2 d、キャパシタ C s の他方側の電極 E cb、選択ライン L s の上層配線層 L s2、電源電圧ライン L v の上層配線層 L v2 は、配線抵抗を低減し、かつ、マイグレーションを低減する目的で、例えはアルミニウム - チタン ( A l T i ) やアルミニウム - ネオジウム - チタン ( A l N d T i ) 等のアルミニウム合金層と、クロム ( C r ) 等の遷移金属層からなる積層配線構造を有しているものであってもよい。

**【 0 0 6 8 】**

次いで、図 6 ( b ) に示すように、上記トランジスタ T r 1 1、T r 1 2、キャパシタ C s、選択ライン L s の上層配線層 L s2 及び電源電圧ライン L v の上層配線層 L v2 を含む絶縁性基板 1 1 の一面側全域を被覆するように、窒化シリコン ( S i N ) 等からなる保護絶縁膜 1 3 を形成し、さらにその上に、平坦化膜 1 4 を積層形成する。ここで、平坦化膜 1 4 は、絶縁性基板 1 1 上に形成された上記画素駆動回路 D C のトランジスタ T r 1 1、T r 1 2 や各配線層による表面段差を緩和して、当該平坦化膜 1 4 表面の平坦性を向上させるように膜材料やその厚みが適宜設定されている。本実施形態に適用可能な平坦化膜材料としては、具体的には、熱硬化性を有する有機材料（例えはアクリル系樹脂、エポキシ系樹脂、ポリイミド系樹脂等）を良好に適用することができる。40

**【 0 0 6 9 】**

次いで、図 6 ( c ) に示すように、フォトリソグラフィ法を用いて上記平坦化膜 14 及び保護絶縁膜 13 をエッティングして、少なくともトランジスタ Tr 12 のソース電極 Tr 12 s ( 又は、キャパシタ Cs の他方側の電極 Ecb ) の上面が露出するコンタクトホール CH 14 を形成する。

#### 【 0 0 7 0 】

次いで、上記コンタクトホール CH 14 を含む平坦化膜 14 上に、スパッタリング法等を用いて銀 ( Ag ) やアルミニウム ( Al ) 等の金属材料、あるいは、アルミニウム - ネオジウム - チタン ( AlNdTi ) 等の合金材料からなる光反射特性を有する ( より具体的には、可視光域に対して高い反射率を有する ) 金属薄膜を形成した後、当該金属薄膜をパターニングして、図 7 ( a ) に示すように、コンタクトホール CH 14 内部においてトランジスタ Tr 12 のソース電極 Tr 12 s と電気的に接続し、かつ、各表示画素 PIX における EL 素子形成領域 Rel に対応する平面形状を有して平坦化膜 14 上に延在する反射層 15 a を形成する。

10

#### 【 0 0 7 1 】

次いで、上記反射層 15 a を含む平坦化膜 14 上に、スパッタリング法等を用いて錫ドープ酸化インジウム ( Indium Tin Oxide ; ITO ) や亜鉛ドープ酸化インジウム ( Indium Zinc Oxide ; IZO ) 、タングステンドープ酸化インジウム ( Indium Tungsten Oxide ; IWO ) 、タングステン - 亜鉛ドープ酸化インジウム ( Indium Tungsten Zinc Oxide ; IWZO ) 等の透明電極材料からなる ( 光透過特性を有する ) 導電性酸化金属層を薄膜形成した後、当該導電性酸化金属層をパターニングして、図 7 ( b ) に示すように、少なくとも上記反射層 15 a の上面及び端面 ( 側面 ) を被覆し、各 EL 素子形成領域 Rel に対応する平面形状を有する透明電極層 15 b を形成する。

20

#### 【 0 0 7 2 】

これにより、反射層 15 a 及び透明電極層 15 b を有し、コンタクトホール CH 14 を介してトランジスタ Tr 12 のソース電極 Tr 12 s に電気的に接続された積層電極構造を有する画素電極 15 が形成される。

この画素電極 15 の形成工程においては、各 EL 素子形成領域 Rel に形成される反射層 15 a が、透明電極層 15 b となる導電性酸化金属層により上面及び側面が完全に被覆されて露出しないようにした状態で、当該導電性酸化金属層をエッティングすることにより透明電極層 15 b のパターニングが行われるので、導電性酸化金属層 ( ITO 等 ) と反射層 15 a との間の電池反応の発生を防止することができるとともに、反射層 15 a がオーバーエッティングされたり、エッティングダメージを受けたりすることを防止することができる。

30

#### 【 0 0 7 3 】

次いで、上記画素電極 15 を含む平坦化膜 14 上に、化学気相成長法 ( CVD 法 ) 等を用いて、例えばシリコン酸化膜やシリコン窒化膜等の無機の絶縁性材料からなる絶縁層を形成した後パターニングすることにより、図 4 及び図 8 ( a ) に示すように、隣接する表示画素 ( 色画素 ) PIX との境界領域 ( すなわち、隣接する画素電極 15 間の領域 ) を被覆するとともに、各画素形成領域 Rpx に画素電極 15 の上面が露出する開口部を有する層間絶縁膜 16 を形成する。

40

#### 【 0 0 7 4 】

次いで、図 8 ( b ) に示すように、隣接する表示画素 PIX ( 画素電極 15 ) 間の境界領域に形成された上記層間絶縁膜 16 上に、例えばポリイミド系やアクリル系等の感光性の樹脂材料からなるバンク 17 を形成する。具体的には、上記層間絶縁膜 16 及び画素電極 15 を含む絶縁性基板 11 の一面側全域を被覆するように形成された感光性樹脂層をパターニングすることにより、図 1 に示したように、行方向に隣接する表示画素 PIX 間の境界領域であって、表示パネル 10 の列方向に延在する領域を含む柵状の平面形状を有し、高さ方向に連続的に突出するバンク ( 隔壁 ) 17 を形成する。これにより、表示パネル 10 の列方向に配列された同一色の複数の表示画素 ( 色画素 ) PIX の EL 素子形成領域 Rel がバンク 17 及び層間絶縁膜 16 により囲まれて画定されて、該 EL 素子形成領域 R

50

el内に各表示画素P IXの画素電極15の上面が露出する。

#### 【0075】

次いで、絶縁性基板11を純水で洗浄した後、例えば酸素プラズマ処理やUVオゾン処理等を施すことにより、EL素子形成領域ReIに露出する各画素電極15の表面を、後述する正孔輸送材料や電子輸送性発光材料の有機化合物含有液に対して親液化する処理を施し、続いて、バンク17の表面にCF<sub>4</sub>プラズマ処理を行い、バンク17の表面を有機化合物含有液に対して撥液化する処理を施す。なお、バンク17を形成する樹脂材料自体に予めフッ素原子が含まれていれば、上記撥液化処理は必ずしも行わなくてもよい。

#### 【0076】

これにより、同一の絶縁性基板11上において、バンク17の表面のみが撥液化処理され、当該バンク17により画定された各画素形成領域Rpxに露出する画素電極15の表面は撥液化されていない状態（親液性）が保持されるので、後述するように、有機化合物含有液を塗布して有機EL層18（電子輸送性発光層18b）を形成する場合であっても、隣接するEL素子形成領域ReIへの有機化合物含有液の漏出や乗り越えを防止することができ、隣接画素相互の混色を抑制して、赤（R）、緑（G）、青（B）色の塗り分けが可能となる。

#### 【0077】

なお、本実施形態において使用する「撥液性」とは、後述する正孔輸送層18aとなる正孔輸送材料を含有する有機化合物含有液や、電子輸送性発光層18bとなる電子輸送性発光材料を含有する有機化合物含有液、もしくは、これらの溶液に用いる有機溶媒を、基板上等に滴下して、接触角の測定を行った場合に、当該接触角が50°以上になる状態と規定する。また、「撥液性」に対峙する「親液性」とは、本実施形態においては、上記接触角が40°以下、好ましくは10°以下になる状態と規定する。

#### 【0078】

次いで、上記バンク17により囲まれた（画定された）各色のEL素子形成領域ReIに対して、プロセス制御性や生産性に優れる、インクジェット法やノズルプリンティング法等を適用して、高分子系の有機材料からなる正孔輸送材料の溶液又は分散液を塗布した後、加熱乾燥させて、R、G、Bの各色画素PXr、PXg、PXbごとに、異なる特定の膜厚を有するように正孔輸送層18aを形成する。続いて、各色画素PXr、PXg、PXbごとに、上記正孔輸送層18a上にR、G、Bの発光色に対応した高分子系の有機材料からなる電子輸送性発光材料の溶液又は分散液を塗布した後、加熱乾燥させて電子輸送性発光層18bを形成する。これにより、図9に示すように、画素電極15上に少なくとも正孔輸送層18a及び電子輸送性発光層18bを有する有機EL層18が積層形成される。なお、有機EL層18の成膜プロセスについては詳しく後述する。

#### 【0079】

その後、図10に示すように、少なくとも各表示画素P IXのEL素子形成領域ReIを含む絶縁性基板11上に光透過性を有する導電層（透明電極層）を形成し、上記有機EL層18（正孔輸送層18a及び電子輸送性発光層18b）を介して各表示画素P IXの画素電極15に対向する共通の対向電極（例えばカソード電極）19を形成する。

#### 【0080】

具体的には、対向電極19は、例えば蒸着法等により電子注入層となるバリウム、マグネシウム、リチウム等の金属材料からなる薄膜を形成した後、その上層にスパッタ法等によりITO等の透明電極層を積層形成した、厚さ方向に透明な膜構造を適用することができる。ここで、対向電極19は、上記画素電極15に対向する領域のみならず、各EL素子形成領域ReIを画定するバンク17上にまで延在する単一の導電層（べた電極）として形成される。

#### 【0081】

次いで、上記対向電極19を形成した後、絶縁性基板11の一面側全域に保護絶縁膜（パッシベーション膜）としてシリコン酸化膜やシリコン窒化膜等からなる封止層20をCVD法等を用いて形成することにより、図4、図5に示したような断面構造を有する表示

10

20

30

40

50

パネル 10 が完成する。なお、図示を省略したが、図 4、図 5 に示したようなパネル構造に加えて、さらに、絶縁性基板 11 に対向するようにガラス基板等からなる封止蓋や封止基板が接合されているものであってもよい。

#### 【 0 0 8 2 】

##### < 有機 E L 層の成膜プロセス >

次に、上述した表示パネルの製造方法において、有機 E L 層 18 ( 正孔輸送層 18 a 及び電子輸送性発光層 18 b ) の成膜プロセスについてさらに詳しく説明する。

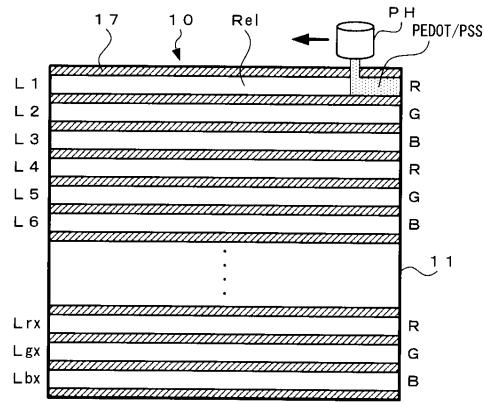

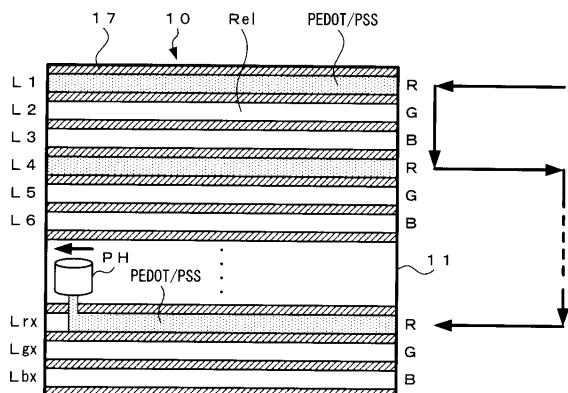

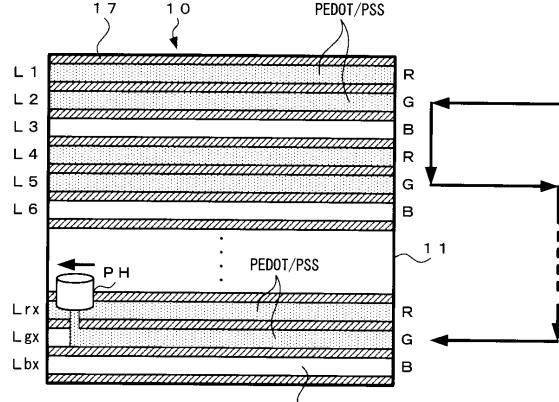

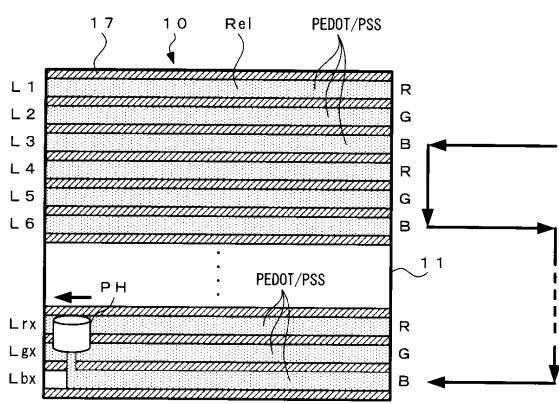

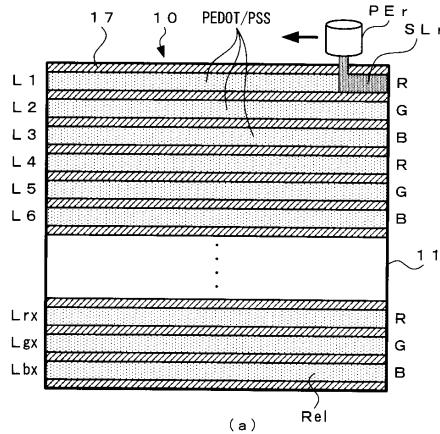

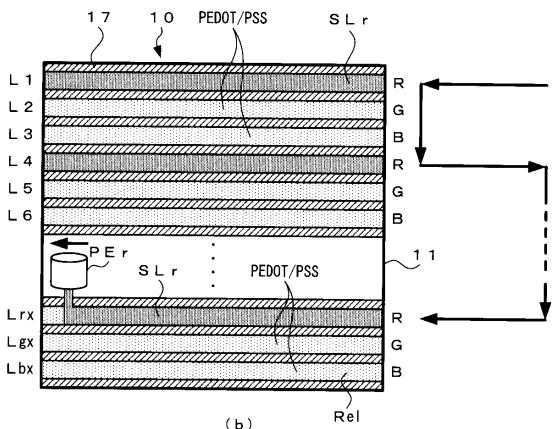

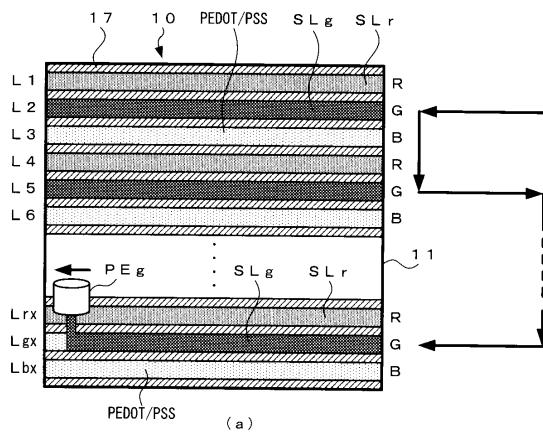

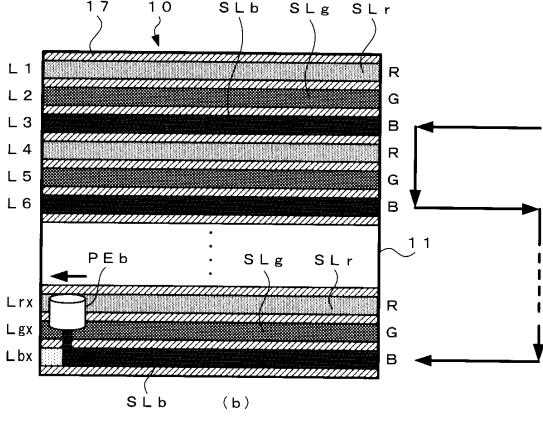

図 11、図 12 は、本実施形態に係る表示装置（表示パネル）の製造方法における正孔輸送層の成膜プロセスを説明するための概念図である。また、図 13、図 14 は、本実施形態に係る表示装置（表示パネル）の製造方法における電子輸送性発光層の成膜プロセスを説明するための概念図である。ここでは、図示を明確にするために、インク塗布処理が実行された各ライン（列）について便宜的にハッチングを施して示した。

10

#### 【 0 0 8 3 】

本実施形態に係る有機 E L 層の成膜プロセスは、上述した表示パネルの製造方法において、バンク 17 により画定された E L 素子形成領域 Rel に露出する画素電極 15 ( 透明電極層 15 b ) 上に、まず、有機高分子系の正孔輸送材料を含む有機化合物含有液として、例えばポリエチレンジオキシチオフェン / ポリスチレンスルホン酸水溶液 ( P E D O T / P S S ; 導電性ポリマーであるポリエチレンジオキシチオフェン P E D O T と、ドーパントであるポリスチレンスルホン酸 P S S を水系溶媒に分散させた分散液 ) を、ノズルプリント成膜装置を用いて塗布した後、加熱乾燥処理を行って溶媒を除去することにより、当該画素電極 15 上に有機高分子系の正孔輸送材料を定着させて、所定の膜厚を有する担体輸送層である正孔輸送層 18 a を形成する。

20

#### 【 0 0 8 4 】

ここで、正孔輸送材料を含む有機化合物含有液の塗布方法は、ノズルプリント成膜装置のプリンタヘッド PH の吐出口から上記 P E D O T / P S S を所定量の液流状にして吐出させ、同一色の色画素（例えば赤 ( R ) 色の色画素 P X r ）が配列される列の E L 素子形成領域 Rel に対して、当該プリンタヘッド PH を所定の速度で順次走査しつつ塗布する。このとき、上述したように、バンク 17 の表面は撥液化処理が施されているので、 E L 素子形成領域 Rel に塗布された P E D O T / P S S の液流はバンク 17 上に着滴した場合であってもはじかれて、親液化処理が施された各画素電極 15 上に馴染んで拡がる。なお、プリンタヘッド PH から吐出される P E D O T / P S S の流量は、例えばノズルプリント成膜装置の吐出ポンプの回転数（吐出量）を制御することにより調整するものであってもよいし、プリンタヘッド PH の吐出口の大きさ（ノズル径）を変化させることにより調整するものであってもよい。

30

#### 【 0 0 8 5 】

具体的には、図 11 ( a ) に示すように、まず、ノズルプリント成膜装置の基板ステージ（図示を省略）上に載置された絶縁性基板 11 に対して、プリンタヘッド PH を表示パネル 10 の例えれば 1 列目の赤 ( R ) 色の色画素 P X r が配列される 1 ライン目 L 1 に沿って相対的に列方向（図 1 に示した表示パネル 10 においては、図面上下方向であるが、図 11 においては、図示の都合上、図面左右方向となる）に走査させながら、 P E D O T / P S S を第 1 の流量で液流状にして吐出して、 1 ライン目 L 1 の E L 素子形成領域 Rel に連続的に塗布する（以下、便宜的に「正孔層（赤）1 走査目」と記す）。

40

#### 【 0 0 8 6 】

次いで、基板ステージ（絶縁性基板 11 ）をプリンタヘッド PH の走査方向（列方向）に対して直交する方向（行方向；図面上方）に 3 ライン（ 3 列）分、相対的に移動させて、プリンタヘッド PH を表示パネル 10 の 4 列目の赤 ( R ) 色の色画素 P X r が配列される 4 ライン目 L 4 に対応する位置に移動させた後、上記正孔層（赤）1 走査目と同様に、プリンタヘッド PH を相対的に列方向に走査させながら、 P E D O T / P S S を上記第 1 の流量で液流状にして吐出して、 4 ライン目 L 4 の E L 素子形成領域 Rel に連続的に塗布する（以下、便宜的に「正孔層（赤）2 走査目」と記す）。

50

**【 0 0 8 7 】**

このようなプリンタヘッドPHを列方向に走査させながらPEDOT/PSSを塗布した後、図11(b)に示すように、プリンタヘッドPHを行方向に所定のピッチ(3ライン分)移動させて、PEDOT/PSSを塗布する一連の動作を順次繰り返し、7ライン目(7列目)L7、10ライン目(10列目)L10、13ライン目(13列目)L13、・・・の赤(R)色の色画素PXrが配列されるEL素子形成領域RelにもPEDOT/PSSを塗布する(正孔層(赤)3走査目～)。

**【 0 0 8 8 】**

次いで、図12(a)に示すように、基板ステージ(絶縁性基板11)をプリンタヘッドPHに対して行方向に相対的に移動させて、プリンタヘッドPHを絶縁性基板11に対して、表示パネル10の2列目の緑(G)色の色画素PXgが配列される2ライン目L2に対応する位置に移動させた後、プリンタヘッドPHを相対的に列方向に走査させながら、PEDOT/PSSを第2の流量で液流状にして吐出して、2ライン目L2のEL素子形成領域Relに連続的に塗布する(以下、便宜的に「正孔層(緑)1走査目」と記す)。

10

**【 0 0 8 9 】**

このとき、上述した正孔層(赤)1走査目で表示パネル10(絶縁性基板11)の1ライン目(1列目)L1のEL素子形成領域Relに塗布されたPEDOT/PSSは、絶縁性基板11が載置された基板ステージを所定の温度に加熱制御することにより、上述した正孔層(赤)2走査目以降の塗布動作が実行される時間中に十分に加熱乾燥が進み、画素電極15(透明電極層15b)上を含む赤(R)色の色画素PXrのEL素子形成領域Rel内に、正孔輸送材料が薄膜状に定着した正孔輸送層18aが形成される。ここで、赤(R)色の色画素PXrの画素電極15(透明電極層15b)上に形成される正孔輸送層18aの膜厚は、上記プリンタヘッドPHの走査速度(塗布速度)や基板ステージの加熱温度等の諸条件を特定の固定値に設定し、PEDOT/PSSの流量のみを任意に設定した場合、プリンタヘッドPHから吐出されるPEDOT/PSSの流量(第1の流量；塗布量に相当する)に依存して決定され、例えば数十nmオーダーの膜厚に形成される。

20

**【 0 0 9 0 】**

次いで、上述した正孔層(赤)2走査目と同様に、基板ステージ(絶縁性基板11)をプリンタヘッドPHの走査方向(列方向)に対して直交する方向(行方向)に3ライン(3列)分、相対的に移動させて、プリンタヘッドPHを表示パネル10の5列目の緑(G)色の色画素PXgが配列される5ライン目L5に対応する位置に移動させた後、上記正孔層(緑)1走査目と同様に、プリンタヘッドPHを相対的に列方向に走査させながら、PEDOT/PSSを上記第2の流量で液流状にして吐出して、5ライン目L5のEL素子形成領域Relに連続的に塗布する(以下、便宜的に「正孔層(緑)2走査目」と記す)

30。

**【 0 0 9 1 】**

以下、上述した正孔層(赤)3走査目以降と同様に、プリンタヘッドPHを列方向に走査させながらPEDOT/PSSを塗布した後、プリンタヘッドPHを行方向に所定のピッチ(3ライン分)移動させて、PEDOT/PSSを塗布する一連の動作を順次繰り返し、8ライン目(8列目)L8、11ライン目(11列目)L11、14ライン目(14列目)L14、・・・の緑(G)色の色画素PXgが配列されるEL素子形成領域RelにもPEDOT/PSSを塗布する(正孔層(緑)3走査目～)。

40

**【 0 0 9 2 】**

さらに、図12(b)に示すように、青(B)色の色画素PXbが配列される各ライン、すなわち、3ライン目(3列目)L3、6ライン目(6列目)L6、9ライン目(9列目)L9、・・・に対しても、上述した赤(R)、緑(G)色の色画素PXr、PXgが配列されるEL素子形成領域Relと同様に、プリンタヘッドPHを列方向に走査させながらPEDOT/PSSを第3の流量で液流状にして吐出、塗布した後、プリンタヘッドPHを行方向に所定のピッチ(3ライン分)移動させて、PEDOT/PSSを塗布する一連の動作を順次繰り返し、青(B)色の色画素PXbが配列されるEL素子形成領域Rel

50

にも P E D O T / P S S を塗布する（正孔層（青）1走査目～）。

#### 【0093】

これにより、緑（G）色の色画素P X g 及び青（B）色の色画素P X b が配列される各E L 素子形成領域R e l に露出する画素電極1 5（透明電極層1 5 b ）上には、プリンタヘッドP H から吐出されるP E D O T / P S S の流量、すなわち、第2の流量及び第3の流量に依存して、所定の膜厚を有する正孔輸送層1 8 a が形成される。ここで、緑（G）色の色画素P X g 及び青（B）色の色画素P X b の画素電極1 5 上に形成される正孔輸送層1 8 a は、いずれも例えれば数十～1 0 0 n m 程度の膜厚に形成される。

#### 【0094】

次に、各色画素P X r 、P X g 、P X b ごとに正孔輸送層1 8 a が形成されたE L 素子形成領域R e l に、有機高分子系の電子輸送性発光材料を含む有機化合物含有液として、例えればポリパラフェニレンビニレン系やポリフルオレン系等の共役二重結合ポリマーを含む赤（R）、緑（G）、青（B）の各発光色に対応した発光材料を、テトラリン、テトラメチルベンゼン、メシチレン、キシレン等の有機溶媒或いは水に溶解した溶液（以下、「発光材料溶液」と記す）を、上記正孔輸送層1 8 a 上に塗布した後、加熱乾燥処理を行って溶媒を除去することにより、上記正孔輸送層1 8 a 上に有機高分子系の電子輸送性発光材料を定着させて、担体輸送層であり発光層でもある電子輸送性発光層1 8 b を形成する。

10

#### 【0095】

ここで、電子輸送性発光材料を含む有機化合物含有液の塗布方法は、上述した正孔輸送層1 8 a を形成する際のP E D O T / P S S （正孔輸送材料を含む有機化合物含有液）の塗布方法と同様に、ノズルプリント成膜装置のプリンタヘッドの吐出口から各発光色に対応した発光材料溶液を液流状にして吐出させ、同一色の色画素（例えは赤（R）色の色画素P X r ）が配列される列のE L 素子形成領域R e l に対して、当該プリンタヘッドを順次走査しつつ塗布する。このとき、上述したように、バンク1 7 の表面は撥液化処理が施されているので、E L 素子形成領域R e l に塗布された発光材料溶液の液流はバンク1 7 上に着滴した場合であってもはじかれて、親液性を有する上記正孔輸送層1 8 a 上に馴染んで拡がる。

20

#### 【0096】

具体的には、図13（a）に示すように、まず、ノズルプリント成膜装置の基板ステージ（図示を省略）上に載置された絶縁性基板1 1 に対して、赤（R）色の発光色に対応した発光材料溶液を吐出するプリンタヘッドP E r を表示パネル1 0 の1列目の赤（R）色の色画素P X r が配列される1ライン目L 1 に沿って相対的に列方向（図面左右方向）に走査させながら、発光材料溶液所定の流量で液流状にして吐出して、1ライン目L 1 のE L 素子形成領域R e l に連続的に塗布する（以下、便宜的に「発光層（赤）1走査目」と記す）。

30

#### 【0097】

次いで、基板ステージ（絶縁性基板1 1 ）をプリンタヘッドP E r の走査方向（列方向）に対して直交する方向（行方向；図面上方）に3ライン（3列）分、相対的に移動させて、プリンタヘッドP E r を表示パネル1 0 の4列目の赤（R）色の色画素P X r が配列される4ライン目L 4 に対応する位置に移動させた後、上記発光層（赤）1走査目と同様に、プリンタヘッドP E r を相対的に列方向に走査させながら、発光材料溶液を上記所定の流量で液流状にして吐出して、4ライン目L 4 のE L 素子形成領域R e l に連続的に塗布する（発光層（赤）2走査目）。

40

#### 【0098】

以下同様に、図13（b）に示すように、プリンタヘッドP E r を表示パネル1 0 の7、1 0 、1 3 ……列目のラインに沿って走査させながら、当該各ラインのE L 素子形成領域R e l に発光材料溶液を順次塗布する（発光層（赤）3走査目～）。すなわち、同色となる3ラインおきのE L 素子形成領域R e l に発光材料溶液を塗布する。

#### 【0099】

次いで、図14（a）に示すように、プリンタヘッドP E g を絶縁性基板1 1 に対して

50

、表示パネル10の2列目の縁( G )色の色画素 P X g が配列される2ライン目 L 2 に対応する位置に移動させた後、上述した発光層( 赤 )1走査目以降と同様に、プリンタヘッド P E g を列方向に走査させながら発光材料溶液を塗布した後、プリンタヘッド P E g を行方向に所定のピッチ( 3 ライン分 )移動させて、発光材料溶液を塗布する一連の動作を順次繰り返し、2ライン目( 2 列目 ) L 2 、5ライン目( 5 列目 ) L 5 、8ライン目( 8 列目 ) L 8 、・・・の縁( G )色の色画素 P X g が配列される E L 素子形成領域 Rel に発光材料溶液を順次塗布する( 発光層( 緑 )1走査目～ )。

#### 【 0 1 0 0 】

さらに、図14( b )に示すように、表示パネル10の青( B )色の色画素 P X b が配列される3ライン目( 3 列目 ) L 3 、6ライン目( 6 列目 ) L 6 、9ライン目( 9 列目 ) L 9 、・・・の E L 素子形成領域 Rel に対しても、上述した発光層( 赤 )1走査目以降と同様に、プリンタヘッド P E b を列方向に走査させながら発光材料溶液を塗布した後、プリンタヘッド P E b を行方向に所定のピッチ( 3 ライン分 )移動させて、発光材料溶液を塗布する一連の動作を順次繰り返す。

#### 【 0 1 0 1 】

これにより、赤( R )、緑( G )、青( B )色の各色画素 P X r 、 P X g 、 P X b が配列される各 E L 素子形成領域 Rel の正孔輸送層 18 a 上に、所定の膜厚を有する電子輸送性発光層 18 b が形成される。ここで、各色の色画素 P X r 、 P X g 、 P X b に形成される電子輸送性発光層 18 b は、いずれも例えば数十～100 nm 程度の膜厚に形成される。

#### 【 0 1 0 2 】

したがって、このような有機 E L 層の成膜プロセスにより、図4、5、9に示したように、各色画素 P X r 、 P X g 、 P X b が配列される E L 素子形成領域 Rel に、少なくとも、赤( R )、緑( G )、青( B )の各色ごとに異なる膜厚を有する正孔輸送層 18 a と、赤( R )、緑( G )、青( B )の各発光色に対応した所定の膜厚を有する電子輸送性発光層 18 b と、を有する有機 E L 層 18 が形成される。

#### 【 0 1 0 3 】

##### < 製造方法の検証 >

ここで、上述した成膜プロセスによる作用効果について実験結果を示して詳しく説明する。

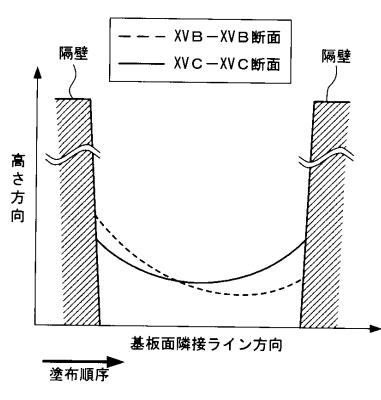

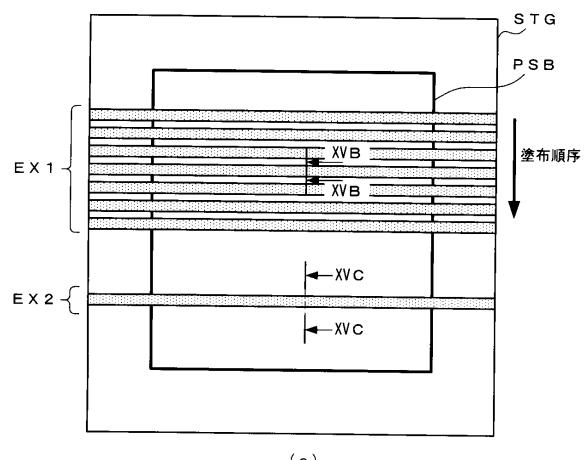

図15は、本実施形態に係る表示装置の製造方法( 有機 E L 層の成膜プロセス )における作用効果の検証結果を示す概略図である。ここで、図15( a )は、パネル基板へのインク塗布方法を示す概略平面図であり、図15( b )は、図15( a )に示した平面図におけるXVB - XVB 線及びXVC - XVC 線( 本明細書においては図15中に示したローマ数字の「 15 」に対応する記号として便宜的に「 XV 」を用いる )に沿った断面を示す概略断面形状図である。また、図15( a )においては、図示を明確にするために、有機化合物含有液の塗布処理が実行されるラインについてハッティングを施して示した。

#### 【 0 1 0 4 】

ここでは、上述した実施形態に示した表示装置( 表示パネル )に対応する実験モデルとして、図15( a )に示すように、ノズルプリント成膜装置の基板ステージ STG 上に載置、固定されたパネル基板 PSB ( 上記絶縁性基板 11 に対応する ) の一面側に設定された各色の E L 素子形成領域 Rel を含むライン( 列 )のうち、相互に隣接するラインに対して高分子系の有機化合物含有液( 上記 P E D O T / P S S や発光材料溶液に相当する )の塗布処理を、例えば図面上側のラインから図面下方向に連続的に順次実行する場合( 図中 EX1 )と、特定の 1 ラインに対してのみ上記有機化合物含有液の塗布処理を実行し、隣接するラインへの塗布処理を行わない場合( 図中 EX2 )における膜厚及び膜断面の形状( プロファイル )について検証する。

#### 【 0 1 0 5 】

また、実験モデルとして、ピクセル密度 80 ppi ( pixels per inch ) とし、上記有機化合物含有液が塗布されるライン数を 420 ライン、ライン間ピッチ 318 μm に設定され

10

20

30

40

50

た表示パネルを適用し、40に加熱した基板ステージSTG上に載置されたパネル基板PSBに対して、上述した成膜プロセスに示した塗布方法で有機化合物含有液を塗布した場合について検証を行った。

#### 【0106】

前者の塗布処理(EX1)において、各ラインのEL素子形成領域ReIに成膜される有機膜(上記正孔輸送層18a又は電子輸送性発光層18bに相当する)の膜厚及び膜断面の形状は、図15(b)に点線でXVB-XVB断面として示すように、図示しない図15(b)に示すラインの左側のラインに有機化合物含有液を塗布した後、連続して図15(b)に示すラインに有機化合物含有液が塗布されることにより、先に塗布されたラインの有機化合物含有液と次に塗布されたラインの有機化合物含有液の乾燥するタイミングが違うことによって生じる隣接するライン方向(図15(b)の左方向)での局所的な溶媒雰囲気の不均一性が、有機化合物含有液の乾燥特性に影響を及ぼし、有機化合物含有液の堆積物の隣接するライン方向での膜厚が不均一になるとともに、先に塗布されたライン側の隔壁側(図15(b)の左方側)において膜表面が壁面に大きく迫り上がり、他方の隔壁側(同図右方側)では壁面への迫り上がりが小さく抑制されて膜断面の形状が大きく偏る現象が確認された。10

#### 【0107】

これに対して、後者の塗布処理(EX2)における有機膜の膜厚及び膜断面の形状は、図15(b)に実線でXVC-XVC断面として示すように、特定のラインに有機化合物含有液を塗布した後、次の塗布処理が隣接するラインに対して実行されないので、有機化合物含有液の乾燥特性への影響をなくして、上記特定のラインに塗布された有機化合物含有液を十分乾燥させて膜厚を略均一にするとともに、膜断面の形状を略均等にすることができる判明した。20

#### 【0108】

すなわち、特定のライン(列)と、当該ラインへの有機化合物含有液の塗布処理の後に、引き続き塗布処理が実行されるラインとが、有機化合物含有液の乾燥特性に影響し合わない程度の離間距離を有し、かつ、特定のラインに隣接するラインへの塗布処理を実行する際に、上記特定のラインに塗布された有機化合物含有液が十分に乾燥する程度に時間が経過しているように製造条件を設定することにより、各表示画素のEL素子形成領域ReIに形成される有機膜(正孔輸送層18aや電子輸送性発光層18b)の膜厚や膜断面形状の均一性を向上させることができる。30

特に、このような製造方法を適用することにより、高分子系の有機化合物含有液を塗布して有機EL層18を形成した有機EL素子OLEDを有する表示装置(表示パネル)において、RGBの各色ごとに異なる膜厚を有する正孔輸送層18aを、均一な膜厚で、かつ、良好な平坦性を有するように形成することができる。

#### 【0109】

なお、上述した実施形態に示した製造方法(有機EL層の成膜プロセス)においては、PEDOT/PSSや発光材料溶液等の有機化合物含有液を、RGB各色の配列に基づいて3ライン(列)おきに塗布する場合について説明したが、本発明はこれに限定されるものではなく、塗布される有機化合物含有液の乾きやすさや上記成膜工程におけるパネル基板の温度等の製造条件に基づいて、3の整数倍となる任意のラインごと(例えば6ラインごとや12ラインごと)に上記有機化合物含有液を塗布するものであってもよい。40

#### 【0110】

また、上述した成膜プロセスにおいては、図1に示したように、RGBの各色で発光する表示画素が2次元配列されたカラー表示パネルについて説明したため、RGB各色の配列に基づいて3ライン(列)おきに塗布する場合について示したが、本発明はこれに限定されるものではなく、表示画素の発光色の種類数に応じて、隣接するライン以外の、相互に離間して配置されたライン(すなわち、複数ラインごと)に有機化合物含有液を塗布するものであってもよい。

#### 【0111】

50

また、上述した成膜プロセスにおいては、プリンタヘッドから吐出する有機化合物含有液（PEDOT/PSSや発光材料溶液）の流量に応じて、正孔輸送層や電子輸送性発光層の膜厚を調整（制御）する場合について説明したが、本発明はこれに限定されるものではなく、上記流量を一定にした状態で、プリンタヘッドの走査速度（基板ステージに対する相対的な移動速度であって、塗布速度に対応する）を変化させることにより膜厚を調整するものであってもよいし、上記流量と走査速度の双方を適宜設定することにより膜厚を調整するものであってもよい。また、例えば上記流量や走査速度を一定として、各ラインへの塗布回数（プリンタヘッドの走査回数）を変化させること（すなわち、2度塗り、3度塗り等）により膜厚を調整するものであってもよいし、更に、これらを組み合わせて用いるものであってもよい。

10

#### 【0112】

##### <表示装置の検証>

次に、上述した製造方法を用いて製造された表示装置（表示パネル）の作用効果について実験結果を示して検証する。

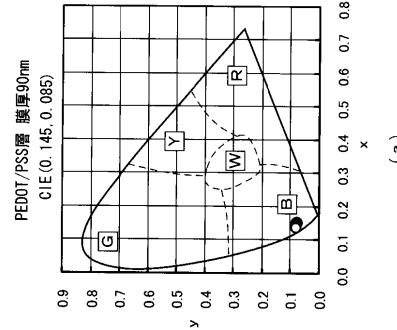

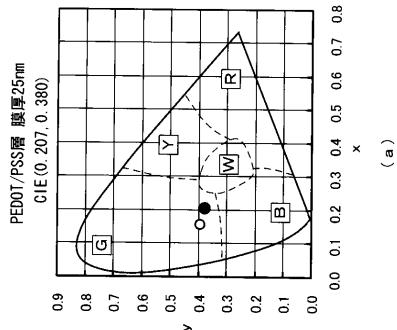

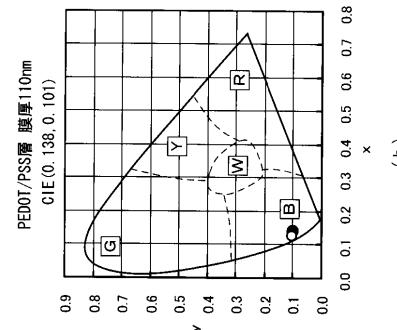

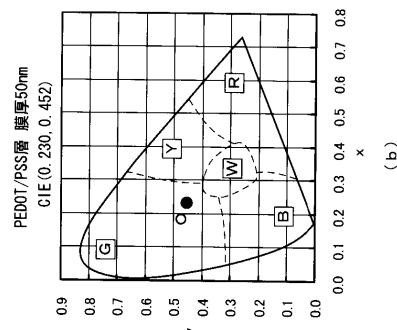

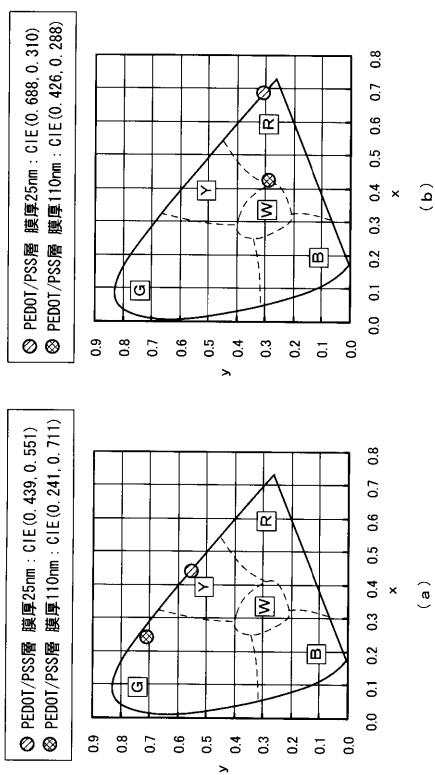

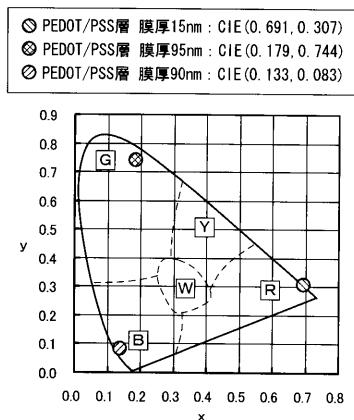

図16は、本実施形態に係る表示装置（表示パネル）に形成される有機EL素子の素子構造の一例（実験モデル）を示す模式図、及び、干渉効果を説明するための概略図である。ここでは、実験モデルとして青色光を発光する有機EL素子の素子構造を示す。図17、図18は、本実施形態に係る表示装置（表示パネル）に形成される青色光を発光する有機EL素子における、正孔輸送層の膜厚と色度との関係を示す色度図である。ここでは、正孔輸送層の膜厚を変化させたときの色度について、図16（a）に示す素子構造を有する有機EL素子を実際に作製して観測した結果（観測結果；図中黒丸で表記）と、当該素子構造に係る各種パラメータに基づくシミュレーション実験の結果（シミュレーション結果；図中白丸で表記）との双方を示す。また、図19は、本実施形態に係る表示装置（表示パネル）に形成される緑色光及び赤色光を発光する有機EL素子における、正孔輸送層の膜厚と色度との関係を示す色度図であり、図20は、本実施形態に係る表示装置（表示パネル）に形成される有機EL素子における、正孔輸送層の膜厚と発光色度との関係を示す色度図である。ここでは、正孔輸送層の膜厚を変化させたときの色度について、図16（a）に示す有機EL素子の素子構造に係る各種パラメータに基づくシミュレーション実験の結果（シミュレーション結果）を示す。

20

#### 【0113】

30

上述した実施形態に係る表示装置の作用効果の検証においては、実験モデルとして、図16（a）に示すように、シリコン窒化膜からなる平坦化膜14上に、アルミニウム（A1）及び銀（Ag）からなる反射層15a、及び、当該反射層15aを被覆するITOからなる透明電極層15bを有する画素電極15と、PEDOT/PSSを塗布して形成された正孔輸送層18aと、電子プロッキング性を有するインターレイヤ層（介在層）18cと、青色発光に対応した発光材料溶液を塗布して形成された発光層（又は電子輸送性発光層）18bと、カルシウム（Ca）の薄膜からなる電子注入層19aと、ITOからなる透明電極層19bと、シリコン窒化膜からなる封止膜（パッシベーション膜）20と、を順次積層した素子構造を有する有機EL素子OLEDを適用して、発光動作時に射出される光の色度を観測した。

40

#### 【0114】

ここで、図16（a）に示した実験モデルは、概略、以下のような製造プロセスにより作成した。

まず、図示を省略した絶縁性の基板（絶縁性基板11）上にシリコン窒化膜からなる平坦化膜14を形成し、その上面にアルミニウム（A1）の薄膜を形成した後、当該アルミニウム薄膜の表面を酸素（O<sub>2</sub>）プラズマ洗浄し、その上に銀（Ag）を100nmの膜厚で真空蒸着する。これにより表面が銀による金属光沢（すなわち光反射特性）を有する反射層15aが形成される。

#### 【0115】

次いで、上記反射層15a上に対向ターゲットスパッタ法によりITOを25nmの膜

50

厚で成膜して、反射層 15 a 表面を被覆する透明導電層 15 b を形成する。

次いで、上記透明電極層 15 b の表面を UV オゾン洗浄を施して親液化した後、スピニコート法により PEDOT / PSS を塗布し、乾燥させて、各色ごとに異なる膜厚を有する正孔輸送層 18 a を成膜する。

#### 【0116】

なお、上述した実施形態においては、絶縁性基板 11 の一面側に複数の塗布ライン（パンク 17 により囲まれた複数の EL 素子形成領域 Rel からなる領域に相当する）が設定されている場合には、ノズルプリント成膜装置により有機化合物含有液を液流状にして連続的に塗布して、正孔輸送層 18 a を成膜するが、ここでは、実験モデルとして便宜的にスピニコート法により PEDOT / PSS を塗布して、各色ごとに任意の膜厚を有する正孔輸送層 18 a を成膜した場合について示す。10

#### 【0117】

具体的には、図 16 (a) に示した有機 EL 素子 OLEO においては、膜厚 25 nm の正孔輸送層 18 a を形成するための成膜条件として、PEDOT / PSS の固形分濃度を 1.4%、基板の回転数を 800 rpm で 5 sec、さらに回転数 4500 rpm で 20 sec に設定し、また、膜厚 50 nm の正孔輸送層 18 a を形成するための成膜条件として、PEDOT / PSS の固形分濃度を 1.4%、基板の回転数を 800 rpm で 5 sec、さらに回転数 2000 rpm で 20 sec に設定し、膜厚 90 nm の正孔輸送層 18 a を形成するための成膜条件として、PEDOT / PSS の固形分濃度を 2.8%、基板の回転数を 800 rpm で 5 sec、さらに回転数 3000 rpm で 20 sec に設定し、膜厚 110 nm の正孔輸送層 18 a を形成するための成膜条件として、PEDOT / PSS の固形分濃度を 2.8%、基板の回転数を 800 rpm で 5 sec、さらに回転数 2000 rpm で 20 sec に設定した。20

#### 【0118】

次いで、スピニコート法により濃度 0.5 wt % のキシレン溶液を正孔輸送層 18 a 上に滴下し、回転数 800 rpm で 5 sec、さらに回転数 2000 rpm で 20 sec の成膜条件で、膜厚 10 nm のインターレイヤ層 18 c を成膜する。

次いで、スピニコート法により濃度 1.0 wt % のキシレン溶液をインターレイヤ層 18 c 上に滴下し、回転数 800 rpm で 5 sec、さらに回転数 2000 rpm で 20 sec の成膜条件で、膜厚 70 nm の青色発光層（又は電子輸送性発光層）18 b を成膜する。30

#### 【0119】

次いで、真空蒸着法により上記青色発光層 18 b 上にカルシウム（Ca）を膜厚 15 nm で成膜して電子注入層 19 a を形成した後、対向ターゲットスパッタ法によりITOを 50 nm の膜厚で成膜して透明電極層 19 b を形成する。

そして、パッシベーション膜として対向ターゲットスパッタ法により窒化シリコンを 600 nm の膜厚で成膜して封止層 20 を形成する。

#### 【0120】

上述したような膜厚を有する各層が積層された有機 EL 素子において、発光時の色度特性（色度座標）を検討すると、正孔輸送層 18 a の膜厚を 25 nm に設定した場合には、図 17 (a) に示すように、観測結果における CIE (Commission International de l'Eclairage ; 国際照明委員会) x y 色度座標は、CIE (0.207, 0.380) であり、シミュレーション結果における CIE x y 色度座標は、CIE (0.163, 0.392) であった。また、正孔輸送層 18 a の膜厚を 50 nm に設定した場合には、図 17 (b) に示すように、観測結果における CIE x y 色度座標は、CIE (0.230, 0.452) であり、シミュレーション結果における CIE x y 色度座標は、CIE (0.186, 0.474) であった。すなわち、正孔輸送層 18 a の膜厚を 25 nm、50 nm に設定したいずれの場合においても、発光色度は青（B）色の色度領域から大きくはずれており、良好な青色発光が行われないことが判明した。40

#### 【0121】

一方、正孔輸送層 18 a の膜厚を 90 nm に設定した場合には、図 18 (a) に示すように、観測結果における CIE xy 色度座標は、CIE (0.145, 0.085) であり、シミュレーション結果における CIE xy 色度座標は、CIE (0.133, 0.083) であった。また、正孔輸送層 18 a の膜厚を 110 nm に設定した場合には、図 18 (b) に示すように、観測結果における CIE xy 色度座標は、CIE (0.138, 0.101) であり、シミュレーション結果における CIE xy 色度座標は、CIE (0.128, 0.103) であった。すなわち、正孔輸送層 18 a の膜厚を 90 nm、110 nm に設定したいずれの場合においても、青 (B) 色の色度領域内の鮮明な青色を示す座標にあって、良好な青色発光が行われることが判明した。

## 【0122】

10

このような正孔輸送層 18 a の膜厚による発光色度の変化は、図 16 (a) に示した素子構造において、図 16 (b) に示すように、青色発光層（電子輸送性発光層）18 b 内の発光点で発光し、厚さ方向に透明な電子注入層 19 a 及び透明電極層 19 b からなる対向電極 19 を透過して直接視野側（図面上方）に出射される光（すなわち、正孔輸送層 18 a を介さないで出射される光）RY1 と、発光点の上方の対向電極 19 表面や封止層 20 表面、及び、発光点の下方の画素電極 15 の透明電極層 15 b 表面や反射層 15 a 表面で反射を繰り返した（多重反射した）後、視野側（図面上方）に出射される光（すなわち、膜厚を変化させた正孔輸送層 18 a を透過して出射される光）RY2 との光路差（光学長の違い）に起因する干渉効果に基づいて発生するものである。したがって、正孔輸送層 18 a の膜厚を適宜調整することにより、CIE 色度図上で最適な発光色度を設定することができる。

## 【0123】

20

また、図 17、図 18 に示したように、正孔輸送層 18 a の膜厚を 25 ~ 110 nm の範囲で変化させた場合の CIE xy 色度座標は、有機 EL 素子を実際に作製した場合の観測結果と、当該有機 EL 素子における各種パラメータに基づくシミュレーション結果が極めて近似することが判明し、このことから、有機 EL 素子における各種パラメータに基づいて発光時の色度特性（色度座標）を比較的高い精度で確定できることが判明した。

## 【0124】

以下、緑色光及び赤色光を発光する有機 EL 素子における発光時の色度特性（色度座標）については、各種パラメータに基づくシミュレーション結果のみを示して説明する。ここでは、上述した青色光を発光する有機 EL 素子の場合と同様に、図 16 (a) に示した素子構造を有しているものとする。

30

## 【0125】

緑色光を発光する有機 EL 素子について、発光時の色度特性（シミュレーション結果）を検討すると、図 19 (a) に示すように、正孔輸送層 18 a の膜厚を 25 nm に設定した場合には、CIE xy 色度座標は、CIE (0.439, 0.551) であり、膜厚を 110 nm に設定した場合には、CIE (0.241, 0.711) であった。また、図 19 (b) に示すように、赤色光を発光する有機 EL 素子について、正孔輸送層 18 a の膜厚を 25 nm に設定した場合には、CIE xy 色度座標は、CIE (0.688, 0.310) であり、膜厚を 110 nm に設定した場合には、CIE (0.426, 0.288) であった。

40

## 【0126】

このように、緑色光及び赤色光を発光する有機 EL 素子においても、上述した青色光を発光する有機 EL 素子の場合と同様に、正孔輸送層 18 a の膜厚に応じて発光色度が変化することが判明した。このことに基づいて、上述した図 16 (a) に示した素子構造を有する有機 EL 素子において、正孔輸送層 18 a の膜厚を適宜調整することにより、図 20 に示すように、CIE 色度図上で青色光、緑色光及び赤色光の最適な発光色度を設定することができた。

## 【0127】

具体的には、正孔輸送層 18 a の膜厚の一例として、青色光を発光する有機 EL 素子においては、90 nm に設定することにより色度座標を CIE (0.133, 0.083) に設定する

50

ことができ、緑色光を発光する有機EL素子においては、95 nmに設定することにより色度座標をCIE(0.179, 0.744)に設定することができ、赤色光を発光する有機EL素子においては、15 nmに設定することにより色度座標をCIE(0.691, 0.307)に設定することができた。これらは各々青(B)色、緑(G)色及び赤(R)色の各色度領域内の鮮明な発光色を示す座標にあって、青色発光、緑色発光及び赤色発光が良好に行われる事が判明した。

#### 【0128】

このように、本実施形態に係る表示装置及びその製造方法によれば、各発光色ごとに正孔輸送層を任意の膜厚に設定し、かつ、当該正孔輸送層を均一な膜厚で良好な平坦性を有して形成することができるので、発光点から出射される光の光学長を各発光色ごとに最適に調整することができ、干渉作用に基づく色度ずれや発光輝度のばらつきを抑制して、簡易に発光色の色度調節や発光強度の調整を行うことができる。よって、画像のにじみやぼけのない表示特性に優れた表示装置を実現することができる。10

#### 【0129】

また、図16～図19に示したように、有機EL層18を形成する特定の層(正孔輸送層)の膜厚を変化させることにより、CIE色度図上の任意の座標の発光色を実現することができる。例えは緑色光を発光する有機EL素子において、正孔輸送層の膜厚を調整することにより長波長領域の成分を干渉効果により強めて赤色光を発光させるように色調を変化させることができる。あるいは、特定の発光色を有する有機EL素子、例えは白色光を発光する有機EL素子において正孔輸送層の膜厚を調整することにより、同一色の発光層を有する有機EL素子において赤色光や緑色光、青色光を発光させるように色調を変化させることができる。20

#### 【0130】

なお、上述した実施形態においては、有機EL層18がRGBの各色ごとに膜厚の異なる正孔輸送層18aと、所定の膜厚を有する電子輸送性発光層18bからなり、正孔輸送層18aを形成するための有機化合物含有液としてPEDOT/PSSを適用し、電子輸送性発光層18bを形成するための有機化合物含有液としてポリフェニレンビニレン系ポリマーを含む発光材料溶液を適用した場合について説明したが、本発明はこれに限定されるものではない。すなわち、各色ごとに膜厚を異ならせる層は、上述した正孔輸送層18aに限定されるものではなく、発光点となる発光層から放射される光が透過する(すなわち光路上にある)層であれば、例えは図16(a)に示したインターレイヤ層18cや、正孔輸送層18aとインターレイヤ層18cの複数層に適用するものであってもよく、また、有機EL層18が例えは各色ごとに膜厚の異なる正孔輸送兼電子輸送性発光層のみを有するものや、正孔輸送性発光層と各色ごとに膜厚の異なる電子輸送層を有するものでもよく、各層間に上記のインターレイヤ層以外の担体輸送層が適宜介在するものであってもよい。さらに、有機EL層18を形成するための有機化合物含有液は、正孔輸送性材料や電子輸送性発光材料等を含む溶液であって、塗布可能なものであれば他の組成を有するものであっても良好に適用することができる。30

#### 【0131】

また、上述した実施形態においては、プリンタヘッドに設けられた唯一の吐出口から吐出される有機化合物含有液により、1回の走査により1ライン(列)分の塗布処理を実行する場合について説明したが、本発明はこれに限定されるものではなく、例えは单一のプリンタヘッドに複数ライン分のピッチ(間隔)で複数の吐出口を設け、例えは3ラインおきの複数のラインに対して有機化合物含有液を同時に吐出して塗布するものであってもよい。

#### 【0132】

また、上述した実施形態においては、画素電極15を有機EL素子のアノード電極とし、対向電極19をカソード電極として、画素電極15側に正孔輸送層18aを、また、対向電極19側に電子輸送性発光層18bを形成した場合について説明したが、本発明はこれに限定されるものではなく、画素電極15を有機EL素子のカソード電極とし、対向電

10

20

30

40

50

極 19 をアノード電極とするものであってもよい。この場合、画素電極 15 側に電子輸送性発光層 18 b を、また、対向電極 19 側に正孔輸送層 18 a を形成した素子構造となる。

### 【 0 1 3 3 】

また、上述した実施形態においては、発光層からの光を絶縁性基板を透過させることなく、絶縁性基板の一面側の視野側に出射するトップエミッショング型の発光構造を有する表示パネルについて説明したが、本発明はこれに限定されるものではなく、発光層からの光を絶縁性基板を透過させて、絶縁性基板の他面側の視野側に出射するボトムエミッショング型の発光構造を有するものであってもよい。この場合、画素電極は ITO 等の光透過特性を有する導電性材料により形成され、対向電極はアルミニウムやクロム等の光反射特性を有する導電性材料により形成されればよい。

### 【 図面の簡単な説明 】

#### 【 0 1 3 4 】

【図 1】本発明に係る表示装置に適用される表示パネルの画素配列状態の一例を示す概略平面図である。

【図 2】本発明に係る表示装置の表示パネルに 2 次元配列される各表示画素（発光素子及び画素駆動回路）の回路構成例を示す等価回路図である。

【図 3】本発明に係る表示装置（表示パネル）に適用可能な表示画素の一例を示す平面レイアウト図である。

【図 4】本実施形態に係る平面レイアウトを有する表示画素における IVA - IVA 線に沿った断面を示す概略断面図である。

【図 5】本実施形態に係る平面レイアウトを有する表示画素における VB - VB 線、VC - VC 線に沿った断面を示す概略断面図である。

【図 6】本実施形態に係る表示装置（表示パネル）の製造方法の一例を示す工程断面図（その 1）である。

【図 7】本実施形態に係る表示装置（表示パネル）の製造方法の一例を示す工程断面図（その 2）である。

【図 8】本実施形態に係る表示装置（表示パネル）の製造方法の一例を示す工程断面図（その 3）である。

【図 9】本実施形態に係る表示装置（表示パネル）の製造方法の一例を示す工程断面図（その 4）である。

【図 10】本実施形態に係る表示装置（表示パネル）の製造方法の一例を示す工程断面図（その 5）である。

【図 11】本実施形態に係る表示装置（表示パネル）の製造方法における正孔輸送層の成膜プロセスを説明するための概念図（その 1）である。

【図 12】本実施形態に係る表示装置（表示パネル）の製造方法における正孔輸送層の成膜プロセスを説明するための概念図（その 2）である。

【図 13】本実施形態に係る表示装置（表示パネル）の製造方法における電子輸送性発光層の成膜プロセスを説明するための概念図（その 1）である。

【図 14】本実施形態に係る表示装置（表示パネル）の製造方法における電子輸送性発光層の成膜プロセスを説明するための概念図（その 2）である。

【図 15】本実施形態に係る表示装置の製造方法（有機 EL 層の成膜プロセス）における作用効果の検証結果を示す概略図である。

【図 16】本実施形態に係る表示装置（表示パネル）に形成される有機 EL 素子の素子構造の一例（実験モデル）を示す模式図、及び、干渉効果を説明するための概略図である。

【図 17】本実施形態に係る表示装置（表示パネル）に形成される青色光を発光する有機 EL 素子における、正孔輸送層の膜厚と色度との関係を示す色度図（その 1）である。

【図 18】本実施形態に係る表示装置（表示パネル）に形成される青色光を発光する有機 EL 素子における、正孔輸送層の膜厚と色度との関係を示す色度図（その 2）である。

【図 19】本実施形態に係る表示装置（表示パネル）に形成される緑色光及び赤色光を発

10

20

30

40

50

光する有機EL素子における、正孔輸送層の膜厚と色度との関係を示す色度図である。

【図20】本実施形態に係る表示装置(表示パネル)に形成される有機EL素子における、正孔輸送層の膜厚と発光色度との関係を示す色度図である。

【符号の説明】

【0135】

|         |          |    |

|---------|----------|----|

| 1 0     | 表示パネル    |    |

| 1 1     | 絶縁性基板    |    |

| 1 2     | ゲート絶縁膜   |    |

| 1 3     | 保護絶縁膜    | 10 |

| 1 4     | 平坦化膜     |    |

| 1 5     | 画素電極     |    |

| 1 6     | 層間絶縁膜    |    |

| 1 7     | バンク      |    |

| 1 8     | 有機EL層    |    |

| 1 8 a   | 正孔輸送層    |    |

| 1 8 b   | 電子輸送性発光層 |    |

| 1 9     | 対向電極     |    |

| D C     | 画素駆動回路   |    |

| O L E D | 有機EL素子   | 20 |

| L s     | 選択ライン    |    |

| L v     | 電源電圧ライン  |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

〔 図 9 〕

【 四 8 】

【図10】

【図11】

(a)

(b)

【図12】

(a)

(b)

【図13】

(a)

(b)

【図14】

(a)

(b)

【図15】

【図16】

【図17】

【図19】

【図20】

---

フロントページの続き

(56)参考文献 特開平09-045477(JP,A)

特開2007-294421(JP,A)

特開2005-209421(JP,A)

特開2006-253015(JP,A)

特開2003-142277(JP,A)

特開2007-027042(JP,A)

特開2006-269327(JP,A)

特開2005-317255(JP,A)

特開2002-370352(JP,A)

特開2007-305505(JP,A)

特開2007-026684(JP,A)

特開2008-091323(JP,A)

特表2008-503871(JP,A)

国際公開第2006/009612(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 51/50-51/56

H05B 33/00-33/28

|                |                                                                                                                           |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置的制造方法                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP4725577B2</a>                                                                                               | 公开(公告)日 | 2011-07-13 |

| 申请号            | JP2007340226                                                                                                              | 申请日     | 2007-12-28 |

| [标]申请(专利权)人(译) | 卡西欧计算机株式会社                                                                                                                |         |            |

| 申请(专利权)人(译)    | 卡西欧计算机有限公司                                                                                                                |         |            |

| 当前申请(专利权)人(译)  | 卡西欧计算机有限公司                                                                                                                |         |            |

| [标]发明人         | 木津貴志<br>田野朋子                                                                                                              |         |            |

| 发明人            | 木津 貴志<br>田野 朋子                                                                                                            |         |            |

| IPC分类号         | H01L51/50 H05B33/10 H05B33/12                                                                                             |         |            |

| CPC分类号         | H01L51/0005 G09G3/3233 G09G3/3291 G09G2300/0842 H01L27/3211 H01L27/3246 H01L27/3276<br>H01L51/0037 H01L51/56 H01L2251/558 |         |            |

| FI分类号          | H05B33/22.C H05B33/10 H05B33/12.B H05B33/14.A H05B33/22.A H01L27/32                                                       |         |            |

| F-TERM分类号      | 3K107/BB01 3K107/CC07 3K107/CC31 3K107/CC33 3K107/DD60 3K107/DD74 3K107/DD78 3K107/EE03 3K107/FF15 3K107/GG06             |         |            |

| 其他公开文献         | JP2009164236A                                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                 |         |            |

## 摘要(译)

要解决的问题：提供一种抑制色度偏差和发光亮度（发光强度）变化的显示单元，并且具有优异的显示特性而不会出现图像的渗色和模糊，并提供显示单元的制造方法。ŽSOLUTION：在由具有至少空穴传输层18a和电子传输发光层18b作为有机EL层（发光功能层）18的元件结构形成的有机EL元件OLED中，空穴传输层的膜厚度形成在像素电极15上的图18a适当地调整为显示面板中R，G和B的各个颜色像素PXr，PXg和PXb的不同的指定膜厚度。因此，在CIE色度图上设置红光，绿光和蓝光的最佳发光色度。Ž

【図 1】