(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-43021

(P2015-43021A)

(43) 公開日 平成27年3月5日(2015.3.5)

|           |                                          |            |                                                                                                                                  |

|-----------|------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2013-174364 (P2013-174364)             | (71) 出願人   | 502356528<br>株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目7番1号                                                                                   |

| (22) 出願日  | 平成25年8月26日 (2013.8.26)                   | (74) 代理人   | 110000408<br>特許業務法人高橋・林アンドパートナーズ                                                                                                 |

| (72) 発明者  | 中村 智樹<br>東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内 | F ターム (参考) | 3K107 AA01 BB01 CC33 DD01 DD03<br>DD38 DD39 HH04<br>5C080 AA06 BB05 DD05 DD22 EE25<br>EE29 FF02 FF11 HH09 JJ02<br>JJ03 JJ04 JJ06 |

(54) 【発明の名称】 表示装置

(57) 【要約】

【課題】トップエミッショ n 型の有機 E L 表示パネルを使用する表示装置において、シェーディングが発生するのを防止する。

【解決手段】各画素は、第1の有機EL素子と第2の有機EL素子とから成る一对の有機EL素子を少なくとも一对有する表示装置であって、基板と、前記基板上に形成され、前記各画素の画素回路が形成される画素回路部と、前記画素回路部上に形成され、前記各画素の前記少なくとも一对の有機EL素子が形成される素子形成部と、前記素子形成部上に形成される誘電体層と、前記誘電体層上に形成される透明導電膜と、交流駆動電圧源とを有し、前記素子形成部に形成される前記少なくとも一对の有機EL素子における前記第1の有機EL素子と前記第2の有機EL素子は、互いに並列で、ダイオード特性が互いに逆方向になるように接続され、点灯期間に、前記少なくとも一对の有機EL素子に対して、前記交流駆動電圧源から交流駆動電圧を印加する。

1

### 【選択図】

1

## 【特許請求の範囲】

## 【請求項 1】

マトリクス状に配置された複数の画素を有し、

前記各画素は、第1の有機EL素子と第2の有機EL素子とから成る一対の有機EL素子を少なくとも一対有する表示装置であって、

基板と、

前記基板上に形成され、前記各画素の画素回路が形成される画素回路部と、

前記画素回路部上に形成され、前記各画素の前記少なくとも一対の有機EL素子が形成される素子形成部と、

前記素子形成部上に形成される誘電体層と、

前記誘電体層上に形成される導電膜と、

交流駆動電圧源とを有し、

前記素子形成部に形成される前記少なくとも一対の有機EL素子における前記第1の有機EL素子と前記第2の有機EL素子は、互いに並列で、ダイオード特性が互いに逆方向になるように接続され、

点灯期間に、前記少なくとも一対の有機EL素子に対して、前記交流駆動電圧源から交流駆動電圧を印加することを特徴とする表示装置。

## 【請求項 2】

マトリクス状に配置された複数の画素を有し、

前記各画素は、第1の有機EL素子と第2の有機EL素子とから成る一対の有機EL素子を少なくとも一対有する表示装置であって、

基板と、

前記基板上に形成され、前記各画素の画素回路が形成される画素回路部と、

前記画素回路部上に形成され、前記各画素の前記少なくとも一対の有機EL素子が形成される素子形成部と、

前記素子形成部上に形成される誘電体層と、

前記誘電体層上に形成される導電膜と、

交流駆動電圧源とを有し、

前記素子形成部に形成される前記少なくとも一対の有機EL素子における前記第1の有機EL素子と前記第2の有機EL素子は、互いに並列に接続され、

前記第1の有機EL素子は、アノード電極として機能する第1の下部電極と、カソード電極として機能する第1の上部電極と、前記第1の下部電極と、前記第1の上部電極との間に挟持される有機層とで構成され、

前記第2の有機EL素子は、カソード電極として機能する第2の下部電極と、アノード電極として機能する第2の上部電極と、前記第2の下部電極と、前記第2の上部電極との間に挟持される有機層とで構成され、

前記各画素の前記画素回路は、第2電極が前記第1および第2の下部電極に接続される駆動トランジスタを有し、

前記交流駆動電圧源は、前記各画素の前記駆動トランジスタの第1電極と、前記導電膜との間に接続され、

点灯期間に、前記各画素の前記駆動トランジスタをオンとして、前記少なくとも一対の有機EL素子に対して、前記交流駆動電圧源から交流駆動電圧を印加することを特徴とする表示装置。

## 【請求項 3】

前記第1の上部電極と前記第2の上部電極、および、前記第1の下部電極と前記第2の下部電極の少なくとも一方は、共通の電極で構成されることを特徴とする請求項2に記載の表示装置。

## 【請求項 4】

前記各画素の前記画素回路には、データ線と、リセット線と、走査線と、消去線とが入力され、

10

20

30

40

50

前記各画素の前記画素回路は、一端が前記駆動トランジスタのゲートに接続される容量素子と、

ゲートが前記リセット線に接続されるとともに、前記駆動トランジスタのゲートと前記駆動トランジスタの第2電極との間に接続される第1トランジスタと、

ゲートが前記走査線に接続されるとともに、前記容量素子の他端と前記データ線との間に接続される第2トランジスタと、

ゲートが前記消去線に接続されるとともに、前記容量素子の他端と接地電位との間に接続される第3トランジスタとを有することを特徴とする請求項2または請求項3に記載の表示装置。

【請求項5】

1フレームは、複数のサブフィールドに分割されており、

前記各サブフィールドは、書込期間と、点灯期間とを有し、

前記点灯期間は、前記各サブフィールド毎に異なっていることを特徴とする請求項1ないし請求項4のいずれか1項に記載の表示装置。

【請求項6】

前記各画素の前記画素回路には、データ線と、リセット線と、走査線と、消去線とが入力され、

前記各画素の前記画素回路は、一端が前記駆動トランジスタのゲートに接続される容量素子と、

ゲートが前記リセット線に接続されるとともに、前記駆動トランジスタのゲートと前記駆動トランジスタの第2電極との間に接続される第1トランジスタと、

ゲートが前記走査線に接続され、第1電極が前記容量素子の他端に接続されるとともに、第2電極に一定の電圧が印加される第2トランジスタと、

前記容量素子の他端と接地電位との間に接続される第3トランジスタと第4トランジスタの直列回路を有し、

前記第4トランジスタのゲートは、前記データ線に接続され、

前記第3トランジスタのゲートは、前記消去線に接続されることを特徴とする請求項2または請求項3に記載の表示装置。

【請求項7】

前記各画素の前記画素回路には、データ線と、リセット線と、走査線と、消去線とが入力され、

前記各画素の前記画素回路は、一端が前記駆動トランジスタのゲートに接続されるとともに、他端が前記走査線に接続される容量素子と、

ゲートが前記リセット線に接続されるとともに、前記駆動トランジスタのゲートと前記駆動トランジスタの第2電極との間に接続される第1トランジスタと、

前記容量素子の他端と接地電位との間に接続される第2トランジスタと第3トランジスタの直列回路を有し、

前記第2トランジスタのゲートは、前記データ線に接続され、

前記第3トランジスタのゲートは、前記消去線に接続されることを特徴とする請求項2または請求項3に記載の表示装置。

【請求項8】

1フレームは、書込期間と、複数の点灯期間とに分割されており、

前記少なくとも一対の有機EL素子が点灯する点灯期間の個数が、表示される画像の階調に応じて異なっていることを特徴とする請求項1、または、請求項2、または、請求項3、または、請求項6、または請求項7に記載の表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置に係わり、特に、トップエミッഷン型の有機EL表示パネルを採用する有機EL表示装置に適用して有効な技術に関する。

10

20

30

40

50

## 【背景技術】

## 【0002】

近年、フラットディスプレイ装置の需要が増大している。特に、有機EL(Electro Luminescence)素子(OLED; Organic Light Emitting Diode)を用いた有機EL表示パネルは、消費電力、軽さ、薄さ、動画特性、視野角などの点で優れており、開発、実用化も進んでいる。有機EL表示パネルは、電流駆動素子であり、直流電流で駆動するのが一般的である。

これに対して、下記特許文献1には、並列に一対の有機EL素子を設け、一対の有機EL素子の一方の有機EL素子のアノードを、他方の有機EL素子のカソードに接続するとともに、一対の有機EL素子の一方の有機EL素子のカソードを、他方の有機EL素子のアノードに接続し、当該一対の有機EL素子を、高周波誘導電流で駆動して発光させることが記載されている。

10

## 【先行技術文献】

## 【特許文献】

## 【0003】

## 【特許文献1】特許第4473472号明細書

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0004】

トップエミッション型の有機EL表示パネルでは、有機EL素子の色度視角対策でキャビティレス構造を採用すると、カソード電極の抵抗値が高いことによるシェーディングが発生するという問題点がある。

20

本発明は、前記従来技術の問題点を解決するためになされたものであり、本発明の目的は、トップエミッション型の有機EL表示パネルを使用する表示装置において、シェーディングが発生するのを防止することが可能となる技術を提供することにある。

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

## 【課題を解決するための手段】

## 【0005】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記の通りである。

30

(1)マトリクス状に配置された複数の画素を有し、前記各画素は、第1の有機EL素子と第2の有機EL素子とから成る一対の有機EL素子を少なくとも一対有する表示装置であって、基板と、前記基板上に形成され、前記各画素の画素回路が形成される画素回路部と、前記画素回路部上に形成され、前記各画素の前記少なくとも一対の有機EL素子が形成される素子形成部と、前記素子形成部上に形成される誘電体層と、前記誘電体層上に形成される透明導電膜と、交流駆動電圧源とを有し、前記素子形成部に形成される前記少なくとも一対の有機EL素子における前記第1の有機EL素子と前記第2の有機EL素子は、互いに並列で、ダイオード特性が互いに逆方向になるように接続され、点灯期間に、前記少なくとも一対の有機EL素子に対して、前記交流駆動電圧源から交流駆動電圧を印加する。

40

## 【0006】

(2)マトリクス状に配置された複数の画素を有し、前記各画素は、第1の有機EL素子と第2の有機EL素子とから成る一対の有機EL素子を少なくとも一対有する表示装置であって、基板と、前記基板上に形成され、前記各画素の画素回路が形成される画素回路部と、前記画素回路部上に形成され、前記各画素の前記少なくとも一対の有機EL素子が形成される素子形成部と、前記素子形成部上に形成される誘電体層と、前記誘電体層上に形成される透明導電膜と、交流駆動電圧源とを有し、前記素子形成部は、下部電極と、上部電極と、前記下部電極と前記上部電極とに挟持される有機層とを有し、前記各画素の前記画素回路は、第2電極が前記下部電極に接続される駆動トランジスタを有し、前記交流駆

50

動電圧源は、前記各画素の前記駆動トランジスタの第1電極と、前記透明導電膜との間に接続され、前記素子形成部に形成される前記少なくとも一対の有機EL素子における前記第1の有機EL素子と前記第2の有機EL素子は、互いに並列に接続され、前記第1の有機EL素子は、前記下部電極がアノード電極として機能するとともに、前記上部電極がカソード電極として機能し、前記第2の有機EL素子は、前記上部電極がアノード電極として機能するとともに、前記下部電極がカソード電極として機能し、点灯期間に、前記各画素の前記駆動トランジスタをオンとして、前記少なくとも一対の有機EL素子に対して、前記交流駆動電圧源から交流駆動電圧を印加する。

【発明の効果】

【0007】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。

本発明によれば、トップエミッション型の有機EL表示パネルを使用する表示装置において、シェーディングが発生するのを防止することが可能となる。

【画面の簡単な説明】

【0008】

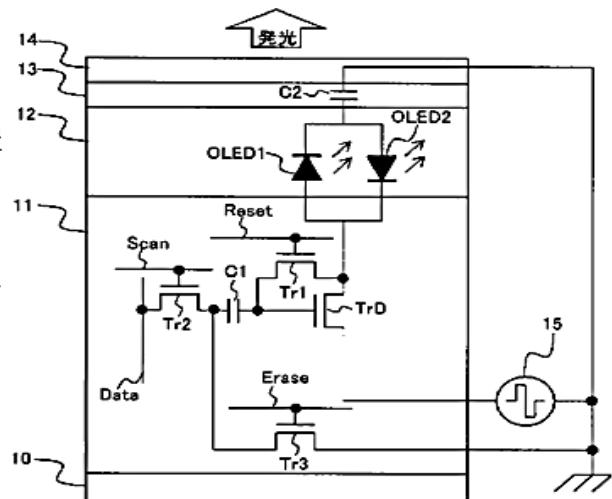

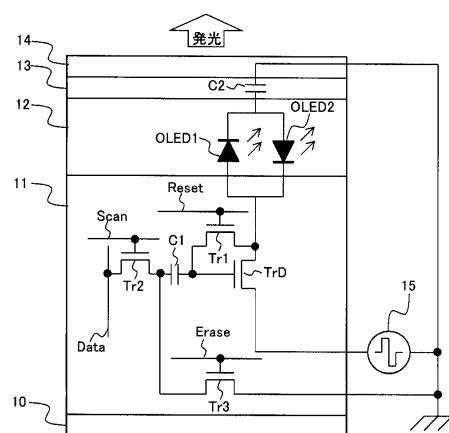

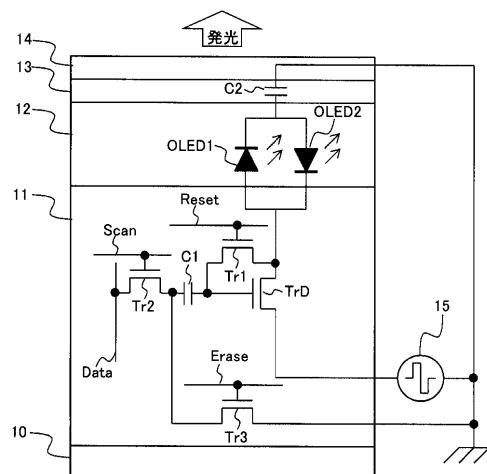

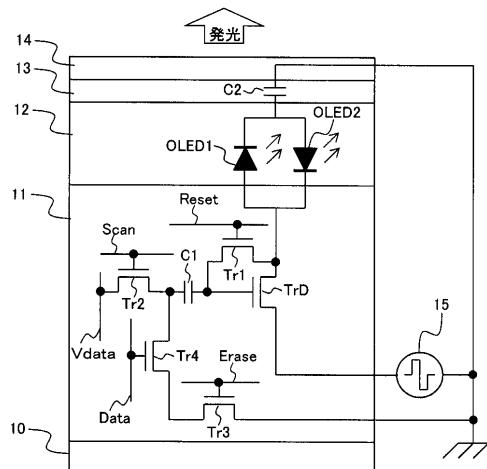

【図1】本発明の実施例1の有機EL表示装置の画素構造と、画素回路の回路構成を示す図である。

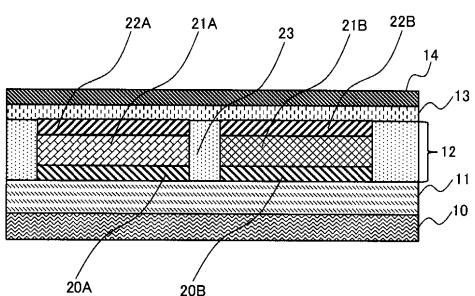

【図2】本発明の実施例1の有機EL表示装置の画素構造の一例を示す図である。

【図3】本発明の実施例1の有機EL表示装置の画素構造の他の例を示す図である。

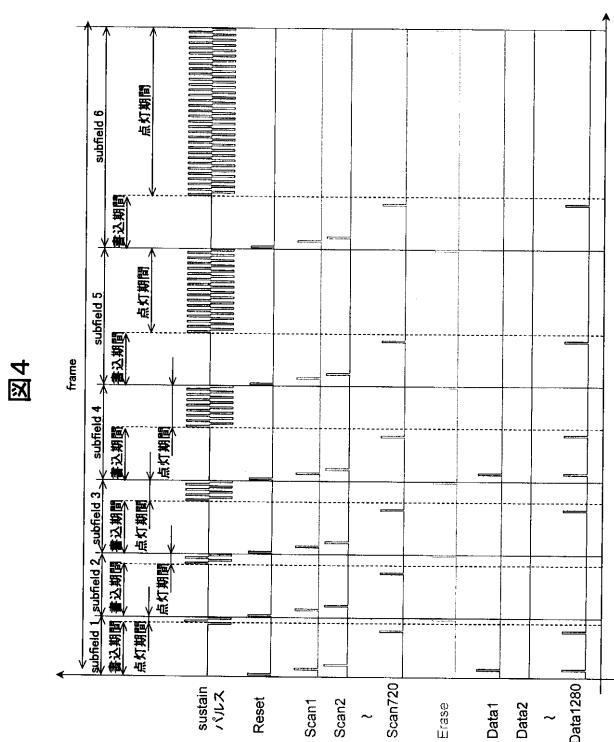

【図4】本発明の実施例1の有機EL表示装置の駆動方法を説明するための図である。

【図5】本発明の実施例2の有機EL表示装置の画素構造と、画素回路の回路構成を示す図である。

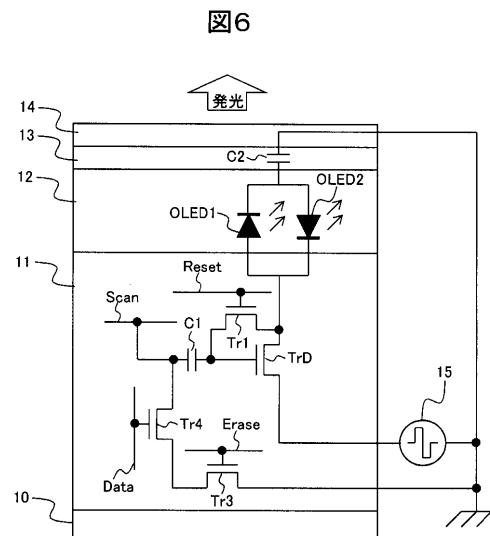

【図6】本発明の実施例2の有機EL表示装置の変形例の画素構造と、画素回路の回路構成を示す図である。

【図7】本発明の実施例2の有機EL表示装置の駆動方法を説明するための図である。

【発明を実施するための形態】

【0009】

以下、図面を参照して本発明の実施例を詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。また、以下の実施例は、本発明の特許請求の範囲の解釈を限定するためのものではない。

図1は、本発明の実施例1の有機EL表示装置の画素構造と、画素回路の回路構成を示す図である。

本実施例の有機EL表示装置は、マトリクス状に配置された複数の画素（または、サブピクセル）を有する。これらの画素は、有機EL表示パネル上に形成される。

図1に示すように、有機EL表示パネルは、基板10と、基板10上に形成される画素回路部11と、画素回路部11上に形成される素子形成部12と、素子形成部12上に形成される誘電体膜13と、誘電体膜13上に形成される陰極配線部14とを有する。

画素回路部11と素子形成部12とは、各画素毎に形成され、誘電体膜13と陰極配線部14とは、各画素に共通に形成される。なお、陰極配線部14は、例えば、ITO (Indium Tin Oxide) 等の透明導電膜で構成される。

図1に示すように、各画素の素子形成部12には、有機EL素子が形成されるが、本実施例では、各画素の素子形成部12には、少なくとも一対の有機EL素子（OLED1, OLED2）が形成される。

ここで、素子形成部12に形成される、少なくとも一対の有機EL素子（OLED1）と有機EL素子（OLED2）は、互いに並列で、ダイオード特性が互いに逆方向になるように接続される。

【0010】

図1に示すように、各画素の画素回路には、データ線（Data）と、走査線（Scan）

10

20

30

40

50

n )と、リセット線 ( R e s e t )と、消去線 ( E r a s e )とが入力される。

各画素の画素回路は、駆動トランジスタ ( T r D )と、駆動トランジスタ ( T r D )のドレイン ( または、ソース )とゲートとの間に接続されるスイッチングトランジスタ ( T r 1 )と、駆動トランジスタ ( T r D )のゲートとデータ線 ( D a t a )との間に接続されるスイッチングトランジスタ ( T r 2 )と容量素子 ( C 1 )の直列回路と、スイッチングトランジスタ ( T r 2 )と容量素子 ( C 1 )の接続点に、基準電圧 ( G N D )を入力するスイッチングトランジスタ ( T r 3 )とを有する。

ここで、スイッチングトランジスタ ( T r 1 )のゲートは、リセット線 ( R e s e t )に接続され、スイッチングトランジスタ ( T r 2 )のゲートは、走査線 ( S c a n )に接続され、スイッチングトランジスタ ( T r 3 )のゲートは、消去線 ( E r a s e )に接続される。

陰極配線部 1 4 は、誘電体膜 1 3 を介して、一対の有機 E L 素子 ( O L E D 1 , O L E D 2 )と対向している。したがって、有機 E L 素子 ( O L E D 1 )のアノードと、有機 E L 素子 ( O L E D 2 )のカソードは、容量素子 ( C 2 )を介して、陰極配線部 1 4 と接続される。

#### 【 0 0 1 1 】

駆動トランジスタ ( T r D )のソース ( または、ドレイン )は、交流駆動電圧源 1 5 の一方の端子に接続され、交流駆動電圧源 1 5 の他方の端子は、陰極配線部 1 4 に接続される。

交流駆動電圧源 1 5 は、点灯期間に、 s u s t a i n パルスを全画素に印加し、駆動トランジスタ ( T r D )がオンの画素のみ、駆動トランジスタ ( T r D ) 有機 E L 素子 ( O L E D 1 )、あるいは、有機 E L 素子 ( O L E D 2 ) 駆動トランジスタ ( T r D )の経路で、交流電流が流れ、有機 E L 素子 ( O L E D 1 )と、有機 E L 素子 ( O L E D 2 )が発光する。

このとき、一対の有機 E L 素子 ( O L E D 1 )と有機 E L 素子 ( O L E D 2 )とは、互いに並列で、ダイオード特性が互いに逆方向になるように接続されているため、画素回路側が正となる電圧の時でも、陰極配線部 1 4 側が正となる電圧の場合でも、一対の有機 E L 素子 ( O L E D 1 )と有機 E L 素子 ( O L E D 2 )とは発光する。

#### 【 0 0 1 2 】

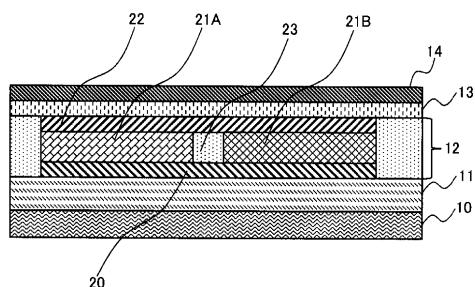

図 2 は、本発明の実施例 1 の有機 E L 表示装置の画素構造の一例を示す図である。

図 2 に示すように、図 1 の素子形成部 1 2 は、各画素毎に、電極 2 0 と、有機層 A ( 2 1 A )と、有機層 B ( 2 1 B )と、電極 2 2 とで構成される。なお、電極 2 0 と、有機層 A ( 2 1 A )と、有機層 B ( 2 1 B )と、電極 2 2 とは、周囲は誘電体層 2 3 で覆われている。

電極 2 0 と、有機層 A ( 2 1 A )と、電極 2 2 とが、有機 E L 素子 ( O L E D 1 )を構成し、電極 2 0 と、有機層 B ( 2 1 B )と、電極 2 2 とが、有機 E L 素子 ( O L E D 2 )を構成する。

したがって、有機 E L 素子 ( O L E D 1 )において、電極 2 0 がアノード電極を構成し、電極 2 2 がカソード電極を構成し、有機 E L 素子 ( O L E D 2 )において、電極 2 2 がアノード電極を構成し、電極 2 0 がカソード電極を構成する。

有機層 A ( 2 1 A )、および、有機層 B ( 2 1 B )は、発光層のみの単一層構造、又は有機正孔輸送層と発光層から成る 2 層構造、或いは有機正孔輸送層と発光層及び有機電子輸送層から成る 3 層構造、さらには、これらの適当な層間に電子又は正孔の注入層やキャリアブロック層を挿入した複数の層からなる積層構造で構成される。

図 2 の電極 2 0 は、図 1 の駆動トランジスタ ( T r D )のドレイン ( またはソース )に接続され、図 2 の電極 2 2 と、誘電体膜 1 3 と、陰極配線部 1 4 とは、容量素子 ( C 2 )を形成する。

#### 【 0 0 1 3 】

図 3 は、本発明の実施例 1 の有機 E L 表示装置の画素構造の他の例を示す図である。

図 2 では、電極 2 0 は、有機 E L 素子 ( O L E D 1 )と有機 E L 素子 ( O L E D 2 )に

対して共通に形成したが、図3では、電極20を、有機EL素子(OLED1)用の電極(20A)と、有機EL素子(OLED2)用の電極(20B)に分離し、それぞれ個別に形成したものである。

同様に、電極22も、有機EL素子(OLED1)用の電極(22A)と、有機EL素子(OLED2)用の電極(22B)に分離し、それぞれ個別に形成したものである。

図3では、有機EL素子(OLED1)において、電極(20A)がアノード電極を構成し、電極(22A)がカソード電極を構成し、有機EL素子(OLED2)において、電極(22B)がアノード電極を構成し、電極(20A)がカソード電極を構成する。

図3の電極(20A)と電極(20B)とは、図1の駆動トランジスタ(TrD)のドレイン(またはソース)に接続され、図3の電極(22A)および電極(22B)と、誘電体膜13と、陰極配線部14とは、容量素子(C2)を形成する。

なお、本実施例において、図2に示す電極20、あるいは、電極22の一方を、図3に示すように、有機EL素子(OLED1)用と、有機EL素子(OLED2)用の電極に分離し、それぞれ個別に形成してもよい。

#### 【0014】

本実施例では、サブフィールド法により、有機EL表示パネルに表示される画像の階調を制御する。

図4は、本発明の実施例1の有機EL表示装置の駆動方法を説明するための図である。

本実施例は、サブフィールド法を用いて階調表示する場合の印加電圧を示す図である。

図4では、1280(データ線)×720(走査線)個の画素の有機EL表示パネルを、1フレーム(Frame)を6つのサブフィールドに分けて、点灯時間を制御することにより6ビットの階調表示(64階調表示)を行う例を示している。なお、サブフィールドは、より点灯時間の長いサブフィールドを複数のサブフィールドに分割することも出来る。

各サブフィールドは、書き込み期間と点灯期間に大別される。

書き込み期間の動作は以下のようになる。

(1)全画素のリセット線(Reset)に、Resetパルスを印加して、駆動トランジスタ(TrD)の0点補正を行う。

即ち、全画素のリセット線(Reset)に、Resetパルスを印加して、スイッチングトランジスタ(Tr1)をオンとして、駆動トランジスタ(TrD)をダイオード接続とした後、スイッチングトランジスタ(Tr1)をオフとして、駆動トランジスタ(TrD)のゲート電圧を閾値電圧とする。

(2)走査線(Scan)に、順次、走査パルス(Scanパルス)を印加して、スイッチングトランジスタ(Tr2)をオンとするとともに、当該サブフィールドで点灯させる画素のデータ線(Data)に、Dataパルスを印加して、容量素子(C1)を充電する。これにより、当該サブフィールドで点灯させる画素の駆動トランジスタ(TrD)がオン状態となる。

(3)前述した動作を、書き込み期間中に全画素に対して行う。

点灯期間には、全画素に対して、交流駆動電圧源15からsustainパルスを印加し、駆動トランジスタ(TrD)がオンとなった画素の、有機EL素子(OLED1)と、有機EL素子(OLED2)のみが発光する。

点灯期間終了後、全画素の消去線(Erase)に、Eraseパルスを印加し、全画素の容量素子(C1)の電荷を放電して、点灯期間を終了する。

その後、次のサブフィールドの動作に移る。

#### 【0015】

前述したように、トップエミッション型の有機EL表示パネルにおいて、色度視角対策でキャビティレス構造をとると、カソード電極の抵抗値が高いことによるシェーディングが発生する。

本実施例では、一つの画素に、有機EL素子(OLED1)と有機EL素子(OLED2)を、互いに並列で、ダイオード特性が互いに逆方向になるように配置する。そして、

電極 20 には直接給電し、電極 22 は誘電体膜 13 を介して陰極配線部 14 に接続する。

したがって、本実施例では、陰極配線部 14 と、有機 EL 素子 (OLED1, OLED2) との直接オーミックコンタクトが不要であるので、独立した製造プロセスで陰極配線部 14 を形成できるので、陰極配線部 14 の抵抗値を下げることが可能となる。

これにより、陰極配線部 14 の抵抗値による輝度シェーディングのない中型の有機 EL 表示パネル、あるいは、小画面のモバイル製品で、高効率でかつ色度視角の特性の良い薄型の有機 EL 表示パネルを実現することが可能となる。

#### 【0016】

図 5 は、本発明の実施例 2 の有機 EL 表示装置の画素構造と、画素回路の回路構成を示す図である。

本実施例の有機 EL 表示装置は、画素構造は、前述の実施例 1 と同じであるが、画素回路の構成が、前述の実施例 1 と相違する。

図 5 に示すように、本実施例では、スイッチングトランジスタ (Tr2) と容量素子 (C1) の接続点と、スイッチングトランジスタ (Tr3) との間にスイッチングトランジスタ (Tr4) が接続される。

このスイッチングトランジスタ (Tr4) のゲートは、データ線 (Data) に接続される。そのため、スイッチングトランジスタ (Tr2) のドレイン (または、ソース) には、一定電位の電圧 (Vdata) が入力される。

図 5 において、走査線 (Scan) のインピーダンスが高い場合は、図 6 に示すように、スイッチングトランジスタ (Tr2) を省略することも可能である。

なお、図 6 は、本発明の実施例 2 の有機 EL 表示装置の変形例の画素構造と、画素回路の回路構成を示す図である。

図 6 に示す画素回路は、スイッチングトランジスタ (Tr2) を省略して、容量素子 (C1) の他端 (駆動トランジスタ (TrD) のゲートに接続される側と反対側の一端) を、走査線 (Scan) に接続して、容量素子 (C1) に他端に、一定電位の電圧 (Vdata) を印加するようにしたものである。

#### 【0017】

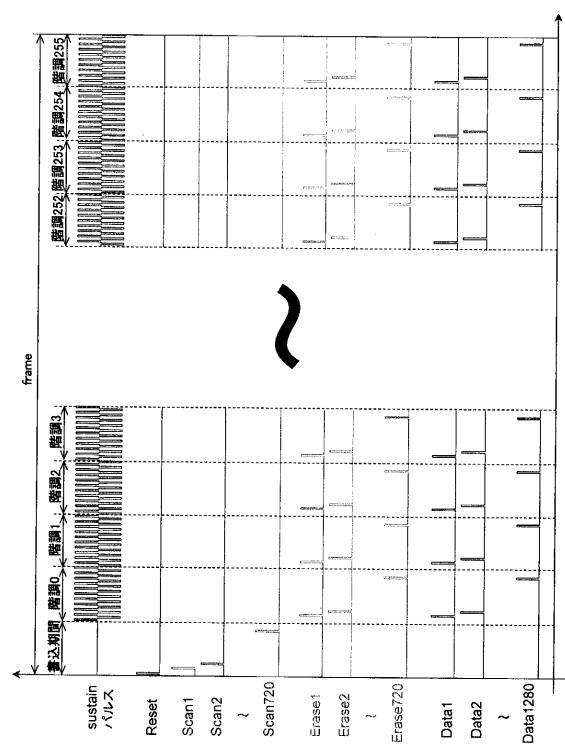

図 7 は、本発明の実施例 2 の有機 EL 表示装置の駆動方法を説明するための図である。

図 7 では、1280 (データ線) × 720 (走査線) 個の画素の有機 EL 表示パネルで、256 階調を表示を行う場合の印加電圧を示している。

本実施例では、フレーム (Frame) は、1 個の書込期間と、256 個の点灯期間に分割される。

書込期間の動作は以下のようになる。

(1) 全画素のリセット線 (Reset) に、Reset パルスを印加して、駆動トランジスタ (TrD) の 0 点補正を行う。

即ち、全画素のリセット線 (Reset) に、Reset パルスを印加して、スイッチングトランジスタ (Tr1) をオンとして、駆動トランジスタ (TrD) をダイオード接続とした後、スイッチングトランジスタ (Tr1) をオフとして、駆動トランジスタ (TrD) のゲート電圧を閾値電圧とする。

(2) 画素回路の構成が、図 5 の場合は、走査線 (Scan) に、順次、走査パルス (Scan パルス) を印加して、スイッチングトランジスタ (Tr2) をオンとして、画素の容量素子 (C1) に、一定電位の電圧 (Vdata) を印加して、全ての画素の容量素子 (C1) を充電する。これにより、全ての画素の駆動トランジスタ (TrD) がオン状態となる。

なお、走査線 (Scan) に、順次、走査パルス (Scan パルス) を印加する代わりに、全ての走査線 (Scan) に走査パルス (Scan パルス) を一度に印加して、全ての画素の容量素子 (C1) を一括して充電するようにしてもよい。

また、画素回路の構成が、図 6 の場合は、走査線 (Scan) に、順次、一定電位の電圧 (Vdata) を印加し、あるいは、全ての走査線 (Scan) に、一定電位の電圧 (Vdata) を一括して印加し、全ての画素の容量素子 (C1) を充電する。

10

20

30

40

50

## 【0018】

(1) 点灯期間には、全画素に対して、交流駆動電圧源15からsustainパルスが印加されるので、全画素の有機EL素子(OLED1)と、有機EL素子(OLED2)が発光する。

(2) 低階調側から各階調毎に消去線(Erase)に、順次、Eraseパルスを印加する。この際、当該階調で消灯させる画素のデータ線(Data)に、Dataパルスを印加する。

これにより、当該階調で消灯させる画素の容量素子(C1)が放電され、駆動トランジスタ(TrD)がオフ状態となるので、当該階調で消灯させる画素の有機EL素子(OLED1)と、有機EL素子(OLED2)が消灯する。

前述した動作を、256階調毎に順次実行して、256階調の画素が消灯したのちに、次のフレームとなる。これにより、PWM方式に相当する駆動が可能となる。

本実施例においても、陰極配線部14と、有機EL素子(OLED1, OLED2)との直接オーミックコンタクトが不要であるので、独立した製造プロセスで陰極配線部14を形成できるので、陰極配線部14の抵抗値を下げることが可能となる。

これにより、陰極配線部14の抵抗値による輝度シェーディングのない中型の有機EL表示パネル、あるいは、小画面のモバイル製品で、高効率でかつ色度視角の特性の良い薄型の有機EL表示パネルを実現することが可能となる。

以上、本発明者によってなされた発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

## 【符号の説明】

## 【0019】

10 基板

11 画素回路部

12 素子形成部

13, 23 誘電体膜

14 陰極配線部

15 交流駆動電圧源

20, 20A, 20B, 22, 22A, 22B 電極

21A 有機層A

21B 有機層B

OLED1, OLED2 有機EL素子

Data データ線

Scan 走査線

Reset リセット線

Erase 消去線

TrD 駆動トランジスタ

Tr1~Tr4 スイッチングトランジスタ

C1, C2 容量素子

10

20

30

40

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

【図7】

## フロントページの続き

| (51) Int.Cl.  |       | F I       |        | テーマコード(参考)   |

|---------------|-------|-----------|--------|--------------|

| <i>H 05 B</i> | 33/26 | (2006.01) | G 09 G | 3/20 6 4 1 B |

| <i>H 05 B</i> | 33/06 | (2006.01) | G 09 G | 3/20 6 4 1 K |

| <i>H 05 B</i> | 33/12 | (2006.01) | G 09 G | 3/20 6 1 1 J |

|               |       |           | G 09 G | 3/20 6 4 2 A |

|               |       |           | H 05 B | 33/14 A      |

|               |       |           | H 05 B | 33/08        |

|               |       |           | H 05 B | 33/22 Z      |

|               |       |           | H 05 B | 33/26 Z      |

|               |       |           | H 05 B | 33/06        |

|               |       |           | H 05 B | 33/12 B      |

F ターム(参考) 5C380 AA01 AB06 AB08 AB11 AB15 AB46 AC05 BA19 BA20 BB02

BB05 CA14 CB01 CB16 CB17 CB31 CC04 CC21 CC27 CC33

CC34 CC37 CC38 CC41 CC61 CC64 CC71 CD014 CD015 CD024

CD025 CE04 CE14 CE20 DA02 DA07 DA08 DA09 DA15 DA16

DA35 DA47

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2015043021A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2015-03-05 |

| 申请号            | JP2013174364                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2013-08-26 |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | 有限公司日本显示器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 中村智樹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 中村 智樹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 H05B33/08 H05B33/22 H05B33/26 H05B33/06 H05B33/12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.612.F G09G3/20.641.E G09G3/20.641.A G09G3/20.641.B G09G3/20.641.K G09G3/20.611.J G09G3/20.642.A H05B33/14.A H05B33/08 H05B33/22.Z H05B33/26.Z H05B33/06 H05B33/12.B G09G3/3233 G09G3/3266 G09G3/3275 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/DD01 3K107/DD03 3K107/DD38 3K107/DD39 3K107/HH04 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD22 5C080/EE25 5C080/EE29 5C080/FF02 5C080/FF11 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C380/AA01 5C380/AB06 5C380/AB08 5C380/AB11 5C380/AB15 5C380/AB46 5C380/AC05 5C380/BA19 5C380/BA20 5C380/BB02 5C380/BB05 5C380/CA14 5C380/CB01 5C380/CB16 5C380/CB17 5C380/CB31 5C380/CC04 5C380/CC21 5C380/CC27 5C380/CC33 5C380/CC34 5C380/CC37 5C380/CC38 5C380/CC41 5C380/CC61 5C380/CC64 5C380/CC71 5C380/CD014 5C380/CD015 5C380/CD024 5C380/CD025 5C380/CE04 5C380/CE14 5C380/CE20 5C380/DA02 5C380/DA07 5C380/DA08 5C380/DA09 5C380/DA15 5C380/DA16 5C380/DA35 5C380/DA47 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

## 摘要(译)

要解决的问题：为了防止在使用顶部发射型有机EL显示面板的显示装置中出现阴影。本发明公开了一种显示装置，该显示装置具有至少一对由第一有机EL元件和第二有机EL元件组成的一对有机EL元件，该显示装置包括：基板；像素电路部分，其中形成每个像素的像素电路；像素电路部分，形成在所述像素电路部分上，其中所述至少一对有机EL元件形成L元件的元件形成部分，形成在元件形成部分上的介电层，形成在介电层上的透明导电膜以及AC驱动电压源，形成部中形成的至少一对有机EL元件中的第一有机EL元件和第二有机EL元件彼此并联连接，并且在点亮期间AC驱动电压从AC驱动电压源施加到至少一对有机EL元件。发明背景