(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-258414

(P2009-258414A)

(43) 公開日 平成21年11月5日(2009.11.5)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | H 3K107     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 611H 5C080  |

| <b>H05B 33/08</b> (2006.01) | G09G 3/20 | 670Q        |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 | 621M        |

|                             | G09G 3/20 | 680G        |

審査請求 未請求 請求項の数 10 O L (全 19 頁) 最終頁に続く

|           |                              |            |                                                                                                                                            |

|-----------|------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2008-107690 (P2008-107690) | (71) 出願人   | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号                                                                                                     |

| (22) 出願日  | 平成20年4月17日 (2008.4.17)       | (74) 代理人   | 100082131<br>弁理士 稲本 義雄                                                                                                                     |

|           |                              | (72) 発明者   | 甚田 誠一郎<br>東京都港区港南1丁目7番1号 ソニー株式会社内                                                                                                          |

|           |                              | F ターム (参考) | 3K107 AA01 BB01 CC33 CC45 EE03<br>GG56 HH02 HH04 HH05<br>5C080 AA06 BB05 DD05 DD15 DD30<br>JJ01 JJ02 JJ03 JJ04 JJ05<br>JJ06 KK02 KK07 KK43 |

(54) 【発明の名称】表示装置及びその製造方法と電子機器

## (57) 【要約】

【課題】基板上に検査手段を備えたアクティブマトリクス型の表示装置を提供する。

【解決手段】表示を行うための画素アレイ部1と、その検査を行うための検査部7とが、基板上に配されている。各画素2は、少なくとも駆動トランジスタTrdと発光素子ELとを含んでいる。駆動トランジスタTrdは、映像信号に応じて駆動電流を出力し、発光素子ELは、駆動電流に応じて発光する。検査部7は、画素2の各行又は各列に対応して配された複数の検査トランジスタTrtを備えている。検査トランジスタTrtは、対応する行又は列の画素2に含まれる駆動トランジスタTrdと同じ特性を有する。検査トランジスタTrtの特性を測定して、対応する駆動トランジスタTrdの特性を検査する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

表示を行うための画素アレイ部と、その検査を行うための検査部とが、基板上に配され、

前記画素アレイ部は、行状の走査線と、列状の信号線と、各走査線と各信号線とが交差する部分に配された行列状の画素とを含み、

前記画素は、対応する走査線によって選択された時動作して対応する信号線から信号を取り込み、

各画素は、少なくとも駆動トランジスタと発光素子とを含んでおり、

前記駆動トランジスタは、該取り込んだ信号に応じて駆動電流を出力し、

前記発光素子は、該駆動電流に応じて発光し、

前記検査部は、画素の各行又は各列に対応して配された複数の検査トランジスタを備え、

前記検査トランジスタは、対応する行又は列の画素に含まれる駆動トランジスタと同じ特性を有し、

前記検査トランジスタの特性を測定して、対応する駆動トランジスタの特性を検査する表示装置。

**【請求項 2】**

前記検査トランジスタで得られた測定の結果に基づき、該信号線に供給する信号を調節する手段を含む請求項 1 記載の表示装置。

**【請求項 3】**

前記検査部は、該複数の検査トランジスタを順次選択して自動的に測定を行う走査回路を含む請求項 1 記載の表示装置。

**【請求項 4】**

前記走査回路は、該複数の検査トランジスタのゲート電極に順次パルスを印加して選択し、且つ各パルスの電圧を変化させて該選択された検査トランジスタの特性を測定する請求項 3 記載の表示装置。

**【請求項 5】**

前記走査回路は、該パルスの電圧を段階的に変化させて該検査トランジスタの特性を測定する請求項 4 記載の表示装置。

**【請求項 6】**

前記走査回路は、該パルスの電圧を連続的に変化させて該検査トランジスタの特性を測定する請求項 4 記載の表示装置。

**【請求項 7】**

前記基板は、パネルになる領域と、パネルから切り落とされる領域とに分かれており、前記画素アレイ部は、該パネルになる領域に形成され、

前記検査部も該パネルになる領域に形成されている請求項 1、2 又は 3 記載の表示装置。

**【請求項 8】**

前記パネルになる領域には、該画素アレイ部を駆動するための回路部も形成されており、

前記回路部は、該走査線に選択パルスを順次印加して画素を行単位で選択する走査回路を含み、

前記検査部は、該回路部に含まれる走査回路を該複数の検査トランジスタを選択するための走査回路として共用する請求項 7 記載の表示装置。

**【請求項 9】**

表示を行うための画素アレイ部と、その検査を行うための検査部とが、基板上に配され、前記画素アレイ部は、行状の走査線と、列状の信号線と、各走査線と各信号線とが交差する部分に配された行列状の画素とを含み、前記画素は、対応する走査線によって選択された時動作して対応する信号線から信号を取り込み、各画素は、少なくとも駆動トランジ

10

20

30

40

50

スタと発光素子とを含んでおり、前記駆動トランジスタは、該取り込んだ信号に応じて駆動電流を出力し、前記発光素子は、該駆動電流に応じて発光する表示装置の製造方法であつて、

前記検査部は、画素の各行又は各列に対応して配された複数の検査トランジスタを備え、

前記検査トランジスタは、対応する行又は列の画素に含まれる駆動トランジスタと同じ特性を有し、

前記検査トランジスタの特性を測定して、対応する駆動トランジスタの特性を検査する表示装置の製造方法。

#### 【請求項 10】

表示部とこれに情報を表示する本体部とを有し、

前記表示部は、表示を行うための画素アレイ部と、その検査を行うための検査部とが、基板上に配され、

前記画素アレイ部は、行状の走査線と、列状の信号線と、各走査線と各信号線とが交差する部分に配された行列状の画素とを含み、

前記画素は、対応する走査線によって選択された時動作して対応する信号線から信号を取り込み、

各画素は、少なくとも駆動トランジスタと発光素子とを含んでおり、

前記駆動トランジスタは、該取り込んだ信号に応じて駆動電流を出力し、

前記発光素子は、該駆動電流に応じて発光し、

前記検査部として、画素の各行又は各列に対応して配された複数の検査トランジスタを設け、

前記検査トランジスタは、対応する行又は列の画素に含まれる駆動トランジスタと同じ特性を有するように形成し、

前記検査トランジスタの特性を測定して、対応する駆動トランジスタの特性を検査する機能を有する電子機器。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は発光素子を画素に用いたアクティブマトリクス型の表示装置に関する。詳しくは各画素に含まれる発光素子を駆動するトランジスタの特性を検査する技術に関する。

##### 【背景技術】

##### 【0002】

アクティブマトリクス型の表示装置は、表示を行うための画素アレイ部が基板上に配されている。画素アレイ部は、行状の走査線と、列状の信号線と、各走査線と各信号線とが交差する部分に配された行列状の画素とを含む。各画素は、対応する走査線によって選択されたとき動作して対応する信号線から映像信号を取り込む。各画素は、少なくとも駆動トランジスタと発光素子とを含んでいる。駆動トランジスタは、信号線から取り込んだ映像信号に応じて駆動電流を出力する。発光素子は、駆動電流に応じた輝度で発光する。かかる構成を有するアクティブマトリクス型の表示装置は、例えば以下の特許文献1に記載されている。

##### 【特許文献1】特開2007-310311公報

##### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0003】

駆動トランジスタは必ずしも均一な電気特性を有しておらず、画素ごとに特性がばらついている。駆動トランジスタの特性がばらつくと、発光輝度が均一にならず、画面のユニフォーミティが低下するという問題がある。画面のユニフォーミティを改善するためには、基板上で各駆動トランジスタの特性を検査し、その結果に応じて補正などの対策を施す必要がある。しかしながら従来のアクティブマトリクス型表示装置は基板上に適当な検査

10

20

30

40

50

手段を備えていないため、画面のユニフォーミティを改善することに支障があった。

【課題を解決するための手段】

【0004】

上述した従来の技術の課題に鑑み、本発明は基板上に検査手段を備えたアクティブマトリクス型の表示装置を提供することを目的とする。かかる目的を達成するために以下の手段を講じた。即ち本発明に係る表示装置は、表示を行うための画素アレイ部と、その検査を行うための検査部とが、基板上に配されている。前記画素アレイ部は、行状の走査線と、列状の信号線と、各走査線と各信号線とが交差する部分に配された行列状の画素とを含み、前記画素は、対応する走査線によって選択された時動作して対応する信号線から信号を取り込む。各画素は、少なくとも駆動トランジスタと発光素子とを含んでおり、前記駆動トランジスタは、該取り込んだ信号に応じて駆動電流を出力し、前記発光素子は、該駆動電流に応じて発光する。前記検査部は、画素の各行又は各列に対応して配された複数の検査トランジスタを備え、前記検査トランジスタは、対応する行又は列の画素に含まれる駆動トランジスタと同じ特性を有し、前記検査トランジスタの特性を測定して、対応する駆動トランジスタの特性を検査する。

10

【0005】

好ましくは、前記検査トランジスタで得られた測定の結果に基づき、該信号線に供給する信号を調節する回路手段を含む。又前記検査部は、該複数の検査トランジスタを順次選択して自動的に測定を行う走査回路を含む。又前記走査回路は、該複数の検査トランジスタのゲート電極に順次パルスを印加して選択し、且つ各パルスの電圧を変化させて該選択された検査トランジスタの特性を測定する。又前記走査回路は、該パルスの電圧を段階的に変化させて該検査トランジスタの特性を測定する。或いは前記走査回路は、該パルスの電圧を連続的に変化させて該検査トランジスタの特性を測定する。又前記基板は、パネルになる領域と、パネルから切り落とされる領域とに分かれており、前記画素アレイ部は、該パネルになる領域に形成され、前記検査部も該パネルになる領域に形成されている。又前記パネルになる領域には、該画素アレイ部を駆動するための回路部も形成されており、前記回路部は、該走査線に選択パルスを順次印加して画素を行単位で選択する走査回路を含み、前記検査部は、該回路部に含まれる走査回路を該複数の検査トランジスタを選択するための走査回路として共用する。

20

【発明の効果】

30

【0006】

本発明によれば、表示を行うための画素アレイ部に加え、その検査を行うための検査部が同じ基板上に配されている。検査部は、画素アレイ部に含まれる画素の各行または各列に対応して配された複数の検査トランジスタを備えている。この検査トランジスタは、対応する行または列の画素に含まれる駆動トランジスタと同じ特性を有する。本発明では、この検査トランジスタの特性を測定して、対応する駆動トランジスタの特性を検査することができる。さらには、検査トランジスタで得られた測定の結果に基づき、信号線に供給する信号を調節することで、画面のユニフォーミティを改善できる。アクティブマトリクス型の表示装置は、製造プロセスの関係から、特に駆動トランジスタの特性ばらつきが画素の行または画素の列に対応して現れる傾向がある。そこで画素行ごともしくは画素列ごとに検査トランジスタを設けることで、対応する画素行もしくは画素列に含まれる全ての駆動トランジスタの特性を検査することが可能となり、検査工数を大幅に削減することができる。

40

【発明を実施するための最良の形態】

【0007】

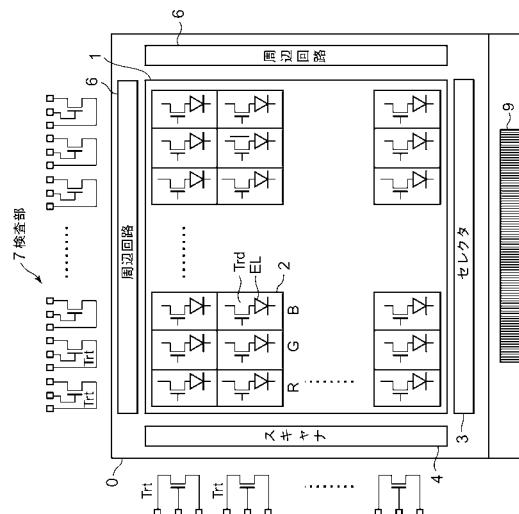

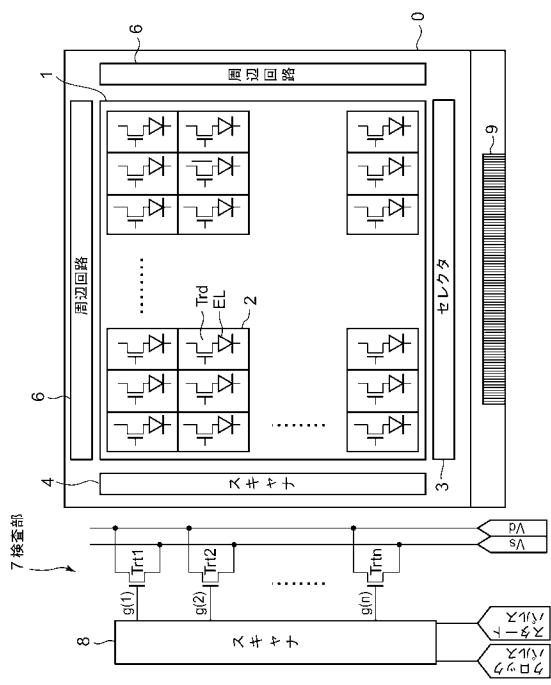

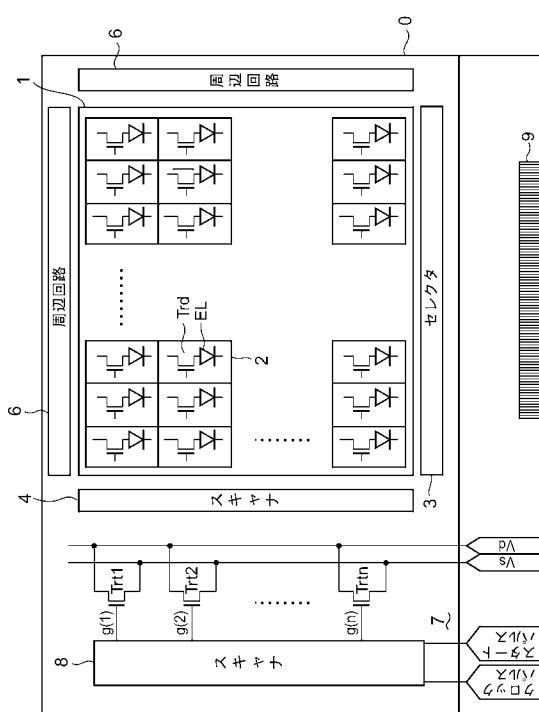

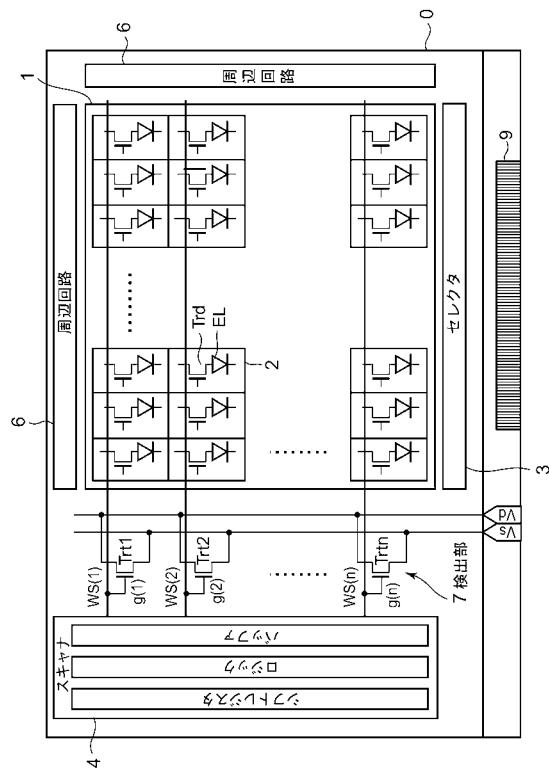

以下図面を参照して本発明の実施の形態を詳細に説明する。図1は、本発明にかかる表示装置の第1実施形態を示す模式的な平面図である。図示するように本表示装置は、表示を行うための画素アレイ部1と、その検査を行うための検査部7とが、基板上に配されている。本実施形態ではこの基板が、パネル0になる領域と、パネルから切り落とされる領域とに分かれている。パネル0となる領域には、上述した画素アレイ部1が含まれる一方

50

、本実施形態では検査部7がパネル0から切り落とされる領域に形成されている。なお、パネル0には、画素アレイ部1を駆動するため、回路部も形成されている。この回路部は、セレクタ3、スキャナ4、その他の周辺回路6が含まれる。またパネル0の下端部には、パネル0内の回路部を外部に接続するための端子部9が形成されている。

【0008】

画素アレイ部1は、行状の走査線と、列状の信号線と、各走査線と各信号線とが交差する部分に配された行列状の画素2とを含んでいる。本実施形態では、個々の画素2は、赤緑青三原色(RGB)のいずれか一色が割り当てられており、カラー表示ができるようになっている。但し本発明はこれに限られるものではなく、白黒モノカラーの表示装置にも適用できる。

10

【0009】

各画素2は、対応する走査線によって選択されたとき動作して対応する信号線から映像信号を取り込む。各画素2は、少なくとも駆動トランジスタTrdと発光素子ELとを含んでいる。駆動トランジスタTrdは、信号線から取り込んだ映像信号に応じて駆動電流を出力する。発光素子ELは、例えば有機エレクトロルミネッセンス素子などからなり、駆動電流に応じた輝度で発光する。

【0010】

本発明の特徴事項として、検査部7は、画素2の各行または各列に対応して配された複数の検査トランジスタTrtを備えている。図示の例では、画素2の各行に対応して、複数の検査トランジスタTrtがパネル0の左辺に沿って縦列配置されている。また画素2の各列に対応して、パネル0の上辺に沿って複数の検査トランジスタTrtが横列配置されている。但し本発明は縦列配置した検査トランジスタTrtと横列配置した検査トランジスタTrtのいずれか一方を含めばよく、両者を設ける必要はない。

20

【0011】

検査トランジスタTrtは、対応する行または列の画素2に含まれる駆動トランジスタTrdと同じ特性を有する。換言すると、駆動トランジスタTrdとこれに対応する検査トランジスタTrtは、製造プロセスにおいて同一条件で形成される。この様な検査トランジスタの特性を測定することで、対応する駆動トランジスタの特性を検査することができる。

30

【0012】

この様に、パネル0の外側に、検査トランジスタTrtを配列することで、画素行間もしくは画素列間における駆動トランジスタTrdの特性差を確認することができる。この結果を画素アレイ部1側にフィードバックすることで、画素行間もしくは画素列間における輝度差を解消することが可能となり、画面のユニフォーミティを改善できる。具体的には、検査トランジスタで得られた特定の結果に基づき、信号線に供給する映像信号を調節する回路手段(回路部)をパネル外に設けている。

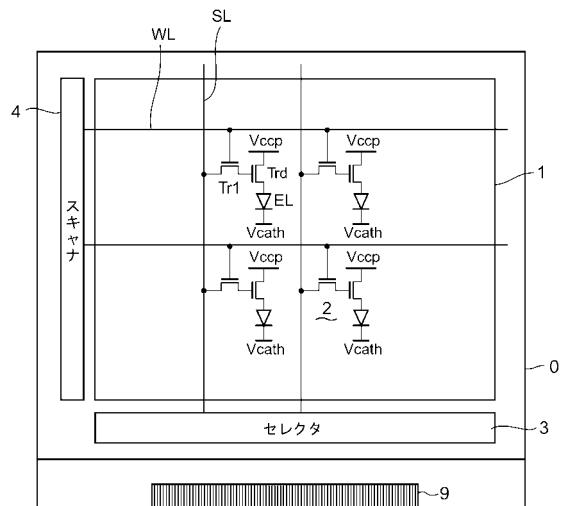

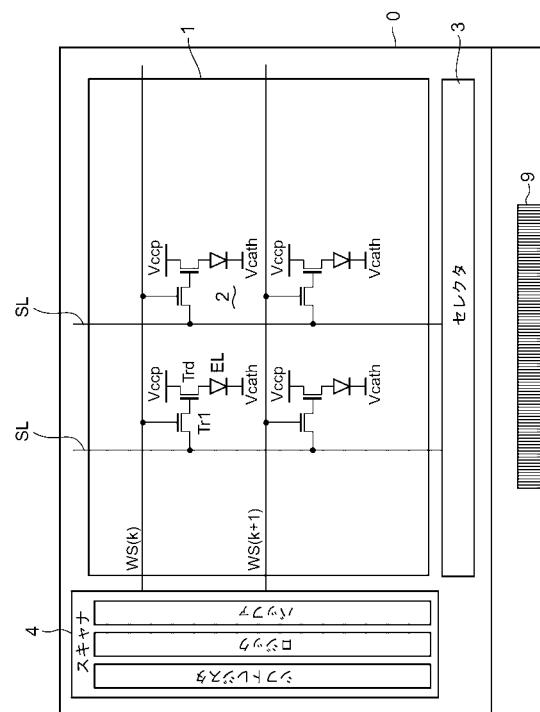

【0013】

以下図2～図7を参照して、本発明の課題、構成、作用および効果を具体的に説明する。図2は、表示装置の典型的な構成例を示す模式的な平面図である。図示するように、画素アレイ部1は、行状の走査線WSと、列状の信号線SLと、各走査線WSと各信号線SLとが交差する部分に配された行列状の画素2とを含む。スキャナ4は各走査線WSを介して画素2を行単位で選択する。セレクタ3は、選択された画素2に各信号線SLを介して信号を供給する。

40

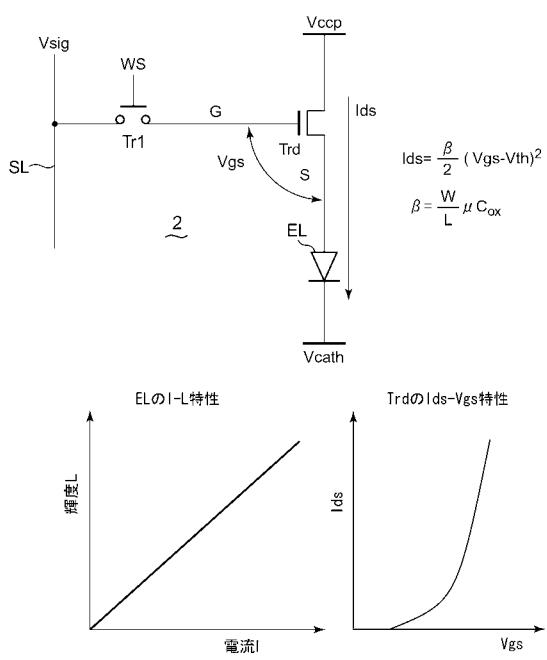

【0014】

画素2は、サンプリングトランジスタTr1と駆動トランジスタTrdと発光素子ELとで構成されている。サンプリングトランジスタTr1及び駆動トランジスタTrdはNチャネル型のTFTである。サンプリングトランジスタTr1の一方の電流端は信号線SLに接続されている。他方の電流端は駆動トランジスタTrdのゲートに接続されている。サンプリングトランジスタTr1のゲートは走査線WSに接続されている。駆動トランジスタTrdの一方の電流端であるドレインは電源Vccpに接続されている。駆動トランジスタTrdの一方の電流端であるドレインは電源Vccpに接続されている。

50

ンジスタ T r d の他方の電流端であるソースは発光素子 E L のアノードに接続されている。発光素子 E L のカソードは接地電位に接続している。即ちこの接地電位はカソード電位 V c a t h となっている。前述したように駆動トランジスタ T r d の制御端となる第 1 のゲート電極はサンプリングトランジスタ T r 1 を介して信号線 S L に接続している。

【 0 0 1 5 】

図 3 は、図 2 に示した画素 2 の動作説明に供する模式図である。図示するように、サンプリングトランジスタ T r 1 は走査線 W S により選択されたときオンして、信号線 S L から映像信号 V s i g をサンプリングし、駆動トランジスタ T r d のゲート G に書き込む。駆動トランジスタ T r d はゲート G に書き込まれたゲート電圧 V g s に応じて、ドレイン電流 I d s を出力する。発光素子 E L はこのドレイン電流（駆動電流） I d s に応じた輝度で発光する。このとき駆動電流 I d s は電源 V c c p から駆動トランジスタ T r d 及び発光素子 E L の直列接続を通して接地ライン（カソード電位 V c a t h ）に流れる。

【 0 0 1 6 】

図 3 のグラフに示すように、発光素子 E L の電流 I と輝度 L は比例関係にある。即ち駆動トランジスタ T r d から供給される電流 I が大きいほど、発光素子 E L の輝度 L が高くなる。駆動電流 I d s はゲート電圧 V g s により制御される。ゲート電圧 V g s は映像信号 V s i g に対応している。従ってこの画素 2 は映像信号 V s i g ( 即ち階調を表すデータ電圧 ) に応じて発光素子の輝度 L を制御しており、電圧プログラム - 電流駆動タイプとなっている。

【 0 0 1 7 】

電圧プログラム - 電流駆動タイプの画素 2 に組み込まれる駆動トランジスタ T r d は飽和領域で動作し、図 3 に示したトランジスタ特性式に従って駆動電流 I d s を出力している。トランジスタ特性式から明らかなように、駆動トランジスタ T r d は飽和領域で動作するとき、ゲート電圧 V g s が閾電圧 V t h を超えた時点でドレイン電流 I d s が流れ始め、以降ゲート電圧 V g s が大きくなるほど、ドレイン電流 I d s が増大する。なおトランジスタ特性式に含まれる係数  $\alpha$  は、パラメータ W, L,  $\mu$ , C o x で決まる定数である。ここで W は駆動トランジスタ T r d のチャネル幅を表し、L は同じくチャネル長を表し、 $\mu$  は同じく移動度を表し、C o x はゲート酸化膜の単位容量を表している。

【 0 0 1 8 】

以上の説明から明らかなように、図 3 に示した電圧プログラム - 電流駆動タイプの画素回路は、セレクタ（ソースドライバ）から供給される映像信号 V s i g をノード G に書き込み、駆動トランジスタ T r d を飽和領域で動作させることで、これを電流源として利用している。一方この電流源に接続した発光素子 E L は輝度が電流に比例する。この様にして駆動トランジスタ T r d は信号 V s i g ( データ電圧 ) を発光電流に変換する役割を担っている。映像信号 V s i g ( データ電圧 ) は階調に応じたレベルを有している。V s i g と V g s が対応しているため、発光素子 E L の輝度を階調制御することができる。

【 0 0 1 9 】

図 3 のトランジスタ特性式に示すように、閾電圧 V t h やパラメータ  $\alpha$  にばらつきがあれば、ゲート電圧 V g s に応じて正確に I d s が得られるため、各画素の発光輝度にばらつきは生じない。しかしながら実際には製造プロセスの影響を受けて、閾電圧 V t h やパラメータ  $\alpha$  中の移動度  $\mu$  にばらつきが生じ、画面のユニフォーミティが乱される。

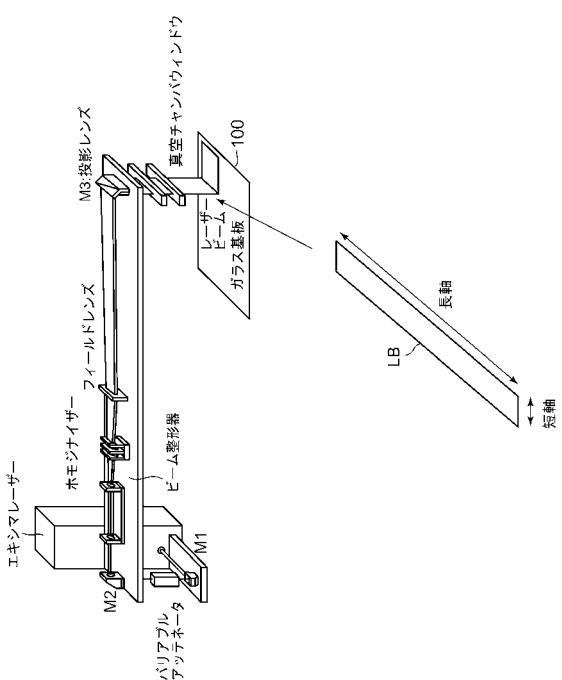

【 0 0 2 0 】

図 4 は、薄膜トランジスタ ( TFT ) の製造プロセスを示す模式図である。薄膜トランジスタは素子領域が例えば多結晶シリコン薄膜からなる。多結晶シリコンは非晶質シリコン（以下本明細書ではアモルファスシリコンと呼ぶ場合がある）の薄膜にレーザ光を照射しアニールすることで得られる。図 4 は、このレーザーアニールプロセスを示す模式図である。エキシマレーザー源から放射したレーザー光はミラー M 1 で反射された後、バリアブルアッテネータを通過する。その後ミラー M 2 で光路が折り曲げられ、ビーム整形器、ホモジナイザー、フィールドレンズ、ミラー M 3 、投影レンズを通ってラインビーム L B に整形される。ラインビーム L B は真空チャンバのウインドウを通過して、ガラス基板 1

10

20

30

40

50

00に照射される。ガラス基板100には予め非晶質シリコン薄膜が成膜されており、これにラインピームLBを照射することで、多結晶シリコンに転換する。

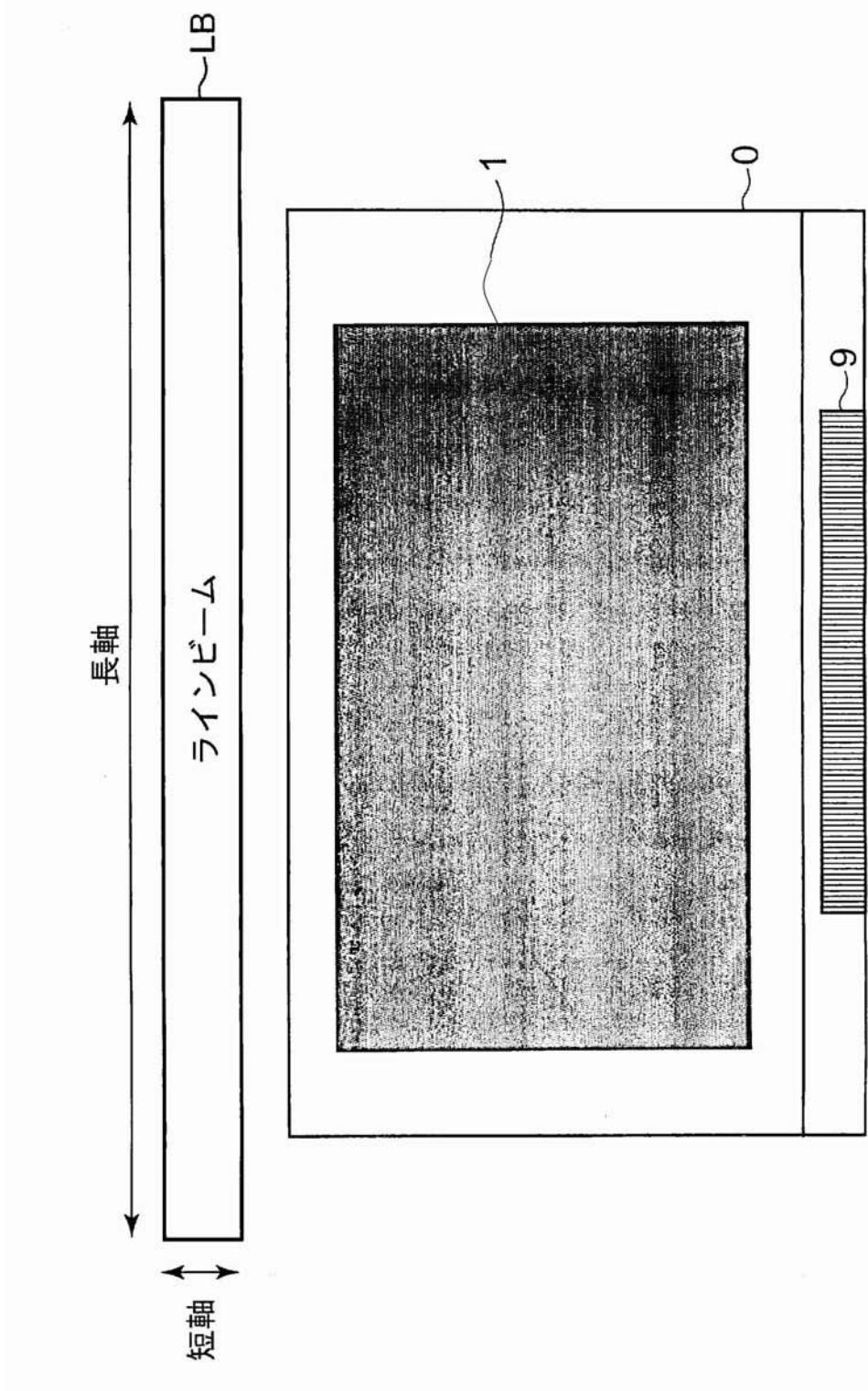

#### 【0021】

図示するように、ラインピームLBは長軸及び短軸を有する短冊状になっている。このラインピームLBを基板100に対して短軸方向にシフトしながら照射することで、基板100全面のアモルファスシリコンを多結晶シリコンに転換することができる。実際のプロセスでは、ラインピームLBの位置を固定する一方、基板100をスライドシフトしながら照射を行う。

#### 【0022】

ラインピームLBの強度は常に一定となるように調整しているが、実際にはその強度が時間的に変動してしまう。これにより多結晶シリコンの結晶ばらつきが生じ、結果的に薄膜トランジスタの特性にばらつきが生じる。このTFT特性のばらつきが表示装置のユニフォーミティの低下原因となっている。

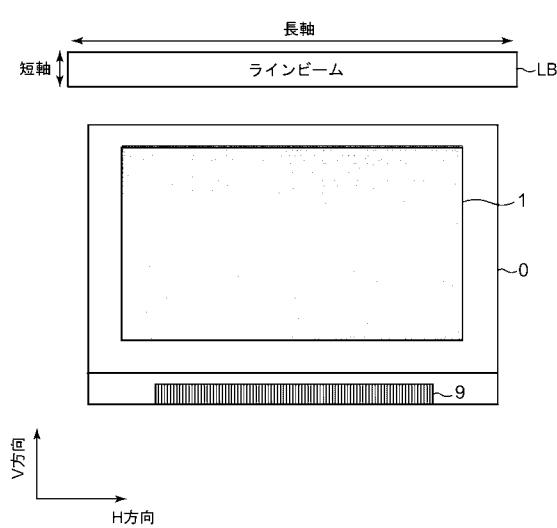

#### 【0023】

図5は、パネル0の画面を写真撮影した図である。前述したように、レーザーアニールは、短冊状のラインピームLBをパネル0になる基板に対して断続的に照射していく。基板を短軸方向にずらしてはラインピームLBを照射するという処理を繰り返すことで、基板全面のアモルファスシリコンを多結晶化できる。ラインピームは照射するたびにエネルギーばらつきがあるため、ラインピームLBの照射領域ごとにTFT特性の差が発生する。ラインピームLB内では、長軸方向に沿って多少のエネルギー分布もあるが、これは連続的であるため大きな影響はない。長軸方向に沿ったTFTの特性ばらつきは連続的であるため、発光輝度のムラもグラデーションを持った状態となり、視覚的には目立たない。これに対して短軸方向に沿って重なり合うラインピームLBの境界ではTFT特性が非連続的に変化するため、TFT特性のばらつきも非連続的となる。このため、画面上では輝度の差が横スジとして認識され、目立つようになってしまふ。図のパネル写真では、ラインピームLBの長軸方向に沿った横スジが現れてしまい、パネル0のユニフォーミティの低下原因となっている。

#### 【0024】

図6は、ラインピームLBと、パネル0の画素アレイ部1に現れる筋ムラとの関係を示す模式図である。図示の例は、画面の水平方向(H方向)にラインピームLBの長軸を合わせて、レーザーアニールを行った場合である。このレーザーアニールでは、ラインピームLBの短軸が画面の垂直方向(V方向)に沿って移動するようにステップ照射している。ラインピームLBはステップ照射ごとにビームエネルギーがばらつくため、V方向の各位置によってポリシリコンの結晶性が変化してしまう。これに対応して駆動トランジスタのTFT特性がV方向の各位置によって異なってしまう。これに応じて各画素行の発光輝度に差が生じ、横スジが発生する。

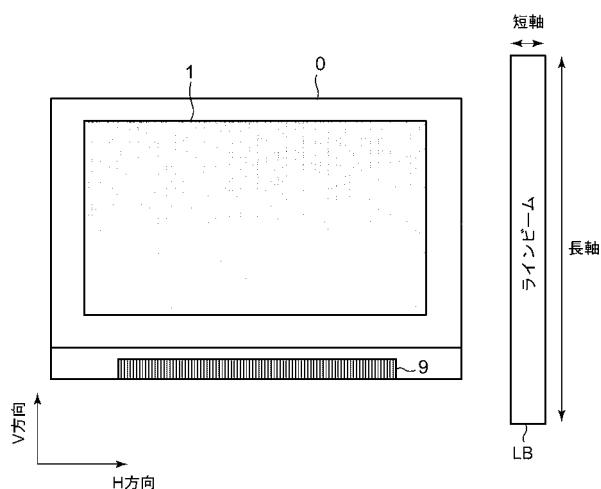

#### 【0025】

図7は、ラインピームLBの長軸がパネル0のV方向となり、ラインピームLBの短軸が同じくH方向となるように設定して、レーザーアニールを行った場合である。ラインピームLBはその照射領域が部分的に重なるように、H方向に沿ってステップ照射される。ラインピームLBは各ショットごとにエネルギーがばらつくため、V方向に沿って多結晶シリコンの結晶性がばらつき、これに応じて駆動トランジスタのTFT特性が画素の列ごとに異なってしまい、縦スジが現われる。

#### 【0026】

本発明では、この様な駆動トランジスタの列ごとの特性ばらつきを測定するため、検査トランジスタを画素の各列に対応して配置している。検査トランジスタの特性を測定することで、対応する画素列の駆動トランジスタの特性が得られる。

#### 【0027】

例えば検査トランジスタのドレイン電流 $I_{ds}$  - ゲート電圧 $V_{gs}$ 特性を測定することで、図3に示したトランジスタ特性が得られる。図3のトランジスタ特性は、検査トラン

10

20

30

40

50

ジスタに対応する駆動トランジスタの  $I_{ds}$  -  $V_{gs}$  特性を推定したものとなっている。なぜならば、検査トランジスタは対応する駆動トランジスタと同じ特性を有するからである。

#### 【0028】

各画素列に対応して検査トランジスタを配することで、各画素列の駆動トランジスタごとに、図3に示した  $I_{ds}$  -  $V_{gs}$  特性が得られる。本発明では、検査トランジスタの測定によって得られた駆動トランジスタの  $I_{ds}$  -  $V_{gs}$  特性を利用して、各画素列ごとに調節された映像信号を各信号線に供給している。換言すると、 $I_{ds}$  -  $V_{gs}$  特性が画素列ごとに異なっていても、その相違をなくすように、各画素列に書き込む映像信号のレベルを調節している。

10

#### 【0029】

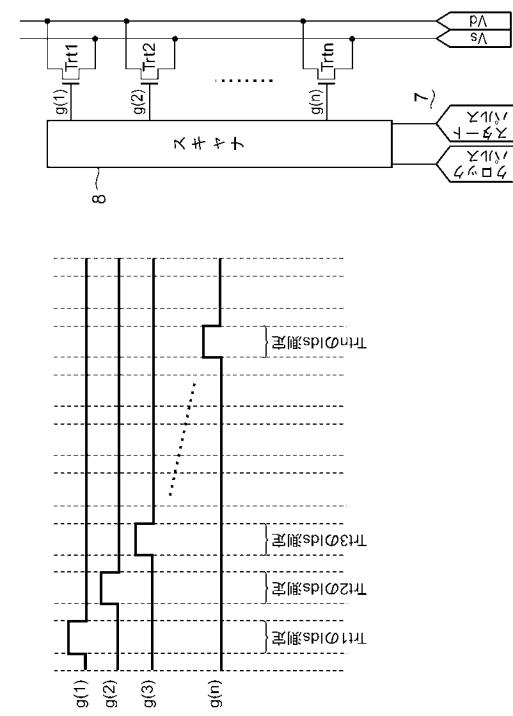

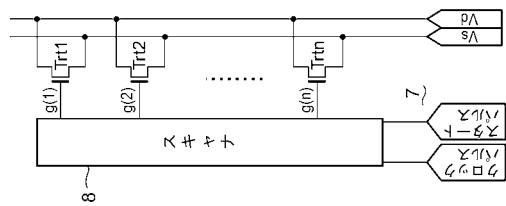

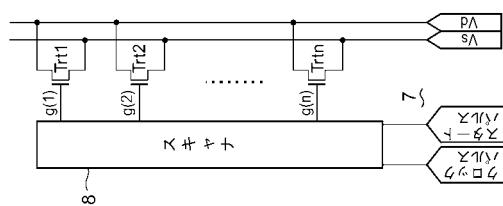

図8は、本発明にかかる表示装置の第2実施形態を示す模式的なブロック図である。理解を容易にするため、図1に示した第1実施形態と対応する部分には対応する参照番号を付してある。本実施形態の表示装置は、検査部7がスキャナ(走査回路)8を備えている。このスキャナ8は、複数の検査トランジスタ  $T_{rt}$  を順次選択して自動的に測定を行う。スキャナ8は外部から供給されるクロックパルスに応じて動作し、同じく外部から供給されるスタートパルスを順次転送して各行ごとに駆動パルス  $g$  を出力する。複数の検出トランジスタ  $T_{rt1} \sim T_{rtn}$  は駆動パルス  $g(1) \sim g(n)$  に応じて順次オンする。各検出トランジスタ  $T_{rt1} \sim T_{rtn}$  は、そのドレインが端子  $V_d$  に共通接続され、そのソースが端子  $V_s$  に共通接続されている。外部の補正手段は、端子  $V_d$  と  $V_s$  の間に流れる電流を設定する。この様にして、スキャナ8は検出トランジスタ  $T_{rt1} \sim T_{rtn}$  を時分割的に駆動してドレイン電流  $I_{ds}$  を時分割的に測定できるようにしている。

20

#### 【0030】

図1に示した第1実施形態では、個々の検査トランジスタ  $T_{rt}$  ごとに、ゲート、ソース及びドレインに対応した端子(パッド)を設けていた。この様に各検査トランジスタごとにパッドを設けると、そのサイズが小さくなってしまうためプローブ用の針をパッドに当てる精度を高める必要がある。プローブの本数が全検査トランジスタの合計パッド数よりも少ない場合、プローブを移動しなければならず、時間がかかってしまう。この様に図1の実施形態は、コスト面やタクト面で非効率的である。これに対し本実施形態は、検査部7にスキャナ8を組み込んで、検査トランジスタ  $T_{rt1} \sim T_{rtn}$  を時分割的に駆動して、検査を行っている。この方式によれば、外部測定手段との接続パッドは4つで済み、コスト面及びタクト面で効率的になる。

30

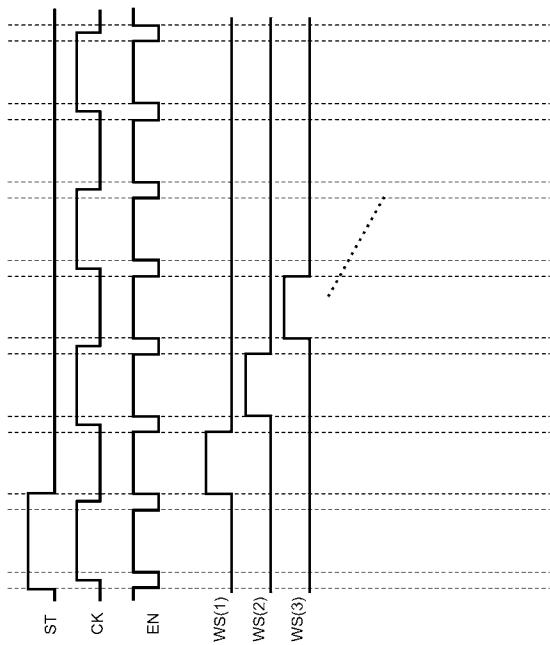

#### 【0031】

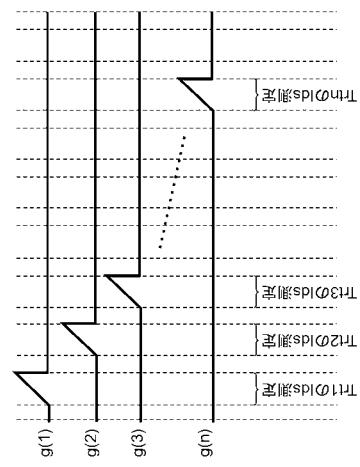

図9は、図8に示した第2実施形態に組み込まれる検査部7の動作説明に供するタイミングチャートである。スキャナ8はシフトレジスタで構成されており、出力が互いにオーバーラップしないように駆動パルス  $g(1) \sim g(n)$  を順次転送していく機能を有する。この転送パルスを各検査トランジスタ  $T_{rt1} \sim T_{rtn}$  のゲートに印加することで、各列の検査トランジスタの  $I_{ds}$  を特定の  $V_{gs}$  に対して測定することができる。この  $V_{gs}$  は転送パルス(駆動パルス)  $g$  の電圧で決まる。スキャナ8の出力の高電位側のレベルを変えることで、 $V_{gs}$  を変更することができるため、複数の動作点で(複数の  $V_{gs}$  のレベルで)ドレイン電流  $I_{ds}$  を測定することができる。これらの測定結果から図3に示したTFT特性が各画素行の駆動トランジスタ  $T_{rd}$  に関して得られる。得られたTFT特性からばらつきを抽出し、映像信号の電位にフィードバックを掛ける。

40

#### 【0032】

スキャナ8が出力する駆動パルスの低側電位は、検査トランジスタがオフになる  $V_{gs}$  を決めている。オン電流に対して十分に測定精度が保たれるようにオフ電流を決める必要がある。例えば画素アレイ部の画素行数(段数)が200程度であれば、オン電流が  $\mu A$  オーダの場合、オフ電流は  $pA$  オーダであれば問題ない。

#### 【0033】

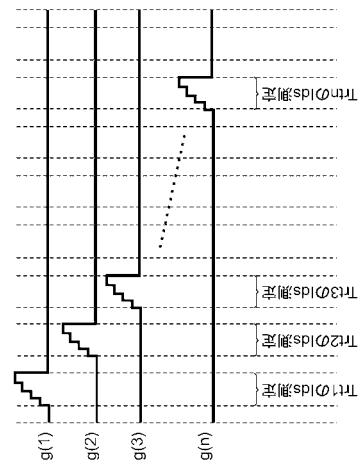

図10は、図9に示した実施例の変形例を表すタイミングチャートである。図9の実施

50

例では、スキャナ 8 の 1 回の走査で所定の  $V_{g_s}$  に対応した  $I_{d_s}$  を測定できる。別の  $V_{g_s}$  で  $I_{d_s}$  を測定するためもう一度スキャナ 8 を走査する必要がある。複数の動作点で測定を行うためには、検査トランジスタのゲートに印加する転送パルスの電圧振幅を複数回切換えるなければならない。そのたびに、スキャナ 8 を走査しなければならず、測定動作点数を増やすと、それだけ測定時間が長くなってしまう。

【0034】

これに対し図 10 に示した実施例は、転送パルスの電圧を段階的に変化させている。この様に各検査トランジスタのゲートに印加する転送パルスをステップ状にすることで、 $V_{g_s}$  を切換えるながら  $I_{d_s}$  を測定することができるようになる。スキャナ 8 は 1 回の走査で各検査トランジスタ  $T_{r_t}$  について図 3 に示した TFT 特性 ( $V_{g_s}$  -  $I_{d_s}$  特性) を測定することができる。

10

【0035】

図 11 は、さらに別の実施例を示すタイミングチャートである。図 10 の実施例では、転送パルスの波形を段階的に切換えて、多点測定を行っていた。これに対し本実施例では転送パルスの波形を低レベルから高レベルまで連続的に切換えて、測定を行っている。この様に転送パルスの電圧を連続的に掃引することでより精密な測定を行うことができる。図 10 の実施例は動作点を多段的に変化させて測定しているが、本実施例では連続的に動作点を変えて測定を行っているため、すべての動作点で測定していることになる。したがって、信号電位へのフィードバックがこの検査トランジスタ測定データから直接的に行える。図 10 の多段的測定の場合は、測定点間はモデル式(たとえば図 3 のモデル式)フィッティングにより補間したデータを信号電位のフィードバックに用いることになる。

20

【0036】

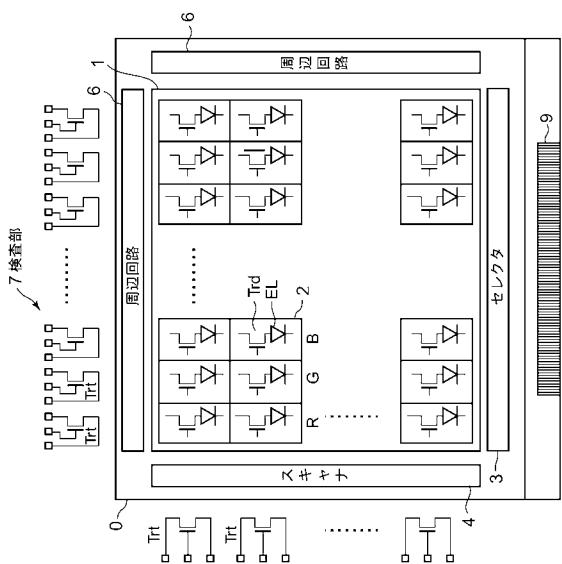

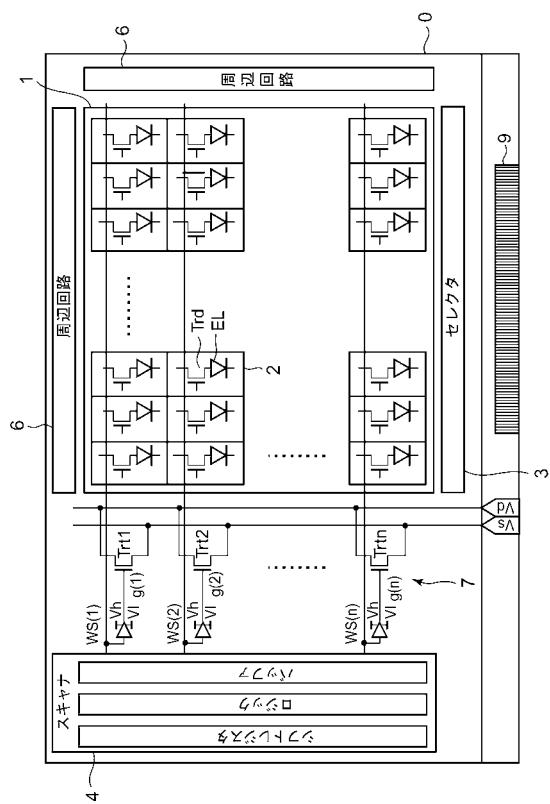

図 12 は、本発明にかかる表示装置の第 3 実施形態を示す模式的な平面図である。理解を容易にするため、図 8 に示した第 2 実施形態と対応する部分には対応する参照番号を付してある。図 8 の第 2 実施形態では、検査部 7 がパネル外にあり、完成品状態ではパネル 0 から切り離されてしまう。従って図 8 の第 2 実施形態の場合、パネルの製造段階で測定を行った後は、もはや駆動トランジスタの特性は測定できず、経時的な変化に対応することができなかった。そこで本実施形態は、検査部 7 をパネル 0 内に形成し、出荷した後の段階でも駆動トランジスタの特性を検査できるようにしている。本実施形態の場合、基板はパネル 0 になる領域とパネル 0 から切り落とされる領域とに分かれている。駆動トランジスタを含む画素アレイ部 1 は、パネル 0 になる領域に形成されている。検査部 7 もまたパネル 0 になる領域に形成されている。この様に検査部 7 をパネル 0 に内蔵することで、画素アレイ部 1 に集積形成された駆動トランジスタ  $T_{r_d}$  の特性を習得し続けることができる。本実施形態の場合、測定用の IC を、パネル 0 の端部に形成された 4 つのパッドに接続することで、定期的に駆動トランジスタの特性を測定できるため、TFT 特性の経時変化にも対応可能である。さらには測定用の IC で定期的に得られたデータを映像信号にフィードバックすることで、画面のユニフォーミティを維持することができる。この様なフィードバック補正是、例えば 補正回路を利用することができます。

30

【0037】

図 12 に示した実施形態は、パネル 0 に検査部 7 を内蔵するため、その分パネル 0 の額縁領域が広がり、レイアウト面積が拡大し、コスト増の要因となる。図 12 の実施形態は、検査部 7 にスキャナ 8 が組み込まれている一方、画素アレイ部 1 を駆動するために別のスキャナ 4 が配されている。2 つのスキャナ 4, 8 を共用することで、レイアウト面積を抑えることが可能である。以下この様な実施形態について説明する。

40

【0038】

図 13 は、アクティブマトリクス型表示装置の典型的な構成を表しており、特にスキャナ 4 の構成に着目している。図示するようにパネル 0 は、画素アレイ部 1 と、これを駆動するための回路部が形成されている。画素アレイ部 1 は、行状の走査線  $W_S$  と、列状の信号線  $S_L$  と、各走査線  $W_S$  と各信号線  $S_L$  とが交差する部分に配された行列状の画素 2 を含む。画素 2 は、対応する走査線  $W_S$  によって選択されたとき動作して対応する信号線

50

S L から信号を取り込む。画素 2 は、サンプリングトランジスタ Tr 1 、駆動トランジスタ Tr d 及び発光素子 E L を含んでいる。サンプリングトランジスタ Tr 1 は走査線 WS を介して選択パルスが印加されたときオンして、信号線 S L から信号を取り込み、駆動トランジスタ Tr d のゲートに書き込む。駆動トランジスタ Tr d はゲートに書き込まれた信号に応じて駆動電流を出力する。発光素子 E L はこの駆動電流に応じた輝度で発光する。

【 0 0 3 9 】

一方画素アレイ部 1 を囲む周辺の回路部は、セレクタ（信号回路）3 とスキヤナ（走査回路）4 とを含む。スキヤナ 4 は、行状の走査線 WS に接続されており、順次選択パルスを出力する。セレクタ 3 は列状の信号線 S L に接続されており、スキヤナ 4 の動作と同期して、各信号線 S L に映像信号を出力する。

10

【 0 0 4 0 】

スキヤナ 4 はシフトレジスタとロジックとバッファで構成されている。シフトレジスタはパネル 0 の外部から供給されるクロックパルスに応じて動作し、同じく外部から供給されるスタートパルスを転送して、ロジック側に出力する。ロジックはシフトレジスタから転送されてきたパルスを論理処理して、選択パルスに適した波形に整形する。バッファはロジックから出力された論理パルスを処理して、実際のゲート駆動に適した選択パルスを走査線 WS に出力する。

【 0 0 4 1 】

図 14 は、図 13 に示したスキヤナの動作説明に供するタイミングチャートである。スキヤナ 4 において、シフトレジスタはクロックパルス CK に応じて動作し、スタートパルス ST を順次転送する。ロジックはシフトレジスタから各段ごとに出力されたパルスをイネーブル信号 EN で論理処理し、各水平周期ごとに分離したパルスを生成する。バッファはロジックから出力されたパルスを電流増幅して各走査線 WS にゲートパルス（選択パルス）を出力する。この選択パルスにより、画素アレイ部 1 側の画素が行単位で順次選択されていく。

20

【 0 0 4 2 】

図 15 は、本発明にかかる表示装置の第 4 実施形態を示す模式的な平面図である。理解を容易にするため、図 12 に示した第 3 実施形態と対応する部分には対応する参照番号を付してある。異なる点は、本実施形態が検査部 7 と画素アレイ部 1 とでスキヤナ 4 を共用したことである。このスキヤナ 4 は、図 13 及び図 14 を参照して説明したとおり、画素の各行に対応して選択パルスを順次出力している。この選択パルスは対応する走査線 WS に印加されると共に、同時に對応する各検査トランジスタ Tr t のゲートに印加される。

30

【 0 0 4 3 】

この様にスキヤナ 4 の出力を検査トランジスタ Tr t のゲートにつなぐことで、パネル 0 の内部で特性評価が可能である。スキヤナ 4 は常に動作しているため、TFT 特性の経時変化を測定できる。駆動トランジスタ Tr t の特性が経時的に変化すると、対応する検査トランジスタ Tr t も同様な特性変化を引き起こす。本実施形態はスキヤナ 4 が常に動作しているため、この様な駆動トランジスタ Tr d の特性変化も検査トランジスタ Tr t を利用してモニタすることができる。なお本実施形態は、スキヤナ 4 の最終出力を各検査トランジスタ Tr t のゲートに印加しているが、本発明はこれに限られるものではない。スキヤナ 4 の内部のノードから検査トランジスタ Tr t のゲートパルスを取り出すようにしても良い。

40

【 0 0 4 4 】

図 16 は、図 15 に示した第 4 実施形態の変形例を示す模式的な平面図である。第 4 実施形態と異なり、本変形例はスキヤナ 4 から出力されたゲートパルス（選択パルス）を直接各検査トランジスタ Tr t のゲートに印加するのではなく、各段ごとに設けたバッファを介して検査トランジスタ Tr t のゲートに印加している。このバッファは検査トランジスタ Tr t のゲートに印加するパルスの高レベル V h と低レベル V l を規定するレベル変換回路となっている。高電位 V h は検査トランジスタ Tr t のゲートを開くための電位で

50

あり、丁度  $I_d$   $s$  測定時の  $V_g$   $s$  となっている。この高電位  $V_h$  をステップ波形もしくはスイープ波形とすることで、 $V_g$   $s$  を変化させながら  $I_d$   $s$  を測定することが可能となる。この様にゲートパルスをステップ波形もしくはスイープ波形とすることで、特性評価の自由度並びに精度を改善することができる。

また、画素アレイ部側の駆動トランジスタ  $T_{rd}$  と、検査トランジスタ  $T_{rt}$  の配置関係（レイアウト）は TFT 特性がレーザアニールに用いるラインビームの長軸方向に揃うため、これに合わせて各画素 2 の駆動トランジスタ  $T_{rd}$  と、検査トランジスタ  $T_{rt}$  が長軸ライン上に並ぶように配置することが好ましい。またトランジスタサイズも駆動トランジスタ  $T_{rd}$  と検査トランジスタ  $T_{rt}$  で揃えておく必要がある。トランジスタサイズが異なると、チャネル内の多結晶シリコン結晶数が異なってしまい、TFT 特性に若干のずれが生まれる原因となる。またトランジスタ構造やその周辺のレイアウトも駆動トランジスタ  $T_{rd}$  と検査トランジスタ  $T_{rt}$  で同じにしておくことが好ましい。レーザアニールでは加熱状態がレイアウトによって異なるためである。

駆動トランジスタ  $T_{rd}$  が NMOS の場合、検査トランジスタ  $T_{rt}$  も NMOS にする必要があり、これについて説明してきた。同様に駆動トランジスタ  $T_{rd}$  が PMOS の場合、検査トランジスタ  $T_{rt}$  も PMOS にする必要がある。

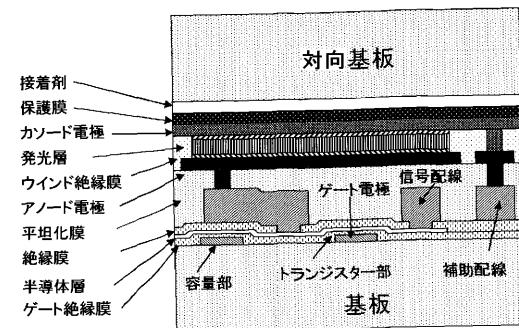

#### 【0045】

本発明にかかる表示装置は、図 17 に示すような薄膜デバイス構成を有する。本図は、絶縁性の基板に形成された画素の模式的な断面構造を表している。図示するように、画素は、複数の薄膜トランジタを含むトランジスター部（図では 1 個の TFT を例示）、保持容量などの容量部及び有機 EL 素子などの発光部とを含む。基板の上に TFT プロセスでトランジスター部や容量部が形成され、その上に有機 EL 素子などの発光部が積層されている。その上に接着剤を介して透明な対向基板を貼り付けてフラットパネルとしている。

#### 【0046】

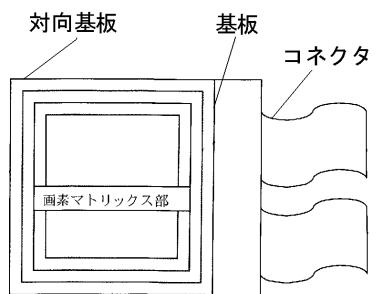

本発明にかかる表示装置は、図 18 に示すようにフラット型のモジュール形状のものを含む。例えば絶縁性の基板上に、有機 EL 素子、薄膜トランジスタ、薄膜容量等からなる画素をマトリックス状に集積形成した画素アレイ部を設ける、この画素アレイ部（画素マトリックス部）を囲むように接着剤を配し、ガラス等の対向基板を貼り付けて表示モジュールとする。この透明な対向基板には必要に応じて、カラーフィルタ、保護膜、遮光膜等を設けてもよい。表示モジュールには、外部から画素アレイ部への信号等を入出力するためのコネクタとして例えば FPC（フレキシブルプリントサーキット）を設けてもよい。

#### 【0047】

以上説明した本発明における表示装置は、フラットパネル形状を有し、様々な電子機器、例えば、デジタルカメラ、ノート型パーソナルコンピューター、携帯電話、ビデオカメラなど、電子機器の本体部に入力された、若しくは、電子機器の本体部内で生成した情報を画像若しくは映像として表示するあらゆる分野の電子機器のディスプレイ（表示部）に適用することが可能である。以下この様な表示部を備えた電子機器の例を示す。

#### 【0048】

図 19 は本発明が適用されたテレビであり、フロントパネル 12、フィルターガラス 13 等から構成される映像表示画面 11 を含み、本発明の表示装置をその映像表示画面 11 に用いることにより作製される。

#### 【0049】

図 20 は本発明が適用されたデジタルカメラであり、上が正面図で下が背面図である。このデジタルカメラは、撮像レンズ、フラッシュ用の発光部 15、表示部 16、コントロールスイッチ、メニュー・スイッチ、シャッター 19 等を含み、本発明の表示装置をその表示部 16 に用いることにより作製される。

#### 【0050】

図 21 は本発明が適用されたノート型パーソナルコンピュータであり、本体 20 には文字等を入力するとき操作されるキーボード 21 を含み、本体カバーには画像を表示する表

示部 22 を含み、本発明の表示装置をその表示部 22 に用いることにより作製される。

【0051】

図 22 は本発明が適用された携帯端末装置であり、左が開いた状態を表し、右が閉じた状態を表している。この携帯端末装置は、上側筐体 23、下側筐体 24、連結部（ここではヒンジ部）25、ディスプレイ 26、サブディスプレイ 27、ピクチャーライト 28、カメラ 29 等を含み、本発明の表示装置をそのディスプレイ 26 やサブディスプレイ 27 に用いることにより作製される。

【0052】

図 23 は本発明が適用されたビデオカメラであり、本体部 30、前方を向いた側面に被写体撮影用のレンズ 34、撮影時のスタート／ストップスイッチ 35、モニター 36 等を含み、本発明の表示装置をそのモニター 36 に用いることにより作製される。

10

【図面の簡単な説明】

【0053】

【図 1】本発明にかかる表示装置の第 1 実施形態を示す模式的な平面図である。

【図 2】表示装置の典型例を示す参考図である。

【図 3】図 2 に示した表示装置の動作説明に供する模式図である。

【図 4】表示装置の製造方法を示す模式図である。

【図 5】表示装置の画面写真図である。

【図 6】表示装置の表示状態を示す模式図である。

【図 7】同じく表示状態を示す模式図である。

20

【図 8】本発明にかかる表示装置の第 2 実施形態を示す模式的な平面図である。

【図 9】図 8 に示した第 2 実施形態の動作説明に供する波形図である。

【図 10】同じく動作説明に供する波形図である。

【図 11】同じく動作説明に供する波形図である。

【図 12】本発明にかかる表示装置の第 3 実施形態を示す模式的な平面図である。

【図 13】表示装置の参考例を示すブロック図である。

30

【図 14】図 13 に示した参考例の動作説明に供するタイミングチャートである。

【図 15】本発明にかかる表示装置の第 4 実施形態を示す模式的な平面図である。

【図 16】第 4 実施形態の変形例を示す模式的な平面図である。

【図 17】本発明にかかる表示装置のデバイス構成を示す断面図である。

【図 18】本発明にかかる表示装置のモジュール構成を示す平面図である。

【図 19】本発明にかかる表示装置を備えたテレビジョンセットを示す斜視図である。

【図 20】本発明にかかる表示装置を備えたデジタルスチルカメラを示す斜視図である。

【図 21】本発明にかかる表示装置を備えたノート型パーソナルコンピュータを示す斜視図である。

【図 22】本発明にかかる表示装置を備えた携帯端末装置を示す模式図である。

【図 23】本発明にかかる表示装置を備えたビデオカメラを示す斜視図である。

【符号の説明】

【0054】

0 · · · パネル、1 · · · 画素アレイ部、2 · · · 画素、3 · · · セレクタ（信号回路）、4 · · · スキャナ（走査回路）、7 · · · 検査部、8 · · · スキャナ（走査回路）、100 · · · 基板、Trd · · · 駆動トランジスタ、Trt · · · 検査トランジスタ、EL · · · 発光素子

40

【図1】

【図2】

【図3】

【図4】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 7】

【図 1 8】

【図 1 9】

【図 2 0】

【図 2 1】

【図 2 3】

【図 2 2】

【図5】

## フロントページの続き

|              |              |            |

|--------------|--------------|------------|

| (51) Int.Cl. | F I          | テーマコード(参考) |

|              | G 09 G 3/20  | 6 4 2 A    |

|              | H 05 B 33/08 |            |

|              | H 05 B 33/14 | A          |

|              | G 09 G 3/20  | 6 7 0 J    |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置，其制造方法以及电子设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2009258414A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2009-11-05 |

| 申请号            | JP2008107690                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2008-04-17 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 甚田誠一郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 甚田 誠一郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H05B33/08 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/30.H G09G3/20.611.H G09G3/20.670.Q G09G3/20.621.M G09G3/20.680.G G09G3/20.642.A H05B33/08 H05B33/14.A G09G3/20.670.J G09G3/3225 G09G3/3266 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/CC45 3K107/EE03 3K107/GG56 3K107/HH02 3K107/IH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD15 5C080/DD30 5C080/JJ01 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5C080/KK02 5C080/KK07 5C080/KK43 5C380/AA01 5C380/AB06 5C380/AB18 5C380/AB24 5C380/AB34 5C380/AC08 5C380/AC09 5C380/BA14 5C380/BA21 5C380/BA22 5C380/BA38 5C380/BA39 5C380/BB01 5C380/BB04 5C380/BB21 5C380/CA12 5C380/CB37 5C380/CB40 5C380/CC02 5C380/CC04 5C380/CC09 5C380/CC27 5C380/CC30 5C380/CC48 5C380/CC61 5C380/CC72 5C380/DA50 5C380/FA03 5C380/FA18 5C380/FA20 5C380/FA22 5C380/FA28 5C380/GA05 5C380/GA08 5C380/GA17 5C380/HA12 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

### 摘要(译)

提供一种有源矩阵型显示装置，包括在基板上的检查装置。解决方案：用于执行显示的像素阵列部分1和用于执行检查的检查部分7布置在基板上。每个像素2至少包括驱动晶体管Trd和发光元件EL。驱动晶体管Trd根据视频信号输出驱动电流，发光元件EL根据驱动电流发光。检查单元7包括与像素2的每行或每列对应布置的多个检查晶体管Trt。测试晶体管Trt具有与相应行或列的像素2中包括的驱动晶体管Trd相同的特性。测量检查晶体管Trt的特性，并检查相应的驱动晶体管Trd的特性。点域1