(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-98989

(P2006-98989A)

(43) 公開日 平成18年4月13日(2006.4.13)

(51) Int.CI.

F 1

テーマコード(参考)

**G09G 3/30 (2006.01)**

**G09G 3/20 (2006.01)**

**H01L 51/50 (2006.01)**

G09G 3/30 J 3K007

G09G 3/30 K 5C080

G09G 3/20 621A

G09G 3/20 624B

G09G 3/20 641D

審査請求 未請求 請求項の数 11 O L (全 21 頁) 最終頁に続く

(21) 出願番号

特願2004-287888 (P2004-287888)

(22) 出願日

平成16年9月30日 (2004.9.30)

(71) 出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100094053

弁理士 佐藤 隆久

(72) 発明者 内野 勝秀

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 山下 淳一

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 豊村 直史

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

最終頁に続く

(54) 【発明の名称】画素回路、表示装置、および画素回路の駆動方法

## (57) 【要約】

【課題】発光素子の電流 - 電圧特性が経時変化しても、輝度劣化の無いソースフォロワー出力が行え、nチャネルトランジスタのソースフォロワー回路が可能となり、現状のアノード・カソード電極を用いたままで、nチャネルトランジスタをELの駆動素子として用いることができ、しかも黒浮きの発生を防止することができる画素回路、表示装置、および画素回路の駆動方法を提供する。

【解決手段】信号書き込み用スイッチとしてのTFT115, TFT1114を導通(オン)させ、その導通(オン)期間に回路電源用スイッチであるTFT113を導通(オン)させて導通期間をオーバラップさせ、その後TFT115, TFT1114をオフさせて、TFT1111に入るカップリング電圧をキャンセルする。

【選択図】 図10

**【特許請求の範囲】****【請求項 1】**

輝度情報に応じたデータ信号が供給されるデータ線と、

第1、第2、および第3の制御線と、

第1、第2、第3、および第4のノードと、

第1および第2の基準電位と、

ソースが上記第1のノードに接続され、ゲートが上記第2のノードに接続され、ドレンが上記第3のノードに接続された駆動トランジスタと、

上記データ線と上記第4のノードとの間に接続され、上記第1の制御線により導通制御される第1のスイッチと、

上記第2のノードと上記第3のノードとの間に接続され、上記第2の制御線により導通制御される第2のスイッチと、

上記第3のノードと上記第1の基準電位との間に接続され、上記第3の制御線により導通制御される第3のスイッチと、

上記第1のノードと第2の基準電位との間に接続された電気光学素子と、

上記第1のノードと上記第2のノードとの間に接続された第1のキャパシタと、

上記第2のノードと上記第4のノードとの間に接続された第2のキャパシタと、

上記電気光学素子が非発光期間に上記第1のノードの電位を固定電位に遷移させるための第1の回路と、

上記第2のスイッチを所定期間導通させてしきい値補正を行った後、上記第1のスイッチを所定期間導通させて、上記データ線の信号を取り入れて書き込み、かつ、上記第3のスイッチを導通させて上記書き込みデータに応じた輝度をもって上記電気光学素子を発光させる第2の回路と、を有し、

上記第2の回路は、上記第1のスイッチの導通期間と上記第3のスイッチの導通期間との少なくとも一部の期間をオーバラップするように導通制御する

画素回路。

**【請求項 2】**

上記第2の回路は、上記第1のスイッチを導通させ、当該第1のスイッチの導通期間に上記第3のスイッチを導通させて導通期間をオーバラップさせ、その後第1のスイッチをオフさせる

請求項1記載の画素回路。

**【請求項 3】**

上記第2の回路は、上記第3のスイッチを信号書き込み前に導通させ、当該第3のスイッチの導通期間内に上記第1のスイッチを所定期間だけ導通させて信号を書き込む

請求項1記載の画素回路。

**【請求項 4】**

上記第1の回路は、上記第1ノードと固定電位との間に接続され、上記第1の制御線により導通制御される第4のスイッチを含む

請求項1記載の画素回路。

**【請求項 5】**

上記第4のノードと固定電位との間に接続され、上記第2の制御線により導通制御される第5のスイッチを含む

請求項4記載の画素回路。

**【請求項 6】**

マトリクス状に複数配列された画素回路と、

上記画素回路のマトリクス配列に対して列毎に配線され、輝度情報に応じたデータ信号が供給されるデータ線と、

上記画素回路のマトリクス配列に対して行毎に配線された第1、第2、および第3の制御線と、

第1および第2の基準電位と、を有し、

10

20

30

40

50

上記画素回路は、

第1、第2、第3、および第4のノードと、

ソースが上記第1のノードに接続され、ゲートが上記第2のノードに接続され、ドレインが上記第3のノードに接続された駆動トランジスタと、

上記データ線と上記第4のノードとの間に接続され、上記第1の制御線により導通制御される第1のスイッチと、

上記第2のノードと上記第3のノードとの間に接続され、上記第2の制御線により導通制御される第2のスイッチと、

上記第3のノードと上記第1の基準電位との間に接続され、上記第3の制御線により導通制御される第3のスイッチと、

上記第1のノードと第2の基準電位との間に接続された電気光学素子と、

上記第1のノードと上記第2のノードとの間に接続された第1のキャパシタと、

上記第2のノードと上記第4のノードとの間に接続された第2のキャパシタと、

上記電気光学素子が非発光期間に上記第1のノードの電位を固定電位に遷移させるための第1の回路と、

上記第2のスイッチを所定期間導通させてしきい値補正を行った後、上記第1のスイッチを所定期間導通させて、上記データ線の信号を取り入れて書き込み、かつ、上記第3のスイッチを導通させて上記書き込みデータに応じた輝度をもって上記電気光学素子を発光させる第2の回路と、を有し、

上記第2の回路は、上記第1のスイッチの導通期間と上記第3のスイッチの導通期間との少なくとも一部の期間をオーバラップするように導通制御する

表示装置。

#### 【請求項7】

上記第2の回路は、上記第1のスイッチを導通させ、当該第1のスイッチの導通期間に上記第3のスイッチを導通させて導通期間をオーバラップさせ、その後第1のスイッチをオフさせる

請求項6記載の表示装置。

#### 【請求項8】

上記第2の回路は、上記第3のスイッチを信号書き込み前に導通させ、当該第3のスイッチの導通期間内に上記第1のスイッチを所定期間だけ導通させて信号を書き込む

請求項6記載の表示装置。

#### 【請求項9】

輝度情報に応じたデータ信号が供給されるデータ線と、

第1、第2、および第3の制御線と、

第1、第2、第3、および第4のノードと、

第1および第2の基準電位と、

ソースが上記第1のノードに接続され、ゲートが上記第2のノードに接続され、ドレインが上記第3のノードに接続された駆動トランジスタと、

上記データ線と上記第4のノードとの間に接続され、上記第1の制御線により導通制御される第1のスイッチと、

上記第2のノードと上記第3のノードとの間に接続され、上記第2の制御線により導通制御される第2のスイッチと、

上記第3のノードと上記第1の基準電位との間に接続され、上記第3の制御線により導通制御される第3のスイッチと、

上記第1のノードと第2の基準電位との間に接続された電気光学素子と、

上記第1のノードと上記第2のノードとの間に接続された第1のキャパシタと、

上記第2のノードと上記第4のノードとの間に接続された第2のキャパシタと、

上記電気光学素子が非発光期間に上記第1のノードの電位を固定電位に遷移させるための第1の回路と、有する画素回路の駆動方法であって、

上記第2のスイッチを所定期間導通させてしきい値補正を行った後、上記第1のスイッ

10

20

30

40

50

チを所定期間導通させて、上記データ線の信号を取り入れて書き込み、かつ、上記第3のスイッチを導通させて上記書き込みデータに応じた輝度をもって上記電気光学素子を発光させるに際し、上記第1のスイッチの導通期間と上記第3のスイッチの導通期間との少なくとも一部の期間をオーバラップするように導通制御する

画素回路の駆動方法。

#### 【請求項 10】

上記第1のスイッチを導通させ、当該第1のスイッチの導通期間に上記第3のスイッチを導通させて導通期間をオーバラップさせ、その後第1のスイッチをオフさせる

請求項9記載の画素回路の駆動方法。

#### 【請求項 11】

上記第3のスイッチを信号書き込み前に導通させ、当該第3のスイッチの導通期間内に上記第1のスイッチを所定期間だけ導通させて信号を書き込む

請求項9記載の画素回路の駆動方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、有機EL(Electroluminescence)ディスプレイなどの、電流値によって輝度が制御される電気光学素子を有する画素回路、およびこの画素回路がマトリクス状に配列された画像表示装置のうち、特に各画素回路内部に設けられた絶縁ゲート型電界効果トランジスタによって電気光学素子に流れる電流値が制御される、いわゆるアクティブマトリクス型画像表示装置、並びに画素回路の駆動方法に関するものである。 20

##### 【背景技術】

##### 【0002】

画像表示装置、たとえば液晶ディスプレイなどでは、多数の画素をマトリクス状に並べ、表示すべき画像情報に応じて画素毎に光強度を制御することによって画像を表示する。

これは有機ELディスプレイなどにおいても同様であるが、有機ELディスプレイは各画素回路に発光素子を有する、いわゆる自発光型のディスプレイであり、液晶ディスプレイに比べて画像の視認性が高い、バックライトが不要、応答速度が速い、等の利点を有する。

また、各発光素子の輝度はそれに流れる電流値によって制御することによって発色の階調を得る、すなわち発光素子が電流制御型であるという点で液晶ディスプレイなどとは大きく異なる。 30

##### 【0003】

有機ELディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として単純マトリクス方式とアクティブマトリクス方式とが可能であるが、前者は構造が単純であるものの、大型かつ高精細のディスプレイの実現が難しいなどの問題があるため、各画素回路内部の発光素子に流れる電流を、画素回路内部に設けた能動素子、一般にはTFT(Thin Film Transistor、薄膜トランジスタ)によって制御する、アクティブマトリクス方式の開発が盛んに行われている。

##### 【0004】

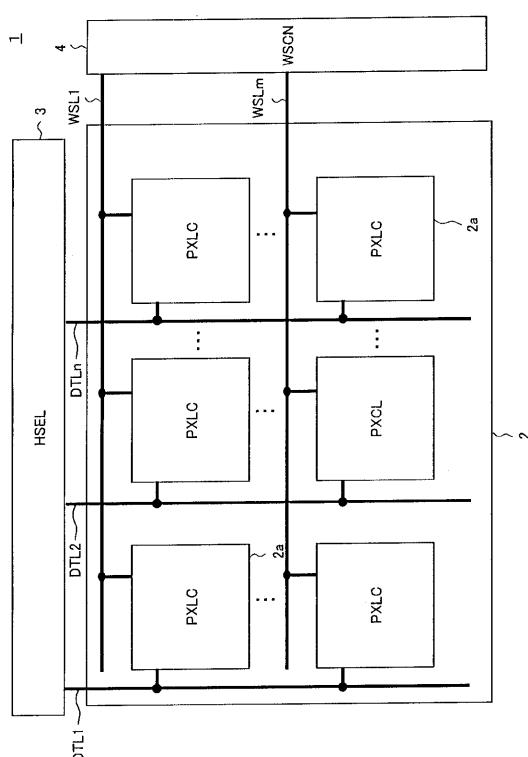

図1は、一般的な有機EL表示装置の構成を示すブロック図である。

この表示装置1は、図1に示すように、画素回路(PXL C)2aがm×nのマトリクス状に配列された画素アレイ部2、水平セレクタ(HSEL)3、ライトスキャナ(WSCN)4、水平セレクタ3により選択され輝度情報に応じたデータ信号が供給されるデータ線DTL1～DTLn、およびライトスキャナ4により選択駆動される走査線WSL1～WSLmを有する。

なお、水平セレクタ3はライトスキャナ4に関しては、多結晶シリコン上に形成する場合や、MOSIC等で画素の周辺に形成することもある。

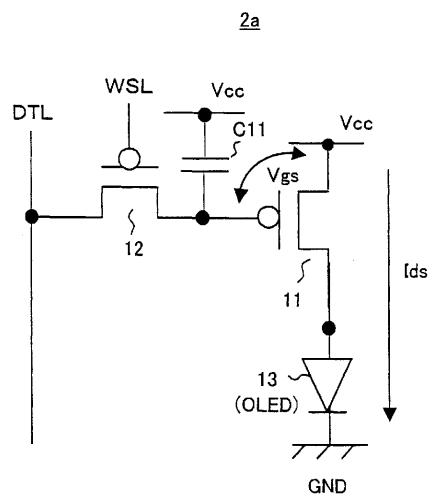

##### 【0005】

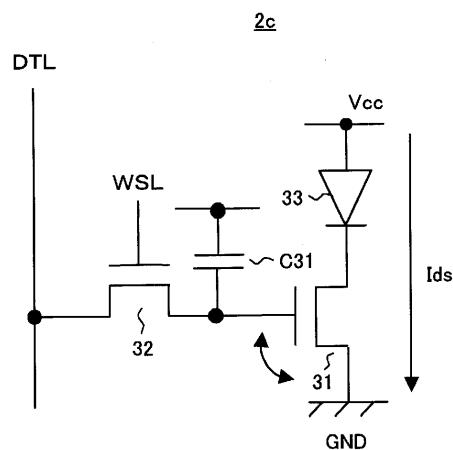

図2は、図1の画素回路2aの一構成例を示す回路図である(たとえば特許文献1、2

参照)。

図2の画素回路は、多数提案されている回路のうちで最も単純な回路構成であり、いわゆる2トランジスタ駆動方式の回路である。

#### 【0006】

図2の画素回路2aは、pチャネル薄膜電界効果トランジスタ(以下、TFTという)11およびTFT12、キャパシタC11、有機EL素子(OLED)である発光素子13を有する。また、図2において、DTLはデータ線を、WSLは走査線をそれぞれ示している。

有機EL素子は多くの場合整流性があるため、OLED(Organic Light Emitting Diode)と呼ばれることがあり、図2その他では発光素子としてダイオードの記号を用いているが、以下の説明においてOLEDには必ずしも整流性を要求するものではない。

図2ではTFT11のソースが電源電位VCCに接続され、発光素子13のカソード(陰極)は接地電位GNDに接続されている。図2の画素回路2aの動作は以下の通りである。

#### 【0007】

##### ステップST1:

走査線WSLを選択状態(ここでは低レベル)とし、データ線DTLに書き込み電位Vdataを印加すると、TFT12が導通してキャパシタC11が充電または放電され、TFT11のゲート電位はVdataとなる。

#### 【0008】

##### ステップST2:

走査線WSLを非選択状態(ここでは高レベル)とすると、データ線DTLとTFT11とは電気的に切り離されるが、TFT11のゲート電位はキャパシタC11によって安定に保持される。

#### 【0009】

##### ステップST3:

TFT11および発光素子13に流れる電流は、TFT11のゲート・ソース間電圧Vgsに応じた値となり、発光素子13はその電流値に応じた輝度で発光し続ける。

上記ステップST1のように、走査線WSLを選択してデータ線に与えられた輝度情報を画素内部に伝える操作を、以下「書き込み」と呼ぶ。

上述のように、図2の画素回路2aでは、一度Vdataの書き込みを行えば、次に書き換えられるまでの間、発光素子13は一定の輝度で発光を継続する。

#### 【0010】

上述したように、画素回路2aでは、ドライブトランジスタであるTFT11のゲート印加電圧を変化させることで、EL発光素子13に流れる電流値を制御している。

このとき、pチャネルのドライブトランジスタのソースは電源電位VCCに接続されており、このTFT11は常に飽和領域で動作している。よって、下記の式1に示した値を持つ定電流源となっている。

#### 【0011】

(数1)

$$I_{ds} = 1/2 \cdot \mu (W/L) C_o x (V_{gs} - |V_{th}|)^2 \quad \dots (1)$$

#### 【0012】

ここで、VthはTFTのしきい値、μはキャリアの移動度、Wはチャネル幅、Lはチャネル長、Coxは単位面積当たりのゲート容量、Vgsはゲート・ソース間電圧をそれぞれ示している。

#### 【0013】

単純マトリクス型画像表示装置では、各発光素子は、選択された瞬間にのみ発光するのに対し、アクティブマトリクスでは、上述したように、書き込み終了後も発光素子が発光を継続するため、単純マトリクスに比べて発光素子のピーク輝度、ピーク電流を下げられるなどの点で、とりわけ大型・高精細のディスプレイでは有利となる。

10

20

30

40

50

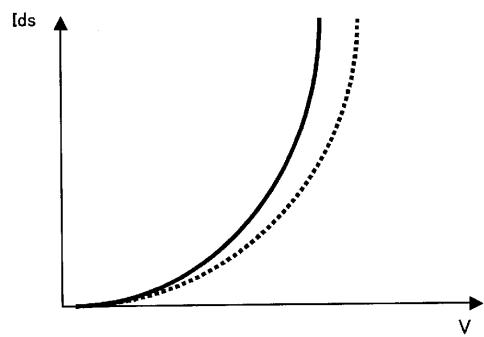

## 【0014】

図3は、有機EL素子の電流-電圧(I-V)特性の経時変化を示す図である。図3において、実線で示す曲線が初期状態時の特性を示し、破線で示す曲線が経時変化後の特性を示している。

## 【0015】

一般的に、有機EL素子のI-V特性は、図3に示すように、時間が経過すると劣化してしまう。

しかしながら、図2の2トランジスタ駆動は定電流駆動のために有機EL素子には上述したように定電流が流れ続け、有機EL素子のI-V特性が劣化してもその発光輝度は経時劣化することはない。

## 【0016】

ところで、図2の画素回路2aは、pチャネルのTFTにより構成されているが、nチャネルのTFTにより構成することができれば、TFT作成において従来のアモルファスシリコン(a-Si)プロセスを用いることができるようになる。これにより、TFT基板の低コスト化が可能となる。

## 【0017】

次に、トランジスタをnチャネルTFTに置き換えた画素回路について考察する。

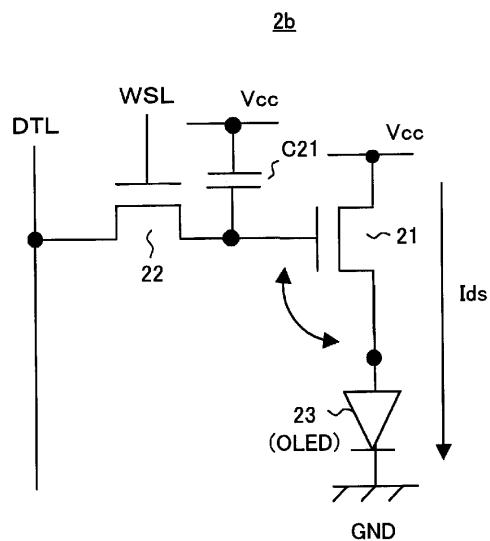

## 【0018】

図4は、図2の回路のpチャネルTFTをnチャネルTFTに置き換えた画素回路を示す回路図である。

## 【0019】

図4の画素回路2bは、nチャネルTFT21およびTFT22、キャパシタC21、有機EL素子(OLED)である発光素子23を有する。また、図4において、DTLはデータ線を、WSLは走査線をそれぞれ示している。

## 【0020】

この画素回路2bでは、ドライブトランジスタとしてTFT21のドレイン側が電源電位VCCに接続され、ソースはEL発光素子23のアノードに接続されており、ソースフォロワー回路を形成している。

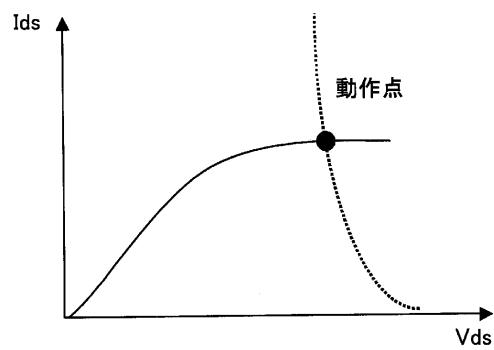

## 【0021】

図5は、初期状態におけるドライブトランジスタとしてのTFT21とEL素子23の動作点を示す図である。図5において、横軸はTFT21のドレイン・ソース間電圧Vdsを、縦軸はドレイン・ソース間電流Idsをそれぞれ示している。

## 【0022】

図5に示すように、ソース電圧はドライブトランジスタであるTFT21とEL発光素子23との動作点で決まり、その電圧はゲート電圧によって異なる値を持つ。

このTFT21は飽和領域で駆動されるので、動作点のソース電圧に対したVgsに関して上記式1に示した方程式の電流値の電流Idsを流す。

## 【特許文献1】U.S.P.5,684,365

## 【特許文献2】特開平8-234683号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

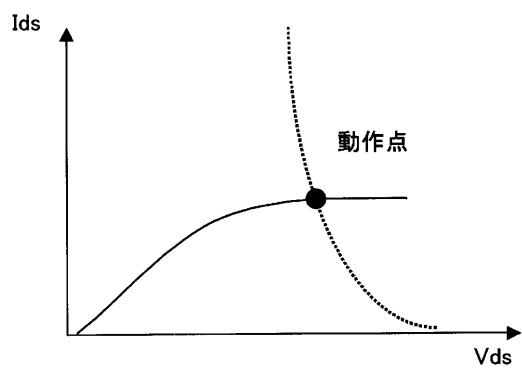

## 【0023】

しかしながら、ここでも同様にEL素子のI-V特性は経時劣化してしまう。図6に示すように、この経時劣化により動作点が変動してしまい、同じゲート電圧を印加していてもそのソース電圧は変動する。

これにより、ドライブトランジスタであるTFT21のゲート・ソース間電圧Vgsは変化してしまい、流れる電流値が変動する。同時にEL発光素子23に流れる電流値も変化するので、EL発光素子23のI-V特性が劣化すると、図4のソースフォロワー回路ではその発光輝度は経時変化してしまう。

## 【0024】

10

20

30

40

50

また、図7に示すように、ドライブトランジスタとしてのnチャネルTFT21のソースを接地電位GNDに接続し、ドレインをEL発光素子23のカソードに接続し、EL発光素子23のアノードを電源電位VCCに接続する回路構成も考えられる。

#### 【0025】

この方式では、図2のpチャネルTFTによる駆動と同様に、ソースの電位が固定されており、ドライブトランジスタとしてTFT21は定電流源として動作して、EL発光素子のI-V特性の劣化による輝度変化も防止できる。

#### 【0026】

しかしながら、この方式ではドライブトランジスタをEL発光素子のカソード側に接続する必要があり、このカソード接続は新規にアノード・カソードの電極の開発が必要であり、現状の技術では非常に困難であるとされている。

以上より、従来の方式では輝度変化のない、nチャネルトランジスタ使用の有機EL素子の開発はなされていなかった。

#### 【0027】

本発明は、かかる事情に鑑みてなされたものであり、その目的は、発光素子の電流-電圧特性が経時変化しても、輝度劣化の無いソースフォロワー出力が行え、nチャネルトランジスタのソースフォロワー回路が可能となり、現状のアノード・カソード電極を用いたままで、nチャネルトランジスタをELの駆動素子として用いることができる画素回路、表示装置、および画素回路の駆動方法を提供することにある。

#### 【課題を解決するための手段】

#### 【0028】

上記目的を達成するため、本発明の第1の観点の画素回路は、輝度情報に応じたデータ信号が供給されるデータ線と、第1、第2、および第3の制御線と、第1、第2、第3、および第4のノードと、第1および第2の基準電位と、ソースが上記第1のノードに接続され、ゲートが上記第2のノードに接続され、ドレインが上記第3のノードに接続された駆動トランジスタと、上記データ線と上記第4のノードとの間に接続され、上記第1の制御線により導通制御される第1のスイッチと、上記第2のノードと上記第3のノードとの間に接続され、上記第2の制御線により導通制御される第2のスイッチと、上記第3のノードと上記第1の基準電位との間に接続され、上記第3の制御線により導通制御される第3のスイッチと、上記第1のノードと第2の基準電位との間に接続された電気光学素子と、上記第1のノードと上記第2のノードとの間に接続された第1のキャパシタと、上記第2のノードと上記第4のノードとの間に接続された第2のキャパシタと、上記電気光学素子が非発光期間に上記第1のノードの電位を固定電位に遷移させるための第1の回路と、上記第2のスイッチを所定期間導通させてしきい値補正を行った後、上記第1のスイッチを所定期間導通させて、上記データ線の信号を取り入れて書き込み、かつ、上記第3のスイッチを導通させて上記書き込みデータに応じた輝度をもって上記電気光学素子を発光させる第2の回路と、を有し、上記第2の回路は、上記第1のスイッチの導通期間と上記第3のスイッチの導通期間との少なくとも一部の期間をオーバラップするように導通制御する。

#### 【0029】

好適には、上記第2の回路は、上記第1のスイッチを導通させ、当該第1のスイッチの導通期間に上記第3のスイッチを導通させて導通期間をオーバラップさせ、その後第1のスイッチをオフさせる。

#### 【0030】

好適には、上記第2の回路は、上記第3のスイッチを信号書き込み前に導通させ、当該第3のスイッチの導通期間内に上記第1のスイッチを所定期間だけ導通させて信号を書き込む。

#### 【0031】

好適には、上記第1の回路は、上記第1ノードと固定電位との間に接続され、上記第1の制御線により導通制御される第4のスイッチを含む。

10

20

30

40

50

## 【0032】

好適には、上記第4のノードと固定電位との間に接続され、上記第2の制御線により導通制御される第5のスイッチを含む。

## 【0033】

本発明の第2の観点の表示装置は、マトリクス状に複数配列された画素回路と、上記画素回路のマトリクス配列に対して列毎に配線され、輝度情報に応じたデータ信号が供給されるデータ線と、上記画素回路のマトリクス配列に対して行毎に配線された第1、第2、および第3の制御線と、第1および第2の基準電位と、を有し、上記画素回路は、第1、第2、第3、および第4のノードと、ソースが上記第1のノードに接続され、ゲートが上記第2のノードに接続され、ドレインが上記第3のノードに接続された駆動トランジスタと、上記データ線と上記第4のノードとの間に接続され、上記第1の制御線により導通制御される第1のスイッチと、上記第2のノードと上記第3のノードとの間に接続され、上記第2の制御線により導通制御される第2のスイッチと、上記第3のノードと上記第1の基準電位との間に接続され、上記第3の制御線により導通制御される第3のスイッチと、上記第1のノードと第2の基準電位との間に接続された電気光学素子と、上記第1のノードと上記第2のノードとの間に接続された第1のキャパシタと、上記第2のノードと上記第4のノードとの間に接続された第2のキャパシタと、上記電気光学素子が非発光期間に上記第1のノードの電位を固定電位に遷移させるための第1の回路と、上記第2のスイッチを所定期間導通させてしきい値補正を行った後、上記第1のスイッチを所定期間導通させて、上記データ線の信号を取り入れて書き込み、かつ、上記第3のスイッチを導通させて上記書き込みデータに応じた輝度をもって上記電気光学素子を発光させる第2の回路と、を有し、上記第2の回路は、上記第1のスイッチの導通期間と上記第3のスイッチの導通期間との少なくとも一部の期間をオーバラップするように導通制御する。10

## 【0034】

本発明の第3の観点は、輝度情報に応じたデータ信号が供給されるデータ線と、第1、第2、および第3の制御線と、第1、第2、第3、および第4のノードと、第1および第2の基準電位と、ソースが上記第1のノードに接続され、ゲートが上記第2のノードに接続され、ドレインが上記第3のノードに接続された駆動トランジスタと、上記データ線と上記第4のノードとの間に接続され、上記第1の制御線により導通制御される第1のスイッチと、上記第2のノードと上記第3のノードとの間に接続され、上記第2の制御線により導通制御される第2のスイッチと、上記第3のノードと上記第1の基準電位との間に接続され、上記第3の制御線により導通制御される第3のスイッチと、上記第1のノードと第2の基準電位との間に接続された電気光学素子と、上記第1のノードと上記第2のノードとの間に接続された第1のキャパシタと、上記第2のノードと上記第4のノードとの間に接続された第2のキャパシタと、上記電気光学素子が非発光期間に上記第1のノードの電位を固定電位に遷移させるための第1の回路と、有する画素回路の駆動方法であって、上記第2のスイッチを所定期間導通させてしきい値補正を行った後、上記第1のスイッチを所定期間導通させて、上記データ線の信号を取り入れて書き込み、かつ、上記第3のスイッチを導通させて上記書き込みデータに応じた輝度をもって上記電気光学素子を発光させるに際し、上記第1のスイッチの導通期間と上記第3のスイッチの導通期間との少なくとも一部の期間をオーバラップするように導通制御する。30

## 【0035】

本発明によれば、たとえば信号書き込み用第1のスイッチを導通させ、その導通期間に回路電源用第3のスイッチを導通させて導通期間をオーバラップさせ、その後第1のスイッチをオフさせる。これにより、駆動トランジスタに入るカップリング電圧をキャンセルしている。したがって、第1のスイッチをオフした後の発光期間においても駆動トランジスタのゲート・ソース電圧はV<sub>t h</sub>に保たれ、黒が浮くことなく表示される。

あるいは、たとえば回路電源用第3のスイッチを、信号書き込み前に導通させ、その後、信号書き込み用第1のスイッチを所定期間だけ導通させて信号を書き込むことにより黒浮きの発生が防止される。40

10

20

30

40

50

## 【0036】

また、本発明によれば、たとえば駆動トランジスタのソース電極を、スイッチを介して固定電位に接続し、ドライブトランジスタのゲートとソース間に画素容量を有することから、発光素子のI-V特性の経時劣化による輝度変化が補正される。

駆動トランジスタがnチャネルの場合に、固定電位を接地電位として、発光素子に印加する電位を接地電位にして発光素子の非発光期間が作り出される。

また、ソース電極と接地電位とを接続している第2のスイッチのオフ時間を調節することで、発光素子の発光・非発光の期間を調整し、Duty駆動が行われる。

また、固定電位を接地電位付近もしくはそれ以下の低電位にすること、もしくはゲート電圧を上げることで、固定電位に接続されるスイッチトランジスタのしきい値V<sub>th</sub>のバラツキに起因の画質劣化が抑制される。10

また、駆動トランジスタがpチャネルの場合に、固定電位を発光素子のカソード電極に接続されている電源電位として、発光素子に印加する電位を電源電位としてEL素子の非発光期間が作り出される。

そして、駆動トランジスタの特性をnチャネルとして、ソースフォロワーが可能となり、アノード接続ができる。

また、駆動トランジスタを全てnチャネル化することが可能となり、一般的なアモルファスシリコンのプロセスを導入することが可能となり、低コスト化が可能となる。15

## 【0037】

また、たとえば画素容量素子を駆動トランジスタのソースに接続し、非発光期間に容量の一方側を電源まで昇圧することで、パネル内部のTFT側にGND配線を有する必要が無くなる。20

また、本発明によれば、駆動トランジスタのゲート電極を、スイッチを介して固定電位に接続し、駆動トランジスタのゲートとソース間に画素容量を有することで、発光素子のI-V特性の経時劣化による輝度変化が補正される。

たとえば駆動トランジスタがnチャネルの場合に、固定電位を駆動トランジスタのドレイン電極が接続されている固定電位として画素内に固定電位は電源電位のみとする。25

## 【発明の効果】

## 【0038】

本発明によれば、黒浮きの発生を防止することができる。

また、EL発光素子のI-V特性が経時変化しても、輝度劣化の無いソースフォロワー出力が行える。

nチャネルトランジスタのソースフォロワー回路が可能となり、現状のアノード・カソード電極を用いたままで、nチャネルトランジスタを発光素子の駆動素子として用いることができる。

さらに、たとえば黒信号でも短時間にて信号線電圧を書き込むことができ、ユニフォーミティの高い画質を得ることができる。同時に信号線容量を増加させ、リーコ特性を抑制することができる。

また、本発明では固定電位に画素電源を使用することができるため、画素面積を小さくすることができ、パネルの高精細化が期待できる。40

さらにまた、発光素子の非発光時間に回路に電流を流さないことで消費電力の低減が可能となる。

## 【発明を実施するための最良の形態】

## 【0039】

以下、本発明の実施形態を添付図面に関連付けて説明する。

## 【0040】

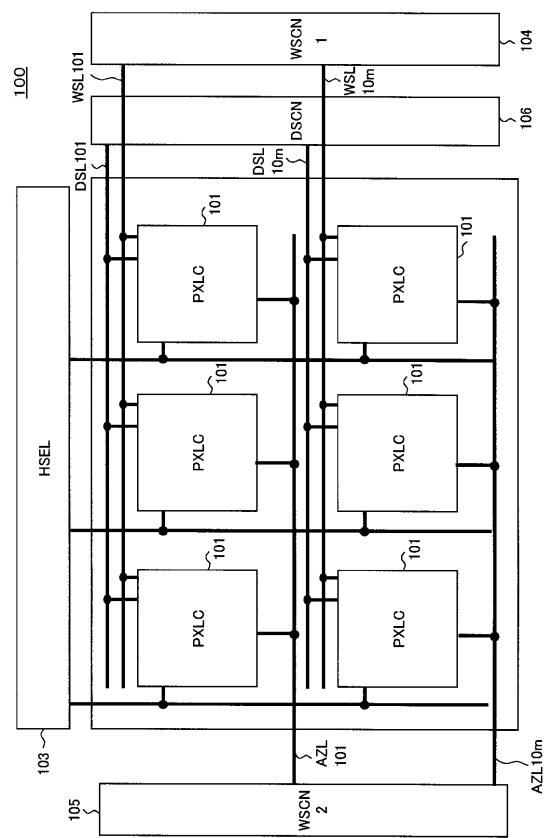

図8は、本実施形態に係る画素回路を採用した有機EL表示装置の構成を示すブロック図である。

図9は、図8の有機EL表示装置において本実施形態に係る画素回路の具体的な構成を50

示す回路図である。

【0041】

この表示装置100は、図8および図9に示すように、画素回路(PXL C)101がm×nのマトリクス状に配列された画素アレイ部102、水平セレクタ(HSEL)103、第1のライトスキャナ(WSCN1)104、第2のライトスキャナ(WSCN2)105、ドライブスキャナ(DSCN)106、水平セレクタ103により選択され輝度情報に応じたデータ信号が供給されるデータ線DTL101～DTL10n、ライトスキャナ104により選択駆動される走査線WSL101～WSL10m、ライトスキャナ105により選択駆動されるオートゼロ線AZL101～AZL10m、およびドライブスキャナ106により選択駆動される駆動線DSL101～DSL10mを有する。 10

【0042】

なお、画素アレイ部102において、画素回路101はm×nのマトリクス状に配列されるが、図9においては図面の簡単化のために2(=m)×3(=n)のマトリクス状に配列した例を示している。

また、図9においても、図面の簡単化のために一つの画素回路の具体的な構成を示している。

【0043】

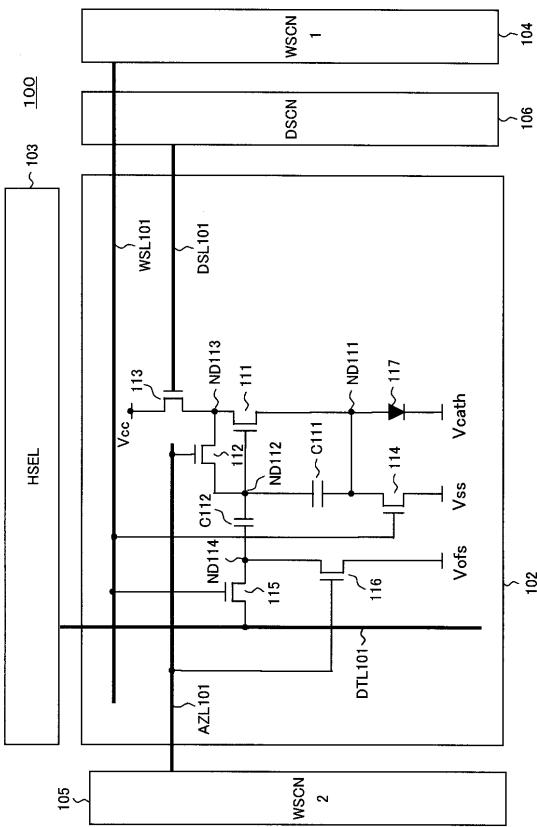

本実施形態に係る画素回路101は、図9に示すように、nチャネルTFT111～TFT116、第1のキャパシタC111、第2のキャパシタC112、有機EL素子(OLED：電気光学素子)からなる発光素子117、および第1のノードND111～第4のND114を有する。 20

また、図9において、DTL101はデータ線を、WSL101は走査線を、AZL101はオートゼロ線を、DSL101は駆動線をそれぞれ示している。

これらの構成要素のうち、TFT111が本発明に係る電界効果トランジスタを構成し、TFT112が第2のスイッチを構成し、TFT113が第3のスイッチを構成し、TFT114が第4のスイッチを構成し、TFT115が第1のスイッチを構成し、TFT116が第5のスイッチを構成している。また、水平セレクタ(HSEL)103、第1のライトスキャナ(WSCN1)104、第2のライトスキャナ(WSCN2)105、ドライブスキャナ(DSCN)106により本発明に係る第2の回路を構成している。 30

また、走査線WSL101が本発明に係る第1の制御線に対応し、駆動線DSL101が第2の制御線に対応し、オートゼロ線AZL101が第3の制御線に対応する。

また、電源電圧VCCの供給ライン(電源電位)が第1の基準電位に相当し、接地電位GNDが第2の基準電位に相当している。

【0044】

画素回路101において、TFT111のソースと第2の基準電位(本実施形態では接地電位GND)との間に発光素子(OLED)117が接続されている。具体的には、発光素子117のアノードがTFT111のソースに接続され、カソード側が接地電位GNDに接続されている。発光素子117のアノードとTFT111のソースとの接続点により第1のノードND111が構成されている。

TFT111のゲートが第2のノードND112に接続され、ドレインが第3のノードND113に接続され、TFT112のソース・ドレインが第3のノードND113(TFT111のドレイン)と第2のノードND112に接続されている。 40

そして、TFT113のソース・ドレインが第3のノードND113と電源電圧VCCの供給ラインに接続されている。

TFT111のソースがTFT114のドレインおよびキャパシタC111の第1電極に接続され、キャパシタC111の第2電極がノードND112に接続され、TFT114のソースが固定電位(本実施形態では接地電位GND)Vssに接続されている。

キャパシタC112の第1電極が第2のノードND112に接続され、第2電極が第4のノードND114に接続されている。

データ線DTL101と第4のノードND114に第1のスイッチとしてのTFT11 50

5 のソース・ドレインがそれぞれ接続されている。また、電圧（プリチャージ電圧） $V_{of}$  の供給ラインと第4のノード N D 1 1 4 に T F T 1 1 6 のソース・ドレインが接続されている。

そして、T F T 1 1 5 および T F T 1 1 4 のゲートが走査線 W S L 1 0 1 に接続され、T F T 1 1 3 および T F T 1 1 6 のゲートがオートゼロ線 A Z L 1 0 1 に接続され、T F T 1 1 3 のゲートが駆動線 D S L 1 0 1 に接続されている。

#### 【 0 0 4 5 】

このように、本実施形態に係る画素回路 1 0 1 は、ドライブトランジスタとしての T F T 1 1 1 のゲート・ソース間にキャパシタ C 1 1 1 が接続され、T F T 1 1 1 のソース電位をスイッチトランジスタとしての T F T 1 1 3 に介して固定電位に接続し、E L 発光素子 1 1 7 の I - V 特性の経時劣化による輝度変化を補正するように構成されている。10

さらに、本実施形態に係る画素回路 1 0 1 は、ドライブトランジスタとしての T F T 1 1 のゲート・ドレインを第2のスイッチとしての T F T 1 1 3 を介して接続することでドライブトランジスタとしての T F T 1 1 1 のしきい値電圧を容量に充電し、その容量を通じて入力電圧を T F T 1 1 1 のゲートにカッピングさせることで T F T 1 1 1 のしきい値電圧のバラツキを補正するように構成されている。

#### 【 0 0 4 6 】

さらに、本実施形態に係る画素回路 1 0 1 は、発光素子 1 1 7 を輝度に応じた電流によって発光させるにあたって、信号書き込み用スイッチとしての T F T 1 1 5 , T F T 1 1 4 を走査線 S C L 1 0 1 により導通させて信号を書き込んで T F T 1 1 5 , T F T 1 1 4 をオフさせた後に、回路電源用スイッチである T F T 1 1 3 を駆動線 D S L 1 0 1 により導通させるのではなく、信号書き込み用スイッチとしての T F T 1 1 5 , T F T 1 1 4 と回路電源用スイッチである T F T 1 1 3 の導通期間（オン期間）が必ずオーバラップするように第1のライトスキャナ 1 0 4 およびドライブスキャナ 1 0 6 により制御して、いわゆる黒浮き現象の発生を防止するように構成されている。20

信号書き込み用スイッチとしての T F T 1 1 5 , T F T 1 1 4 と回路電源用スイッチである T F T 1 1 3 の導通期間を必ずオーバラップさせる方法として、本実施形態においては、次の2つの方法を採用している。

第1の方法は、信号書き込み用スイッチとしての T F T 1 1 5 , T F T 1 1 4 を導通（オン）させ、その導通（オン）期間に回路電源用スイッチである T F T 1 1 3 を導通（オン）させて導通期間をオーバラップさせ、その後 T F T 1 1 5 , T F T 1 1 4 をオフさせて、T F T 1 1 1 に入るカッピング電圧をキャンセルし黒浮きの発生を防止する方法である。30

第2の方法は、回路電源用スイッチである T F T 1 1 3 を、信号書き込み前に導通（オン）させ、その後、信号書き込み用スイッチとしての T F T 1 1 5 , T F T 1 1 4 を所定期間だけ導通（オン）させて信号を書き込むことにより黒浮きの発生を防止する方法である。

#### 【 0 0 4 7 】

次に、上記構成の動作を、画素回路の動作を中心に、第1の方法を採用した場合の動作と、第2の方法を採用した場合の動作について説明する。40

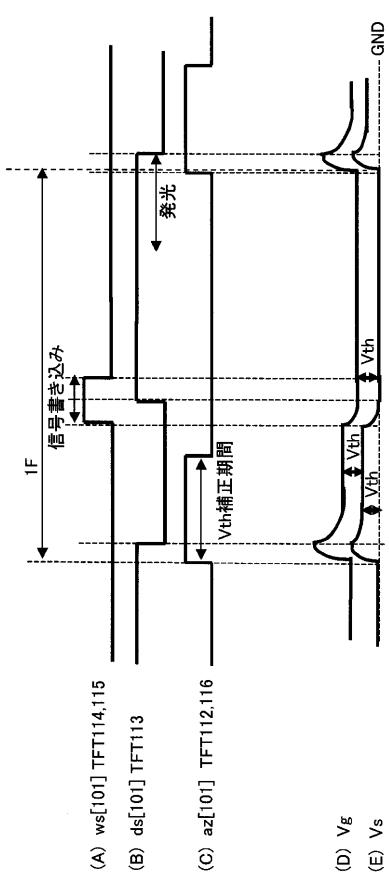

#### 【 0 0 4 8 】

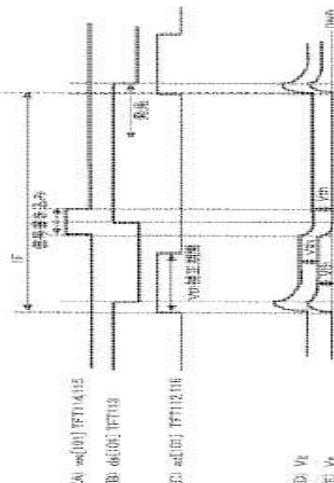

まず、第1の方法を採用した場合の動作を、図 1 0 ( A ) ~ ( E ) に関連付けて説明する。

なお、図 1 0 ( A ) は画素配列の第1行目の走査線 W S L 1 0 1 に印加される走査信号 w s [101] を、図 1 0 ( B ) は画素配列の第1行目の駆動線 D S L 1 0 1 に印加される駆動信号 d s [101] を、図 1 0 ( C ) は画素配列の第1行目のオートゼロ線 a z [101] を、図 1 0 ( D ) は T F T 1 1 1 のゲート電位 V g を、図 1 0 ( E ) は T F T 1 1 1 のソース電位 V s をそれぞれ示している。

#### 【 0 0 4 9 】

まず、通常の E L 発光素子 1 1 7 の発光状態時は、図 1 0 ( A ) ~ ( C ) に示すように

、第1のライトスキャナ104より走査線W<sub>S</sub>L101への走査信号w<sub>s</sub>[101]が選択的にローレベルに設定され、第2のライトスキャナ105よりオートゼロ線A<sub>Z</sub>L101へのオートゼロ信号a<sub>z</sub>[101]が選択的にローレベルに設定され、ドライブスキャナ106により駆動線D<sub>S</sub>L101への駆動信号d<sub>s</sub>[101]が選択的にハイレベルに設定される。

その結果、画素回路101においては、TFT112、TFT114～TFT116がオフした状態に保持される。

ドライブトランジスタとしてのTFT111は、飽和領域で動作するよう設計されており、EL発光素子117に流れる電流は、次式で示される値となる。

#### 【0050】

(数2)

$$I_{ds} = (V_{gs} - V_{th})^2 \quad \dots (2)$$

#### 【0051】

次に、図10(B),(C)に示すように、ドライブスキャナ106により駆動線D<sub>S</sub>L101への駆動信号d<sub>s</sub>[101]が選択的にハイレベルに設定されている状態で、第2のライトスキャナ105よりオートゼロ線A<sub>Z</sub>L101へのオートゼロ信号a<sub>z</sub>[101]が選択的にハイレベルに設定され後、ドライブスキャナ106により駆動線D<sub>S</sub>L101への駆動信号d<sub>s</sub>[101]が選択的にローレベルに設定される。

すなわち、TFT113がオン状態にある間に、TFT112とTFT116をオンさせた後、TFT113をオフさせる。ここで、発光素子117は非発光状態となる。

#### 【0052】

TFT112がオンしたことに伴い、TFT111のゲートとドレインはTFT112を介して接続されていることから、TFT111は飽和領域で動作する。

また、TFT111のゲート(第2のノードND112)には、容量C1,C2のキャパシタC111,C112が並列に接続されていることから、TFT111のゲート・ドレイン電圧は時間と共に緩やかに減少していく。

一定時間経過後、TFT111のゲート・ソース間電圧はTFT111のしきい値電圧(V<sub>th</sub>)となる。

このとき、キャパシタC112には(V<sub>ofs</sub>-V<sub>th</sub>)が充電され、キャパシタC111にはV<sub>th</sub>が充電される。

#### 【0053】

次に、図10(A)～(C)に示すように、TFT113～TFT115がオフした状態で、第2のライトスキャナ105よりオートゼロ線A<sub>Z</sub>L101へのオートゼロ信号a<sub>z</sub>[101]が選択的にローレベルに設定される。これにより、TFT112とTFT116がオフし、全てのスイッチとしてのTFT112～TFT116がオフ状態に保持される。

この状態で、第1のライトスキャナ104より走査線W<sub>S</sub>L101への走査信号w<sub>s</sub>[101]が選択的にハイレベルに設定される。これにより、TFT115とTFT114がオンする。

TFT115がオンしたことに伴い、水平セレクタ103によりデータ線D<sub>T</sub>L101に伝搬された入力信号(V<sub>in</sub>)が第4のノードND114に伝搬される。そして、第4のノードND114の電圧変化量がTFT111のゲートにカップリングされる。

カップリング容量Vは、キャパシタC111の容量C1、キャパシタC112の容量C2、およびTFT111の寄生容量C3によって次式のように決定される。

#### 【0054】

(数3)

$$V = V_{in} \times \{ C_2 / (C_1 + C_2 + C_3) \} \quad \dots (3)$$

#### 【0055】

キャパシタC111の容量C1とキャパシタC112の容量C2を、TFT111の寄生容量C3に比べて十分大きくとれば、TFT111のゲートへのカップリング容量はキャパシタC111の容量C1とキャパシタC112の容量C2のみによって決まる。

10

20

30

40

50

## 【0056】

また、図10(E)に示すように、TFT114がオンしたことに伴い、TFT111のソース電位Vsは接地電位GNDまで下降する。

## 【0057】

そして、TFT115とTFT114をオン状態に保持したまま、ドライブスキャナ106により駆動線DSL101への駆動信号ds[101]が選択的にハイレベルに設定される。これにより、TFT112がオンし、TFT115とTFT114のオン期間とTFT112のオン期間がオーバラップする。

## 【0058】

すなわち、TFT114がオン状態にあることからTFT111のソース電位Vsは接地電位GNDとなり、Vthを保っているキャパシタC111を介してTFT111のゲート電圧も下がる。

次に、TFT115とTFT114がオン状態中に、TFT112をオンさせる。

この場合、TFT115とTFT114がオン状態であるため、図10(D),(F)に示すように、TFT111のゲート電位、ソース電位が変動することなく一定の値に保持されており、この期間にTFT113がオンさせることから、TFT113をオンした際にTFT111のゲートに入るカップリングは起こらない。

また、TFT113がオンしたことに伴い、TFT111のドレインは電源電圧VCCの供給ラインに接続される。換言すれば、TFT111のドレイン電位は電源電圧VCCとなる。

## 【0059】

次に、図10(A),(B)に示すように、第1のライトスキャナ104より走査線WSL101への走査信号ws[101]が選択的にローレベルに設定される。これにより、TFT115とTFT114がオフする。

TFT114がオフしたことに伴い、図10(E)に示すように、ドライブトランジスタとしてのTFT111のソース電位Vsは上昇し、EL発光素子117にも電流が流れれる。

## 【0060】

TFT111は飽和領域で動作するように設計されていることから、TFT111のゲートにカップリングされている電圧量に応じた電流IdSが流れる。

TFT111のゲート・ソース間電圧は一定であるので、TFT111は一定電流IdSをEL発光素子117に流す。

これにより、第2のノードND112の電位は、EL発光素子117にIdSという電流が流れる電圧Vxまで上昇し、EL発光素子117は発光する。

このとき、上述したように、TFT113がオンした際に、TFT111のゲートに入るカップリングが生じていないことから、TFT115,TFT114をオフした後の発光期間においてもTFT111のゲート・ソース電圧はVthに保たれ、黒が浮くことなく表示される。

## 【0061】

本画素回路101において、EL発光素子117は、発光時間が長くなるとI-V特性は変化してしまう。そのため、第2のノードND112の電位も変化する。

しかしながら、TFT111のゲート・ソース間電圧は一定値に保たれていることから、EL発光素子117に流れる電流は変化しない。よって、EL発光素子117のI-V特性が劣化しても、一定電流IdSが流れ続け、EL発光素子117の輝度が変化することはない。

## 【0062】

ここで、画素回路101において、TFT115とTFT113をオンするタイミングについて、図11(A)～(E)に関連付けて考察する。

## 【0063】

図11(A)～(E)の動作タイミングは、本実施形態と異なり、キャパシタC111

10

20

30

40

50

にV<sub>t h</sub>を充電した後、TFT115（およびTFT114）をオンし、その後TFT113をオンさせている。

#### 【0064】

この場合、図11(A)～(E)に示すように、V<sub>t h</sub>補正完了後、TFT115およびTFT114をオンし、TFT111のソース電位を接地電位GNDとする。信号書き込み完了後、TFT115およびTFT114をオフし、その後TFT113をオンさせる。

TFT113をオンした瞬間、TFT113のオン電圧 V<sub>113</sub> に対して TFT111 のドレイン・ゲート間の寄生容量 C4 と、次式で示すキャパシタ C111 の容量 C1 で決まるカップリング電圧 V が TFT111 のゲートに飛び込む。

10

#### 【0065】

(数4)

$$V = V_{113} \times \{ C4 / (C1 + C4) \} \quad \dots (4)$$

#### 【0066】

黒表示の場合、いわゆるブートストラップ直前のTFT111のゲート・ソース電圧は v<sub>t h</sub> でなければならないのに対して、V の飛び込みにより、図11(E)に示すように、ゲート・ソース電圧が v<sub>t h</sub> + V の状態でブートストラップ動作が開始し、その結果、黒表示時に V の分だけ黒が浮いてしまう。

#### 【0067】

これに対して、本実施形態の第1の駆動方法によれば、信号書き込み用スイッチとしてのTFT115, TFT114を導通（オン）させ、その導通（オン）期間に回路電源用スイッチであるTFT113を導通（オン）させて導通期間をオーバラップさせ、その後 TFT115, TFT114をオフさせて、TFT111に入るカップリング電圧をキャンセルしている。

20

したがって、TFT115, TFT114をオフした後の発光期間においても TFT111 のゲート・ソース電圧は v<sub>t h</sub> に保たれ、黒が浮くことなく表示することが可能となる。

#### 【0068】

次に、第2の方法を採用した場合の動作を、図12(A)～(E)に関連付けて説明する。

30

なお、図12(A)は画素配列の第1行目の走査線 WSL101 に印加される走査信号 w<sub>s</sub>[101] を、図12(B)は画素配列の第1行目の駆動線 D<sub>S</sub>L101 に印加される駆動信号 d<sub>s</sub>[101] を、図12(C)は画素配列の第1行目のオートゼロ線 a<sub>z</sub>[101] を、図12(D)は TFT111 のゲート電位 V<sub>g</sub> を、図12(E)は TFT111 のソース電位 V<sub>s</sub> をそれぞれ示している。

#### 【0069】

まず、通常のEL発光素子117の発光状態時は、図12(A)～(C)に示すように、第1のライトスキャナ104より走査線 WSL101への走査信号 w<sub>s</sub>[101] が選択的にローレベルに設定され、第2のライトスキャナ105よりオートゼロ線 A<sub>Z</sub>L101へのオートゼロ信号 a<sub>z</sub>[101] が選択的にローレベルに設定され、ドライブスキャナ106により駆動線 D<sub>S</sub>L101への駆動信号 d<sub>s</sub>[101] が選択的にハイレベルに設定される。

40

その結果、画素回路101においては、TFT112、TFT114～TFT116がオフした状態に保持される。

ドライブトランジスタとしてのTFT111は、飽和領域で動作するように設計されており、EL発光素子117に流れる電流は、上記式(2)で示される値となる。

#### 【0070】

次に、図12(B), (C)に示すように、ドライブスキャナ106により駆動線 D<sub>S</sub>L101への駆動信号 d<sub>s</sub>[101] が選択的にハイレベルに設定されている状態で、第2のライトスキャナ105よりオートゼロ線 A<sub>Z</sub>L101へのオートゼロ信号 a<sub>z</sub>[101] が選択的にハイレベルに設定され後、ドライブスキャナ106により駆動線 D<sub>S</sub>L101への

50

駆動信号 d s [101] が選択的にローレベルに設定される。

すなわち、TFT113 がオン状態にある間に、TFT112 と TFT116 をオンさせた後、TFT113 をオフさせる。ここで、発光素子 117 は非発光状態となる。

#### 【0071】

TFT112 がオンしたことに伴い、TFT111 のゲートとドレインは TFT112 を介して接続されていることから、TFT111 は飽和領域で動作する。

また、TFT111 のゲート（第 2 のノード ND112）には、容量 C1, C2 のキャパシタ C111, C112 が並列に接続されていることから、TFT111 のゲート・ドレイン電圧は時間と共に緩やかに減少していく。

一定時間経過後、TFT111 のゲート・ソース間電圧は TFT111 のしきい値電圧 (Vth) となる。10

このとき、キャパシタ C112 には (Vofs - Vth) が充電され、キャパシタ C111 には Vth が充電される。

#### 【0072】

次に、図 12 (A) ~ (C) に示すように、TFT113 ~ TFT115 がオフした状態で、第 2 のライトスキャナ 105 よりオートゼロ線 AZL101 へのオートゼロ信号 az [101] が選択的にローレベルに設定される。これにより、TFT112 と TFT116 がオフし、全てのスイッチとしての TFT112 ~ TFT116 がオフ状態に保持される。20

この状態で、ドライブスキャナ 106 により駆動線 DSL101 への駆動信号 d s [101] が選択的にハイレベルに設定されて、TFT113 がオンとなる。

TFT113 がオンとなったことに伴い、TFT113 をオンした瞬間、TFT113 のオン電圧  $V_{113}$  に対して TFT111 のドレイン・ゲート間の寄生容量 C4 と、次式で示すキャパシタ C111 の容量 C1、キャパシタ C112 の容量 C2 で決まるカップリング電圧  $V$  が TFT111 のゲートに飛び込む。30

#### 【0073】

(数 5 )

$$V = V_{113} \times \{ C4 / (C1 + C2 + C4) \} \quad \dots (5)$$

#### 【0074】

このとき、TFT115, TFT114 はオフ状態にあることから、第 1 のノード ND111、第 4 のノード ND114 はフローティングの状態にあるので、第 2 のノード ND112 にキャパシタ C112 を介してカップリング電圧が飛び込み、第 2 のノード ND112 の電位は上昇する。30

#### 【0075】

TFT113 をオンさせた状態で、第 1 のライトスキャナ 104 より走査線 WSL101 への走査信号 ws [101] が選択的にハイレベルに設定される。これにより、TFT115 と TFT114 がオンする。

TFT115 がオンして黒信号を書き込んだ瞬間、第 2 のノード ND112 は、TFT113 からのカップリング電圧を含んだ電圧から黒信号の電圧となり、TFT111 のゲートにマイナスのカップリング電圧が飛び込み、キャパシタ C111 には再び Vth が保持される。40

また、TFT114 もオンしたことにより、TFT111 のソース電位 Vs は接地電位 GND まで下降し。キャパシタ C111 の保持電位 Vth を保ちながら TFT111 のゲート電位も下がる。

#### 【0076】

その後、図 12 (A), (B) に示すように、第 1 のライトスキャナ 104 より走査線 WSL101 への走査信号 ws [101] が選択的にローレベルに設定される。これにより、TFT115 と TFT114 がオフし、EL 発光素子 117 のドライブトランジスタである TFT111 が Vth を保ちながら、ポートストラップ発光期間を迎え、正常に黒表示が行われる。50

## 【0077】

なお、このとき、第1の方法のとき同様に、TFT114がオフしたことに伴い、図2(E)に示すように、ドライブトランジスタとしてのTFT111のソース電位Vsは上昇し、EL発光素子117にも電流が流れる。

## 【0078】

TFT111は飽和領域で動作するように設計されていることから、TFT111のゲートにカップリングされている電圧量に応じた電流Idsが流れる。

TFT111のゲート・ソース間電圧は一定であるので、TFT111は一定電流IdsをEL発光素子117に流す。

これにより、第2のノードND112の電位は、EL発光素子117にIdsという電流が流れる電圧Vxまで上昇し、EL発光素子117は発光する。 10

このとき、TFT111のゲート・ソース電圧はVthに保たれ、黒が浮くことなく表示される。

## 【0079】

本画素回路101において、EL発光素子117は、発光時間が長くなるとI-V特性は変化してしまう。そのため、第2のノードND112の電位も変化する。

しかしながら、TFT111のゲート・ソース間電圧は一定値に保たれていることから、EL発光素子117に流れる電流は変化しない。よって、EL発光素子117のI-V特性が劣化しても、一定電流Idsが流れ続け、EL発光素子117の輝度が変化することはない。 20

## 【0080】

本実施形態の第2の駆動方法によれば、回路電源用スイッチであるTFT113を、信号書き込み前に導通(オン)させ、その後、信号書き込み用スイッチとしてのTFT115、TFT114を所定期間だけ導通(オン)させて信号を書き込むことにより黒浮きの発生を防止することができる。

## 【0081】

また、本実施形態によれば、ドライブトランジスタとしてのTFT111のソースが発光素子117のアノードに接続され、ドレンがTFT113を介して電源電位VCCに接続され、TFT111のゲート・ソース間にキャパシタC111が接続され、TFT111のソース電位をスイッチトランジスタとしてのTFT114に介して固定電位に接続するよう構成されていることから、以下の効果を得ることができる。 30

EL発光素子のI-V特性が経時変化しても、輝度劣化の無いソースフォロワー出力が行える。

nチャネルトランジスタのソースフォロワー回路が可能となり、現状のアノード・カソード電極を用いたままで、nチャネルトランジスタをEL発光素子の駆動素子として用いることができる。

また、nチャネルのみで画素回路のトランジスタを構成することができ、TFT作成においてa-Siプロセスを用いることができるようになる。これにより、TFT基板の低コスト化が可能となる。

## 【図面の簡単な説明】

## 【0082】

【図1】一般的な有機EL表示装置の構成を示すブロック図である。

【図2】図1の画素回路の一構成例を示す回路図である。

【図3】有機EL素子の電流-電圧(I-V)特性の経時変化を示す図である。

【図4】図2の回路のpチャネルTFTをnチャネルTFTに置き換えた画素回路を示す回路図である。

【図5】初期状態におけるドライブトランジスタとしてのTFTとEL素子の動作点を示す図である。

【図6】経時変化後のドライブトランジスタとしてのTFTとEL素子の動作点を示す図である。 40

【図7】ドライブトランジスタとしてのnチャネルTFTのソースを接地電位に接続した画素回路を示す回路図である。

【図8】本実施形態に係る画素回路を採用した有機EL表示装置の構成を示すブロック図である。

【図9】図1の有機EL表示装置において本実施形態に係る画素回路の具体的な構成を示す回路図である。

【図10】第1の駆動方法による図2の回路の動作を説明するためのタイミングチャートである。

【図11】従来の駆動方法による図2の回路の動作を説明するためのタイミングチャートである。

【図12】第2の駆動方法による図2の回路の動作を説明するためのタイミングチャートである。

#### 【符号の説明】

#### 【0083】

100...表示装置、101...画素回路(PXLC)、102...画素アレイ部、103...水平セレクタ(HSEL)、104...第1のライトスキャナ(WSCN1)、105...第2のライトスキャナ(WSCN2)、106...ドライブスキャナ(DSCN)、DTL101~DTL10n...データ線、WSL101~WSL10m...走査線、AZL101~AZL10m...オートゼロ線、DSL101~DSL10m...駆動線、111~116...TFT、117...発光素子、ND111~ND114...ノード。

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図 12】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 7 0 J

H 0 5 B 33/14 AF ターム(参考) 3K007 AB11 AB17 BA06 DB03 GA00 GA04

5C080 AA06 BB05 DD03 DD29 EE28 EE29 FF11 JJ02 JJ03 JJ04

JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路，显示装置和像素电路的驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">JP2006098989A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2006-04-13 |

| 申请号            | JP2004287888                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2004-09-30 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 内野勝秀<br>山下淳一<br>豊村直史                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 内野 勝秀<br>山下 淳一<br>豊村 直史                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| F1分类号          | G09G3/30.J G09G3/30.K G09G3/20.621.A G09G3/20.624.B G09G3/20.641.D G09G3/20.670.J H05B33/14.A G09G3/20.622.D G09G3/3233 G09G3/3266 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 3K007/AB11 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 5C080/AA06 5C080/BB05 5C080/DD03 5C080/DD29 5C080/EE28 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 3K107/AA01 3K107/BB01 3K107/CC14 3K107/CC21 3K107/CC35 3K107/EE04 3K107/HH02 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AA03 5C380/AB06 5C380/AB22 5C380/AB23 5C380/AC04 5C380/BA01 5C380/BA10 5C380/BA28 5C380/BA38 5C380/BA39 5C380/BB08 5C380/BB23 5C380/BD01 5C380/CA12 5C380/CB16 5C380/CB18 5C380/CB26 5C380/CB31 5C380/CC02 5C380/CC04 5C380/CC26 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC61 5C380/CC62 5C380/CC64 5C380/CD012 5C380/CD026 5C380/DA02 5C380/DA06 5C380/DA20 |         |            |

| 代理人(译)         | 佐藤隆久                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 其他公开文献         | <a href="#">JP4639730B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

### 摘要(译)

要解决的问题：即使发光元件的电流-电压特性随时间变化，也要进行源极跟随器输出而亮度不会降低，并使n沟道晶体管的源极跟随器电路成为可能。提供了一种像素电路，显示装置以及用于驱动像素电路的方法，其可以将沟道晶体管用作EL驱动元件并且可以防止黑色浮动。解决方案：将TFT 115和作为信号写入开关的TFT 114导通(ON)，作为电路电源开关的TFT 113在导通(ON)期间与导通周期重叠，使其导通(ON)，然后TFT 115，TFT 114截止以消除进入TFT 111的耦合电压。[选择图]图10