(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-235491

(P2005-235491A)

(43) 公開日 平成17年9月2日(2005.9.2)

(51) Int.Cl.<sup>7</sup>

**H05B 33/14**

**H05B 33/12**

**H05B 33/22**

**H05B 33/26**

F 1

H05B 33/14

H05B 33/12

H05B 33/22

H05B 33/26

テーマコード(参考)

A 3K007

B

Z

Z

審査請求 未請求 請求項の数 19 O L (全 30 頁)

(21) 出願番号

特願2004-41299 (P2004-41299)

(22) 出願日

平成16年2月18日(2004.2.18)

(71) 出願人 000003067

TDK株式会社

東京都中央区日本橋1丁目13番1号

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100095407

弁理士 木村 满

(74) 代理人 100109449

弁理士 毛受 隆典

(72) 発明者 高山 一郎

東京都中央区日本橋一丁目13番1号 TDK株式会社内

最終頁に続く

(54) 【発明の名称】画像表示装置

## (57) 【要約】

【課題】メタルマスクを使用して上部画素電極用補助配線を作成するとコスト上昇を招く。また、パーティクルの発生を抑制することが困難であり、リーク、ダークスפוטタなどの不良が生じて、画像表示装置の欠陥となりやすい。

【解決手段】メタルマスクを使用せずに補助配線を形成し、アクティブ型有機ELディスプレイ基板の下部画素電極と同一面上に表面が荒れた補助配線を形成し、上部画素電極との接続を可能とする。また、補助配線上に構造体を形成して上部画素電極との接続を可能とする。これにより、簡単な構造でアクティブ型有機EL画像表示装置を実現し、リーク、ダークスポット発生を低減することができ、十分な発光領域により画像装置の表示品位を確保することが可能となる。上部画素電極が不透明電極で下部画素電極が透明な場合でも、上部画素電極の配線抵抗を下げることができる。

【選択図】図7

**【特許請求の範囲】****【請求項 1】**

一对の基板と、

前記一对の基板の一方の側に形成されたトランジスタと、

前記一对の基板の間に形成され、少なくともいずれか一つは光を透過する一对の画素電極と、

前記一对の画素電極間に挟持された発光層と、

前記発光層からなる画素が、前記一对の基板の間に少なくともひとつ以上形成された画像表示装置において、

前記一对の画素電極のうちの一方が、前記トランジスタのドレイン電極と接続されており、

前記トランジスタと前記ドレイン電極と接続された画素電極の間には、絶縁膜が形成されており、

前記絶縁膜上において、前記ドレイン電極と接続された画素電極と電気的に絶縁され、かつ、

前記一对の画素電極のうちの他方の画素電極と電気的に接続された補助配線が形成されていることを特徴とする画像表示装置。

**【請求項 2】**

前記補助配線は、前記他方の画素電極と電気的に接続された部分において、前記発光層の膜厚の半分以上の局所的な凸部を有していることを特徴とする請求項 1 に記載の画像表示装置。

**【請求項 3】**

前記補助配線は、前記他方の画素電極と電気的に接続された部分において、接触抵抗が、500K 以下であることを特徴とする請求項 1 に記載の画像表示装置。

**【請求項 4】**

前記発光層が、有機EL発光素子材料で形成されていることを特徴とする請求項 1 に記載の画像表示装置。

**【請求項 5】**

基板上に一对の画素電極を有し、

前記一对の画素電極の少なくとも一方が、光を透過する画素電極であり、前記画素電極間に挟持された発光層を有する画素が、少なくとも 1 個以上前記基板上に形成された画像表示装置であって、

前記画素電極の基板側に形成された下部画素電極が、前記基板上に形成された薄膜トランジスタのドレイン電極と接続されており、

前記薄膜トランジスタおよび前記薄膜トランジスタのソース電極およびゲート電極と接続される配線上に絶縁膜が形成されており、

前記絶縁膜上において、前記下部画素電極が形成されており、

前記下部画素電極と電気的に絶縁されており、かつ、前記下部画素電極と対をなす上部画素電極用補助配線が、前記絶縁膜上において、前記下部画素電極に隣接して形成されており、

前記上部画素電極用補助配線は前記上部画素電極と接続されてなることを特徴とする画像表示装置。

**【請求項 6】**

前記上部画素電極用補助配線と前記上部画素電極の接触抵抗が、500K 以下であり、前記補助配線を形成する導電材料の表面粗さが 3 nm 以上で、かつ、P-V 値が 30 nm 以上であることを特徴とする請求項 5 に記載の画像表示装置。

**【請求項 7】**

前記上部画素電極用補助配線と前記上部画素電極の接触抵抗が、500K 以下であり、前記補助配線を形成する導電材料の表面粗さが 15 nm 以上であることを特徴とする請求項 5 に記載の画像表示装置。

10

20

30

40

50

## 【請求項 8】

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、500K以下であり、前記補助配線を形成する導電材料がP-V値30nm以上であり、かつ、それぞれの間隔が40mm以下の突起状の表面を有することを特徴とする請求項5に記載の画像表示装置。

## 【請求項 9】

前記発光層が、有機EL発光素子材料で形成されていることを特徴とする請求項5に記載の画像表示装置。

## 【請求項 10】

一対の基板と、

前記一対の基板の一方の側に形成されたトランジスタと、

前記一対の基板の間に形成され、少なくともいずれか一つは光を透過する一対の画素電極と、

前記一対の画素電極間に挟持された発光層と、

前記発光層からなる画素が、前記一対の基板の間に少なくともひとつ以上形成された画像表示装置において、

前記一対の画素電極のうちの一方が、前記トランジスタのドレイン電極と接続されており、

前記トランジスタと前記ドレイン電極と接続された画素電極の間には、絶縁膜が形成されており、

前記絶縁膜上において、前記ドレイン電極と接続された画素電極と電気的に絶縁され、かつ、

前記一対の画素電極のうちの他方の画素電極と電気的に接続された補助配線が形成されており、

前記補助配線上には、構造体が形成されていることを特徴とする画像表示装置。

## 【請求項 11】

前記補助配線は、前記他方の画素電極と電気的に接続された部分において、接触抵抗が、500K以下であることを特徴とする請求項10に記載の画像表示装置。

## 【請求項 12】

前記発光層が、有機EL発光素子材料で形成されていることを特徴とする請求項10に記載の画像表示装置。

## 【請求項 13】

基板上に一対の画素電極を有し、

前記一対の画素電極の少なくとも一方が、光を透過する画素電極であり、前記画素電極間に挟持された発光層を有する画素が、少なくとも1個以上前記基板上に形成された画像表示装置であって、

前記画素電極の基板側に形成された下部画素電極が、前記基板上に形成された薄膜トランジスタのドレイン電極と接続されており、

前記薄膜トランジスタおよび前記薄膜トランジスタのソース電極およびゲート電極と接続される配線上に絶縁膜が形成されており、

前記絶縁膜上において、前記下部画素電極が形成されており、

前記下部画素電極と電気的に絶縁されており、かつ、前記下部画素電極と対をなす上部画素電極用補助配線が、前記絶縁膜上において、前記下部画素電極に隣接して形成されており、

前記上部画素電極用補助配線は前記上部画素電極と接続されており、

前記補助配線上には、構造体が形成されていることを特徴とする画像表示装置。

## 【請求項 14】

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、500K以下であり、前記構造体はオーバーハング形状の絶縁性構造体として形成され、該構造体の下部幅が、前記補助配線より狭いことを特徴とする請求項13に記載の画像表示装置。

## 【請求項 15】

10

20

30

40

50

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、500K以下であり、前記構造体は絶縁性構造体であることを特徴とする請求項13に記載の画像表示装置。

【請求項16】

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、500K以下であり、前記構造体は導電性構造体であることを特徴とする請求項13に記載の画像表示装置。

【請求項17】

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、500K以下であり、前記構造体は導電性構造体であって、前記下部画素電極と同一の材料で形成されていることを特徴とする請求項13に記載の画像表示装置。

【請求項18】

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、500K以下であり、前記構造体はオーバーハング形状であることを特徴とする請求項13に記載の画像表示装置。

【請求項19】

前記発光層が、有機EL発光素子材料で形成されていることを特徴とする請求項13に記載の画像表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はカーステレオ、携帯機器などに使用される画像表示装置に関する。

20

【背景技術】

【0002】

薄膜表示装置を実現する場合、透明絶縁基板側から光を取り出す構造が主流となっている。しかしながら、この構造だと開口率を上げるには限界があり、基板の反対側から光を取り出す、トップエミッション型の構造が提案されている。本構造では上部画素電極には光を取り出す電極が必須となる。このような電極を実現するには透明電極と金属の積層構造が採用される（たとえば、特許文献1参照）。

【0003】

しかしながら、このような構造の場合、抵抗を十分に下げ可視光に対する透過率を確保するには限界がある。そこで、透明電極用補助配線を形成する技術もあり、これによれば、抵抗を十分に下げることが可能であり、透過率の確保も可能である（たとえば、特許文献2参照）。

30

【特許文献1】特開平10-294182号公報

【特許文献2】特開2001-230086号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、上述の構造では有機層を蒸着する場合に、シャドーマスクを使用する必要があり、シャドーマスクの位置合わせを真空室で行う必要がある。また、シャドーマスクを使用するので、基板と非接触にすることは不可能に近く、ゴミの発生する確率が非常に高く、ダーツスポットと呼ばれる黒点やリークの原因となってしまう。シャドーマスクを使用した場合には、ゴミの発生する確率が高く、位置合わせを真空中で行う必要があり、成膜装置にマスクアライメント機能を取り付ける必要があるからである。この方法では装置のコストが高くなる上に、ゴミの発生による、リーク、ダーツスポット発生は避けられない。

【0005】

また、シャドーマスクは、通常金属で形成されることが多く、マスクの撓みを考慮するとマスクサイズを大きくするには限界があるからである。特に開口部が大きいマスクでは、十分な強度を得ることは困難であり、必然的に基板サイズを大きくすることは不可能である。

40

50

**【 0 0 0 6 】**

さらに、高精細を実現するにはマスク金属部分が極端に細くなってしまい、マスクの撓みが発生して、高精細化にも限界がある。そこで、本発明ではシャドーマスクを使用せず、基板側に補助配線を形成することで、上述した課題を解決するものである。

**【課題を解決するための手段】****【 0 0 0 7 】**

上記目的を達成するため、本願における電子装置の第一の解決手段として代表的な発明は、一対の基板と、一対の基板の一方の側に形成されたトランジスタと、一対の基板の間に形成され、少なくともいずれか一つは光を透過する一対の画素電極と、一対の画素電極間に挟持された発光層と、発光層からなる画素が、一対の基板の間に少なくともひとつ以上形成された画像表示装置において、一対の画素電極のうちの一方が、トランジスタのドレイン電極と接続されており、トランジスタとドレイン電極と接続された画素電極の間に、絶縁膜が形成されており、絶縁膜上において、ドレイン電極と接続された画素電極と電気的に絶縁され、かつ、一対の画素電極のうちの他方の画素電極と電気的に接続された補助配線が形成されていることを特徴とする。

**【 0 0 0 8 】**

前記補助配線は、他方の画素電極と電気的に接続された部分において、発光層の膜厚の半分以上の局所的な凸部を有していることを特徴としてもよい。

**【 0 0 0 9 】**

前記補助配線は、他方の画素電極と電気的に接続された部分において、接触抵抗が、5 20 00 K 以下であることを特徴としてもよい。

**【 0 0 1 0 】**

前記発光層が、有機 E L 発光素子材料で形成されていることを特徴としてもよい。

**【 0 0 1 1 】**

また、本願の第二の解決手段として代表的な発明は、基板上に一対の画素電極を有し、一対の画素電極の少なくとも一方が、光を透過する画素電極であり、画素電極間に挟持された発光層を有する画素が、少なくとも 1 個以上基板上に形成された画像表示装置であって、画素電極の基板側に形成された下部画素電極が、基板上に形成された薄膜トランジスタのドレイン電極と接続されており、薄膜トランジスタおよび薄膜トランジスタのソース電極およびゲート電極と接続される配線上に絶縁膜が形成されており、絶縁膜上において、下部画素電極が形成されており、下部画素電極と電気的に絶縁されており、かつ、下部画素電極と対をなす上部画素電極用補助配線が、絶縁膜上において、下部画素電極に隣接して形成されており、上部画素電極用補助配線は上部画素電極と接続されてなることを特徴とする。

**【 0 0 1 2 】**

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、5 0 0 K 以下であり、補助配線を形成する導電材料の表面粗さが 3 nm 以上で、かつ、P - V 値が 3 0 nm 以上であることを特徴としてもよい。

**【 0 0 1 3 】**

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、5 0 0 K 以下であり、補助配線を形成する導電材料の表面粗さが 1 5 nm 以上であることを特徴としてもよい。

**【 0 0 1 4 】**

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、5 0 0 K 以下であり、補助配線を形成する導電材料が P - V 値 3 0 nm 以上であり、かつ、それぞれの間隔が 4 0 mm 以下の突起状の表面を有することを特徴としてもよい。

**【 0 0 1 5 】**

前記発光層が、有機 E L 発光素子材料で形成されていることを特徴としてもよい。

**【 0 0 1 6 】**

また、本願の第三の解決手段として代表的な発明は、一対の基板と、一対の基板の一方の側に形成されたトランジスタと、一対の基板の間に形成され、少なくともいずれか一つ

は光を透過する一对の画素電極と、一对の画素電極間に挟持された発光層と、発光層からなる画素が、一对の基板の間に少なくともひとつ以上形成された画像表示装置において、一对の画素電極のうちの一方が、トランジスタのドレイン電極と接続されており、トランジスタとドレイン電極と接続された画素電極の間には、絶縁膜が形成されており、絶縁膜上において、ドレイン電極と接続された画素電極と電気的に絶縁され、かつ、一对の画素電極のうちの他方の画素電極と電気的に接続された補助配線が形成されており、補助配線上には、構造体が形成されていることを特徴とする。

## 【0017】

前記補助配線は、他方の画素電極と電気的に接続された部分において、接触抵抗が、500K以下であることを特徴としてもよい。

10

## 【0018】

前記発光層が、有機EL発光素子材料で形成されていることを特徴としてもよい。

## 【0019】

また、本願の第四の解決手段として代表的な発明は、基板上に一对の画素電極を有し、一对の画素電極の少なくとも一方が、光を透過する画素電極であり、画素電極間に挟持された発光層を有する画素が、少なくとも1個以上基板上に形成された画像表示装置であって、画素電極の基板側に形成された下部画素電極が、基板上に形成された薄膜トランジスタのドレイン電極と接続されており、薄膜トランジスタおよび薄膜トランジスタのソース電極およびゲート電極と接続される配線上に絶縁膜が形成されており、絶縁膜上において、下部画素電極が形成されており、下部画素電極と電気的に絶縁されており、かつ、下部画素電極と対をなす上部画素電極用補助配線が、絶縁膜上において、下部画素電極に隣接して形成されており、上部画素電極用補助配線は上部画素電極と接続されており、補助配線上には、構造体が形成されていることを特徴とする。

20

## 【0020】

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、500K以下であり、構造体はオーバーハング形状の絶縁性構造体として形成され、該構造体の下部幅が、補助配線より狭いことを特徴としてもよい。

30

## 【0021】

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、500K以下であり、構造体は絶縁性構造体であることを特徴としてもよい。

## 【0022】

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、500K以下であり、構造体は導電性構造体であることを特徴としてもよい。

## 【0023】

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、500K以下であり、構造体は導電性構造体であって、下部画素電極と同一の材料で形成されていることを特徴としてもよい。

## 【0024】

前記上部画素電極用補助配線と上部画素電極の接触抵抗が、500K以下であり、構造体はオーバーハング形状であることを特徴としてもよい。

40

## 【0025】

前記発光層が、有機EL発光素子材料で形成されていることを特徴としてもよい。

## 【発明の効果】

## 【0026】

アクティブ型有機ELディスプレイ装置において、簡単な構成で上部画素電極用補助配線を形成することができ、プロセスの簡略化、およびリーク、ダーカスポット発生を低減させることができとなるものである。

## 【発明を実施するための最良の形態】

## 【0027】

本発明は上部画素電極用補助配線を簡単な構造で実現するものである。基板上に電界効

50

果型薄膜トランジスタに代表されるスイッチング素子を形成し、このスイッチング素子を利用して発光素子を発光させるアクティブ型表示装置において、薄膜トランジスタを形成した基板に有機EL素子を形成することで画像表示を実現できる。

【実施例1】

【0028】

ここで、有機EL素子を挟持する一対の電極のうち、基板側に形成された電極を下部画素電極とし、対をなす電極を上部画素電極とする。薄膜トランジスタを形成した基板に平坦性のよい上部画素電極用補助配線を形成し、下部画素電極、有機層、上部画素電極を一様に形成すると、上部画素電極と上部画素電極用補助配線の間に有機層が存在するため、上部画素電極の配線抵抗を下げる機能を、上部画素電極用補助配線は満たすことはできない。そこで、以下のような構造を考える。

【0029】

薄膜トランジスタが形成された基板上に、平坦性の悪い導電物や導電物の表面を意図的に荒して、平坦な膜表面から凸形状を有する膜面が形成された膜面を形成する。そして、このような膜を上部画素電極用補助配線として利用する。この時、このように形成された凸形状膜面上の有機膜は、極力薄膜化されるので、上部画素電極と上部画素電極用補助配線を接続させる構造が可能となる。つまり、上部画素電極用補助配線は、上部画素電極の配線抵抗をさげる機能を満たすことが出来る。その他の構造としては以下のような構造が考えられる。

【0030】

上部画素電極用補助配線上にオーバーハング形状を有する絶縁性構造体を形成する。また、この構造においては絶縁性構造体の下部線幅が、上部画素電極用補助配線の線幅より狭いことが必要である。このような構成を採用すれば絶縁性構造体脇の有機層の横側に上部画素電極膜が回りこむことで、上部画素電極と上部画素電極用補助配線が接続される。

【0031】

下部画素電極と同一の材料を上部画素電極用補助配線上に形成する。この時、下部画素電極と同一の材料である膜の線幅は、上部画素電極用補助配線の線幅より狭いことが好ましい。このような構造を採用することにより下部画素電極と同一の材料である膜のエッジ部分では有機層が極力薄くなるので、上部画素電極と上部画素電極用補助配線は接続されることとなる。

【0032】

上部画素電極用補助配線上に構造体を形成する。この時、この構造体の線幅は上部画素電極用補助配線の線幅より狭いことが好ましい。そして、この構造体の片側及び下部画素電極上に有機層を形成し、上部画素電極用補助配線上の一方の側には有機層を形成しない。この場合、有機層が形成されていない側の上部画素電極用補助配線にも有機層は形成されないようにする。そして、上部画素電極を全面形成する。このような構造を採用することで、上部画素電極と上部画素電極用補助配線は接続されることとなる。

【0033】

上部画素電極用補助配線上を順テーパー状に形成する。そして、この上に上部画素電極用補助配線の上部線幅より広い構造体を形成する。ただし、構造体の線幅は上部画素電極用補助配線の下部線幅より狭いかほぼ同じであることが好ましい。このような構造を採用することにより上部画素電極が構造体の下に回りこむことで上部画素電極と上部画素電極用補助配線が接続されることとなる。

【0034】

以上のような構造を採用することで、上部画素電極用補助配線が実現されるものである。ここで、上部画素電極用補助配線と上部画素電極全体の接触抵抗は500kΩ以下であることが好ましい。また、下限値としては $1.0 \times 10^{-2}$ Ω程度である。接触抵抗500kΩ以下であれば、接触抵抗分の電圧降下を抑えることが可能となり、不必要にスイッチング素子に電圧をかけることなく有機EL素子の発光を実現出来るものであり、発光輝度バラツキが生じることはない。

10

20

30

40

50

## 【0035】

ここで、上部画素電極用補助配線を形成する場所は、下部画素電極と隣接する下部画素電極の隙間とし、下部画素電極と接触しないように配置する。このような構成を採用することで、下部画素電極と上部画素電極用補助配線は電気的に絶縁される。

## 【0036】

また、上部画素電極用補助配線の線幅を狭くすることで表示領域面積の低下を抑えることが可能である。本実施の形態における上部画素電極用補助配線は成膜、エッティング工程で作成されるので、露光技術が適用可能となり、精度良く補助配線を形成することが可能となる。また、本実施の形態は上部画素電極用補助配線パターンが形成されたシャドーマスクを使用せず簡単な構造で補助配線を形成できる。

10

## 【0037】

つまり、シャドーマスクを使用した場合に発生するゴミに伴う不具合（発光素子が上下電極間でショート、あるいは発光点が発光しないことにより発生する黒点不良）のない画像表示装置が実現可能となる。また、上部画素電極が光に対して透過性を持っていて、上部画素電極側から光を取り出す場合には、有機EL素子が形成された基板の対向基板に、カラーフィルタや色変換層を形成することで、白色発光素子や青色発光素子などの発光素子を使用してカラー表示装置を実現することができる。

## 【0038】

下部画素電極が光に対して透過性を持っていて、下部画素電極側から光を取り出す場合には、薄膜トランジスタと有機EL素子の間にカラーフィルタや色変換層を形成することで、白色発光素子や青色発光素子などの発光素子を使用してカラー表示装置を実現することができる。

20

## 【0039】

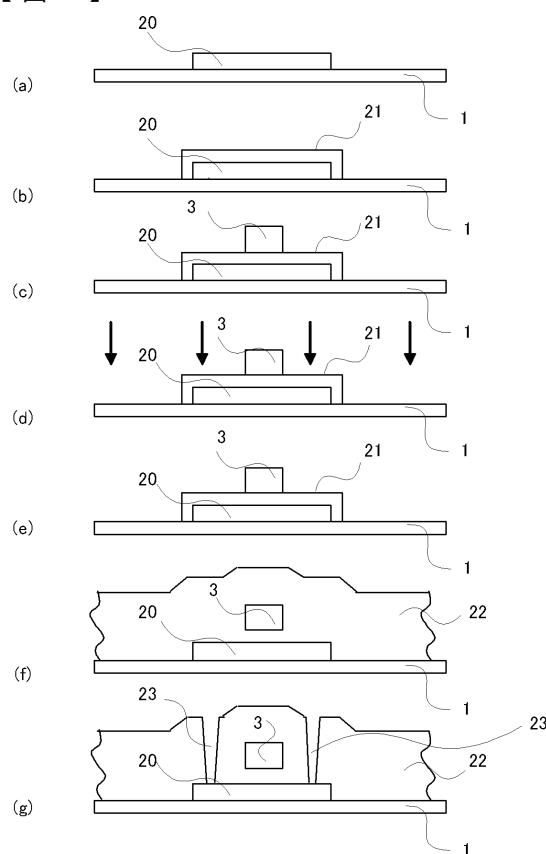

まず、本実施の形態に用いるTFT型有機ELディスプレイ作成の実施の形態を、図1～図5に基づき説明する。図1は、薄膜トランジスタを形成する工程の一例として、N型FETの製造工程を説明するための工程図である。P型FETを製造する場合もほぼ同様な製造工程であり、イオン注入工程に違いがあるのみである。図2は、このFETに対する有機EL素子形成状態を説明するための基板概念図である。P型FETを接続する場合には、下部画素電極を陽極とすればよい。図3は、有機EL素子の青緑色発光特性を説明するための発光スペクトル図、図4は、カラーフィルタ説明図、図5は、有機EL素子とカラーフィルタの組み合わせ状態を説明するための概念図である。図1及び図2にもとづき、薄膜型がN型FETトランジスタの場合についての製造工程について説明する。

30

## 【0040】

図1(a)では、まず石英あるいはガラス基板1の上にSiO<sub>2</sub>層（図示省略）を、たとえばスパッタリング法により約1000nmの厚さで成膜する。そしてこのSiO<sub>2</sub>層の上にアモルファス・シリコン層を約1000nmの厚さで、たとえばCVD法により成膜する。この成膜条件は、たとえば下記の通りである。Si<sub>2</sub>H<sub>6</sub>ガス100SCCMを、圧力条件0.3Torr、温度条件480度としている。それから、このアモルファス・シリコン層を固相成長させてポリシリコン層とする。この固相成長の条件は、たとえば下記の通りである。たとえば、N<sub>2</sub>ガス1SLMを、温度条件600度で、処理時間5hr～20hrとする。それから、このポリシリコン層をパターニングして活性シリコン層20を得る。

40

## 【0041】

図1(b)で、この活性シリコン層20の上に、ゲート酸化膜21となるSiO<sub>2</sub>層を、たとえばプラズマCVD法により、約1000nm成膜する。成膜条件はたとえば下記の通りである。パワーは、50W、TEOS（テトラエトキシシラン）ガス、50SCCM、O<sub>2</sub>ガス、500SCCM、圧力条件は0.1～0.5Torr、温度条件は350度（C）である。このSiO<sub>2</sub>層21の上に、ゲート電極3となるアモルファス・シリコン層を、たとえば上記図1(a)と同様の条件で、CVD法により約4000nm成膜する。そしてこのアモルファス・シリコン層を、たとえば上記図1(a)と同様の条件でアニー

50

ルして、ゲート電極3となるポリシリコン層を形成する。

【0042】

それから、図1(c)で、このポリシリコン層及び上記図1(b)で形成したSiO<sub>2</sub>層を、たとえばドライエッチングによりパターニングし、ゲート電極3及びゲード酸化膜21を作る。

【0043】

図1(d)では、このゲート電極3をマスクとして活性シリコン層20のソース・ドレイン領域となるべき部分にイオンドーピング法により、N型の不純物たとえばPをドーピングする。P型の場合にはP型不純物、たとえば、Bをドーピングする。

【0044】

図1(e)で、これを窒素雰囲気中で約550度で5時間加熱して、ドーパントの活性化を行う。更に水素雰囲気中で約400度で30分加熱処理して水素化を行い、半導体の欠陥準位密度を減少させる。

【0045】

図1(f)で、この基板全体にTEOSを出発材料として層間絶縁層22となるSiO<sub>2</sub>層を、厚さ約4000成形する。この層間絶縁層22となるSiO<sub>2</sub>の成膜条件は、たとえば以下の通りである。

【0046】

パワ-は50～300W、TEOSガス、10～50SCCM、O<sub>2</sub>ガス、500SCCM、圧力条件は0.1～0.5Torr、温度条件は350度である。

【0047】

図1(g)で、この層間絶縁層22となるSiO<sub>2</sub>膜をエッチングコンタクト用のホール23を形成する。

【0048】

以下の説明はN型FETと有機EL素子を接続する場合である。図2(a)に示す如く、A1配線24を蒸着する。

【0049】

次に、図2(b)に示す如く、有機EL素子の配置領域にA1・Mgメタル(Mg90モル%)を蒸着して、下部画素電極(陰極)25を形成する。なお、A1・Mgメタル以外にも4eV程度以下の仕事関数の材料を用いることもできる。そして配線部分をパターニングする。

【0050】

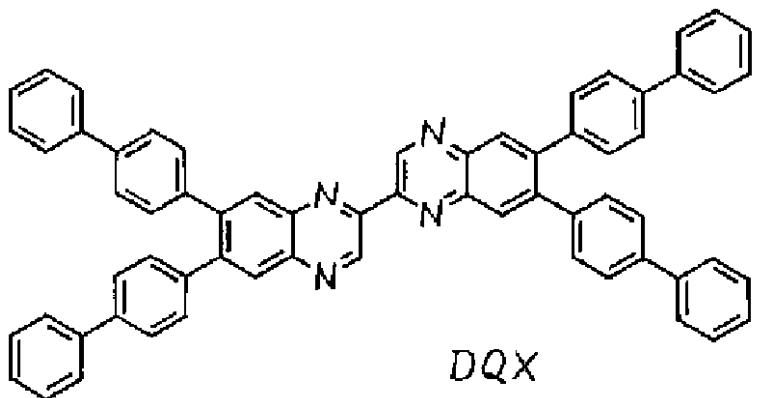

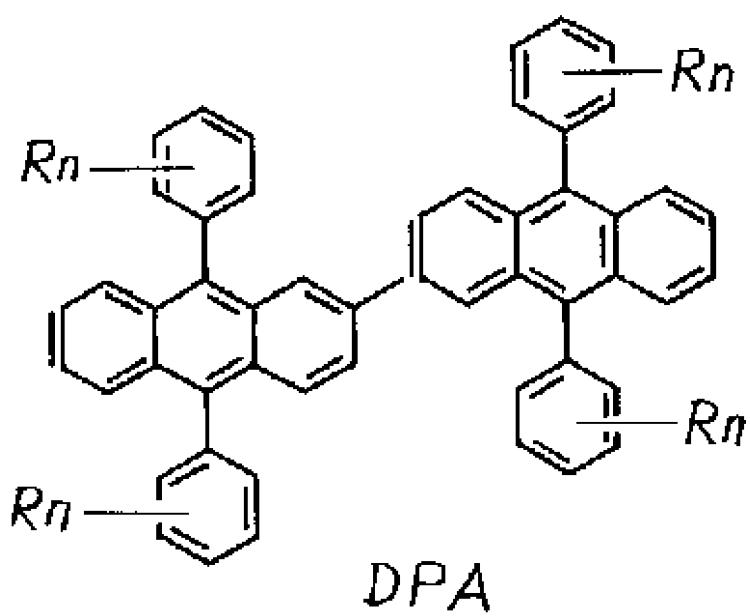

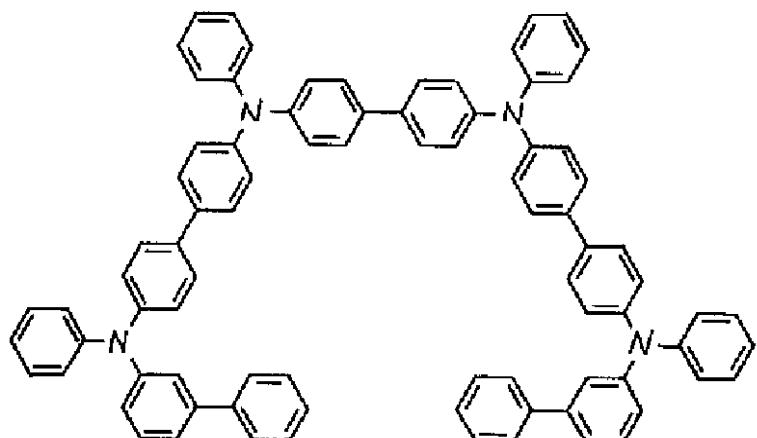

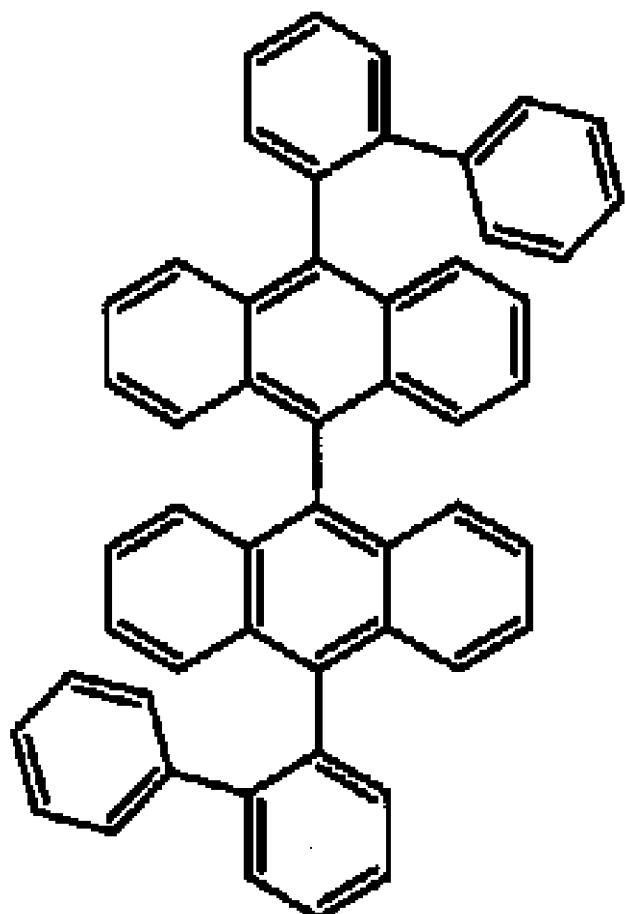

図2(c)では、この有機EL素子の配置領域にポリイミドを被覆し、発光部分だけA1・Mgメタル25を露出させてエッジカバー26とする。図2(d)では、それからマルチチャンバーにてこの発光部分のA1・Mgメタル25をスパッタエッチングして、その表面の酸化膜をエッチングする。それから、たとえば、蒸着により電子輸送層となる第1有機層8-1を構成する下記化学式1に示す化学式のDQX、発光層を構成する下記化学式2に示す化学式のDPA、正孔輸送層を構成する下記化学式3に示す化学式のTPD、正孔注入層8-4を構成する下記化学式4に示す化学式のMTDATAの順に成膜して有機EL層を成膜する。なお化学式2においてR<sub>n</sub>はメチル基またはエチル基である。

【化 1】

## Electron Transport Material

10

【化 2】

### *Emitting Material*

20

30

【化3】

*Hole Transport Material*

10

TPD

【化4】

*Hole Injection Material*

20

30

40

MTDATA

【0051】

そして、この有機EL層の上に陽極として透明導電膜のIZO (In<sub>2</sub>O<sub>3</sub> · ZnO (5モル%) ) 9を成膜し、その上にSiO<sub>2</sub>膜10を成膜してSiO<sub>2</sub>封止を行い、図2(d)に示す如く、N型FETのドレイン側に有機EL素子を接続する。このとき直線特性を示す負荷抵抗は、N型FETのゲートポリシリコンまたは活性シリコンを使用する

50

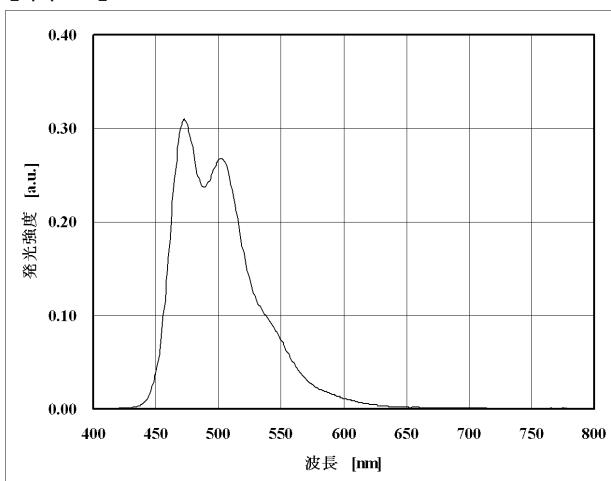

。なお、透明導電膜としては、IZO以外にITO (In<sub>2</sub>O<sub>3</sub>、SnO<sub>2</sub> (10モル%)等を用いることもできる。なお、この有機EL素子は、図3に示す如く、波長-出力強度特性(相対値)を有し、青緑発光する。図3は、有機EL素子の青緑色発光特性説明図である。図3の縦軸には発光強度を、横軸には波長を示している。

#### 【0052】

以下はP型FETと接続する場合である。P型であってもN型と同様な構造を採用することが可能であり、図2(a)~図2(d)と同様な工程が採用されるものである。つまり、下部画素電極が陽極であること以外は、N型と構造上の違いはない。それでは、有機EL発光素子が、白色の発光をする素子構造を採用した場合について説明する。陽極には透明電極と金属の積層構造あるいは、金属の積層構造が好ましい。具体的にはTiNを反射陽極として、TiN上にITOを成膜した積層体を下部画素電極(陽極)とした。

#### 【0053】

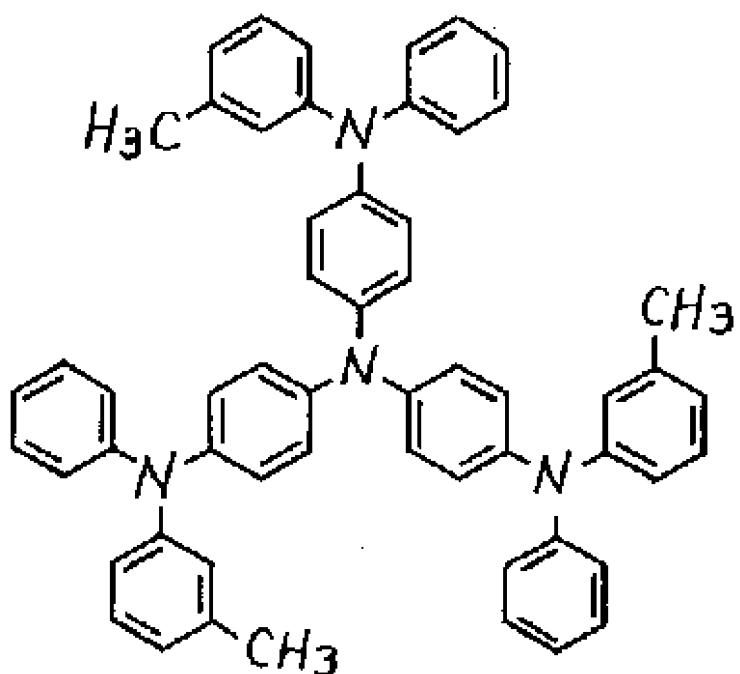

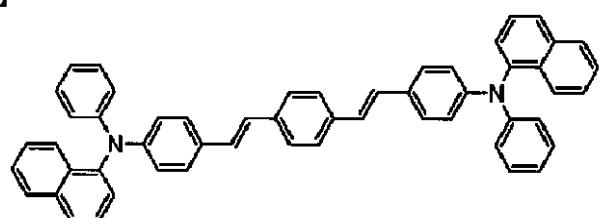

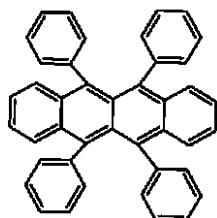

次にホール注入層として、N、N'-ジフェニル-N、N'-ビス(N-(4-メチルフェニル)-N-フェニル(4-アミノフェニル))-1、1'-ビスフェニル-4、4'-ジアミンを形成し、次にホール輸送層として、N、N'-ジフェニル-N、N'-ビス(1-ナフチル)-1、1'-ジフェニル-4、4'-ジアミンを形成した。次に下部発光層として、下記化学式5の化合物X、下記化学式6の化合物Yを100:3の体積比率として形成した。そして、次に、ホール注入層として、N、N'-ジフェニル-N、N'-ビス(N-(4-メチルフェニル)-N-フェニル(4-アミノフェニル))-1、1'-ビスフェニル-4、4'-ジアミンを形成し、次にホール輸送層として、N、N'-ジフェニル-N、N'-ビス(1-ナフチル)-1、1'-ジフェニル-4、4'-ジアミンを形成した。次に下部発光層として、下記化学式5の化合物X、下記化学式6の化合物Yを100:3の体積比率として形成した。

#### 【0054】

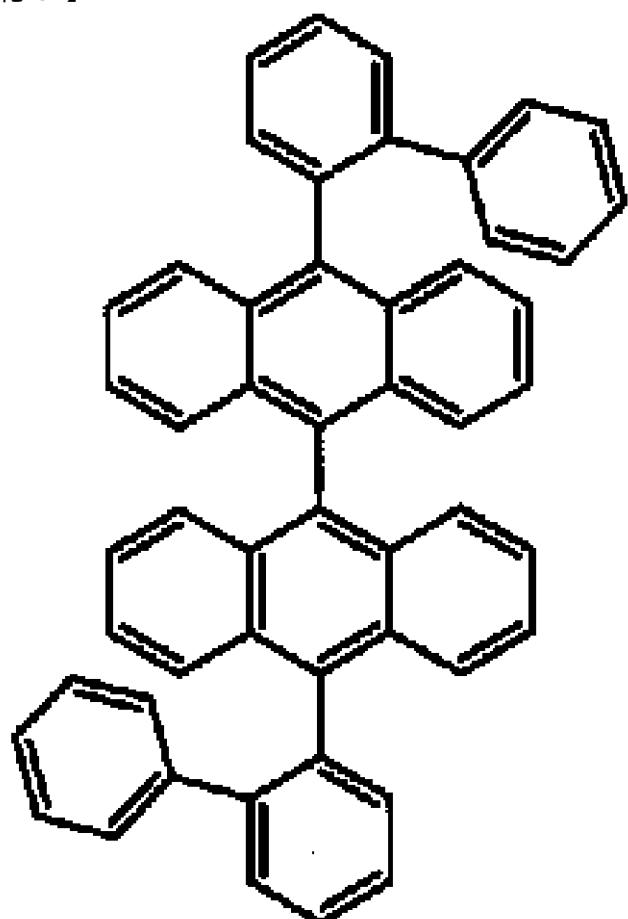

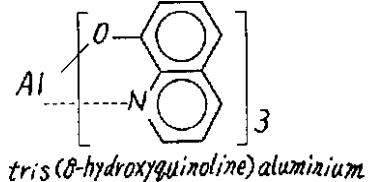

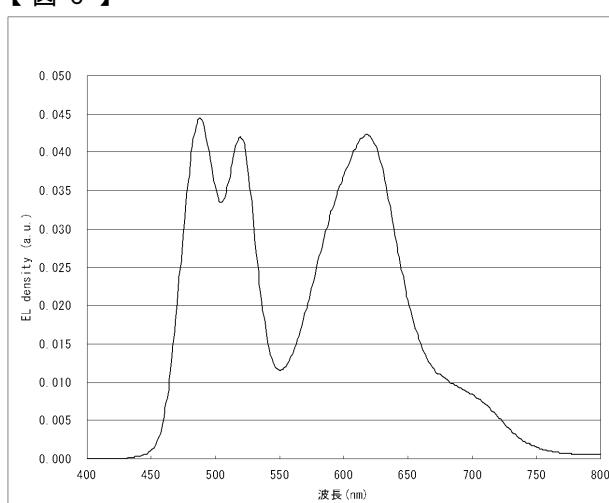

次に上部発光層として下記化学式7の化合物X、下記化学式8の化合物Zを100:3の体積比率として形成した。次に電子輸送層として、tris(8-hydroxyquinoline)aluminumを形成した。次に無機電子注入層として、LiFを形成した。そして、最後に透明上部画素電極(陰極)として、ZnO-Al(ZnO、Al(3モル%))とAuの積層構造体を形成した。そして、P型FETのドレイン側に有機EL素子を接続する。このとき直線特性を示す負荷抵抗は、P型FETのゲートポリシリコンまたは活性シリコンを使用する。なお、透明導電膜としては、ZnO-AlとAuの積層体以外にIZO(In<sub>2</sub>O<sub>3</sub>、ZnO<sub>2</sub>(5モル%))、ITO等を用いることができる。なお、この有機EL素子は、図6に示す如く、波長-出力強度特性(相対値)を有し、白色発光する。

10

20

30

【化5】

10

20

【化6】

30

4,4'-ビス (N-フェニル-N-1-ナフチル) アミノースチルベン)

## 【化7】

10

20

【化8】

ルブレン

30

## 【0055】

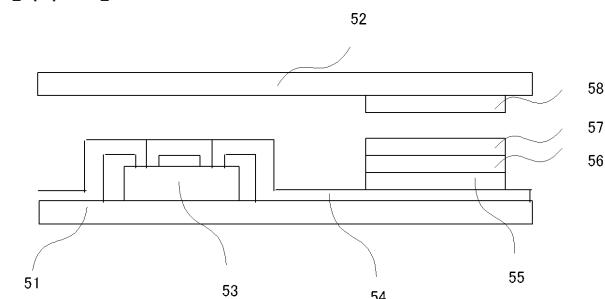

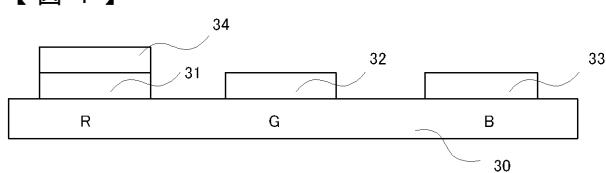

そして、以下に示すように、カラーフィルタ基板と貼り合わせカラー表示が可能となる。この有機EL素子に使用されるカラーフィルタは、図4に示す如く、ガラス板30上に赤色フィルタ31、緑色フィルタ32、青色フィルタ33を配置したものを使用する。なお赤色フィルタ31のみ発光強度を高めるため蛍光フィルタ34が積層されている。そして、この図4に示すカラーフィルタと、図2(d)に示す如きN型FETあるいはP型FETと有機EL素子が形成された基板1とを、図5に示すように貼り合わせる。図5は、有機EL素子とカラーフィルタの組み合わせ状態説明図である。本図で示すように、基板51および52の上にFET53が形成され、FET53は配線54を介して、下部電極55に接続されている。そして、下部電極55の上には有機EL層56、上部電極57が設けられ、上部電極57に対応する基板52側には、カラーフィルタ・蛍光変換フィルタ58が形成されている。

40

## 【0056】

なお、上記説明では、青緑色発光素子、白色発光する有機EL素子にRGBカラーフィルタを設けたものについて説明したが、青色発光する有機EL素子にG、Rの蛍光フィルタをつけてその上にRGBカラーフィルタを設けたもの、青色+赤色発光する有機EL素子にGの蛍光フィルタをつけてその上にRGBカラーフィルタを設けたものを使用してもよい。

50

## 【0057】

また電子注入層としてはn型のアモルファスSiCを使用し、ホール輸送層としてはp型のアモルファスSiCを使用し、発光層として下記化学式9で示すtris(8-hydroxyquinoxoline)aluminiumを使用した場合、発光層にn型のアモルファスSiC及びp型のアモルファスSiCを混合させたものを、使用してもよい。

## 【化9】

## 【0058】

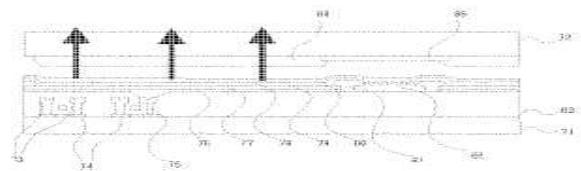

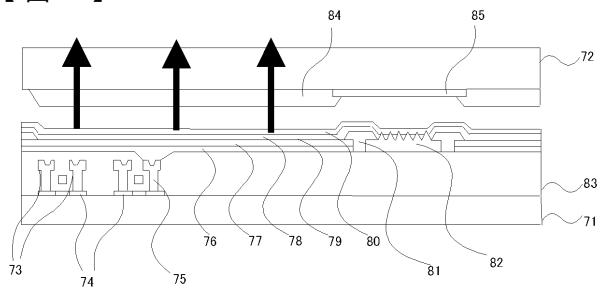

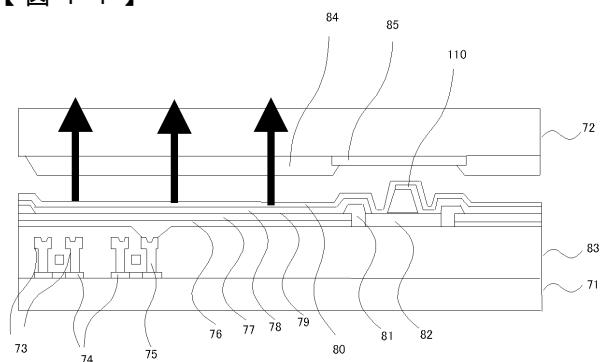

前述した構成を採用することで、基板と反対側から光を取り出す（上部光取りだし）TFT型有機ELディスプレイ構造を実現できる。しかしながら、上部光取りだし TFT型有機ELディスプレイ構造では上部画素電極用補助配線を採用し、配線抵抗を低くしないとパネルの大型化、高精細化は困難である。そこで、本実施形態による補助配線の形成方法について説明する。まず本実施の形態を、図7を用いて説明する。図7は、絶縁基板71上に薄膜プロセスで薄膜トランジスタを形成する。薄膜トランジスタ（TFT）は、有機EL発光素子部分78に最低1個は形成するものとする。そして、最終的にメタル76およびITO77からなる画素電極を、TFTのドレイン電極75と接続させる。ソース電極73はポリシリコンTFT74を介してドレイン電極75と接続している。そして、このドレイン電極75は、メタル76およびITO77からなる下部画素電極と電気的に接続しており、有機EL発光素子部分78およびLif79と上部画素電極80を介して矢印方向に光を照射している。

## 【0059】

画素電極が陽極の場合はP型TFTのドレインを陰極の場合は、N型TFTのドレインを接続すればよい。この時、画素電極を形成した同一面の隣接する画素電極の隙間に上部画素電極用補助配線82を形成することで、簡単な構造で上部画素電極補助配線82を形成するものである。なお、他方の基板72には、カラーフィルター84およびブラックマトリクス85が形成されている。具体的には、上部画素電極用補助配線82の形成方法について述べる。図7に示すようにTFT素子74を形成した基板71の最上面は絶縁膜83が形成されている。絶縁膜83上にTFT素子74とコンタクトホールを介して接続された陽極であるTiNとITOの積層膜をドット毎に形成して画素電極とする。そして、その上に導電膜を成膜する。そして、導電膜を格子状あるいはストライプ上に形成する。この際、格子状あるいはストライプ上に形成された導電膜は、画素電極には接触しないように形成する。

## 【0060】

このような構成をとることで、画素電極と導電膜はショートすることではなく、画素電極の開口率を低下させることはなくなる。この時、意図的に導電膜表面を荒す、あるいは平坦性の悪い導電膜を形成するものである。導電膜表面を荒すにはプラズマに晒す（Ar、酸素など）ことが考えられる。平坦性の悪い導電膜にはAl、Al合金が考えられる。または、Al、Al合金と他金属の積層構造が考えられる。このように表面あれが起きた導電膜上に有機膜を形成し、その上に上部画素電極80を形成すれば上部画素電極80と上部画素電極用補助配線82が接続されるものである。これは表面あれがおきた場所では有機膜が薄くなることにより、電界がその場所に集中することにより、接続されるからである。

## 【0061】

ここで、表面あれについて説明する。ここで、表面あれとは平坦な膜表面から凸形状を有する膜面が形成された膜面の粗さをいう。通常有機EL素子の膜厚は、30nm～500nm程度である。この膜厚に対して、上部画素電極用補助配線82が上部画素電極80

10

20

30

40

50

と接続するには膜厚に対して半分以上の局所的な凸面を有していれば、上部画素電極 8 0 と上部画素電極用補助配線 8 2 は接続されるものとなる。J I S B 0 6 0 1 - 1 9 9 4 に準拠すると、R a (算術平均粗さ) は膜厚に対して 1 / 1 0 以下程度であれば、局所的な接触が起きることはない。また、P - V 値 (膜面の最大高さ 最小高さ) は 3 0 n m 以上が好ましい。また、十点平均粗さ R z は P - V 値の半分の 1 5 n m 以上が好ましい。つまり、R a 値が 3 n m 以上であり、P - V 値が 3 0 n m 以上、あるいは R z 値が 1 5 n m 以上であれば、局所的な凸面で上部画素電極 8 0 と上部画素電極用補助配線 8 2 は接続されることとなる (なお、ここで表面あれの測定範囲は 1  $\mu$  m とし、測定箇所は基板で 1 0 ケ所以上とする。) また、局所的な凸面は、その高さ / 下辺が 0 . 5 以上であれば、局所的な凸面での有機層を他の面部に形成された有機層より、薄く形成することが可能となるものである。

10

#### 【 0 0 6 2 】

この時、上部画素電極用補助配線 8 2 と上部画素電極 8 0 全体の接触抵抗は、5 0 0 / 以下であることが好ましい。上部画素電極 8 0 のシート抵抗値が 8 / 以下であり、4 階調を実現するには上部画素電極用補助配線 8 2 と上部画素電極 8 0 全体が接触する場所は一箇所でもよく、上部画素電極用補助配線 8 2 は補助配線として機能する。また、上部画素電極 8 0 のシート抵抗値が 8 / 以上であるか、4 階調以上を実現するには局所的な凸部が形成される場所は、その凸部間隔が 4 0 m m 以下であればより好ましく、上部画素電極用補助配線 8 2 として機能する。つまり、Q - V G A パネルで上部画素電極 8 0 のシート抵抗値が 8 / 以上であり、8 階調を実現する場合、凸部間隔が 4 0 m m 以下であれば十分な階調表現が可能となる。上部画素電極 8 0 のシート抵抗値が 8 / 程度であり、1 6 階調を実現する場合では凸部が形成される場所は、その凸部間隔が 2 0 m m 程度であることが好ましい。

20

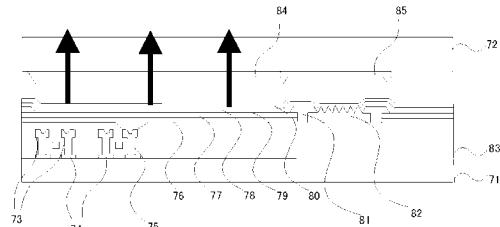

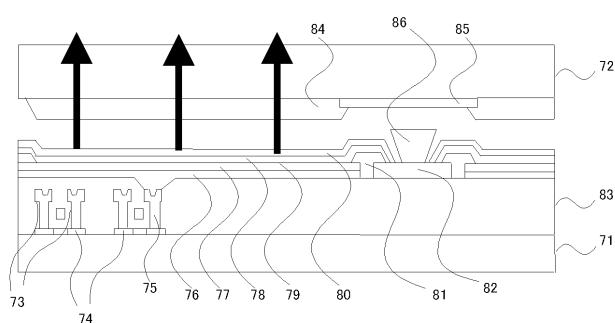

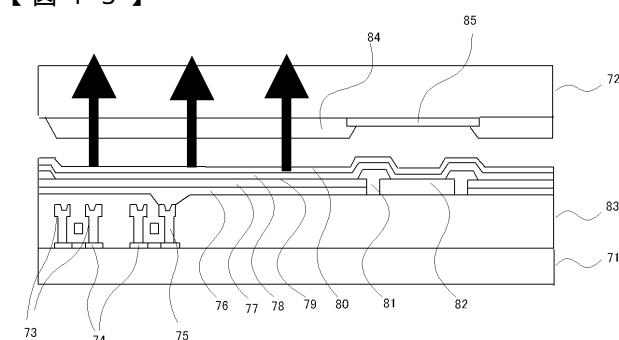

#### 【 0 0 6 3 】

また、図 8 に示すように、T F T 上の絶縁膜上において、画素電極と画素電極の間に、上部画素電極用補助配線 8 2 が形成されていて、さらにその上部にオーバーハンプ形状を持つ絶縁性構造体 8 6 が形成され、絶縁性構造体 8 6 の下部幅が補助配線 8 2 の幅より狭いことを特徴とする構造を採用することで、有機膜 7 8 の横に上部画素電極補助配線 8 2 を形成する金属が回りこみ、直接上部画素電極 8 0 と接触する構造でも、上部画素電極用補助配線 8 2 と上部画素電極 8 0 は、接続されることとなる。

30

#### 【 0 0 6 4 】

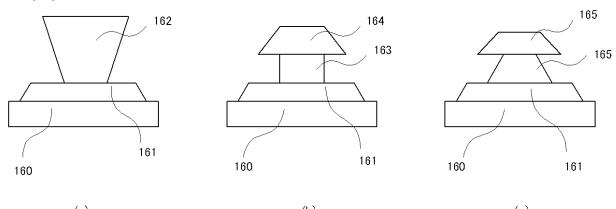

ここで、図 1 6 に本実施の形態に使用される構造体 8 6 の概念図を示す。オーバーハンプ形状を持つ構造体 8 6 は、基板 1 6 0 の上に形成された上部電極用補助配線 1 6 1 の上に、逆テープレジスト 1 6 2 で形成したり (図 1 6 ( a )) 、ポリイミド 1 6 3 とレジスト 1 6 4 の積層構造にしたり (図 1 6 ( b )) 、導電物 1 6 5 とレジスト 1 6 6 の積層構造にしたり (図 1 6 ( c )) することで、実現可能となるものである。

40

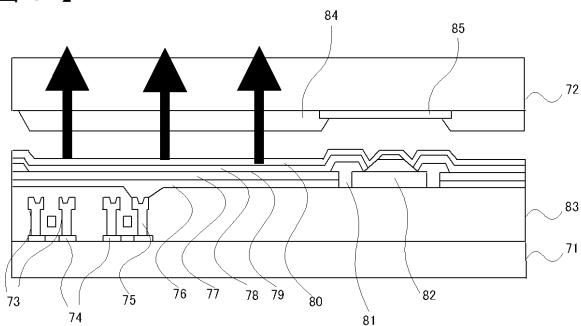

#### 【 0 0 6 5 】

その他の上部画素電極用補助配線 8 2 を形成する構造としては、図 9 に示すような構造が考えられる。図 9 は、本実施の形態に使用される上部光取りだし有機 E L 表示装置の補助配線形成時の概念図である。下部画素電極 7 7 と同一の材料を上部画素電極用補助配線 8 2 上に形成する。下部画素電極 7 7 と同一の材料である膜の線幅は、上部画素電極用補助配線 8 2 の線幅より狭いことが好ましい。このような構造を採用することにより、下部画素電極と同一の材料である膜のエッジ部分では有機層が極力薄くなるので、上部画素電極 8 0 と上部画素電極用補助配線 8 2 は接続されることとなる。

40

#### 【 0 0 6 6 】

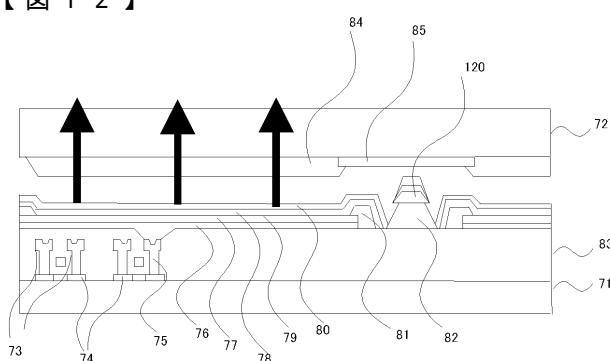

図 1 1 に示すように、上部画素電極用補助配線 8 2 上に構造体 1 1 0 を形成する際に、この構造体 1 1 0 の線幅は、上部画素電極用補助配線 8 2 の線幅より狭いことが好ましい。そして、この構造体 1 1 0 の片側及び下部画素電極上に有機層 1 0 2 を形成し、上部画素電極用補助配線 8 2 上の一方の側には有機層 1 0 2 を形成しない。この場合、有機層 1 0 2 が形成されていない側の上部画素電極用補助配線 8 2 にも有機層 1 0 2 は形成されな

50

いようにする。そして、上部画素電極 80 を全面形成する。このような構造を採用することで、上部画素電極 80 と上部画素電極用補助配線 82 は接続されることとなる。

#### 【0067】

また、図 12 に示すように、上部画素電極用補助配線 82 上を順テーパー状に形成する。そして、この上に上部画素電極用補助配線 82 の上部線幅より広い、構造体 120 を形成する。ただし、構造体 120 の線幅は、上部画素電極用補助配線 82 の下部線幅より狭いか、ほぼ同じであることが好ましい。このような構造を採用することにより上部画素電極 80 が構造体の下に回りこむことで上部画素電極 80 と上部画素電極用補助配線 82 が接続されることとなる。これら構造体 110 または 120 を使用した場合には上部画素電極用補助配線 82 の表面あれがなくてもよく、上部画素電極用補助配線 82 に使用される導電物は A1、A1 系合金に限らず、導電性酸化物や Mo、W、Cr に代表される高融点金属でも使用可能である。また、対向する基板には図 7～12 に示されたようにカラーフィルタ 84 または色変換層を使用することで、上部光取りだし有機 EL 表示装置は、多色発光が実現できるものである。また、図 7～12 に示されたように補助配線 82 と重なる位置に遮光層 85 を形成することも可能である。これにより、コントラストが向上した画像表示装置が実現できるものである。

#### 【0068】

ここで、図 7 に示される定電圧 TFT 駆動方式トップエミッショントンネル型パネルの作成方法の工程について述べる。(1) まず石英あるいはガラス基板 71 上にアモルファス・シリコン層を約 1000 の厚さで CVD 法により成膜した。この成膜条件は、たとえば下記の通りである。Si<sub>2</sub>H<sub>6</sub> ガス 100 SCCM で、圧力条件 0.3 Torr、温度条件 480 度などである。それからこのアモルファス・シリコン層を固相成長させてポリシリコン層とする。この固相成長の条件は下記の通りである。N<sub>2</sub> ガス 1 SLM で、温度条件 600 度、処理時間 5 hr～20 hr などである。それからこのポリシリコン層をパターニングして活性シリコン層 74 を得る。

#### 【0069】

(2) この活性シリコン層 74 上にゲート酸化膜となる SiO<sub>2</sub> 層を、プラズマ CVD 法により、約 1000 成膜する。成膜条件は下記の通りである。パワー 50 W、TEOS (テトラエトキシシラン) ガス、50 SCCM、O<sub>2</sub> ガス、500 SCCM で、圧力条件 0.1～0.5 Torr、温度条件 350 度などである。

#### 【0070】

(3) この SiO<sub>2</sub> 層の上に、ゲート電極となる N 型アモルファス・シリコン層を成膜した。この成膜条件は、下記の通りである。たとえば、(Si<sub>2</sub>H<sub>6</sub>+0.5%PH<sub>3</sub>) ガス、100 SCCM、圧力条件 0.3 Torr、温度条件 480 度などで、CVD 法により約 4000 成膜する。そしてこのアモルファス・シリコン層を上記(1)と同様の条件でアニールしてゲート電極となる N 型ポリシリコン層を形成する。それからこのポリシリコン層及び上記(2)で形成した SiO<sub>2</sub> 層を、ドライエッティングによりパターニングし、ゲート電極及びゲード酸化膜を作る。

#### 【0071】

(4) それからこのゲート電極をマスクとしてシリコン活性層のソース・ドレイン領域となるべき部分に、イオンドーピング法により、P 型の不純物 B を  $1 \times 10^{15}$  (イオン/cm<sup>2</sup>) ドーピングする。

#### 【0072】

(5) 次に、これを窒素雰囲気中で約 550 度で 5 時間加熱して、ドーパントの活性化を行う。更に水素雰囲気中で約 400 度で 30 分加熱処理して水素化を行い、半導体の欠陥準位密度を減少させる。

#### 【0073】

(6) そして、この基板全体に、TEOS を出発材料として第 1 層間絶縁層となる SiO<sub>2</sub> 層を、厚さ約 4000 成形する。この層間絶縁層となる SiO<sub>2</sub> の成膜条件は、以下の通りである。

10

20

30

40

50

## 【0074】

パワ-50~300W、TEOSガス、10~50SCCM、O<sub>2</sub>ガス、500SCCM、圧力条件0.1~0.5Torr、温度条件350度などである。

## 【0075】

(7) この層間絶縁層となるSiO<sub>2</sub>膜をエッティングコンタクト用のホールを形成する。

## 【0076】

(8) それから、活性層シリコンのドレイン、ソースの配線用のTiN73をスパッタ法にて1500成膜した後、所定の形状にパターニングしてソース電極73、ドレイン電極75を形成した。

10

## 【0077】

(9) それから、第2層間絶縁膜となるSiO<sub>2</sub>層を、厚さ約4000成形する。この層間絶縁層83となるSiO<sub>2</sub>の成膜条件は、(6)と同様とした。それから、この層間絶縁層83となるSiO<sub>2</sub>膜をエッティングしコンタクト用のホールを形成する。

## 【0078】

(10) 次に電源配線用のAl-0.18wt%Scをスパッタ法にて10000成膜した後、所定の形状にパターニングして電源配線を形成した(図示せず。)。

## 【0079】

(11) それから、第3層間絶縁膜となるSiO<sub>2</sub>層を、厚さ約4000成形する。この層間絶縁層となるSiO<sub>2</sub>の成膜条件は、(6)と同様とした。それから、この層間絶縁層となるSiO<sub>2</sub>膜をエッティングしコンタクト用のホールを形成する。

20

## 【0080】

(12) 最後に下部画素電極76とドレイン電極75が接続出きるように第1~第3層間絶縁膜にコントクト用ホールをエッティングにてSiO<sub>2</sub>層を除去することで形成した。

## 【0081】

以上の工程(1)~(12)はTFT基板作成までである。なお図中第1~第3層間絶縁膜はまとめて絶縁膜と記載する。

## 【0082】

また、R(赤)G(緑)B(青)のカラーフィルタ84が規則的に配列され、かつそれぞれの隙間には黒色樹脂層85(ブラックマトリックス)が形成されたTFT基板71の対向基板72を用意した。以上のようにして形成されたTFT基板71、及び対向基板72を使用して、サイズが対角4.0インチ(縦横比4:3)、解像度がVGA、表示色数が26万色である有機ELフルカラーパネルを、TFT基板71と対向基板72と接着剤を使用して貼り合せることで作成した。そして、下記のように各々の条件を変えてパネルを作成し、パネルの各部分での面平均輝度を比較した。TFT基板71上に形成される上部画素電極用補助配線82の構造は、以下のようにした。上部画素電極用補助配線82は、下部画素電極間の隙間に形成し、下部画素電極と上部画素電極用補助配線82が電気的に絶縁される構造とした。

30

## 【0083】

また、その間にはレジストを格子状に形成し、下部画素電極および上部画素電極用のエッジカバー81とした。上部画素電極用補助配線82の材料はAlとTiNの積層構造とし、膜厚はそれぞれ1.0μm、0.1μmとした。ここで、透明陰極と上部画素電極用補助配線82の接触抵抗を測定したところ、接触抵抗は200kであった(表1)。

40

## 【0084】

また、Al配線を形成した後、アッシング処理を施し表面を荒した後、カバー電極層としてTiN層を設けた。ここで、透明陰極と上部画素電極用補助配線82の接触抵抗を測定したところ、接触抵抗は30kであった(表1)。

## 【0085】

下部画素電極は、TiNを膜厚50nm形成した上にITOを膜厚100nm形成した2層構造とした。また、下部画素電極は、TFT上の絶縁層を開口しTFTのドレイン電

50

極 75 と接続する構造とした。白色発光層は下部発光層として、前述した化合物 X、化合物 Y を 100 : 3 の体積比率として 10 nm 形成した。

【 0 0 8 6 】

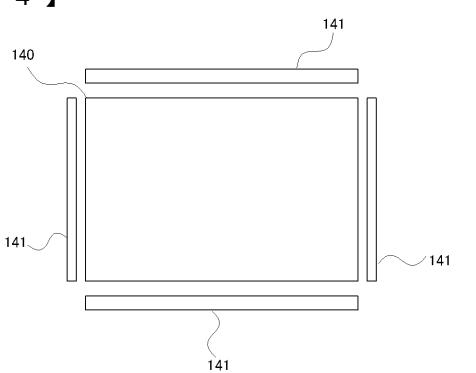

次に上部発光層として前述した化合物X、化合物Zを100:3の体積比率として30nm形成した。陰極層は蒸着法でLiF79を膜厚5nm成膜した後に、スパッタ法でZnO·Alを膜厚120nm成膜した。さらに蒸着法でAuを膜厚10nm成膜した後、スパッタ法でZnO·Alを膜厚80nm成膜して、可視光における平均透過率が70%で、シート抵抗が8Ω/□になるようにした。陰極コンタクトパッドはパネルの周囲（上下左右部分）に配置した（図14）。

【 0 0 8 7 】

R<sub>a</sub>、P-V、R<sub>z</sub>値がそれぞれ、3 nm以上、30 nm以上、15 nm以上の上部画素電極用補助配線82を使用した場合には、測定箇所における面内輝度バラツキは±3%以内であった（測定ポイントは図15参照）（表2）。

## 【实施例 2】

【 0 0 8 8 】

図 8 のように、定電圧 TFT 駆動方式トップエミッション型パネルにおいて、サイズが対角 4.0 インチ（縦横比 4:3）、解像度が VGA、表示色数が 26 万色である有機EL フルカラーパネルにおいて、下記のようパネルを作成した。なお、TFT 基板 71 の作成と対向基板 72 は、実施例 1 と同様とした。

【 0 0 8 9 】

TFT基板71上に形成される下部画素電極は、TiNを膜厚50nm形成した上にITOを膜厚100nm形成した2層構造とした。また、下部画素電極は、TFT上の絶縁層を開口しTFTのドレイン電極75と接続する構造とした。白色発光層は下部発光層として、前述した化合物X、化合物Yを100:3の体積比率として10nm形成した。次に上部発光層として前述した化合物X、化合物Zを100:3の体積比率として30nm形成した。陰極層は蒸着法でLiFを膜厚5nm成膜した後に、スパッタ法でZnO·A1を膜厚120nm成膜した。

【 0 0 9 0 】

さらに、蒸着法で  $Au$  を膜厚 10 nm 成膜した後、スパッタ法で  $ZnO \cdot Al$  を膜厚 80 nm 成膜して、可視光における平均透過率が 70 % で、シート抵抗が 8 / となるようにした。また、図 14 に示すように、陰極コンタクトパッド 141 は、パネル 140 の周囲（上下左右部分）に配置した。

【 0 0 9 1 】

面平均輝度結果を表3に示す。ここで、上部画素電極用補助配線82は、以下のような構造とした。上部画素電極用補助配線82は下部画素電極間の隙間に形成し、下部画素電極と上部画素電極用補助配線82が、電気的に絶縁される構造とした。また、その間にはレジストを格子状に形成し、下部画素電極および上部画素電極用のエッジカバー81とした。

〔 0 0 9 2 〕

上部画素電極用補助配線 8 2 に使用される材料は Mo として、膜厚は 0.6  $\mu\text{m}$  とした。その上部に逆テープレジストを 1.5  $\mu\text{m}$  塗布し、逆テープレジストの下部線幅が、上部画素電極用補助配線 8 2 の線幅より、狭くなるように上部画素電極用補助配線 8 2 上に逆テープレジストを形成した。この場合、Ra、P-V、Rz 値がそれぞれ、3 nm 以下、30 nm、15 nm 以下であっても面内輝度バラツキは 3% 以内であった。構造体がない場合は面内輝度バラツキは  $\pm 10\%$  以上であった（測定ポイントは図 15 参照）ここで、透明陰極と上部画素電極用補助配線 8 2 の接触抵抗を測定したところ、接触抵抗は 50 k であった。構造体がない場合の接触抵抗は 50 M であった（表 4）。

### 【实施例 3】

【 0 0 9 3 】

対角4.0インチ(縦横比4:3)、解像度がVGA、表示色数が26万色である有機ELフルカラーパネルにおいて、下記のようパネルを作成した。なお、TFT基板71の作成と対向基板72は、実施例1と同様とした。TFT基板71上に形成される下部画素電極はTiNを膜厚50nm形成した上に、ITOを膜厚100nm形成した2層構造とした。

#### 【0094】

また、下部画素電極は、TFT上の絶縁層を開口しTFTのドレイン電極75と接続する構造とした。白色発光層は下部発光層として、前述した化合物X、化合物Yを100:3の体積比率として10nm形成した。次に上部発光層として前述した化合物X、化合物Zを100:3の体積比率として30nm形成した。陰極層は蒸着法でLiFを膜厚5nm成膜した後に、スパッタ法でZnO·Alを膜厚120nm成膜した。さらに蒸着法でAuを膜厚10nm成膜した後、スパッタ法でZnO·Alを膜厚80nm成膜して、可視光における平均透過率が70%で、シート抵抗が8/ menjadiようにした。陰極コンタクトパッド141はパネル140の周囲(上下左右部分)に配置した(図14)。面平均輝度結果を表5に示す。

#### 【0095】

ここで、上部画素電極用補助配線82は以下のよう構造とした。上部画素電極用補助配線82は下部画素電極間の隙間に形成し、下部画素電極と上部画素電極用補助配線82が電気的に絶縁される構造とした。また、その間にはレジストを格子状に形成し、下部画素電極および上部画素電極用のエッジカバー81とした。上部画素電極用補助配線82に使用される材料はMoとして、膜厚は0.6μmとした。その上部に下部画素電極の一部であるITOを膜厚100nm成膜し、上部画素電極用補助配線82と同じ形状にパーテーニング形成した。

#### 【0096】

ここで、ITOのエッジは切り立っており、エッジの基板に対する角度は約45度であった。この場合、Ra、P-V、Rz値がそれぞれ、3nm以下、30nm以下、15nm以下であっても面内輝度バラツキは3%以内であった(測定ポイントは図15参照)ここで、透明陰極と上部画素電極用補助配線82の接触抵抗を測定したところ、接触抵抗は80k、50kであった(表6)。つまり、ITOのエッジ部分で上部画素電極80と上部画素電極用補助配線82が接続されていることが解った。

#### 【実施例4】

#### 【0097】

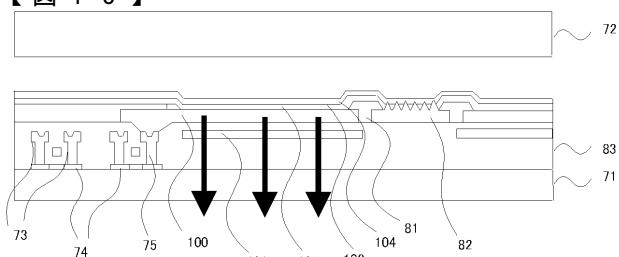

図10は、本実施の形態に使用される下部光取りだし有機EL表示装置の補助配線形成時の概念図である。図7と異なる点としては、下部電極であるITO100は、カラーフィルタ101の上に絶縁膜83を介して形成されており、有機発光層102とLiF103は、上部電極である陰極Al104と、下部電極であるITO100の間に形成されている。そして、矢印方向に光を発光させて、表示を行っている。

#### 【0098】

図10のように、定電圧TFT駆動方式ボトムエミッショントン型パネルにおいて、サイズが対角4.0インチ(縦横比4:3)、解像度がVGA、表示色数が26万色である有機ELフルカラーパネルとして、下記のようパネルを作成した。なお、TFT基板71の構成は、上述の構成以外は実施例1と同様とし、さらにTFT基板71上にカラーフィルタ101を形成した。TFT基板71上に形成される下部画素電極は、ITOを膜厚100nm形成した1層構造とした。また、下部画素電極はTFT上の絶縁層を開口しTFTのドレイン電極75と接続する構造とした。白色発光層は下部発光層として、前述した化合物X、化合物Yを100:3の体積比率として10nm形成した。

#### 【0099】

次に上部発光層として前述した化合物X、化合物Zを100:3の体積比率として30nm形成した。陰極層は蒸着法でLiFを膜厚5nm成膜した後に、蒸着法にてAlを膜厚300nmとして形成した。陰極コンタクトパッドはパネルの周囲(上下左右部分)に

10

20

30

40

50

配置した(図14)。面平均輝度結果を表7に示す。ここで、上部画素電極用補助配線82は以下のような構造とした。上部画素電極用補助配線82は下部画素電極間の隙間に形成し、下部画素電極100と上部画素電極用補助配線82が、電気的に絶縁される構造とした。また、その間にはレジストを格子状に形成し、下部画素電極100および上部画素電極用のエッジカバー81とした。表7の試料1では、上部画素電極用補助配線82の材料はA1とTiNの積層構造とし、膜厚はそれぞれ1.0μm、0.1μmとした。また、表7の試料2および3では、上部画素電極用補助配線82の材料をA1として、1.0μm、0.5μmとして、酸素プラズマでアッシング処理し表面を荒した。この場合、Ra、P-V、Rz値がそれぞれ、3nm以上、30nm以上、15nm以上であって、面内輝度バラツキは3%以内であった(測定ポイントは図15参照)ここで、透明陰極と上部画素電極用補助配線82の接触抵抗を測定したところ、接触抵抗はそれぞれ300k、50k、100kであった(表8)。

10

### 【实施例 5】

[ 0 1 0 0 ]

図11は、本実施の形態に使用される上部光取りだし有機EL表示装置の補助配線形成時の概念図である。図11のように、定電圧 TFT 駆動方式トップエミッション型パネルにおいて、サイズが対角4.0インチ（縦横比4:3）、解像度がVGA、表示色数が26万色である有機ELフルカラーパネルにおいて、下記のようパネルを作成した。なお、TFT基板71の作成と対向基板72は、実施例1と同様とした。TFT基板71上に形成される下部画素電極は、TiNを膜厚50nm形成した上にITOを膜厚100nm形成した2層構造とした。また、下部画素電極はTFT上の絶縁層を開口しTFTのドレイン電極75と接続する構造とした。白色発光層は下部発光層として、前述した化合物X、化合物Yを100:3の体積比率として10nm形成した。

20

[ 0 1 0 1 ]

次に上部発光層として前述した化合物X、化合物Zを100:3の体積比率として30nm形成した。陰極層は蒸着法でLiFを膜厚5nm成膜した後に、スパッタ法でZnO・Alを膜厚120nm成膜した。さらに蒸着法でAuを膜厚10nm成膜した後、スパッタ法でZnO・Alを膜厚80nm成膜して、可視光における平均透過率が70%で、シート抵抗が8 / にるようにした。陰極コンタクトパッドはパネルの周囲（上下左右部分）に配置した（図9）。面平均輝度結果を表9に示す。

30

[ 0 1 0 2 ]

ここで、上部画素電極用補助配線82は以下のような構造とした。上部画素電極用補助配線82は下部画素電極間の隙間に形成し、下部画素電極と上部画素電極用補助配線82が電気的に絶縁される構造とした。また、その間にはレジストを格子状に形成し、下部画素電極および上部画素電極用のエッジカバー81とした。上部画素電極用補助配線82に使用される材料はMoとして、膜厚は0.6μmとした。その上部にレジストを1.5μm塗布し、レジストの下部線幅が上部画素電極用補助配線82の線幅より、狭くなるように上部画素電極用補助配線82上にレジストを形成した。

[ 0 1 0 3 ]

そして、上記有機発光層は基板を回転せずに斜め蒸着成膜し、レジストの片側には有機発光層が形成されないようにした。次に上部画素電極を基板を回転して、蒸着、スパッタ成膜し、レジストの両側に成膜形成されたようにした。この場合、 $R_a$ 、 $P-V$ 、 $R_z$  値がそれぞれ、3 nm 以下、30 nm 以下、15 nm 以下であっても面内輝度バラツキは3% 以内であった。構造体がない場合は面内輝度バラツキは  $\pm 10\%$  以上であった（測定ポイントは図15 参照）ここで、透明陰極と上部画素電極用補助配線82の接触抵抗を測定したところ、接触抵抗は 10 k $\Omega$  であった。構造体がない場合の接触抵抗は 50 M $\Omega$  であった（表10）。

40

### 【寒施例 6】

[ 0 1 0 4 ]

図12のように、定電圧TFT駆動方式トップエミッショントransistor型パネルにおいて、サイズ

50

が対角4.0インチ(縦横比4:3)、解像度がVGA、表示色数が26万色である有機ELフルカラーパネルにおいて、下記のようパネルを作成した。なお、TFT基板71の作成と対向基板72は、実施例1と同様とした。TFT基板71上に形成される下部画素電極はTiNを膜厚50nm形成した上にITOを膜厚100nm形成した2層構造とした。また、下部画素電極は、TFT上の絶縁層を開口してTFTのドレイン電極75と接続する構造とした。

【 0 1 0 5 】

白色発光層は下部発光層として、前述した化合物X、化合物Yを100:3の体積比率として10nm形成した。次に上部発光層として前述した化合物X、化合物Zを100:3の体積比率として30nm形成した。陰極層は蒸着法でLiFを膜厚5nm成膜した後に、スパッタ法でZnO・Alを膜厚120nm成膜した。さらに蒸着法でAuを膜厚10nm成膜した後、スパッタ法でZnO・Alを膜厚80nm成膜して、可視光における平均透過率が70%で、シート抵抗が8/Ωになるようにした。陰極コンタクトパッドはパネルの周囲（上下左右部分）に配置した（図14）。面平均輝度結果を表11に示す。

【 0 1 0 6 】

ここで、上部画素電極用補助配線 8 2 は、以下のような構造とした。上部画素電極用補助配線 8 2 は下部画素電極間の隙間に形成し、下部画素電極と上部画素電極用補助配線 8 2 が電気的に絶縁される構造とした。また、その間にはレジストを格子状に形成し、下部画素電極および上部画素電極用のエッジカバー 8 1 とした。上部画素電極用補助配線 8 2 に使用される材料は Mo として、膜厚は  $0.4 \mu\text{m}$  とした。その上部に上部画素電極用補助配線 8 2 形成時のレジストを残存させた。ここで、上部画素電極用補助配線 8 2 の下部線幅とほぼ同じ線幅でレジストの下部線幅を形成するようにした。この場合、Ra、P-V、Rz 値がそれぞれ、3 nm 以下、30 nm 以下、15 nm 以下であっても面内輝度バラツキは 3 % 以内であった。構造体がない場合は面内輝度バラツキは  $\pm 10\%$  以上であった（測定ポイントは図 15 参照）。ここで、透明陰極と上部画素電極用補助配線 8 2 の接触抵抗を測定したところ、接触抵抗は 15 k であった。構造体がない場合の接触抵抗は 70 M であった（表 1 2）。

## 【比較例】

【 0 1 0 7 】

〔 0 1 0 8 〕

ここで、透明陰極と上部画素電極用補助配線 8 2 の接触抵抗を測定したところ、接触抵抗は 3 0 M $\Omega$  であった(表 1 3)。また、上部画素電極用補助配線 8 2 の材料を TiN とし、膜厚は 0.1  $\mu\text{m}$  として同様に接触抵抗を測定した。ここで、透明陰極と上部画素電極用補助配線 8 2 の接触抵抗を測定したところ、接触抵抗は 2 0 M $\Omega$  であった(表 1 3)。下部画素電極は TiN を膜厚 50 nm 形成した上に ITO を膜厚 100 nm 形成した 2 層構造とした。また、下部画素電極は TFT 上の絶縁層を開口し TFT のドレイン電極 7 5 と接続する構造とした。

[ 0 1 0 9 ]

白色発光層は、下部発光層として、前述した化合物X、化合物Xを100:3の体積比率として10nm形成した。次に上部発光層として前述した化合物X、化合物Xを100:3の体積比率として30nm形成した。陰極層は蒸着法でLiFを膜厚5nm成膜した後に、スパッタ法でZnO·Alを膜厚120nm成膜した。さらに蒸着法でAuを膜厚

10 nm 成膜した後、スパッタ法で ZnO・Al を膜厚 80 nm 成膜して、可視光における平均透過率が 70 % で、シート抵抗が 8 / になるようにした。

【0110】

陰極コンタクトパッド 141 は、パネル 140 の縦横サイズと同じ長さでパネルの周囲に配置した（図 14）。面平均輝度結果を表 14 に示す。表 14 から明らかなように、Ra、P・V、Rz 値がそれぞれ、3 nm 以下、30 nm 以下、15 nm 以下の上部画素電極用補助配線 82 を使用した場合には、測定箇所における面内輝度バラツキは ±10 % 以上であった（測定ポイントは図 15 参照）。

【表 1】

| 抵抗値 (Ω) |       |

|---------|-------|

| 1       | 200 k |

| 2       | 30 k  |

10

実施例 1 の接触抵抗

【表 2】

|   | Ra     | P・V   | Rz      | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---|--------|-------|---------|------|------|------|------|------|------|------|------|------|

| 1 | 3.1 nm | 31 nm | 16.4 nm | 1540 | 1536 | 1582 | 1560 | 1523 | 1519 | 1502 | 1521 | 1535 |

| 2 | 6.4 nm | 61 nm | 30.5 nm | 1584 | 1574 | 1588 | 1588 | 1572 | 1592 | 1590 | 1578 | 1595 |

20

実施例 1 の面平均輝度 (cd/m<sup>2</sup>)

【表 3】

|   | 構造体の有無 | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---|--------|------|------|------|------|------|------|------|------|------|

| 1 | あり     | 1690 | 1672 | 1653 | 1642 | 1625 | 1654 | 1687 | 1699 | 1718 |

| 2 | なし     | 1680 | 1402 | 1510 | 1417 | 1350 | 1447 | 1514 | 1528 | 1703 |

30

実施例 2 の面平均輝度 (cd/m<sup>2</sup>)

【表 4】

| 抵抗値 (Ω) |      |

|---------|------|

| 1       | 50 K |

| 2       | 50 M |

40

実施例 2 の接触抵抗

【表 5】

|   | Ra     | P・V     | Rz     | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---|--------|---------|--------|------|------|------|------|------|------|------|------|------|

| 1 | 1.3 nm | 12.6 nm | 6.3 nm | 1569 | 1642 | 1591 | 1573 | 1518 | 1506 | 1487 | 1501 | 1525 |

| 2 | 0.8 nm | 5.2 nm  | 2.8 nm | 1582 | 1570 | 1593 | 1571 | 1532 | 1574 | 1577 | 1590 | 1585 |

実施例 3 の面平均輝度 (cd/m<sup>2</sup>)

【表6】

| 抵抗値 (Ω) |      |

|---------|------|

| 1       | 80 k |

| 2       | 50 k |

実施例3の接触例

10

【表7】

|   | Ra    | P・V    | Rz     | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---|-------|--------|--------|------|------|------|------|------|------|------|------|------|

| 1 | 4.5nm | 36.2nm | 17.5nm | 1240 | 1236 | 1282 | 1267 | 1223 | 1219 | 1202 | 1221 | 1235 |

| 2 | 8.1nm | 76nm   | 37.4nm | 1284 | 1274 | 1288 | 1288 | 1272 | 1292 | 1290 | 1278 | 1295 |

| 3 | 6.3nm | 47.5nm | 22.9nm | 1234 | 1223 | 1241 | 1229 | 1245 | 1222 | 1231 | 1230 | 1246 |

実施例4の面平均輝度 (cd/m<sup>2</sup>)

20

【表8】

| 抵抗値 (Ω) |       |

|---------|-------|

| 1       | 300 k |

| 2       | 50 k  |

| 3       | 100 k |

実施例4の接触抵抗

30

【表9】

|   | 構造体の有無 | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---|--------|------|------|------|------|------|------|------|------|------|

| 1 | あり     | 1592 | 1586 | 1571 | 1552 | 1520 | 1559 | 1589 | 1599 | 1611 |

| 2 | なし     | 1580 | 1342 | 1610 | 1319 | 1252 | 1350 | 1603 | 1422 | 1632 |

実施例5の面平均輝度 (cd/m<sup>2</sup>)

40

【表10】

| 抵抗値 (Ω) |      |

|---------|------|

| 1       | 10 K |

| 2       | 50 M |

実施例5の接触抵抗

50

【表11】

|   | 構造体の有無 | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---|--------|------|------|------|------|------|------|------|------|------|

| 1 | あり     | 1572 | 1584 | 1560 | 1541 | 1580 | 1527 | 1535 | 1543 | 1621 |

| 2 | なし     | 1575 | 1379 | 1621 | 1280 | 1211 | 1328 | 1628 | 1481 | 1642 |

実施例6の面平均輝度 (cd/m<sup>2</sup>)

【表12】

| 抵抗値 (Ω) |     |

|---------|-----|

| 1       | 15K |

| 2       | 70M |

実施例6の接触抵抗

10

【表13】

| 抵抗値 (Ω) |     |

|---------|-----|

| 1       | 30M |

| 2       | 20M |

比較例の接触抵抗

20

【表14】

|   | R <sub>a</sub> | P・V    | R <sub>z</sub> | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---|----------------|--------|----------------|------|------|------|------|------|------|------|------|------|

| 1 | 1nm            | 10.3nm | 5.1nm          | 1540 | 1350 | 1590 | 1305 | 1180 | 1290 | 1590 | 1360 | 1570 |

| 2 | 0.7nm          | 5.7nm  | 2.6nm          | 1580 | 1390 | 1620 | 1340 | 1220 | 1320 | 1610 | 1405 | 1630 |

比較例の面平均輝度 (cd/m<sup>2</sup>)

【0111】

以上本発明によれば、実施例は比較例に比べて、上部画素電極補助配線と上部画素電極の接触抵抗が低いため、陰極シート抵抗による電圧低下が生じないことから画面の輝度が均一になっている。

30

【産業上の利用可能性】

【0112】

本発明は、有機EL画像表示に代表される画像表示装置に関して、形態機器、TVなどのカラーディスプレイに使用できる。

【図面の簡単な説明】

【0113】

【図1】本実施の形態に使用される薄膜トランジスタを形成する工程図である。

【図2】本実施の形態に使用される上部光取りだし有機EL表示装置の基板概念図である。

【図3】本実施の形態に使用される青緑色発光素子の発光スペクトル図である。

【図4】本実施の形態に使用されるカラーフィルタ、および蛍光変換フィルタ図である。

【図5】本実施の形態に使用される上部光取りだし有機EL表示装置の概念図である。

【図6】本実施の形態に使用される白色発光素子の発光スペクトル図である。

【図7】本実施の形態に使用される上部光取りだし有機EL表示装置の補助配線形成時の概念図である。

【図8】本実施の形態に使用される上部光取りだし有機EL表示装置の補助配線形成時の概念図である。

【図9】本実施の形態に使用される上部光取りだし有機EL表示装置の補助配線形成時の概念図である。

【図10】本実施の形態に使用される下部光取りだし有機EL表示装置の補助配線形成時

40

50

の概念図である。

【図11】本実施の形態に使用される上部光取りだし有機EL表示装置の補助配線形成時の概念図である。

【図12】本実施の形態に使用される上部光取りだし有機EL表示装置の補助配線形成時の概念図である。

【図13】上部光取りだし有機EL表示装置の補助配線形成時の比較例概念図である。

【図14】本実施の形態に使用される上部光取りだし有機EL表示装置の陰極コンタクト説明図である。

【図15】本実施の形態に使用される上部光取りだし有機EL表示装置の発光測定概念図である。

10

20

30

【図16】本実施の形態に使用される構造体の概念図である。

【符号の説明】

【0114】

|       |             |

|-------|-------------|

| 1     | 絶縁性基板       |

| 3     | ゲート電極       |

| 8 - 1 | 第1有機層       |

| 8 - 2 | 第2有機層       |

| 8 - 3 | 第3有機層       |

| 8 - 4 | 第4有機層       |

| 9     | 上部画素電極      |

| 10    | 封止絶縁膜       |

| 20    | 活性シリコン層     |

| 21    | ゲート絶縁膜      |

| 22    | 層間絶縁膜       |

| 23    | コンタクトホール    |

| 24    | 配線          |

| 25    | 下部画素電極      |

| 26    | エッジカバー      |

| 30    | カラーフィルタ付き基板 |

| 31    | 赤色カラーフィルタ   |

| 32    | 緑色カラーフィルタ   |

| 33    | 青色カラーフィルタ   |

| 34    | 蛍光変換層       |

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図13】

【図12】

【図14】

【図15】

【図16】

(a)

(b)

(c)

---

フロントページの続き

(72)発明者 安川 浩司

東京都中央区日本橋一丁目13番1号 TDK株式会社内

(72)発明者 荒井 三千男

東京都中央区日本橋一丁目13番1号 TDK株式会社内

(72)発明者 福田 純也

東京都中央区日本橋一丁目13番1号 TDK株式会社内

(72)発明者 青谷 淳司

東京都中央区日本橋一丁目13番1号 TDK株式会社内

(72)発明者 宮城 徳子

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 坂倉 真之

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 棚田 好文

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 西川 智子

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 荒尾 達也

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

F ターム(参考) 3K007 AB17 AB18 BA06 BB06 CC00 DB03 EA00 FA01

|                |                                                                                                                                                                                 |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 画像表示装置                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2005235491A</a>                                                                                                                                                   | 公开(公告)日 | 2005-09-02 |

| 申请号            | JP2004041299                                                                                                                                                                    | 申请日     | 2004-02-18 |

| [标]申请(专利权)人(译) | 东京电气化学工业株式会社<br>株式会社半导体能源研究所                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | TDK株式会社<br>半导体能源研究所有限公司                                                                                                                                                         |         |            |

| [标]发明人         | 高山一郎<br>安川浩司<br>荒井三千男<br>福田純也<br>青谷淳司<br>宮城徳子<br>坂倉真之<br>棚田好文<br>西川智子<br>荒尾達也                                                                                                   |         |            |

| 发明人            | 高山 一郎<br>安川 浩司<br>荒井 三千男<br>福田 純也<br>青谷 淳司<br>宮城 徳子<br>坂倉 真之<br>棚田 好文<br>西川 智子<br>荒尾 達也                                                                                         |         |            |

| IPC分类号         | H01L51/50 H05B33/12 H05B33/14 H05B33/22 H05B33/26                                                                                                                               |         |            |

| FI分类号          | H05B33/14.A H05B33/12.B H05B33/22.Z H05B33/26.Z H01L27/32                                                                                                                       |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/AB18 3K007/BA06 3K007/BB06 3K007/CC00 3K007/DB03 3K007/EA00 3K007/FA01 3K107/AA01 3K107/BB01 3K107/DD37 3K107/DD89 3K107/DD90 3K107/EE03 3K107/FF04 3K107/FF07 |         |            |

| 代理人(译)         | 木村充                                                                                                                                                                             |         |            |

| 其他公开文献         | JP4664604B2                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                       |         |            |

**摘要(译)**

要解决的问题使用金属掩模为上部像素电极准备辅助布线时增加成本。另外，难以抑制颗粒的产生，并且产生诸如泄漏，暗点等的缺陷，这倾向于导致图像显示装置中的缺陷。在不使用金属掩模的情况下形成辅助布线，在与有源型有机EL显示基板的下部像素电极相同的表面上形成表面粗糙的辅助布线，并且可以与上部像素电极连接到。此外，在辅助布线上形成结构体，以使得能够与上像素电极连接。由此，可以实现具有简单结构的有源型有机EL图像显示装置，以减少泄漏和暗点的发生，并且可以确保具有足够发光区域的图像装置的显示质量。即使当上像素电极是不透明电极并且下像素电极是透明的时，也可以降低上像素电极的布线电阻。点域7