(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5738910号

(P5738910)

(45) 発行日 平成27年6月24日(2015.6.24)

(24) 登録日 平成27年5月1日(2015.5.1)

|                               |                            |

|-------------------------------|----------------------------|

| (51) Int.CI.                  | F 1                        |

| G 0 9 G    3/30    (2006.01)  | G 0 9 G    3/30    J       |

| G 0 9 G    3/20    (2006.01)  | G 0 9 G    3/20    6 2 4 B |

| H 0 1 L    51/50    (2006.01) | G 0 9 G    3/20    6 1 1 H |

|                               | G 0 9 G    3/20    6 7 0 J |

|                               | G 0 9 G    3/20    6 7 0 B |

請求項の数 2 (全 27 頁) 最終頁に続く

|              |                               |                     |                     |

|--------------|-------------------------------|---------------------|---------------------|

| (21) 出願番号    | 特願2013-32522 (P2013-32522)    | (73) 特許権者           | 514188173           |

| (22) 出願日     | 平成25年2月21日 (2013.2.21)        | 株式会社 J O L E D      |                     |

| (62) 分割の表示   | 特願2009-548819 (P2009-548819)  | 東京都千代田区神田錦町三丁目23番地  |                     |

| 原出願日         | の分割                           | (74) 代理人            | 100189430           |

| (65) 公開番号    | 平成20年12月26日 (2008.12.26)      | 弁理士                 | 吉川 修一               |

| (43) 公開日     | 特開2013-148908 (P2013-148908A) | (74) 代理人            | 100190805           |

| 審査請求日        | 平成25年8月1日 (2013.8.1)          | 弁理士                 | 傍島 正朗               |

| (31) 優先権主張番号 | 特願2008-779 (P2008-779)        | (72) 発明者            | 小田原 理恵              |

| (32) 優先日     | 平成20年1月7日 (2008.1.7)          | 大阪府門真市大字門真1006番地 パナ |                     |

| (33) 優先権主張国  | 日本国 (JP)                      | ソニック株式会社内           |                     |

|              |                               | (72) 発明者            | 小野 晋也               |

|              |                               |                     | 大阪府門真市大字門真1006番地 パナ |

|              |                               |                     | ソニック株式会社内           |

|              |                               | 審査官                 | 橋本 直明               |

最終頁に続く

(54) 【発明の名称】表示装置、電子装置及び駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素部と、当該複数の画素部の発光を決定する複数のデータ線とを有するアクティブマトリクス型の発光パネルを備える表示装置であって、

前記複数の画素部のそれぞれは、

前記複数のデータ線のうちいずれかのデータ線から供給された信号電圧を信号電流に変換する第1トランジスタと、

前記データ線と前記第1トランジスタのゲートとの間に挿入され、前記データ線と前記第1トランジスタのゲートとの導通及び非導通を切り換える第1スイッチ素子と、

前記第1トランジスタのソース及びドレインの一方である第1端子からアノード及びカソードの一方に入力される前記信号電流により発光する発光素子とを備え、

検査電流を前記データ線に供給する検査電流発生回路と、

前記データ線から入力される前記検査電流を前記発光素子に流すように回路バスを形成する第1回路バス形成手段と、

前記検査電流により発生した前記発光素子のアノード及びカソードの一方の電圧を前記データ線に発生させるよう回路バスを形成する第2回路バス形成手段と、

前記検査電流により発生した前記発光素子のアノード及びカソードの一方の電圧を、前記第2回路バス形成手段により形成されたバスを介して前記データ線にて検出する電圧検出回路とを備え、

前記第1回路バス形成手段及び前記第2回路バス形成手段は、

10

20

前記第1端子と前記発光素子のアノード及びカソードの一方との接続点と、前記データ線との導通及び非導通を切り換える第2スイッチングトランジスタを備え、

前記検査電流発生回路及び前記電圧検出回路は、前記データ線の両側に、前記複数の画素部を挟んで接続されている

ことを特徴とする表示装置。

【請求項2】

複数の画素部の発光を決定する複数のデータ線のうちいずれかのデータ線から供給された信号電圧を信号電流に変換する第1トランジスタと、前記データ線と前記第1トランジスタのゲートとの間に挿入され前記データ線と前記第1トランジスタのゲートとの導通及び非導通を切り換える第1スイッチ素子と、前記第1トランジスタのソース及びドレインの一方である第1端子からアノード及びカソードの一方に入力される前記信号電流により発光する発光素子と、前記第1端子と前記発光素子のアノード及びカソードの一方との接続点と、前記データ線との導通及び非導通を切り換える第2スイッチングトランジスタとを備える画素部を複数有するアクティブマトリクス型の発光パネルを備える表示装置の駆動方法であって、

前記信号電圧を前記データ線に供給するデータ駆動回路と前記データ線との接続を非導通状態にし、前記発光素子に検査電流を供給する検査電流発生回路と前記データ線との接続を導通状態にする電流源接続ステップと、

前記電流源接続ステップの後、前記検査電流発生回路から前記データ線を介して入力される前記検査電流を前記発光素子に流す電流供給ステップと、

前記第2検査電流を流すことにより発生した前記発光素子のアノード及びカソードの一方の電圧を、前記データ線に接続され、前記複数の画素部を挟んで前記検査電流発生回路と反対側に配置された電圧検出回路により検出する電圧検出ステップとを含む

ことを特徴とする表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は表示装置、電子装置及びそれらの駆動方法に関し、特に電流駆動型の発光素子を用いた表示装置、電子装置及びそれらの駆動方法に関する。

【背景技術】

【0002】

電流駆動型の発光素子を用いた画像表示装置として、有機EL素子(OLED:Organic Light Emitting Diode)を用いた画像表示装置(有機ELディスプレイ)が知られている。この有機ELディスプレイは、視野角特性が良好で、消費電力が少ないという利点を有するため、次世代のFPD(Flat Panel Display)候補として注目されている。

【0003】

有機ELディスプレイでは、通常、画素を構成する有機EL素子がマトリクス状に配置される。複数の行電極(走査線)と複数の列電極(データ線)との交点に有機EL素子を設け、選択した行電極と複数の列電極との間にデータ信号に相当する電圧を印加するようにして有機EL素子を駆動するものをパッシブマトリクス型の有機ELディスプレイと呼ぶ。

【0004】

一方、複数の走査線と複数のデータ線との交点に薄膜トランジスタ(TFT:Thin Film Transistor)を設け、このTFTにドライビングトランジスタのゲートを接続し、選択した走査線を通じてこのTFTをオンさせてデータ線からデータ信号をドライビングトランジスタに入力し、そのドライビングトランジスタによって有機EL素子を駆動するものをアクティブマトリクス型の有機ELディスプレイと呼ぶ。

【0005】

各行電極(走査線)を選択している期間のみ、それに接続された有機EL素子が発光す

10

20

30

40

50

るパッシブマトリクス型の有機ELディスプレイとは異なり、アクティブマトリクス型の有機ELディスプレイでは、次の走査（選択）まで有機EL素子を発光させることが可能であるため、デューティ比が上がってもディスプレイの輝度減少を招くようなことはない。従って、低電圧で駆動できるので、低消費電力化が可能となる。しかしながら、アクティブマトリクス型の有機ELディスプレイでは、ドライビングトランジスタや有機EL素子の特性のばらつきに起因して、同じデータ信号を与えても、各画素において有機EL素子の輝度が異なり、輝度むらが発生するという欠点がある。

#### 【0006】

従来の有機ELディスプレイにおける、ドライビングトランジスタや有機EL素子の特性のばらつきや劣化（以下、特性の不均一と総称する）による輝度ムラの補償方法としては、複雑な画素回路による補償、代表画素によるフィードバック補償、また、全画素に流れる電流の合計によるフィードバック補償などが代表的である。

10

#### 【0007】

しかし、複雑な画素回路は歩留まりを下げてしまう。また、代表画素によるフィードバックや、全画素に流れる電流の合計によるフィードバックでは、画素ごとの特性の不均一を補償できない。

#### 【0008】

上記理由により、簡単な画素回路で、画素ごとに特性の不均一を検出する方法がいくつか提案されている。

#### 【0009】

例えば、特許文献1に開示された発光パネル用基板、発光パネル用基板の検査方法及び発光パネルでは、従来の2つのトランジスタからなる電圧駆動画素回路に、ダイオード接続のトランジスタを接続し、それをELに見立てることによって、EL形成前の発光パネル用基板の状態において、そのダイオード接続のトランジスタに接続されたテスト線に流れる電流を測定し、データ電圧と駆動トランジスタを流れる電流との関係を検出して、画素検査及び画素特性抽出がなされている。また、そのEL形成後もダイオード接続のトランジスタはテスト線を用いて逆バイアスとして電流を流さないようにできるため、通常の電圧書き込み動作が行える。また、アレイの状態で検出された特性は、有機EL発光パネルを使用する際のデータ線への印加電圧の補正制御に利用することができる。

20

#### 【先行技術文献】

30

#### 【特許文献】

#### 【0010】

#### 【特許文献1】特開2006-139079号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0011】

しかしながら、画素に流れる駆動電流は非常に微小であり、微小電流の測定を精度よく行うことは困難である。また、初期の特性ばらつきや劣化による特性変化は、トランジスタにのみ起こるものではなく、有機EL素子にも起こるものなので、有機EL特性を検出しない方法では、画素の輝度の不均一を補償できない。

40

#### 【0012】

さらに、従来の方法では、発光パネル完成後の動作においても、駆動トランジスタ及び有機EL素子の特性の経時変化を精度よく補償する手段を有しない。一般に、駆動トランジスタは、その材料として低温ポリシリコンが用いられる場合は、初期特性にばらつきはあるものの、その後の特性は安定している。これに対し、発光パネルの大面積化に有利なアモルファスシリコンが駆動トランジスタの材料として用いられる場合は、特性パラメータの経時変化が大きい。また、一般に、有機EL素子の寿命特性は駆動電流の積算時間にも依存する。従って、駆動トランジスタおよび有機EL素子の経時変化による特性パラメータの変化を精度よく補償することは重要である。

#### 【0013】

50

上述したように、従来技術では、トランジスタの特性を検出する際、電流測定を用いるので、特性の検出精度が悪いという課題、そして、有機EL素子形成後のパネルにおいて、有機EL素子の特性を検出する手段をもたないという課題を有する。

【0014】

上記課題に鑑み、本発明は、単純な画素回路でありながら、電圧測定により、各画素のトランジスタと有機ELの素子の特性を切り分けて精度よく検出することを可能とする表示装置、電子装置及びそれらの駆動方法を提供することを第1の目的とする。また、その検出結果を用いることにより駆動能動素子や発光素子の特性の不均一に起因する輝度ムラを補正できる表示装置、電子装置及びそれらの駆動方法を提供することを目的とする。

【課題を解決するための手段】

10

【0015】

上記目的を達成するために、本発明に係る表示装置は、複数の画素部と、当該複数の画素部の発光を決定する複数のデータ線とを有するアクティブマトリクス型の発光パネルを備える表示装置であって、前記複数の画素部のそれぞれは、前記複数のデータ線のうちいずれかのデータ線から供給された信号電圧を信号電流に変換する第1トランジスタと、前記データ線と前記第1トランジスタのゲートとの間に挿入され、前記データ線と前記第1トランジスタのゲートとの導通及び非導通を切り換える第1スイッチ素子と、前記第1トランジスタのソース及びドレインの一方である第1端子からアノード及びカソードの一方に入力される前記信号電流により発光する発光素子とを備え、検査電流を前記データ線に供給する検査電流発生回路と、前記データ線から入力される前記検査電流を前記発光素子に流すように回路バスを形成する第1回路バス形成手段と、前記検査電流により発生した前記発光素子のアノード及びカソードの一方の電圧を前記データ線に発生させるよう回路バスを形成する第2回路バス形成手段と、前記検査電流により発生した前記発光素子のアノード及びカソードの一方の電圧を、前記第2回路バス形成手段により形成されたバスを介して前記データ線にて検出する電圧検出回路とを備え、前記第1回路バス形成手段及び前記第2回路バス形成手段は、前記第1端子と前記発光素子のアノード及びカソードの一方との接続点と、前記データ線との導通及び非導通を切り換える第2スイッチングトランジスタを備え、前記検査電流発生回路及び前記電圧検出回路は、前記データ線の両側に、前記複数の画素部を挟んで接続されていることを特徴とする。

20

【0016】

30

これにより、発光素子のばらつきに関する特性情報を独立に取得することができる。また、検査電流が発光素子を流れ、その時のデータ線の電圧が測定されるので、電圧を入力して微小電流を検出するという従来の測定方法型に比べ、高精度な測定が実現される。さらに、取得した特性情報を通常動作時のデータ電圧の補正に用いることで、発光素子の特性ばらつきによる輝度ムラを改善することができる。

【0017】

また、本発明に係る電子装置は、発光素子を形成することが可能な複数の画素部と複数のデータ線とを有するアクティブマトリクス型の発光用パネル基板を備える電子装置であって、前記複数の画素部のそれぞれは、前記複数のデータ線のうちいずれかのデータ線から供給された前記信号電圧を信号電流に変換する第1トランジスタと、前記データ線と前記第1トランジスタのゲートとの間に挿入され、前記データ線と前記第1トランジスタのゲートとの導通及び非導通を切り換える第1スイッチ素子とを備え、検査電流を前記データ線に供給する検査電流発生回路と、前記データ線から入力される前記検査電流を前記第1トランジスタのソース-ドレイン間に流すように回路バスを形成する第1回路バス形成手段と、前記検査電流により発生した前記第1トランジスタのゲート電圧に対応した電圧を前記データ線に発生させるよう回路バスを形成する第2回路バス形成手段と、前記検査電流により発生した前記第1トランジスタのゲート電圧に対応した電圧を前記データ線にて検出する電圧検出回路とを備え、前記第1回路バス形成手段及び前記第2回路バス形成手段は、前記第1トランジスタのソース及びドレインの一方である第1端子と、前記データ線との導通及び非導通を切り換える第2スイッチングトランジスタを備え、前記検査電

40

50

流発生回路及び前記電圧検出回路は、前記データ線の両側に、前記複数の画素部を挟んで接続されていることを特徴とする。

【0018】

これにより、発光素子が形成される前の状態において、駆動トランジスタである第1トランジスタのばらつきに関する特性情報を取得することができる。また、検査電流が駆動トランジスタに流れ、その時のデータ線の電圧が測定されるので、電圧を入力して微小電流を検出するという従来の測定方法型に比べ、高精度な測定が実現される。さらに、取得した特性情報を通常動作時のデータ電圧の補正に用いることで、駆動トランジスタの特性ばらつきによる輝度ムラを改善することができる。

【0019】

また、本発明は、このような特徴的な手段を備える表示装置又は電子装置として実現することができるだけでなく、表示装置又は電子装置に含まれる特徴的な手段をステップとする表示装置又は電子装置の駆動方法として実現することができる。

【発明の効果】

【0020】

本発明の表示装置、電子装置及びそれらの駆動方法によれば、単純な画素回路構成でしかも検出精度の高い電圧測定により、各画素の駆動トランジスタと有機EL素子の特性を切り分けて高精度測定できるので、駆動能動素子や発光素子の特性の不均一に起因する輝度ムラを補正できるという効果を奏する。

【図面の簡単な説明】

【0021】

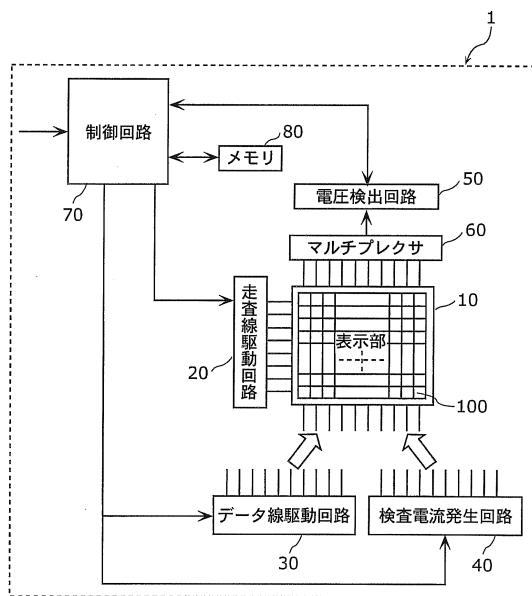

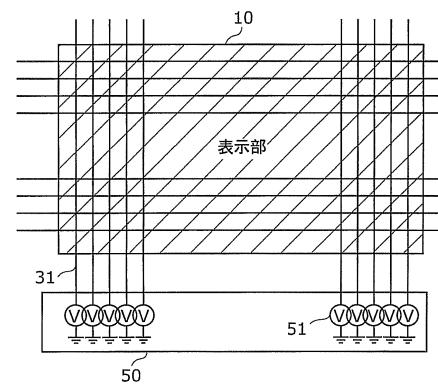

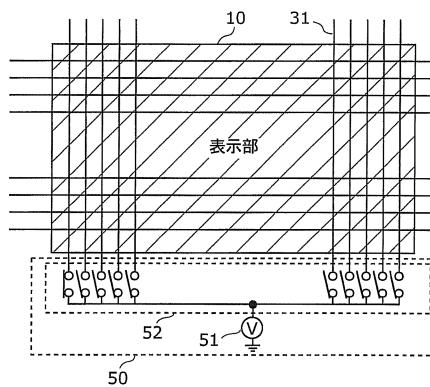

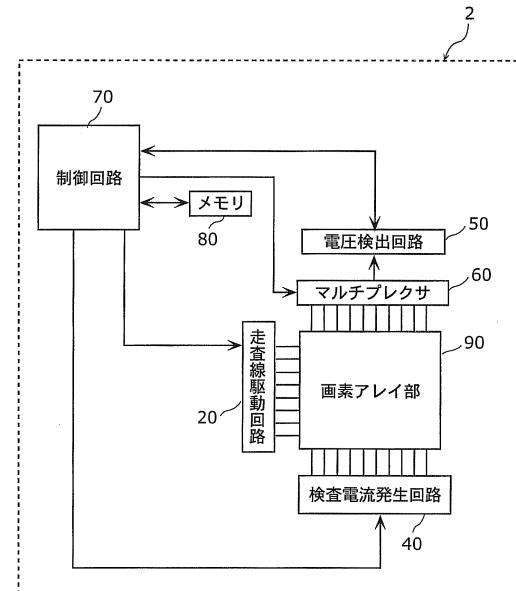

【図1】図1は、本発明の実施の形態1に係る表示装置の電気的な構成を示すブロック図である。

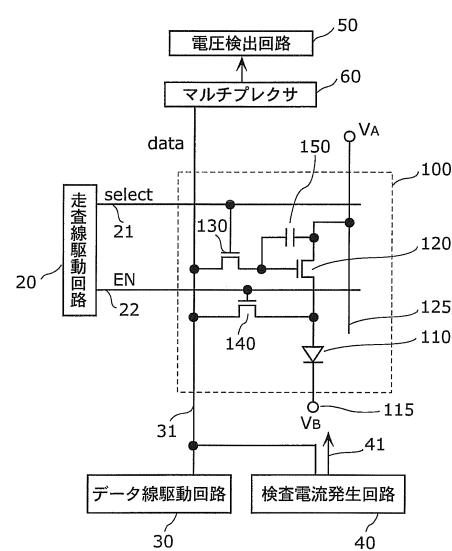

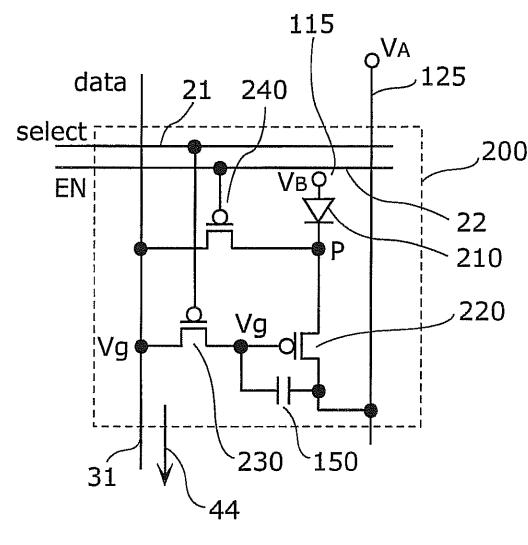

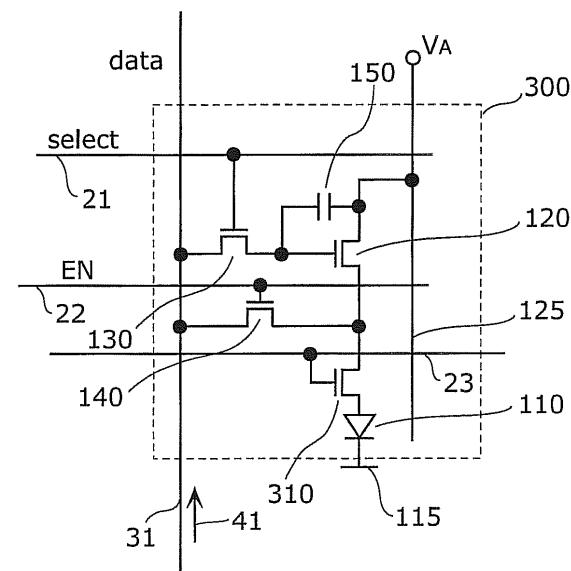

【図2】図2は、表示部の有する一画素部の回路構成及びその周辺回路との接続を示す図である。

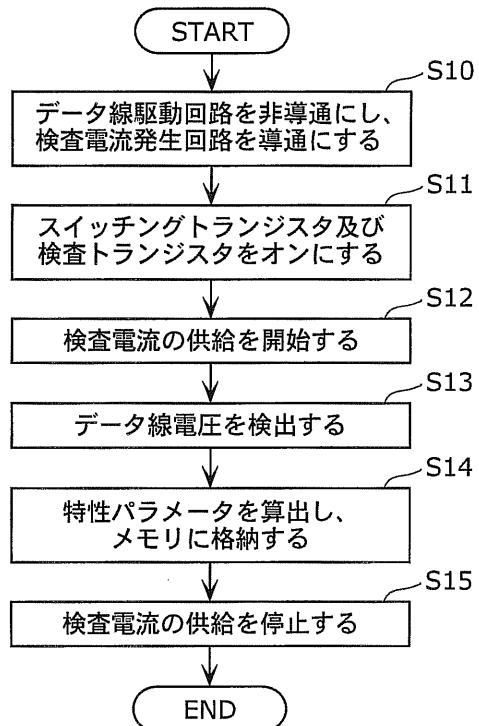

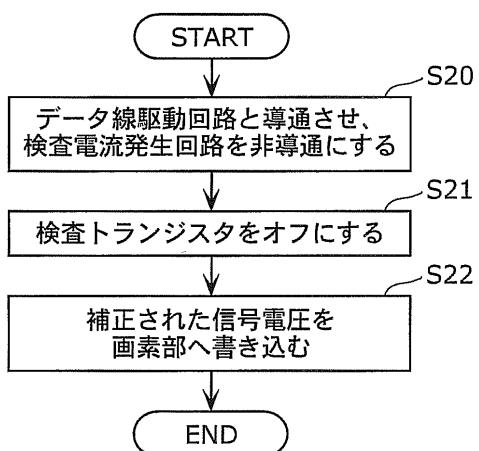

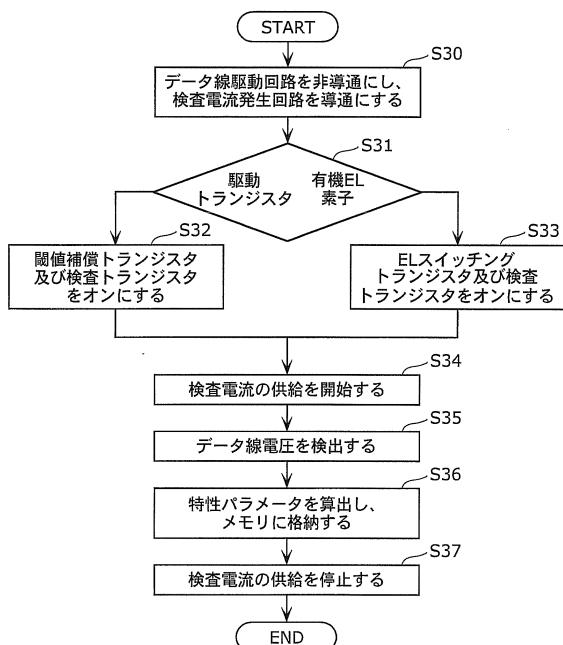

【図3】図3は、本発明の実施の形態1に係る表示装置の有する制御回路の、駆動トランジスタ又は有機EL素子の特性を検出する場合の動作フローチャートである。

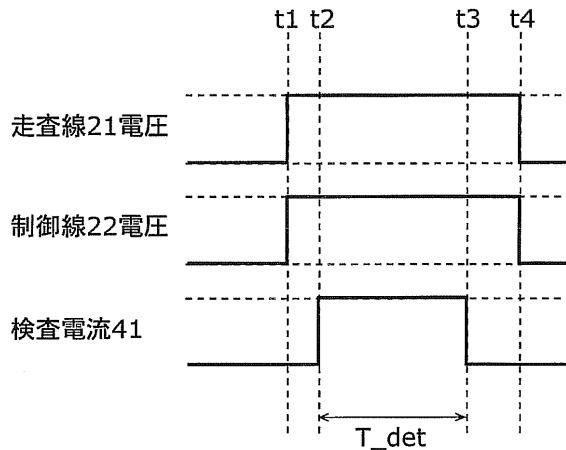

【図4】図4は、駆動トランジスタ特性又は有機EL素子特性を検出する場合の検査電流の供給タイミングを示すタイミングチャートである。

【図5】図5は、通常動作時における制御回路の動作フローチャートである。

30

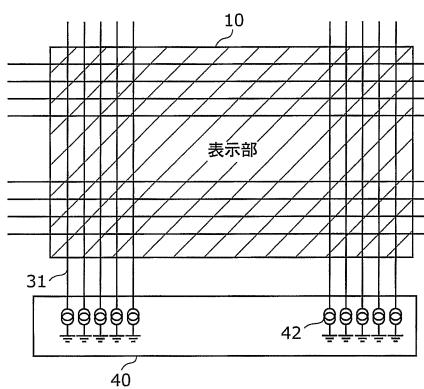

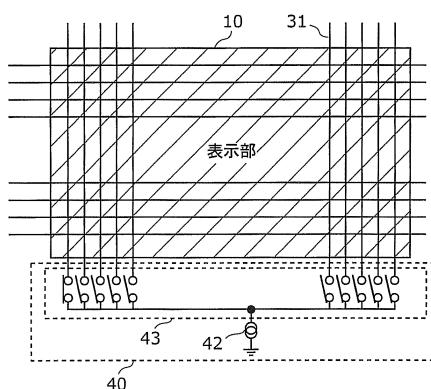

【図6】図6は、データ線と検査電流発生回路との接続関係を示す図である。

【図7】図7は、データ線と検査電流発生回路との接続関係を示す図である。

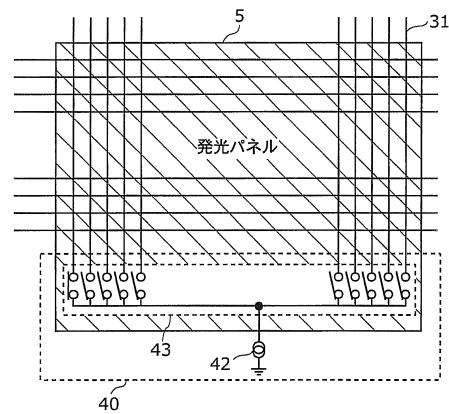

【図8】図8は、データ線と検査電流発生回路との接続関係を示す図である。

【図9】図9は、データ線と電圧検出回路との接続関係を示す図である。

【図10】図10は、データ線と電圧検出回路との接続関係を示す図である。

【図11】図11は、データ線と電圧検出回路との接続関係を示す図である。

【図12】図12は、本発明の実施の形態1の第1の変形例を示す表示装置の備える画素部の回路構成図である。

【図13】図13は、本発明の実施の形態1の第2の変形例を示す表示装置の備える画素部の回路構成図である。

40

【図14】図14は、本発明の実施の形態1の第3の変形例を示す表示装置の備える画素部の回路構成図である。

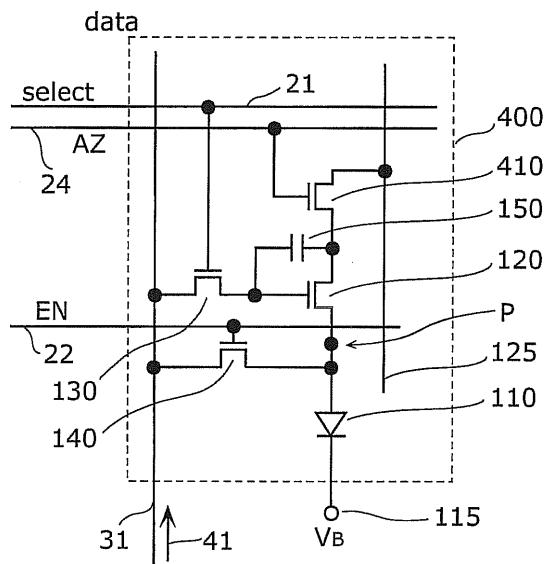

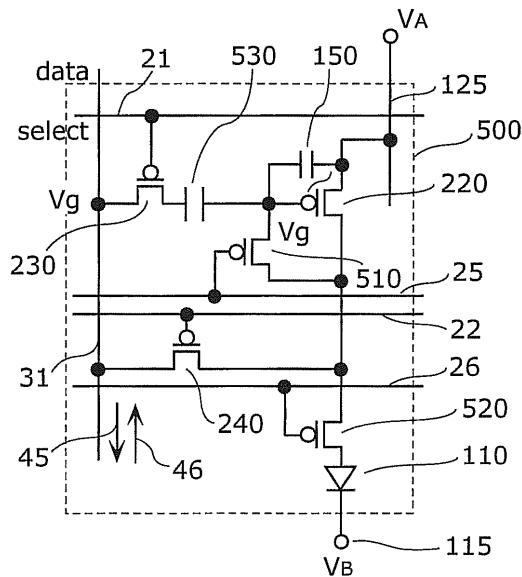

【図15】図15は、本発明の実施の形態2に係る表示装置の有する画素部の回路構成図である。

【図16】図16は、本発明の実施の形態2に係る表示装置の有する制御回路の、駆動トランジスタ又は有機EL素子の特性を検出する場合の動作フローチャートである。

【図17】図17は、駆動トランジスタ特性検出時の検査電流の供給タイミングを示すタイミングチャートである。

【図18】図18は、有機EL素子特性検出時の検査電流の供給タイミングを示すタイミングチャートである。

50

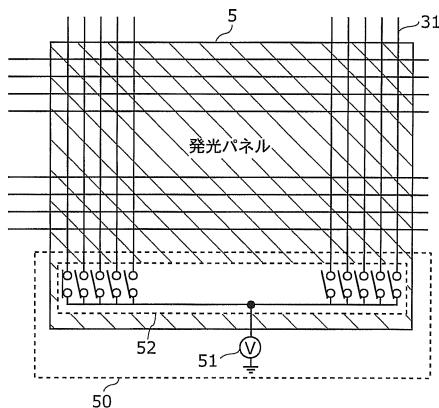

【図19】図19は、本発明の実施の形態3に係る電子装置の電気的な構成を示すブロック図である。

【図20】図20は、画素アレイ部の有する一画素部の回路構成及びその周辺回路との接続を示す図である。

【図21】図21は、本発明の表示装置を内蔵した薄型フラットTVの外観図である。

【発明を実施するための形態】

【0022】

(実施の形態1)

本実施の形態における表示装置は、複数の画素部を有するアクティブマトリクス型の発光パネルを備え、画素部は、選択されたデータ線から供給された信号電圧に対応した信号電流を出力する第1トランジスタと、第1トランジスタへの信号電圧の供給をオンオフする第1スイッチ素子と、信号電流の入力により光信号を出力する発光素子と、選択されたデータ線と第1トランジスタの第2端子とが短絡状態であることを可能とするように接続された第2スイッチ素子とを備える。また、本表示装置は、さらに、第1トランジスタ又は発光素子に検査電流を流す検査電流発生回路と、当該検査電流により発生した電圧を選択されたデータ線にて測定する電圧検出回路とを備える。これにより、各画素に配置された駆動トランジスタと発光素子の特性を独立に高精度測定できるので、駆動トランジスタや発光素子の特性の不均一に起因する輝度ムラを補正できる。

10

【0023】

図1は、本発明の実施の形態1に係る表示装置の電気的な構成を示すブロック図である。同図における表示装置1は、表示部10と、走査線駆動回路20と、データ線駆動回路30と、検査電流発生回路40と、電圧検出回路50と、マルチプレクサ60と、制御回路70と、メモリ80とを備える。

20

【0024】

表示部10は、複数の画素部100を備える。

【0025】

図2は、表示部の有する一画素部の回路構成及びその周辺回路との接続を示す図である。同図における画素部100は、有機EL素子110と、駆動トランジスタ120と、スイッチングトランジスタ130と、検査トランジスタ140と、保持容量150と、共通電極115と、電源線125と、走査線21と、制御線22と、データ線31とを備える。また、周辺回路は、走査線駆動回路20と、データ線駆動回路30と、検査電流発生回路40と、電圧検出回路50と、マルチプレクサ60とを備える。

30

【0026】

まず、図1に記載された構成要素について、その機能を説明する。

【0027】

走査線駆動回路20は、走査線21、第1制御線である制御線22に接続されており、画素部100のスイッチングトランジスタ130及び検査トランジスタ140の導通・非導通を制御する機能を有する。

【0028】

データ線駆動回路30は、データ線31に接続されており、信号電圧を出力して、駆動トランジスタ120に流れる信号電流を決定する機能を有する。また、データ線駆動回路30は、データ線31との接続を開放したり、ショートしたりすることが可能なスイッチを有する。

40

【0029】

検査電流発生回路40は、データ線31に接続されており、駆動トランジスタ120や有機EL素子110の特性を検出するための検査電流を出力する機能を有し、第1回路バス形成手段の構成要素である。

【0030】

電圧検出回路50は、マルチプレクサ60を介してデータ線31に接続されており、検査電流発生回路40が検査電流を出力している間に、データ線31の電圧を検出する機能

50

を有し、第2回路バス形成手段の構成要素である。

【0031】

マルチプレクサ60は、電圧検出回路50に接続されるデータ線31の切り替えを行う機能を有する。

【0032】

制御回路70は、走査線駆動回路20、データ線駆動回路30、検査電流発生回路40、マルチプレクサ60、電圧検出回路50、及びメモリ80の制御を行う機能を有する。電圧検出回路50により検出された電圧値は、デジタル値に変換され、演算により特性パラメータ化される。そして、制御回路70によりメモリ80に書き込まれる。また、制御回路70は、メモリ80に書き込まれた特性パラメータを読み出し、外部から入力された映像信号データを、その特性パラメータに基づいて補正して、データ線駆動回路30へと出力する。

【0033】

次に、画素部100の内部回路構成について、図2を用いて説明する。

【0034】

駆動トランジスタ120は、第1トランジスタとして機能し、駆動トランジスタ120のゲートは、スイッチングトランジスタ130を介してデータ線31に接続され、第1端子であるソース及びドレインの一方が有機EL素子110の一方の端子であるアノードに接続され、第2端子であるソース及びドレインの他方が、電源線125に接続されている。

【0035】

また、スイッチングトランジスタ130は、第1スイッチングトランジスタとして機能し、スイッチングトランジスタ130のゲートは、走査線21に接続されている。

【0036】

検査トランジスタ140は、第2トランジスタとして機能し、検査電流バスを形成する第1回路バス形成手段の構成要素である。また、検査トランジスタ140は、有機EL素子110のアノード電圧をデータ線31にて測定する電圧バスを形成する第2回路バス形成手段の構成要素を兼用している。検査用トランジスタ140のゲートは、制御線22に接続され、ソースは、有機EL素子110の一方の端子であるアノードに接続され、ドレインは、データ線31に接続されている。

【0037】

保持容量150は、電源線125と駆動トランジスタ120のゲート端子との間に接続されている。

【0038】

有機EL素子110は、発光素子として機能し、有機EL素子110の他方の端子であるカソードは、共通電極115に接続されている。

【0039】

なお、図1、図2には記載されていないが、電源線125はすべて同じ電源に接続されている。また、共通電極115も電源に接続されている。

【0040】

次に、本発明の実施の形態1にかかる表示装置の駆動方法について説明をする。本駆動方法により、駆動トランジスタ120の特性の検出、有機EL素子110の特性の検出が可能である。

【0041】

図3は、本発明の実施の形態1に係る表示装置の有する制御回路の、駆動トランジスタ又は有機EL素子の特性を検出する場合の動作フローチャートである。

【0042】

最初に、データ線駆動回路30とデータ線31との接続を非導通状態とし、検査電流発生回路40とデータ線31との接続を導通状態に設定する(S10)。この接続は、例えば、データ線駆動回路30とデータ線31との間のスイッチをオフすること、及び検査電

10

20

30

40

50

流発生回路 4 0 とデータ線 3 1 との間のスイッチをオンすることにより実現される。

【0043】

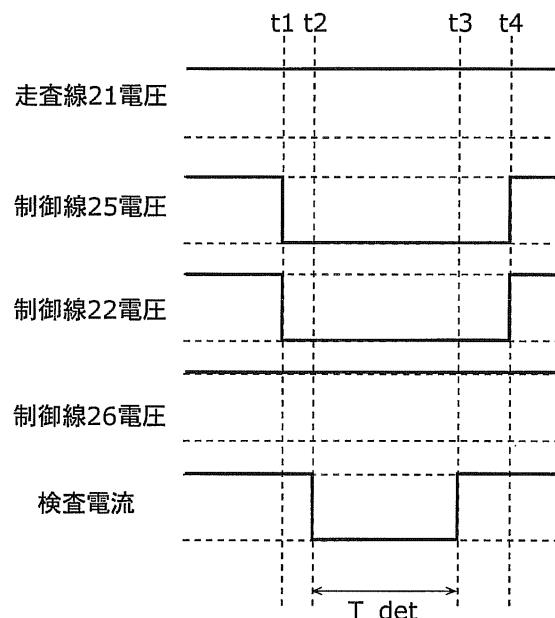

図 4 は、駆動トランジスタ特性又は有機 E L 素子特性を検出する場合の検査電流の供給タイミングを示すタイミングチャートである。同図において、横軸は時間を表している。また縦方向には、上から順に、走査線 2 1 に発生する電圧の波形図、制御線 2 2 に発生する電圧の波形図、及び検査電流 4 1 の波形図が示されている。

【0044】

次に、図 4 の t 1 において、走査線 2 1 及び制御線 2 2 の電圧のレベルを H I G H にして、それぞれ、スイッチングトランジスタ 1 3 0 及び検査トランジスタ 1 4 0 をオンにする (S 1 1)。なお、有機 E L 素子特性の検出時には、スイッチングトランジスタ 1 3 0 はオフであってもよい。

10

【0045】

次に、図 4 の t 2 において、検査電流発生回路 4 0 から図 2 中の矢印の向きに検査電流 4 1 を流す (S 1 2)。

【0046】

ステップ S 1 2 において、駆動トランジスタ 1 2 0 の特性検出時においては、共通電極 1 1 5 には、共通電極 1 1 5 に接続された第 2 電源により有機 E L 素子 1 1 0 に逆バイアスがかかるような可変電圧  $V_B$  が加えられるため、有機 E L 素子 1 1 0 には電流は流れない。よって、この検査電流 4 1 は、第 1 検査電流として、データ線 3 1 、検査トランジスタ 1 4 0 、及び駆動トランジスタ 1 2 0 を経由して、電源線 1 2 5 に流れこむ。その際、スイッチングトランジスタ 1 3 0 がオン状態であるので、駆動トランジスタ 1 2 0 のゲート端子はデータ線 3 1 に接続されている。よって、データ線 3 1 の電圧は、駆動トランジスタ 1 2 0 に検査電流 4 1 が流れた際の駆動トランジスタ 1 2 0 のゲート電圧とほぼ等しくなる。

20

【0047】

一方、ステップ S 1 2 において、有機 E L 素子 1 1 0 の特性検出時には、電源線 1 2 5 には、電源線 1 2 5 に接続された第 1 電源により、駆動トランジスタ 1 2 0 に電流が流れないように、駆動トランジスタ 1 2 0 のゲート電圧と同程度かそれ以上の可変電圧  $V_A$  が印加されており、この検査電流 4 1 は、第 2 検査電流として、データ線 3 1 、検査トランジスタ 1 4 0 、及び有機 E L 素子 1 1 0 を経由して、共通電極 1 1 5 に流れこむ。その際、検査トランジスタ 1 4 0 がオン状態であるので、有機 E L 素子 1 1 0 のアノード端子はデータ線 3 1 に接続されている。よって、データ線 3 1 の電圧は、有機 E L 素子 1 1 0 に検査電流 4 1 が流れた際の有機 E L 素子 1 1 0 のアノード電圧とほぼ等しくなる。

30

【0048】

次に、図 4 の t 2 から t 3 の間において、検査電流 4 1 を供給し、データ線 3 1 に現れた電圧を電圧検出回路 5 0 で検出する (S 1 3)。これにより、検査電流 4 1 の大きさに対する、駆動トランジスタ 1 2 0 のゲート電圧、又は有機 E L 素子 1 1 0 のアノード電圧を知ることができる。

【0049】

ここで、駆動トランジスタ 1 2 0 の特性を検出する場合には、上記ステップ S 1 3 において、駆動トランジスタ 1 2 0 のゲート端子とドレイン端子は、スイッチングトランジスタ 1 3 0 及び検査トランジスタ 1 4 0 を介して接続されているため、駆動トランジスタ 1 2 0 は飽和領域で動作している。また、駆動トランジスタ 1 2 0 のソース電圧は電源線 1 2 5 に印加された電圧である。ここで、検出された電圧を  $V_{det}$  、駆動トランジスタ 1 2 0 のソース端子に印加された電源電圧を  $V_{dd}$  、及び検査電流を  $I_{test}$  とすると、以下の式 1 が成り立つ。

40

【0050】

【数 1】

$$I_{test} = (\beta/2)(V_{det} - V_{dd} - V_{th})^2 \quad (式 1)$$

50

## 【0051】

ここで、 $\beta$ は、駆動トランジスタ120のチャネル領域、酸化膜容量、及び移動度に関する特性パラメータであり、 $V_{th}$ は、駆動トランジスタ120の閾値電圧であり移動度に関係する。

## 【0052】

式1により、大きさの異なる2種類の検査電流 $I_1$ 及び $I_2$ を流して検出された電圧をそれぞれ $V_{det1}$ 、 $V_{det2}$ とすると、以下のような連立方程式を立てることができる。

## 【0053】

## 【数2】

$$I_1 = (\beta/2)(V_{det1} - V_{dd} - V_{th})^2 \quad (式2)$$

## 【0054】

## 【数3】

$$I_2 = (\beta/2)(V_{det2} - V_{dd} - V_{th})^2 \quad (式3)$$

## 【0055】

$V_{gs1} = V_{det1} - V_{dd}$ 、 $V_{gs2} = V_{det2} - V_{dd}$ とおき、この連立方程式を解くと、 $\beta$ と $V_{th}$ はそれぞれ以下のようになる。

## 【0056】

## 【数4】

$$\beta = \left( \frac{\sqrt{2I_1} - \sqrt{2I_2}}{V_{gs1} - V_{gs2}} \right)^2$$

$$V_{th} = \frac{V_{gs2} \times \sqrt{2I_1} - V_{gs1} \times \sqrt{2I_2}}{\sqrt{2I_1} - \sqrt{2I_2}} \quad (式4)$$

## 【0057】

このようにして、検査電流41を流し、その時のデータ線31の電圧を測定することにより、駆動トランジスタ120の移動度や閾値といった特性パラメータを算出することができる。

## 【0058】

一方、有機EL素子110の特性を検出する場合には、検査電流41を $I_{EL}$ 、発生した有機EL素子110のアノード電圧を $V_{EL}$ とすると、予め取得されている有機EL素子110の初期の電流-電圧特性と、今回取得された( $I_{EL}$ 、 $V_{EL}$ )とのズレ量を算出する。

## 【0059】

次に、制御回路70は、電圧検出回路50により検出された電圧値 $V_{det1}$ 及び $V_{det2}$ 、または $V_{EL}$ をデジタル値に変換し、それらと式2ないし式4又は初期電流-電圧特性を用いて算出した特性パラメータをメモリ80に格納する(S14)。

## 【0060】

次に、図4のt3において、検査電流41の供給を停止する(S15)。

## 【0061】

なお、ステップS15は、ステップS14の後である必要はなく、ステップS14と並行して実行されてもよく、または、ステップS13の後であってステップS14の前に実行されてもよい。

## 【0062】

上述した一連の動作ステップにより、データ線の電圧が測定され、その検出結果が評価されることにより、画素部の画素欠陥が発見されるだけでなく、駆動トランジスタや有機EL素子のばらつきや経時変動に関する情報が独立に取得できる。取得された特性パラメ

10

20

30

40

50

ータがメモリに保存され、後述する通常動作時のデータ電圧の補正に用いられることで、駆動トランジスタや有機EL素子の特性ばらつきや経時変動による輝度ムラが改善される。

【0063】

次に、本発明の実施の形態1にかかる表示装置の通常動作時における駆動方法について説明する。

【0064】

図5は、通常動作時における制御回路の動作フローチャートである。

【0065】

最初に、データ線駆動回路30とデータ線31との接続を導通状態とし、検査電流発生回路40とデータ線31との接続を非導通状態に設定する(S20)。この接続は、例えば、検査電流発生回路40の出力電流をゼロにすることで実現できる。また、検査電流発生回路40とデータ線31との間に設けられたスイッチをオフすることで、接続を開放してもよい。

10

【0066】

次に、検査トランジスタ140を、オフ状態にする(S21)。なお、本ステップS21は、ステップS20の前に実行されていてもよい。また、通常動作時では、検査トランジスタ140は常にオフ状態であるが、検査トランジスタ140をオン状態とすることで、データ線駆動回路30の出力電圧を直接有機EL素子110に印加することができるため、駆動時の黒挿入に使ってもよい。

20

【0067】

最後に、メモリ80から読み出された特性パラメータにより補正された信号電圧をデータ線駆動回路30から出力し、画素部100へ書き込むことにより画像表示を実行する(S22)。

【0068】

以上、駆動トランジスタ及び有機EL素子の特性検出動作、及び通常動作により、特性検出時に得られた特性パラメータに基づき信号電圧が補正されるので、駆動トランジスタや有機EL素子の特性ばらつきや経時変動による輝度ムラが改善される。

【0069】

なお、図2において、電圧検出回路50と検査電流発生回路40とは、データ線31の両側に、画素部を挟んで接続されているが、電圧検出回路50と検査電流発生回路40とが、画素部に対してデータ線31の同じ側に接続されていてもよい。大きな検査電流を流してデータ線31の電圧が測定される場合、電圧検出回路50が、検査電流発生回路40と同じ側にあると、データ線31の配線抵抗による電圧降下により検出精度が低下する可能性がある。その場合は、電圧検出回路50と検査電流発生回路40とは、データ線31の両側に、画素部を挟んで接続されているのが好ましい。検査電流を大きくすることにより、検出時間を早めたい場合、データ線31の両側に接続する構成は非常に有効である。

30

【0070】

また、検査電流発生回路40は、データ線駆動回路30とともにデータドライバICに内蔵されていてもよいし、データドライバICとは別にあってもよい。

40

【0071】

また、検査電流発生回路40は、図6に示されるデータ線と検査電流発生回路との接続関係のように、データ線31の本数と同数の電流発生源42を有するものであってもよい。

【0072】

また、検査電流発生回路40は、図7に示されるデータ線と検査電流発生回路との接続関係のように、データ線31の切り替えを行うマルチプレクサ43とデータ線31の本数より少ない電流発生源42を有するものであってもよい。

【0073】

また、データ線31の切り替えを行うマルチプレクサ43とデータ線31より少ない電

50

流発生源 4 2 をもつ場合、マルチプレクサ 4 3 は、図 8 に示されるデータ線と検査電流発生回路との接続関係のように、発光パネル 5 上に形成されていてもよい。

【 0 0 7 4 】

さらに、電圧検出回路 5 0 は、データ線駆動回路 3 0 とともにデータドライバ IC に内蔵されていてもよいし、データドライバ IC とは別にあってもよい。

【 0 0 7 5 】

また、電圧検出回路 5 0 は、図 9 に示されるデータ線と電圧検出回路との接続関係のように、データ線 3 1 の本数と同数の電圧検出器 5 1 を有するものであってもよい。

【 0 0 7 6 】

また、電圧検出回路 5 0 は、図 1 0 に示されるデータ線と電圧検出回路との接続関係のように、データ線 3 1 の切り替えを行うマルチプレクサ 5 2 とデータ線 3 1 の本数より少ない電圧検出器 5 1 をもつものであってもよい。

【 0 0 7 7 】

また、データ線 3 1 の切り替えを行うマルチプレクサ 5 2 とデータ線 3 1 より少ない電圧検出器 5 1 をもつ場合、マルチプレクサ 5 2 は、図 1 1 に示されるデータ線と電圧検出回路との接続関係のように、発光パネル 5 上に形成されていてもよい。

【 0 0 7 8 】

図 1 2 は、本発明の実施の形態 1 の第 1 の変形例を示す表示装置の備える画素部の回路構成図である。同図における画素部 2 0 0 は、有機 EL 素子 2 1 0 と、駆動トランジスタ 2 2 0 と、スイッチングトランジスタ 2 3 0 と、検査トランジスタ 2 4 0 と、保持容量 1 5 0 と、共通電極 1 1 5 と、電源線 1 2 5 と、走査線 2 1 と、制御線 2 2 と、データ線 3 1 とを備える。

【 0 0 7 9 】

同図に記載された画素部 2 0 0 は、図 2 に記載された画素部 1 0 0 と比較して、トランジスタがすべて p チャネルであり、駆動トランジスタ 2 2 0 と接続される有機 EL 素子 2 1 0 の端子はカソードである点のみが回路構成として異なる。以下、画素部 2 0 0 を有する表示装置の駆動方法について、図 3 に記載された画素部 1 0 0 を有する表示装置の駆動方法と異なる点のみ説明する。

【 0 0 8 0 】

図 3 に記載されたステップ S 1 1 では、スイッチングトランジスタ 2 3 0 及び検査トランジスタ 2 4 0 をオン状態にするために、走査線 2 1 及び制御線 2 2 の電圧を HIGH レベルから LOW レベルに切り換える。なお、有機 EL 素子特性の検出時には、スイッチングトランジスタ 2 3 0 はオフであってもよい。

【 0 0 8 1 】

また、図 3 に記載されたステップ S 1 2 では、検査電流 4 4 は、図 2 に記載された検査電流 4 1 と逆向きになる。

【 0 0 8 2 】

これにより、ステップ S 1 3 では、検査電流 4 4 の大きさに対する、駆動トランジスタ 2 2 0 のゲート電圧、又は有機 EL 素子 2 1 0 のカソード電圧を知ることができる。

【 0 0 8 3 】

図 1 3 は、本発明の実施の形態 1 の第 2 の変形例を示す表示装置の備える画素部の回路構成図である。同図における画素部 3 0 0 は、有機 EL 素子 1 1 0 と、駆動トランジスタ 1 2 0 と、スイッチングトランジスタ 1 3 0 と、EL スイッチングトランジスタ 3 1 0 と、検査トランジスタ 1 4 0 と、保持容量 1 5 0 と、共通電極 1 1 5 と、電源線 1 2 5 と、走査線 2 1 と、制御線 2 2 及び 2 3 と、データ線 3 1 とを備える。

【 0 0 8 4 】

同図に記載された画素部 3 0 0 は、図 2 に記載された画素部 1 0 0 と比較して、有機 EL 素子 1 1 0 のアノード端子に EL スイッチングトランジスタ 3 1 0 が挿入されている点、及び EL スイッチングトランジスタ 3 1 0 のオンオフを制御するための制御線 2 3 が EL スイッチングトランジスタ 3 1 0 のゲートに接続されている点のみが回路構成として異

10

20

30

40

50

なる。

【0085】

ELスイッチングトランジスタ310は、第2スイッチ素子として機能し、有機EL素子110への検査電流の供給の有無を制御する。

【0086】

以下、画素部300を有する表示装置の駆動方法について、図3に記載された画素部100を有する表示装置の駆動方法と異なる点のみ説明する。

【0087】

図3に記載されたステップS12では、有機EL素子110に逆バイアス電圧が印加されることにより、有機EL素子110には検査電流が流れず、駆動トランジスタ120に検査電流41が流れるように制御されていた。これに対して、本実施例では、有機EL素子110のアノードに接続されたELスイッチングトランジスタ310を、制御線23を介してオフ状態とすることで、有機EL素子110に電流が流れず、駆動トランジスタ120に検査電流41が流れるように制御されている。

10

【0088】

図14は、本発明の実施の形態1の第3の変形例を示す表示装置の備える画素部の回路構成図である。同図における画素部400は、有機EL素子110と、駆動トランジスタ120と、スイッチングトランジスタ130及び410と、検査トランジスタ140と、保持容量150と、共通電極115と、電源線125と、走査線21と、制御線22及び24と、データ線31とを備える。

20

【0089】

同図に記載された画素部400は、図2に記載された画素部100と比較して、駆動トランジスタ120の第2端子と電源線125との間にスイッチングトランジスタ410が挿入されている点、及びスイッチングトランジスタ410のオンオフを制御するための制御線24がスイッチングトランジスタ410のゲートに接続されている点のみが回路構成として異なる。

【0090】

スイッチングトランジスタ410は、第3スイッチ素子として機能し、駆動トランジスタ120への検査電流の供給の有無を制御する。

30

【0091】

以下、画素部400を有する表示装置の駆動方法について、図3に記載された画素部100を有する表示装置の駆動方法と異なる点のみ説明する。

【0092】

図3に記載されたステップS12では、電源線125に駆動トランジスタ120のゲート電圧と同程度かそれ以上の電圧が印加されることにより、駆動トランジスタ120には検査電流が流れず、有機EL素子110に検査電流41が流れるように制御されていた。これに対して、本実施例では、駆動トランジスタ120の第2端子に接続されたスイッチングトランジスタ410を、制御線24を介してオフ状態とすることで、駆動トランジスタ120に電流が流れず、有機EL素子110に検査電流41が流れるように制御されている。

40

【0093】

なお、本実施例にて追加されたスイッチングトランジスタ410は、駆動トランジスタ120の第1端子に挿入(図14中の点P)されていてもよい。

【0094】

上述した本発明の実施の形態1における第1～第3の変形例においても、データ線の電圧が測定され、その検出結果が評価されることにより、画素部の画素欠陥が発見されるだけでなく、駆動トランジスタや有機EL素子のばらつきに関する情報が独立に取得できる。取得された特性パラメータがメモリに保存され、後述する通常動作時のデータ電圧の補正に用いられることで、駆動トランジスタや有機EL素子の特性ばらつきによる輝度ムラが改善される。

50

## 【0095】

## (実施の形態2)

本実施の形態における表示装置は、複数の画素部を有するアクティブマトリクス型の発光パネルを備え、画素部は、選択されたデータ線から供給された信号電圧に対応した信号電流を出力する第1トランジスタと、第1トランジスタへの信号電圧の供給をオンオフする第1スイッチ素子と、信号電流の入力により光信号を出力する発光素子と、第1トランジスタと第1スイッチ素子との間に接続された電圧変換部と、選択されたデータ線と第1トランジスタのゲート端子とが短絡状態または一定の電位差を有する導通状態であること、及び、選択されたデータ線と第1トランジスタの第2端子とが短絡状態であること、を可能とするように接続された1以上の第2スイッチ素子とを備える。また、電子装置は、さらに、第1トランジスタ又は発光素子に検査電流を流す検査電流発生回路と、当該検査電流により発生した電圧を、選択されたデータ線にて測定する電圧検出回路とを備える。これにより、第1トランジスタの閾値( $V_{th}$ )変動が補償された回路においても、各画素に配置された駆動トランジスタと発光素子の特性を独立に高精度測定できるので、駆動トランジスタや発光素子の特性の不均一に起因する輝度ムラを補正できる。

10

## 【0096】

図15は、本発明の実施の形態2に係る表示装置の有する画素部の回路構成図である。同図における画素部500は、有機EL素子110と、駆動トランジスタ220と、スイッチングトランジスタ230とELスイッチングトランジスタ520と、検査トランジスタ240と、閾値補償トランジスタ510と、保持容量150と、閾値補償容量530と、共通電極115と、電源線125と、走査線21と、制御線22、25、及び26と、データ線31とを備える。同図における画素部500は、実施の形態1に係る表示装置の備える画素部100と比較して、閾値補償トランジスタ510及びその動作を制御する第2制御線である制御線25が付加されていること、有機EL素子110のアノード端子にELスイッチングトランジスタ520及びその動作を制御する制御線26が付加されていること、スイッチングトランジスタ230と駆動トランジスタ220のゲート端子との間に閾値補償容量530が付加されていること、及び各種トランジスタは全てpチャネルのトランジスタであることが異なる。図2に記載された画素部100と同じ点は説明を省略し、以下、異なる点について説明する。

20

## 【0097】

30

閾値補償トランジスタ510は、ソース及びドレインの一方が駆動トランジスタ220の第1端子であるソース及びドレインの一方に接続され、ソース及びドレインの他方が駆動トランジスタ220のゲートに接続されている。

## 【0098】

画素部100が、駆動トランジスタ120、スイッチングトランジスタ130、及び保持容量150という、2つのトランジスタ及び1つの容量という基本回路で有機EL素子110への電流供給を制御しているのに対し、画素部500は、上記基本回路に、閾値補償トランジスタ510及び電圧変換部として機能する閾値補償容量530が付加されることにより、駆動トランジスタの閾値電圧 $V_{th}$ の変動を補償する機能を有する。これにより、駆動トランジスタ220は、閾値電圧 $V_{th}$ の変動による出力信号電流の変動を生じない。

40

## 【0099】

ELスイッチングトランジスタ520は、図13に記載された画素部300におけるELスイッチングトランジスタ310と同様の機能を有し、検査電流41の有機EL素子110への供給の有無を制御する。

## 【0100】

図16は、本発明の実施の形態2に係る表示装置の有する制御回路の、駆動トランジスタ又は有機EL素子の特性を検出する場合の動作フローチャートである。ここで、画素部500の周辺回路の構成及び接続は図2に記載された周辺回路と同様である。

## 【0101】

50

最初に、データ線駆動回路 30 とデータ線 31 との接続を非導通状態とし、検査電流発生回路 40 とデータ線 31 との接続を導通状態に設定する (S30)。この接続は、例えば、データ線駆動回路 30 とデータ線 31 との間のスイッチをオフすること、及び検査電流発生回路 40 とデータ線 31 との間のスイッチをオンすることにより実現される。

【0102】

次に、駆動トランジスタ 220 特性を検出する場合と有機 EL 素子 110 特性を検出する場合とを選択する (S31)。

【0103】

次に、ステップ S31 で駆動トランジスタ 220 特性検出を選択した場合の動作について説明する。

10

【0104】

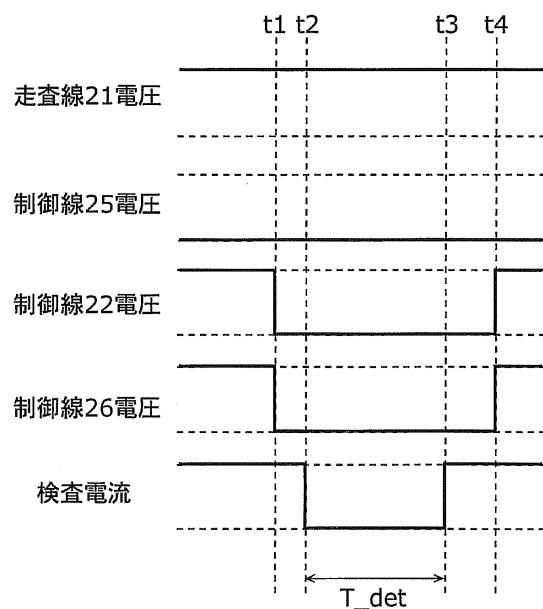

図 17 は、駆動トランジスタ特性検出時の検査電流の供給タイミングを示すタイミングチャートである。同図において、横軸は時間を表している。また縦方向には、上から順に、走査線 21 の電圧、制御線 25 の電圧、制御線 22 の電圧、制御線 26 の電圧、及び検査電流を表している。

【0105】

図 17 の時刻  $t_1$  において、制御線 25 及び制御線 22 の電圧のレベルを LOW にして、それぞれ、閾値補償トランジスタ 510 及び検査トランジスタ 240 をオンにする (S32)。

【0106】

次に、ステップ S31 で有機 EL 素子 110 特性検出を選択した場合の動作について説明する。

20

【0107】

図 18 は、有機 EL 素子特性検出時の検査電流の供給タイミングを示すタイミングチャートである。同図において、横軸は時間を表している。また縦方向には、上から順に、走査線 21 の電圧、制御線 25 の電圧、制御線 22 の電圧、制御線 26 の電圧、及び検査電流を表している。

【0108】

図 18 の時刻  $t_1$  において、制御線 22 及び制御線 26 の電圧のレベルを LOW にして、それぞれ、検査トランジスタ 240 及び EL スイッチングトランジスタ 520 をオンにする (S33)。

30

【0109】

以降のステップについては、駆動トランジスタ特性検出時及び有機 EL 素子特性検出時における動作を共通ステップとして説明する。

【0110】

図 17 又は図 18 の時刻  $t_2$  において、駆動トランジスタ特性検出時には検査電流発生回路 40 から図 15 中の矢印の向きに検査電流 45 を流す。あるいは、有機 EL 素子特性検出時には検査電流発生回路 40 から図 15 中の矢印の向きに検査電流 46 を流す (S34)。

【0111】

駆動トランジスタ特性検出時の検査電流 45 は、データ線 31、検査トランジスタ 240、駆動トランジスタ 220 を経由して、電源線 125 に流れこむ。その際、閾値補償トランジスタ 510 及び検査トランジスタ 240 により、駆動トランジスタ 220 のゲート端子がデータ線 31 に接続されることになり、データ線 31 の電圧は、駆動トランジスタ 220 に検査電流 45 が流れた際の駆動トランジスタ 220 のゲート電圧とほぼ等しくなる。

40

【0112】

ここで、駆動トランジスタ 220 のゲート端子とドレイン端子は、閾値補償トランジスタ 510 を介して接続されているため、駆動トランジスタ 220 は飽和領域で動作している。また、駆動トランジスタ 220 のソース電圧は電源線 125 に印加された電圧である

50

。ここで、検出された電圧を  $V_{det}$ 、駆動トランジスタ 220 のソース端子に印加された電源電圧を  $V_{dd}$ 、及び検査電流を  $I_{test}$  とすると、前述した式 1 が成り立つ。

【0113】

ここで、実施の形態 1 と同様に、大きさの異なる 2 種類の検査電流  $I_1$  及び  $I_2$  を流して、連立方程式を解くことにより、式 4 より  $I_1$  と  $V_{th}$  が求まる。あるいは、本実施の形態 2 における画素部 500 は、通常動作時に駆動トランジスタ 220 の閾値電圧  $V_{th}$  の変動が補償されるので、画素間の特性ばらつきを補正する場合には、初期値  $V_{th}$  を定数として扱うことができる。よって、 $V_{th}$  の初期値を求めた後は、以下のように、1 種類の検査電流  $I_{test}$  により、変数  $I_1$  のみを求めてよい。

【0114】

式 2 において、 $V_{gs} = V_{det} - V_{dd}$  とおき、この方程式を解くと、 $I_1$  は以下のようになる。

【0115】

【数 5】

$$\beta = \frac{2 \times I_{test}}{(V_{gs} - V_{th})^2} \quad (式 5)$$

【0116】

よって、検査電流 45 供給時のデータ線 31 の電圧が測定されることにより、駆動トランジスタ 220 の移動度などに関する特性パラメータ  $\beta$  を算出することができる。

【0117】

一方、有機 EL 素子特性検出時の検査電流 46 は、駆動トランジスタ 220 のゲート電位と同程度かそれ以下の電圧が電源線 125 に印加されているため、駆動トランジスタ 220 には流れない。検査電流 46 は、データ線 31、検査トランジスタ 240、ELスイッチングトランジスタ 520、有機 EL 素子 110 を経由して、共通電極 115 に流れ込む。その際、検査トランジスタ 240 及び ELスイッチングトランジスタ 520 により、有機 EL 素子 110 のアノードがデータ線 31 に接続されているため、データ線 31 の電圧は、有機 EL 素子 110 に検査電流 46 が流れた際の有機 EL 素子 110 のアノード電圧とほぼ等しくなる。

【0118】

次に、図 17 又は図 18 の  $t_2$  から  $t_3$  の間において、検査電流 45 又は 46 を供給し、データ線 31 に現れた電圧を電圧検出回路 50 で検出する (S35)。これにより、検査電流の大きさに対する、駆動トランジスタ 220 のゲート電圧、又は有機 EL 素子 110 のアノード電圧を知ることができる。

【0119】

ここで、検査電流 46 を  $I_{EL}$ 、発生した有機 EL 素子 110 のアノード電圧を  $V_{EL}$  とすると、予め取得されている有機 EL 素子 110 の初期の電流 - 電圧特性と、今回取得された ( $I_{EL}$ 、 $V_{EL}$ ) とのズレ量を算出することができる。

【0120】

次に、上述したように、電圧検出回路 50 により検出された電圧値  $V_{det}$  ( または  $V_{det_1}$  及び  $V_{det_2}$  )、又は  $V_{EL}$  をデジタル値に変換し、それらと式 2 ないし式 5、又は初期電流 - 電圧特性を用いて算出した特性パラメータをメモリ 80 に格納する (S36)。

【0121】

次に、図 17 又は図 18 の  $t_3$  において、検査電流の供給を停止する (S37)。

【0122】

なお、ステップ S37 は、ステップ S36 の後である必要はなく、ステップ S36 と並行して実行されてもよく、または、ステップ S35 の後であってステップ S36 の前に実行されてもよい。

【0123】

10

20

30

40

50

上述した一連の動作ステップにより、駆動トランジスタの閾値電圧を補償するトランジスタや容量が付加された画素部においても、データ線の電圧が測定され、その検出結果が評価されることにより、画素部の画素欠陥が発見されるだけでなく、駆動トランジスタや有機EL素子のばらつきや経時変動に関する情報が独立に取得できる。取得された特性パラメータがメモリに保存され、後述する通常動作時のデータ電圧の補正に用いられることで、駆動トランジスタや有機EL素子の特性ばらつきや経時変動による輝度ムラが改善される。

【0124】

次に、本発明の実施の形態2にかかる表示装置の通常動作時における駆動方法について説明する。本実施の形態における通常動作時の制御回路の動作フローチャートは、図5に記載された通常動作時における制御回路の動作フローチャートと同様である。よって、図5を用いてその動作を説明する。

【0125】

最初に、データ線駆動回路30とデータ線31との接続を導通状態とし、検査電流発生回路40とデータ線31との接続を非導通状態に設定する(S20)。

【0126】

次に、検査トランジスタ240を、オフ状態にする(S21)。なお、本ステップS21は、ステップS20の前に実行されていてもよい。また、通常動作時では、検査トランジスタ240は常にオフ状態であるが、検査トランジスタ240及びELスイッチングトランジスタ520をオン状態とすることで、データ線駆動回路30の出力電圧を直接有機EL素子110に印加することができるため、駆動時の黒挿入に使ってもよい。

【0127】

最後に、メモリ80から読み出された特性パラメータにより補正された信号電圧をデータ線駆動回路30から出力し、画素部500へ書き込むことにより画像表示を実行する(S22)。

【0128】

以上のように、本発明の実施の形態2に係る駆動トランジスタの閾値電圧を補償するトランジスタや容量が付加された画素部を有する表示装置においても、駆動トランジスタ及び有機EL素子の特性検出動作、及び通常動作により、特性検出時に得られた特性パラメータに基づき信号電圧が補正されるので、駆動トランジスタや有機EL素子の特性ばらつきや経時変動による輝度ムラが改善される。

【0129】

なお、閾値補償容量530は、データ線からの信号電圧を、その信号電圧に対応する電圧に変換して駆動トランジスタ220のゲートに出力する電圧変換回路であってもよい。

【0130】

また、閾値補償容量530が電圧変換回路である場合、閾値補償トランジスタ510のソース及びドレインの一方は、駆動トランジスタ220の第1端子であるソース及びドレインの一方に接続されておらず、データ線31に接続されていてもよい。

【0131】

また、閾値補償容量530が電圧変換回路である場合、閾値補償トランジスタ510のソース及びドレインの一方は、駆動トランジスタ220の第1端子であるソース及びドレインの一方に接続されておらず、スイッチングトランジスタ230と電圧変換回路との接続点に接続されていてもよい。

【0132】

また、閾値補償容量530が電圧変換回路である場合、検査トランジスタ240のソース及びドレインの一方は、データ線31に接続されておらず、スイッチングトランジスタ230と電圧変換回路との接続点に接続されていてもよい。

【0133】

また、閾値補償容量530が電圧変換回路である場合、検査トランジスタ240のソース及びドレインの一方は、データ線31に接続されておらず、スイッチングトランジスタ

10

20

30

40

50

230と電圧変換回路との接続点に接続され、かつ、閾値補償トランジスタ510のソース及びドレインの一方は、駆動トランジスタ220の第1端子であるソース及びドレインの一方接続されておらず、データ線31に接続されていてもよい。

【0134】

また、閾値補償容量530が電圧変換回路である場合、検査トランジスタ240のソース及びドレインの一方は、データ線31に接続されておらず、スイッチングトランジスタ230と電圧変換回路との接続点に接続され、かつ、閾値補償トランジスタ510のソース及びドレインの一方は、駆動トランジスタ220の第1端子であるソース及びドレインの一方接続されておらず、スイッチングトランジスタ230と電圧変換回路との接続点に接続されていてもよい。

10

【0135】

また、閾値補償容量530が電圧変換回路である場合、検査トランジスタ240のソース及びドレインの他方は、駆動トランジスタ220の第1端子であるソース及びドレインの一方接続されておらず、駆動トランジスタ220のゲートに接続されていてもよい。

【0136】

なお、実施の形態1及び2において、各画素部における駆動トランジスタ及び有機EL素子のいずれかの特性を検出する動作について説明したが、実施の形態1及び2で示された回路構成及び動作により、各画素部の有する駆動トランジスタ及び有機EL素子の両方の特性を検出してもよい。具体的には、駆動トランジスタ及び有機EL素子の両方の特性検出は、実施の形態1においては第1検査電流が流れた際の駆動トランジスタ120のゲート電圧と第2電流が流れた際の有機EL素子の110のアノード電圧を検出することで実現される。以下、各画素部における駆動トランジスタ及び有機EL素子の両方の特性を検出する効果について説明する。

20

【0137】

駆動トランジスタのソース端子に有機EL素子が接続されている画素回路構成の場合、発光輝度は、駆動トランジスタの劣化だけでなく、有機EL素子の劣化による影響をも受けやすい。以下、この理由を説明する。

【0138】

駆動トランジスタにおける、ソース端子に対するゲート電圧によって、有機EL素子に流れる電流が決まる。そのソース端子に、定電圧の電源線ではなく有機EL素子が接続されると、有機EL素子の特性によりソース電圧が変動する。有機EL素子は、経時劣化により、同じ電流を流したときの電圧が増加していく。つまり、高抵抗化していく傾向がある。そのため、例えば、実施の形態1に記載された画素部100では、有機EL素子の高抵抗化により、駆動トランジスタ120のソース電圧が上昇する。よって、同じデータ電圧を、駆動トランジスタ120のゲート端子に印加しても、流れる電流が減少してしまう。

30

【0139】

よって、駆動トランジスタの劣化のみを検出し、所望の電流を流すためのゲート電圧を求めたとしても、有機EL素子の劣化によりソース電圧がどのように変化しているかわからぬため、所望の電流を流すための適切な補正データ電圧を導出することができない。

40

【0140】

ここで、有機EL素子の特性も同時に検出しておくと、有機EL素子の特性を反映したソース電圧が分かるため、適切な補正データ電圧を導出することができる。

【0141】

よって、有機EL素子及び駆動トランジスタの双方が経時劣化する場合、当該双方の特性を検出することにより、所望の輝度を得るためのデータ電圧をより適切に制御できる。

【0142】

また、ここでは、劣化についてのみ述べたが、出荷前などの初期段階においても、同様の理由により、有機EL素子と駆動トランジスタの双方の特性を検出することは有効である。これにより、駆動トランジスタの特性検出のみでは導出できない、適切なデータ電圧

50

を製品出荷前に把握することができる。

【0143】

本発明によれば、画素部100のように、基本画素回路に一つの検査トランジスタ140を追加するのみで、駆動トランジスタ及び有機EL素子の双方の特性検出ができ、上述した高精度な補正データ電圧を導出することが可能となる。

【0144】

(実施の形態3)

本実施の形態における電子装置は、発光素子の形成される前の複数の画素部を有するアクティブマトリクス型のパネル基板を備え、画素部は、選択されたデータ線から供給された信号電圧に対応した信号電流を出力する第1トランジスタと、第1トランジスタへの信号電圧の供給をオンオフする第1スイッチ素子と、選択されたデータ線と第1トランジスタの第2端子とが短絡状態であることを可能とするように接続された第2スイッチ素子とを備える。また、電子装置は、さらに、第1トランジスタに検査電流を流す検査電流発生回路と、当該検査電流により発生した電圧を選択されたデータ線にて測定する電圧検出回路とを備える。これにより、各画素に配置された駆動トランジスタの特性を高精度測定できることで、発光素子が形成された後の発光パネルにおける駆動トランジスタ特性の不均一に起因する輝度ムラを補正できる。

【0145】

図19は、本発明の実施の形態3に係る電子装置の電気的な構成を示すブロック図である。同図における電子装置2は、走査線駆動回路20と、検査電流発生回路40と、電圧検出回路50と、マルチブレクサ60と、制御回路70と、メモリ80と、画素アレイ部90とを備える。

【0146】

図19に記載された電子装置は、図1に記載された発光パネルを有する表示装置の形成課程における途中段階のものである。同図に記載された実施の形態3に係る電子装置は、図1に記載された実施の形態1に係る表示装置と比較して、表示部の代わりに画素アレイ部90が配置され、データ線駆動回路30が配置されていない点が、構成として異なる。

【0147】

画素アレイ部は、複数の画素部を備える。

【0148】

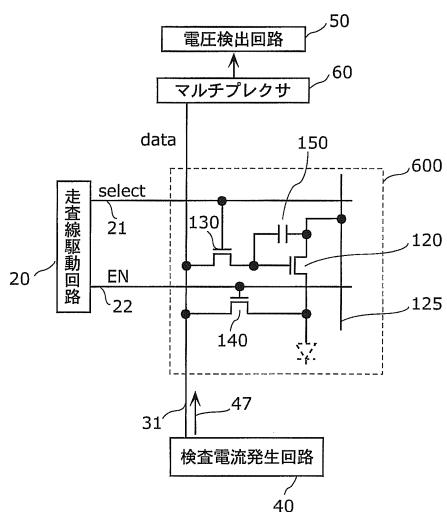

図20は、画素アレイ部の有する一画素部の回路構成及びその周辺回路との接続を示す図である。同図における画素部600は、駆動トランジスタ120と、スイッチングトランジスタ130と、検査トランジスタ140と、保持容量150と、電源線125と、走査線21と、制御線22と、データ線31とを備える。また、周辺回路は、走査線駆動回路20と、検査電流発生回路40と、電圧検出回路50と、マルチブレクサ60とを備える。

【0149】

図20に記載された画素部600は、図2に記載された画素部100と比較して、有機EL素子110が配置されていない点のみが回路構成として異なる。画素部600は、有機EL素子110が形成される前の課程のものであり、画素部600に有機EL素子110が形成されることにより、画素部100が生成される。図19及び図20に記載された構成要素について、図1及び図2に記載された構成要素と同じものは説明を省略し、以下、異なる点のみを説明する。

【0150】

検査電流発生回路40は、データ線31に接続されており、駆動トランジスタ120の特性を検出するための検査電流47を出力する。

【0151】

電圧検出回路50は、マルチブレクサ60を介してデータ線31に接続されており、検査電流発生回路40が検査電流47を出力している間に、データ線31の電圧を検出する。

10

20

30

40

50

## 【0152】

制御回路70は、走査線駆動回路20、検査電流発生回路40、マルチプレクサ60、電圧検出回路50、メモリ80の制御を行い、電圧検出回路50により検出された電圧値は、デジタル値に変換され、演算により得られた特性パラメータをメモリ80に書き込む。

## 【0153】

次に、画素部600の回路構成について説明する。

## 【0154】

駆動トランジスタ120のゲートは、スイッチングトランジスタ130を介してデータ線31に接続され、第1端子であるソース及びドレインの一方が、後に形成される有機EL素子のアノードに後に接続され、第2端子であるソース及びドレインの他方が、電源線125に接続されている。

10

## 【0155】

検査トランジスタ140のゲートは制御線22に接続され、ソースは後に形成される有機EL素子のアノードに後に接続され、ドレインはデータ線31に接続されている。

## 【0156】

次に、本発明の実施の形態3にかかる電子装置の駆動方法について説明をする。本駆動方法により、発光素子が形成される前の駆動トランジスタ120の特性の検出が可能である。

## 【0157】

20

本駆動方法においても、図3に記載された動作フローチャート、及び図4に記載された検査電流の供給タイミングを示すタイミングチャートにより説明できる。

## 【0158】

最初に、検査電流発生回路40とデータ線31との接続を導通状態に設定する(S10)。

## 【0159】

次に、図4のt1において、走査線21及び制御線22の電圧のレベルをHIGHにして、それぞれ、スイッチングトランジスタ130及び検査トランジスタ140をONにする(S11)。

## 【0160】

30

次に、図4のt2において、検査電流発生回路40から図20中の矢印の向きに検査電流47を流す(S12)。

## 【0161】

ステップS12において、検査電流47は、データ線31、検査トランジスタ140、及び駆動トランジスタ120を経由して、電源線125に流れこむ。その際、データ線31の電圧は、駆動トランジスタ120に検査電流47が流れた際の駆動トランジスタ120のゲート電圧とほぼ等しくなる。

## 【0162】

次に、図4のt2からt3の間において、検査電流47を供給し、データ線31に現れた電圧を電圧検出回路50で検出する(S13)。これにより、検査電流47の大きさに対する駆動トランジスタ120のゲート電圧を知ることができる。

40

## 【0163】

次に、電圧検出回路50により検出された電圧値をデジタル値に変換して算出した特性パラメータをメモリ80に格納する(S14)。このときの特性パラメータの算出方法については、実施の形態1と同様に、式2～式4を用いることにより算出される。

## 【0164】

最後に、図4のt3において、検査電流47の供給を停止する(S15)。

## 【0165】

なお、ステップS15は、ステップS14の後である必要はなく、ステップS14と並行して実行されてもよく、または、ステップS13の後であってステップS14の前に実

50

行されてもよい。

【0166】

上述した一連の動作ステップにより、データ線の電圧が測定され、その検出結果が評価されることにより、画素部の画素欠陥が発見されるだけでなく、駆動トランジスタのばらつきに関する情報が取得できる。取得された特性パラメータがメモリに保存され、発光素子形成後の発光パネルの通常動作時のデータ電圧の補正に用いられることで、駆動トランジスタの特性ばらつきによる輝度ムラが改善される。

【0167】

なお、図20において、電圧検出回路50と検査電流発生回路40とは、データ線31の両側に、画素部を挟んで接続されているが、電圧検出回路50と検査電流発生回路40とが、画素部に対してデータ線31の同じ側に接続されてもよい。

10

【0168】

また、検査電流発生回路40は、データ線31の本数と同数の電流発生源を有するものであってもよい。

【0169】

また、検査電流発生回路40は、データ線31の切り替えを行うマルチプレクサとデータ線31の本数より少ない電流発生源を有するものであってもよい。

【0170】

また、データ線31の切り替えを行うマルチプレクサとデータ線31より少ない電流発生源をもつ場合、当該マルチプレクサは、パネル用基板上に形成されていてもよい。

20

【0171】

また、電圧検出回路50は、データ線31の本数と同数の電圧検出器を有するものであってもよい。

【0172】

また、電圧検出回路50は、データ線31の切り替えを行うマルチプレクサとデータ線31の本数より少ない電圧検出器をもつものであってもよい。

【0173】

また、データ線31の切り替えを行うマルチプレクサとデータ線31より少ない電圧検出器をもつ場合、当該マルチプレクサは、パネル用基板上に形成されていてもよい。

【0174】

以上のように、本発明に係る表示装置は、駆動トランジスタとスイッチングトランジスタ及び発光素子からなる従来の画素部およびその画素部にデータ電圧を与えるデータ線に対して、データ線から入力される第1検査電流を駆動トランジスタのソース-ドレイン間に流し、又は、前記データ線から入力される第2検査電流を発光素子に流すように回路バスを形成する第1回路バス形成手段と、第1検査電流により発生した駆動トランジスタのゲート電圧に対応した電圧、又は、第2検査電流により発生した発光素子のアノード及びカソードの一方の電圧をデータ線に発生させるよう回路バスを形成する第2回路バス形成手段と、第1検査電流により発生した駆動トランジスタのゲート電圧に対応した電圧、又は、第2検査電流により発生した発光素子のアノード及びカソードの一方の電圧を、第2回路バス形成手段によりデータ線にて検出する電圧検出手段とを備えることにより、駆動トランジスタや発光素子のばらつきに関する特性情報を独立に取得することができる。また、検査電流が駆動トランジスタや発光素子に流れ、その時のデータ線の電圧が測定されるので、電圧を入力して微小電流を検出するという従来の測定方法型に比べ、高精度な測定が実現される。さらに、取得した特性情報を通常動作時のデータ電圧の補正に用いることで、駆動トランジスタや発光素子の特性ばらつきによる輝度ムラを改善することができる。

30

【0175】

また本発明に係る電子装置は、駆動トランジスタとスイッチングトランジスタからなり、発光素子が形成される前の画素部およびその画素部にデータ電圧を与えるデータ線に対して、データ線から入力される検査電流を駆動トランジスタのソース-ドレイン間に流す

40

50

ように回路パスを形成する第1回路パス形成手段と、第1検査電流により発生した駆動トランジスタのゲート電圧に対応した電圧をデータ線に発生させるよう回路パスを形成する第2回路パス形成手段と、検査電流により発生した駆動トランジスタのゲート電圧に対応した電圧を、第2回路パス形成手段によりデータ線にて検出する電圧検出手段とを備えることにより、駆動トランジスタのばらつきに関する特性情報を取得することができる。また、検査電流が駆動トランジスタに流れ、その時のデータ線の電圧が測定されるので、電圧を入力して微小電流を検出するという従来の測定方法型に比べ、高精度な測定が実現される。さらに、取得した特性情報を通常動作時のデータ電圧の補正に用いることで、駆動トランジスタの特性ばらつきによる輝度ムラを改善することができる。

【0176】

10

なお、本発明に係る電子装置は、上記実施の形態に限定されるものではない。実施の形態1ないし3及びその変形例における任意の構成要素を組み合わせて実現される別の実施形態や、実施の形態1ないし3及びその変形例に対して本発明の主旨を逸脱しない範囲で当業者が思いつく各種変形を施して得られる変形例や、本発明に係る電子装置を内蔵した各種機器も本発明に含まれる。

【0177】

20

例えば、図13に記載された本発明の実施の形態1の第2の変形例を示す画素部300に、図14に記載された本発明の実施の形態1の第3の変形例を示す画素部400の備えるスイッチングトランジスタ410を挿入することにより、実施の形態1の第2の変形例における画素部300の検査電流410パスを、ELスイッチングトランジスタ310及びスイッチングトランジスタ410のオンオフにより制御することができる。

【0178】

また、例えば、実施の形態1とその変形例及び実施の形態2に記載された各画素部の回路構成から有機EL素子110を削除した回路構成、つまり有機EL素子110が形成される前段階の各画素部を有するパネル用基板を備えた電子装置は、図19に記載された本発明の実施の形態3に示された電子装置と同様に適用されることにより、同様の効果を奏する。

【0179】

30

また、本発明に係る実施の形態では、駆動トランジスタ、スイッチングトランジスタ、検査トランジスタ、及びELスイッチングトランジスタの各機能を有するトランジスタは、ゲート、ソース及びドレインを有するFET(Field Effect Transistor)であることを前提として説明してきたが、これらのトランジスタには、ベース、コレクタ及びエミッタを有するバイポーラトランジスタが適用されてもよい。この場合にも、本発明の目的が達成され同様の効果を奏する。

【0180】

また、例えば、本発明に係る表示装置は、図21に記載されたような薄型フラットTVに内蔵される。本発明に係る表示装置により、輝度ムラが抑制されたディスプレイを備えた薄型フラットTVが実現される。

【産業上の利用可能性】

【0181】

40

本発明は、特に表示装置を内蔵する有機ELフラットパネルディスプレイに有用であり、画質の均一性が要求されるディスプレイの表示装置およびその駆動方法として用いるのに最適である。

【符号の説明】

【0182】

- 1 表示装置

- 2 電子装置

- 5 発光パネル

- 10 表示部

- 20 走査線駆動回路

50

|                                          |                  |    |

|------------------------------------------|------------------|----|

| 2 1                                      | 走査線              |    |

| 2 2、 2 3、 2 4、 2 5、 2 6                  | 制御線              |    |

| 3 0                                      | データ線駆動回路         |    |

| 3 1                                      | データ線             |    |

| 4 0                                      | 検査電流発生回路         |    |

| 4 1、 4 4、 4 5、 4 6、 4 7                  | 検査電流             |    |

| 4 2                                      | 電流発生源            |    |

| 4 3、 5 2、 6 0                            | マルチブレクサ          |    |

| 5 0                                      | 電圧検出回路           |    |

| 5 1                                      | 電圧検出器            | 10 |

| 7 0                                      | 制御回路             |    |

| 8 0                                      | メモリ              |    |

| 9 0                                      | 画素アレイ部           |    |

| 1 0 0、 2 0 0、 3 0 0、 4 0 0、 5 0 0、 6 0 0 | 画素部              |    |

| 1 1 0、 2 1 0                             | 有機 E L 素子        |    |

| 1 1 5                                    | 共通電極             |    |

| 1 2 0、 2 2 0                             | 駆動トランジスタ         |    |

| 1 2 5                                    | 電源線              |    |

| 1 3 0、 2 3 0、 4 1 0                      | スイッチングトランジスタ     |    |

| 1 4 0、 2 4 0                             | 検査トランジスタ         | 20 |

| 1 5 0                                    | 保持容量             |    |

| 3 1 0、 5 2 0                             | E L スイッチングトランジスタ |    |

| 5 1 0                                    | 閾値補償トランジスタ       |    |

| 5 3 0                                    | 閾値補償容量           |    |

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(51)Int.Cl.

| F I     |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 4 2 A |

| G 0 9 G | 3/20  | 6 4 2 P |

| G 0 9 G | 3/20  | 6 7 0 Q |

| H 0 5 B | 33/14 | A       |

(56)参考文献 特開2007-206139 (JP, A)

特開2007-293328 (JP, A)

特開2004-191484 (JP, A)

特開2008-224863 (JP, A)

特開2008-216872 (JP, A)

特表2007-536585 (JP, A)

特開2006-184866 (JP, A)

特開2009-031712 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |           |

|---------|-----------|

| G 0 9 G | 3 / 3 0   |

| G 0 9 G | 3 / 2 0   |

| H 0 1 L | 5 1 / 5 0 |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置、电子装置及び駆動方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP5738910B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2015-06-24 |

| 申请号            | JP2013032522                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2013-02-21 |

| [标]申请(专利权)人(译) | 松下电器产业株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 松下电器产业株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 当前申请(专利权)人(译)  | 株式会社JOLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 小田原理惠<br>小野晋也                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 小田原 理惠<br>小野 晋也                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| CPC分类号         | G09G3/3233 G09G3/006 G09G3/3241 G09G2300/0814 G09G2300/0842 G09G2300/0852 G09G2300/0861 G09G2310/0262 G09G2320/02 G09G2320/0223 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.611.H G09G3/20.670.J G09G3/20.670.B G09G3/20.642.A<br>G09G3/20.642.P G09G3/20.670.Q H05B33/14.A G09G3/3225                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC21 3K107/CC33 3K107/CC45 3K107/EE03 3K107/HH04 3K107/<br>/HH05 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD22 5C080/FF11 5C080/HH09 5C080/JJ01<br>5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ07 5C080/KK43 5C380/AA01 5C380/AB06 5C380<br>/AB22 5C380/AB24 5C380/AC07 5C380/BA13 5C380/BA38 5C380/BB04 5C380/BD04 5C380/CC63<br>5C380/CC64 5C380/CC65 5C380/CD013 5C380/CD014 5C380/CD025 5C380/CF01 5C380/CF51<br>5C380/CF52 5C380/FA02 5C380/FA22 5C380/GA02 5C380/GA05 5C380/GA08 5C380/GA09 |         |            |

| 代理人(译)         | 吉川修<br>Sobashima正雄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 审查员(译)         | Naoaki桥本                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 优先权            | 2008000779 2008-01-07 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 其他公开文献         | JP2013148908A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

**摘要(译)**

本发明提供一种显示装置，其能够在使用简单的像素电路的同时通过电压测量精确地检测每个像素的晶体管的特性和有机EL的元件。根据本发明的显示装置1的像素单元100包括驱动晶体管120，开关晶体管130和有机EL元件110。显示装置1使用来自数据线31的检查电流41作为有机物。第一电路通路形成装置，用于形成流向EL元件110的电路通路，以及第二电路通路，用于形成电路通路，以产生由数据线31上的检查电流41产生的有机EL元件110的阳极电压。像素单元100还包括有机EL元件110和电压检测电路50，用于经由由第二电路路径形成装置形成的路径通过数据线31检测阳极的电压。以及开关晶体管140，其在数据线31的导通和非导通之间切换。[选择图]图2

0 0 5 6】

数 4】

$$\beta = \left( \frac{\sqrt{2I_1} - \sqrt{2I_2}}{V_{gs1} - V_{gs2}} \right)^2$$

$$V_{th} = \frac{V_{gs2} \times \sqrt{2I_1} - V_{gs1} \times \sqrt{2I_2}}{\sqrt{2I_1} - \sqrt{2I_2}}$$