### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2016-95381 (P2016-95381A)

(43) 公開日 平成28年5月26日 (2016.5.26)

| (51) Int.Cl. | F 1                          |          |                    | テーマコート    | ・ (参考) |

|--------------|------------------------------|----------|--------------------|-----------|--------|

| GO9G 3/30    | <b>(2006.01)</b> GO9G        | 3/30     | J                  | 3 K 1 O 7 |        |

| GO9G 3/20    | <b>(2006.01)</b> GO9G        | 3/20     | 642A               | 5CO8O     |        |

| HO1L 51/50   | <b>(2006.01)</b> GO9G        | 3/20     | 624B               | 5C38O     |        |

|              | G09G                         | 3/20     | 611D               |           |        |

|              | но 5 в                       | 33/14    | A                  |           |        |

|              | 審査請求 未                       | 請求請求項    | の数 26 O L          | (全 48 頁)  | 最終頁に続く |

| (21) 出願番号    | 特願2014-231097 (P2014-231097) | (71) 出願人 | 514188173          |           |        |

| (22) 出願日     | 平成26年11月13日 (2014.11.13)     |          | 株式会社JOLED          |           |        |

|              |                              |          | 東京都千代田区神田錦町三丁目23番地 |           |        |

|              |                              | (74) 代理人 | 100189430          |           |        |

|              |                              |          | 弁理十 吉川             | 修一        |        |

(74)代理人 100190805

弁理士 傍島 正朗

(72) 発明者 戎野 浩平

大阪府門真市大字門真1006番地 パナ

ソニック株式会社内

(72) 発明者 小野 晋也

大阪府門真市大字門真1006番地 パナ

ソニック株式会社内

|Fターム(参考) 3K107 AA01 BB01 CC33 EE04 FF04

FF15 HH02 HH05

最終頁に続く

# (54) 【発明の名称】表示装置およびその駆動方法

# (57)【要約】

【課題】スイッチ素子の突抜け電圧による書き込電圧の 変動が抑制された表示装置を提供する。

【解決手段】表示装置1は、スイッチ205を非導通状態かつスイッチ203を導通状態とすることにより容量素子210にデータ電圧を書込む期間である書込み期間と、スイッチ205を導通状態かつスイッチ203を非導通状態とすることによりデータ電圧に応じた電流を有機EL素子201に流す期間である発光期間とを実行する制御回路60を備え、スイッチ205は、書込み期間において、ゲート電極からソース電極への突抜け電圧によりソース電極の電位を低下させる、および、スイッチ203は、書込み期間の終了時において、ゲート電極からソース電極への突抜け電圧によりソース電極への突抜け電圧によりソース電極の電位を低下させる、の少なくともいずれかである。

【選択図】図7B

### 【特許請求の範囲】

### 【請求項1】

複数の表示画素が行列状に配置された表示部を有する表示装置であって、

前記複数の表示画素に高電位側の駆動電圧を供給するための第1駆動電源線と、

画素列に対応して配置され、映像信号を反映したデータ電圧を前記複数の表示画素へ伝達する複数のデータ線とを備え、

前記複数の表示画素の各々は、

発光素子と、

前記データ電圧に対応した電圧を保持するための容量素子と、

前記電圧がゲート・ソース間に印加されることにより当該電圧に応じた電流を前記発光素子に流す駆動トランジスタと、

第1ゲート電極、第2電極および第3電極を有し、前記第2電極が前記第1駆動電源線に接続され、前記第3電極が前記駆動トランジスタのソースおよびドレインの一方に接続され、前記第1駆動電源線と前記駆動トランジスタの導通および非導通を切り換える第1スイッチトランジスタと、

第2ゲート電極、第4電極および第5電極を有し、前記第4電極が前記複数のデータ線のうち対応するデータ線に接続され、前記第5電極が前記容量素子に接続され、前記データ線と前記容量素子との導通および非導通を切り換える第2スイッチトランジスタとを備え、

前記表示装置は、さらに、

前記第1スイッチトランジスタを非導通状態かつ前記第2スイッチトランジスタを導通状態とすることにより前記容量素子に前記データ電圧を書込む書込みステップと、前記第1スイッチトランジスタを導通状態かつ前記第2スイッチトランジスタを非導通状態とすることにより当該電圧に応じた電流を前記発光素子に流す発光ステップとを実行する制御部とを備え、

前記第1スイッチトランジスタは、前記書込みステップにおいて前記第3電極から前記第1ゲート電極への電荷突抜けにより前記第3電極の電位を低下させる、および、前記第2スイッチトランジスタは、前記書込みステップの終了時において前記第5電極から前記第2ゲート電極への電荷突抜けにより前記第5電極の電位を低下させる、の少なくともいずれかが実行される

表示装置。

# 【請求項2】

前記表示装置は、

前記複数の表示画素に低電位側の駆動電圧を供給するための第2駆動電源線を備え、前記制御部は、

前記書込みステップにおいて、前記第2駆動電源線の電圧値から所定値だけ小さい電圧よりもさらに小さい第1制御電圧を前記第1ゲート電極に印加することにより、前記第1 スイッチトランジスタを非導通状態とする

請求項1に記載の表示装置。

### 【請求項3】

前記第1スイッチトランジスタは、前記電荷突抜けにより前記第3電極の電位が前記駆動トランジスタのソースおよびドレインの他方の電位となるまで前記電位を低下させる 請求項1または2に記載の表示装置。

# 【請求項4】

前記制御部は、

前記書込みステップの終了時において、前記データ電圧の電圧範囲の下限電圧値から所 定値だけ小さい電圧よりもさらに小さい第2制御電圧を前記第2ゲート電極に印加するこ とにより、前記第2スイッチトランジスタを非導通状態とする

請求項1~3のいずれか1項に記載の表示装置。

# 【請求項5】

20

10

30

40

前記第1スイッチトランジスタは、

前記第1ゲート電極と前記第2電極とで形成された第1寄生容量と、

前記第1ゲート電極と前記第3電極とで形成された第2寄生容量とを有し、

前記第2寄生容量が前記第1寄生容量よりも大きくなるよう形成されている

請求項1~4のいずれか1項に記載の表示装置。

### 【請求項6】

前 記 第 1 ス イ ッ チ ト ラ ン ジ ス タ は 、 ス タ ガ 型 ま た は 逆 ス タ ガ 型 構 造 を 有 す る 請求項5に記載の表示装置。

### 【請求項7】

さらに、

前記制御部と前記表示部との間に配置され、前記制御部の指示により行順次に前記第1 ゲート電極に制御信号を印加する第1駆動回路を備え、

前記表示部に配置された前記複数の表示画素において、前記第1駆動回路に近い表示画 素ほど前記第2寄生容量が小さい前記第1スイッチトランジスタを備える

請求項5または6に記載の表示装置。

### 【請求項8】

前記第2スイッチトランジスタは、

前記第2ゲート電極と前記第4電極とで形成された第3寄生容量と、

前記第2ゲート電極と前記第5電極とで形成された第4寄生容量とを有し、

前記第4寄生容量が前記第3寄生容量よりも大きくなるよう形成されている

請求項1~7のいずれか1項に記載の表示装置。

前記第2スイッチトランジスタは、スタガ型または逆スタガ型構造を有する 請求項8に記載の表示装置。

### 【請求項10】

さらに、

前記制御部と前記表示部との間に配置され、前記制御部の指示により行順次に前記第2 ゲート電極に制御信号を印加する第2駆動回路を備え、

前記表示部に配置された前記複数の表示画素において、前記第2駆動回路に近い表示画 素ほど前記第4寄生容量が小さい前記第2スイッチトランジスタを備える 請求項8または9に記載の表示装置。

# 【請求項11】

前記第1駆動電源線の電圧をVtft、前記容量素子および前記駆動トランジスタのゲ 一ト電極に印加される参照電圧を V r e f 、前記駆動トランジスタの閾値電圧を V t h d r v 、前記第1スイッチトランジスタの閾値電圧をVth e n b 、および前記駆動トラン ジスタのゲートと前記ソースおよびドレインの一方とで形成される寄生容量をCdrvと した場合、前記第1スイッチトランジスタを非導通状態とするゲート電位V。nbLおよ び前記第1ゲート電極と前記第3電極とで形成される寄生容量Cenbは、

$$V_{tft} - (V_{ref} - Vth_{drv}) = (V_{tft} + Vth_{enb} - V_{enb}L) \times \left(\frac{Cenb}{Cenb + Cdrv}\right)$$

なる関係を満たす

請求項1に記載の表示装置。

# 【請求項12】

前 記 駆 動 ト ラ ン ジ ス タ の ゲ ー ト - ソ ー ス 間 電 圧 V g s の 低 階 調 側 へ の 目 標 シ フ ト 量 を Vgs、階調特性に歪みが発生する前記データ電圧をVdata、前記第2スイッチトラ ンジスタの閾値電圧をVthggn、および前記容量素子の静電容量をCsとした場合、 前記第2スイッチトランジスタを非導通状態とするゲート電位VscnLおよび前記第2 10

20

30

40

ゲート電極と前記第5電極とで形成される寄生容量Cscnは、

# 【数2】

$$\Delta Vgs = \left(Vdata + Vth_{scn} - V_{scn}L\right) \times \left(\frac{Cscn}{Cs + Cscn}\right)$$

なる関係を満たす

請求項1に記載の表示装置。

### 【請求項13】

複数の表示画素が行列状に配置された表示部を有する表示装置であって、

前記複数の表示画素に駆動電圧を供給するための駆動電源線と、

画素列に対応して配置され、映像信号を反映したデータ電圧を前記複数の表示画素へ伝達する複数のデータ線とを備え、

前記複数の表示画素の各々は、

発光素子と、

前記データ電圧に対応した電圧を保持するための容量素子と、

前記電圧がゲート・ソース間に印加されることにより当該電圧に応じた電流を前記発光素子に流す駆動トランジスタと、

第 1 ゲート電極、第 2 電極および第 3 電極を有し、前記第 2 電極が前記駆動電源線に接続され、前記第 3 電極が前記駆動トランジスタのソースおよびドレインの一方に接続され、前記駆動電源線と前記駆動トランジスタの導通および非導通を切り換える第 1 スイッチトランジスタと、

第2ゲート電極、第4電極および第5電極を有し、前記第4電極が前記複数のデータ線のうち対応するデータ線に接続され、前記第5電極が前記容量素子に接続され、前記データ線と前記容量素子との導通および非導通を切り換える第2スイッチトランジスタとを備え、

前記表示装置は、さらに、

前記第1スイッチトランジスタを非導通状態かつ前記第2スイッチトランジスタを導通状態とすることにより前記容量素子に前記データ電圧を書込む書込みステップと、前記第1スイッチトランジスタを導通状態かつ前記第2スイッチトランジスタを非導通状態とすることにより当該電圧に応じた電流を前記発光素子に流す発光ステップとを実行する制御部とを備え、

前記駆動トランジスタは、

ゲート電極と前記ソースおよびドレインの一方とで形成された第 5 寄生容量と、前記ゲート電極とソースおよびドレインの他方とで形成された第 6 寄生容量とを有し、前記第 5 寄生容量が前記第 6 寄生容量よりも小さくなるよう形成されている表示装置。

# 【請求項14】

前記制御部は、さらに、

前記書込みステップの前に、前記駆動トランジスタのゲートに参照電圧を印加した状態で、かつ前記第1スイッチトランジスタを導通状態かつ前記第2スイッチトランジスタを非導通状態とすることにより前記容量素子に前記駆動トランジスタの閾値電圧を保持させる閾値電圧検出ステップを実行する

請求項1~13のいずれか1項に記載の表示装置。

# 【請求項15】

前記複数の表示画素の各々は、さらに、

前記参照電圧を伝達する参照電源線と前記容量素子との導通および非導通を切り換える第3スイッチトランジスタを備える

請求項14に記載の表示装置。

# 【請求項16】

10

20

30

40

前記複数の表示画素の各々は、さらに、

初期化電圧を伝達する初期化電源線と前記容量素子との導通および非導通を切り換える第4スイッチトランジスタを備え、

前記制御部は、

前記第1スイッチトランジスタおよび前記第2スイッチトランジスタを非導通状態かつ前記第3スイッチトランジスタおよび前記第4スイッチトランジスタを導通状態とすることにより、前記駆動トランジスタを導通状態とすることで初期化期間を開始する初期化ステップと、

前記第1スイッチトランジスタおよび前記第3スイッチトランジスタを導通状態かつ前記第2スイッチトランジスタを非導通状態とすることにより前記容量素子に前記駆動トランジスタの閾値電圧を保持させる前記閾値電圧検出ステップと、

前記閾値電圧検出ステップの後、前記第1スイッチトランジスタおよび前記第3スイッチトランジスタを非導通状態かつ前記第2スイッチトランジスタを導通状態とすることにより前記容量素子に前記データ電圧を書込む前記書込みステップと、

前記発光ステップと、

前記閾値電圧検出ステップの終了時点と前記書込みステップの終了時点との間に、前記駆動トランジスタの前記ソースおよびドレインの一方の電位とソースおよびドレインの他方の電位とが同電位となるまで、前記ソースおよびドレインの一方に蓄積されている電荷を前記ソースおよびドレインの他方へと引き抜く電荷引き抜きステップとを実行し、

前記初期化ステップの前に前記第1スイッチトランジスタ、前記第2スイッチトランジスタ、前記第3スイッチトランジスタおよび前記第4スイッチトランジスタのうち前記第4スイッチトランジスタのみを導通状態に切り換えることで第1期間を開始し、前記第3スイッチトランジスタを導通状態に切り換えることで前記第1期間に続く前記初期化期間を開始する

請求項15に記載の表示装置。

### 【請求項17】

前記初期化電源線は、前記駆動電源線および前記参照電源線と直交する方向に配置されている

請求項16に記載の表示装置。

# 【請求項18】

前記制御部は、さらに、

前記第1期間前に、前記第1スイッチトランジスタを非導通に切り換えることで、前記発光素子を発光させる期間を終了させて、前記第1スイッチトランジスタ、前記第2スイッチトランジスタ、前記第3スイッチトランジスタが非導通状態に切り換えられた第2期間を開始し、前記第4スイッチトランジスタを導通状態に切り換えることで前記第2期間に続く前記1期間を開始する

請求項16または17に記載の表示装置。

### 【請求項19】

複数の表示画素が行列状に配置された表示部を有する表示装置の駆動方法であって、 前記表示装置は、

前記複数の表示画素に高電位側の駆動電圧を供給するための第1駆動電源線と、

画素列に対応して配置され、映像信号を反映したデータ電圧を前記複数の表示画素へ伝達する複数のデータ線とを備え、

前記複数の表示画素の各々は、

発光素子と、

前記データ電圧に対応した電圧を保持するための容量素子と、

前記電圧がゲート - ソース間に印加されることにより当該電圧に応じた電流を前記発光素子に流す駆動トランジスタと、

第 1 ゲート電極、第 2 電極および第 3 電極を有し、前記第 2 電極が前記第 1 駆動電源線に接続され、前記第 3 電極が前記駆動トランジスタのソースおよびドレインの一方に接続

10

20

30

40

され、前記第1駆動電源線と前記駆動トランジスタの導通および非導通を切り換える第1 スイッチトランジスタと、

第2ゲート電極、第4電極および第5電極を有し、前記第4電極が前記複数のデータ線のうち対応するデータ線に接続され、前記第5電極が前記容量素子に接続され、前記データ線と前記容量素子との導通および非導通を切り換える第2スイッチトランジスタとを備え、

前記第1スイッチトランジスタを非導通状態かつ前記第2スイッチトランジスタを導通 状態とすることにより前記容量素子に前記データ電圧を書込む書込みステップと、

前記書込みステップの後、前記第1スイッチトランジスタを導通状態とすることにより当該電圧に応じた電流を前記発光素子に流す発光ステップと、

前記書込みステップにおいて前記第1スイッチトランジスタを非導通状態にし、前記第3電極から前記第1ゲート電極への電荷突抜けにより前記第3電極の電位を低下させる、および、前記書込みステップの終了時において前記第2スイッチトランジスタを非導通状態にし、前記第5電極から前記第2ゲート電極への電荷突抜けにより前記第5電極の電位を低下させる、の少なくともいずれかを実行する電荷突抜けステップとを含む表示装置の駆動方法。

### 【請求項20】

前記表示装置は、さらに、

前記複数の表示画素に低電位側の駆動電圧を供給するための第2駆動電源線を備え、 前記電荷突抜けステップでは、

前記第2駆動電源線の電圧値から所定値だけ小さい電圧よりもさらに小さい第1制御電圧を前記第1ゲート電極に印加することにより、前記第1スイッチトランジスタを非導通状態とする

請求項19に記載の表示装置の駆動方法。

### 【請求項21】

前記電荷突抜けステップでは、

前記データ電圧の電圧範囲の下限電圧値から所定値だけ小さい電圧よりもさらに小さい 第2制御電圧を前記第2ゲート電極に印加することにより、前記第2スイッチトランジス タを非導通状態とする

請求項19または20に記載の表示装置の駆動方法。

### 【請求項22】

前記表示装置は、さらに、

前記書込みステップの前に、前記駆動トランジスタのゲートに参照電圧を印加した状態で、かつ前記第1スイッチトランジスタを導通状態かつ前記第2スイッチトランジスタを 非導通状態とすることにより前記容量素子に前記駆動トランジスタの閾値電圧を保持させ る閾値電圧検出ステップとを含む、

請求項19~21のいずれか1項に記載の表示装置の駆動方法。

### 【請求項23】

前記複数の表示画素の各々は、さらに、

前記参照電圧を伝達する参照電源線と前記容量素子との導通および非導通を切り換える第3スイッチトランジスタを備え、

前記書込みステップでは、前記第1スイッチトランジスタおよび前記第3スイッチトランジスタを非導通状態かつ前記第2スイッチトランジスタを導通状態とすることにより前記容量素子に前記データ電圧を書込む

請求項22に記載の表示装置の駆動方法。

# 【請求項24】

前記複数の表示画素の各々は、さらに、

初期化電圧を伝達する初期化電源線と前記容量素子との導通および非導通を切り換える 第4スイッチトランジスタを備え、

前記表示装置の駆動方法は、さらに、

10

20

30

前記閾値電圧検出ステップの前に、前記第1スイッチトランジスタおよび前記第2スイッチトランジスタを非導通状態かつ前記第3スイッチトランジスタおよび前記第4スイッチトランジスタを導通状態とすることにより、前記駆動トランジスタを導通状態とすることで初期化期間を開始する初期化ステップを含み、

前記初期化ステップの前において、前記第1スイッチトランジスタ、前記第2スイッチトランジスタ、前記第3スイッチトランジスタおよび前記第4スイッチトランジスタのうち前記第4スイッチトランジスタのみを導通状態に切り換えることで第1期間を開始し、

前記初期化ステップにおいて、前記第3スイッチトランジスタを導通状態に切り換えることで前記第1期間に続く前記初期化期間を開始する

請求項23に記載の表示装置の駆動方法。

### 【請求項25】

前記初期化電源線は、前記駆動電源線および前記参照電源線と直交する方向に配置されている

請求項24に記載の表示装置の駆動方法。

## 【請求項26】

さらに、前記第1期間前に、

前記第1スイッチトランジスタを非導通状態に切り換えることで、前記発光素子を発光させる期間を終了させて、前記第1スイッチトランジスタ、前記第2スイッチトランジスタ、前記第3スイッチトランジスタおよび前記第4スイッチトランジスタが非導通状態に切り換えられた第2期間を開始し、前記第4スイッチトランジスタを導通状態に切り換えることで前記第2期間に続く前記1期間を開始する

請求項23または24に記載の表示装置の駆動方法。

【発明の詳細な説明】

# 【技術分野】

### [0001]

本発明は、表示装置およびその駆動方法に関する。

# 【背景技術】

### [0002]

電流駆動型の発光素子を用いた表示装置として、有機エレクトロルミネッセンス(EL)素子を用いた表示装置が知られている。この自発光する有機EL素子を用いた表示装置は、液晶を用いた表示装置に必要なバックライトが不要で装置の薄型化に最適である。また、視野角にも制限がないため、次世代の表示装置として実用化が期待されている。また、有機EL素子は、各発光素子の輝度がそこに流れる電流値により制御される点で、液晶セルがそこに印加される電圧により制御されるのとは異なる。

### [0003]

有機EL素子を用いた表示装置では、通常、画素を構成する有機EL素子がマトリクス状に配置される。複数の走査線と複数のデータ線との交点にスイッチング薄膜トランジスタ(TFT:Thin Film Transistor)を設け、このスイッチングTFTに駆動トランジスタのゲート電極を接続し、選択した走査線を通じてこのスイッチングTFTを導通状態(導通状態)にさせてデータ線からデータ信号電圧を駆動トランジスタに入力する。この駆動トランジスタによって有機EL素子を駆動するものをアクティブマトリクス型の有機EL表示装置と呼ぶ。

### [0004]

アクティブマトリクス型の有機 E L 表示装置では、高精度な画像表示を実現するため、映像信号を反映したデータ電圧を、画素回路に正確に書き込むことが必要となる。つまり、駆動トランジスタは、上記データ電圧に対応した駆動電流を発光素子に流すことで発光素子を所望の輝度で発光させるため、駆動トランジスタのゲート・ソース間に正確にデータ電圧を書き込むことが必要となる。

# [0005]

例えば、特許文献 1 では、駆動素子の移動度を補正することで、駆動素子のデバイス特

10

20

30

40

性のばらつきを抑える方法が開示されている。具体的には、駆動電源Vcc、駆動トランジスタTrd、および有機EL素子ELが接続された駆動電流経路に、有機EL素子の発光および非発光を制御するスイッチ素子Tr4が存在し、データ電圧の書込み時においてデータ電圧が、駆動トランジスタTrdのゲートに印加される。

【先行技術文献】

【特許文献】

[0006]

【特許文献1】特開2008-310352号公報

【発明の概要】

【発明が解決しようとする課題】

[0007]

しかしながら、特許文献1に開示された画素回路では、データ電圧の書込み時に、駆動トランジスタのドレイン側の寄生容量からソース側に放電される電荷量が、データ電圧の大きさおよびスイッチ素子の突抜け電圧により影響を受ける。このため、データ電圧書込み完了時の駆動トランジスタのドレイン電位が階調によって変動する。これにより、駆動トランジスタの発光時のゲート・ソース電圧が上記変動の影響を受け、データ電圧と駆動電流との関係を表すガンマカーブに歪みが生じる。また、上記歪みが発生する階調が面内分布を持つため、表示パネルに輝度ムラが生じる。

[0008]

本発明は上記課題に鑑みてなされたものであり、ガンマカーブの歪みが抑制された表示 装置およびその駆動方法を提供することを目的とする。

【課題を解決するための手段】

[0009]

上記目的を達成するために、本発明の一態様に係る表示装置は、複数の表示画素が行列 状に配置された表示部を有する表示装置であって、前記複数の表示画素に高電位側の駆動 電圧を供給するための第1駆動電源線と、画素列に対応して配置され、映像信号を反映し た デ ー タ 電 圧 を 前 記 複 数 の 表 示 画 素 へ 伝 達 す る 複 数 の デ ー タ 線 と を 備 え 、 前 記 複 数 の 表 示 画素の各々は、発光素子と、前記データ電圧に対応した電圧を保持するための容量素子と 、前記電圧がゲート・ソース間に印加されることにより当該電圧に応じた電流を前記発光 素子に流す駆動トランジスタと、第1ゲート電極、第2電極および第3電極を有し、前記 第 2 電 極 が 前 記 第 1 駆 動 電 源 線 に 接 続 さ れ 、 前 記 第 3 電 極 が 前 記 駆 動 ト ラ ン ジ ス タ の ソ ー ス お よ び ド レ イ ン の 一 方 に 接 続 さ れ 、 前 記 第 1 駆 動 電 源 線 と 前 記 駆 動 ト ラ ン ジ ス タ の 導 通 お よ び 非 導 通 を 切 り 換 え る 第 1 ス イ ッ チ ト ラ ン ジ ス タ と 、 第 2 ゲ ー ト 電 極 、 第 4 電 極 お よ び 第 5 電 極 を 有 し 、 前 記 第 4 電 極 が 前 記 複 数 の デ ー タ 線 の う ち 対 応 す る デ ー タ 線 に 接 続 さ れ、前記第5電極が前記容量素子に接続され、前記データ線と前記容量素子との導通およ び非導通を切り換える第2スイッチトランジスタとを備え、前記表示装置は、さらに、前 記 第 1 ス イ ッ チ ト ラ ン ジ ス タ を 非 導 通 状 態 か つ 前 記 第 2 ス イ ッ チ ト ラ ン ジ ス タ を 導 通 状 態 とすることにより前記容量素子に前記データ電圧を書込む書込みステップと、前記第1ス イッチトランジスタを導通状態かつ前記第2スイッチトランジスタを非導通状態とするこ とにより当該電圧に応じた電流を前記発光素子に流す発光ステップとを実行する制御部と を備え、前記第1スイッチトランジスタは、前記書込みステップにおいて前記第3電極か ら前記第1ゲート電極への電荷突抜けにより前記第3電極の電位を低下させる、および、 前 記 第 2 ス イ ッ チ ト ラ ン ジ ス タ は 、 前 記 書 込 み ス テ ッ プ の 終 了 時 に お い て 前 記 第 5 電 極 か ら前記第2ゲート電極への電荷突抜けにより前記第5電極の電位を低下させる、の少なく ともいずれかが実行されることを特徴とする。

【発明の効果】

[0010]

本発明に係る表示装置によれば、容量素子のへ書込み電圧を変動させる要因である駆動トランジスタのソースおよびドレインの一方、ならびに、駆動トランジスタのゲート、の少なくとも一方について、スイッチトランジスタのオフ時に電荷突抜けを発生させること

10

20

30

40

により電位を低下させる。これにより、駆動トランジスタのソースおよびドレインの一方からゲートへの突抜け電圧のデータ電圧依存性を低減する、および、駆動トランジスタのゲート電位を低電位側へとシフトさせる、の少なくともいずれかが実行される。よって、書込み電圧の変動が抑制され、表示パネルの輝度ムラを抑制できる。

【図面の簡単な説明】

- [0011]

- 【図1】表示装置の全体構成を示す機能ブロック図である。

- 【図2A】表示装置の画素回路構成の一例を示す図である。

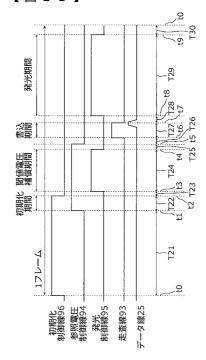

- 【図2B】表示装置の画素回路の動作タイミングチャートの一例である。

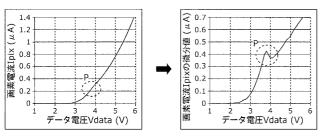

- 【図3】データ電圧と画素電流との関係を表すグラフである。

- 【図4A】データ電圧が1.0Vの場合の、Vth検出期間の終了時点~発光期間開始時点の画素回路の状態遷移図である。

- 【図4B】データ電圧が2.6Vの場合の、Vth検出期間の終了時点~発光期間開始時点の画素回路の状態遷移図である。

- 【図4C】データ電圧が3.4Vの場合の、Vth検出期間の終了時点~発光期間開始時点の画素回路の状態遷移図である。

- 【図4D】データ電圧が4.0Vの場合の、Vth検出期間の終了時点~発光期間開始時点の画素回路の状態遷移図である。

- 【図5】駆動トランジスタのドレイン電位の時間変化を表すグラフである。

- 【 図 6 】階調特性と駆動トランジスタのゲート ソース間電圧との関係を表すグラフである。

- 【図7A】実施の形態1に係る画素回路のスイッチ制御を説明する回路図である。

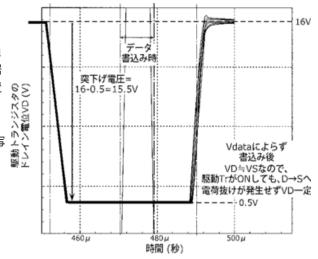

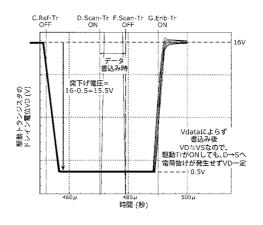

- 【図7B】実施の形態1に係るスイッチ制御による駆動トランジスタのドレイン電位の時間変化を表すグラフである。

- 【図7C】従来のスイッチ制御による駆動トランジスタのドレイン電位の時間変化を表すグラフである。

- 【図8】実施の形態の変形例1に係るスイッチの構成を表す概略平面図である。

- 【図9】実施の形態の変形例2に係るスイッチの構成を表す概略平面図である。

- 【図10A】実施の形態2に係る画素回路のスイッチ制御を説明する回路図である。

- 【図10B】遷移領域を非発光領域ヘシフトさせた階調特性を表すグラフである。

- 【図11】実施の形態3に係る駆動トランジスタの構成を表す概略平面図である。

- 【図12】実施の形態1~3のいずれかに係る表示装置を内蔵した薄型フラットTVの外観図である。

- 【図13】表示装置の電源線の配置の一例を示す図である。

- 【図14】表示装置の電源線の配置の一例を示す図である。

- 【発明を実施するための形態】

- [0012]

- (本発明の基礎となった知見)

本発明者は、「背景技術」の欄において記載した表示装置に関し、 0 - 3 . 階調特性の 歪みで後述するような問題が生じることを見出した。以下、図面を用いて本問題について 説明する。

[ 0 0 1 3 ]

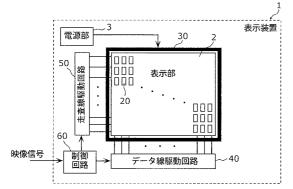

[0-1.表示装置の全体構成]

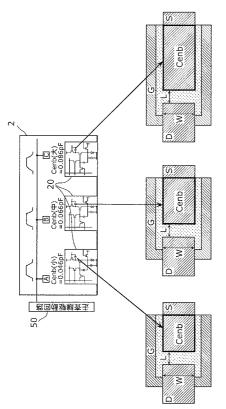

図1は、表示装置の全体構成を示す機能ブロック図である。表示装置1は、表示部2と、電源部3と、データ線駆動回路40と、走査線駆動回路50と、制御回路60とを備える。

[0014]

表示部 2 は、有機 E L 素子および当該有機 E L 素子を発光駆動するための回路素子を有する画素 2 0 が行列状に配置されている。

[0015]

10

20

30

電源部3は、表示部2の外周領域に配置された給電線30から各画素20に電源電圧を 給電する。なお、給電線30は、正電源電圧を伝達する正電圧給電線と、当該正電源電圧 よりも低電位である負電源電圧を伝達する負電圧給電線とを有している。なお、給電線3 0は、図1のように表示部2の外周部を包囲している必要はなく、例えば、表示部2の上 下辺または左右辺に分割して配置されていてもよい。なお、給電線30の電位は、正電圧 給電線の電位より相対的に低ければよく、必ずしも負の電位である必要はない。

[0016]

制御回路 6 0 は、外部から入力された映像信号に基づいて、データ線駆動回路 4 0 を制御するための制御信号 S 4 を生成し、生成した制御信号 S 4 をデータ線駆動回路 4 0 へ出力する。また、制御回路 6 0 は、入力される同期信号に基づいて走査線駆動回路 5 0 を制御するための制御信号 S 5 を生成し、当該生成した制御信号 S 5 を走査線駆動回路 5 0 へ出力する。

10

[0017]

データ線駆動回路40は、制御回路60で生成された制御信号S4に基づいて、表示部 2のデータ線を駆動する。より具体的には、データ線駆動回路40は、映像信号および水 平同期信号に基づいて、各画素回路に映像信号を反映したデータ電圧を出力する。

[0018]

走査線駆動回路50は、制御回路60で生成された制御信号S5に基づいて、表示部2の走査線を駆動する。より具体的には、走査線駆動回路50は、垂直同期信号および水平同期信号に基づいて、各画素回路に走査信号等を、少なくとも表示ライン単位で出力する

20

[0019]

[0・2.画素回路構成および駆動方法]

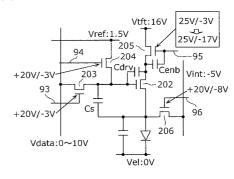

図2Aは、表示装置の画素回路構成の一例を示す図である。また、図2Bは、表示装置の画素回路の動作タイミングチャートの一例である。図2Aには、有機EL発光パネル上に行列状に配置された複数の画素のうちの一画素における回路が示されている。画素20は、有機EL素子201と、駆動トランジスタ202と、スイッチ203~206と、容量素子210とを備えた表示画素である。また、画素20には、参照電源線24と、ELアノード電源線21(第1駆動電源線:Vtft)と、ELカソード電源線22(第2駆動電源線:Ve1)と、初期化電源線23(Vini)と、走査線93と、参照電圧制御線94と、初期化制御線96と、発光制御線95と、データ線25とが配線されている。

30

[0020]

図2Aに示されように、スイッチ205および203を有する画素回路構成では、図3に示されたような、階調特性の歪みが発生する。

[0021]

図3は、データ電圧と画素電流との関係を表すグラフである。同図の左側には、データ電圧Vdata 画素電流Ipix特性であるガンマカーブが示されており、右側には、データ電圧Vdata 画素電流Ipixの微分値特性が示されている。ガンマカーブの特性を、微分により詳細に分析した右側のグラフでは、階調特性の歪み(領域P)が観測される。この歪みが発生する階調は表示パネル内でばらつくため、輝度ムラとなって表示品位を下げる原因となる。この歪みが発生する主要因として、駆動トランジスタ202のゲート・ドレイン間寄生容量を介した発光時の突上げ電圧量が表示階調により異なること、が挙げられる。

40

[0022]

以下、図2Bの駆動タイミングチャート、図4A~図4Dの状態遷移図、図5の駆動トランジスタ202のドレイン電位の時間変化、および図6のガンマカーブと駆動トランジスタ202のゲート・ソース間電圧Vgsとの関係を参照しながら、上記歪みの発生原理について説明する。

[ 0 0 2 3 ]

[期間T21]

20

30

40

50

図2Bに示すように、時刻 t 0 において、スイッチ 2 0 6 のみを導通状態として、駆動トランジスタ 2 0 2 のソース電位を安定させる(駆動トランジスタ 2 0 2 のソース電位を初期化電圧 V i n i に設定する)。より具体的には、時刻 t 0 において、走査線駆動回路 5 0 は、走査線 9 3 と参照電圧制御線 9 4 と発光制御線 9 5 との電圧レベルをLOWに維持しつつ、初期化制御線 9 6 の電圧レベルをLOWからHIGHに変化させる。すなわち、時刻 t 0 において、スイッチ 2 0 3、スイッチ 2 0 4 およびスイッチ 2 0 5 は非導通状態(オフ状態)のままで、スイッチ 2 0 6 が導通状態(オン状態)にされる。なお初期化電圧 V i n i は、電位差(V i n i - V e l) < 0 である。

#### [0024]

このように、初期化制御線96の動作により、スイッチ203、スイッチ204、スイッチ205およびスイッチ206のうちスイッチ206のみを導通とする期間T21を設けることにより、駆動トランジスタ202のソース電位を初期化電源線23の電圧Viniにより短期間に設定することができる。また、容量素子210により、駆動トランジスタ202のゲート電位も、初期化電源線23の電圧Vini+前フレームでの発光時の駆動トランジスタ202のゲート・ソース間電圧に低下する。

### [0025]

この期間T21を設ける理由は次の通りである。

### [0026]

表示装置1を構成する表示部2のサイズや1画素あたり(画素20)のサイズが大きい場合に、有機EL素子201の容量が大きくなり、初期化電源線23の配線時定数が大きくなることで、駆動トランジスタ202のソース電位を初期化電源線23の電圧Viniにすることに時間を要する。そのため、スイッチ206を先に導通させる期間T21を設けることにより、駆動トランジスタ202のソース電位を初期化電源線23の電圧Viniにより短期間で設定(電圧Viniを書込み)することができる。

### [0027]

なお、参照電源線24の電圧Vrefを駆動トランジスタ202のゲートに印加することも同様に時間を要する。しかし、電圧Vrefを充放電する時間に影響する要因は、容量素子210および参照電源線24の配線時定数である。つまり、参照電源線24と初期化電源線23との配線時定数がほぼ同等であるが、有機EL素子201の容量>容量素子210であり、容量比は、(有機EL素子201)/(容量素子210)が1.3~9倍である。そのため、有機EL素子201を充電する(駆動トランジスタ202のソース電位に初期化電源線23の電圧Viniを書き込む)方が容量素子210を充電する(駆動トランジスタ202のゲート電位に参照電源線24の電圧Vrefを書き込む)よりも時間がかかる。

## [0028]

また、期間T21において、スイッチ206のみを導通させスイッチ204の導通を遅らせる利点としては次のようなものもある。

# [0029]

すなわち、期間T21において、駆動トランジスタ202のソース電位に初期化電源線23の電圧Viniを書き込む期間を設けることで参照電源線24の電圧Vrefを駆動トランジスタ202のゲートに書き込む負荷を軽くすることができる利点がある。つまり、期間T21を設けることで、駆動トランジスタ202のゲート電位を低い電位に設定することができ、参照電源線24は画素20に充電するための電流(電圧)を供給するのみでよくなる。換言すると、参照電源線24の電圧Vrefが有機EL素子201を充電するための電圧として用いられないため、参照電源線24の負荷が軽くなるという利点がある。

# [0030]

さらに、参照電源線 2 4 の負荷をより軽くするために、初期化電源線 2 3 を、 E L アノード電源線 2 1 および参照電源線 2 4 と直交する方向に配置されているとしてもよい。以

下、この場合について図を用いて説明する。

### [0031]

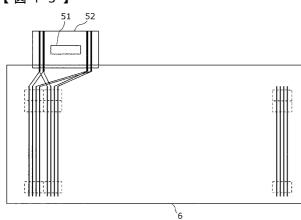

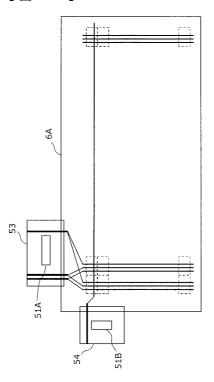

図13および図14は、表示装置の電源線の配置の一例を示す図である。

#### [0032]

以下では、参照電源線24、ELアノード電源線21、ELカソード電源線22および初期化電源線23を電源線とも称する。

#### [0033]

例えば図13に示すように、表示パネル6上に、4本の電源線をすべて縦方向に引くとしてもよい。しかし、この場合、表示部2の外周およびドライバIC51を備える走査線駆動回路50のフレキ部分52での抵抗を下げることが難しい。

### [0034]

それに対して、例えば図14に示すように、表示パネル6A上に、4本の電源線のうち1本の電源線を横に引く(つまり、他の3本の電源線と直交するように配置されること)。それにより、表示部2の外周とドライバIC51Aおよび51Bとを備える走査線駆動回路50のフレキ部分53、54で1電源線あたりの端子数および配線幅を太くすることができ、電圧ドロップによる電力損失を小さくできる。

### [0035]

横に引く1本の電源線としては、上述したように、初期化電源線23を選ぶとよい。すなわち、初期化電源線23を他の3本の電源線と直交するように配置される1本の電源線とすればよい。

### [0036]

より具体的には、画素 2 0 に必要な電源線は 4 種類あるが、電源線が表示パネル 6 A の外部に引き出される場合には、配線抵抗による電圧ドロップが生じる。そのため、この電圧ドロップを抑えるために、表示パネル 6 A の消費電力に影響する参照電源線 2 4 および E L カソード電源線 2 2 を、図 1 4 の縦方向(データ線の方向)に引き出すとよい。また、電源の揺れが直接表示輝度に影響する参照電源線 2 4 も、図 1 4 の縦方向(データ線の方向)に引き出すとよい。参照電源線 2 4 が縦方向に配置されると、参照電源線 2 4 が充放電する容量素子 2 1 0 の数は、期間 T 2 2 ~ T 2 4 の長さに対応した画素数となるので、負荷となる容量の数が小さくなり充放電が容易となる。

# [0037]

一方、初期化電源線23は、1水平走査期間で、有機 E L 素子201を1行分同時に充電する必要があるため、特に時定数が大きく、充放電に時間がかかるため、図14の横方向(データ線と直交する方向)に引き出すとよい。それにより、初期化電源線23の配線幅を太くすることができるので、初期化電源線23の配線遅延を少なくでき、より早く駆動トランジスタ202のソース電位を安定させることができる。

# [0038]

なお、図13および図14では、走査線駆動回路50の一部として、TAB(Tape Automated Bonding)で形成されたフレキ部分52、53、54を一例に図示されているが、それに限らない。COF(Chip on Film)またはTCP(Tape Carrier Package)で形成されていてもよくドライバIC51等を表示パネル6または6A上に搭載したCOG(Chip on Glass)で形成されているとしてもよい。また、図13および図14では、表示パネル6または6Aの片側にのみ形成されている例を示しているが、それに限らず両側からの給電される構成でもよい。

# [0039]

また、後述する期間T24(閾値補償動作時)においては、参照電源線24は画素20から電流を引き込むことが要求されるため、期間T21を設けることで、たとえ期間T21で参照電源線24から画素20に対して電流の供給(双方向)を十分に行えなくとも、期間T24において画素20間で電荷を再配分できるので所望の動作が実現できるようになる。つまり、期間T21を設けることで、参照電源線24の電源能力が高くなくても画

10

20

30

40

素20を駆動できる。

### [0040]

また、表示装置1を構成する表示部2のサイズが大きい場合には、電源線は、表示部2の端から中央に引き回された配線抵抗により電圧ドロップの問題が生じるが、期間21と設けることで、期間T24において画素20間で電荷やり取りが可能となるため、電圧ドロップを抑制できる。つまり、期間T21を設けることで、参照電源線24の配線幅を小さくできる。

## [0041]

このように、スイッチ 2 0 6 のみを導通状態(オン状態)に切り換えて、先に駆動トランジスタ 2 0 2 のソース電位を安定させる期間 T 2 1 を設ける。それにより、表示部 2 の電力消費と表示部 2 の輝度変動の影響とを小さくしつつ、期間 T 2 1 以降の期間 T 2 2 の総時間を短くすることができる。

### [0042]

なお、図12を用いて、初期化電源線23がELアノード電源線21および参照電源線24と直交する方向に配置されている場合について説明したが、それに限らない。参照電源線24がELアノード電源線21および初期化電源線23と直交する方向に配置されているとしてもよい。

### [0043]

この場合、表示部 2 の外部(パネル外部)への電源線の引き出しが、参照電源線 2 4 とそれ以外で異なる方向に引き出されることから、パネル外部への電源引き出し配線を太くすることができ、表示部 2 の周辺から外部電源回路までの参照電源線 2 4 の抵抗を小さく設計することが容易となる。それにより、抵抗による電圧ドロップによる電源変動の影響を受けにくくなり、均一性の高い表示が実現可能となる。

#### [0044]

### [期間T22]

図2Bに示す時刻t1~時刻t2の期間T22は、駆動トランジスタ202の閾値電圧補償を行うために駆動トランジスタ202を導通状態とし、ドレイン電流を流すのに必要な電圧を駆動トランジスタ202のゲート・ソース間に印加する初期化期間である。

# [0045]

具体的には、時刻 t 1 において、走査線駆動回路 5 0 は、走査線 9 3 と発光制御線 9 5 の電圧レベルを L O W に維持し、初期化制御線 9 6 の電圧レベルを H I G H に維持しつつ、参照電圧制御線 9 4 の電圧レベルを L O W から H I G H に変化させる。すなわち、時刻 t 1 において、スイッチ 2 0 3 およびスイッチ 2 0 5 は非導通状態(オフ状態)、かつ、スイッチ 2 0 6 が導通状態(オン状態)のままで、スイッチ 2 0 4 が導通状態(オン状態)にされる。

## [0046]

これにより、駆動トランジスタ202のゲート電位が参照電源線24の電圧Vrefに設定される。ここで、スイッチ206が導通状態であるから、駆動トランジスタ202のソース電位は初期化電源線23の電圧Viniに設定されている。すなわち、駆動トランジスタ202は、参照電源線24の電圧Vrefおよび初期化電源線23の電圧Viniが印加される。

### [0047]

なお、期間T22は、駆動トランジスタ202のゲートおよび駆動トランジスタ202のソース電位が、所定電位になるまでの長さ(時間)に設定される。

### [0048]

また、上述したように、駆動トランジスタ202のゲート・ソース間電圧は、閾値補正動作を行うのに必要な初期ドレイン電流を確保できる電圧に設定されることが必要である。そのため、参照電源線24の電圧Vrefと初期化電源線23の電圧Viniの電位差は駆動トランジスタ202の最大閾値電圧よりも大きな電圧に設定される。また、電圧Vrefおよび電圧Viniは、有機EL素子201に電流が流れないように、電圧Vin

10

20

30

40

20

30

40

50

i <(電圧Ve1+有機EL素子201の順方向電流閾値電圧)、および、Vref<(電圧Ve1+有機EL素子201の順方向電流閾値電圧+駆動トランジスタ202の閾値電圧)、となるように設定される。

# [0049]

[期間T23]

図 2 B に示す時刻 t 2 ~ 時刻 t 3 の期間 T 2 3 は、スイッチ 2 0 6 とスイッチ 2 0 5 とが同時に導通状態とならないようにするための期間である。

### [0050]

より具体的には、時刻 t 2 において、走査線駆動回路 5 0 は、走査線 9 3 と発光制御線 9 5 の電圧レベルを L O Wに維持し、参照電圧制御線 9 4 の電圧レベルを H I G H に維持しつつ、初期化制御線 9 6 の電圧レベルを H I G H から L O Wに変化させる。すなわち、時刻 t 2 において、スイッチ 2 0 3 およびスイッチ 2 0 5 は非導通状態(オフ状態)、かつ、スイッチ 2 0 4 が導通状態(オン状態)のままで、スイッチ 2 0 6 が非導通状態(オフ状態)にされる。

### [0051]

このように、初期化制御線 9 6 の動作によりスイッチ 2 0 6 を非導通とする期間T 2 3 を設けることにより、期間T 2 3 がなければスイッチ 2 0 6 とスイッチ 2 0 5 とが同時に導通状態となり、スイッチ 2 0 5、駆動トランジスタ 2 0 2、および、スイッチ 2 0 6 を介して、ELアノード電源線 2 1 と初期化電源線 2 3 との間に貫通電流が流れてしまうのを防止することができる。

### [0052]

なお、この時の貫通電流は、駆動トランジスタ202が閾値補償動作を行うのに十分な電流となるため、駆動トランジスタ202の閾値電圧が小さい場合には最高階調以上の電流が流れることも想定される。

### [ 0 0 5 3 ]

ELアノード電源線21は、発光期間において有機EL素子201に流れる電流に対応して、電圧降下が少ないように太く配線されているため、期間T23での貫通電流があっても、電圧変動の影響が少ない。一方、初期化電源線23については、駆動トランジスタ202のソースを所定電位に充電できればよく、電流が必要でない配線のため、ELアノード電源線21ほど太く配線されない。しかし、貫通電流が発生すると、ELアノード電源線21の配線抵抗により電圧降下がおき、電圧降下量が大きくなることから、駆動トランジスタ202のソースの所定の電位が印加できなくなる場合も考えられる。初期化電源線23の配線幅を太くすればよいが、配線幅を太くしないで良い方法として、本開示のように期間T23を設ける(挿入する)方法がある。期間T23を挿入する(設ける)ことにより、上述したように、初期化電源線23に流れる電流を少なくすることができるので、細い配線であっても駆動トランジスタ202のソースに所定電圧を印加することができる。

### [0054]

「期間 T 2 4 1

次に、図2Bの時刻t3~時刻t4の期間T24は、駆動トランジスタ202の閾値電圧を補償する閾値補償期間である。

### [0055]

具体的には、時刻 t 3 において、走査線駆動回路 5 0 は、走査線 9 3 および初期化制御線 9 6 の電圧レベルを L O W、参照電圧制御線 9 4 の電圧レベルを H I G H に維持し、発光制御線 9 5 の電圧レベルを L O W から H I G H に変化させる。すなわち、時刻 t 3 において、スイッチ 2 0 3 およびスイッチ 2 0 6 は非導通状態(オフ状態)に、かつ、スイッチ 2 0 4 は導通状態(オン状態)に維持されつつ、スイッチ 2 0 5 が導通状態(オン状態)にされる。

# [0056]

ここで、電圧は、初期化期間(期間T22)で上述したように設定されているので、有

機EL素子201には電流が流れない。駆動トランジスタ202は、ELアノード電源線21の電圧Vtftによりドレイン電流が供給されるが、それとともに駆動トランジスタ202のソース電位が変化する。言い換えると、駆動トランジスタ202は、ELアノード電源線21の電圧Vtftにより供給されるドレイン電流がほぼ0となる点まで駆動トランジスタ202のソース電位が変化する。

### [0057]

このように、駆動トランジスタ202のゲート電極に参照電源線24の電圧Vrefを入力した状態で、スイッチ205を導通状態(オン状態)にすると、駆動トランジスタ202の閾値補償動作を開始することができる。

#### [0058]

そして、期間T24の終了時(時刻t4)には、駆動トランジスタ202のゲートと駆動トランジスタ202のソースとの電位差(駆動トランジスタ202のゲート・ソース間電圧)は駆動トランジスタ202の閾値に相当する電位差となっており、この電圧は容量素子210に保持(記憶)される。

### [0059]

「期間T25]

図 2 B に示す時刻 t 4 ~ 時刻 t 5 の期間 T 2 5 は、閾値補償動作を終了させるための期間である。

### [0060]

より具体的には、走査線駆動回路50は、走査線93および初期化制御線96の電圧レベルをLOW、参照電圧制御線94の電圧レベルをHIGHに維持し、発光制御線95の電圧レベルをHIGHからLOWに変化させる。すなわち、時刻t4において、スイッチ203およびスイッチ206は非導通状態(オフ状態)に、かつ、スイッチ204は導通状態(オン状態)に維持されつつ、スイッチ205が非導通状態(オフ状態)にされる。

### [0061]

このようにして、発光制御線95の動作によりスイッチ205を非導通とする期間T25を設けることにより、駆動トランジスタ202経由で、ELアノード電源線21から駆動トランジスタ202のソースへの電流の供給をなくすことができ、閾値補償動作を確実に終了させてから次の動作を行うことができる。

# [0062]

「期間T26]

図2Bに示す時刻t5~時刻t6の期間T26は、スイッチ204を非導通状態(オフ状態)にすることで、データ線25を介して供給されたデータ電圧と参照電源線24の電圧Vrefとが同時に駆動トランジスタ202のゲートに印加されるのを防止する期間である。

## [0063]

具体的には、時刻 t 5 において、走査線駆動回路 5 0 は、走査線 9 3 と初期化制御線 9 6 と発光制御線 9 5 との電圧レベルを L O W に維持しつつ、参照電圧制御線 9 4 の電圧レベルを H I G H から L O W に変化させる。すなわち、時刻 t 5 において、スイッチ 2 0 3 、スイッチ 2 0 6 およびスイッチ 2 0 5 は非導通状態(オフ状態)のままで、スイッチ 2 0 4 が非導通状態(オフ状態)にされる。

### [0064]

このように、参照電圧制御線94の動作によりスイッチ204をさらに非導通とし、スイッチ203およびスイッチ204が非導通状態(オフ状態)となる期間T26を設けることで、データ線25を介してスイッチ203から供給されるデータ電圧と、参照電源線24の電圧Vrefとが駆動トランジスタ202のゲートに同時に印加されるのを防止することができる。

# [0065]

なお、スイッチ 2 0 4 とスイッチ 2 0 5 とを同時に非導通状態 (オフ状態)にし、期間 T 2 5 および期間 T 2 6 は一つにまとめてもよい。 10

20

30

20

30

40

50

#### [0066]

期間T25および期間T26と2段階にわける場合には、以下に説明する利点がある。すなわち、期間T25および期間T26を設けることで、駆動トランジスタ202のゲート電位である駆動トランジスタ202のゲート電位が不定となる期間をなるべく短くし、不定期間中で発生する恐れのある電位変動を抑え、映像信号に基づいた表示がより正確にできる。

### [0067]

また、階調表示は期間T26の最後(時刻t6)の駆動トランジスタ202のゲート電位と、データ線25で入力されるデータ電圧(映像信号)の書込み完了時(時刻t27)の駆動トランジスタ202のゲート電位との電位差によって行われるため、期間T26における駆動トランジスタ202のゲート電位変動は少ないほうが好ましい。理想的には、期間T24において駆動トランジスタ202のゲートに参照電源線24の電圧Vrefが印加され、期間T25においては駆動トランジスタ202のゲート電位が保持されることから、電位差(データ電圧・電圧Vref)に基づいて有機EL素子201の表示輝度が決まる。

### [0068]

なお、(データ電圧・電圧Vref)の電位差を正確に反映させるには、期間T26はなるべく短い方がよい。

### [0069]

また、発光制御線95に接続されるスイッチ205は駆動トランジスタ202のドレイン側に接続されている。スイッチ205をn型トランジスタで形成した場合、スイッチ205のオン抵抗は高くなりやすく、オン抵抗による電圧ドロップは、表示部2の消費電力に影響する。そのため、できる限りスイッチ205のオン抵抗を下げて形成する。一般的にはスイッチ205のチャネルサイズを大きくしたり、発光制御線95のオン制御電圧を高くしたりするなどでオン抵抗を下げる方法が知られているが、いずれの方法であっても発光制御線95の立下り時間を長くする方向となってしまう。

### [ 0 0 7 0 ]

そこで、以下に示す実施の形態では、参照電圧制御線94に対して先に発光制御線95を立ち下げる期間T25を設けることにより、駆動トランジスタ202のゲートの電圧が不安定となる期間を短くすることができる、つまり、立下り時間を短くすることができる

# [0071]

### 「期間 T 2 7 1

次に、図2Bの時刻t6~時刻t7の期間T27は、データ線25から表示階調に応じた映像信号電圧(データ電圧)を画素20にスイッチ203を介して取り込み、容量素子210に書き込む書込期間である。

### [0072]

具体的には、時刻 t 6 において、走査線駆動回路 5 0 は、初期化制御線 9 6 、参照電圧制御線 9 4 および発光制御線 9 5 の電圧レベルを L O W に維持しつつ、走査線 9 3 の電圧レベルを L O W から H I G H に変化させる。すなわち、時刻 t 6 において、スイッチ 2 0 4 とスイッチ 2 0 6 とスイッチ 2 0 5 は非導通状態(オフ状態)に維持されつつ、スイッチ 2 0 3 が導通状態(オン状態)にされる。

# [0073]

これにより、容量素子210には、閾値補償期間で記憶された駆動トランジスタ202の閾値電圧Vthに加えて、データ電圧と参照電源線24の電圧Vrefとの電圧差が、(容量211の静電容量) / (容量211の静電容量 + 容量素子210の静電容量)倍されて、記憶(保持)される。スイッチ205が非導通状態にあるため、駆動トランジスタ202のソース電位は期間T27の間で大きく変化することはない。なお、容量211は、有機EL素子201が有する寄生容量であってもよいし、容量素子210のようにTFT工程で形成してもよい

# [0074]

大画面化(表示部 2 のサイズが大きくなる)、かつ、画素 2 0 の数が増加するのに伴い、画素 2 0 に映像信号を書き込むための期間(水平走査期間)が短くなる。大画面化に伴い走査線 9 3 配線時定数も増加するため、水平走査期間の短縮とあわせて、所定の階調電圧を画素 2 0 に書き込むことが難しくなる。

#### [0075]

そこで、以下に示す実施の形態では、図2Bに示すように、限られた時間で映像信号(データ電圧)を取り込むために、スイッチ203を導通させる時間(期間 T27)を増加させている。また、以下に示す実施の形態では、走査線93の波形なまりがあっても、所定の映像信号(データ電圧)がデータ線25に入力される前に走査線93が立ち上がりを完了させて、スイッチ203が導通状態(オン状態)となるようにしている。これは期間 T27での駆動トランジスタ202のソース電位変動が大きく発生しないためである。

[0076]

これにより、走査線 9 3 の負荷(配線時定数)が大きく、立ち上がりに時間がかかるような大画面、高画素数の表示部 2 であっても確実に書き込むことができる。

[0077]

なお、このように駆動させることから、走査線 9 3 の配線幅をより細くすることもできる。その場合、配線幅を細くした分を容量素子 2 1 0 の大きさ(容量)を拡大することに用いて、表示性能を上げるとしてもよい。

[0078]

表示性能は、容量素子210が小さいと、駆動トランジスタ202のドレインゲート間寄生容量と容量素子210と容量211が直列になっている関係から、ELカソード電源線22の変動により、容量素子210に書き込まれている電荷量が変化するという問題が顕著となる。そのため、表示性能は、寄生容量と蓄積容量(容量素子210の静電容量)の比率が重要であり、蓄積容量/寄生容量>>1が好ましい。

[0079]

このように、期間T27(書込期間)では、データ電圧(映像信号電圧)および駆動トランジスタ202の閾値電圧に応じた電圧が容量素子210に記憶(保持)される。

[0080]

「期間T28]

図 2 B に示す時刻 t 7 ~ 時刻 t 8 の期間 T 2 8 は、スイッチ 2 0 3 を確実に非導通にさせるための期間である。

[0081]

より具体的には、時刻 t 7 において、走査線駆動回路 5 0 は、参照電圧制御線 9 4 と初期化制御線 9 6 と発光制御線 9 5 の電圧レベルを L O W に維持しつつ、走査線 9 3 の電圧レベルを H I G H から L O W に変化させる。すなわち、時刻 t 7 において、スイッチ 2 0 4、スイッチ 2 0 6 およびスイッチ 2 0 5 は非導通状態(オフ状態)のままで、スイッチ 2 0 3 が非導通状態(オフ状態)にされる。

[0082]

これにより、続く期間T29(発光期間)においてスイッチ205が導通状態(オン状態)にするまえにスイッチ203を確実に非導通状態(オフ状態)にすることができる。

[0083]

期間T28を設けず、スイッチ205とスイッチ203とが同時に導通状態(オン状態)になってしまった場合、駆動トランジスタ202のドレイン電流により、駆動トランジスタ202のゲート電位はデータ電圧となることから、駆動トランジスタ202のゲート・ソース間電圧が小さくなってしまう。この場合には、所望の輝度に比べて少ない輝度で発光してしまうという問題となる。これを防止するため、本実施の形態では、期間T28を設けてスイッチ203が非導通であることを確保してから、続く期間T29においてスイッチ205を導通状態にする

10

20

30

40

[0084]

[期間T29]

次に、図2Bに示す時刻t8~時刻t9の期間T29は、発光期間である。

[0085]

具体的には、時刻 t 8 において、走査線駆動回路 5 0 は、走査線 9 3 、参照電圧制御線 9 4 および初期化制御線 9 6 の電圧レベルを L O W に維持しつつ、発光制御線 9 5 の電圧レベルを L O W から H I G H に変化させる。すなわち、時刻 t 8 において、スイッチ 2 0 3 、スイッチ 2 0 4 およびスイッチ 2 0 6 は非導通状態(オフ状態)に維持されつつ、スイッチ 2 0 5 が導通状態(オン状態)にされる。

[0086]

このように、スイッチ205を導通状態(オン状態)にさせることで、容量素子210に蓄えられた電圧に応じて駆動トランジスタ202に有機EL素子201に電流を供給し有機EL素子201を発光させることができる。

[0087]

「期間T301

図2Bに示す時刻 t 9 ~ 時刻 t 0 の期間 T 3 0 は、すべてのスイッチを非導通状態として、駆動トランジスタ 2 0 2 のゲートおよび駆動トランジスタ 2 0 2 のソース電位を、期間 T 2 1 で必要な電圧に近い電位まで変化させるための期間である。

[0088]

より具体的には、時刻 t 9 において、走査線駆動回路 5 0 は、走査線 9 3 と参照電圧制御線 9 4 と初期化制御線 9 6 の電圧レベルを L O W に維持しつつ、発光制御線 9 5 の電圧レベルを H I G H から L O W に変化させる。すなわち、時刻 t 9 において、スイッチ 2 0 3、スイッチ 2 0 4、スイッチ 2 0 6 は非導通状態(オフ状態)のままで、さらにスイッチ 2 0 5 が非導通状態(オフ状態)にされる。

[0089]

このようにすることで、期間T29と期間T21の間に期間T30を設けることで、電源線による電流の充放電なしに、駆動トランジスタ202のゲートおよび駆動トランジスタ202のソース電位を、期間T21で必要な電圧に近い電位まで変化させることができる。

[0090]

より具体的には、駆動トランジスタ202のソースは、期間T30において、ELカソード電源線22の電圧Ve1+有機EL素子201の閾値電圧に収束する。また、駆動トランジスタ202のゲートは、期間T30において、駆動トランジスタ202のソースの電圧+容量素子210に記憶された電位となる。

[0091]

つまり、期間 T 2 1 の開始時点(時刻 t 0 ) では、期間 T 2 9 の終了時点(時刻 t 9 ) に比べ、有機 E L 素子 2 0 1 の発光時電圧 - 閾値電圧分だけ低くできる。

[0092]

この電位低下により、期間T21での初期化電源線23の電圧Viniと参照電源線2 4の電圧Vrefによる充放電作業の負荷が軽くなる。

[0093]

以上のようなシーケンスにより、画素20は、階調表示を行う。

[0094]

なお、制御回路 6 0 は、表示部 2 を構成する他の画素 2 0 についても、同様の駆動方法を線順次に行う。

[0095]

以上、表示パネルのサイズが大きい場合でも高精度な画像表示を可能とする駆動方法および表示装置を実現することができる。

[0096]

10

20

30

40

より具体的には、例えば、制御回路60は、複数の画素20の各々において,スイッチ205(第1スイッチ)およびスイッチ203(第2スイッチ)が非導通、かつ、スイッチ204(第3スイッチ)およびスイッチ206(第4スイッチ)が導通に切り換えられて駆動トランジスタ202が初期化される期間T22(初期化期間)を実行する。また、制御回路60は、スイッチ205(第1スイッチ)およびスイッチ204(第3スイッチ)が導通、かつ、スイッチ203(第2スイッチ)およびスイッチ206(第4スイッチ)が非導通に切り換えられて駆動トランジスタ202の閾値電圧が補償される期間T24(閾値電圧補償期間)を実行する。

# [0097]

また、例えば、制御回路 6 0 は、複数の画素 2 0 の各々において、期間 T 2 2 (初期化期間)の前にスイッチ 2 0 6 (第 4 スイッチ)のみ導通に切り換えることで期間 T 2 1 を開始させ、スイッチ 2 0 4 (第 3 スイッチ)を導通に切り換えることで期間 T 2 1 に続く期間 T 2 2 (初期化期間)を開始させる。

# [0098]

また、例えば、制御回路60は、複数の画素20の各々において、期間T21の前にスイッチ205(第1スイッチ)を非導通に切り換えることで、有機EL素子201を発光させる期間を終了させて、スイッチ205(第1スイッチ)、スイッチ204(第3スイッチ)、スイッチ203(第2スイッチ)およびスイッチ206(第4スイッチ)が非導通に切り換えられた後の期間T30を開始し、スイッチ206(第4スイッチ)を導通に切り換えることで期間T30に続く期間T21を開始する。

### [0099]

また、制御回路60は、複数の画素20の各々において、期間T24(閾値電圧補償期間)内で、スイッチ205(第1スイッチ)を非導通に切り換えることで、期間T24(閾値電圧補償期間)を終了させて期間T24(閾値電圧補償期間)に続く期間T25を開始し、期間T25の終了後に、スイッチ203(第2スイッチ)が導通に、かつ、スイッチ205(第1スイッチ)、スイッチ204(第3スイッチ)およびスイッチ206(第4スイッチ)が非導通に切り換えられた後の期間であって容量素子210に電圧を書き込む期間T27(書込期間)を開始する。

## [0100]

また、例えば、制御回路60は、複数の画素20の各々において、期間T25内で、スイッチ204(第3スイッチ)を非導通に切り換えることで、期間T25を終了させて期間T25に続く期間T26を開始し、期間T26内で、スイッチ203(第2スイッチ)を導通に切り換えることで、期間T26を終了させて期間T26に続く期間T27(書込期間)を開始する。

# [0101]

以上のように、表示パネルのサイズが大きい場合でも高精度な画像表示を可能とする駆動方法および表示装置を実現することができる。

# [0102]

上述したように、期間T21~T30は、1フレームに相当し、初期化期間、Vth検出期間、書込み期間、および発光期間で構成される。

# [0103]

### [ 0 - 3 . 階調特性の歪み]

階調特性の歪みは、上述したVth検出期間の終了時点~発光期間開始時点の動作に起因して発生する。また、上記歪みが発生する領域Pは、データ電圧Vdataの中域にて発生する。以下、データ電圧Vdataの低域(Vdata=1.0V、1.5V)、中域(Vdata=2.6V、3.4V)、高域(Vdata=4.0V、5.0V)、に分けて説明する。なお、ここでは、全階調を表現するデータ電圧の電圧範囲を0V(最低輝度)~10V(最高輝度)としている。また、ELアノード電源電圧(Vtft)=16V、および参照電圧(Vref)=1.5Vとし、駆動トランジスタ202の閾値電圧Vthを1Vと想定している。

10

20

30

20

30

40

50

[0104]

[ V d a t a = 1 . 0 V ]

図4Aは、データ電圧が1.0Vの場合の、Vth検出期間の終了時点~発光期間開始 時点の画素回路の状態遷移図である。

[ 0 1 0 5 ]

まず、V t h 検出終了( t 4 )直前において(図 4 A の A )、スイッチ 2 0 5 および 2 0 4 が 導通状態であるので、駆動トランジスタ 2 0 2 のドレイン電位 V D = 1 6 V 、ゲート電位 V G = 1 . 5 V 、およびソース電位 V S = 0 . 5 V となっている。

[0106]

次に、時刻 t 4 において(図 4 A の B)、スイッチ 2 0 5 を非導通としたことに伴い、ドレイン電位 V D は 1 6 V 7 V へと低下する。これは、スイッチ 2 0 5 の突下げによるものである。具体的には、発光制御線 9 5 に印加されたオフ電圧( - 3 V)が、スイッチ 2 0 5 のゲート・ソース間に存在する寄生容量 C e n b を介して駆動トランジスタ 2 0 2 のドレインノードへと突抜けることによるものである。

[0107]

次に、時刻 t 5 において(図 4 A の C )、スイッチ 2 0 4 を非導通としたことに伴い、ゲート電位 V G は 1 .5 V 0 .3 V へと低下する。これは、スイッチ 2 0 4 の突下げによるものである。具体的には、参照電圧制御線 9 4 に印加されたオフ電圧(- 3 V)が、スイッチ 2 0 4 のゲート・ソース間に存在する寄生容量を介して駆動トランジスタ 2 0 2 のゲートノードへと突抜けることによるものである。

[0108]

次に、時刻 t 6 において(図 4 A の D)、スイッチ 2 0 3 を導通させたことに伴い、ゲート電位 V G は 0 . 3 V 1 . 5 V へと増加する。これは、スイッチ 2 0 3 の突上げによるものである。具体的には、走査線 9 3 に印加されたオン電圧(+ 2 0 V)が、スイッチ 2 0 3 のゲート・ソース間に存在する寄生容量を介して駆動トランジスタ 2 0 2 のゲート ノードへと突抜けることによるものである。

[0109]

次に、期間T27において(図4AのE)、データ電圧Vdata=1.0Vが駆動トランジスタ202のゲートノードに印加されたことに伴い、ゲート電位VGは1.0Vとなる。また、ドレイン電位VDは、7V 6.7Vへと低下する。これは、第1には、ゲート電位VGが、駆動トランジスタ202のゲート・ドレイン間に存在する寄生容量Cdrvを介して駆動トランジスタ202のドレインノードへと突抜けることによるものである。また、第2には、ゲート電位VG=1.0Vであるので、駆動トランジスタ202が非導通状態となり、駆動トランジスタ202のドレイン電極からソース電極への電荷放電がほぼ無い状態となることによるものである。

[0110]

次に、時刻 t 7 において(図 4 A の F )、スイッチ 2 0 3 を非導通としたことに伴い、ゲート電位 V G は 1 V 0 . 1 V へと低下する。これは、スイッチ 2 0 3 の突下げによるものである。具体的には、走査線 9 3 に印加されたオフ電圧(- 3 V )が、スイッチ 2 0 3 のゲート・ソース間に存在する寄生容量を介して駆動トランジスタ 2 0 2 のゲートノードへと突抜けることによるものである。また、同時に、ドレイン電位 V D は、6 . 7 V 6 . 4 V へと低下する。これは、ゲート電位 V G が、駆動トランジスタ 2 0 2 のゲート・ドレイン間に存在する寄生容量 C d r v を介して駆動トランジスタ 2 0 2 のドレインノードへと突抜けることによるものである。

[0111]

次に、時刻 t 8 において(図 4 A の G )、スイッチ 2 0 5 を導通させたことに伴い、ドレイン電位 V D は、 E L アノード電源線 2 1 の電圧( 1 6 V )へと増加する。

[0112]

20

30

40

50

VGは1.0Vとなる。これは、ドレイン電位VDが、駆動トランジスタ202のゲート・ドレイン間に存在する寄生容量Cdrvを介して駆動トランジスタ202のゲートノードへと突抜けることによるものである。

[ 0 1 1 3 ]

[Vdata=1.5V]

データ電圧 V d a t a = 1 . 5 V の場合の状態遷移については図示していないが、図 4 A を用いてその差異点を説明する。

[0114]

V t h 検出終了( t 4 ) 直前(図 4 A の A ) ~ 時刻 t 6 (図 4 A の D ) まではデータ電圧によらず、図 4 A と同様の回路状態となる。

[0115]

次に、期間T27において(状態E)、データ電圧Vdata=1.5Vが駆動トランジスタ202のゲートノードに印加されたことに伴い、ゲート電位VGは1.5Vとなる。また、ドレイン電位VDは、7V 6.7Vへと減少する。これは、第1には、ゲート電位VGが、駆動トランジスタ202のゲート・ドレイン間に存在する寄生容量Cdrvを介して駆動トランジスタ202のドレインノードへと突抜けることによるものである。また、第2には、ゲート電位VG=1.5Vであるので、駆動トランジスタ202が非導通状態となり、駆動トランジスタ202のドレイン電極からソース電極への電荷放電がほぼ無い状態となることによるものである。

[0116]

次に、時刻 t 7 において(状態 F )、スイッチ 2 0 3 を非導通としたことに伴い、ゲート電位 V G は 1 .5 V 0 .6 V へと低下する。これは、スイッチ 2 0 3 の突下げによるものである。具体的には、走査線 9 3 に印加されたオフ電圧( - 3 V )が、スイッチ 2 0 3 のゲート・ソース間に存在する寄生容量を介して駆動トランジスタ 2 0 2 のゲートノードへと突抜けることによるものである。また、同時に、ドレイン電位 V D は、6 . 7 V 6 . 4 V へと低下する。これは、ゲート電位 V G が、駆動トランジスタ 2 0 2 のゲート・ドレイン間に存在する寄生容量 C d r v を介して駆動トランジスタ 2 0 2 のドレインノードへと突抜けることによるものである。

[0117]

次に、時刻 t 8 において ( 状態 G ) 、スイッチ 2 0 5 を導通させたことに伴い、ドレイン電位 V D は、 E L アノード電源電圧 V t f t ( 1 6 V ) へと増加する。

[0118]

上記回路動作により、 V d a t a = 1 . 5 V を書込んだ場合、時刻 t 7 t 8 でのドレイン電位 V D の変動量は、 1 6 V - 6 . 4 V = 9 . 6 V である。

[0119]

データ電圧 V d a t a が 1 . 0 V および 1 . 5 V の場合には、期間 T 2 7 (状態 E ) において駆動トランジスタ 2 0 2 が導通状態とならず駆動トランジスタ 2 0 2 のドレイン電極からソース電極へと電荷が抜けない。これにより、時刻 t 7 でのドレイン電位 V D は、いずれの場合も 6 . 4 V となる。

[0120]

ここで、時刻 t 7 t 8 でのドレイン電位変動量 V D によるゲート電位突上げ量 V G は、以下の式 1 で表される。

[0121]

【数1】

$$\Delta VG = \Delta VD(\frac{CdrvD}{CdrvD + CdrvS + Cs}) \tag{$\vec{x}_{1}$}$$

[0122]

上記式 1 において、Csは容量素子 2 1 0 の静電容量であり、CdrvDは駆動トランジスタ 2 0 2 のゲート・ドレイン間に発生する寄生容量であり、CdrvSは駆動トラン

ジスタ 2 0 2 のゲート・ソース間に発生する寄生容量である。 V d a t a = 1 . 0 V および 1 . 5 V の場合において、ドレイン電位変動量 V D によるゲート電位突上げ量 V G は、上記式 3 に各容量値(C s = 0 . 5 p F 、C d r v D = C d r v S = 0 . 0 5 6 p F ) および V D = 9 . 6 V を代入すると、 V G = 0 . 8 S V となる。

[ 0 1 2 3 ]

[Vdata=2.6V]

図4Bは、データ電圧が2.6Vの場合の、Vth検出期間の終了時点~発光期間開始時点の画素回路の状態遷移図である。

[0124]

V t h 検出終了( t 4 ) 直前(図4BのA) ~ 時刻 t 6 (図4BのD) まではデータ電圧によらず、図4Aと同様の回路状態となる。

[ 0 1 2 5 ]

次に、期間T27において(図4BのE)、データ電圧Vdata=2.6Vが駆動トランジスタ202のゲートノードに印加されたことに伴い、ゲート電位VGは2.6Vとなる。また、ドレイン電位VDは、7V 6Vへと低下する。これは、ゲート電位VG=2.6Vであるので、駆動トランジスタ202が導通状態となり、駆動トランジスタ202のドレイン電極からソース電極への電荷放電が発生することによるものである。

[0126]

次に、時刻 t 7 において(図 4 BのF)、スイッチ 2 0 3 を非導通としたことに伴い、ゲート電位 V G は 2 . 6 V 1 . 4 V へと低下する。これは、スイッチ 2 0 3 の突下げによるものである。具体的には、走査線 9 3 に印加されたオフ電圧(- 3 V)が、スイッチ 2 0 3 のゲート・ソース間に存在する寄生容量を介して駆動トランジスタ 2 0 2 のゲート ノードへと突抜けることによるものである。また、同時に、ドレイン電位 V D は、 6 V 5 . 7 V へと低下する。これは、ゲート電位 V G が、駆動トランジスタ 2 0 2 のゲート・ドレイン間に存在する寄生容量 C d r v を介して駆動トランジスタ 2 0 2 のドレイン ノードへと突抜けることによるものである。

[0127]

[0128]

上記回路動作により、 V d a t a = 2 . 6 V を書込んだ場合、時刻 t 7 t 8 でのドレイン電位 V D の変動量は、 1 6 V - 5 . 7 V = 1 0 . 3 V である。

[0129]

データ電圧 V d a t a が 2 . 6 V の場合には、期間 T 2 7 (状態 E )において駆動トランジスタ 2 0 2 が導通状態となりドレイン電極からソース電極へと電荷が抜け始める。これにより、時刻 t 7 でのドレイン電位 V D は、 5 . 7 V となる。

[0130]

V d a t a = 2 . 6 V の場合において、ドレイン電位変動量 V D によるゲート電位突上げ量 V G は、上記式 3 に駆動トランジスタ 2 0 2 の各容量値および V D = 1 0 . 3 V を代入すると、 V G = 0 . 9 4 V となる。

[ 0 1 3 1 ]

[Vdata=3.4V]

図4Cは、データ電圧が3.4Vの場合の、Vth検出期間の終了時点~発光期間開始 時点の画素回路の状態遷移図である。

[0132]

V t h 検出終了( t 4 ) 直前(図4CのA) ~ 時刻 t 6 (図4CのD) まではデータ電圧によらず、図4Aと同様の回路状態となる。

[0133]

次に、期間 T 2 7 において(図 4 C の E )、データ電圧 V d a t a = 3 . 4 V が駆動トランジスタ 2 0 2 のゲートノードに印加されたことに伴い、ゲート電位 V G は 3 . 4 V と

10

20

30

40

20

30

40

50

なる。また、ドレイン電位 V D は、 7 V 4 . 6 V へと低下する。これは、ゲート電位 V G = 3 . 4 V であるので、駆動トランジスタ 2 0 2 が導通状態となり、駆動トランジスタ 2 0 2 のドレイン電極からソース電極への電荷放電が発生することによるものである。

[0134]

次に、時刻 t 7 において(図 4 C の F )、スイッチ 2 0 3 を非導通としたことに伴い、ゲート電位 V G は 3 . 4 V 2 . 2 V へと低下する。これは、スイッチ 2 0 3 の突下げによるものである。具体的には、走査線 9 3 に印加されたオフ電圧(- 3 V)が、スイッチ 2 0 3 のゲート・ソース間に存在する寄生容量を介して駆動トランジスタ 2 0 2 のゲート ノードへと突抜けることによるものである。また、同時に、ドレイン電位 V D は、 4 . 6 V 4 . 3 V へと低下する。これは、ゲート電位 V G が、駆動トランジスタ 2 0 2 のゲート・ドレイン間に存在する寄生容量 C d r v を介して駆動トランジスタ 2 0 2 のドレイン ノードへと突抜けることによるものである。

[0135]

次に、時刻 t 8 において(図4 C の G)、スイッチ 2 0 5 を導通させたことに伴い、ドレイン電位 V D は、E L アノード電源電圧 V t f t (16 V)へと増加する。

[0136]

上記回路動作により、 V d a t a = 3 . 4 V を書込んだ場合、時刻 t 7 t 8 でのドレイン電位 V D の変動量は、 1 6 V - 4 . 3 V = 1 1 . 7 V である。

[0137]

データ電圧 V d a t a が 3 . 4 V の場合には、期間 T 2 7 (状態 E ) において駆動トランジスタ 2 0 2 が導通状態となり、 V d a t a = 2 . 6 V の場合よりもドレイン電極からソース電極への電荷放電量が多い。これにより、時刻 t 7 でのドレイン電位 V D は、 4 . 3 V となる。

[ 0 1 3 8 ]

V d a t a = 3 . 4 V の場合において、ドレイン電位変動量 V D によるゲート電位突上げ量 V G は、上記式 3 に駆動トランジスタ 2 0 2 の各容量値および V D = 1 1 . 7 V を代入すると、 V G = 1 . 0 7 V となる。

[ 0 1 3 9 ]

[ V d a t a = 4 . 0 V ]

図4Dは、データ電圧が4.0Vの場合の、Vth検出期間の終了時点~発光期間開始時点の画素回路の状態遷移図である。

[0140]

V t h 検出終了( t 4 ) 直前(図4DのA) ~ 時刻 t 6 (図4DのD) まではデータ電圧によらず、図4Aと同様の回路状態となる。

[0141]

次に、期間T27において(図4DのE)、データ電圧Vdata=4.0Vが駆動トランジスタ202のゲートノードに印加されたことに伴い、ゲート電位VGは4.0Vとなる。また、ドレイン電位VDは、7V 1Vへと低下する。これは、ゲート電位VG=4.0Vであるので、駆動トランジスタ202が導通状態となり、駆動トランジスタ202のドレイン電極からソース電極への電荷放電が発生することによるものである。

[0142]

次に、時刻 t 7 において(図 4 D の F )、スイッチ 2 0 3 を非導通としたことに伴い、ゲート電位 V G は 4 V 2 . 8 V へと低下する。これは、スイッチ 2 0 3 の突下げによるものである。具体的には、走査線 9 3 に印加されたオフ電圧(- 3 V )が、スイッチ 2 0 3 のゲート・ソース間に存在する寄生容量を介して駆動トランジスタ 2 0 2 のゲートノードへと突抜けることによるものである。また、同時に、ドレイン電位 V D は、 1 V 0 . 5 V へと低下する。これは、ゲート電位 V G が、駆動トランジスタ 2 0 2 のゲート・ドレイン間に存在する寄生容量 C d r v を介して駆動トランジスタ 2 0 2 のドレインノードへと突抜けることによるものである。

[0143]

20

30

40

50

次に、時刻 t 8 において(図 4 D の G)、スイッチ 2 0 5 を導通させたことに伴い、ドレイン電位 V D は、E L アノード電源電圧 V t f t ( 1 6 V ) へと増加する。

### [0144]

上記回路動作により、 V d a t a = 4 . 0 V を書込んだ場合、時刻 t 7 t 8 でのドレイン電位 V D の変動量は、 1 6 V - 0 . 5 V = 1 5 . 5 V である。

### [0145]

データ電圧 V d a t a が 4 . 0 V の場合には、期間 T 2 7 (状態 E ) において駆動トランジスタ 2 0 2 が導通状態となり、 V d a t a = 3 . 4 V の場合よりもドレイン電極からソース電極への電荷放電量が多い。これにより、時刻 t 7 でのドレイン電位 V D は、 0 . 5 V となる。

[0146]

[Vdata=5.0V]

データ電圧 V d a t a = 5 . 0 V の場合の状態遷移については図示していないが、図 4 D を用いてその差異点を説明する。

### [0147]

Vth検出終了(t4)直前(状態A)~時刻t6(状態D)まではデータ電圧によらず、図4Dと同様の回路状態となる。

[0148]

次に、期間T27において(状態E)、データ電圧Vdata=5.0Vが駆動トランジスタ202のゲートノードに印加されたことに伴い、ゲート電位VGは5.0Vとなる。また、ドレイン電位VDは、7V 1Vへと低下する。これは、ゲート電位VG=5. 0Vであるので、駆動トランジスタ202が導通状態となり、駆動トランジスタ202のドレイン電極からソース電極への電荷放電が発生することによるものである。

[0149]

[0150]

次に、時刻 t 8 において ( 状態 G ) 、スイッチ 2 0 5 を導通させたことに伴い、ドレイン電位 V D は、 E L アノード電源電圧 V t f t ( 1 6 V ) へと増加する。

[ 0 1 5 1 ]

上記回路動作により、 V d a t a = 5 . 0 V を書込んだ場合、時刻 t 7 t 8 でのドレイン電位 V D の変動量は、 1 6 V - 0 . 5 V = 1 5 . 5 V である。

[0152]

データ電圧 V d a t a が 5 . 0 V の場合には、期間 T 2 7 (状態 E)において駆動トランジスタ 2 0 2 が導通状態となり、ドレイン電極からソース電極への電荷放電が発生するが、 V d a t a = 4 . 0 V 以上の場合は、駆動トランジスタ 2 0 2 のドレインノードに溜まった電荷が全て抜けきっているので、ドレイン電位 V D は 0 . 5 V で一定となる。

[ 0 1 5 3 ]

V d a t a = 4 . 0 V および 5 . 0 V の場合において、ドレイン電位変動量 V D によるゲート電位突上げ量 V G は、上記式 3 に駆動トランジスタ 2 0 2 の各容量値および V D = 1 5 . 5 V を代入すると、いずれの場合も V G = 1 . 4 1 V となる。

[0154]

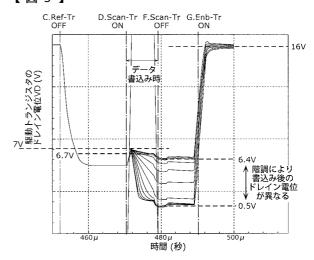

図 5 は、駆動トランジスタのドレイン電位の時間変化を表すグラフである。同図において、横軸は 1 フレームにおける閾値電圧検出期間の終了時( t 5 ) ~ 発光期間の終了時(

20

30

40

50

t9)までを表している。データ電圧の書込み直前である時刻 t6(Scan・Tr ON)では、ドレイン電位 VDは、いずれのデータ電圧においても7 Vとなっている。その後、データ電圧 Vdataの大きさ(階調レベル)により、書込み終了時点(t7)でのドレイン電位 VDは 0.5 V~6.4 Vの間で変化する。つまり、階調により駆動トランジスタ 202を介して抜ける電荷量が変わるため、書込み後のドレイン電位 VDが異なる

#### [ 0 1 5 5 ]

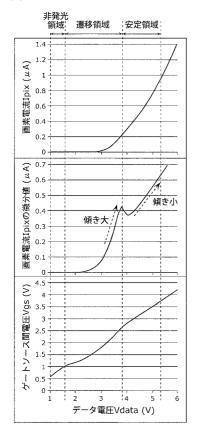

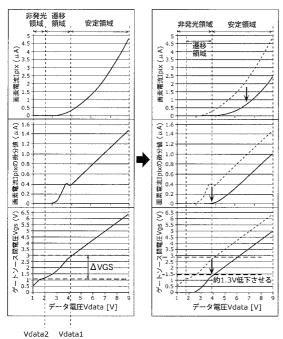

図 6 は、階調特性と駆動トランジスタのゲート - ソース間電圧との関係を表すグラフである。

# [0156]

非発光領域(Vdata=1.0V、1.5 V)では、駆動トランジスタ202のドレインからソースへ電荷が抜けないので、ドレイン電位変動量 VDは9.6 Vで一定であり、ゲート電位突上げ量 VGは0.87Vで一定である。

# [0157]

これに対して、遷移領域(Vdata=2.6V、3.4V)では、データ電圧が大きくなるほど駆動トランジスタ202のドレインからソースへの電荷放電量が多くなるので、Vdataに連動してドレイン電位変動量 VDは大きくなる。これに伴い、ゲート電位突上げ量 VGも大きくなり、ゲート電位VGもその分大きくなる。これにより、階調カーブの傾きが大きくなる。

# [0158]

また、安定領域(Vdata=4.0V、5.0V)では、駆動トランジスタ202のドレインからソースへの電荷放電が発生しないので、ドレイン電位変動量 VDおよびゲート電位突上げ量 VGが一定となる。これにより、階調カーブの傾きが低下する。遷移領域と安定領域との境界において、階調カーブの傾きが変わることにより、歪みが発生する。

# [0159]

以上のように、(1)駆動トランジスタ202のドレイン側に発光を制御するスイッチ205が存在し、(2)スイッチ205をデータ書込み時に非導通とし発光時に消通され、(3)データ書込み時にデータ電圧が駆動トランジスタ202のドレイン側にされる寄生容量からソース側に放電される電荷量が、データ電圧およびスイッチの突抜けて変動を受ける。このため、データ書込み完了時のドレイン電位VDが階調によて変動では、発光開始時の駆動トランジスタ202のゲートとを、発明者らして、発光開始時の駆動トランジスタ202のゲートとを、発明者らは、スイッチのとは、非導通とした際に、各制御線から駆動トランジスタ202のゲートおよるによび、第1には、スイッチイに交抜ける電圧は、走査線駆動回路50からの距離に応じて異なるためである。第通、非導通とした際に、各制御線から駆動トランジスタ202のゲートおよびにデータ線駆動回路50からの距離に応じて異なるためである。カタ線駆動回路40、および走査線駆動回路50からの距離に応じて異なるためである。このため、表示部において輝度ムラが発生する問題を有する。

### [0160]

上記の課題は、特にスタガ型または逆スタガ型構造の様なセルフアライメント構造を取らないトランジスタにおいて顕著である。セルフアライメント構造を取らないトランジスタにおいては、チャネル領域を確実にゲート電極で覆うために、マスクのアライメントずれ量や各層のエッチング後退量を考慮して、ゲート電極とドレイン電極またはソース電極とをオーバーラップさせる構造を取ることが一般的である。そのため、スイッチ205のゲート・ソース間に存在する寄生容量Cenbや、駆動トランジスタ202のゲート・ドレイン間に存在する寄生容量Cdrvが大きくなり、データ書込み時に駆動トランジスタ202のドレイン側の寄生容量からソース側に放電される電荷量の影響を受けやすいと言

20

30

40

50

う特徴がある。スタガ型または逆スタガ型構造を取るトランジスタとしては、アモルファスシリコントランジスタや、IGZO(Indium Gallium Zinc Oxide)などの酸化物半導体が代表的である。

# [0161]

このような問題を解決するために、本発明の一態様に係る表示装置は、複数の表示画素 が行列状に配置された表示部を有する表示装置であって、前記複数の表示画素に高電位側 の駆動電圧を供給するための第1駆動電源線と、画素列に対応して配置され、映像信号を 反映したデータ電圧を前記複数の表示画素へ伝達する複数のデータ線とを備え、前記複数 の表示画素の各々は、発光素子と、前記データ電圧に対応した電圧を保持するための容量 素子と、前記電圧がゲート・ソース間に印加されることにより当該電圧に応じた電流を前 記 発 光 素 子 に 流 す 駆 動 ト ラ ン ジ ス タ と 、 第 1 ゲ ー ト 電 極 、 第 2 電 極 お よ び 第 3 電 極 を 有 し 、 前 記 第 2 電 極 が 前 記 第 1 駆 動 電 源 線 に 接 続 さ れ 、 前 記 第 3 電 極 が 前 記 駆 動 ト ラ ン ジ ス タ のソースおよびドレインの一方に接続され、前記第1駆動電源線と前記駆動トランジスタ の導通および非導通を切り換える第1スイッチトランジスタと、第2ゲート電極、第4電 極 お よ び 第 5 電 極 を 有 し 、 前 記 第 4 電 極 が 前 記 複 数 の デ ー タ 線 の う ち 対 応 す る デ ー タ 線 に 接続され、前記第5電極が前記容量素子に接続され、前記データ線と前記容量素子との導 通および非導通を切り換える第2スイッチトランジスタとを備え、前記表示装置は、さら に、前記第 1 スイッチトランジスタを非導通状態かつ前記第 2 スイッチトランジスタを導 通状態とすることにより前記容量素子に前記データ電圧を書込む書込みステップと、前記 第 1 スイッチトランジスタを導通状態かつ前記第 2 スイッチトランジスタを非導通状態と することにより当該電圧に応じた電流を前記発光素子に流す発光ステップとを実行する制 御 部 と を 備 え 、 前 記 第 1 ス イ ッ チ ト ラ ン ジ ス タ は 、 前 記 書 込 み ス テ ッ プ に お い て 前 記 第 3 電 極 か ら 前 記 第 1 ゲ ー ト 電 極 へ の 電 荷 突 抜 け に よ り 前 記 第 3 電 極 の 電 位 を 低 下 さ せ る 、 お よび、前記第2スイッチトランジスタは、前記書込みステップの終了時において前記第5 電 極 か ら 前 記 第 2 ゲ ー ト 電 極 へ の 電 荷 突 抜 け に よ り 前 記 第 5 電 極 の 電 位 を 低 下 さ せ る 、 の 少なくともいずれかが実行されることを特徴とする。

### [0162]

本態様によれば、容量素子のへ書込み電圧を変動させる要因である駆動トランジスタのソースおよびドレインの一方、ならびに、駆動トランジスタのゲート、の少なくとも一方を、スイッチトランジスタのオフ時に電荷突抜けを発生させることにより電位を低下させる。これにより、駆動トランジスタのソースおよびドレインの一方からゲートへの突抜け電圧のデータ電圧依存性を低減する、および、駆動トランジスタのゲート電位を低電位側へとシフトさせる、の少なくともいずれかが実行される。よって、書込み電圧の変動が抑制され、表示パネルの輝度ムラを抑制できる。

# [0163]

また、前記表示装置は、前記複数の表示画素に低電位側の駆動電圧を供給するための第2駆動電源線を備え、前記制御部は、前記書込みステップにおいて、前記第2駆動電源線の電圧値から所定値だけ小さい電圧よりもさらに小さい第1制御電圧を前記第1ゲート電極に印加することにより、前記第1スイッチトランジスタを非導通状態としてもよい。

### [0164]

これにより、駆動トランジスタのソースおよびドレインの一方の電位は、データ書込み 完了時において、データ電圧の大きさによらず一定電位となる。よって、全階調範囲にお ける書込み電圧の変動が抑制される。

# [0165]

また、前記第1スイッチトランジスタは、前記電荷突抜けにより前記第3電極の電位が前記駆動トランジスタのソースおよびドレインの他方の電位となるまで前記電位を低下させてもよい。

# [0166]

これにより、第1スイッチトランジスタが非導通状態である書込み期間において、駆動 トランジスタのソースおよびドレインの一方に蓄積された電荷を、第1スイッチトランジ スタの寄生容量を介して、第1スイッチトランジスタのゲート電極へと突抜けさせることが可能となる。よって、駆動トランジスタのソースおよびドレインの一方の電位は、データ書込み完了時において、データ電圧の大きさによらず一定電位となる。よって、全階調範囲における書込み電圧の変動が抑制される。

# [0167]

また、前記制御部は、前記書込みステップの終了時において、前記データ電圧の電圧範囲の下限電圧値から所定値だけ小さい電圧よりもさらに小さい第2制御電圧を前記第2ゲート電極に印加することにより、前記第2スイッチトランジスタを非導通状態としてもよい。

# [0168]

これにより、第2スイッチトランジスタが非導通状態である書込み期間の終了時において、駆動トランジスタのゲートに蓄積された電荷を、第2スイッチトランジスタの寄生容量を介して、第2スイッチトランジスタのゲート電極へと突抜けさせることが可能となる。よって、書込み電圧である駆動トランジスタのゲート・ソース間電圧Vgsは、データ書込み完了時において低電位側へシフトする。このため、階調特性の歪みが発生する領域は、階調特性の歪みが目立たない低階調側へと移動するので、輝度ムラが視認され易い中階調以上での書込み電圧の変動が抑制される。

### [0169]

また、前記第1スイッチトランジスタは、前記第1ゲート電極と前記第2電極とで形成された第1寄生容量と、前記第1ゲート電極と前記第3電極とで形成された第2寄生容量とを有し、前記第2寄生容量が前記第1寄生容量よりも大きくなるよう形成されていてもよい。

### [0170]

これにより、第1スイッチトランジスタが非導通状態である書込み期間において、駆動トランジスタのソースおよびドレインの一方から第1スイッチトランジスタのゲート電極への電荷突抜け量を大きくすることが可能となる。よって、駆動トランジスタのソースおよびドレインの一方の電位は、データ書込み完了時において、データ電圧の大きさによらず一定電位となる。よって、全階調範囲における書込み電圧の変動が抑制される。

## [0171]

また、前記第1スイッチトランジスタは、スタガ型または逆スタガ型構造を有してもよい。

# [0172]

これにより、第1スイッチトランジスタにおいて、ゲート電極が構成要素となって形成される寄生容量を大きく確保することが可能となる。よって、駆動トランジスタのソースおよびドレインの一方から第1スイッチトランジスタのゲート電極への電荷突抜け量を大きくすることが可能となる。

# [0173]

また、さらに、前記制御部と前記表示部との間に配置され、前記制御部の指示により行順次に前記第1ゲート電極に制御信号を印加する第1駆動回路を備え、前記表示部に配置された前記複数の表示画素において、前記第1駆動回路に近い表示画素ほど前記第2寄生容量が小さい前記第1スイッチトランジスタを備えてもよい。

### [0174]

これにより、第1スイッチトランジスタの非導通時における突下げ電圧を、表示部内で均一化することが可能となる。よって、全階調範囲における書込み電圧の変動が抑制され、表示パネルの輝度ムラを抑制できる。

# [0175]

また、前記第2スイッチトランジスタは、前記第2ゲート電極と前記第4電極とで形成された第3寄生容量と、前記第2ゲート電極と前記第5電極とで形成された第4寄生容量とを有し、前記第4寄生容量が前記第3寄生容量よりも大きくなるよう形成されていてもよい。

10

20

30

40

20

30

40

[0176]

これにより、第2スイッチトランジスタが非導通状態である書込み期間の終了時において、駆動トランジスタのゲートから第2スイッチトランジスタのゲート電極への電荷突抜け量を大きくすることが可能となる。よって、書込み電圧である駆動トランジスタのゲート・ソース間電圧Vgsは、データ書込み完了時において低電位側へシフトする。このため、階調特性の歪みが発生する領域は、階調特性の歪みが目立たない低階調側へと移動するので、書込み電圧の変動が抑制される。

[0177]

また、前記第2スイッチトランジスタは、スタガ型または逆スタガ型構造を有してもよい。

[0178]

これにより、第2スイッチトランジスタにおいて、ゲート電極が構成要素となって形成される寄生容量を大きく確保することが可能となる。よって、駆動トランジスタのゲートから第2スイッチトランジスタのゲート電極への電荷突抜け量を大きくすることが可能となる。

[0179]

また、さらに、前記制御部と前記表示部との間に配置され、前記制御部の指示により行順次に前記第2ゲート電極に制御信号を印加する第2駆動回路を備え、前記表示部に配置された前記複数の表示画素において、前記第2駆動回路に近い表示画素ほど前記第4寄生容量が小さい前記第2スイッチトランジスタを備えてもよい。

[0180]

これにより、第2スイッチトランジスタの非導通時における突下げ電圧を、表示部内で均一化することが可能となる。よって、輝度ムラが視認され易い中階調範囲における書込み電圧の変動が抑制され、表示パネルの輝度ムラを抑制できる。

[0181]

また、前記第1駆動電源線の電圧を $V_{tft}$ 、前記容量素子および前記駆動トランジスタのゲート電極に印加される参照電圧を $V_{ref}$ 、前記駆動トランジスタの閾値電圧を $V_{thenb}$ 、前記第1スイッチトランジスタの閾値電圧を $V_{thenb}$ 、および前記駆動トランジスタのゲートと前記ソースおよびドレインの一方とで形成される寄生容量を $C_{tt}$  のとした場合、前記第1スイッチトランジスタを非導通状態とするゲート電位 $V_{enb}$  L および前記第1ゲート電極と前記第3電極とで形成される寄生容量 $C_{tt}$  の に し に し に し に し に し に し に し に で 形成される寄生容量  $C_{tt}$  の に の し は 、

【数2】

$$V_{tft} - \left(V_{ref} - Vth_{drv}\right) = \left(V_{tft} + Vth_{enb} - V_{enb}L\right) \times \left(\frac{Cenb}{Cenb + Cdrv}\right)$$

なる関係を満たしてもよい。

[0182]

上記関係式により、第1スイッチトランジスタのオフ電圧(第1制御電圧) VenbLおよび第1ゲート電極と第3電極とで形成される寄生容量 Cenbを選択することにより、画素回路の設計パラメータの自由度が大きくなる。

[0183]

また、前記駆動トランジスタのゲート・ソース間電圧Vgsの低階調側への目標シフト量を Vgs、階調特性に歪みが発生する前記データ電圧をVdata、前記第2スイッチトランジスタの閾値電圧をVthscn、および前記容量素子の静電容量をCsとした場合、前記第2スイッチトランジスタを非導通状態とするゲート電位VscnLおよび前記第2ゲート電極と前記第5電極とで形成される寄生容量Cscnは、

### 【数3】

$$\Delta Vgs = \left(Vdata + Vth_{scn} - V_{scn}L\right) \times \left(\frac{Cscn}{Cs + Cscn}\right)$$

なる関係を満たしてもよい。

### [0184]

上記関係式により、第2スイッチトランジスタのオフ電圧(第2制御電圧)VscnL および第2ゲート電極と第5電極とで形成される寄生容量Cscnを選択することにより 、画素回路の設計パラメータの自由度が大きくなる。

### [0185]

また、本発明の一態様に係る表示装置は、複数の表示画素が行列状に配置された表示部 を有する表示装置であって、前記複数の表示画素に駆動電圧を供給するための駆動電源線 と、画素列に対応して配置され、映像信号を反映したデータ電圧を前記複数の表示画素へ 伝達する複数のデータ線とを備え、前記複数の表示画素の各々は、発光素子と、前記デー 夕電圧に対応した電圧を保持するための容量素子と、前記電圧がゲート・ソース間に印加 されることにより当該電圧に応じた電流を前記発光素子に流す駆動トランジスタと、第1 ゲート電極、第2電極および第3電極を有し、前記第2電極が前記駆動電源線に接続され 、 前 記 第 3 電 極 が 前 記 駆 動 ト ラ ン ジ ス タ の ソ ー ス お よ び ド レ イ ン の 一 方 に 接 続 さ れ 、 前 記 駆 動 電 源 線 と 前 記 駆 動 ト ラ ン ジ ス タ の 導 通 お よ び 非 導 通 を 切 り 換 え る 第 1 ス イ ッ チ ト ラ ン ジスタと、第 2 ゲート電極、第 4 電極および第 5 電極を有し、前記第 4 電極が前記複数の デ ー タ 線 の う ち 対 応 す る デ ー タ 線 に 接 続 さ れ 、 前 記 第 5 電 極 が 前 記 容 量 素 子 に 接 続 さ れ 、 前 記 デ ー タ 線 と 前 記 容 量 素 子 と の 導 通 お よ び 非 導 通 を 切 り 換 え る 第 2 ス イ ッ チ ト ラ ン ジ ス タとを備え、前記表示装置は、さらに、前記第1スイッチトランジスタを非導通状態かつ 前 記 第 2 ス イ ッ チ ト ラ ン ジ ス タ を 導 通 状 態 と す る こ と に よ り 前 記 容 量 素 子 に 前 記 デ ー タ 電 圧 を 書 込 む 書 込 み ス テ ッ プ と 、 前 記 第 1 ス イ ッ チ ト ラ ン ジ ス タ を 導 通 状 態 か つ 前 記 第 2 ス イッチトランジスタを非導通状態とすることにより当該電圧に応じた電流を前記発光素子 に流す発光ステップとを実行する制御部とを備え、前記駆動トランジスタは、ゲート電極 と前記ソースおよびドレインの一方とで形成された第5寄生容量と、前記ゲート電極とソ ースおよびドレインの他方とで形成された第 6 寄生容量とを有し、前記第 5 寄生容量が前 記第6寄生容量よりも小さくなるよう形成されていることを特徴とする。

### [0186]

本態様によれば、発光期間開始時において、駆動トランジスタのソースおよびドレインの一方からゲートへの電荷突抜け量を小さくすることが可能となる。よって、駆動トランジスタのゲートの電位は、データ書込み完了時における上記ソースおよびドレインの一方の電位変動の影響を受けず、正確なデータ電圧を反映した電位となる。よって、全階調範囲における書込み電圧の変動が抑制され、表示パネルの輝度ムラを抑制できる。

# [0187]

また、前記制御部は、さらに、前記書込みステップの前に、前記駆動トランジスタのゲートに参照電圧を印加した状態で、かつ前記第1スイッチトランジスタを導通状態かつ前記第2スイッチトランジスタを非導通状態とすることにより前記容量素子に前記駆動トランジスタの閾値電圧を保持させる閾値電圧検出ステップを実行してもよい。

# [0188]

これにより、データ書込み前に、駆動トランジスタの閾値電圧が容量素子に書き込まれるので、駆動トランジスタの特性を考慮した書込み動作が可能となり、輝度ムラをより抑制することが可能となる。

# [0189]

また、前記複数の表示画素の各々は、さらに、前記参照電圧を伝達する参照電源線と前記容量素子との導通および非導通を切り換える第3スイッチトランジスタを備えてもよい

10

20

30

40

50

20

30

40

50

### [0190]

これにより、駆動トランジスタのゲート電極に印加される参照電圧を、他の電源線および信号線から独立して制御出来るので、より精度よく閾値電圧を容量素子に書込むことが可能となり、輝度ムラをより抑制することが可能となる。

# [0191]

また、前記複数の表示画素の各々は、さらに、初期化電圧を伝達する初期化電源線と前 記容量素子との導通および非導通を切り換える第4スイッチトランジスタを備え、前記制 御 部 は 、 前 記 第 1 ス イ ッ チ ト ラ ン ジ ス タ お よ び 前 記 第 2 ス イ ッ チ ト ラ ン ジ ス タ を 非 導 通 状 態 か つ 前 記 第 3 ス イ ッ チ ト ラ ン ジ ス タ お よ び 前 記 第 4 ス イ ッ チ ト ラ ン ジ ス タ を 導 通 状 態 と することにより、前記駆動トランジスタを導通状態とすることで初期化期間を開始する初 期 化 ス テ ッ プ と 、 前 記 第 1 ス イ ッ チ ト ラ ン ジ ス タ お よ び 前 記 第 3 ス イ ッ チ ト ラ ン ジ ス タ を 導 通 状 熊 か つ 前 記 第 2 ス イ ッ チ ト ラ ン ジ ス タ を 非 導 通 状 熊 と す る こ と に よ り 前 記 容 量 素 子 に前記駆動トランジスタの閾値電圧を保持させる前記閾値電圧検出ステップと、前記閾値 電圧検出ステップの後、前記第1スイッチトランジスタおよび前記第3スイッチトランジ スタを非導通状態かつ前記第2スイッチトランジスタを導通状態とすることにより前記容 量 素 子 に 前 記 デ ー タ 電 圧 を 書 込 む 前 記 書 込 み ス テ ッ プ と 、 前 記 発 光 ス テ ッ プ と 、 前 記 閾 値 電 圧 検 出 ス テ ッ プ の 終 了 時 点 と 前 記 書 込 み ス テ ッ プ の 終 了 時 点 と の 間 に 、 前 記 駆 動 ト ラ ン ジ ス タ の 前 記 ソ ー ス お よ び ド レ イ ン の 一 方 の 電 位 と ソ ー ス お よ び ド レ イ ン の 他 方 の 電 位 と が同電位となるまで、前記ソースおよびドレインの一方に蓄積されている電荷を前記ソー スおよびドレインの他方へと引き抜く電荷引き抜きステップとを実行し、前記初期化ステ ップの前に前記第1スイッチトランジスタ、前記第2スイッチトランジスタ、前記第3ス イッチトランジスタおよび前記第 4 スイッチトランジスタのうち前記第 4 スイッチトラン ジスタのみを導通状態に切り換えることで第1期間を開始し、前記第3スイッチトランジ スタを導通状態に切り換えることで前記第1期間に続く前記初期化期間を開始してもよい

### [0192]

これにより、短期間に駆動トランジスタのソース電位を初期化することが出来るので、 表示パネルのサイズが大きい場合でも高精度な画像表示を可能とする駆動方法および表示 装置を実現することができる。

# [0193]

また、前記初期化電源線は、前記駆動電源線および前記参照電源線と直交する方向に配置されていてもよい。

### [0194]

これにより、初期化電源線の配線幅を太くすることができるので、初期化電源線の配線 遅延を少なくでき、より早く駆動トランジスタのソース電位を安定させることが可能となる。

# [0195]

また、前記制御部は、さらに、前記第1期間前に、前記第1スイッチトランジスタを非導通に切り換えることで、前記発光素子を発光させる期間を終了させて、前記第1スイッチトランジスタ、前記第3スイッチトランジスタおよび前記第4スイッチトランジスタが非導通状態に切り換えられた第2期間を開始し、前記第4スイッチトランジスタを導通状態に切り換えることで前記第2期間に続く前記1期間を開始してもよい。

# [0196]

これにより、駆動トランジスタのソース電位を発光素子の発光時電圧 閾値電圧分だけ低くできるので、初期化電源線と参照電源線による充放電作業の負荷を軽くすることが可能となる。

# [0197]

また、本発明は、このような特徴的な手段を備える表示装置として実現することができるだけでなく、表示装置に含まれる特徴的な手段をステップとする表示装置の駆動方法と

して実現することができる。

### [0198]

以下、適宜図面を参照しながら、実施の形態を詳細に説明する。但し、必要以上に詳細な説明は省略する場合がある。例えば、既によく知られた事項の詳細説明や実質的に同一の構成に対する重複説明を省略する場合がある。

## [0199]

なお、発明者らは、当業者が本開示を十分に理解するために添付図面および以下の説明を提供するのであって、これらによって特許請求の範囲に記載の主題を限定することを意図するものではない。

# [0200]

(実施の形態1)

以下、実施の形態1に係る表示装置およびその駆動方法について、図面を参照しながら 説明する。

# [ 0 2 0 1 ]

[1-1.表示装置の全体構成]

本実施の形態に係る表示装置の全体構成は、図1に示された表示装置1と同様の構成であるため、ここでは、説明を省略する。

### [0202]

[ 1 - 2 . 画素回路構成およびスイッチ制御]

本実施の形態に係る表示装置の画素回路構成は、図2Aに示された画素20の回路構成と同様の構成であるため、ここでは、詳細な説明を省略する。

#### [0203]

本実施の形態に係る表示装置1は、複数の画素20が行列状に配置された表示部2を有する。また、表示装置1は、複数の画素20にELアノード電圧Vtftを供給するためのELアノード電源線21と、画素列に対応して配置され、映像信号を反映したデータ電圧Vdataを複数の画素20へ伝達する複数のデータ線25とを備える。

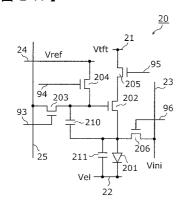

### [0204]

画素 2 0 は、有機 E L 素子 2 0 1 と、データ電圧 V d a t a に対応した電圧を保持するための容量素子 2 1 0 と、容量素子 2 1 0 に保持された電圧がゲート・ソース間に印加されることにより当該電圧に応じた電流を有機 E L 素子 2 0 1 に流す駆動トランジスタ 2 0 2 と、スイッチ 2 0 3 ~ 2 0 6 を備える。

# [0205]

スイッチ 2 0 5 は、ゲート電極(第 1 ゲート電極)、ドレイン電極(第 2 電極)および ソース電極(第 3 電極)を有し、ドレイン電極が E L アノード電源線 2 1 (第 1 駆動電源 線)に接続され、ソース電極が駆動トランジスタ 2 0 2 のドレイン電極に接続されている 。スイッチ 2 0 5 は、E L アノード電源線 2 1 と駆動トランジスタ 2 0 2 との導通および 非導通を切り換える第 1 スイッチトランジスタである。

### [0206]

スイッチ 2 0 3 は、ゲート電極(第 2 ゲート電極)、ドレイン電極(第 4 電極)および ソース電極(第 5 電極)を有し、ドレイン電極がデータ線 2 5 に接続され、ソース電極が 容量素子 2 1 0 の第 1 電極に接続されている。スイッチ 2 0 3 は、データ線 2 5 と容量素 子 2 1 0 との導通および非導通を切り換える第 2 スイッチトランジスタである。

# [0207]

スイッチ 2 0 4 は、ドレイン電極が参照電源線 2 4 に接続され、ソース電極が容量素子 2 1 0 の第 1 電極に接続されている。スイッチ 2 0 4 は、参照電圧 V r e f を伝達する参照電源線 2 4 と容量素子 2 1 0 との導通および非導通を切り換える第 3 スイッチトランジスタである。

# [0208]

スイッチ 2 0 6 は、ドレイン電極が初期化電源線 2 3 に接続され、ソース電極が容量素子 2 1 0 の第 2 電極に接続されている。スイッチ 2 0 6 は、初期化電圧 V i n i を伝達す

10

20

30

40

20

30

40

50

る 初 期 化 電 源 線 2 3 と 容 量 素 子 2 1 0 と の 導 通 お よ び 非 導 通 を 切 り 換 え る 第 4 ス イ ッ チ ト ラン ジ ス タ で あ る 。

[0209]

表示装置1は、さらに、スイッチ205および204を導通状態かつスイッチ203を非導通状態とすることにより容量素子210に駆動トランジスタ202の閾値電圧Vthを保持させる期間である閾値電圧検出期間(T24)と、スイッチ205を非導通状態かつスイッチ203を導通状態とすることにより容量素子210にデータ電圧Vdataを書込む期間である書込み期間(T27)と、スイッチ205を導通状態かつスイッチ203を非導通状態とすることにより当該電圧に応じた電流を有機EL素子201に流す期間である発光期間(T29)とを実行する制御回路60を備える。

[0210]

ここで、スイッチ 2 0 5 は、書込み期間(T 2 7 )において、ソース電極からゲート電極への電荷突抜けにより駆動トランジスタ 2 0 2 のドレイン電極の電位を低下させる。

[0211]

より具体的には、制御回路60は、書込み期間(T27)において、ELカソード電圧 Velから所定値だけ小さい電圧よりもさらに小さい第1制御電圧をゲート電極に印加することにより、スイッチ205を非導通状態とする。

[0212]

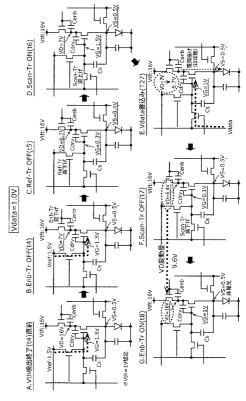

本実施の形態に係る表示装置のスイッチ制御について、図2Bおよび図7Aを用いて説明する。

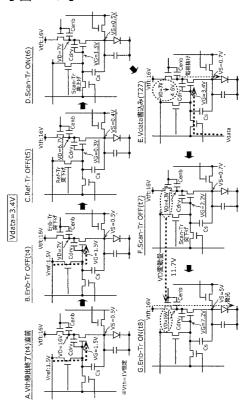

[0213]

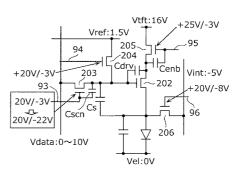

図7Aは、実施の形態1に係る画素回路のスイッチ制御を説明する回路図である。本実施の形態に係る表示装置の駆動シーケンスについては、図2Bに示されたT21~T30が実行される。ここで、制御回路60は、スイッチ205のゲート電極に印加されるオン/オフ電圧を、25V/・17Vとしている。なお、本実施の形態において、データ電圧Vdataの電圧範囲は、0V(最低階調)~10V(最高階調)であり、ELアノード電圧Vtftは16V、ELカソード電圧Velは0Vである。

[0214]

従来の画素回路のスイッチにおけるオン/オフ電圧は、スイッチング時のゲート電位の変動による突上げおよび突下げにより各ノードの電位が変動してしまうことを回避するため、データ電圧Vdataの電圧範囲、および、画素回路内の各ノードの駆動電圧の範囲に対して所定値を加算した範囲に設定されている。この観点から、従来の駆動方法によるオフ電圧は、例えば、25V/・3Vである。ここで、従来の駆動方法によるオフ電圧は、発光期間の終了時(t9)において、駆動トランジスタのドレインノードが取り得る電位の最小値、すなわち、ELカソード電圧Vel(0V)から所定値(3V)だけ小さい電圧に設定されている。これによれば、スイッチ205のドレイン電極およびソース電極の一方にELアノード電圧に相当する電圧が、他方にELカソード電圧に相当する電圧が印加されていても、ゲート電位により、確実にスイッチ205を非導通状態とし、有機EL素子201に電流が流れない様にして、発光期間を終了させることが出来る。

[0215]

ここで、スイッチ 2 0 5 のオフ電圧が - 3 Vである場合について、ドレイン電位 V D の 突下げ電圧 V D d を求める。スイッチ 2 0 5 の閾値電圧 V t h e n b を 1 V、 V t f t = 1 6 V とする。この場合、スイッチ 2 0 5 が非導通状態となるのは、スイッチ 2 0 5 のゲート電位が 2 5 V から 1 7 V ( V t f t + V t h e n b ) まで下がった時である。その後、スイッチ 2 0 5 のゲート電位が 1 7 V ~ - 3 V までは、スイッチ 2 0 5 が非導通状態であり、駆動トランジスタ 2 0 2 のドレインノードはフローティングとなり、スイッチ 2 0 5 の寄生容量 C e n b の影響を受けて、ドレイン電位 V D が低下する (突下げ)。ここで、突下げ電圧 V D d は、以下の式 2 で求められる。

[0216]

### 【数4】

$$VDd = (V_{tft} + Vth_{enb} - V_{enb}L) \times \left(\frac{Cenb}{Cenb + Cdrv}\right)$$

(£2)

### [0217]

上記式 2 は、スイッチ 2 0 5 の非導通状態におけるゲート電極の電圧変化量が、 Cenbe かんして駆動トランジスタ 2 0 2 のドレイン電極へ突抜ける電圧変化量を表している。式 2 に、  $Vth_{enb}=1$  V、 Vtft=1 6 V、  $V_{enb}$  L=-3 V、 Cenb=0 . 0 4 6 p F、 Cdrv=0 . 0 5 6 p F を代入すると、 V Dd=9 . 2 V となる。つまり、データ書込み開始時には、ドレイン電位 V D=1 6 V - 9 . 2 V = 6 . 8 V 程度となっている。

# [0218]

これに対して、本実施の形態では、スイッチ205のゲート電極に印加されるオフ電圧(第1制御電圧)は、-17Vに設定されている。つまり、本実施の形態に係る駆動方法によるスイッチ205のオフ電圧は、ELカソード電圧Ve1(0V)から所定値(3V)だけ小さい電圧よりもさらに小さい電圧が設定されている。つまり、図2Bの駆動シーケンスにおける書込み期間を含む期間(時刻t4~t7)において、例えば、走査線駆動回路50から発光制御線95に-17Vのオフ電圧を印加することにより、駆動トランジスタ202のドレインプードに、スイッチ205のゲート電極から駆動トランジスタ202のドレインノードに、スイッチ205のゲート電極から駆動トランジスタ202のドレインリードに、又イッチ205の大きな電荷突抜けが発生する。式2に、Vthenb=1V、tft=16V、Venb=17V、Cenb=0.046pF、Cdrv=0.056pFを代入すると、VDd=15.7Vとなる。つまり、データ書込み開始時にはぼりしくなっている。つまり、書込み期間に書き込まれるデータ電圧Vdataの大きさにでで低いている。

# [0219]

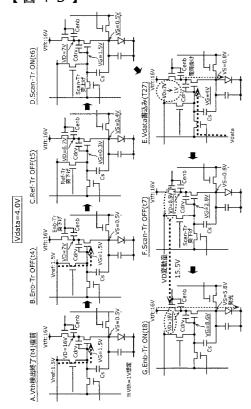

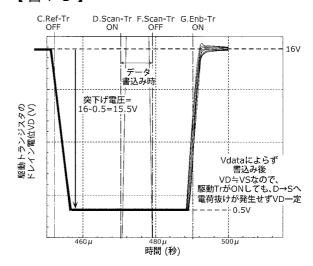

図 7 B は、実施の形態 1 に係るスイッチ制御による駆動トランジスタのドレイン電位の時間変化を表すグラフである。また、図 7 C は、従来のスイッチ制御による駆動トランジスタのドレイン電位の時間変化を表すグラフである。

# [0220]

図7Bに示すように、スイッチ205が非導通状態となる時刻t4から、スイッチ20 5 の突下げ現象により、ドレイン電位 V D はソース電位 V S と同じ電位まで低下する。こ のとき、スイッチ205の非導通によるドレイン電位VDの突下げ量は、16V-0.5 V=15.5Vであり、前述のVDd=15.7Vとほぼ等しい(若干の違いはシミュレ ーションパラメータの誤差によるものである)。これにより、 その後、データ電圧 V d a taが書き込まれても、駆動トランジスタ202のドレイン電極からソース電極への電荷 放電は発生せず、データ電圧の大きさによらずドレイン電位VDは所定の低電位(0.5 V)を保っている。よって、時刻t7において、スイッチ205が導通状態となったとき 、VD変動量はデータ電圧によらず一定( VD=15.5V)となる。つまり、スイッ チ 2 0 5 が 非 導 通 状 態 で あ る 書 込 み 期 間 に お い て 、 駆 動 ト ラ ン ジ ス タ 2 0 2 の ド レ イ ン に 蓄積された電荷を、スイッチ205の寄生容量Cenbを介して、スイッチ205のゲー ト電極へと突抜けさせて、ドレイン電位VDとソース電位VSとをほぼ同じ電位にするこ とが可能となる。よって、駆動トランジスタ202のドレイン電極からソース電極への電 荷 放 電 は 発 生 せ ず 、 駆 動 ト ラ ン ジ ス タ 2 0 2 の ド レ イ ン 電 位 V D は 、 デ ー タ 書 込 み 完 了 時 において、データ電圧の大きさによらず一定電位となる。よって、全階調範囲において書 込み電圧の変動が抑制され、表示パネルの輝度ムラを抑制できる。

# [0221]

10

20

30

20

30

40

50

一方、図7Cに示すように、従来のスイッチ制御によれば、データ書込み前における、スイッチ205の非導通によるドレイン電位VDの突下げ量VDdは、16V-7V=9Vであり、ドレイン電位VDとソース電位VSとの間に電位差が生じる。このため、その後の書込み期間において、データ電圧の大きさにより駆動トランジスタ202のドレイン電極からソース電極への電荷放電が発生し、ドレイン電位が変動するため、階調特性に歪みが生じてしまう。

- [0222]

- [ 1 3 . 駆動方法]

また、本実施の形態に係る表示装置の駆動方法は、以下のステップを実行する。

[0223]

まず、スイッチ 2 0 5 を非導通状態かつスイッチ 2 0 3 を導通状態とすることにより容量素子 2 1 0 にデータ電圧 V d a t a を書込む(書込みステップ)。

[0224]

次に、スイッチ205を導通状態とすることによりデータ電圧Vdataに応じた電流を有機EL素子201に流す(発光ステップ)。

[ 0 2 2 5 ]

ここで、上記書込みステップでは、スイッチ 2 0 5 を非導通状態にし、駆動トランジスタのドレイン電極からスイッチ 2 0 5 のゲート電極への電荷突抜けにより駆動トランジスタのドレイン電極の電位を低下させる(電荷突抜けステップ)。

[0226]

上記駆動方法によれば、容量素子210のへ書込み電圧を変動させる要因である駆動トランジスタ202のドレイン電極に対して、スイッチ205のオフ時の電荷突抜け量を発生させることにより電位を低下させる。これにより、書込みステップにおける駆動トランジスタ202のドレイン電極からソース電極への電荷放電を抑制し、発光ステップにおける駆動トランジスタ202のドレインからゲートへの突抜け電圧のデータ電圧依存性を低減できる。よって、全階調範囲において書込み電圧の変動が抑制され、表示パネルの輝度ムラを抑制できる。

- [ 0 2 2 7 ]

- [1-4.変形例1]

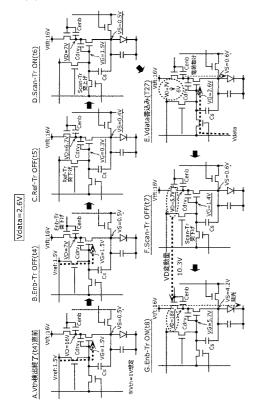

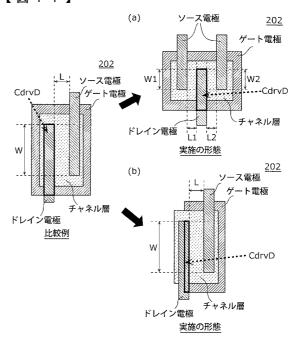

上記実施の形態では、スイッチ 2 0 5 のオフ電圧を低電位に設定することにより駆動トランジスタ 2 0 2 のドレイン電極からスイッチ 2 0 5 のゲート電極への電荷突抜け量を大きくした。これにより、ドレイン電位 V Dをソース電位 V S 程度まで低減させ、書込み終了時から発光開始時までのレイン電圧の変化量 V Dを、データ電圧によらず一定とした。これに対して、本変形例では、スイッチ 2 0 5 のオフ電圧を低電位に設定する代わりに、スイッチ 2 0 5 の容量構成によりドレイン電位 V Dを低減させる。

[0228]

本変形例に係るスイッチ 2 0 5 は、ゲート電極とドレイン(第 2 電極)とで形成された第 1 寄生容量と、ゲート電極とソース電極(第 3 電極)とで形成された第 2 寄生容量( C e n b )とを有し、第 2 寄生容量が第 1 寄生容量よりも大きくなるよう形成されている。 【 0 2 2 9 】

上記第 1 寄生容量および第 2 寄生容量( C e n b )は、通常は同じ静電容量を有し、例えば、第 1 寄生容量 = 第 2 寄生容量( C e n b ) = 0 . 0 4 6 p F である。これに対して、本変形例では、第 2 寄生容量( C e n b )を 0 . 2 p F まで大きくする。式 2 に、 V t h e n b = 1 V 、 V t f t = 1 6 V 、 V e n b L = -3 V 、 C e n b = 0 . 2 p F 、 C d r v = 0 . 0 5 6 p F を代入すると、 V D d = 1 5 . 6 V となる。つまり、実施の形態 1 のように、スイッチ 2 0 5 のオフ電圧を - 1 7 V まで低くする代わりに、第 2 寄生容量( C e n b )を大きくする。

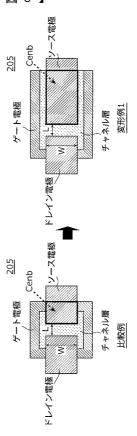

[0230]

図8は、実施の形態の変形例1に係るスイッチの構成を表す概略平面図である。同図の左側に示される平面図は、比較例に係るスイッチ205の電極構成を表し、右側に示され

る平面図は本変形例に係るスイッチ205の電極構成を表す。同図の右側に示すように、例えば、ソース電極の電極長さを大きくすることによりソース電極とゲート電極との重複面積を増加させ、寄生容量Cenbを増大させることが可能となる。

# [ 0 2 3 1 ]

本変形例のスイッチ構成により、スイッチ205が非導通状態である書込み期間において、駆動トランジスタ202のドレイン電極からスイッチ205のゲート電極への電荷突抜け量を大きくすることが可能となる。よって、駆動トランジスタ202のドレイン電位VDは、データ書込み完了時において、データ電圧の大きさによらず一定電位となる。よって、全階調範囲において書込み電圧の変動が抑制される。

# [0232]

なお、スイッチ205は、スタガ型または逆スタガ型構造を有することが好ましい。これにより、スイッチ205において、ゲート電極が構成要素となって形成される第2寄生容量(Cenb)を大きく確保することが容易になる。よって、駆動トランジスタ202のドレイン電極からスイッチ205のゲート電極への電荷突抜け量を大きくすることが可能となる。

### [0233]

以上より、上記式2で表されるドレイン電位 V D の突下げ電圧 V D d により、データ書込み期間において、ドレイン電位 V D がソース電位 V S とほぼ等しくなればよいという観点から、以下の式3が成立する。また式3 は、式4のように表すことができる。この式4を満たすようなスイッチ205のオフ電圧(第1制御電圧) V e n b L および第2寄生容量 C e n b を選択すればよい。

### [ 0 2 3 4 ]

### 【数5】

$$VD - VDd = VS \tag{式 3}$$

# 【数6】

$$V_{tft} - \left(V_{ref} - Vth_{drv}\right) = \left(V_{tft} + Vth_{enb} - V_{enb}L\right) \times \left(\frac{Cenb}{Cenb + Cdrv}\right) \quad (\sharp \downarrow 4)$$

### [0235]

上記式 4 により、スイッチ 2 0 5 のオフ電圧(第 1 制御電圧) V <sub>e n b</sub> L および第 2 寄生容量 C e n b を選択することにより、画素回路の設計パラメータの自由度が大きくなる

# [ 0 2 3 6 ]

### 「1-5.変形例2]

なお、図1に示すように、表示部2における画素20の配置により、画素20と走査線駆動回路50との距離が異なる。これにより、スイッチ205のゲート電極に印加される第1制御信号は、第1駆動回路である走査線駆動回路50に近い画素20では、ほぼ走査線駆動回路50の出力波形そのままの信号が入力されるが、表示部中央の画素20 表示部右端の画素20へと向かうにつれ、信号波形は鈍ってゆく。信号波形が鈍るほど、スイッチ205の非導通時の突下げ電圧量が減少する。このため、表示部上の位置により、画素20ごとに階調特性の歪みの改善度合いが変わってしまうことが起こり得る。

# [0237]

上記観点から、本変形例に係るスイッチ 2 0 5 は、表示部 2 内のスイッチ 2 0 5 の非導通時の突下げ電圧を均一化するために、第 2 寄生容量( C e n b )に対して表示部 2 内での分布を持たせる構成とする。

### [0238]

図9は、実施の形態の変形例2に係るスイッチの構成を表す概略平面図である。同図に示すように、走査線駆動回路50に近い画素20のスイッチ205ほど第2寄生容量(C

10

20

30

40

e n b ) を小さくし、遠い画素 2 0 のスイッチ 2 0 5 ほど第 2 寄生容量( C e n b ) を大きくする。

# [0239]

これにより、スイッチ205の非導通時における突下げ電圧を、表示部内で均一化することが可能となる。よって、全階調範囲において書込み電圧の変動が抑制され、表示パネルの輝度ムラを抑制できる。

### [0240]

(実施の形態2)

以下、実施の形態 2 に係る表示装置およびその駆動方法について、図面を参照しながら説明する。本実施の形態に係る表示装置は、実施の形態 1 に係る表示装置がスイッチ 2 0 5 の電荷突抜け量を大きくさせる構成を有しているのに対して、スイッチ 2 0 3 の電荷突抜け量を大きくさせる構成を有する。以下、実施の形態 1 と同じ構成は説明を省略し、実施の形態 1 と異なる点を中心に説明する。

# [ 0 2 4 1 ]

[2-1.表示装置の全体構成]

本実施の形態に係る表示装置の全体構成は、図1に示された表示装置1と同様の構成であるため、ここでは、説明を省略する。

### [ 0 2 4 2 ]

[ 2 - 2 . 画素回路構成およびスイッチ制御]

本実施の形態に係る表示装置の画素回路構成は、図2Aに示された画素20の回路構成と同様の構成であるため、ここでは、詳細な説明を省略する。

#### [0243]

スイッチ 2 0 3 は、ゲート電極 (第 2 ゲート電極)、ドレイン電極 (第 4 電極) および ソース電極 (第 5 電極) を有し、ドレイン電極がデータ線 2 5 に接続され、ソース電極が 容量素子 2 1 0 の第 1 電極に接続されている。スイッチ 2 0 3 は、データ線 2 5 と容量素 子 2 1 0 との導通および非導通を切り換える第 2 スイッチトランジスタである。

### [0244]

さらに、本実施の形態に係る表示装置は、スイッチ 2 0 5 を非導通状態かつスイッチ 2 0 3 を導通状態とすることにより容量素子 2 1 0 にデータ電圧 V d a t a を書込む期間である書込み期間(T27)と、スイッチ 2 0 5 を導通状態かつスイッチ 2 0 3 を非導通状態とすることにより当該電圧に応じた電流を有機 E L 素子 2 0 1 に流す期間である発光期間(T29)とを実行する制御回路 6 0 を備える。

### [0245]

ここで、スイッチ 2 0 3 は、書込み期間の終了時において、ソース電極からゲート電極への電荷突抜けにより駆動トランジスタ 2 0 2 のゲート電極の電位を低下させる。これにより、書込み電圧である駆動トランジスタのゲート・ソース間電圧 V g s は低電位側へシフトする。このため、階調特性の歪みが発生する領域は、階調特性の歪みが目立たない低階調側へと移動するので、輝度ムラが視認され易い中階調以上での書込み電圧の変動が抑制される。

### [0246]

より具体的には、制御回路 6 0 は、書込み期間の終了時において、データ電圧 V d a t a の電圧範囲の下限電圧値から所定値だけ小さい電圧よりもさらに小さい第 2 制御電圧をゲート電極に印加することにより、スイッチ 2 0 3 を非導通状態とする。

# [0247]

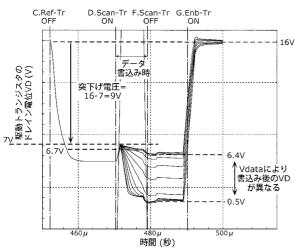

本実施の形態に係る表示装置のスイッチ制御について、図2B、図10Aおよび図10 Bを用いて説明する。

### [0248]

図10Aは、実施の形態 2 に係る画素回路のスイッチ制御を説明する回路図である。また、図10Bは、遷移領域を非発光領域へシフトさせた階調特性を表すグラフである。本実施の形態に係る表示装置の駆動シーケンスについては、図2Bに示されたT21~T

10

20

30

40

10

20

30

40

50

3 0 が実行される。ここで、制御回路 6 0 は、スイッチ 2 0 3 のゲート電極に印加されるオン / オフ電圧を、 2 0 V / - 2 2 V としている。なお、本実施の形態において、データ電圧 V d a t a の電圧範囲は、 0 V (最低階調) ~ 1 0 V (最高階調)であり、 E L ア / ード電圧 V t f t は 1 6 V である。

## [0249]

従来の画素回路のスイッチにおけるオン/オフ電圧は、スイッチング時のゲート電位による突上げおよび突下げにより各ノードの電位が変動してしまうことを回避するため、データ電圧Vdataの電圧範囲、および、駆動電圧の範囲に対して所定値を加算した範囲に設定されている。この観点から、従来の駆動方法によればスイッチ203のゲート電極に印加されるオン/オフ電圧は、例えば、20V/・3Vである。ここで、従来の駆動方法によるオフ電圧は、データ電圧の最小電圧(0V)から所定値(3V)だけ小さい電圧に設定されている。これによれば、スイッチ203のドレイン電極またはソース電極にデータ電圧の最小電圧(0V)に相当する電圧が印加されていても、ゲート電位により、確実にスイッチ203を非導通状態とし、データ線25と容量素子210間に電流が流れない様にして、当該電圧が変動することを回避できる。

#### [0250]

ここで、スイッチ203のオフ電圧が・3Vである場合について、ゲート電位VGの突下げ電圧VGdを求める。スイッチ203の閾値電圧Vth<sub>scn</sub>を1V、図10Bの右側のグラフに示されるように遷移領域と安定領域とのの境界となるデータ電圧Vdata=4.0Vとする。このとき、スイッチ203が非導通状態となるのは、スイッチ203のゲート電位(第2制御電圧)が20Vから5V(Vdata+Vth<sub>scn</sub>)まで下がった時である。その後、スイッチ203のゲート電位が5V~・3Vまでは、スイッチ203が非導通状態であり、駆動トランジスタ202のゲートノードはフローティングとなり、スイッチ203の寄生容量Cscnの影響を受けて、ゲート電位VGが低下する(突下げ)。ここで、突下げ電圧VGdは、以下の式4で求められる。

[0251]

### 【数7】

$$VGd = (Vdata + Vth_{scn} - V_{scn}L) \times \left(\frac{Cscn}{Cs + Cscn}\right)$$

(£5)

# [ 0 2 5 2 ]

上記式 5 は、スイッチ 2 0 3 の非導通状態におけるゲート電極の電圧変化量が、C s c n を介して駆動トランジスタ 2 0 2 のゲート電極へ突抜けする変化量を表している。式 5 に、V t h e n b = 1 V 、V d a t a = 4 V 、V s c n L = - 3 V 、C s = 0 . 5 p F 、C s c n = 0 . 0 2 5 p F を代入すると、V G d = 0 . 3 8 V となる。つまり、データ書込み終了時には、ゲート・ソース間電圧 V g s が 0 . 3 8 V だけ小さくなることとなる。【 0 2 5 3 】

これに対して、本実施の形態では、スイッチ203のゲート電極に印加されるオフ電圧(第2制御電圧)は、・22Vに設定されている。つまり、本実施の形態に係る駆動方法によるスイッチ203のオフ電圧は、データ電圧の最小電位(0V)から所定値(3V)だけ低い電位よりもさらに低い電位が設定されている。つまり、図2Bの駆動シーケンスにおける書込み期間の終了時(時刻t7~t8)において、例えば、走査線駆動回路50から走査線93に・22Vのオフ電圧を印加することにより、駆動トランジスタ202のゲート電位VGは、いわゆる突下げされる。言い換えると、駆動トランジスタ202のゲートノードからスイッチ203のゲート電極に、スイッチ203の寄生容量Cscnを介して、大きな電荷突抜けが発生する。式5に、Vthscn=1V、Vdata=4V、VscnL=・22V、Cs=0.5pF、Cscn=0.025pFを代入すると、VGd=1.3Vとなる。つまり、データ書込み終了時には、ゲート・ソース間電圧Vgsが1.3V程度小さくなる。

[0254]

0 - 3 . 階調特性の歪み、でも述べたように、歪みが発生する階調は、データ書込み時に駆動トランジスタ202が導通するデータ電圧(約3 . 5 ~ 4 . 0 V付近)で決まるため、歪み発生の階調領域は変わらない。つまり、図10B左側グラフに示された遷移領域は必ず存在する。

[0255]

これに対して、本実施の形態に係るスイッチ制御によれば、階調特性を全体的に低域側にシフトさせて(輝度を低下させて)、歪みが発生する遷移領域を非発光領域に追いやってしまうものである。これにより、歪みが発生する遷移領域は映像表示に使用されなくなるので、ムラは発生しなくなる。

[0256]

上述したように、スイッチ 2 0 3 のオフ電圧を - 2 2 V まで下げて、スイッチ 2 0 3 の 非 導通 時 の 突下 げ 電圧を 大 きくすることにより、 ゲート - ソース 間 電圧 V g s を 1 . 3 V 程 度 小 さくすること が 可能となる。よって、 書込み 電圧の 変動 が 抑制 され、 表示 パネルの 輝 度 ムラを 抑制 できる。

- [ 0 2 5 7 ]

- [2-3.駆動方法]

また、本実施の形態に係る表示装置の駆動方法は、以下のステップを実行する。

[ 0 2 5 8 ]

まず、スイッチ 2 0 5 を非導通状態かつスイッチ 2 0 3 を導通状態とすることにより容量素子 2 1 0 にデータ電圧 V d a t a を書込む(書込みステップ)。

[0259]

次に、スイッチ205を導通状態とすることによりデータ電圧Vdataに応じた電流を有機EL素子201に流す(発光ステップ)。

[ 0 2 6 0 ]

ここで、上記書込みステップの終了時において、スイッチ203を非導通状態にし、駆動トランジスタ202のゲート電極からスイッチ203のゲート電極への電荷突抜けにより駆動トランジスタ202のゲート電極の電位を低下させる(電荷突抜けステップ)。

[0261]

上記駆動方法によれば、容量素子210のへ書込み電圧を変動させる要因である駆動トランジスタ202のゲート電極に対して、スイッチ203のオフ時の電荷突抜け量を発生させることにより電位を低下させる。これにより、駆動トランジスタ202のゲート・ソース間電圧を低域側へシフトできる。よって、書込み電圧の変動が抑制され、表示パネルの輝度ムラを抑制できる。

- [ 0 2 6 2 ]

- 「2-4.変形例1]

上記実施の形態では、スイッチ 2 0 3 のオフ電圧を低電位に設定することにより駆動トランジスタ 2 0 2 のゲート電極からスイッチ 2 0 3 のゲート電極への電荷突抜け量を大きくした。これに対して、本変形例では、スイッチ 2 0 3 のオフ電圧を低電位に設定する代わりに、スイッチ 2 0 3 の容量構成によりゲート電位 V G を低下させる。

[0263]

本変形例に係るスイッチ203は、ゲート電極とドレイン(第4電極)とで形成された 第3寄生容量と、ゲート電極とソース電極(第5電極)とで形成された第4寄生容量(Cscn)とを有し、第4寄生容量が第3寄生容量よりも大きくなるよう形成されている。

[0264]

上記第3寄生容量および第4寄生容量(Cscn)は、通常は同じ静電容量を有し、例えば、第3寄生容量=第4寄生容量(Cscn)=0.025pFである。これに対して、第4寄生容量(Cscn)を0.095pFまで大きくする。式5に、Vth<sub>scn</sub>=1V、Vdata=4V、V<sub>scn</sub>L=-3V、Cs=0.5pF、Cscn=0.095pFを代入すると、VGd=1.3Vとなる。つまり、実施の形態2のように、スイッ

10

20

30

40

50

10

20

40

50

チ 2 0 3 のオフ電圧を - 2 2 V まで低くする代わりに、第 4 寄生容量( C s c n )を大きくする。

[0265]

なお、第4寄生容量(Cscn)を大きくする方法としては、実施の形態1における第2寄生容量(Cenb)を大きくする方法と同様であり、図8を参照することができる。同図の左側に示される平面図を、比較例に係るスイッチ203の電極構成とし、右側に示される平面図は本変形例に係るスイッチ203の電極構成とみなす。同図の右側に示すように、例えば、ソース電極の電極長さを大きくすることによりソース電極とゲート電極との重複面積を増加させ、寄生容量Cscnを増大させることが可能となる。

[0266]

本変形例のスイッチ構成により、スイッチ203が非導通状態である書込み期間の終了時において、駆動トランジスタ202のゲート電極からスイッチ203のゲート電極への電荷突抜け量を大きくすることが可能となる。よって、書込み電圧である駆動トランジスタのゲート・ソース間電圧Vgsは、データ書込み完了時において低電位側へシフトする。このため、階調特性の歪みが発生する領域は階調特性の歪みが目立たない低階調側へと移動するので、書込み電圧の変動が抑制される。

[0267]

なお、スイッチ 2 0 3 は、スタガ型または逆スタガ型構造を有することが好ましい。これにより、スイッチ 2 0 3 において、ゲート電極が構成要素となって形成される第 4 寄生容量(Cscn)を大きく確保することが容易になる。よって、駆動トランジスタ 2 0 2 のゲート電極からスイッチ 2 0 3 のゲート電極への電荷突抜け量を大きくすることが可能となる。

[0268]

以上より、上記式 5 で表されるゲート電位 V G の突下げ電圧 V G d は、データ書込み期間の終了時における駆動トランジスタ 2 0 2 のゲート・ソース間電圧の変動量 V g s である。よって、変動量 V g s は以下の式 6 で表される。

[0269]

【数8】

$$\Delta Vgs = \left(Vdata + Vth_{scn} - V_{scn}L\right) \times \left(\frac{Cscn}{Cs + Cscn}\right)$$

(\$\frac{1}{2}\$)

[0270]

ここで、変動量 Vgsの決定方法を例示する。

[ 0 2 7 1 ]

[0272]

一方、非発光領域と遷移領域との境界となるデータ電圧( V d a t a 2 = 2 V ) におけるゲートソース間電圧 V g s 2 は、トランジスタの特性より、ほぼ V g s 2 = V t h である。

[0273]

以上より、 Vgs=Vgs1-Vgs2を上記の方法で取得することができる。 なお、 Vgsを取得する方法はこれに限らない。 例えば、 SPICEシミュレーションにより計算してもよい。

[0274]

設定すべき Vgsを予め決定しておき、上記式 6を満たすようなスイッチ 203のオフ電圧(第 2 制御電圧) Vscn L および第 4 寄生容量 Cscn を選択すればよい。

#### [0275]

上記式 6 により、スイッチ 2 0 3 のオフ電圧(第 2 制御電圧) V <sub>s c n</sub> L および第 4 寄 生容量 C s c n を選択することにより、画素回路の設計パラメータの自由度が大きくなる

## [0276]

### 「2-5.変形例2]

なお、図1に示すように、表示部2における画素20の配置により、画素20と走査線駆動回路50との距離が異なる。これにより、スイッチ203のゲート電極に印加される第2制御信号は、第2駆動回路である走査線駆動回路50に近い画素20では、ほぼ走査線駆動回路50の出力波形そのままの信号が入力されるが、表示部中央の画素20 表示部右端の画素20へと向かうにつれ、信号波形は鈍ってゆく。信号波形が鈍るほど、スイッチ203の非導通時の突下げ電圧量が減少する。このため、表示部上の位置により、画素20ごとに階調特性の歪みの改善度合いが変わってしまうことが起こり得る。

## [ 0 2 7 7 ]

上記観点から、本変形例に係るスイッチ203は、表示部2内のスイッチ203の非導通時の突下げ電圧を均一化するために、第4寄生容量(Cscn)に対して表示部2内での分布を持たせる構成とする。つまり、走査線駆動回路50に近い画素20のスイッチ203ほど第4寄生容量(Cscn)を小さくし、遠い画素20のスイッチ203ほど第4寄生容量(Cscn)を大きくする。

## [0278]

これにより、スイッチ203の非導通時における突下げ電圧を、表示部内で均一化する ことが可能となる。よって、書込み電圧の変動が抑制され、表示パネルの輝度ムラを抑制 できる。

#### [0279]

### (実施の形態3)

以下、実施の形態 3 に係る表示装置およびその駆動方法について、図面を参照しながら説明する。本実施の形態に係る表示装置は、実施の形態 1 に係る表示装置が発光を制御するためのスイッチ 2 0 5 の電荷突抜け量を大きくさせる構成を有しているのに対して、駆動トランジスタ 2 0 2 のドレイン電極からゲート電極への電荷突抜け量を小さくさせる構成を有する。以下、実施の形態 1 と同じ構成は説明を省略し、実施の形態 1 と異なる点を中心に説明する。

## [0280]

#### [3-1.表示装置の全体構成]

本実施の形態に係る表示装置の全体構成は、図1に示された表示装置1と同様の構成であるため、ここでは、説明を省略する。

## [0281]

#### [ 3 - 2 . 画素回路構成]

本実施の形態に係る表示装置の画素回路構成は、図2Aに示された画素20の回路構成と同様の構成であるため、ここでは、詳細な説明を省略する。

#### [0282]

さらに、本実施の形態に係る表示装置は、スイッチ205を非導通状態かつスイッチ203を導通状態とすることにより容量素子210にデータ電圧Vdataを書込む期間である書込み期間(T27)と、スイッチ205を導通状態かつスイッチ203を非導通状態とすることにより当該電圧に応じた電流を有機EL素子201に流す期間である発光期間(T29)とを実行する制御回路60を備える。

# [0283]

ここで、駆動トランジスタ202は、ゲート電極とドレイン電極とで形成された第5寄生容量(CdrvD)と、ゲート電極とソース電極とで形成された第6寄生容量(CdrvS)よりも小さvS)とを有し、第5寄生容量(CdrvS)よりも小さくなるよう形成されている。

10

20

30

30

\_

40

50

10

20

30

40

50

#### [0284]

図11は、実施の形態3に係る駆動トランジスタの構成を表す概略平面図である。同図の左側には、比較例に係る駆動トランジスタ202の積層レイアウト構造が示されている。比較例に係る構造では、ドレイン電極とゲート電極とで形成される第5寄生容量CdrvDと、ソース電極とゲート電極とで形成される第6寄生容量CdrvSとは、同じ容量値を有している。

#### [0285]

これに対して、右側に示された、本実施の形態に係る駆動トランジスタ202の積層レイアウト構造では、(a)ソース電極とドレイン電極とを櫛形構造とし、ドレイン電極よりもソース電極の本数を多くしている。これにより、第5寄生容量CdrvD<第6寄生容量CdrvSを実現している。また、(b)ドレイン電極とゲート電極との重複面積を低減させる構造とし、第5寄生容量CdrvD<第6寄生容量CdrvSを実現している

## [0286]

以上のように、第5寄生容量CdrvDを、第6寄生容量CdrvSよりも小さくすることで、駆動トランジスタ202のドレイン電位VDの変動をゲート・ソース電圧Vgsに伝播することを低減できる。なお、第5寄生容量CdrvDを、容量素子210の容量Cs+第6寄生容量CdrvSよりも小さくすることが好ましい。

#### [0287]

本実施の形態に係る駆動トランジスタ202の構成によれば、発光期間開始時において、駆動トランジスタ202のドレイン電極からゲート電極への電荷突抜け量を小さくすることが可能となる。よって、駆動トランジスタ202のゲート電位は、データ書込み完了時における上記ドレイン電極の電位変動の影響を受けず、正確なデータ電圧を反映した電位となる。よって、全階調範囲における書込み電圧の変動が抑制され、表示パネルの輝度ムラを抑制できる。

### [0288]

### (その他の実施の形態)

以上、実施の形態 1 ~ 3 に係る表示装置およびその駆動方法について説明したが、本発明表示装置およびその駆動方法は、上述した実施の形態に限定されるものではない。実施の形態 1 ~ 3 およびその変形例に対して、本発明の主旨を逸脱しない範囲で当業者が思いつく各種変形を施して得られる変形例や、実施の形態 1 ~ 3 に係る表示装置のいずれかを内蔵した各種機器も本発明に含まれる。

#### [0289]

また、上記実施の形態1~3およびその変形例では、本発明に係る表示装置が有する画素回路構成の一例を挙げたが、画素20の回路構成は上記回路構成に限定されない。上記実施の形態1~3では、ELアノード電源線21とELカソード電源線22との間に、スイッチ205、駆動トランジスタ202および有機EL素子201が、この順に配置されている構成を例示したが、これらの3素子が異なる順で配置されていてもよい。つまり、本発明の表示装置は、駆動トランジスタがn型であってもp型であっても、駆動トランジスタ202のドレイン電極およびソース電極、ならびに有機EL素子201のアノード電極およびカソード電極が、ELアノード電源線21とELカソード電源線22との間の電流径路上に配置されていればよく、駆動トランジスタ202および有機EL素子201の配置順には限定されない。

# [0290]

また、上記実施の形態では、スイッチ203~206は、ゲート電極、ソース電極およびドレイン電極を有するMOSFETであることを前提として説明してきたが、これらのトランジスタには、ベース、コレクタおよびエミッタを有するバイポーラトランジスタが適用されてもよい。この場合にも、本発明の目的が達成され同様の効果を奏する。

#### [0291]

また、上記実施の形態に係る表示装置に含まれる制御回路および演算回路は、典型的に

は集積回路であるLSIとして実現される。なお、上記表示装置に含まれる制御回路および演算回路の一部を、表示部2と同一の基板上に集積することも可能である。また、専用回路又は汎用プロセッサで実現してもよい。また、LSI製造後にプログラムすることが可能なFPGA(Field Programmable Gate Array)、又はLSI内部の回路セルの接続や設定を再構成可能なリコンフィギュラブル・プロセッサを利用してもよい。

#### [0292]

また、上記実施の形態に係る表示装置に含まれる走査線駆動回路 5 0 、データ線駆動回路 4 0 、および制御回路 6 0 の機能の一部を、 C P U 等のプロセッサがプログラムを実行することにより実現してもよい。

[0293]

また、上記実施の形態 1 ~ 3 およびその変形例に係る表示装置では、有機 E L 素子を用いた表示装置である場合を例に述べたが、有機 E L 素子以外の発光素子を用いた表示装置に適用してもよい。

### [0294]

また、例えば、実施の形態 1 ~ 3 およびその変形例に係る表示装置は、図 1 2 に示されたような薄型フラットTVに内蔵される。上記実施の形態 1 ~ 3 のいずれかに係る表示装置が内蔵されることにより、表示ムラが抑制された高精度な画像表示が可能な薄型フラットTVが実現される。

# 【産業上の利用可能性】

[0295]

本発明は、特に、アクティブ型の有機ELフラットパネルディスプレイに有用である。

### 【符号の説明】

- [0296]

- 1 表示装置

- 2 表示部

- 3 電源部

- 6、6A 表示パネル

- 2 0 画素

- 2 1 E L ア ノ ー ド 電 源 線

- 2 2 E L カソード電源線

- 2 3 初期化電源線

- 2 4 参照電源線

- 2 5 データ線

- 3 0 給電線

- 4 0 データ線駆動回路

- 5 0 走 査 線 駆 動 回 路

- 5 1 ドライバIC

- 5 2 、 5 3 、 5 4 フレキ部分

- 60制御回路

- 9 3 走査線

- 9 4 参照電圧制御線

- 9 5 発光制御線

- 9 6 初期化制御線

- 201 有機 E L 素子

- 2 0 2 駆動トランジスタ

- 203、204、205、206 スイッチ

- 2 1 0 容量素子

- 2 1 1 容量

20

10

30

40

# 【図1】

# 【図2A】

【図2B】

【図3】

【図4A】

# 【図4B】

# 【図4C】

【図4D】

【図5】

## 【図6】

## 【図7A】

# 【図7B】

【図7C】

【図8】

【図9】

## 【図10A】

【図10B】

# 【図11】

【図12】

【図13】

【図14】

## フロントページの続き

(51) Int.CI. F I テーマコード (参考)

G 0 9 G 3/20 6 4 2 P G 0 9 G 3/20 6 4 1 Q

Fターム(参考) 50080 AA06 BB05 DD05 DD09 DD10 EE29 FF11 FF12 HH10 JJ02

JJ03 JJ04 JJ05 JJ06 KK43

5C380 AA01 AB06 AB22 AB46 AC07 BA10 BA19 BA38 BA39 BA40 BB02 CA12 CB01 CC04 CC07 CC26 CC33 CC39 CC41 CC65

CC72 CD025 CE17 CE19 CF23 DA02 DA06 DA47 HA02 HA03

HA05 HA08

| 专利名称(译)        | 显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | JP2016095381A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2016-05-26 |

| 申请号            | JP2014231097                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2014-11-13 |

| [标]申请(专利权)人(译) | 日本有机雷特显示器股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | 株式会社JOLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 戎野浩平<br>小野晋也                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 戎野 浩平<br>小野 晋也                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |