(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-215275

(P2006-215275A)

(43) 公開日 平成18年8月17日(2006.8.17)

(51) Int.C1.

**G09G 3/30** (2006.01)

**G09G 3/20** (2006.01)

**H01L 51/50** (2006.01)

F 1

G09G 3/30 J 3K007

G09G 3/30 K 5C080

G09G 3/20 611H

G09G 3/20 621A

G09G 3/20 624B

テーマコード(参考)

審査請求 未請求 請求項の数 4 O L (全 20 頁) 最終頁に続く

(21) 出願番号

特願2005-28021 (P2005-28021)

(22) 出願日

平成17年2月3日(2005.2.3)

(71) 出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100086841

弁理士 脇 篤夫

(74) 代理人 100114122

弁理士 鈴木 伸夫

(72) 発明者 山本 哲郎

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 内野 勝秀

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

最終頁に続く

(54) 【発明の名称】表示装置

(57) 【要約】 (修正有)

【課題】nチャネルTFTによる画素回路において高品質な画像表示を可能とするとともに、歩留まり向上や画素回路の小型化、高精細化を可能とする。

【解決手段】画素回路は、有機EL素子と、保持容量、サンプリングトランジスタ、ドライブトランジスタ、スイッチングトランジスタ、第1及び第2の検知トランジスタで構成する。ドライブトランジスタの閾値電圧の変動と有機EL素子の経時劣化を補償する保持容量のブーストストラップ機能を備え、有機EL素子のI-V特性経時変化やドライブトランジスタの閾値電圧変動を補償する。その上で、サンプリングトランジスタの導通制御を行う走査線(サンプリングトランジスタのゲートラインWSL)を、第2の検知トランジスタT2を介してドライブトランジスタT5のゲートに与える第2の固定電位VofSの供給ラインとして共用し、第2の固定電位の供給ラインを独立して設ける必要をなくす。

【選択図】図7

**【特許請求の範囲】****【請求項 1】**

信号線と所要数の走査線が交差する部分に形成される画素回路がマトリクス状に配置されて成る表示装置であって、

各画素回路は、有機エレクトロルミネッセンス素子と、保持容量と、サンプリングトランジスタ、ドライブトランジスタ、第1，第2の検知トランジスタ、及びスイッチングトランジスタからなる5個のnチャネル薄膜トランジスタとを備え、

上記ドライブトランジスタのソースとゲートとの間に上記保持容量が接続され、

上記ドライブトランジスタのソースと所定のカソード電位との間に上記有機エレクトロルミネッセンス素子が接続され、

上記ドライブトランジスタのソースと第1の固定電位との間に上記第1の検知トランジスタが接続され、

上記ドライブトランジスタのゲートと第2の固定電位との間に上記第2の検知トランジスタが接続され、

上記ドライブトランジスタのゲートと上記信号線との間に上記サンプリングトランジスタが接続され、

上記ドライブトランジスタのドレインと所定の電源電位との間に上記スイッチングトランジスタが接続され、

上記サンプリングトランジスタ、上記第1，第2の検知トランジスタ、及び上記スイッチングトランジスタは、それぞれ対応する走査線によって導通制御されるように構成されているとともに、

上記サンプリングトランジスタの導通制御を行う走査線が、上記第2の固定電位の供給ラインとされて、該走査線に上記第2の検知トランジスタが接続されていることを特徴とする表示装置。

**【請求項 2】**

上記第2の検知トランジスタは、該第2の検知トランジスタに対応する走査線に与えられる走査パルスによって、上記サンプリングトランジスタが非導通とされている期間に導通されるとともに、

上記サンプリングトランジスタに対応する走査線に与えられる走査パルスのローレベルが、上記第2の固定電位とされていることを特徴とする請求項1に記載の表示装置。

**【請求項 3】**

信号線と所要数の走査線が交差する部分に形成される画素回路がマトリクス状に配置されて成る表示装置であって、

各画素回路は、有機エレクトロルミネッセンス素子と、保持容量と、サンプリングトランジスタ、ドライブトランジスタ、第1，第2の検知トランジスタ、及びスイッチングトランジスタからなる5個のnチャネル薄膜トランジスタとを備え、

上記ドライブトランジスタのソースとゲートとの間に上記保持容量が接続され、

上記ドライブトランジスタのソースと所定のカソード電位との間に上記有機エレクトロルミネッセンス素子が接続され、

上記ドライブトランジスタのソースと第1の固定電位との間に上記第1の検知トランジスタが接続され、

上記ドライブトランジスタのゲートと第2の固定電位との間に上記第2の検知トランジスタが接続され、

上記ドライブトランジスタのゲートと上記信号線との間に上記サンプリングトランジスタが接続され、

上記ドライブトランジスタのドレインと所定の電源電位との間に上記スイッチングトランジスタが接続され、

上記サンプリングトランジスタ、上記第1，第2の検知トランジスタ、及び上記スイッチングトランジスタは、それぞれ対応する走査線によって導通制御されるように構成されているとともに、

10

20

30

40

50

上記サンプリングトランジスタの導通制御を行う走査線が、上記第1の固定電位の供給ラインとされて、該走査線に上記第1の検知トランジスタが接続されていることを特徴とする表示装置。

【請求項4】

上記第1の検知トランジスタは、該第1の検知トランジスタに対応する走査線に与えられる走査パルスによって、上記サンプリングトランジスタが非導通とされている期間に導通されるとともに、

上記サンプリングトランジスタに対応する走査線に与えられる走査パルスのローレベルが、上記第1の固定電位とされていることを特徴とする請求項3に記載の表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、信号線と所要数の走査線が交差する部分に形成される画素回路がマトリクス状に配置されて成る表示装置であって、特に発光素子として有機エレクトロルミネッセンス素子（有機EL素子）を用いた表示装置に関する。

【背景技術】

【0002】

【特許文献1】特開2003-255856

【特許文献2】特開2003-271095

【0003】

有機EL素子を画素に用いた画像表示装置が開発されている。有機EL素子は自発光素子であることから、例えば液晶ディスプレイに比べて画像の視認性が高く、バックライトが不要であり、応答速度が速いなどの利点を有する。又、各発光素子の輝度レベル（階調）はそれに流れる電流値によって制御可能である（いわゆる電流制御型）。

有機ELディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として単純マトリクス方式とアクティブマトリクス方式とがある。前者は構造が単純であるものの、大型且つ高精細のディスプレイの実現が難しいなどの問題がある為、現在はアクティブマトリクス方式の開発が盛んに行なわれている。この方式は、各画素回路内部の発光素子に流れる電流を、画素回路内部に設けた能動素子（一般には薄膜トランジスタ：TFT）によって制御するものである。

【0004】

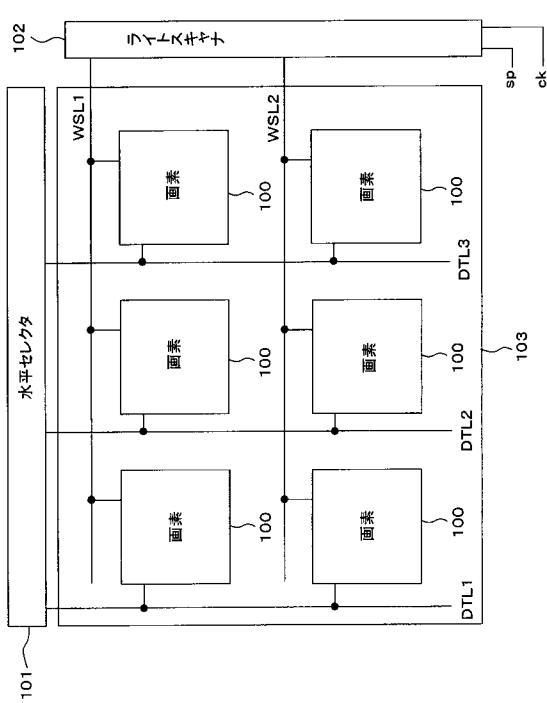

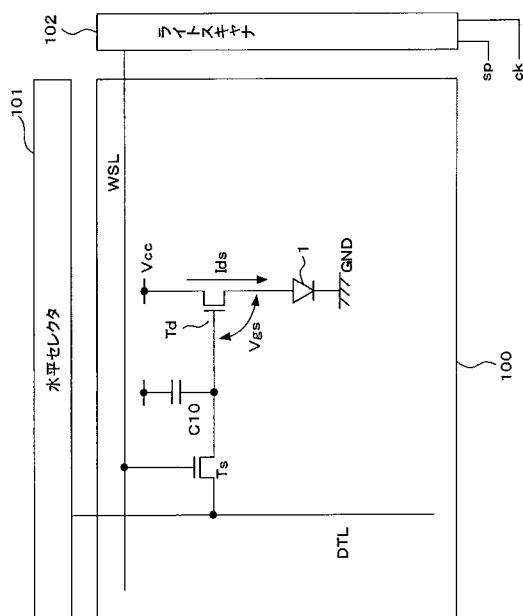

図13に一般的なアクティブマトリクス型有機EL表示装置のブロック図を示す。

この表示装置は、画素回路100が $m \times n$ のマトリクス状に配列された画素アレイ部103、水平セレクタ101、ライトスキャナ102、水平セレクタ101により選択され輝度情報に応じた信号が供給される信号線DTL1、DTL2…、ライトスキャナ102により選択駆動される走査線WSL1、WSL2…を有する。

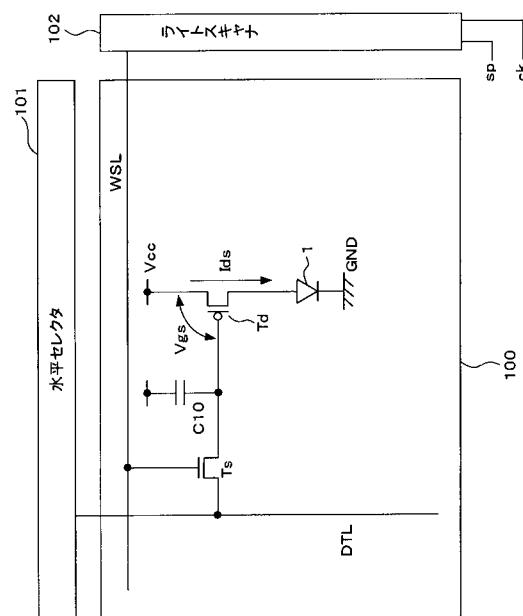

【0005】

図14には、図13に示した画素回路100の最も単純な構成例を示している。図示するように、この画素回路100は、nチャネルTFTによるサンプリングトランジスタTs、保持容量C10、pチャネルTFTによるドライブトランジスタTd、有機EL素子1を有する。この画素回路100は、信号線DTLと走査線WSLとの交差部に配され、信号線DTLはサンプリングトランジスタTsのドレインに接続され、走査線WSLはサンプリングトランジスタTsのゲートに接続されている。

ドライブトランジスタTd及び有機EL素子1は、電源電位Vccと接地電位GNDの間で直列に接続されている。すなわちドライブトランジスタ1のソースが電源電位Vccに接続される一方、有機EL素子（発光素子）1のカソードが接地電位GNDに接続されている。一般に有機EL素子1は整流性がある為ダイオードの記号で表わしている。一方、サンプリングトランジスタTs及び保持容量C10は、ドライブトランジスタTdのゲートに接続されている。ドライブトランジスタTdのゲート・ソース間電圧をVgsで表わしている。

10

20

30

40

50

## 【0006】

この画素回路100では、まず走査線W<sub>S</sub>Lを選択状態とし、信号線D<sub>T</sub>Lに信号を印加すると、サンプリングトランジスタT<sub>S</sub>が導通して信号が保持容量C10に書き込まれる。保持容量C10に書き込まれた信号電位がドライブトランジスタT<sub>d</sub>のゲート電位となる。走査線W<sub>S</sub>Lを非選択状態とすると、信号線D<sub>T</sub>LとドライブトランジスタT<sub>d</sub>とは電気的に切り離されるが、ドライブトランジスタT<sub>d</sub>のゲート電位V<sub>g</sub>sは保持容量C10によって安定に保持される。そして電源電位V<sub>c</sub>cから接地電位GNDに向かって駆動電流がドライブトランジスタT<sub>d</sub>及び有機EL素子1を流れる。

このときドライブトランジスタT<sub>d</sub>及び有機EL素子1に流れる電流I<sub>d</sub>sは、ドライブトランジスタT<sub>d</sub>のゲート・ソース間電圧V<sub>g</sub>sに応じた値となり、有機EL素子1はその電流値に応じた輝度で発光する。10

つまりこの画素回路100の場合、保持容量C10に信号線D<sub>T</sub>Lからの信号電位を各込むことによってドライブトランジスタT<sub>d</sub>のゲート印加電圧を変化させ、これにより有機EL素子1に流れる電流値をコントロールして発色の階調を得る。

## 【0007】

pチャンネルTFTによるドライブトランジスタT<sub>d</sub>のソースは電源V<sub>c</sub>cに接続されており、常に飽和領域で動作するように設計されているので、ドライブトランジスタT<sub>d</sub>は次の式1に示した値を持つ定電流源となる。

$$I_{d}s = (1/2) \cdot \mu \cdot (W/L) \cdot C_{ox} \cdot (V_{gs} - V_{th})^2 \dots \text{ (式1)}$$

但し、I<sub>d</sub>sは飽和領域で動作するトランジスタのドレイン・ソース間に流れる電流、 $\mu$ は移動度、Wはチャネル幅、Lはチャネル長、C<sub>ox</sub>はゲート容量、V<sub>th</sub>はトランジスタの閾値電圧を表している。20

この式1から明らかな様に、飽和領域ではトランジスタのドレイン電流I<sub>d</sub>sはゲート・ソース間電圧V<sub>g</sub>sによって制御される。図14に示したドライブトランジスタT<sub>d</sub>は、V<sub>g</sub>sが一定に保持される為、定電流源として動作し、有機EL素子1を一定の輝度で発光させることができる。

## 【0008】

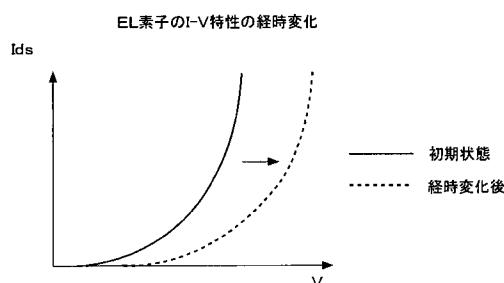

ここで図15に、有機EL素子の電流-電圧(I-V)特性の経時変化を示す。実線で示す曲線が初期状態時の特性を示し、破線で示す曲線が経時変化後の特性を示している。一般的に、有機EL素子のI-V特性は、図示するように時間が経過すると劣化してしまう。そして図14の画素回路100においては、有機EL素子1の経時変化とともに、ドライブトランジスタT<sub>d</sub>のドレイン電圧が変化してゆく。ところが図14の画素回路100では上記のようにゲート・ソース間電圧V<sub>g</sub>sが一定であるので、有機EL素子1には一定量の電流が流れ、発光輝度は変化しない。つまり安定した階調制御ができる。30

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0009】

ところで図14に示した画素回路100は、pチャンネル型のドライブトランジスタT<sub>d</sub>を用いて構成されているが、nチャンネル型のTFTにより構成することができれば、TFT作成において従来のアモルファスシリコン(a-Si)プロセスを用いることが可能になる。これにより、TFT基板の低コスト化が可能となり、開発が期待されている。40

図16は、図14に示した画素回路100のpチャンネルTFTであるドライブトランジスタT<sub>d</sub>をnチャンネルTFTに置き換えた構成を示す回路図である。図示する様に、この場合の画素回路100は、nチャンネル型のTFTとしてサンプリングトランジスタT<sub>S</sub>、ドライブトランジスタT<sub>d</sub>、保持容量C10、有機EL素子1で構成されている。

この画素回路100では、ドライブトランジスタT<sub>d</sub>のドレイン側が電源電位V<sub>c</sub>cに接続され、ソースは有機EL素子1のアノードに接続されており、ソースフォロワ回路を形成している。

## 【0010】

ところが、このようにドライブトランジスタT<sub>d</sub>をnチャンネルTFTに置き換えた場合50

は、ソースが有機EL素子1に接続されてしまうため、図15に示したような有機EL素子1の経時変化とともにゲート・ソース間電圧 $V_{g,s}$ が変化してしまう。これにより、有機EL素子1に流れる電流量が変化し、その結果発光輝度は変化してしまう。つまり適切な階調制御ができなくなる。

また、アクティブマトリクス型の有機ELディスプレイは、有機EL素子1の特性変動に加え、画素回路100を構成するnチャネル型TFTの閾値電圧も経時的に変化する。前述の式1から明らかな様に、ドライブトランジスタTdの閾値電圧 $V_{t,h}$ が変動するとも、ドレン電流 $I_{d,s}$ が変化してしまう。これにより、同じゲート電圧 $V_{g,s}$ を与えても、閾値電圧 $V_{t,h}$ の変動により発光輝度が変化してしまう。このため発光輝度も画素ごとに変化してしまう。

nチャネルTFTにより画素回路100を構成した場合、以上のように有機EL素子1の経時劣化やドライブトランジスタTdの閾値電圧の変動やバラツキにより電流量が変動してしまうことで、表示画像として高品質な画像表示が実現できないという課題があった。

#### 【課題を解決するための手段】

##### 【0011】

そこで本発明では、nチャネルTFTによる画素回路を用いても、高品質な画像表示が可能な表示装置、表示方法を実現することを目的とする。さらには、回路構成を効率化することも目的とする。

##### 【0012】

本発明の表示装置は、信号線と所要数の走査線が交差する部分に形成される画素回路がマトリクス状に配置されて成る表示装置であって、各画素回路は、有機エレクトロルミネッセンス素子と、保持容量と、サンプリングトランジスタ、ドライブトランジスタ、第1，第2の検知トランジスタ、及びスイッチングトランジスタからなる5個のnチャネル薄膜トランジスタとを備える。上記ドライブトランジスタのソースとゲートとの間に上記保持容量が接続され、上記ドライブトランジスタのソースと所定のカソード電位との間に上記有機エレクトロルミネッセンス素子が接続され、上記ドライブトランジスタのソースと第1の固定電位との間に上記第1の検知トランジスタが接続され、上記ドライブトランジスタのゲートと第2の固定電位との間に上記第2の検知トランジスタが接続され、上記ドライブトランジスタのゲートと上記信号線との間に上記サンプリングトランジスタが接続され、上記ドライブトランジスタのドレンと所定の電源電位との間に上記スイッチングトランジスタが接続され、上記サンプリングトランジスタ、上記第1，第2の検知トランジスタ、及び上記スイッチングトランジスタは、それぞれ対応する走査線によって導通制御されるように構成されている。

そして、上記サンプリングトランジスタの導通制御を行う走査線が、上記第2の固定電位の供給ラインとされて、該走査線に上記第2の検知トランジスタが接続されている。この場合、上記第2の検知トランジスタは、該第2の検知トランジスタに対応する走査線に与えられる走査パルスによって、上記サンプリングトランジスタが非導通とされている期間に導通されるとともに、上記サンプリングトランジスタに対応する走査線に与えられる走査パルスのローレベルが、上記第2の固定電位とされている。

又は、上記サンプリングトランジスタの導通制御を行う走査線が、上記第1の固定電位の供給ラインとされて、該走査線に上記第1の検知トランジスタが接続されている。この場合、上記第1の検知トランジスタは、該第1の検知トランジスタに対応する走査線に与えられる走査パルスによって、上記サンプリングトランジスタが非導通とされている期間に導通されるとともに、上記サンプリングトランジスタに対応する走査線に与えられる走査パルスのローレベルが、上記第1の固定電位とされている。

##### 【0013】

即ち本発明では画素回路は、有機EL素子と、1個の保持容量と、サンプリングトランジスタ、ドライブトランジスタ、スイッチングトランジスタ、第1及び第2の検知トランジスタからなる5個のnチャネル薄膜トランジスタとで構成されている。そしてこの画素

回路は、ドライブトランジスタの閾値電圧の変動と有機EL素子の経時劣化を補償する保持容量のブートストラップ機能（特性変動補償機能）を備えることになるため、電流駆動型の有機EL素子のI-V特性が経時変化しても、発光輝度を一定に保持することができる。また、第1及び第2の検知トランジスタでドライブトランジスタの閾値電圧を検出し、その経時変化を回路的に補償することで、安定して有機EL素子を駆動できる。

そのうえで、上記サンプリングトランジスタの導通制御を行う走査線（サンプリングトランジスタのゲートライン）が、上記第2の固定電位の供給ライン（又は上記第1の固定電位の供給ライン）として共用される。これにより、上記第2の固定電位の供給ライン（又は上記第1の固定電位の供給ライン）を独立して設ける必要がなくなる。

#### 【発明の効果】

#### 【0014】

本発明によれば、画素回路を有機EL素子と、1個の保持容量と、サンプリングトランジスタ、ドライブトランジスタ、スイッチングトランジスタ、第1及び第2の検知トランジスタからなる5個のnチャネル薄膜トランジスタとで構成し、この画素回路にブートストラップ機能を備えることで、有機EL素子の経時劣化やドライブトランジスタの閾値電圧変動によっても安定して有機EL素子を駆動でき、nチャネルTFTによる画素回路を用いた表示装置として、表示画像の高画質化を実現できる。

また、それにより、トランジスタを全てnチャネルTFTで構成し、ソースフォロワーが可能となり、アノード接続のできる回路構成を実用化できる。このため一般的なアモルファスシリコンのプロセスを導入することが可能となり、低コスト化が促進できる。

#### 【0015】

また本発明では、サンプリングトランジスタの導通制御を行う走査線が、第2の固定電位の供給ライン（又は第1の固定電位の供給ライン）とされ、その走査線に第2の検知トランジスタ（又は第1の検知トランジスタ）が接続される構成とする。この場合、サンプリングトランジスタの導通制御を行う走査線に与えられる走査パルスのローレベルが、第2の固定電位（又は第1の固定電位）であるようにしている。すなわち、サンプリングトランジスタの導通制御を行う走査線を、第2の固定電位（又は第1の固定電位）の供給ラインとして共用する構成とされる。

これによって第2の固定電位（又は第1の固定電位）の供給ラインを独立して配設することを不要とし、画素回路内で配される電源線としてのライン数が低減される。またそれによってライン間のスペースを大きくとることができ。その結果、ダストなどによる各ラインのショートの低減や、歩留まりの向上が実現される。

さらに、ライン及びスペースの余裕ができるることは、画素サイズの小型化にも好適となり、表示装置としての高精細化にも有利である。

#### 【発明を実施するための最良の形態】

#### 【0016】

以下、本発明の表示装置の実施の形態を説明するが、説明の都合上、まず実施の形態の表示装置としての全体の構成を述べた後、その表示装置構成において本発明に相当しない参考例としての画素回路を説明し、その後、実施の形態としての4つの画素回路例I～IVを説明する。即ち以下の順序で説明する。

#### [1. 実施の形態の表示装置の構成]

#### [2. 画素回路の参考例]

#### [3. 実施の形態の画素回路例I]

#### [4. 実施の形態の画素回路例II]

#### [5. 実施の形態の画素回路例III]

#### [6. 実施の形態の画素回路例IV]

#### 【0017】

#### [1. 実施の形態の表示装置の構成]

図1に実施の形態の表示装置の構成を示す。この表示装置は後述するように、発光素子

10

20

30

40

50

である有機EL素子の特性変動及びドライブトランジスタの閾値電圧変動に対する補償機能であるポートストラップ機能を備えた画素回路を含むものである。

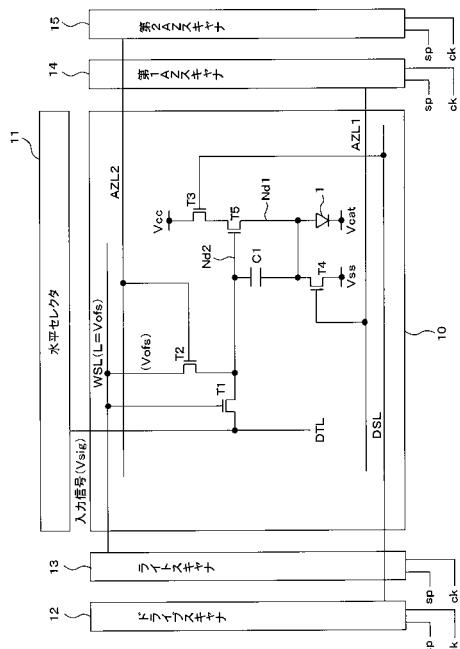

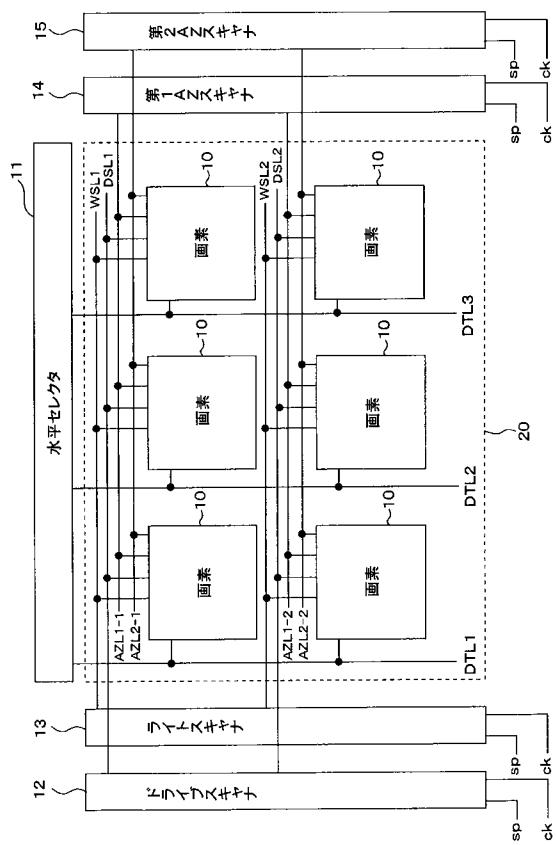

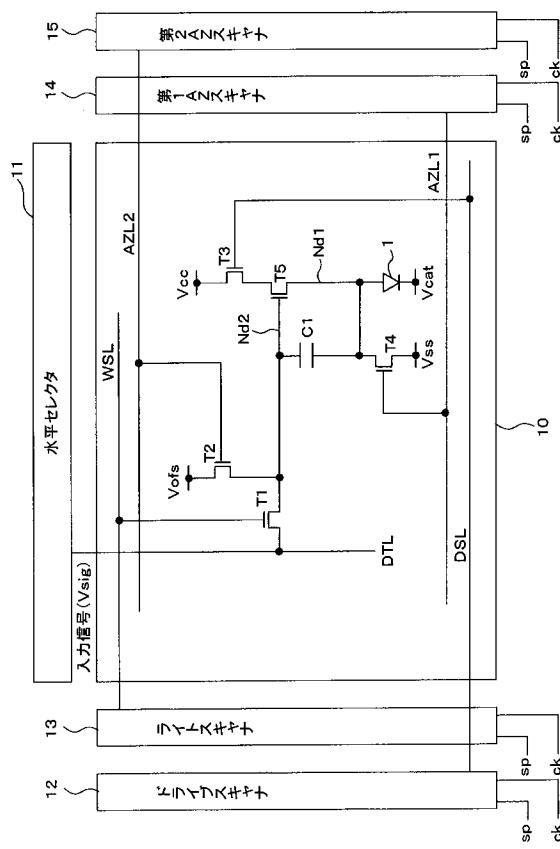

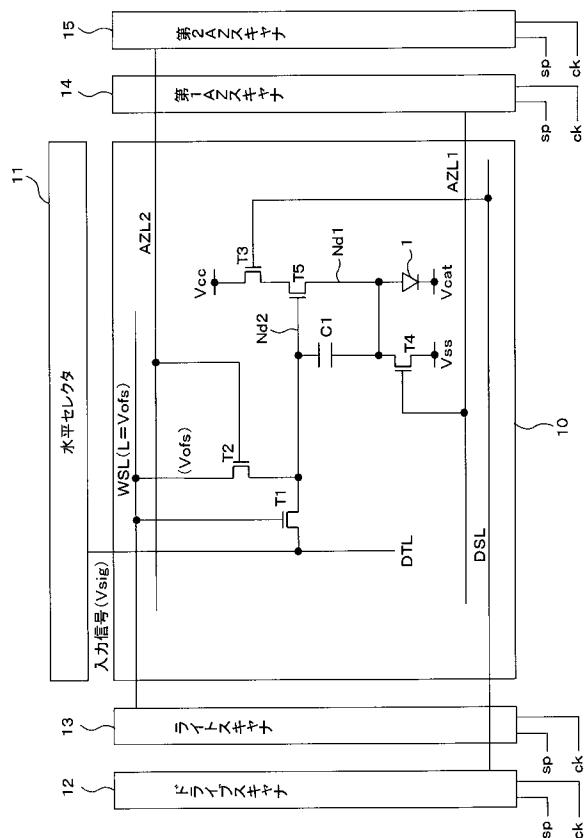

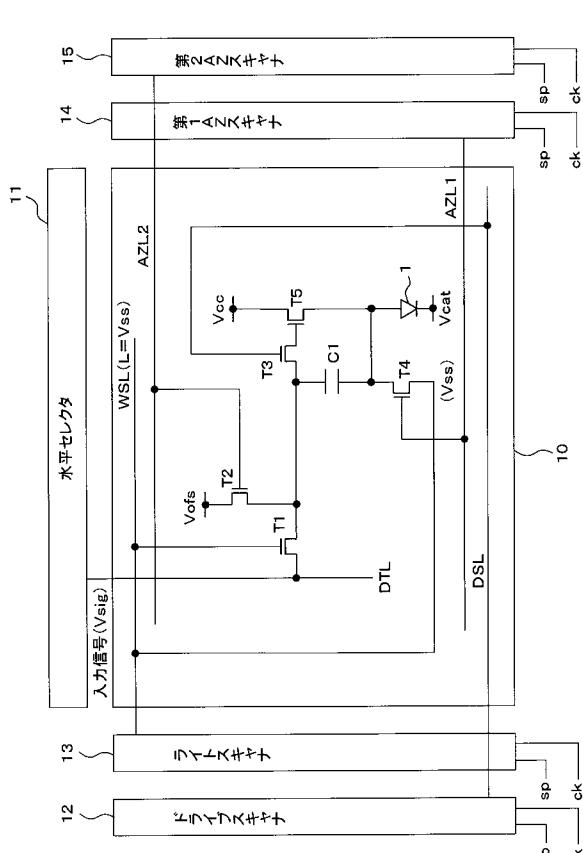

図1に示すように、本例の表示装置は、画素回路10がm行×n列のマトリクス状に配列された画素アレイ部20、水平セレクタ11、ドライブスキャナ12、ライトスキャナ13、第1AZスキャナ14、第2AZスキャナ15を備える。

また水平セレクタ11により選択され、輝度情報に応じた映像信号を画素10に対する入力信号として供給する信号線DTL1、DTL2・・・が、画素アレイ部20に対して列方向に配されている。信号線DTL1、DTL2・・・は、画素アレイ部20においてマトリクス配置された画素回路10の列数分だけ配される。

また画素アレイ部20に対して、行方向に走査線WSL1、WSL2・・・、走査線DSL1、DSL2・・・、走査線AZL1-1、AZL1-2・・・、走査線AZL2-1、AZL2-2・・・が配されている。これらの走査線はそれぞれ、画素アレイ部20においてマトリクス配置された画素回路10の行数分だけ配される。

走査線WSL(WSL1, WSL2...)はライトスキャナ13により選択駆動される。

走査線DSL(DSL1, DSL2...)はドライブスキャナ12により選択駆動される。

走査線AZL1(AZL1-1, AZL1-2...)は第1AZスキャナ14により選択駆動される。

走査線AZL2(AZL2-1, AZL2-2...)は第2AZスキャナ15により選択駆動される。

ドライブスキャナ12、ライトスキャナ13、第1AZスキャナ14、第2AZスキャナ15は、それぞれ入力されるスタートパルスspとクロックckを基準として、設定された所定のタイミングで各走査線に選択パルス(走査パルス)を与える。

【0018】

[2. 画素回路の参考例]

このような表示装置において画素回路10として採用できる構成例を図2で説明する。この図2の画素回路10の構成自体は、実施の形態の説明の都合上、例示する参考例であり本発明に該当するものではない。ただし、図3～図5で述べる画素回路10の動作は、後述する実施の形態の画素回路の動作と同じものである。

【0019】

図2では簡略化のため、信号線DTLと走査線WSL, DSL, AZL1, AZL2が交差する部分に配される1つの画素回路10のみを示している。

この画素回路10は、発光素子である有機EL素子1と、1個の保持容量C1と、サンプリングトランジスタT1、ドライブトランジスタT5、スイッチングトランジスタT3、第1、第2の検知トランジスタT2, T4からなる5個のNチャネル薄膜トランジスタで構成されている。

【0020】

保持容量C1は、一方の端子がドライブトランジスタT5のソースに接続され、他方の端子が同じくドライブトランジスタT5のゲートに接続されている。図では、ドライブトランジスタT5のソースノードをノードNd1、ドライブトランジスタT5のゲートノードをノードNd2として示している。従って、保持容量C1はノードNd1とノードNd2の間に接続されていることになる。

画素回路10の発光素子は例えばダイオード構造の有機EL素子1とされ、アノードとカソードを備えている。有機EL素子1のアノードはドライブトランジスタT5のソース(ノードNd1)に接続され、カソードは所定のカソード電位Vcatに接続されている。なお、有機EL素子1はアノード/カソード間に容量成分を含んでおり、後述する図では、この容量成分をCe1として示す場合がある。

【0021】

10

20

30

40

50

第1の検知トランジスタT4は、そのソースが第1の固定電位Vssに接続され、そのドレインがドライブトランジスタT5のソース（ノードNd1）に接続され、ゲートが走査線AZL1に接続されている。

第2の検知トランジスタT2は、そのソースが第2の固定電位Vofsに接続され、そのドレインがドライブトランジスタT5のゲート（ノードNd2）に接続され、そのゲートは走査線AZL2に接続されている。

サンプリングトランジスタT1は、その一端が信号線DTLに接続され、他端がドライブトランジスタT5のゲート（ノードNd2）に接続され、そのゲートが走査線WSLに接続されている。

スイッチングトランジスタT3は、そのドレインが電源電位Vccに接続され、そのソースがドライブトランジスタT5のドレインに接続され、そのゲートが走査線DSLに接続されている。

#### 【0022】

サンプリングトランジスタT1は走査線WSLによって選択されたときに動作し、信号線DTLからの入力信号VsigをサンプリングしてノードNd2を介し保持容量C1に保持させる。

ドライブトランジスタT5は、保持容量C1に保持された信号電位に応じて有機EL素子1を電流駆動する。

スイッチングトランジスタT3は走査線DSLによって選択されたときに導通して電源電位VccからドライブトランジスタT5に電流を供給する。

第1、第2の検知トランジスタT4、T2は、それぞれ走査線AZL1、AZL2によって所定のタイミングで選択されることで導通される。この第1、第2の検知トランジスタT4、T2のオン／オフは、有機EL素子1の電流駆動に先立ってドライブトランジスタT5の閾値電圧Vthを検知し、あらかじめその影響をキャンセルする為に該検知した閾値電圧を保持容量C1に保持する動作（閾値検出動作）に関連して実行される。

#### 【0023】

この画素回路10の正常な動作を保証する為の条件として、固定電位Vssは、固定電位VofsからドライブトランジスタT5の閾値電圧Vthを差し引いたレベルよりも低く設定されている。すなわち、 $Vss < Vofs - Vth$ である。

また固定電位Vssは、有機EL素子1の閾値電圧Velと、カソード電位Vcatの和よりも小さく設定されている（ $Vss < Vth + Vcat$ ）。

また固定電位Vofsは、ドライブトランジスタT5の閾値電圧Vthと、有機EL素子1の閾値電圧Vtheと、カソード電圧Vcatの和よりも小さく設定されている（ $Vofs < Vth + Vthe + Vcat$ ）。

例えば固定電位Vofsはグランド電位、固定電位Vssは負電位とされ、上記各条件を満たすようにされる。

#### 【0024】

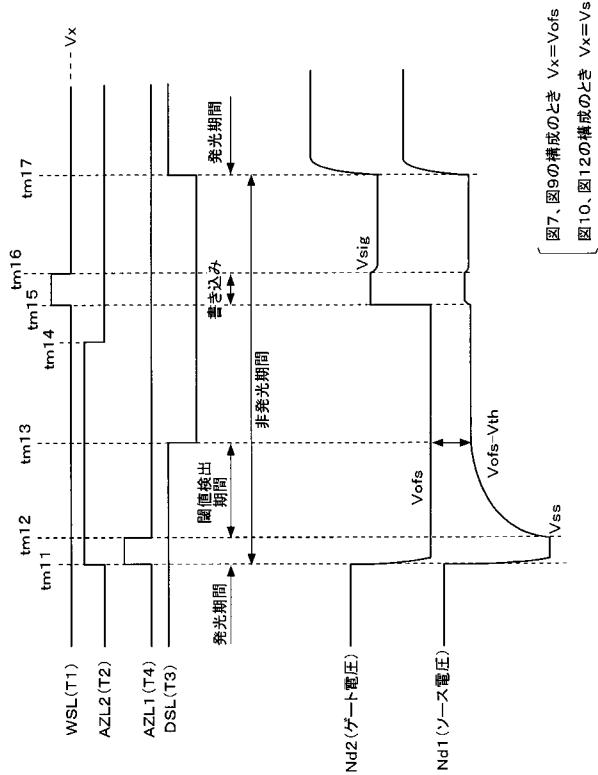

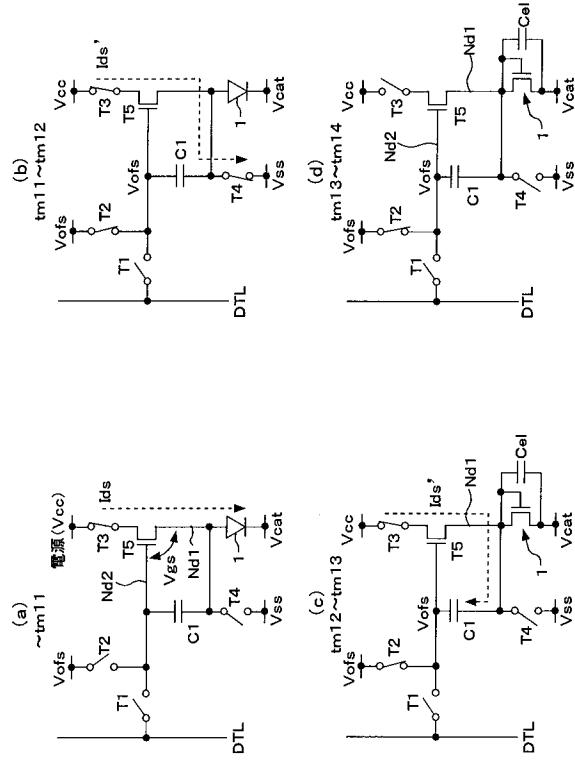

この図2の画素回路10の構成において実行される動作を図3～図5で説明する。

図3に走査線WSL、AZL2、AZL1、DSLのタイミングチャートを示している。これは上記構成からわかるように、それぞれサンプリングトランジスタT1、検知トランジスタT2、検知トランジスタT4、スイッチングトランジスタT3のオン／オフタイミングとなる。またこの図3には、ドライブトランジスタT5のゲート電圧（ノードNd2）、ソース電圧（ノードNd1）の変化を示している。また、図4、図5は各時点の等価回路を示している。

#### 【0025】

図3のタイミングチャートは、発光素子である有機EL素子1が発光駆動される1サイクル、つまり画像表示の1フレーム期間を表している。1フレーム期間は、有機EL素子1の非発光期間と発光期間から成り、例えば時点tm11が、前回の1フレームの終了タイミング、かつ今回の1フレームの開始タイミングとしている。

#### 【0026】

10

20

30

40

50

時点  $t_{m11}$  に至るまでの期間、つまり前のフレームの終了直前の期間では、走査線  $W_{SL}$ ,  $A_{ZL2}$ ,  $A_{ZL1}$  がローレベルにある一方、走査線  $D_{SL}$  がハイレベルにある。従って図 4 (a) に示すように、スイッチングトランジスタ  $T_3$  がオン状態にある一方、サンプリングトランジスタ  $T_1$ 、及び検知トランジスタ  $T_2$ ,  $T_4$  はオフ状態にある。

このときドライブトランジスタ  $T_5$  はノード  $N_{d2}$ ,  $N_{d1}$  間の電圧に応じて駆動電流  $I_{ds}$  を流し、有機 EL 素子 1 を発光させている。このときドライブトランジスタ  $T_5$  のソース電位（ノード  $N_{d1}$  の電位）は所定の動作点に保持されている。

ドライブトランジスタ  $T_5$  は飽和領域で動作するように設定されているため、有機 EL 素子 1 に流れる電流  $I_{ds}$  はドライブトランジスタ  $T_5$  のゲート・ソース間電圧  $V_{gs}$  に応じて、上述した式 1 に示される値をとる。

#### 【0027】

時点  $t_{m11}$  から、1 フレーム期間が開始される。このとき、走査線  $A_{ZL2}$ ,  $A_{ZL1}$  が共にローレベルからハイレベルに立ち上がる。この結果、図 4 (b) に示すように、検知トランジスタ  $T_2$ ,  $T_4$  が共にオフ状態からオン状態に切り替わる。

これによりノード  $N_{d2}$  は急速に固定電位  $V_{of}$  まで下がり、ノード  $N_{d1}$  も急速に固定電位  $V_{ss}$  まで下がる。つまりドライブトランジスタ  $T_5$  のゲート電圧は  $V_{of}$ 、ソース電圧は  $V_{ss}$  という値に充電される。上記のように、 $V_{ss} < V_{of} - V_{th}$  に設定されている為、ドライブトランジスタ  $T_5$  はオン状態を維持し、ドレン電流  $I_{ds}$  が流れる。

そしてこのときドライブトランジスタ  $T_5$  のゲート・ソース間電圧  $V_{gs}$  は、 $V_{of} - V_{ss}$  という値をとり、それに応じた電流  $I_{ds}'$  が、図 4 (b) に破線で示すように、電源  $V_{cc}$  側から固定電位  $V_{ss}$  側に流れることになる。

また、有機 EL 素子 1 を非発光とするために、上述のように有機 EL 素子 1 にかかる電圧  $V_{e1}$  (= ノード  $N_{d1}$  電位) が、有機 EL 素子 1 の閾値電圧  $V_{thel}$  とカソード電圧  $V_{cat}$  の和より小さくなるように固定電位  $V_{of}$ ,  $V_{ss}$  の電圧値が設定されているため、有機 EL 素子 1 は逆バイアス状態となっており、電流は流れず、従って、非発光状態になる。

なお、この時点  $t_{m11}$  となった後、検知トランジスタ  $T_2$ ,  $T_4$  はどちらが先にオンしてもよい。

#### 【0028】

時点  $t_{m12}$  では、ブートストラップ機能のための閾値検出動作が開始される。このため走査線  $A_{ZL1}$  がハイレベルからローレベルに戻され図 4 (c) のように検知トランジスタ  $T_4$  がオフ状態とされる。

そして有機 EL 素子 1 の等価回路はダイオードと容量で表されるため、 $V_{e1} - V_{cat} + V_{thel}$  (有機 EL 素子 1 のリーク電流がドライブトランジスタ  $T_5$  に流れる電流よりもかなり小さい) である限り、ドライブトランジスタ  $T_5$  の電流は保持容量  $C_1$  と有機 EL 素子 1 の容量  $C_{e1}$  を充電するために使われる。

このときドライブトランジスタ  $T_5$  を流れるドレン電流  $I_{ds}'$  の電流路が遮断される為、有機 EL 素子 1 にかかる電圧  $V_{e1}$  (= ノード  $N_{d1}$  電位) は図 5 (d) のように時間と共に上昇してゆく。

一定時間経過後、ドライブトランジスタ  $T_5$  のゲート・ソース間電圧  $V_{gs}$  は閾値電圧  $V_{th}$  をとる。このとき有機 EL 素子 1 にかかる電圧  $V_{e1} = V_{of} - V_{th} - V_{cat} + V_{thel}$  となっている。

このときに、ノード  $N_{d1}$  とノード  $N_{d2}$  の間に現われた電位差  $V_{th}$  は保持容量  $C_1$  に保持されることになる。つまり閾値検出動作として、ドライブトランジスタ  $T_5$  の閾値電圧  $V_{th}$  を検知し、これを保持容量  $C_1$  に保持する。

#### 【0029】

次に時点  $t_{m13}$  において、走査線  $D_{SL}$  がローレベルとされ、図 4 (d) のようにスイッチングトランジスタ  $T_3$  がオフとされる。これによって電流  $I_{ds}$  が流れなくなり、この時点で閾値検出動作が終了される。

その後、時点  $t_m 14$  で走査線  $A Z L 2$  がロー・レベルとされ、図 5 (a) のように検知トランジスタ  $T 2$  がオフとされる。

### 【0030】

次に時点  $t_m 15$  では、走査線  $W S L$  がハイ・レベルとされ、図 5 (b) のようにサンプリングトランジスタ  $T 1$  がオンとされて信号線  $D T L$  からの信号電圧  $V_{sig}$  の保持容量  $C 1$  への書きが行われる。これによりドライブトランジスタ  $T 5$  のゲート電圧が信号線  $D T L$  からの信号電圧  $V_{sig}$  とされる。

このとき、ドライブトランジスタ  $T 5$  のゲート・ソース間電圧  $V_{gs}$  は保持容量  $C 1$ 、有機  $E L$  素子  $1$  の寄生容量  $C_{el}$ 、ドライブトランジスタ  $T 5$  の寄生容量  $C 2$  によって式 2 のように決定される。

$$V_{gs} = (C_{el} / (C_{el} + C 1 + C 2)) \cdot (V_{sig} - V_{of}) + V_{th} \quad \dots \text{(式2)}$$

ただし、寄生容量  $C_{el}$  は容量  $C 1$ 、 $C 2$  に比べて大きいために、ドライブトランジスタ  $T 5$  のゲート・ソース間電圧  $V_{gs}$  は、ほぼ  $V_{sig} + V_{th}$  となる。

### 【0031】

信号線  $D T L$  からの信号電圧  $V_{sig}$  の書きが終了した時点  $t_m 16$  の後に、時点  $t_m 17$  で走査線  $D S L$  がハイ・レベルとされ、図 5 (c) のようにスイッチングトランジスタ  $T 3$  がオンとされることで、ドライブトランジスタ  $T 5$  のドレイン電圧が電源電圧まで上昇される。

保持容量  $C 1$  の作用によりドライブトランジスタ  $T 5$  のゲート・ソース間電圧  $V_{gs}$  は一定であるので、ドライブトランジスタ  $T 5$  は一定電流  $I_{ds}$  を有機  $E L$  素子  $1$  に流し、ノード  $N d 1$  の電位は有機  $E L$  素子  $1$  に電流が流れる電圧まで上昇し、これにより有機  $E L$  素子  $1$  は発光する。つまり今回のフレームにおける発光期間が開始される。

### 【0032】

図 2 の参考例としての画素回路  $10$  の動作は以上のようになるが、この図 2 の画素回路  $10$  においても、有機  $E L$  素子  $1$  は発光時間が長くなるとその  $I - V$  特性は変化してしまう。そのためノード  $N d 1$  の電位も変化する。

しかしながら、上記動作の場合、ドライブトランジスタ  $T 5$  のゲート・ソース間電圧  $V_{gs}$  は一定値に保たれているので有機  $E L$  素子  $1$  に流れる電流は変化しない。よって有機  $E L$  素子  $1$  の  $I - V$  特性が劣化しても、一定電流  $I_{ds}$  が常に流れ続け、有機  $E L$  素子  $1$  の輝度が変化することはない。このため、 $n$  チャネル  $TFT$  による画素回路を用いた表示装置として、表示画像の高画質化を実現できる。

### 【0033】

但し、次のように回路構成上、不利な点がある。

画素回路  $10$  内に存在する固定電源について考える。画素回路  $10$  には電源電圧  $V_{cc}$ 、固定電位  $V_{of}$ 、 $V_{ss}$ 、カソード電位  $V_{cat}$  と、4つの固定電源が存在している。そのうち、画素のレイアウトに影響を及ぼすものは  $V_{cc}$ 、 $V_{of}$ 、 $V_{ss}$  としての固定電源ラインの3つである。

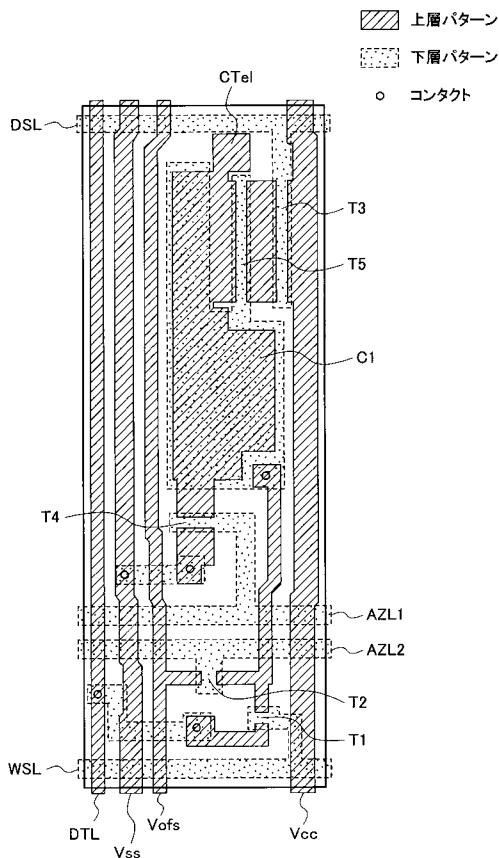

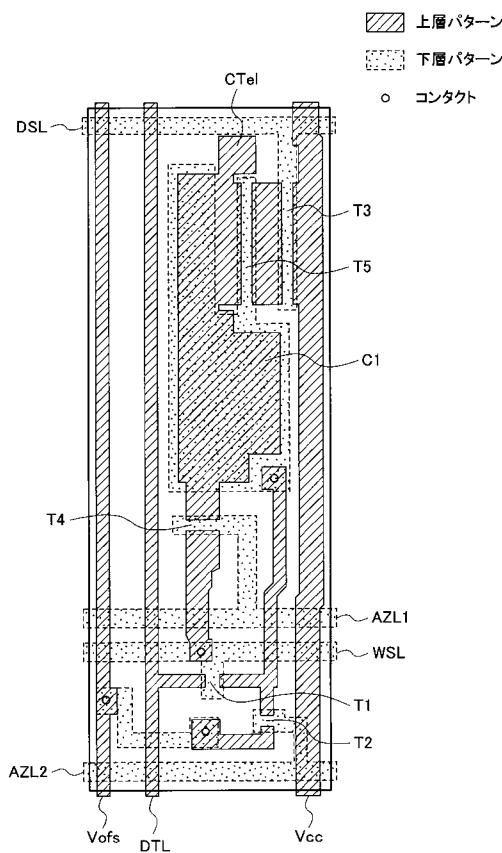

図 6 に、図 2 の構成の場合の画素レイアウト例を示している。

図 6 には固定電源ライン  $V_{cc}$ 、 $V_{of}$ 、 $V_{ss}$  と信号線  $D T L$  が上層パターンとして形成され、また下層パターンとして走査線  $D S L$ 、 $A Z L 1$ 、 $A Z L 2$ 、 $W S L$  が形成されている状態を示している。上層パターンと下層パターンはコンタクトポイントとして「」で示す部位で接続されている。

保持容量  $C 1$  は略中央部分の上層パターンと下層パターンの対向面部分により形成されている。そして図示するようにサンプリングトランジスタ  $T 1$ 、検知トランジスタ  $T 2$ 、 $T 4$ 、スイッチングトランジスタ  $T 3$ 、ドライブトランジスタ  $T 5$  が形成される。

なおコンタクト  $C T e 1$  は、有機  $E L$  素子  $1$  のアノードに対する接続ポイントである。図示しない有機  $E L$  素子  $1$  のカソード側は、この図 6 のパターンの上面に形成されるカソード電極に接続される。

### 【0034】

10

20

30

40

50

この図 6 からわかるように、特に固定電源ライン  $V_{ccc}$ ,  $V_{ofs}$ ,  $V_{ss}$  としての専有面積は広いものとなる。

つまりこれらの固定電源ラインの数が多いと画素のサイズが大きくなってしまい、高精細化を実現することに不利となる。

また、固定電源ライン  $V_{ss}$ ,  $V_{ofs}$  及び信号線  $DTL$  の配線パターンは、狭いスペースを介して隣接している。このような状態は、ダストなどによるライン間のショートを引き起こしやすい。もちろんショートの可能性が高くなることは、製造歩留まりを悪化させることにつながる。

【0035】

[3. 実施の形態の画素回路例 I]

10

そこで実施の形態としては、固定電源ラインを削減し、ライン間のショートの可能性の低減、歩留まりの向上、さらには画素の小型化や高精細化の容易性を考慮した画素回路 10 を提供する。

【0036】

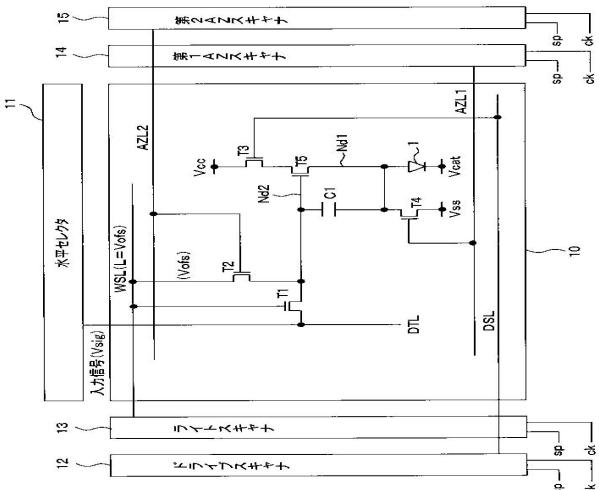

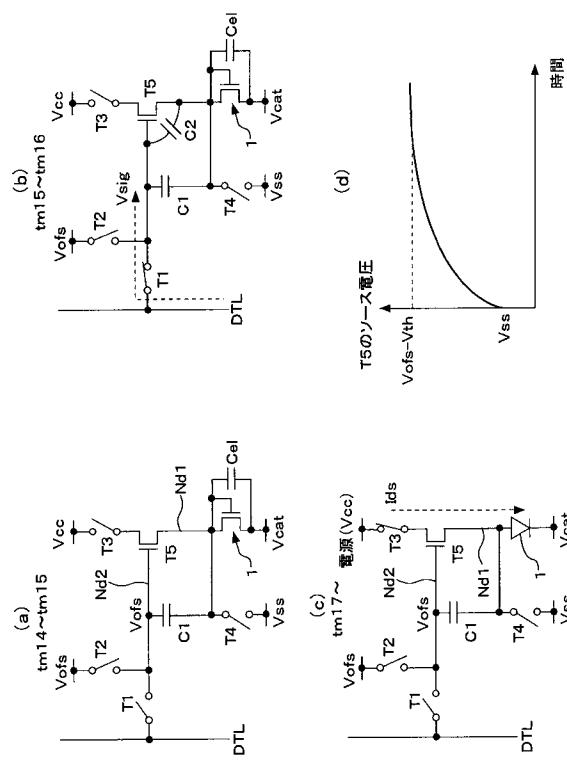

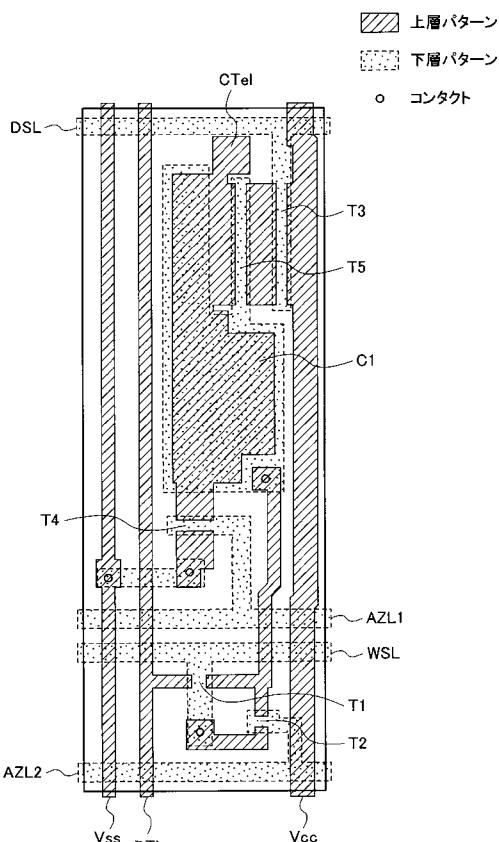

実施の形態の画素回路例 I としての画素回路 10 の構成を図 7 に示す。

この画素回路 10 も、上記図 2 の参考例と同様に、発光素子である有機 EL 素子 1 と、1 個の保持容量  $C_1$  と、サンプリングトランジスタ  $T_1$ 、ドライブトランジスタ  $T_5$ 、スイッチングトランジスタ  $T_3$ 、第 1、第 2 の検知トランジスタ  $T_2$ ,  $T_4$  からなる 5 個の N チャネル薄膜トランジスタとで構成されている。そして信号線  $DTL$  と走査線  $WSL$ ,  $DSL$ ,  $AZL_1$ ,  $AZL_2$  が配される。

【0037】

有機 EL 素子 1、保持容量  $C_1$  と、サンプリングトランジスタ  $T_1$ 、ドライブトランジスタ  $T_5$ 、スイッチングトランジスタ  $T_3$ 、第 1 の検知トランジスタ  $T_4$  については、その回路接続状態は図 2 と同様であるため、重複説明を避けるが、この図 7 の場合、第 2 の検知トランジスタ  $T_2$  のソースが、走査線  $WSL$  に接続されていることが図 2 と異なる。つまり、第 2 の固定電位  $V_{ofs}$  としての電源ラインは設けられず、サンプリングトランジスタ  $T_1$  を制御するための走査線  $WSL$  を、固定電位  $V_{ofs}$  を供給する電源ラインとして共用するものである。

そしてこの図 7 の画素回路 10 の動作は図 3 で説明した動作と同様となる。

30

【0038】

上述した図 3 による説明からわかるように、検知トランジスタ  $T_2$  は、走査線  $AZL_2$  によって閾値検出動作のために時点  $t_{m11} \sim t_{m14}$  の期間、オンとされる。そしてこの検知トランジスタ  $T_2$  がオンしている期間のみ、ドライブトランジスタ  $T_5$  のゲートは固定電位  $V_{ofs}$  という値が充電されている。上述したように、この期間中に有機 EL 素子 1 が発光することができないように  $V_{ofs} < V_{cat} + V_{the1} + V_{th}$  とされる。

一方、サンプリングトランジスタ  $T_1$  は、信号線  $DTL$  からの入力信号  $V_{sig}$  の書き込み期間（時点  $t_{m15} \sim t_{m16}$ ）のみ、走査線  $WSL$  によってオンとされる。

換言すれば、固定電位  $V_{ofs}$  が必要な期間、つまり検知トランジスタ  $T_2$  がオンとされる期間は、走査線  $WSL$  に与えられる走査パルスがローレベルとされている期間である。

従って、図 3 に示すように、走査線  $WSL$  に与えられる走査パルスのローレベル  $V_x$  が、固定電位  $V_{ofs}$  としての電位に設定されていることで、走査線  $WSL$  を固定電位  $V_{ofs}$  の供給ラインとして兼用できるものである。

【0039】

ここで入力信号  $V_{sig}$  の信号電圧とサンプリングトランジスタ  $T_1$  のゲートラインの電圧設定について考える。入力信号  $V_{sig}$  はその電位によって黒から白までの階調を表現する。黒を表現する場合、有機 EL 素子 1 に流れる電流は 0 であるのでドライブトランジスタ  $T_5$  のゲート・ソース間電圧  $V_{gs}$  は、その閾値電圧  $V_{th}$  以下とならなければならない。また、時点  $t_{m15}$  からの書き動作直前のドライブトランジスタ  $T_5$  のゲート電

40

50

位は  $V_{ofs}$  であることから考えて、入力信号  $V_{sig}$  の信号電圧が固定電位  $V_{ofs}$  以下であるならば黒を表現することができる。

また、サンプリングトランジスタ T 1 がオフの時のゲートラインについて考える。オフ時は信号線 DTL のどんな電圧に対してもオフしなければならないので、サンプリングトランジスタ T 1 のオフ時のゲート電圧  $V_{off}$  は、黒電圧  $V_{sigb}$  に対して  $V_{sigb} + V_{tht1}$  よりも低い電圧でなければならない。 $V_{tht1}$  はサンプリングトランジスタ T 1 の閾値電圧である。

以上より  $V_{off} < V_{sigb} + V_{tht1}$   $V_{ofs} + V_{tht1}$  であるため、 $V_{off} = V_{ofs}$  としても問題はない。つまり、図 3 における走査線 WSL に与えられる走査パルスのローレベル  $V_x = V_{ofs}$  としても問題はない。

#### 【0040】

さらにサンプリングトランジスタ T 1 がオンのときについて考える。サンプリングトランジスタ T 1 がオンのときは、そのゲート電圧は、正常に書き込みを行うため白を表現する入力信号  $V_{sig}$  の信号電圧  $V_{sigw}$  とサンプリングトランジスタ T 1 の閾値電圧  $V_{tht1}$  の和、つまり  $V_{sigw} + V_{tht1}$  よりも高い電圧である必要がある。

ここでサンプリングトランジスタ T 1 のゲートラインと固定電位  $V_{ofs}$  のラインを一致させれば、検知トランジスタ T 2 のソースに与えられる電圧も  $V_{sigw} + V_{tht1}$  よりも高い値をとる。しかしながら上述したように書き込み期間においては、検知トランジスタ T 2 はオフしているので、ドライブトランジスタ T 5 のソース電圧 (Nd1) には影響を及ぼさない。

#### 【0041】

以上のことから、図 7 のように走査線 WSL を固定電位  $V_{ofs}$  の供給ラインとして共有することに、問題がないことが理解される。

そしてこの図 7 の構成によれば、固定電位  $V_{ofs}$  としての電源ラインを削減できることになり、その画素回路 10 のレイアウトを例えれば図 8 のようにすることができる。

つまり、走査線 WSL がサンプリングトランジスタ T 1 のゲートラインとされるとともに、検知トランジスタ T 2 のソースに接続され、固定電位  $V_{ofs}$  としての電源ラインが設けられない。特に上述した図 6 と比較してわかるように、固定電源 Vss、信号線 DTL としての各ライン間のスペースに余裕が生ずる。

その結果、ダストなどによる各ライン間のショートの数を低減することができるようになり、歩留まりを上昇させることができるとなる。

もちろん、この図 8 はレイアウトの一例であり、例えは上記のように生じたスペース的な余裕を利用して電源 Vcc の周辺のライン間スペースやライン幅を広げることなども可能となる。

さらには、固定電位  $V_{ofs}$  としての電源ラインを削減できることは。当然、画素の小型化も容易となり、表示装置としての高精細化にも好適である。

#### 【0042】

もちろん、図 7 の画素回路 10 でも、有機 EL 素子 1 の I - V 特性は変化は補償される。つまりドライブトランジスタ T 5 のゲート・ソース間電圧  $V_{gs}$  は一定値に保たれているので有機 EL 素子 1 に流れる電流は変化しない。よって有機 EL 素子 1 の I - V 特性が劣化しても、一定電流  $I_{ds}$  が常に流れ続け、有機 EL 素子 1 の輝度が変化することはない。

そして、ドライブトランジスタ T 5 に n チャネル TFT を使用した本例のソースフォロワーとしての画素回路 10 において、適正に閾値電圧の変動及び有機 EL 素子 1 の経時劣化の補償が実現できることで、画素回路 10 のトランジスタを全て n チャネル化することに問題が無くなり、一般的なアモルファスシリコンのプロセスを導入することが可能となるため、低コスト化が実現できる。

#### 【0043】

#### [4. 実施の形態の画素回路例 11]

10

20

20

30

40

50

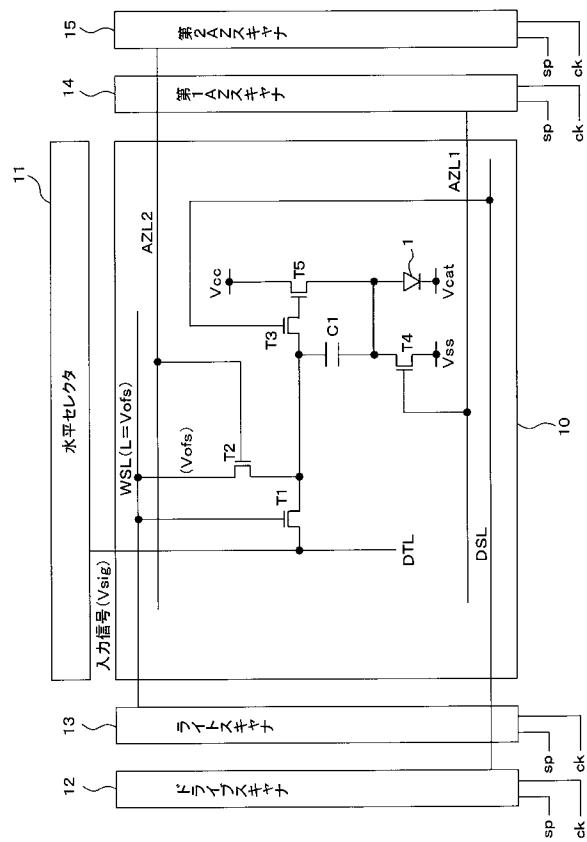

図9に実施の形態の画素回路例IIとしての構成を示す。

この図9の画素回路10も、走査線WSLを固定電位Vofsとしての電源供給ラインとして共用していることは上記図7と同様である。

これはスイッチングトランジスタT3を、ドライブトランジスタT5のドレインと電源電圧Vccの間ではなく、ドライブトランジスタT5のゲートとサンプリングトランジスタT1の間に接続した例である。つまり、スイッチングトランジスタT3を、電源電圧Vccの供給制御素子ではなく、ドライブトランジスタT5の導通制御素子として用いる。

画素回路10の動作としては、図3で説明した動作と同様であり、また走査線WSLに与えられる走査パルスのローレベルVx=Vofsとされていればよい。固定電位Vofs, Vss、及び入力信号Vsigの電圧設定は図7の場合と同様である。

この図9の画素回路10によっても図7の画素回路10を採用した場合と同様の効果を得ることができる。

【0044】

#### [5. 実施の形態の画素回路例III]

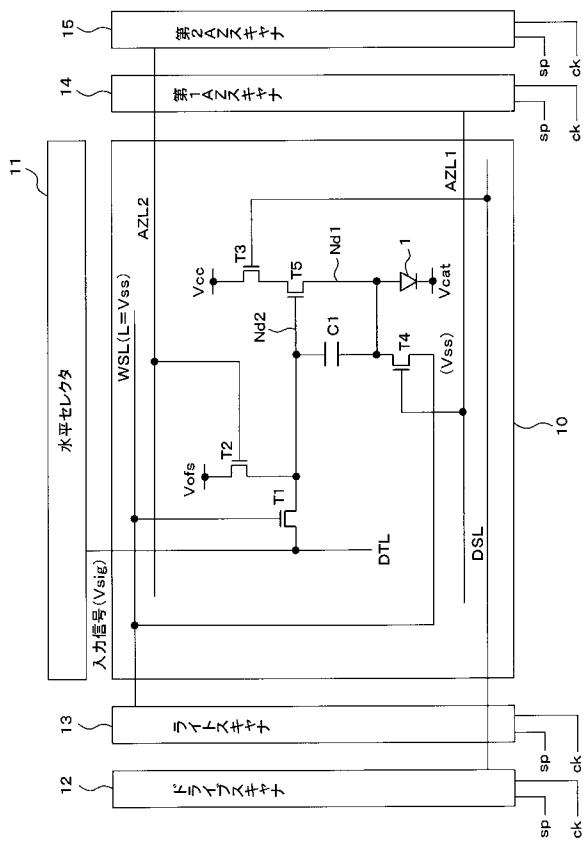

図10に実施の形態の画素回路例IIIとしての構成を示す。

この画素回路10も、上記図2の参考例と同様に、発光素子である有機EL素子1と、1個の保持容量C1と、サンプリングトランジスタT1、ドライブトランジスタT5、スイッチングトランジスタT3、第1、第2の検知トランジスタT2, T4からなる5個のNチャネル薄膜トランジスタとで構成されている。そして信号線DTLと走査線WSL, DSL, AZL1, AZL2が配される。

【0045】

有機EL素子1、保持容量C1と、サンプリングトランジスタT1、ドライブトランジスタT5、スイッチングトランジスタT3、第2の検知トランジスタT2については、その回路接続状態は図2と同様であるため、重複説明を避けるが、この図10の場合、第1の検知トランジスタT4のソースが、走査線WSLに接続されていることが図2と異なる。つまり、第1の固定電位Vssとしての電源ラインは設けられず、サンプリングトランジスタT1を制御するための走査線WSLを、固定電位Vssを供給する電源ラインとして共用するものである。

そしてこの図7の画素回路10の動作は図3で説明した動作と同様となる。

【0046】

図3による説明からわかるように、検知トランジスタT4は、走査線AZL1によって閾値検出動作の直前である時点tm11～tm12の期間、オンとされる。そしてこの検知トランジスタT2がオンしている期間のみ、固定電位Vssにドレイン電流Idsが流れ込み、ドライブトランジスタT5のソース電圧は固定電位Vssとなる。

ここで閾値検出動作を行うために、検知トランジスタT4がオンしたときはVofs-Vss>Vthでなければならないため、VssはVofsよりも低い電位とされている。

一方、サンプリングトランジスタT1は、信号線DTLからの入力信号Vsigの書込期間（時点tm15～tm16）のみ、走査線WSLによってオンとされる。

換言すれば、固定電位Vssが必要な期間、つまり検知トランジスタT4がオンとされる期間は、走査線WSLに与えられる走査パルスがローレベルとされている期間である。

従って、図3に示すように、走査線WSLに与えられる走査パルスのローレベルVxが、固定電位Vssとしての電位に設定されていることで、走査線WSLを固定電位Vssの供給ラインとして兼用できるものである。

【0047】

ここで入力信号Vsigの信号電圧とサンプリングトランジスタT1のゲートラインの電圧設定について考える。入力信号Vsigはその電位によって黒から白までの階調を表現する。黒を表現する場合、有機EL素子1に流れる電流は0であるのでドライブトランジスタT5のゲート・ソース間電圧Vgsは、その閾値電圧Vth以下とならなければな

10

20

30

40

50

らない。また、書込動作直前のドライブトランジスタT5のゲート電位は $V_{off}$ であることから考えて入力信号 $V_{sig}$ の信号電圧が $V_{off}$ 以下であるならば黒を表現することができる。

またサンプリングトランジスタT1がオフのときのゲートラインについて考える。オフ時は信号線DTLのどんな電圧に対してもオフしなければならぬので、ゲート電圧は黒電圧 $V_{sigb}$ に対して $V_{sigb} + V_{tht1}$ （サンプリングトランジスタT1の閾値電圧）よりも低い電圧でなければならない。ちなみにオフ時のゲート電圧 $V_{offf}$ はサンプリングトランジスタT1のリークを考え $V_{sigb}$ より低く設定するのが一般的である。

以上より $V_{ss} < V_{off} - V_{th}$ 、 $V_{offf} < V_{sigb} + V_{tht1}$   $V_{off} + V_{tht1}$ であるため、 $V_{offf} = V_{ss}$ としても問題はない。つまり、図3における走査線WSLに与えられる走査パルスのローレベル $V_x = V_{ss}$ としても問題はない。

#### 【0048】

さらにサンプリングトランジスタT1がオンの時にについて考える。サンプリングトランジスタT1がオンの時に正常に書き込みを行うため、そのゲート電圧は、白を表現する信号電圧 $V_{sigw}$ とサンプリングトランジスタT1の閾値電圧 $V_{tht1}$ の和、つまり $V_{sigw} + V_{tht1}$ よりも高い電圧である必要がある。ここでサンプリングトランジスタT1のゲートラインと固定電位 $V_{ss}$ のラインを一致させれば、検知トランジスタT4のソースに与えられる電圧も $V_{sigw} + V_{tht1}$ よりも高い値をとる。しかしながら上述したように書込期間においては、検知トランジスタT4はオフしているので、ドライブトランジスタT5のソース電圧( $N_{d1}$ )には影響を及ぼさない。

#### 【0049】

以上のことから、図10のように走査線WSLを固定電位 $V_{ss}$ の供給ラインとして共有することに、問題がないことが理解される。

そしてこの図10の構成によれば、固定電位 $V_{ss}$ としての電源ラインを削減できることになり、その画素回路10のレイアウトを例えば図11のようにすることができる。

つまり、走査線WSLがサンプリングトランジスタT1のゲートラインとされるとともに、検知トランジスタT4のソースに接続され、固定電位 $V_{ss}$ としての電源ラインが設けられない。特に上述した図6と比較してわかるように、固定電源 $V_{off}$ 、信号線DTLとしての各ライン間のスペースに余裕が生ずる。

その結果、ダストなどによる各ライン間のショートの数を低減することができるようになり、歩留まりを上昇させることができるとなる。

もちろん、この図10はレイアウトの一例であり、例えば上記のように生じたスペース的な余裕を利用して電源 $V_{cc}$ の周辺のライン間スペースやライン幅を広げることなども可能となる。

さらには、固定電位 $V_{ss}$ としての電源ラインを削減できることは。当然、画素の小型化も容易となり、表示装置としての高精細化にも好適である。

#### 【0050】

また、図10の画素回路10でも、有機EL素子1のI-V特性は変化は補償される。つまりドライブトランジスタT5のゲート・ソース間電圧 $V_{gs}$ は一定値に保たれているので有機EL素子1に流れる電流は変化しない。よって有機EL素子1のI-V特性が劣化しても、一定電流 $I_{ds}$ が常に流れ続け、有機EL素子1の輝度が変化することはない。

そして、ドライブトランジスタT5にnチャネルTFTを使用した本例のソースフォロワーとしての画素回路10において、適正に閾値電圧の変動及び有機EL素子1の経時劣化の補償が実現できることで、画素回路10のトランジスタを全てnチャネル化することに問題が無くなり、一般的なアモルファスシリコンのプロセスを導入することができるため、低コスト化が実現できる。

#### 【0051】

### [6. 実施の形態の画素回路例IV]

10

20

30

40

50

図12に実施の形態の画素回路例IVとしての構成を示す。

この図12の画素回路10も、走査線WSLを固定電位Vssとしての電源供給ラインとして共用していることは上記図10と同様である。

これはスイッチングトランジスタT3を、ドライブトランジスタT5のドレインと電源電圧Vccの間ではなく、ドライブトランジスタT5のゲートとサンプリングトランジスタT1の間に接続した例である。つまり、スイッチングトランジスタT3を、電源電圧Vccの供給制御素子ではなく、ドライブトランジスタT5の導通制御素子として用いる。

画素回路10の動作としては、図3で説明した動作と同様であり、また走査線WSLに与えられる走査パルスのローレベルVx=Vssとされていればよい。固定電位Vofs, Vss、及び入力信号Vsigの電圧設定は図10の場合と同様である。 10

この図12の画素回路10によっても図10の画素回路10を採用した場合と同様の効果を得ることができる。

#### 【図面の簡単な説明】

#### 【0052】

【図1】本発明の実施の形態の表示装置のブロック図である。

【図2】参考例の画素回路の回路図である。

【図3】実施の形態及び参考例としての動作の説明図である。

【図4】実施の形態及び参考例の動作における各時点の等価回路図である。

【図5】実施の形態及び参考例の動作における各時点の等価回路図である。 20

【図6】参考例における画素回路のラインパターンの説明図である。

【図7】第1の実施の形態の画素回路の回路図である。

【図8】第1の実施の形態における画素回路のラインパターンの説明図である。

【図9】第2の実施の形態の画素回路の回路図である。

【図10】第3の実施の形態の画素回路の回路図である。

【図11】第3の実施の形態における画素回路のラインパターンの説明図である。

【図12】第4の実施の形態の画素回路の回路図である。

【図13】従来の有機EL表示装置のブロック図である。

【図14】従来の有機EL表示装置の画素回路の回路図である。

【図15】有機EL表示の経時変化の説明図である。 30

【図16】従来の有機EL表示装置の画素回路の回路図である。

#### 【符号の説明】

#### 【0053】

1 有機EL素子、10 画素回路、11 水平セレクタ、12 ドライブスキャナ、

13 ライトスキャナ、14 第1AZスキャナ、15 第2AZスキャナ、C1 保持

容量、T1 サンプリングトランジスタ、T2, T4 検知トランジスタ、T3 スイッ

チングトランジスタ、T5 ドライブトランジスタ、WSL, DSL, AZL1, AZL

2 走査線、DTL 信号線

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 4 1 D |

| G 0 9 G | 3/20  | 6 7 0 J |

| H 0 5 B | 33/14 | A       |

(72)発明者 山下 淳一

東京都品川区北品川6丁目7番35号 ソニー株式会社内

F ターム(参考) 3K007 AB17 BA06 DB03 GA00

5C080 AA06 BB05 DD03 DD23 DD28 EE28 FF11 JJ02 JJ03 JJ04

JJ05 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2006215275A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2006-08-17 |

| 申请号            | JP2005028021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2005-02-03 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| [标]发明人         | 山本哲郎<br>内野勝秀<br>山下淳一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 山本 哲郎<br>内野 勝秀<br>山下 淳一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G09G3/30.J G09G3/30.K G09G3/20.611.H G09G3/20.621.A G09G3/20.624.B G09G3/20.641.D G09G3/20.670.J H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 5C080/AA06 5C080/BB05 5C080/DD03 5C080/DD23 5C080/DD28 5C080/EE28 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 3K107/AA01 3K107/BB01 3K107/CC35 3K107/CC43 3K107/CC45 3K107/EE03 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB06 5C380/AB22 5C380/BA11 5C380/BA12 5C380/BA28 5C380/BA29 5C380/BA38 5C380/BA39 5C380/BB02 5C380/BB21 5C380/BD02 5C380/CA12 5C380/CB17 5C380/CB20 5C380/CB26 5C380/CC02 5C380/CC04 5C380/CC07 5C380/CC26 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC41 5C380/CC52 5C380/CC62 5C380/CC65 5C380/CC77 5C380/CD012 5C380/CD015 5C380/DA02 5C380/DA06 5C380/DA47 5C380/HA05 |         |            |

| 代理人(译)         | 铃木信夫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

### 摘要(译)

要解决的问题：要在使用n沟道TFT的像素电路中实现高质量的图像显示，请提高产量，缩小像素电路的尺寸并提高清晰度。像素电路包括有机EL元件，存储电容器，采样晶体管，驱动晶体管，开关晶体管以及第一和第二检测晶体管。它具有存储电容器的自举功能，可以补偿驱动晶体管的阈值电压的波动和有机EL元件随时间的劣化，并可以补偿有机EL元件的I-V特性随时间的变化以及驱动晶体管的阈值电压的波动。然后，用于控制采样晶体管的导通的扫描线（采样晶体管的栅极线WSL）被共享作为经由第二检测晶体管T2提供给驱动晶体管T5的栅极的第二固定电势Vofs的供给线。但是，不必单独设置第二固定电位供给线。[选择图]图7