(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4910779号

(P4910779)

(45) 発行日 平成24年4月4日(2012.4.4)

(24) 登録日 平成24年1月27日(2012.1.27)

|                      |                |

|----------------------|----------------|

| (51) Int.Cl.         | F 1            |

| G09G 3/30 (2006.01)  | G09G 3/30 J    |

| G09F 9/30 (2006.01)  | G09F 9/30 338  |

| H01L 51/50 (2006.01) | H05B 33/14 A   |

| H05B 33/10 (2006.01) | H05B 33/10     |

| H01L 27/32 (2006.01) | G09F 9/30 365Z |

請求項の数 12 (全 26 頁) 最終頁に続く

(21) 出願番号 特願2007-52416 (P2007-52416)

(22) 出願日 平成19年3月2日 (2007.3.2)

(65) 公開番号 特開2008-216529 (P2008-216529A)

(43) 公開日 平成20年9月18日 (2008.9.18)

審査請求日 平成22年2月23日 (2010.2.23)

(73) 特許権者 000003193

凸版印刷株式会社

東京都台東区台東1丁目5番1号

(74) 代理人 110000408

特許業務法人高橋・林アンドパートナーズ

(72) 発明者 石 ▼崎▲ 守

東京都台東区台東1丁目5番1号 凸版印

刷株式会社内

審査官 福村 拓

最終頁に続く

(54) 【発明の名称】有機ELディスプレイおよびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁基板上に形成され、マトリクス状に配置された複数の画素回路を有する薄膜トランジスタ回路と、前記複数の画素回路に接続された複数のゲート線及び複数のソース線と、前記基板上に形成された有機EL層と、

を少なくとも含む有機ELディスプレイであって、

前記画素回路は、少なくとも第1の薄膜トランジスタ、第2及び第3の薄膜トランジスタ、キャパシタ並びに抵抗を有し、

前記第1の薄膜トランジスタのゲート電極、ソース電極、ドレイン電極は、それぞれ、前記ゲート線、前記ソース線、前記第2の薄膜トランジスタのゲート電極及び前記キャパシタの一方の電極に接続されており、

前記キャパシタの他方の電極は、定電位に接続されており、

前記第2の薄膜トランジスタはpチャネル型薄膜トランジスタであり、前記第2の薄膜トランジスタのソース電極、ドレイン電極は、それぞれ、電源電位、前記第3の薄膜トランジスタのゲート及び前記抵抗の一端に接続されており、

前記第3の薄膜トランジスタはnチャネル型薄膜トランジスタであり、前記第3の薄膜トランジスタのドレイン、ソースは、それぞれ、前記電源電位、前記抵抗の他端及び陽極に接続されており、

前記陽極と陰極との間に前記有機EL層を含むことを特徴とする有機ELディスプレイ。

## 【請求項 2】

10

20

前記第1の薄膜トランジスタは走査トランジスタであり、且つ、前記第2の薄膜トランジスタ及び前記第3の薄膜トランジスタは、前記有機ELを駆動する駆動トランジスタであることを特徴とする請求項1に記載の有機ELディスプレイ。

【請求項3】

前記抵抗の代わりに1つの負荷トランジスタが接続されていることを特徴とする請求項1又は2に記載の有機ELディスプレイ。

【請求項4】

前記負荷トランジスタはnチャネル型トランジスタであり、且つ、前記負荷トランジスタのゲートとドレインとが短絡していることを特徴とする請求項3記載の有機ELディスプレイ。

10

【請求項5】

前記第3の薄膜トランジスタ及び前記負荷トランジスタの半導体の材質、ゲート絶縁層の材質と厚さ、チャネル長がそれぞれ同じであることを特徴とする請求項3または4に記載の有機ELディスプレイ。

【請求項6】

前記第2の薄膜トランジスタは半導体層に有機物を用いたトランジスタであり、前記第3の薄膜トランジスタは半導体層に酸化物を用いたトランジスタであることを特徴とする請求項1～5の何れか一に記載の有機ELディスプレイ。

【請求項7】

前記絶縁基板がプラスチックであり、その上に酸素や水分を通しにくいバリア膜を設けていることを特徴とする請求項1～6の何れか一に記載の有機ELディスプレイ。

20

【請求項8】

前記絶縁基板、前記ゲート電極、前記ソース電極、前記ドレイン電極、前記ゲート絶縁層が透明であることを特徴とする請求項1～7の何れか一に記載の有機ELディスプレイ。

【請求項9】

請求項1～8の何れか一に記載の有機ELディスプレイの製造方法であって、前記絶縁基板上に第一半導体パターンを形成し、

第一電極パターンを形成し、

第一絶縁パターンを形成し、

第二電極パターンを形成し、

30

第二半導体パターンを形成し、

第二絶縁パターンを形成し、

第三電極を形成し、

前記有機EL層を形成し、

前記陰極を形成することを少なくとも有することを特徴とする有機ELディスプレイの製造方法。

【請求項10】

請求項1～8の何れか一に記載の有機ELディスプレイの製造方法であって、前記絶縁基板上に第一電極パターンを形成し、

第一絶縁パターンを形成し、

40

第一半導体パターンを形成し、

第二電極パターンを形成し、

第二半導体パターンを形成し、

第二絶縁パターンを形成し、

第三電極を形成し、

前記有機EL層を形成し、

前記陰極を形成することを少なくとも有することを特徴とする有機ELディスプレイの製造方法。

【請求項11】

前記絶縁基板上にあらかじめバリア膜を形成し、前記陰極を形成した後にバリア構造を形

50

成することを有することを特徴とする請求項 9 または 10 に記載の有機 E L ディスプレイの製造方法。

【請求項 12】

前記第二電極を形成した後、かつ、前記第二絶縁層を形成する前に、前記抵抗を形成することを有することを特徴とする請求項 9 ~ 11 の何れか一に記載の有機 E L ディスプレイの製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、フラットパネルディスプレイの一つである有機 E L ディスプレイに関する。 10

【背景技術】

【0002】

フラットパネルディスプレイとして、液晶ディスプレイやプラズマディスプレイが商品化されている。一般的に、液晶ディスプレイは視野角が狭く、高速画素信号に対して応答性が充分ではないという問題がある。また、プラズマディスプレイは消費電力が大きく、現在商品化されているもの以上の大型化を実現するためには技術的解決課題が多いという問題がある。

【0003】

液晶ディスプレイやプラズマディスプレイに対して最近注目されてきているのが、有機発光材料を用いた有機エレクトロルミネッセンスディスプレイ（有機 E L ディスプレイ）である。有機 E L ディスプレイは有機化合物を発光材料として用いているので、自発光であつて応答速度が高速であり、更に視野角依存性が無い低消費電力のフラットパネルディスプレイを実現できるものとして期待されている。 20

【0004】

有機 E L ディスプレイには、薄膜トランジスタ（ T F T ）を用いない単純マトリクス型と、 T F T を用いたアクティブマトリクス型とがある。単純マトリクス型の有機 E L ディスプレイは、ガラス基板上に形成された平行な複数の電極と、有機 E L 層と、前記平行な複数の電極に直交する複数の電極を有している。単純マトリクス型の有機 E L ディスプレイにおいては、選択された一瞬の間に有機 E L 層を高輝度に発光させる必要があり、有機 E L 層の劣化が激しいとともに、配線抵抗の影響が大きいという問題があった。一方、アクティブマトリクス型の有機 E L ディスプレイにおいては、ガラス基板上に T F T 回路を形成し、その上に有機 E L 層を形成し、さらに対向電極が形成される。通常、 T F T 回路を構成する半導体にはアモルファスシリコン（ a - S i ）またはポリシリコン（ p - S i ）が用いられる。また、対向電極側を陰極として用い、光を基板側から取り出すタイプ（下方出射タイプ（ボトムエミッションタイプ））が一般的である。 30

【0005】

ところが、アモルファスシリコンやポリシリコンを成膜する際には 250 以上の高温工程が必要であり、基板としてガラスを使う必要があった。また、アモルファスシリコンやポリシリコンを用いた T F T は可視光で光伝導性を有するため遮光が必須であり、基板側から取り出せる光は、不透明な T F T の面積を差し引いた部分に限られる。よって、アモルファスシリコンやポリシリコンを用いたアクティブマトリクス型の有機 E L ディスプレイは開口率（ = 発光面積 / 画素面積 ）が小さく、十分な画質を実現するためには、単純マトリクスほどではないものの高輝度で発光させる必要があった。 40

【0006】

一方、世の中ではフレキシブルディスプレイが求められている。フレキシブルディスプレイは、軽い、薄い、曲げられる、衝撃に強いなどの特長を有している。しかし、フレキシブルディスプレイに用いるプラスチック基板が熱に弱いため、高温プロセスに耐えることができず、シリコン系材料の使用が難しい。

【0007】

そこで注目されているのが、有機半導体を半導体層に用いた所謂「有機 T F T 」や、酸化

50

物半導体を半導体層に用いた所謂「酸化物 TFT」である。これらの TFT は、200 以下の低温プロセスで作製できるため、プラスチック基板上に形成することができる。

#### 【0008】

ところが有機 TFT は、安定して得られるのが p チャネル型の TFT のみであることと、移動度が  $1 \text{ cm}^2 / \text{V s}$  以下と小さいことが問題であった。また、酸化物 TFT は、良好な特性が得られるのは n チャネル型の TFT のみであることが問題であった。

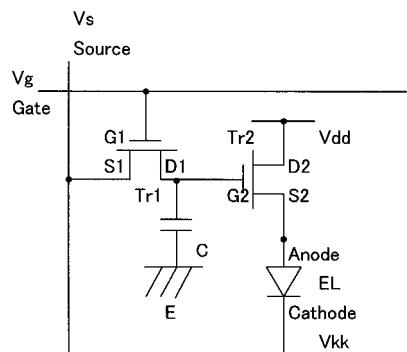

#### 【0009】

ところで、有機 EL に接続される TFT 回路は、基本構造として、図 11 に示すように走査トランジスタと駆動トランジスタとを有している（非特許文献 1）。走査トランジスタは p チャネル型でも n チャネル型でもよいが、高速応答特性が求められる。駆動トランジスタには大電流特性が求められ、かつ p チャネル型が好ましい。

10

#### 【0010】

【非特許文献 1】2003 FPD テクノロジー大全（電子ジャーナル） p.684

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0011】

本発明は上記問題を解決するためになされたものであり、有機 EL ディスプレイの駆動トランジスタとして、酸化物 TFT のような n チャネル型 TFT を、 p チャネル型のように用いることができる有機 EL ディスプレイを実現することを課題とする。また、有機 TFT のような p チャネル型 TFT を用いた場合であっても大電流駆動を行うことができる有機 EL ディスプレイを実現することを課題とする。

20

#### 【0012】

請求項 1 に係る本発明によると、

絶縁基板上に形成され、マトリクス状に配置された複数の画素回路を有する薄膜トランジスタ回路と、前記複数の画素回路に接続された複数のゲート線及び複数のソース線と、前記基板上に形成された有機 EL 層と、

を少なくとも含む有機 EL ディスプレイであって、

前記画素回路は、少なくとも第 1 の薄膜トランジスタ、第 2 及び第 3 の薄膜トランジスタ、キャパシタ並びに抵抗を有し、

前記第 1 の薄膜トランジスタのゲート電極、ソース電極、ドレイン電極は、それぞれ、前記ゲート線、前記ソース線、前記第 2 の薄膜トランジスタのゲート電極及び前記キャパシタの一方の電極に接続されており、

30

前記キャパシタの他方の電極は、定電位に接続されており、

前記第 2 の薄膜トランジスタは p チャネル型薄膜トランジスタであり、前記第 2 の薄膜トランジスタのソース電極、ドレイン電極は、それぞれ、電源電位、前記第 3 の薄膜トランジスタのゲート及び前記抵抗の一端に接続されており、

前記第 3 の薄膜トランジスタは n チャネル型薄膜トランジスタであり、前記第 3 の薄膜トランジスタのドレイン、ソースは、それぞれ、前記電源電位、前記抵抗の他端及び陽極に接続されており、

前記陽極と陰極との間に前記有機 EL 層を含むことを特徴とする有機 EL ディスプレイが提供される。

40

#### 【0013】

請求項 2 に係る本発明によると、前記第 1 の薄膜トランジスタは走査トランジスタであり、且つ、前記第 2 の薄膜トランジスタ及び前記第 3 の薄膜トランジスタは、前記有機 EL を駆動する駆動トランジスタである。

#### 【0014】

請求項 3 に係る本発明によると、前記抵抗の代わりに 1 つの負荷トランジスタが接続されているようにしてもよい。

#### 【0015】

請求項 4 に係る本発明によると、前記負荷トランジスタは n チャネル型トランジスタであ

50

り、且つ、前記負荷トランジスタのゲートとドレインとが短絡しているようにしてもよい。

【0016】

請求項5に係る本発明によると、前記第3の薄膜トランジスタ及び前記負荷トランジスタの半導体の材質、ゲート絶縁層の材質と厚さ、チャネル長がそれぞれ同じであるようにしてもよい。

【0017】

請求項6に係る本発明によると、前記第2の薄膜トランジスタは半導体層に有機物を用いたトランジスタであり、前記第3の薄膜トランジスタは半導体層に酸化物を用いたトランジスタであるようにしてもよい。

10

【0018】

請求項7に係る本発明によると、前記絶縁基板がプラスチックであり、その上に酸素や水分を通しにくいバリア膜を設けるようにしてもよい。

【0019】

請求項8に係る本発明によると、前記絶縁基板、前記ゲート電極、前記ソース電極、前記ドレイン電極、前記ゲート絶縁層が透明であるようにしてもよい。

【0020】

請求項9に係る本発明によると、上述の請求項1～8に係る本発明の有機ELディスプレイの製造方法であって、

前記絶縁基板上に第一半導体パターンを形成し、

20

第一電極パターンを形成し、

第一絶縁パターンを形成し、

第二電極パターンを形成し、

第二半導体パターンを形成し、

第二絶縁パターンを形成し、

第三電極を形成し、

前記有機EL層を形成し、

前記陰極を形成することを少なくとも有することを特徴とする有機ELディスプレイの製造方法が提供される。

【0021】

30

請求項10に係る本発明によると、上述の請求項1～8に係る本発明の有機ELディスプレイの製造方法であって、

前記絶縁基板上に第一電極パターンを形成し、

第一絶縁パターンを形成し、

第二電極パターンを形成し、

第二半導体パターンを形成し、

第二絶縁パターンを形成し、

第三電極を形成し、

前記有機EL層を形成し、

前記陰極を形成することを少なくとも有することを特徴とする有機ELディスプレイの製造方法が提供される。

【0022】

40

前請求項11に係る本発明によると、記絶縁基板上にあらかじめバリア膜を形成し、前記陰極を形成した後にバリア構造を形成するようにしてもよい。

【0023】

前請求項11に係る本発明によると、前記第二電極を形成した後、かつ、前記第二絶縁層を形成する前に、前記抵抗を形成するようにしてもよい。

【発明の効果】

【0024】

50

本発明によれば、駆動トランジスタとしてpチャネルTFTとnチャネルTFTを組み合わせることにより、pチャネル形の動作とnチャネル様の高性能を両立させることができ、良好な有機ELディスプレイを実現できる。また、本発明によれば、有機TFTのようなpチャネル型TFTを用いた場合であっても大電流駆動を行うことができる。

【発明を実施するための最良の形態】

【0025】

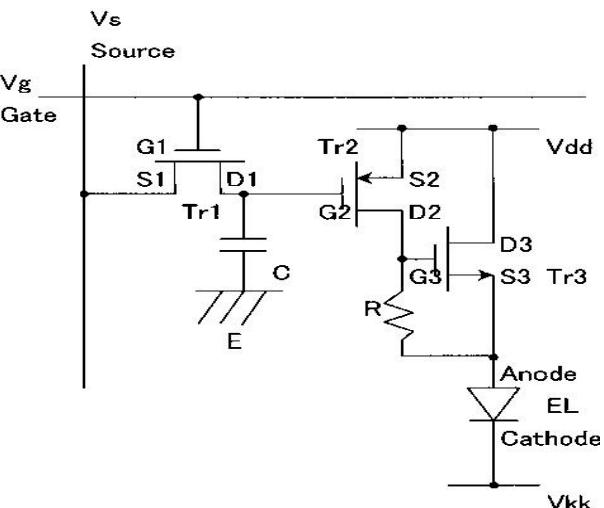

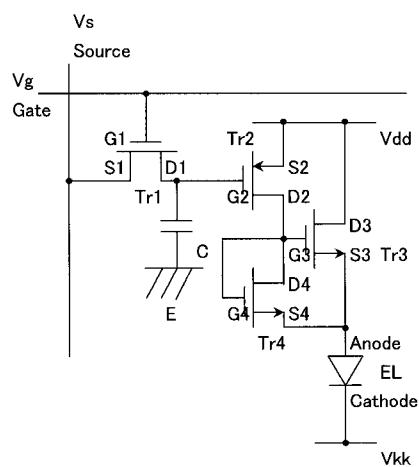

以下、本発明の実施の形態を図面に基づいて説明する。図1は、本実施形態に係る本発明の有機ELディスプレイの画素部のTFT回路を構成する画素回路の回路構成図である。本実施形態に係る本発明の有機ELディスプレイの画素部のTFT回路は、図1に示すように、1画素当たりの画素回路において、薄膜トランジスタTr1、薄膜トランジスタTr2、薄膜トランジスタTr3、負荷抵抗R及びキャパシタCを有している。ここで、説明の便宜上、薄膜トランジスタTr1を走査トランジスタといい、薄膜トランジスタTr2、Tr3をそれぞれ駆動トランジスタTr2、Tr3という。本実施形態に係る本発明の有機ELディスプレイにおいては、図1に示すとおり、駆動トランジスタTr2はpチャネル型であり、駆動トランジスタTr3はnチャネル型である。走査トランジスタTr1はpチャネル型でもnチャネル型でもよいが、応答が速い方が望ましい。キャパシタCの対向電極の電位Eは、定電位点であればGNDでなくてもよく、例えばVddでもよい。

【0026】

本実施形態に係る本発明の有機ELディスプレイにおいては、走査トランジスタTr1のゲート電極G1、ソース電極S1、ドレイン電極D1は、それぞれ、ゲート線(走査線)(Gate)、ソース線(データ線)(Source)、駆動トランジスタTr2のゲート電極G2及びキャパシタCの一方の電極に接続されている。また、駆動トランジスタTr2のソース電極S2、ドレイン電極D2は、それぞれ、電源電位Vdd、負荷抵抗Rの一端及び駆動トランジスタTr3のゲート電極G3に接続されている。また、駆動トランジスタTr3のドレイン電極D3、ソース電極S3は、それぞれ、電源電位Vdd、EL層の陽極(Anode)に接続されている。負荷抵抗Rの他端は、EL層の陽極(Anode)に接続されている。また、EL層の陰極は共通電位Vkkに接続されている。

【0027】

本実施形態に係る本発明の有機ELディスプレイにおいては、走査トランジスタTr1のソース電極S1にソース線(Source)を通して信号電圧Vsを印加した状態で、ゲート線(Gate)に印加するゲート電圧Vgを所定の選択電位にすると、信号電圧VsがキャパシタCに書き込まれる。そして、駆動トランジスタTr2のソース電極S2・ゲート電極G2間電圧(Vdd - Vs)によって決まる電流Iが駆動トランジスタTr2に流れ。すると、その電流Iによって決まる電圧が抵抗Rの両端に発生する。そして、その電圧によって決まる電流Id3が駆動トランジスタTr3に流れ、負荷抵抗Rを流れる電流Iとの和IELがEL層に流れ。この電流IELによってEL層が駆動される。ここで、EL層を流れる電流IELは、下記式(1)で与えられる。ここで、μはTr3の移動度、LはTr3のチャネル長、W3はTr3のチャネル幅、CoxはTr3のゲート絶縁膜の単位面積当りのキャパシタンス、VtはTr3のしきい値である。Vt = RIかつ相互コンダクタンスgm = μWCox(RI - Vt)/Lなら、IELはI^2に比例する。

$$I_{EL} = I + \frac{\mu W_3}{2L} Cox (RI - V_t)^2 \quad \dots (1)$$

【0028】

本実施形態に係る有機ELディスプレイをフレキシブルディスプレイとするためにプラスチック基板を用いる場合、他の理由で製造プロセス温度を上げたくない場合、また、開口率を大きくしたい場合は、pチャネル型トランジスタに有機TFTを用い、nチャネルトランジスタに酸化物TFTを用いるのが望ましい。有機TFT及び酸化物TFTは、製造

に要するプロセス温度が200℃以下であり、プラスチック基板を使用することができる。この場合、走査トランジスタには移動度の大きいnチャネル型トランジスタ（酸化物TFT）を用いるのが望ましい。また、酸化物半導体は透明であり、可視光での光伝導が小さいので、基板、電極、絶縁層にも透明な材料を用いることによって、開口率を上げることができる。

#### 【0029】

本実施形態に係る有機ELディスプレイの基板1としては、ガラスを用いることもできるが、例えば、ポリエチレンテレフタレート（PET）、ポリエチレンナフタレート（PEN）、ポリエーテルスルホン（PES）、ポリイミド（PI）などのプラスチック材料を用いることもできる。また、基板にプラスチックを用いる場合、TFT、有機EL層及び陰極を保護する目的で、バリア層を設けることが望ましい。バリア層は酸素や水分を透過しにくいものであり、 $\text{SiO}_x$ 、 $\text{SiON}$ 、 $\text{Al}_2\text{O}_3$ 、 $\text{Y}_2\text{O}_3$ 等の無機膜や、無機膜とアクリル等の有機膜との積層構造などを用いることができる。バリア層の成膜には、CVD、蒸着、スパッタ等を用いることができる。

10

#### 【0030】

また、陰極形成後にバリア構造を設けることが望ましい。バリア構造は、前記バリア層と同じでもよいが、ガラスや金属の構造体の周囲に接着剤を付けて貼り付けてもよい。その場合、内部に乾燥剤を配置してもよい。

#### 【0031】

本実施形態において、酸化物TFTに用いる酸化物半導体としてはIn、Ga、Zn、Sn、Mgのいずれかを含む酸化物を用いることができる。具体的には、酸化インジウム、酸化亜鉛、酸化スズ、Zn-Mg酸化物、In-Ga-Zn酸化物、 $\text{In}_{x}\text{Zn}_{1-x}$ 酸化物、 $\text{In}_{x}\text{Sn}_{1-x}$ 酸化物、 $\text{In}_{x}(\text{Zn}, \text{Sn})_{1-x}$ 酸化物、Ga-Sn酸化物、In-Ga-Sn酸化物、In-Ga-Zn-Mg酸化物などを用いることができる。これらの酸化物半導体は、スパッタ、レーザアブレーション、蒸着等で成膜することができる。特にIn-Ga-Zn酸化物は、室温以上200℃以下のいずれの温度でスパッタ成膜しても、移動度5cm²/Vs以上を容易かつ再現性よく得ることができ、酸化物TFTに用いる酸化物半導体としては好適な材料である。また、In-Ga-Zn-Mg酸化物はIn-Ga-Zn酸化物と同等の移動度を有し、さらにバンドギャップが大きいので紫外線に強い（誤動作しにくい）という特徴を有している。ここで、In-Ga-Zn酸化物は、組成比がIn:Ga:Zn:O=1:1:1:4に近いものであるが、実際には若干の酸素空孔が存在し、若干の金属組成ずれがあっても特性は変わらないので、組成比はIn:Ga:Zn:O=(0.7~1.3):(0.7~1.3):(0.7~1.3):(3~4)が許容される。また、In-Ga-Zn-Mg酸化物はアモルファス状態を基本とするが、一部微結晶構造を含有していてもよい。なお、In-Ga-Zn-Mg酸化物は、In-Ga-Zn酸化物のZnの一部（例えば50%以下）をマグネシウム（Mg）に置き換えたものである。これらの酸化物半導体をスパッタ成膜する場合は、RFあるいはDCの反応性スパッタが好適である。

20

#### 【0032】

本実施形態において、有機TFTに用いる有機半導体としては、ポリチオフェン誘導体、ポリフェニレンビニレン誘導体、ポリチエニレンビニレン誘導体、ポリアリルアミン誘導体、ポリアセチレン誘導体、アセン誘導体、オリゴチオフェン誘導体等を用いることができる。これらの有機半導体は、ディスペンサ、インクジェット、フレキソ印刷、反転印刷等の印刷法や、マスク蒸着等によって形成することができる。

30

#### 【0033】

本実施形態において、ソース／ドレイン電極やキャパシタの電極としては、酸化インジウム錫（ITO）、酸化インジウム亜鉛（IZO）等が好適に用いられる。電極に透明性を要しない場合にはAl、Ag、Au、Pt、Pd、Ni、Cr、Mo、Ti、Sn等の金属を用いてもよい。絶縁層としては、 $\text{SiO}_2$ 、 $\text{SiON}$ 、 $\text{Al}_2\text{O}_3$ 、 $\text{Y}_2\text{O}_3$ 等が好適に用いられる。これらの絶縁材料も、室温以上200℃以下の温度で、スパッタ、レーザアブレーション、蒸着等によって成膜することができる。特に、反応性スパ

40

50

ツタが好適である。また、絶縁層に対しポストアニールを行ってもよい。ポストアニールの温度も、200以下でよい。また、絶縁層に透明な有機絶縁層を用いることも可能である。例えば絶縁層にフッ素樹脂やポリビニルアルコール、エポキシ、アクリル等を用いることができる。感光性樹脂ならば、パターニングが容易である。さらには、異種の絶縁層を重ねて用いてもよい。

#### 【0034】

本実施形態に係る有機ELディスプレイにおいては、画素回路がマトリクス状に配置されている。駆動トランジスタTr3のソースに接続された上部画素電極がELディスプレイの陽極(Anode)となり、その上に有機EL層が積層される。本実施形態に係る有機ELディスプレイにおいては、有機EL層としては、正孔輸送層41、発光層42等の積層構造を用いるようにしてもよい。10

#### 【0035】

本実施形態に係る有機ELディスプレイにおいて、正孔輸送層41をなす材料としては、ポリアニリン誘導体、ポリチオフェン誘導体、ポリビニルカルバゾール誘導体、ポリ(3,4-エチレンジオキシチオフェン)とポリスチレンスルホン酸との混合物(PEDOT:PSS)等の導電性高分子材料が挙げられる。これらの正孔輸送材料は、トルエン、キシレン、アセトン、メチルエチルケトン、メチルイソブチルケトン、シクロヘキサン、メタノール、エタノール、イソプロピルアルコール、酢酸エチル、酢酸ブチル、水等の単独または混合溶媒に溶解または分散させ、スピンドルコート、バーコート、ワイヤーコート、スリットコート等のコーティング法により塗布することができる。また、必要に応じてパターニングを行っても良い。更に、正孔輸送層41には必要に応じて、界面活性剤、酸化防止剤、粘度調整剤、紫外線吸収剤等を添加してもよい。正孔輸送層41の膜厚は、10nmないし200nmの範囲が好ましい。あるいは、TPD(トリフェニルジアミン)、20

-NPD(ビス[N-ナフチル-N-フェニル]ベンジデイン)などの低分子材料を用いてもよい。

#### 【0036】

実施形態に係る有機ELディスプレイにおいて、正孔輸送層41の上に発光層42を積層する。発光層42は、単層構造に限らず、さらに電荷輸送層等を設けた多層構造であってもよい。発光層42としては、例えば、クマリン系、ペリレン系、ピラン系、アンスロン系、ポルフィリン系、キナクリドン系、N,N'-ジアルキル置換キナクリドン系、ナフトアルイミド系、N,N'-ジアリール置換ピロロピロール系、イリジウム錯体系等の有機溶剤に可溶な有機発光材料や該有機発光材料をポリスチレン、ポリメチルメタクリレート、ポリビニルカルバゾール等の高分子中に分散させたものや、ポリアリーレン系、ポリアリーレンビニレン系やポリフルオレン系などの高分子蛍光体を用いることができる。これらの高分子蛍光体はトルエン、キシレン、アセトン、メチルエチルケトン、メチルイソブチルケトン、シクロヘキサン、メタノール、エタノール、イソプロピルアルコール、酢酸エチル、酢酸ブチル、水等の単独または混合溶媒に溶解し、スピンドルコート法、カーテンコート法、バーコート法、ワイヤーコート法、スリットコート法等のコーティング法により塗布することができる。また、これらの高分子蛍光体は、印刷法により形成することができる。また、高分子蛍光体層には必要に応じて、界面活性剤、酸化防止剤、粘度調整剤、紫外線吸収剤等を添加してもよい。発光層42の膜厚は、単層または多層構造いずれの場合にも合わせて1000nm以下が好ましく、より好ましくは合わせて50nmないし30150nmの範囲であるのが好ましい。あるいは、アルミキノリン錯体やジスチリル誘導体等に、キナクリドン、クマリン誘導体、ルブレン、DCM(4-(Dicyanomethylidene)-2-methyl-6-(p-dimethylaminostyryl)-4H-pyran)誘導体、ペリレン、イリジウム錯体等をドーピングした低分子蛍光体を用いることができる。

#### 【0037】

低分子蛍光体では、発光色は材料自体やドーパントで決まる。実施形態に係る有機ELディスプレイにおいて、青色発光としてはジスチルアリーレン誘導体にスチリルアリーレン40

誘導体やスチリルアミン誘導体をドープしたものなど、緑色発光としてはアルミキノリン錯体など、赤色発光としてはアルミキノリン錯体にDCMをドープしたものなど、白色発光としては青色発光材料と黄～橙色発光材料を積層した構造などが用いられる。一方、高分子蛍光体では、発光色は側鎖を替えることによって調整が可能であり、RGBとも、同一の基本骨格を持つ高分子を用いることができる。また、それらを混合することで白色発光が得られる。

#### 【0038】

実施形態に係る有機ELディスプレイにおいて、有機EL層をRGB塗り分け方式とする場合、低分子発光層の場合にはマスク蒸着で行うことになるが、大面積に均一な塗り分けを行うのは困難である。高分子発光層を用いる場合には印刷法を用いることができ、大面積に均一な塗り分けを行うことができる。印刷法としては、インクジェット、反転印刷、フレキソ印刷等を用いることができる。特にフレキソ印刷は、大面積に均一な印刷を短時間に行うことができて、最も好ましい。なお、マスク蒸着でも、インクジェット、反転印刷、フレキソ印刷等の印刷法でも、基板温度は室温でよい。また、塗り分けに先立ち、正孔輸送層41形成前に、塗り分け境界に隔壁を設けておいてもよい。隔壁としては、レジスト等を用いることができる。

10

#### 【0039】

実施形態に係る有機ELディスプレイにおいて、陰極5としては、有機EL層の発光特性に応じたものを使用でき、例えば、リチウム、マグネシウム、カルシウム、イッテルビウム、アルミニウムなどの金属単体やこれらの合金、あるいはこれらと金、銀などの安定な金属との合金などを用いることができる。これらの材料は、通常の抵抗加熱、EB加熱などの真空蒸着法などで形成することができ、膜厚は特に限定されないが、1nm以上500nm以下の範囲が好ましい。また、フッ化リチウムなどの薄膜を陰極層と発光層との間に設けてもよい。

20

#### 【0040】

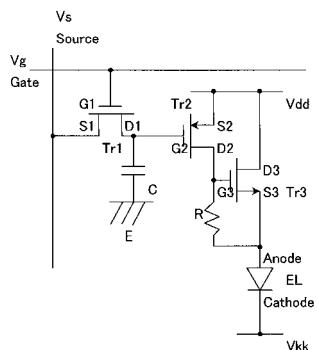

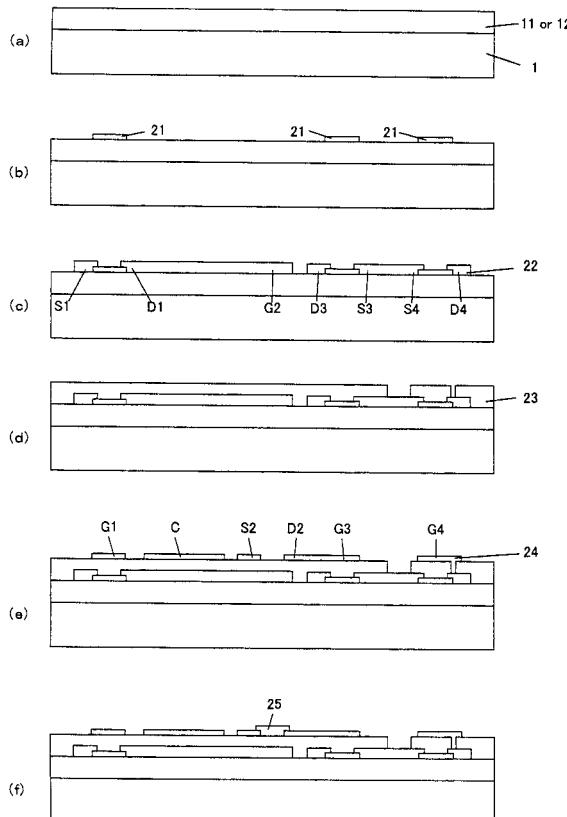

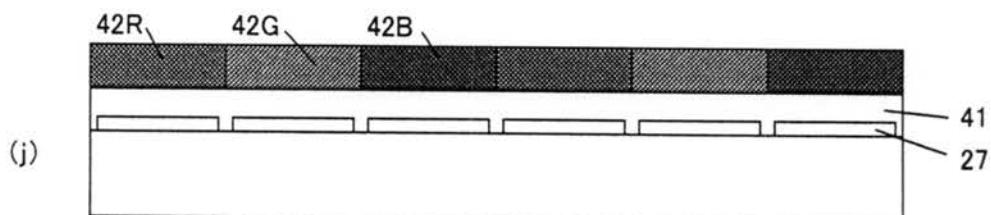

次に、本実施形態に係る本発明の有機ELディスプレイの製造方法について詳細に述べる。図2は図1に示す本実施形態に係る本発明の有機ELディスプレイの画素回路(TFT回路)の平面図(図2(a))及び断面図(図2(b))であり、その製造工程を図3A及び図3Bに示す。なお、図3A及び図3Bにおいては、図3(a)～(i)は1画素回路(1サブピクセル)分の断面図を示しており、図3(j)～(l)は画素回路6個(6サブピクセル)分の断面図を示しており、図3(m)は本実施形態に係る本発明のELディスプレイの全体の断面図を示している。

30

#### 【0041】

まず、基板1上に、バリア膜11を形成する(図3(a))。次に、Tr1およびTr3の半導体層となる第一半導体層21として酸化物半導体を反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図3(b))。そして、ソース電極(S1)、ドレイン電極(D1)兼ゲート電極(G2)、ソース電極(S3)、ドレイン電極(D3)を含む第一電極層22としてITOを反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図3(c))。

40

#### 【0042】

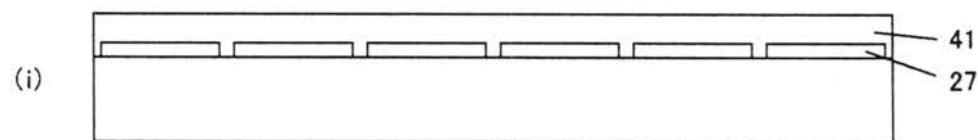

次に、ゲート絶縁層となる第一絶縁層23を反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図3(d))。さらにゲート電極(G1)、キャパシタ(C)の電極、ソース電極(S2)、ドレイン電極(D2)兼ゲート電極(G3)を含む第二電極層24としてITOを反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図3(e))。そして、抵抗ペーストをスクリーン印刷する等の方法によって抵抗体3を形成する(図3(f))。さらに、Tr2の半導体層となる第二半導体層25をディスペンサ等によって成膜する(図3(g))。次に、層間絶縁膜となる第二絶縁層26を成膜しパターニングする(図3(h))。さらに、画素電極となる第三電極層27を成膜しパターニングする(図3(i))。

#### 【0043】

50

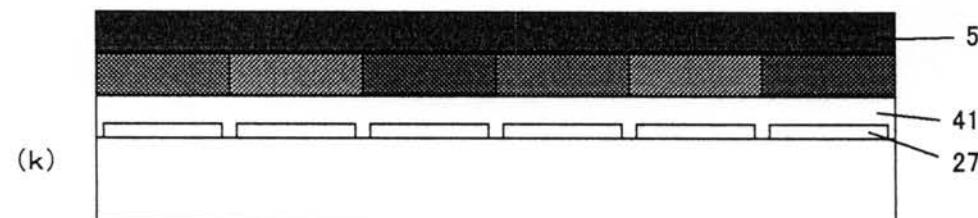

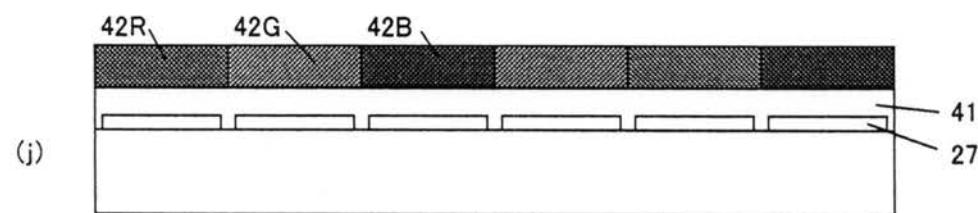

そして、有機EL層4を形成する。まず、全面に正孔輸送層41を塗布する(図3(j))。次に、フレキソ印刷等によって発光層42R、42G、42Bを形成する(図3(k))。

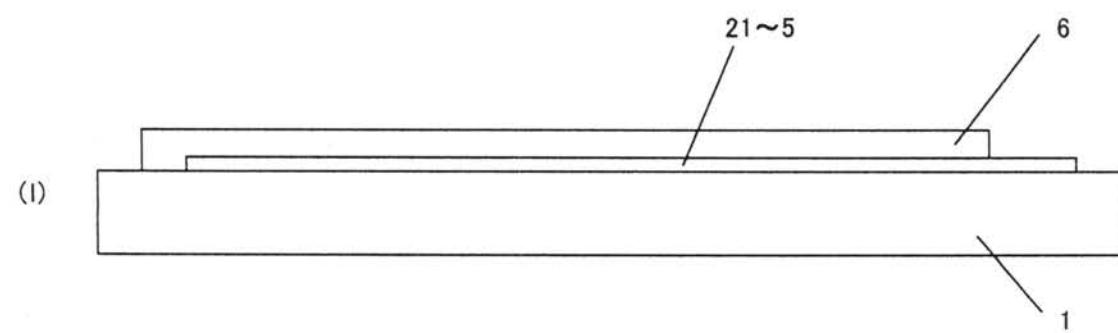

#### 【0044】

さらに、蒸着によって陰極5を全面に成膜する(図3(l))。最後に、全体をガラス板や金属板で覆うか、封止層を成膜する等の方法によって、バリア構造6を形成することが望ましい(図3(m))。ガラス板や金属板は、エポキシ等の接着剤でシールすることができ、試料とガラス板や金属板の空隙に乾燥剤を入れるようにしてもよい。

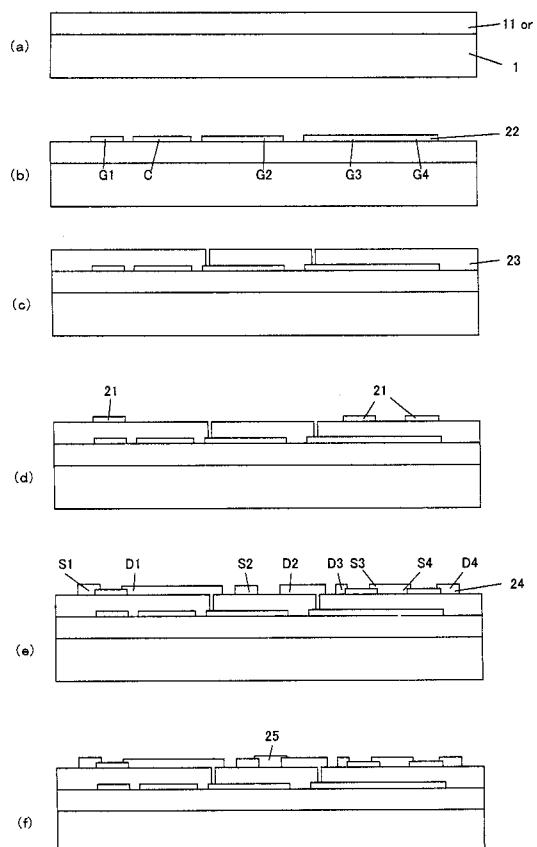

#### 【0045】

(実施形態2)本実施形態2においては、実施形態1とは画素回路の構成が異なる本発明の有機ELディスプレイについて説明する。なお、実施形態1に係る本発明の有機ELディスプレイと同様の構成については、ここでは改めて説明しない場合がある。

10

#### 【0046】

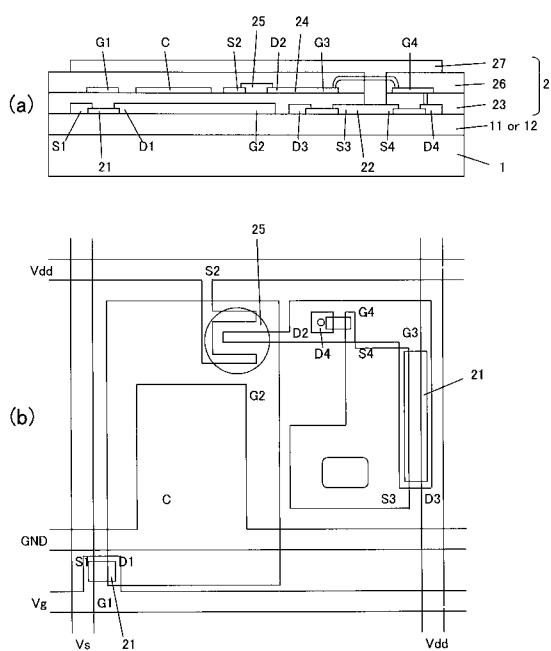

図4は、本実施形態に係る本発明の有機ELディスプレイの画素部のTFT回路を構成する画素回路の回路構成図である。本実施形態に係る本発明の有機ELディスプレイの画素部のTFT回路は、図4に示すように、1画素当たりの画素回路において、薄膜トランジスタTr1、薄膜トランジスタTr2、薄膜トランジスタTr3、薄膜トランジスタTr4及びキャパシタCを有している。ここで、説明の便宜上、実施形態1と同様、薄膜トランジスタTr1を走査トランジスタといい、薄膜トランジスタTr2、Tr3をそれぞれ駆動トランジスタTr2、Tr3という。また、薄膜トランジスタTr4を負荷トランジスタとい。本実施形態に係る本発明の有機ELディスプレイにおいては、図4に示すとおり、駆動トランジスタTr2はpチャネル型であり、駆動トランジスタTr3はnチャネル型であり、負荷トランジスタTr4はnチャネル型トランジスタである。走査トランジスタTr1はpチャネル型でもnチャネル型でもよいが、応答が速い方が望ましい。キャパシタCの対向電極の電位(E)は、定電位点であればGNDでなくてもよく、例えばVddでもよい。

20

#### 【0047】

本実施形態に係る本発明の有機ELディスプレイにおいては、走査トランジスタTr1のゲート電極G1、ソース電極S1、ドレイン電極D1は、それぞれ、ゲート線(走査線)(Gate)、ソース線(データ線)(Source)、駆動トランジスタTr2のゲート電極G2及びキャパシタCの一方の電極に接続されている。また、駆動トランジスタTr2のソース電極S2、ドレイン電極D2は、それぞれ、電源電位Vdd、負荷トランジスタTr4のゲート電極G4及びドレイン電極D4並びに駆動トランジスタTr3のゲート電極G3に接続されている。また、駆動トランジスタTr3のドレイン電極D3、ソース電極S3は、それぞれ、電源電位Vdd、EL層の陽極(Node)に接続されている。また、負荷トランジスタTr4のソース電極は、EL層の陽極(Node)に接続されている。また、EL層の陰極は共通電位(Vkk)に接続されている。

30

#### 【0048】

本実施形態に係る本発明の有機ELディスプレイにおいては、走査トランジスタTr1のソースS1にソース線(Source)を通して信号電圧Vsを印加した状態で、ゲート線(Gate)に印加するゲート電圧Vgを所定の選択電位にすると、信号電圧VsがキャパシタCに書き込まれる。そして、駆動トランジスタTr2のソース電極S2・ゲート電極G2間電圧(Vdd-Vs)によって決まる電流Iが駆動トランジスタTr2に流れ。すると、その電流Iできまる電圧が負荷トランジスタTr4の両端に発生する。そして、その電圧によって決まる電流が駆動トランジスタTr3に流れ、駆動トランジスタTr4を流れる電流との和IELがEL層に流れる。この電流IELによってEL層が駆動される。ここで、EL層を流れる電流は、下記式(2)で与えられる。ここで、 $\mu$ はTr3およびTr4の移動度、LはTr3およびTr4のチャネル長、W3はTr3のチャネル幅、W4はTr4のチャネル幅、CoxはTr3およびTr4のゲート絶縁膜の単位面積当りのキャパシタンス、VtはTr3およびTr4のしきい値である。なお、Tr3と

40

50

$T_{r4}$  の半導体の材質と厚さ、ゲート絶縁層の材質と厚さ、チャネル長がそれぞれ同じであれば、 $\mu$ 、 $L$ 、 $C_{ox}$ 、 $V_t$  は等しいと見なせる。この場合、 $V_t$  が小さければ  $I_{EL}$  は  $I$  に比例する。その比例係数はチャネル幅のみで決定でき、設計が容易である。

$$I_{EL} = \frac{W_3 + W_4}{W_4} I + \frac{\mu W_3}{2L} C_{ox} V_t^2 \dots \quad (2)$$

#### 【0049】

実施形態 1 と同様、本実施形態 2 に係る有機 EL ディスプレイをフレキシブルディスプレイするためにプラスチック基板を用いる場合、他の理由で製造プロセス温度を上げたくない場合、また、開口率を大きくしたい場合は、p チャネル型トランジスタに有機 TFT を用い、n チャネルトランジスタに酸化物 TFT を用いるのが望ましい。有機 TFT 及び酸化物 TFT は、製造に要するプロセス温度が 200 以下であり、プラスチック基板を使用することができる。この場合、走査トランジスタには移動度の大きい n チャネル型トランジスタ（酸化物 TFT）を用いるのが望ましい。また、酸化物半導体は透明であり、可視光での光伝導が小さいので、基板、電極、絶縁層にも透明な材料を用いることによって、開口率を上げることができる。

#### 【0050】

また、本実施形態に係る有機 EL ディスプレイの基板 1 としては、実施形態 1 で説明したものと同様のものを用いることができる。

#### 【0051】

また、本実施形態に係る有機 EL ディスプレイにおいては、実施形態 1 と同様、陰極形成後にバリア構造を設けることが望ましい。バリア構造は、前記バリア層と同じでもよいが、ガラスや金属の構造体の周囲に接着剤を付けて貼り付けてもよい。その場合、内部に乾燥剤を配置してもよい。

#### 【0052】

本実施形態に係る有機 EL ディスプレイにおいても、実施形態 1 と同様、酸化物 TFT 及び有機 TFT を用いることができる。本実施形態に用いる酸化物 TFT 及び有機 TFT は、実施形態 1 と同様のものを用いることができる。

#### 【0053】

また、本実施形態におけるソース / ドレイン電極やキャパシタの電極などの電極、絶縁膜、としては、実施形態 1 と同様の材料を用いることができる。

#### 【0054】

本実施形態に係る有機 EL ディスプレイにおいては、実施形態 1 と同様、画素回路がマトリクス状に配置されている。駆動トランジスタ  $T_{r3}$  のソースに接続された上部画素電極が EL ディスプレイの陽極（Anode）となり、その上有機 EL 層が積層される。本実施形態に係る有機 EL ディスプレイにおいては、実施形態 1 と同様、有機 EL 層としては、正孔輸送層 41、発光層 42 等の積層構造を用いるようにしてもよい。本実施形態 2 においても、実施形態 1 と同様の正孔輸送層 41、発光層 42 等を用いることができる。

#### 【0055】

実施形態に係る有機 EL ディスプレイにおいて、陰極 5 としては、有機 EL 層の発光特性に応じたものを使用でき、実施形態 1 と同様のものを用いることができる。また、フッ化リチウムなどの薄膜を陰極層と発光層との間に設けてもよい。

#### 【0056】

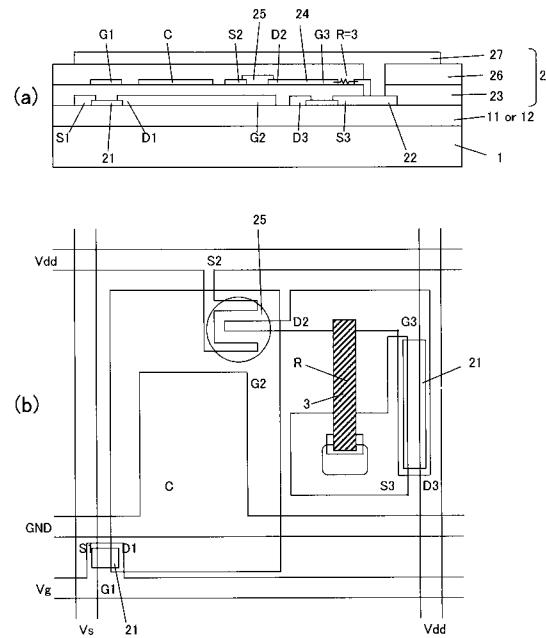

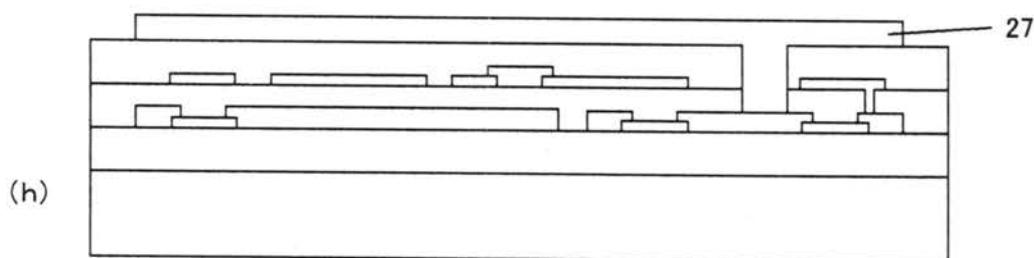

次に、本実施形態 2 に係る本発明の有機 EL ディスプレイの製造方法の例について詳細に述べる。図 5 は図 4 に示す本実施形態に係る本発明の有機 EL ディスプレイの画素回路（TFT 回路）の平面図（図 5(a)）及び断面図（図 5(b)）であり、その製造工程を図 6 A 及び図 6 B に示す。図 5において駆動トランジスタ  $T_{r3}$  のゲート電極（G3）と負荷トランジスタ  $T_{r4}$  のゲート電極（G4）とは断面図以外の部分にて接続されている

10

20

30

40

50

ことを示している。なお、図6 A及び図6 Bにおいては、図6 ( a ) ~ ( h ) は1画素回路(1サブピクセル)分の断面図を示しており、図6 ( i ) ~ ( k ) は画素回路6個(6サブピクセル)分の断面図を示しており、図6 ( l ) は本実施形態に係る本発明のELディスプレイの全体の断面図を示している。

#### 【0057】

まず、基板1上に、バリア膜11を形成する(図6 ( a ) )。次に、Tr1およびTr3の半導体層となる第一半導体層21として酸化物半導体を反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図6 ( b ) )。そして、ソース電極(S1)、ドレイン電極(D1)兼ゲート電極(G2)、ソース電極(S3)兼ソース電極(S4)、ドレイン電極(D3)、ドレイン電極(D4)を含む第一電極層22としてITOを反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図6 ( c ) )。

#### 【0058】

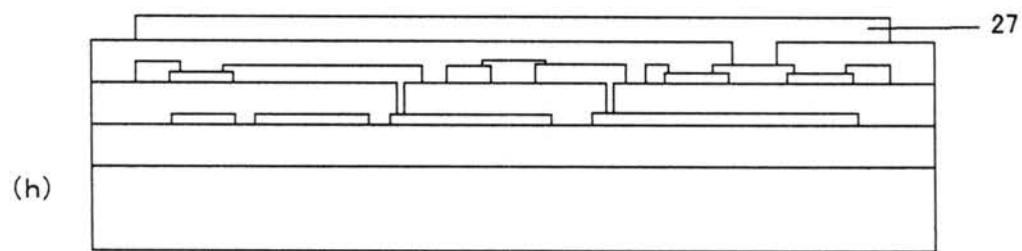

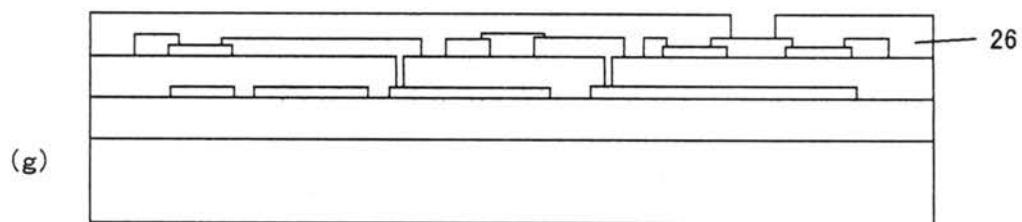

次に、ゲート絶縁層となる第一絶縁層23を反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図6 ( d ) )。さらにゲート電極(G1)、キャパシタ電極(C)、ソース電極(S2)、ドレイン電極(D2)兼ゲート電極(G3)兼ゲート電極(G4)を含む第二電極層24としてITOを反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図6 ( e ) )。さらに、Tr2の半導体層となる第二半導体層25をディスペンサ等によって成膜する(図6 ( f ) )。次に、層間絶縁膜となる第二絶縁層26を成膜しパターニングする(図6 ( g ) )。さらに、画素電極となる第三電極層27を成膜しパターニングする(図6 ( h ) )。

#### 【0059】

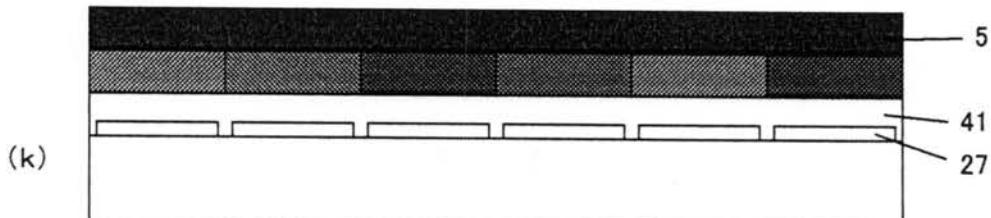

そして、有機EL層4を形成する。まず、全面に正孔輸送層41を塗布する(図6 ( i ) )。次に、フレキソ印刷等によって発光層42R、42G、42Bを形成する(図6 ( j ) )。

#### 【0060】

さらに、蒸着によって陰極5を全面に成膜する(図6 ( k ) )。最後に、全体をガラス板や金属板で覆うか、封止層を成膜する等の方法によって、バリア構造6を設けることが望ましい(図6 ( l ) )。ガラス板や金属板は、エポキシ等の接着剤でシールすることができ、試料とガラス板や金属板の空隙に乾燥剤を入れるようにしてもよい。

#### 【0061】

(実施形態3) 本実施形態3に係る本発明の有機ELディスプレイの画素回路(TFT回路)の回路構成は、実施形態1に係る本発明の有機ELディスプレイの画素回路(TFT回路)の回路構成と同様である。本実施形態3においては、実施形態1に係る本発明の有機ELディスプレイの画素回路のデバイス構造とは異なるデバイス構造を有する有機ELディスプレイについて説明する。なお、本実施形態3においては、実施形態1と同様の構成については、用いる材料等を含め、重複した説明を避けるため再度説明しない場合がある。

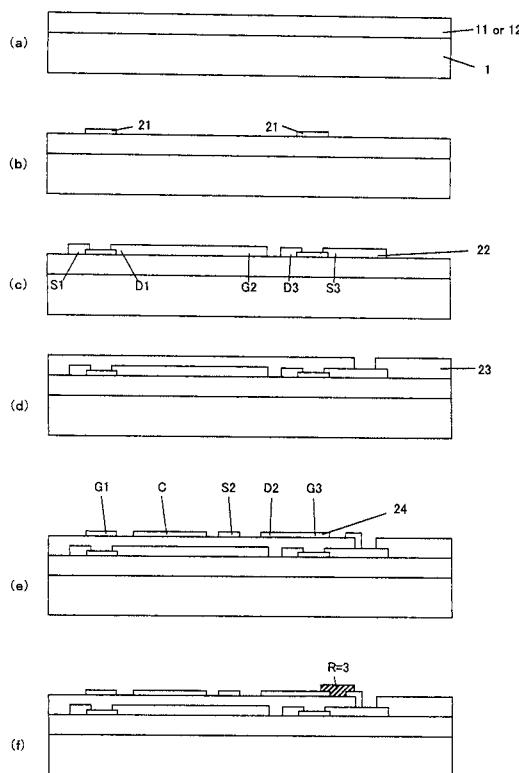

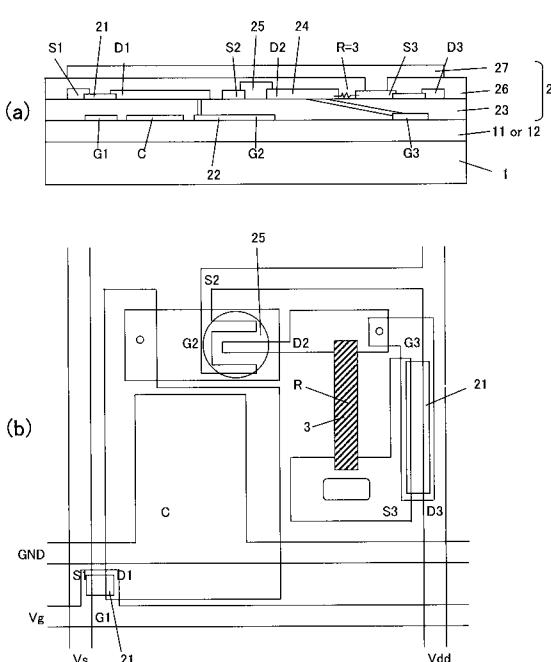

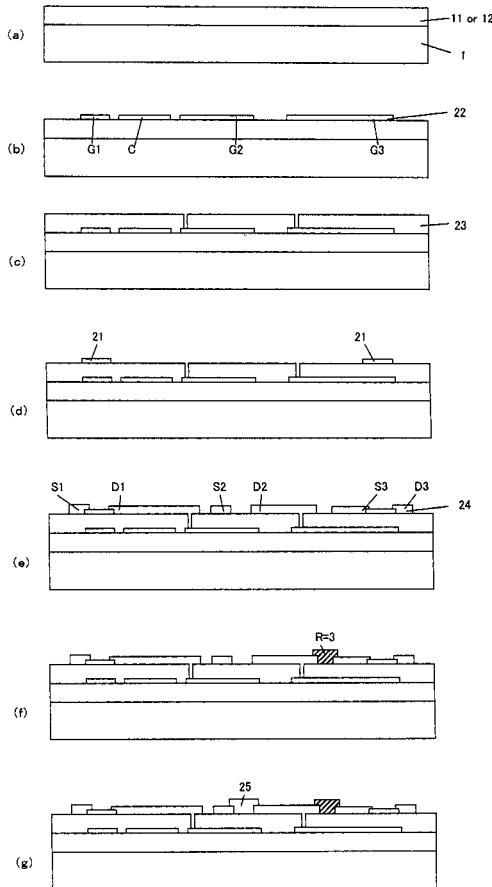

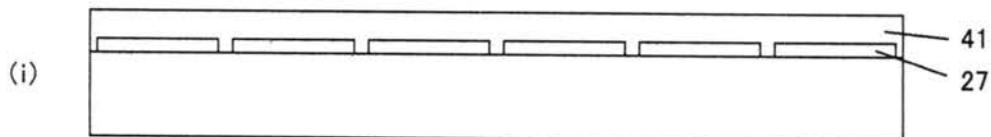

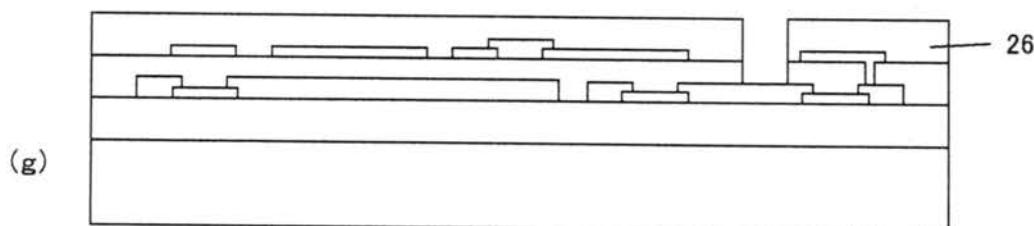

#### 【0062】

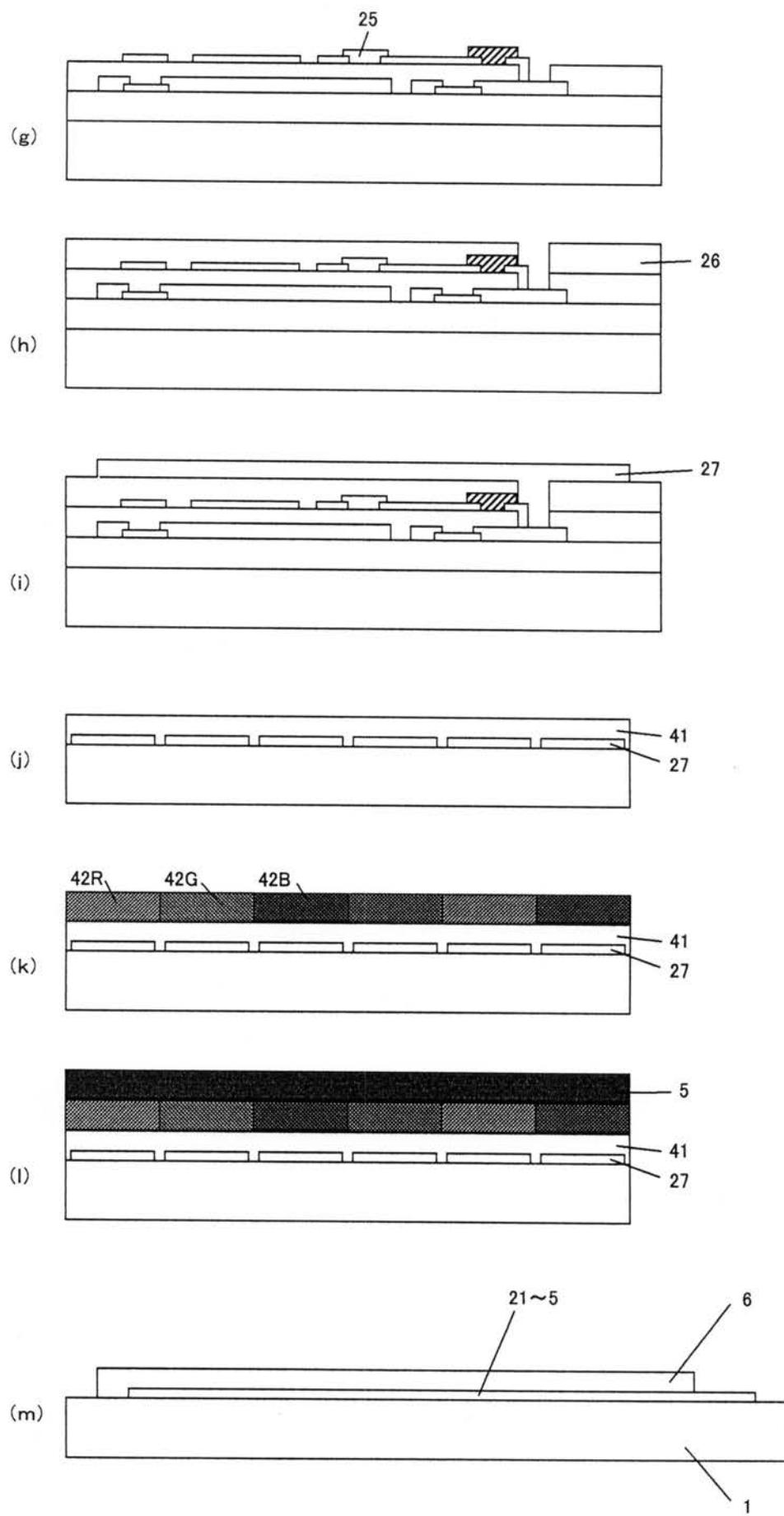

図7は、本実施形態に係る本発明の有機ELディスプレイの画素回路(TFT回路)の平面図(図7 ( a ) )及び断面図(図7 ( b ) )であり、その製造工程を図8 A及び図8 Bに示す。なお、図8 A及び図8 Bにおいては、図8 ( a ) ~ ( i ) は1画素回路(1サブピクセル)分の断面図を示しており、図8 ( j ) ~ ( l ) は画素回路6個(6サブピクセル)分の断面図を示しており、図8 ( m ) は本実施形態に係る本発明のELディスプレイの全体の断面図を示している。

#### 【0063】

まず、基板1上に、バリア膜11を形成する(図8 ( a ) )。次に、ゲート電極G1、G2、G3、キャパシタ電極Cを含む第一電極層22としてITOを反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図8 ( b ) )。そして、ゲート絶縁層となる第一絶縁層23を反応性スパッタによって成膜し、フォトリソ技術を使って

パターニングする(図8(c))。

#### 【0064】

次に、Tr1およびTr3の半導体層となる第一半導体層21として酸化物半導体を反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図8(d))。そして、ソース電極(S1、S2、S3)、ドレイン電極(D1、D2、D3)を含む第二電極層24としてITOを反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図8(e))。そして、抵抗ペーストをスクリーン印刷する等の方法によって抵抗体3を形成する(図8(f))。さらに、Tr2の半導体層となる第二半導体層25をディスペンサ等によって成膜する(図8(g))。次に、層間絶縁膜となる第二絶縁層26を成膜しパターニングする(図8(h))。さらに、画素電極となる第三電極層27を成膜しパターニングする(図8(i))。

10

#### 【0065】

そして、有機EL層4を形成する。まず、全面に正孔輸送層41を塗布する(図8(j))。次に、フレキソ印刷等によって発光層42R、42G、42Bを形成する(図8(k))。

#### 【0066】

さらに、蒸着によって陰極5を全面に成膜する(図8(l))。最後に、全体をガラス板や金属板で覆うか、封止層を成膜する等の方法によって、バリア構造を設けることが望ましい(図8(m))。ガラス板や金属板は、エポキシ等の接着剤でシールすることができ、試料とガラス板や金属板の空隙に乾燥剤を入れるようにしてもよい。

20

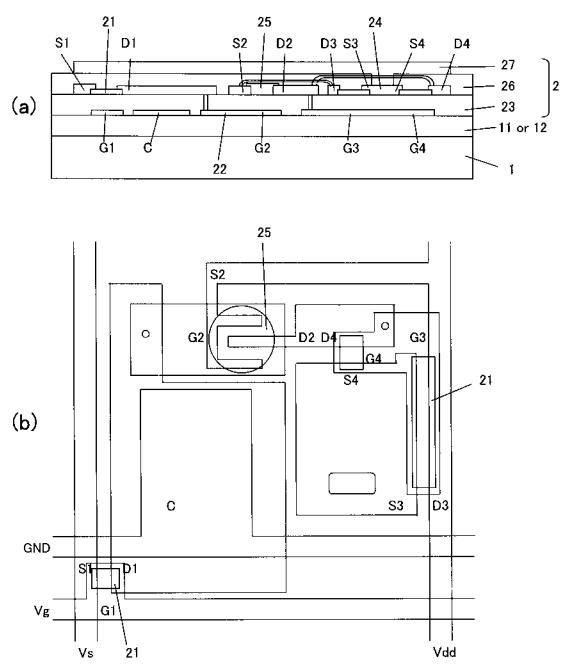

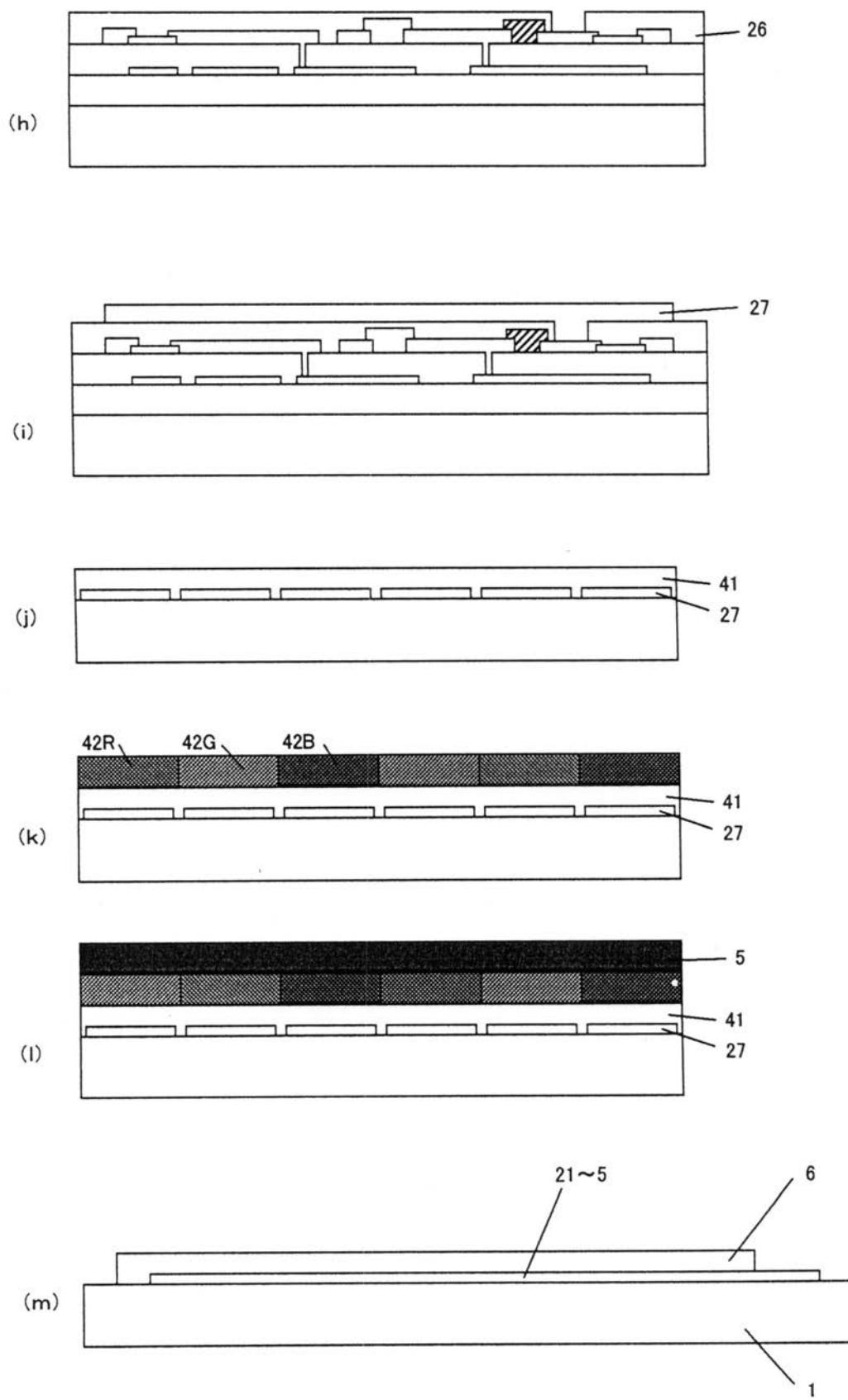

#### 【0067】

(実施形態4)本実施形態4に係る本発明の有機ELディスプレイの画素回路(TFT回路)の回路構成は、実施形態2に係る本発明の有機ELディスプレイの画素回路(TFT回路)の回路構成と同様である。本実施形態4においては、実施形態2に係る本発明の有機ELディスプレイの画素回路のデバイス構造とは異なるデバイス構造を有する有機ELディスプレイについて説明する。なお、本実施形態4においては、実施形態2と同様の構成については、用いる材料等を含め、重複した説明を避けるため再度説明しない場合がある。

#### 【0068】

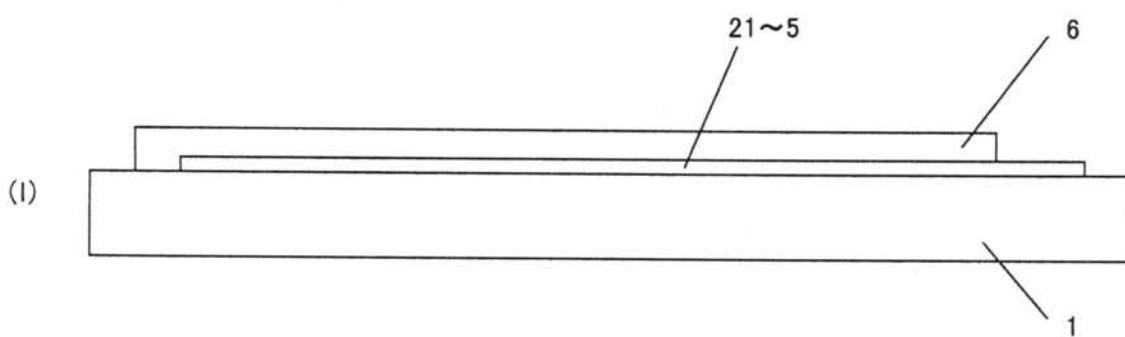

図9は、本実施形態に係る本発明の有機ELディスプレイの画素回路(TFT回路)の平面図(図9(a))及び断面図(図9(b))であり、その製造工程を図10A及び図10Bに示す。図9において駆動トランジスタTr2のソース(S2)と駆動トランジスタTr3のドレイン(D3)とは断面図以外の部分にて接続されており、駆動トランジスタTr2のドレイン(D2)と負荷トランジスタTr4のドレイン(D4)とは断面図以外の部分にて接続されていることを示している。なお、図10A及び図10Bにおいては、図10(a)～(h)は1画素回路(1サブピクセル)分の断面図を示しており、図10(i)～(k)は画素回路6個(6サブピクセル)分の断面図を示しており、図10(l)は本実施形態に係る本発明のELディスプレイの全体の断面図を示している。

30

#### 【0069】

まず、基板1上に、バリア膜11を形成する(図10(a))。次に、ゲート電極G1、G2、G3兼G4となる第一電極層22としてITOを反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図10(b))。そして、ゲート絶縁層となる第一の絶縁層23を反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図10(c))。

40

#### 【0070】

次に、Tr1、Tr3、Tr4の半導体層となる第一半導体層21として酸化物半導体を反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図10(d))。そして、ソース・ドレイン電極(S1、S2兼D3、S3兼S4、D1、D2兼D4)となる第二電極層24としてITOを反応性スパッタ等によって成膜し、フォトリソ技術を使ってパターニングする(図10(e))。さらに、Tr2の半導体層となる第

50

二半導体層 25 をディスペンサ等によって成膜する(図10(f))。次に、層間絶縁膜となる第二絶縁層 26 を成膜しパターニングする(図10(g))。さらに、画素電極となる第三電極層 27 を成膜しパターニングする(図10(h))。

#### 【0071】

そして、有機EL層 4 を形成する。まず、全面に正孔輸送層 41 を塗布する(図10(i))。次に、フレキソ印刷等によって発光層 42R、42G、42B を形成する(図10(j))。

#### 【0072】

さらに、蒸着によって陰極 5 を全面に成膜する(図10(k))。最後に、全体をガラス板や金属板で覆うか、封止層を成膜する等の方法によって、バリア構造を設けることが望ましい(図10(l))。ガラス板や金属板は、エポキシ等の接着剤によってシールすることができ、試料とガラス板や金属板の空隙に乾燥剤を入れるようにしてよい。10

#### 【0073】

なお、ここでは第一電極層 22、第二電極層 24 としてITOを用いた例を示したが、実施形態1で説明したとおり、電極材料はIZO、ATO等の透明導電膜を用いることができる他、開口率が低下することを考慮した上でAl、Ag、Au等の金属を用いることもできる。あるいは、例えば駆動トランジスタTr2のゲート電極(G2)のみに金属を用いて、有機TFTのみを遮光するという方法もある。また、有機TFT部分のみに、別途遮光膜を形成することもできる。さらには、有機半導体や酸化物半導体に接して(半導体の劣化を20

防止するための)封止層を設けてもよい。封止層と遮光層は同一層であってよい。

#### 【実施例】

#### 【0074】

以下、上述の実施形態1～4に係る本発明の有機ELディスプレイの具体的な構造を実施例を用いて詳細に説明する。<実施例1>本実施例1においては、上述の実施形態1に係る本発明の有機ELディスプレイの具体的な構造を説明する。

#### 【0075】

基板1としてPENを用い、その上に、バリア層11としてSiO<sub>2</sub>を100nmCVDで成膜した(図3(a))。次に、Tr1およびTr3の半導体層となる第一半導体層21としてInGaZn酸化物を、InGaZnO<sub>4</sub>をターゲットとしAr+O<sub>2</sub>ガス下での反応性スパッタ(室温、RFスパッタ)によって成膜し、フォトレジスト塗布・露光・現像・塩酸によるウェットエッチング・レジスト剥離によってパターニングした(図3(b))。さらに、あらかじめフォトレジストパターン形成後にソース電極S1、ドレイン電極D1兼ゲート電極G2、ソース電極S3、ドレイン電極D3を含む第一電極層22としてITOを、ITOをターゲットとしAr+O<sub>2</sub>ガス下での反応性スパッタ(室温、DCスパッタ)によって成膜し、リフトオフによってパターニングした(図3(c))。そして、あらかじめフォトレジストパターン形成後に第一の絶縁層23としてSiONを、SiNをターゲットとしAr+O<sub>2</sub>+N<sub>2</sub>ガス下での反応性スパッタ(室温、RFスパッタ)によって成膜し、リフトオフによってパターニングした(図3(d))。さらに、あらかじめフォトレジストパターン形成後にゲート電極G1、キャパシタ電極C、ソース電極S2、ドレイン電極D2兼ゲート電極G3を含む第二の電極層24としてITOを、第一の電極層22と同様の反応性スパッタによって成膜し、リフトオフによってパターニングした(図3(e))。30

#### 【0076】

そして、カーボン系の抵抗体ペーストをスクリーン印刷・焼成して抵抗体3を形成した(図3(f))。次に、第二半導体層25としてチオフェン系材料をディスペンス・焼成した(図3(g))。ここで第二半導体層25を覆うように、封止兼遮光層としてフッ素系黒色樹脂をスクリーン印刷し(図示せず)、さらに第二絶縁層26として感光性アクリル樹脂を塗布・露光・現像によってパターニングし(図3(h))、第三電極層27としてITOを、第一の電極層22と同様の反応性スパッタによって成膜し、フォトレジスト塗布40

・露光・現像によってパターニングした(図3(i))。最後に、ガラス板や金属板で覆うか、封止層を成膜する等の方法によって、バリア構造を設けることが望ましい(図3(j))。50

布・露光・現像・塩酸によるウェットエッティング・レジスト剥離によってパターニングした(図3(i))。

#### 【0077】

そして、有機EL層4を形成した。まず、全面に正孔輸送層41としてPEDOT:PSSの溶液をスピンドルコートし、100℃で焼成した(図3(j))。次に、フレキソ印刷にて赤色発光層42R、緑色発光層42G、青色発光層42Bとしていずれもポリフルオレン系物質を順次形成した(図3(k))。

#### 【0078】

さらに、蒸着によって陰極5としてカルシウムを10nm、銀を300nm、全面に成膜した(図3(l))。最後に全体にバリア構造6としてSiO<sub>2</sub>/アクリル/SiO<sub>2</sub>積層膜を蒸着した(図3(m))。

10

#### 【0079】

このようにして作製した本実施例に係る本発明の有機ELディスプレイは、フレキシブルで軽く、薄く、少し曲げても壊れず、1mの高さから落としても壊れなかった。また、基板側から見て、開口率が大きくて明るい表示ができた。

#### 【0080】

<実施例2>本実施例2においては、上述の実施形態2に係る本発明の有機ELディスプレイの具体的な構造を説明する。

#### 【0081】

基板1としてガラスを用い、その上に、バッファ層12としてSiO<sub>2</sub>を100nmCVDで成膜した(図6(a))。次に、Tr1およびTr3の半導体層となる第一半導体層21としてInGaZn酸化物を、InGaZnO<sub>4</sub>をターゲットとしAr+O<sub>2</sub>ガス下での反応性スパッタ(室温、RFスパッタ)によって成膜し、フォトレジスト塗布・露光・現像・塩酸によるウェットエッティング・レジスト剥離によってパターニングした(図6(b))。さらに、あらかじめフォトレジストパターン形成後にソース電極S1、ドレイン電極D1兼ゲート電極G2、ソース電極S3兼ソース電極S4、ドレイン電極D3、ドレイン電極D4を含む第一電極層22としてITOを、ITOをターゲットとしAr+O<sub>2</sub>ガス下での反応性スパッタ(室温、DCスパッタ)によって成膜し、リフトオフによってパターニングした(図6(c))。そして、あらかじめフォトレジストパターン形成後に第一絶縁層23としてSiONを、SiNをターゲットとしAr+O<sub>2</sub>+N<sub>2</sub>ガス下での反応性スパッタ(室温、RFスパッタ)によって成膜し、リフトオフによってパターニングした(図6(d))。さらに、あらかじめフォトレジストパターン形成後にゲート電極G1、キャパシタ電極C、ソース電極S2、ドレイン電極D2兼ゲート電極G3兼ゲート電極G4を含む第二電極層24としてITOを、第一電極層22と同様の反応性スパッタによって成膜し、リフトオフによってパターニングした(図6(e))。

20

30

30

#### 【0082】

次に、第二半導体層25としてチオフェン系材料をディスペンス・焼成した(図6(f))。ここで第二半導体層25を覆うように、封止兼遮光層28としてフッ素系黒色樹脂をスクリーン印刷し(図示せず)、さらに第二絶縁層26として感光性アクリル樹脂を塗布・露光・現像によってパターニングし(図6(g))、第三電極層27としてITOを、第一の電極層22と同様の反応性スパッタによって成膜し、フォトレジスト塗布・露光・現像・塩酸によるウェットエッティング・レジスト剥離によってパターニングした(図6(h))。

40

#### 【0083】

そして、有機EL層4を形成した。まず、全面に正孔輸送層41としてPEDOT:PSSの溶液をスピンドルコートし、100℃で焼成した(図6(i))。次に、フレキソ印刷にて赤色発光層42R、緑色発光層42G、青色発光層42Bとしていずれもポリフルオレン系物質を順次形成した(図6(j))。

#### 【0084】

さらに、蒸着によって陰極5としてカルシウムを10nm、銀を300nm、全面に成膜

50

した(図6(k))。最後に全体にバリア構造6としてガラスを接着剤で貼り付けた(図6(l))。

#### 【0085】

このようにして作製した本実施例に係る本発明の有機ELディスプレイは、基板側から見て、開口率が大きくて明るい表示ができた。また、輝度ムラの小さい、良好な表示ができた。

#### 【0086】

<実施例3>本実施例3においては、上述の実施形態3に係る本発明の有機ELディスプレイの具体的な態様を説明する。

#### 【0087】

基板1としてPENを用い、その上に、バリア層11としてSiO<sub>2</sub>を100nmCVDで成膜した(図8(a))。次に、ゲート電極G1、G2、G3、キャパシタ電極Cを含む第一電極層22としてITOを、ITOをターゲットとしAr+O<sub>2</sub>ガス下での反応性スパッタ(室温、DCスパッタ)によって成膜し、フォトレジスト塗布・露光・現像・塩酸によるウェットエッチング・レジスト剥離によってパターニングした(図8(b))。さらに、あらかじめフォトレジストパターン形成後に第一の絶縁層23としてSiONを、SiNをターゲットとしAr+O<sub>2</sub>+N<sub>2</sub>ガス下での反応性スパッタ(室温、RFスパッタ)によって成膜し、リフトオフによってパターニングした(図8(c))。そして、あらかじめフォトレジストパターン形成後にTr1およびTr3の半導体層となる第一半導体層21としてInGaZn酸化物を、InGaZnO<sub>4</sub>をターゲットとしAr+O<sub>2</sub>ガス下での反応性スパッタ(室温、RFスパッタ)によって成膜し、リフトオフによってパターニングした(図8(d))。さらに、あらかじめフォトレジストパターン形成後にソース電極S1、S2、S3、ドレイン電極D1、D2、D3を含む第二電極層24としてITOを、第一電極層22と同様の反応性スパッタによって成膜し、リフトオフによってパターニングした(図8(e))。

#### 【0088】

そして、カーボン系の抵抗体ペーストをスクリーン印刷・焼成して抵抗体3を形成した(図8(f))。次に、第二半導体層25としてチオフェン系材料をディスペンド・焼成した(図8(g))。ここで第一半導体層21および第二半導体層25を覆うように、封止兼遮光層28としてフッ素系黒色樹脂をスクリーン印刷し(図示せず)、さらに第二絶縁層26として感光性アクリル樹脂を塗布・露光・現像によってパターニングし(図8(h))、第三電極層27としてITOを、第一の電極層22と同様の反応性スパッタによって成膜し、フォトレジスト塗布・露光・現像・塩酸によるウェットエッチング・レジスト剥離によってパターニングした(図8(i))。

#### 【0089】

そして、有機EL層4を形成した。まず、全面に正孔輸送層41としてPEDOT:PSSの溶液をスピンドルコートし、100℃で焼成した(図8(j))。次に、フレキソ印刷にて赤色発光層42R、緑色発光層42G、青色発光層42Bとしていずれもポリフルオレン系物質を順次形成した(図8(k))。

#### 【0090】

さらに、蒸着によって陰極5としてカルシウムを10nm、銀を300nm、全面に成膜した(図8(l))。最後に全体にバリア構造6としてSiO<sub>2</sub>/アクリル/SiO<sub>2</sub>積層膜を蒸着した(図8(m))。

#### 【0091】

このようにして作製した本実施例に係る本発明の有機ELディスプレイは、フレキシブルで軽く、薄く、少し曲げても壊れず、1mの高さから落としても壊れなかった。また、基板側から見て、開口率が大きくて明るい表示ができた。

#### 【0092】

<実施例4>本実施例4においては、上述の実施形態3に係る本発明の有機ELディスプレイの具体的な態様を説明する。

10

20

30

30

40

50

**【0093】**

基板1としてガラスを用い、その上に、バッファ層12としてSiO<sub>2</sub>を100nmCVDで成膜した(図10(a))。次に、ゲート電極G1、G2、G3兼G4を含む第一電極層22としてITOを、ITOをターゲットとしAr+O<sub>2</sub>ガス下での反応性スパッタ(室温、RFスパッタ)によって成膜し、レジスト塗布・露光・現像・塩酸によるウェットエッチング・レジスト剥離によってパターニングした(図10(b))。さらに、あらかじめフォトレジストパターン形成後に第一絶縁層23としてSiONを、SiNをターゲットとしAr+O<sub>2</sub>+N<sub>2</sub>ガス下での反応性スパッタ(室温、RFスパッタ)によって成膜し、リフトオフによってパターニングした(図10(c))。そして、あらかじめフォトレジストパターン形成後に、Tr1、Tr3およびTr4の半導体層となる第一半導体層21としてInGaZn酸化物を、InGaZnO<sub>4</sub>をターゲットとしAr+O<sub>2</sub>ガス下での反応性スパッタ(室温、RFスパッタ)によって成膜し、リフトオフによってパターニングした(図10(d))。さらに、あらかじめフォトレジストパターン形成後にソース・ドレイン電極S1、S2兼D3、S3兼S4、D1、D2兼D4を含む第二電極層24としてITOを、第一電極層22と同様の反応性スパッタによって成膜し、リフトオフによってパターニングした(図10(e))。

**【0094】**

次に、第二半導体層25としてチオフェン系材料をディスペンス・焼成した(図10(f))。ここで第一半導体層21および第二半導体層25を覆うように、封止兼遮光層28としてフッ素系黒色樹脂をスクリーン印刷し(図示せず)、さらに第二絶縁層26として感光性アクリル樹脂を塗布・露光・現像によってパターニングし(図10(g))、第三電極層27としてITOを、第一の電極層32と同様の反応性スパッタによって成膜し、フォトレジスト塗布・露光・現像・塩酸によるウェットエッチング・レジスト剥離によってパターニングした(図10(h))。

**【0095】**

そして、有機EL層4を形成した。まず、全面に正孔輸送層41としてPEDOT:PS的溶液をスピンドルコートし、焼成した100℃で焼成した(図10(i))。次に、フレキソ印刷にて赤色発

光層42R、緑色発光層42G、青色発光層42Bとしていずれもポリフルオレン系物質を順次形成した(図10(j))。

**【0096】**

さらに、蒸着によって陰極5としてカルシウムを10nm、銀を300nm、全面に成膜した(図10(k))。最後に全体にバリア構造6としてガラスを接着剤で貼り付けた(図10(l))。

**【0097】**

このようにして作製した本実施例に係る本発明の有機ELディスプレイは、基板側から見て、開口率が大きくて明るい表示ができた。また、輝度ムラの小さい、良好な表示ができた。

**【図面の簡単な説明】****【0098】**

【図1】実施形態1及び3に係る本発明のELディスプレイの画素回路の回路構成図である。

【図2】実施形態1に係る本発明のELディスプレイの構造の一例を示す断面模式図(図2(a))と平面図(図2(b))である。

【図3A】実施形態1に係る本発明のELディスプレイの製造工程の一例を示す断面図である。

【図3B】実施形態1に係る本発明のELディスプレイの製造工程の一例を示す断面図である。

【図4】実施形態2及び4に係る本発明のELディスプレイの画素回路の回路構成図である。

10

20

30

40

50

【図5】実施形態2に係る本発明のELディスプレイの構造の一例を示す断面模式図(図5(a))と平面図(図5(b))である。

【図6A】実施形態2に係る本発明のELディスプレイの製造工程の一例を示す断面図である。

【図6B】実施形態2に係る本発明のELディスプレイの製造工程の一例を示す断面図である。

【図7】実施形態3に係る本発明のELディスプレイの構造の一例を示す断面模式図(図7(a))と平面図(図7(b))である。

【図8A】実施形態3に係る本発明のELディスプレイの製造工程の一例を示す断面図である。

【図8B】実施形態3に係る本発明のELディスプレイの製造工程の一例を示す断面図である。

【図9】実施形態4に係る本発明のELディスプレイの構造の一例を示す断面模式図(図9(a))と平面図(図9(b))である。

【図10A】実施形態4に係る本発明のELディスプレイの製造工程の一例を示す断面図である。

【図10B】実施形態4に係る本発明のELディスプレイの製造工程の一例を示す断面図である。

【図11】従来のELディスプレイの画素回路の回路構成図である。

#### 【符号の説明】

##### 【0099】

1 透明基板

1 1 バリア層

1 2 バッファ層

2 TFT回路

2 1 第一半導体層

2 2 第一電極層

2 3 第一絶縁層

2 4 第二電極層

2 5 第二半導体層

2 6 第二絶縁層

2 7 第三電極層

2 8 封止層兼遮光層

3 抵抗体

G 1 ~ G 4 ゲート電極

S 1 ~ S 4 ソース電極

D 1 ~ D 4 ドレイン電極

C キャパシタ電極

R 抵抗体

4 有機EL層

4 1 正孔輸送層

4 2 発光層

4 2 R 赤色発光層

4 2 G 緑色発光層

4 2 B 青色発光層

5 陰極

6 バリア構造

10

20

30

40

【図1】

【図2】

【図3A】

( 4 )

【図5】

【図6 A】

【図7】

【図8 A】

【図9】

【図10A】

【図11】

【図3B】

【図 6 B】

【図 8 B】

【図10B】

---

フロントページの続き

| (51)Int.Cl.             | F I                                         |

|-------------------------|---------------------------------------------|

| H 01 L 29/786 (2006.01) | H 01 L 29/78 6 1 4                          |

| H 01 L 21/336 (2006.01) | H 01 L 29/78 6 1 2 Z                        |

| H 01 L 51/05 (2006.01)  | H 01 L 29/78 6 1 8 B                        |

| G 09 G 3/20 (2006.01)   | H 01 L 29/28 1 0 0 A<br>G 09 G 3/20 6 2 4 B |

(56)参考文献 実開平6 - 2391 (JP, U)

特開平9 - 8631 (JP, A)

特開2007 - 88210 (JP, A)

特開2004 - 70074 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

|        |         |

|--------|---------|

| G 09 G | 3 / 3 0 |

| G 09 F | 9 / 3 0 |

| G 09 G | 3 / 2 0 |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机EL显示器及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP4910779B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2012-04-04 |

| 申请号            | JP2007052416                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2007-03-02 |

| [标]申请(专利权)人(译) | 凸版印刷株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | 凸版印刷株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 当前申请(专利权)人(译)  | 凸版印刷株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| [标]发明人         | 石崎守                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 发明人            | 石崎守                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | G09G3/30 G09F9/30 H01L51/50 H05B33/10 H01L27/32 H01L29/786 H01L21/336 H01L51/05 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G09G3/30.J G09F9/30.338 H05B33/14.A H05B33/10 G09F9/30.365.Z H01L29/78.614 H01L29/78.612.Z H01L29/78.618.B H01L29/28.100.A G09G3/20.624.B G09F9/30.365 G09G3/3233 G09G3/3291 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC36 3K107/CC45 3K107/DD90 3K107/EE04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/CC03 5C080/DD05 5C080/DD08 5C080/DD28 5C080/EE29 5C080/FF11 5C080/HH09 5C080/JJ03 5C080/JJ06 5C094/AA53 5C094/BA03 5C094/BA27 5C094/DB01 5C094/FB19 5C380/AA01 5C380/AB06 5C380/AB12 5C380/AB21 5C380/AB25 5C380/AB34 5C380/CA12 5C380/CC01 5C380/CC27 5C380/CC28 5C380/CC33 5C380/CC62 5C380/CD012 5C380/CD013 5C380/CD014 5C380/CF41 5C380/DA02 5F110/AA30 5F110/BB01 5F110/CC01 5F110/CC03 5F110/DD01 5F110/DD12 5F110/DD13 5F110/DD14 5F110/DD17 5F110/EE03 5F110/EE04 5F110/EE07 5F110/EE42 5F110/EE43 5F110/EE44 5F110/FF01 5F110/FF02 5F110/FF04 5F110/FF27 5F110/FF28 5F110/FF36 5F110/GG04 5F110/GG05 5F110/GG06 5F110/GG42 5F110/GG43 5F110/HK03 5F110/HK04 5F110/HK07 5F110/HK32 5F110/HK33 5F110/NN02 5F110/NN02 5F110/NN71 5F110/NN73 5F110/NN78 5F110/QQ14 |         |            |

| 审查员(译)         | 福村 拓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | <a href="#">JP2008216529A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

## 摘要(译)

要解决的问题：使用n沟道TFT，例如氧化物TFT作为p沟道型TFT作为有机EL显示器的驱动晶体管，并通过p沟道TFT实现大电流驱动。有机TFT。解决方案：有机EL显示器包括具有多个像素电路和有机EL层的薄膜TFT电路，并且每个像素电路包括第一，第二和第三薄膜TFT。第一薄膜TFT的栅电极，源电极和漏电极分别连接到栅极线，源极线，第二薄膜TFT的栅电极和电容器的一个电极。第二薄膜TFT是p沟道型薄膜TFT，第二薄膜TFT的源电极和漏电极连接到电源电位，第三薄膜TFT的栅极和电阻器的一端，分别。第三薄膜TFT是n沟道型薄膜TFT，第三薄膜TFT的漏极和源极分别连接到电源电位，电阻器的另一端和阳极。Z