(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4836718号

(P4836718)

(45) 発行日 平成23年12月14日(2011.12.14)

(24) 登録日 平成23年10月7日(2011.10.7)

|                      |              |

|----------------------|--------------|

| (51) Int.Cl.         | F 1          |

| G09G 3/30 (2006.01)  | G09G 3/30 H  |

| H05B 33/12 (2006.01) | H05B 33/12 Z |

| H01L 51/50 (2006.01) | H05B 33/14 A |

| H05B 33/10 (2006.01) | H05B 33/10   |

| G09G 3/20 (2006.01)  | G09G 3/30 J  |

請求項の数 5 (全 23 頁) 最終頁に続く

(21) 出願番号 特願2006-239626 (P2006-239626)

(22) 出願日 平成18年9月4日 (2006.9.4)

(65) 公開番号 特開2008-64806 (P2008-64806A)

(43) 公開日 平成20年3月21日 (2008.3.21)

審査請求日 平成21年8月31日 (2009.8.31)

(73) 特許権者 311003743

オンセミコンダクター・トレーディング・

リミテッド

英国領バミューダ・エイチエム 11 ハ

ミルトン・チャーチストリート2・クラレ

ンドンハウス・コーダン サービシーズ

リミテッド 気付

(74) 代理人 110001210

特許業務法人 Y K I 国際特許事務所

(72) 発明者 小川 隆司

群馬県邑楽郡大泉町坂田一丁目1番1号

三洋半導体株式会社内

審査官 福村 拓

最終頁に続く

(54) 【発明の名称】エレクトロルミネッセンス表示装置の欠陥検査方法及び欠陥検査装置及びこれらを利用したエレクトロルミネッセンス表示装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

エレクトロルミネッセンス表示装置の欠陥検査方法であって、前記表示装置は、各画素に、エレクトロルミネッセンス素子と、該エレクトロルミネッセンス素子に接続され、該エレクトロルミネッセンス素子に流れる電流を制御するための素子駆動トランジスタと、を備え、

各画素に、前記エレクトロルミネッセンス素子を発光レベルとする検査用オン表示信号を供給し、かつ、前記素子駆動トランジスタを該トランジスタの飽和領域で動作させて、前記エレクトロルミネッセンス素子の発光状態を観察し、発光輝度が基準輝度未満の画素を異常表示欠陥画素として検出し、

各画素に、前記エレクトロルミネッセンス素子を発光レベルとする検査用オン表示信号を供給し、かつ、前記素子駆動トランジスタを該トランジスタの線形領域で動作させて、前記エレクトロルミネッセンス素子の発光状態を観察して、非発光画素を、前記エレクトロルミネッセンス素子に起因した滅点欠陥画素として検出し、

前記異常表示欠陥画素として検出された画素のうち、前記滅点欠陥画素として検出されない画素を、前記素子駆動トランジスタに起因した暗点欠陥画素として検出することを特徴とするエレクトロルミネッセンス表示装置の欠陥検査方法。

## 【請求項 2】

請求項 1 に記載のエレクトロルミネッセンス表示装置の欠陥検査方法において、

各画素の前記エレクトロルミネッセンス素子に対し、逆バイアス電圧を印加してから、

前記滅点欠陥画素の検出を実行することを特徴とするエレクトロルミネッセンス表示装置の欠陥検査方法。

**【請求項 3】**

エレクトロルミネッセンス表示装置の製造方法において、

請求項1に記載の欠陥検査方法によって検出された前記滅点欠陥画素に対しては、該画素の前記エレクトロルミネッセンス素子の陽極と陰極とのショート領域に選択的にレーザ光を照射して該ショート領域の電流経路を切断するレーザ修正を実行することを特徴とすることをエレクトロルミネッセンス表示装置の製造方法。

**【請求項 4】**

エレクトロルミネッセンス表示装置の製造方法において、

請求項1に記載の検査方法によって検出された前記暗点欠陥画素に対しては、該画素の前記素子駆動型トランジスタに所定のバイアスを印加した状態で紫外線光を照射して、前記素子駆動型トランジスタの電流供給特性のずれを修正することを特徴とするエレクトロルミネッセンス表示装置の製造方法。

**【請求項 5】**

各画素に、ダイオード構造のエレクトロルミネッセンス素子と、該エレクトロルミネッセンス素子に接続され、該エレクトロルミネッセンス素子に流れる電流を制御するための素子駆動トランジスタと、を備えるエレクトロルミネッセンス表示装置の欠陥検査装置であって、

欠陥検査時に各画素に供給する複数の電源を発生する電源発生部と

欠陥検査モードに応じて、前記素子駆動トランジスタの飽和領域での動作と線形領域での動作を切り替え制御するために、画素に供給する電源を切り替える電源切り替え部と、検査用のタイミング信号及び検査用オン表示信号を発生する検査用信号発生部と、

前記エレクトロルミネッセンス素子の発光状態を検出する発光検出部と、

欠陥判定部と、を備え

異常表示検査モードにおいて

前記電源切り替え部によって選択した暗点検査用の電源及び前記タイミング信号によって、前記素子駆動トランジスタを該トランジスタの飽和領域で動作させ、かつ、前記エレクトロルミネッセンス素子を発光レベルとする検査用オン表示信号を対応する画素に供給し、

前記発光検出部は、前記エレクトロルミネッセンス素子の発光輝度を検出し、

前記欠陥判定部は、前記検出された発光輝度を基準輝度と比較し、該発光輝度が前記基準輝度未満の画素を異常表示欠陥画素と判定し、

滅点検査モードにおいて、

前記電源切り替え部によって選択した滅点検査用の電源及び前記タイミング信号によって、前記素子駆動トランジスタを該トランジスタの線形領域で動作させ、かつ、前記エレクトロルミネッセンス素子を発光レベルとする滅点検査用オン表示信号を対応する画素に供給し、

前記発光検出部は、前記エレクトロルミネッセンス素子の発光輝度を検出し、

欠陥判定部は、前記検出された発光輝度を基準輝度と比較し、該発光輝度が前記基準輝度未満の画素を、前記エレクトロルミネッセンス素子に起因した滅点欠陥画素と判定し、

暗点検査モードにおいて、前記欠陥判定部は、前記異常表示欠陥画素として検出された画素のうち、前記滅点欠陥画素として検出されない画素を、前記素子駆動トランジスタに起因した暗点欠陥画素と判定することを特徴とするエレクトロルミネッセンス表示装置の欠陥検査装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

エレクトロルミネッセンス素子を各画素に有する表示装置のエレクトロルミネッセンス素子に起因した欠陥、又は、エレクトロルミネッセンス素子を駆動するトランジスタに起

10

20

30

40

50

因した欠陥の検査に関する。

【背景技術】

【0002】

自発光素子であるエレクトロルミネッセンス素子（以下EL素子という）を各画素の表示素子に採用したEL表示装置は、次世代の平面表示装置として期待され、研究開発が行われている。

【0003】

このようなEL表示装置は、ガラスやプラスチックなどの基板上にEL素子及びこのEL素子を画素毎に駆動するための薄膜トランジスタ（TFT）などを形成したELパネルを作成した後、幾度かの検査を経て製品として出荷されることとなる。現在EL表示装置において、歩留まりの向上が非常に重要であり、EL素子やTFTなどの製造工程の改良や材料の改良などと共に、検査工程における効率化を図ることが求められる。10

【0004】

【特許文献1】特開2005-149768号

【特許文献2】特開2005-149769号

【発明の開示】

【発明が解決しようとする課題】

【0005】

現在のEL表示装置に対して行われている検査においては、例えば、RGBそれぞれについてのラスター画像や、モノスコパターンを表示させて表示欠陥などの不良項目を検査する。不良項目としては、表示ムラ、滅点、輝点などが含まれる。20

【0006】

輝点については、該当画素回路のショートなどに起因して発生することが多く、この場合、画素回路をレーザ照射などで絶縁化して滅点化させるなどの方法が採用される。

【0007】

一方、表示ムラ（DIM）や、滅点については、様々な原因が存在することが解明されつつある。見かけ上、同様な表示欠陥であっても、その発生原因が異なる場合には、その原因を特定し、原因に応じた修正をすることが必要である。しかし、発生原因に応じた効率的な検査手法は確立されるに至っていない。

【0008】

本発明は、正確にかつ効率的にEL表示装置の欠陥検査を行うことを目的とする。30

【課題を解決するための手段】

【0009】

本発明は、エレクトロルミネッセンス表示装置の欠陥検査方法であって、前記表示装置は、各画素に、エレクトロルミネッセンス素子と、該エレクトロルミネッセンス素子に接続され、該エレクトロルミネッセンス素子に流れる電流を制御するための素子駆動トランジスタと、を備え、各画素に、前記エレクトロルミネッセンス素子を発光レベルとする検査用オン表示信号を供給し、かつ、前記素子駆動トランジスタを該トランジスタの飽和領域で動作させて、前記エレクトロルミネッセンス素子の発光状態を観察し、発光輝度が基準輝度未満の画素を異常表示欠陥画素として検出し、各画素に、前記エレクトロルミネッセンス素子を発光レベルとする検査用オン表示信号を供給し、かつ、前記素子駆動トランジスタを該トランジスタの線形領域で動作させて、前記エレクトロルミネッセンス素子の発光状態を観察して、非発光画素を、前記エレクトロルミネッセンス素子に起因した滅点欠陥画素として検出し、前記異常表示欠陥画素として検出された画素のうち、前記滅点欠陥画素として検出されない画素を、前記素子駆動トランジスタに起因した暗点欠陥画素として検出する。40

【0011】

なお、本発明において、上記欠陥検査方法において、各画素の前記エレクトロルミネッセンス素子に対し、逆バイアス電圧を印加してから、前記滅点欠陥画素の検出を実行することで、滅点を顕在化させてから、この滅点欠陥検査を実行することが可能となる。50

**【発明の効果】**

**【0016】**

本発明者の研究により、各画素に設けられてEL素子を駆動する素子駆動トランジスタを線形領域で動作させてEL素子を発光させた場合、EL素子にショートが発生していると、非発光画素、つまり滅点が観察されると共に、ショートが発生していない正常な場合と比較し、このEL素子に流れる電流値が大きくなることが判明した。また、素子駆動トランジスタを飽和領域で動作させてEL素子を発光させた場合、上記EL素子のショート及びTFTの特性変動が発生していると、その画素は異常表示（正常時よりも発光輝度が低い又は非発光）となる。このときのEL素子に流れる電流値は、正常な場合と比較して小さくなることも判明した。

10

**【0017】**

したがって、本発明のように、素子駆動トランジスタを線形領域で動作させてEL素子を観察またはEL素子のカソード電流値を測定することで、EL素子のショートによる滅点欠陥を精度良く検出することができる。

**【0018】**

また、素子駆動トランジスタを飽和領域で動作させてEL素子を観察することで、この素子駆動トランジスタの特性ばらつきに起因した異常表示と、EL素子のショートによる異常表示を検出できる。このため、上記のようにトランジスタを線形領域で動作させた際に観察された滅点欠陥画素をこの異常表示欠陥画素と判定した画素から除くことで、簡単に素子駆動トランジスタの特性ばらつきに起因した異常表示画素を暗点欠陥画素として特定することができる。また、EL素子のカソード電流値を測定すると、EL素子のショートによって異常表示が発生している場合には、正常時におけるカソード電流値との差は小さいが、素子駆動トランジスタの特性変動によりEL素子での発光輝度が低下する場合、正常な場合よりそのカソード電流値が小さくなる。よって、カソード電流値を測定することで、迅速かつ客観的に、素子駆動トランジスタの特性変動に起因した暗点欠陥画素を検出することができる。

20

**【0019】**

また、検査結果によって直ちに欠陥の発生原因を特定できるため、原因に応じた適切な修正工程に表示装置を送り、修正効率を高めることが可能となる。

**【0020】**

30

さらに、素子駆動トランジスタを線形領域又は飽和領域で動作させながら、EL素子に対して検査用のオフ表示信号とオン表示信号を供給して、各信号印加時におけるカソード電流値を測定することにより、オフ表示信号に応じたカソード電流値を基準としてオン表示信号に応じたカソード電流値を検出することができ、欠陥検出装置を用いた自動判定を高速に実行することが容易となる。

**【0021】**

検査は画素毎に実行するが、素子駆動トランジスタ及びEL素子を画素毎にかつ複数回連続して動作させることにより、制御信号などにノイズ等が重畠した結果の誤判定の影響を低減することが容易となる。

**【発明を実施するための最良の形態】**

40

**【0022】**

以下、図面を用いてこの発明の最良の実施の形態（以下実施形態という）について説明する。

**【0023】**

**[検査原理]**

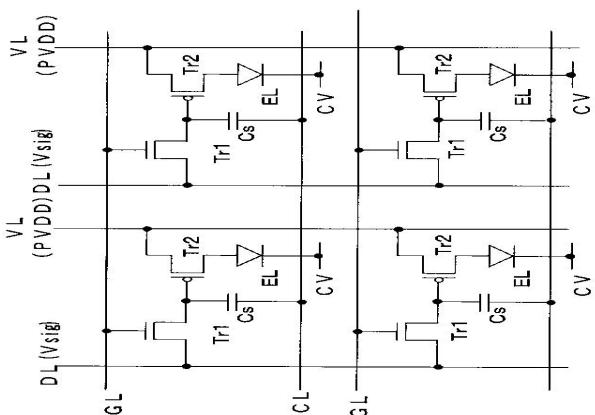

本実施形態において、表示装置は、具体的にはアクティブマトリクス型の有機EL表示装置であり、複数の画素を備える表示部がELパネル100に形成されている。図1は、この実施形態に係るアクティブマトリクス型表示装置の等価回路構成を示す図であり、図2及び図3は、本実施形態において採用するEL表示装置の各画素の欠陥検査原理を示している。ELパネル100の表示部には、マトリクス状に複数の画素が配置され、マトリ

50

クスの水平走査方向（行方向）には、順次選択信号が出力される選択ライン G L が形成されており、垂直走査方向（列方向）には、データ信号が出力されるデータライン D L と、被駆動素子である有機 E L 素子（以下、単に E L 素子という）に、駆動電源 P V D D を供給するための電源ライン V L が形成されている。

#### 【 0 0 2 4 】

各画素は、概ねこれらのラインによって区画される領域に設けられており、各画素は、被駆動素子として有機 E L 素子を備え、また、n チャネルの T F T より構成された選択トランジスタ T r 1 （以下、選択 T r 1 ）、保持容量 C s 、p チャネルの T F T より構成された素子駆動トランジスタ T r 2 （以下、素子駆動 T r 2 ）が設けられている。

#### 【 0 0 2 5 】

選択 T r 1 は、そのドレインが垂直走査方向に並ぶ各画素にデータ電圧（ V sig ）を供給するデータライン D L に接続され、ゲートが 1 水平走査ライン上に並ぶ画素を選択するためのゲートライン G L に接続され、そのソースは素子駆動 T r 2 のゲートに接続されている。

#### 【 0 0 2 6 】

また、素子駆動 T r 2 のソースは電源ライン V L に接続され、ドレインは E L 素子のアノードに接続されている。 E L 素子のカソードは各画素共通で形成され、カソード電源 C V に接続されている。

#### 【 0 0 2 7 】

E L 素子は、ダイオード構造で下部電極と上部電極の間に発光素子層を備える。発光素子層は、例えば少なくとも有機発光材料を含む発光層を備え、発光素子層に用いる材料特性などにより、単層構造や、2 層、3 層あるいは 4 層以上の多層構造を採用することができる。本実施形態では、下部電極が画素毎に個別形状にパターニングされ上記アノードとして機能し、素子駆動 T r 2 に接続されている。また、上部電極が複数の画素に共通でカソードとして機能する。

#### 【 0 0 2 8 】

画素毎に上記のような回路構成を備えるアクティブマトリクス型 E L 表示装置において、 E L 素子のアノードとカソード間の短絡（ショート）が発生した場合と、素子駆動 T r 2 の特性が低下した場合のいずれの画素も、 E L 素子は非発光となるか、その発光輝度が正常な画素よりも低くなり、滅点、又は暗点（ D I M ）と呼ばれる表示欠陥となる。

#### 【 0 0 2 9 】

E L 素子の発光素子層は、非常に薄く、また、その膜厚のはらつきなどを生ずることで、アノードとカソードにショート生ずる欠陥が発生する場合がある。ショートが発生すると、素子駆動 T r 2 のゲートに発光（オン）表示信号を印加し、 E L 素子に電流を供給しても、発光素子層には正孔及び電子が注入されず、 E L 素子は発光せず、滅点欠陥となる。

#### 【 0 0 3 0 】

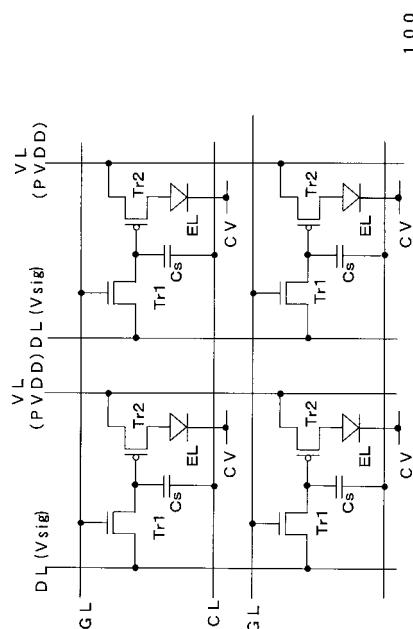

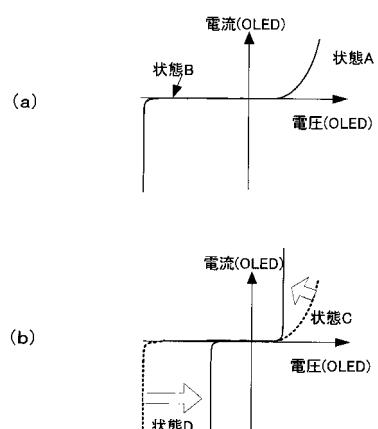

図 2 は、このような E L 素子ショートが発生した画素の回路構成及びその場合の素子駆動 T r 2 及び E L 素子の I V 特性について示している。 E L 素子にショートが発生した場合、回路的には、図 2 ( b ) に示すように、素子駆動 T r 2 のドレイン側がカソード電源 C V に接続されることと等価となる。このため、 E L 素子に流れる電流をカソード電流 I c v で評価した場合、その電流 I c v の P V D D - C V 電圧に対する特性は、図 2 ( a ) に示すように、ショートの発生した E L 素子の電流特性は、正常な E L 素子の電流特性よりも傾きが大きくなる。

#### 【 0 0 3 1 】

ここで、素子駆動 T r 2 への印加電圧が V g s - V t h < V d s を満たし、ゲートソース間電圧が小さく、ドレイン・ソース間（ P V D D ・ C V ）電圧が大きい場合（本実施形態では通常表示モードと同様の条件）、素子駆動 T r 2 は飽和領域で動作する。このときショート発生画素の E L 素子は非発光（滅点）となる。また、ショート発生画素と正常画素の E L 素子の電流特性の傾きは大きく異なるが、素子駆動 T r 2 のソースドレイン間電

10

20

30

40

50

流  $I_{dS}$  特性の傾きの小さい領域に相当するため、EL 素子に流れる電流  $I_{cV}$  の差  $|I|$  は小さい。

#### 【0032】

一方、素子駆動  $T_{r2}$  への印加電圧が、 $V_{gs} - V_{th} > V_{ds}$  を満たし、ゲートソース間電圧が大きく、ドレイン・ソース間（PVDD・CV）電圧が小さい場合、この素子駆動  $T_{r2}$  は線形領域で動作する。この線形領域ではショート発生画素（滅点画素）と正常画素とで、EL 素子の電流特性の傾きは飽和領域の場合と同様に異なっている。さらに、この線形領域では素子駆動  $T_{r2}$  の  $I_{dS}$  特性の傾きが急峻であり、滅点画素の EL 素子のカソード電流  $I_{cV}$  と、正常画素の EL 素子のカソード電流  $I_{cV}$  との差  $|I|$  は、非常に大きくなる。また、この線形領域での動作において、ショート発生画素の EL 素子は、ショート状態のままであるため非発光（滅点）となり、正常画素の発光輝度とは大きく異なる。したがって、EL 素子のショートによる欠陥は、発光輝度に関しては、素子駆動  $T_{r2}$  を線形領域で動作させても飽和領域で動作させても検出することができ、EL 素子に流れる電流については、素子駆動  $T_{r2}$  を線形領域で動作させて測定することにより、高い精度で検出することができる。10

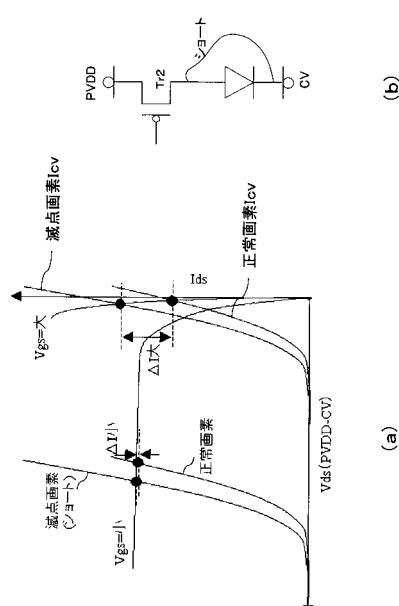

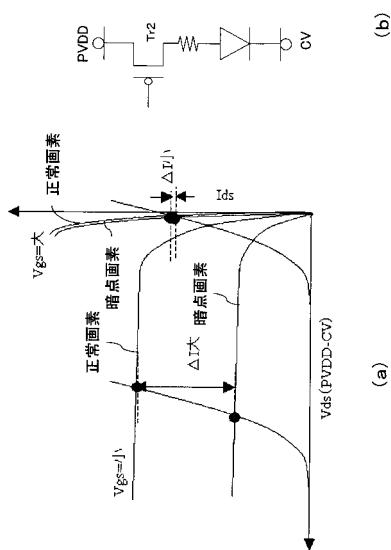

#### 【0033】

次に、EL 素子は正常であるが、素子駆動  $T_{r2}$  の特性がばらついて正常トランジスタよりも特性が劣化した場合について説明する。図3は、このような素子駆動  $T_{r2}$  の特性ばらつき（電流供給特性のばらつき。例えば、動作しきい値  $V_{th}$  の低下）が生じた場合の画素の等価回路及び素子駆動  $T_{r2}$  及び EL 素子の  $IV$  特性を示している。素子駆動  $T_{r2}$  に動作しきい値  $V_{th}$  の低下が生じた場合、回路的には、図3（b）に示すように、素子駆動  $T_{r2}$  のドレイン側に正常よりも大きな抵抗が接続されたことと見なすことができる。よって、EL 素子が流す電流（本実施形態では、カソード電流  $I_{cV}$ ）特性は、正常画素と変わらないが、実際に EL 素子に流れる電流は素子駆動  $T_{r2}$  の特性ばらつきに応じて変化することとなる。20

#### 【0034】

まず、素子駆動  $T_{r2}$  への印加電圧が  $V_{gs} - V_{th} < V_{ds}$  を満たす場合、上記と同様、素子駆動  $T_{r2}$  は飽和領域で動作する。図3（a）に示すように、このとき素子駆動  $T_{r2}$  の特性が、正常よりも低下した画素においては、該トランジスタのドレインソース間電流  $I_{dS}$  が、正常のトランジスタよりも小さくなり、EL 素子への供給電流量、つまり、EL 素子の流す電流は、正常画素よりも小さくなる（ $|I|$  大）。また、その結果、素子駆動  $T_{r2}$  に特性ばらつきが発生した画素は、正常画素よりも発光輝度は低くなり、暗点として認識される。なお、素子駆動  $T_{r2}$  の特性劣化が著しい場合は、EL 素子はほぼ非発光の状態となる。30

#### 【0035】

一方、素子駆動  $T_{r2}$  への印加電圧が、 $V_{gs} - V_{th} > V_{ds}$  を満たす場合、この素子駆動  $T_{r2}$  は線形領域で動作し、この線形領域では、特性が低下した素子駆動  $T_{r2}$  と正常の素子駆動  $T_{r2}$  とで、 $I_{dS} - V_{ds}$  特性の差が小さいため、EL 素子への供給電流量の差（ $|I|$ ）も小さい。このため、EL 素子は、素子駆動  $T_{r2}$  の特性ばらつきの有無によらず、概ね同様の発光輝度を示し、線形領域においては特性ばらつきに起因した暗点を検出することは難しい。しかし、上記のように、素子駆動  $T_{r2}$  を飽和領域で動作させることで、この素子駆動  $T_{r2}$  の特性ばらつきに起因した暗点欠陥については、電流値及び EL 発光輝度のいずれの観点からも検出することができる。40

#### 【0036】

なお、以上の画素回路では、素子駆動トランジスタとして、p チャネルの TFT を採用したが、n チャネルの TFT を用いてもよい。さらに、以上の画素回路では、1 画素について、トランジスタとして、選択トランジスタと駆動トランジスタの 2 つのトランジスタを備える構成を採用した例を説明したが、トランジスタが 2 つのタイプ及び上記回路構成には限られない。

#### 【0037】

何れの場合も、採用する画素回路においてEL素子に電流を供給する素子駆動トランジスタを線形領域で動作させてEL素子を観察またはEL素子のカソード電流値を測定することで、EL素子のショートによる滅点欠陥を精度良く検出することができる。

#### 【0038】

また、何れの場合も、素子駆動トランジスタを飽和領域で動作させてEL素子の発光輝度やカソード電流などを検出することで、素子駆動トランジスタの特性ばらつきに起因した暗点欠陥を検出できる。

#### 【0039】

##### [欠陥検査]

次に、上記原理に基づく欠陥検査について、EL素子の特性として、その発光状態を用いた検査及びカソード電流を用いた検査についてそれぞれ説明する。 10

#### 【0040】

##### (発光状態検査)

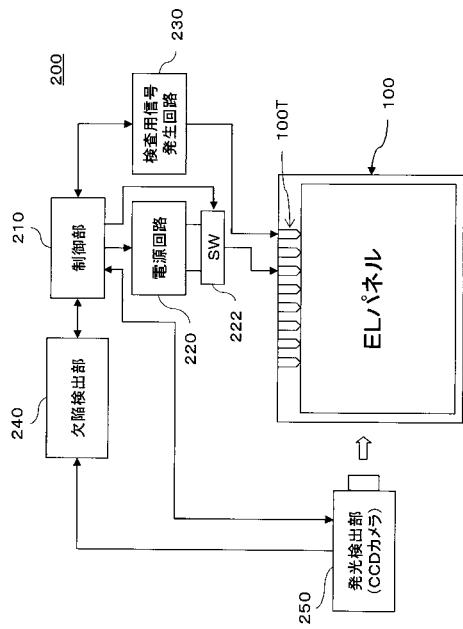

図4は発光状態(発光輝度)の観察(輝度検出)から、滅点・暗点欠陥を検出するための検出装置の構成の一例を示している。

#### 【0041】

検査装置200は、装置内の各部を制御する制御部210、素子駆動Tr2の飽和領域検査モード、線形領域検査モードのそれぞれにおいて必要な電源を発生する電源回路220、上記検査モードに応じてELパネルに供給する電源を切り替える電源切り替え部222、検査時に用いる検査用信号を発生する検査用信号発生回路230を備える。また、装置200は、CCDカメラなどが採用可能でありELパネルの各画素の発光状態を観察する発光検出部250、発光検出部250からの検出結果を利用して欠陥を検出する検出部240を備える。 20

#### 【0042】

このような検査装置200を採用した場合において、表示輝度が正常値以下の異常表示画素の検出及びEL素子のショートに起因した滅点画素の検出を実行し、さらに、異常表示画素と滅点画素との比較から、素子駆動Tr2の特性ばらつきに起因した暗点一致・不一致を判断することで、暗点画素、滅点画素を判定することができる。

#### 【0043】

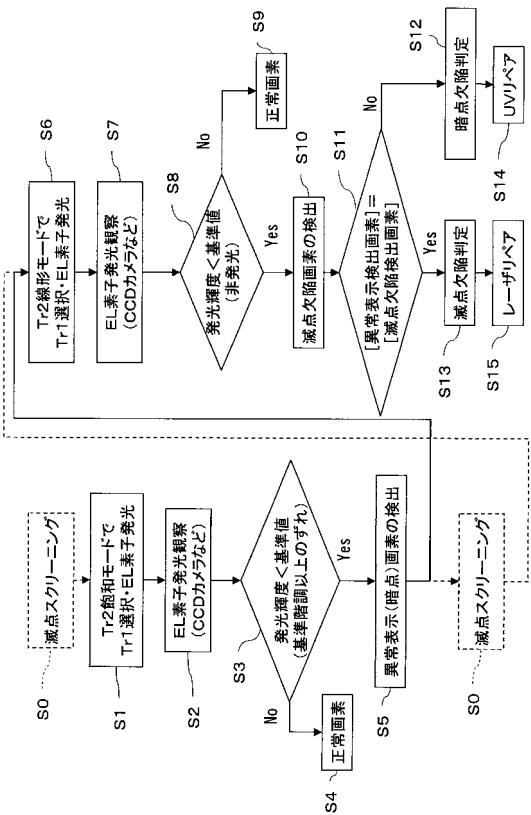

以下、図5を参照して検出方法の一例について具体的に説明する。図5の例では、先に素子駆動Tr2の特性ばらつき(電流供給特性ばらつき。例えば、動作しきい値のばらつき)に起因した異常表示画素の検出を行う。素子駆動Tr2の特性ばらつきに起因した欠陥は、この素子駆動Tr2を飽和領域で動作させてEL素子を発光状態とする制御によって検出する。 30

#### 【0044】

素子駆動Tr2を飽和領域で動作させる条件としては上述の通り $V_{gs} - V_{th} < V_d$ とすればよいが、素子駆動Tr2としてpチャネル型TFTを採用する場合、一例として、電源回路220は、8.5Vの駆動電源PVDD、-3.0Vのカソード電源CVを発生してELパネル100の対応する端子100Tに供給し、検査用信号発生回路230は、表示信号Vsigとして、0Vの検査用オン表示信号を作成する。また、検査用信号発生回路230は、各画素を駆動するために必要なタイミング信号を作成し、これら検査用オン表示信号及びタイミング信号は、端子100TからELパネル100に供給する。 40

#### 【0045】

なお、この素子駆動Tr2の飽和領域での動作は、本実施形態では通常表示動作と同一条件とできるため、駆動電源PVDD、カソード電源CVは、検査装置の電源回路220からではなく、ELパネル100の通常時の駆動用各種電源回路から供給することも可能である。

#### 【0046】

以上のような条件で、電源回路220がELパネル100に所定の駆動電源PVDD、カソード電源CVを供給し、かつ、検査用信号発生回路230が、順次各画素を選択して 50

(選択 Tr 1 をオンして)、素子駆動 Tr 2 を飽和領域で動作させ(飽和動作モード)、また EL 素子を発光させるための検査用オン表示信号を供給する(S 1)。

#### 【0047】

発光検出部 250 は、上記のように素子駆動 Tr 2 を飽和領域で動作させて EL 素子を発光させたときのその発光状態(発光輝度)を撮影する(S 2)。輝度情報は、欠陥検出部 240 に供給され、欠陥検出部 240 は、各画素の発光輝度が、所定基準値より低いかどうかを判断する(S 3)。この基準値は、正常画素における発光輝度の許容最少しきい値であり、要求精度に応じた階調以上の輝度ずれに応じた値に設定することができる(例えば 1 階調 ~ 30 階調相当分のずれ)。

#### 【0048】

10

発光輝度の判断の結果、検査対象の画素の発光輝度が基準値未満でない場合(No)には、該当画素は正常画素であると判定する(S 4)。逆に検査対象の画素の発光輝度が基準値未満である場合(Yes)、この画素は、正常画素よりも輝度の低い異常表示(暗点)画素として判断する(S 5)。また、異常表示画素として判断された画素は、検査装置 200において、データ記憶部(図示せず)に記憶しておく。

#### 【0049】

各画素について、素子駆動 Tr 2 を飽和領域で動作させて異常表示検査を実行した後、検査装置は、素子駆動 Tr 2 を線形領域で動作させるモードに移行する。素子駆動 Tr 2 を線形領域で動作させる条件は、上述の通り、Vgs - Vth > Vds を満足することが必要であり、素子駆動 Tr 2 として p チャネル型 TFT を採用する場合、一例として、EL パネル 100 に、8.0V の駆動電源 PVDD、3V のカソード電源 CV を供給し、各画素に供給する検査用オン表示信号は、0V の信号を採用する。このような条件で、電源回路 220 が EL パネル 100 に所定の駆動電源 PVDD、カソード電源 CV を供給し、かつ、検査用信号発生回路 230 が、順次各画素を選択して、素子駆動 Tr 2 を線形領域で動作させ、かつこの素子駆動 Tr 2 を介して EL 素子を発光させるための検査用オン表示信号を供給する(S 6)。

20

#### 【0050】

発光検出部 250 は、素子駆動 Tr 2 を線形領域で動作させて EL 素子を発光させたときのその発光状態(発光輝度)を撮影する(S 7)。輝度情報は、欠陥検出部 240 に供給され、欠陥検出部 240 は、各画素の発光輝度が基準値より低いかどうかを判断する(S 8)。この基準値は、いわゆる非発光かどうかを判定する基準値であり、上記飽和モードでの測定時と同様に、正常画素における発光輝度の許容最少しきい値としてもよい。

30

#### 【0051】

発光輝度の判断の結果、検査対象の画素の発光輝度が基準値未満でない場合(No)には、該当画素は正常画素であると判定する(S 9)。逆に検査対象の画素の発光輝度が基準値未満である場合(Yes)、この画素は、非発光の滅点欠陥画素と判断する(S 10)。

#### 【0052】

次に、欠陥検出部 240 は、飽和領域モードにおいて異常表示画素と検出され、また線形領域モードにおいて滅点欠陥画素と検出された画素が、一致するかどうかを判断する(S 11)。EL 素子のショートに起因する滅点欠陥は、上述のように、素子駆動 Tr 2 を線形領域及び飽和領域のいずれで駆動しても発光せず滅点として検出される。一方、素子駆動 Tr 2 の特性ばらつきによる暗点欠陥は、素子駆動 Tr 2 を線形領域で駆動した場合には観察されず、飽和領域で駆動した場合にのみ観察される。したがって、飽和領域モードにおいて異常表示画素と検出され、また線形領域モードで滅点欠陥画素と検出された画素が、一致しない場合(No)、その画素を暗点欠陥であると判定する(S 12)。また、一致する場合(Yes)は、滅点欠陥であると判定する(S 13)。

40

#### 【0053】

以上のような手法により、発光状態から暗点欠陥、滅点欠陥をそれぞれ区別して判定することができる。さらに、欠陥の発生数、発生位置、要求品質に応じて修正が可能と判断

50

された場合には、暗点欠陥であると判定された画素に対しては、UVリペアが実行され(S14)、逆に滅点欠陥であると判定された画素に対しては、レーザリペアが実行される(S15)。

#### 【0054】

なお、図5においては、素子駆動Tr2の飽和領域検査モードを実行してから、線形領域検査モードを実行しているが、モードの順番は、どちらでも良く、線形領域検査モードを先に実行し、滅点欠陥として検出された画素を記憶しておき、異常表示画素として検出された画素との一致・不一致を判断して暗点結果を判定しても良い。

#### 【0055】

ここで、滅点欠陥は、その発生が不安定であることが多いことが本発明者らの研究により明らかになっている。このため、複数段階を経る検査工程において、後発的に滅点が発生する又は後発的に滅点が消滅するなどの可能性があり、検査効率や修正効率を低下させる原因となる。そこで、図5においてはステップS0として示すように、滅点欠陥の顕在化処理(滅点スクリーニング)を、少なくとも滅点欠陥の検査開始前(S6よりも前であればよく、S1の前でも良い)に実行することが好適である。

#### 【0056】

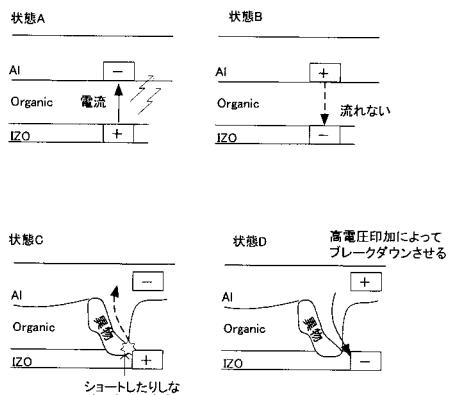

以下に、滅点欠陥の顕在化原理について、図6、図7を参照して説明する。図6の状態Aは、正常なEL素子の発光状態を示し、状態BはEL素子のアノード・カソード間に逆バイアス電圧を印加したときの状態を示している。状態Aでは、アノードとして導電性透明金属酸化物であるIZO(Indium Zinc Oxide)を用い、カソードとしてAlを用いた構成で、このアノード・カソード間に、順方向バイアス電圧を印加したときの状態である。有機層(発光素子層)にはアノードから正孔、カソードから電子が注入され、回路的にはダイオードのアノードからカソードに電流が流れ、図7(a)に示すようなダイオード特性に従って、電流に応じた輝度で発光素子層中の発光材料が発光する。

#### 【0057】

このようなEL素子のアノード・カソード間に逆方向のバイアス電圧を印加しても、正常なEL素子は、その発光素子層が原理的に絶縁性(整流性)で、図7(a)に示すように逆方向耐性が高く電流は流れない。一例としてアノード・カソード間電圧が-30V程度の逆バイアスまで、このEL素子はブレークダウンせず、電流は流れない。

#### 【0058】

一方、図6の状態Cに示すように、発光素子層の成膜時などに異物がアノードとカソードの間に導入されているような場合、薄膜として形成される発光素子層がこの異物を完全に被覆できないことがあり、被覆が不完全な領域でアノードとカソードがショートするなどの場合がある。ところが、このようなショートは必ずしも定常に発生せず、また、ショートの程度が小さいと、同一のEL素子内でショートしていない領域では発光が起き、検査タイミングによって発光したりしなかったりと挙動が一定しない。図7(b)に示すように、ショートしなければこのEL素子は正常画素と同様に発光するが、ショートする非発光となる。順方向バイアス電圧を印加する場合には、このショートは起きたり起きなかったりを繰り返すこととなり、例えば一次検査では滅点と判定されたが、後の二次検査では未検出となったり、その逆で、製品出荷後に滅点となったりする可能性がある。これに対し、異物など混入部分は正常時のような発光素子層による高い耐圧性が得られないため、図6の状態Dに示すように、不安定なEL素子に対して所定値以上の高い逆バイアス電圧を印加すると、図7(b)に示されるように、正常なEL素子と比較してより小さい逆バイアス電圧でブレークダウンが発生すると考えられる(マイグレーション的効果)。また、アノード・カソード間が一旦ブレークダウンすると、このEL素子に対して、順方向バイアスを印加しても、定常にショートモードとなり、常時、非発光の欠陥(滅点欠陥)となる。

#### 【0059】

したがってEL素子のショートに起因した滅点欠陥を検査する前に、このような逆バイアス電圧による滅点の顕在化(スクリーニング)を実行することにより、滅点の可

10

20

30

40

50

能性のある画素を確実にあぶり出すことができる。

#### 【0060】

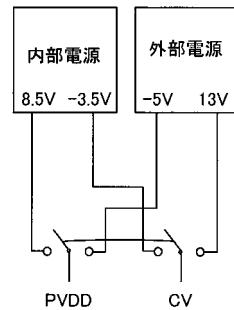

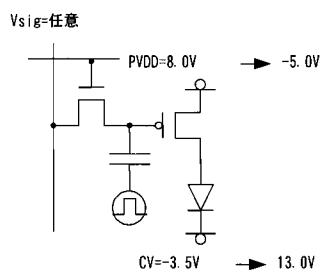

E L 素子への逆バイアス電圧の印加は、図8に示すように、例えば、駆動電源P V D D を通常表示電圧(8.0V)から-5Vに切り替え、カソード電源C V を通常表示電圧(-3.5V)から13.0Vに変更し、素子駆動T r 2 のゲートに接続された保持容量C s 電位を固定して任意の表示信号(V sig)を選択T r 1 を介して素子駆動T r 2 のゲートに印加することにより実行することができる。

#### 【0061】

駆動電源P V D D 及びカソード電源C V の滅点スクリーニング用電源への切り替えは、図9に示すように、スクリーニング装置に、スクリーニング用電源を外部電源により選択的に供給できるようにスイッチを設け、E Lパネル100に表示用に供給される内部電源に代えて上記外部電源を供給可能な構成することで実行することができる。また、このスクリーニング装置は、図4に示すような検査装置に内蔵してもよい。この場合、電源回路220が上記のような検査用電源だけでなくスクリーニング用電源を発生し、また検査用信号発生回路230がスクリーニング用信号を作成し、これらを選択的にE Lパネル100に供給してもよい。なお、スクリーニングに際し、画素の選択・駆動タイミングについては、通常表示と同様に制御すれば良く、また逆バイアス電圧の印加時間は、極めて短時間で効果が得られ、一例として10sec程度でよい。

#### 【0062】

次に、素子駆動T r 2 の特性ばらつきに起因した暗点欠陥のリペアについて説明する。本願発明者らの研究により、素子駆動T r 2 の特性ばらつきを発生させるその動作しきい値V t hについて、この素子駆動T r 2 に所定条件でUV光を照射することで修正できることが判明した。

#### 【0063】

具体的には、素子駆動T r 2 のゲートに所望の電圧を印加し、かつ素子駆動T r 2 のソース電圧、ドレイン電圧を等しいバイアス電圧V biasとする。なお、駆動電源P V D D をV biasとし、カソード電源C V を同じV biasとすることで、素子駆動T r 2 のソース及びドレインに、等しいバイアス電圧V biasを印加することができる。このとき素子駆動T r 2 のゲートには、素子駆動T r 2 のゲート・チャネル間に必要な電圧を印加するための任意の電圧(E Lオフ表示信号)を印加すれば良く、一例として、pチャネルT F Tから構成される素子駆動T r 2 をオフさせる所望のオフ表示電圧(V sig = V black)を印加している。もちろん、オフ表示電圧には限定されず、オン表示信号(V sig = V white)を印加しても良い。

#### 【0064】

そして、このバイアス電圧V biasを素子駆動T r 2 の動作しきい値V t hの目的とするシフト量に応じて設定し、素子駆動T r 2 の多結晶シリコンなどから構成される能動層(チャネル領域)にUV光を照射することで、動作しきい値V t hを修正することができる。

#### 【0065】

なお、素子駆動T r 2 の動作しきい値シフトに必要とされるUV光の波長は、概ね295nm以下であり、このような波長のUV光を素子駆動T r 2 のチャネル領域に照射できるように、E Lパネル100のパネル材料を選択し(該当する波長について透過性のあるパネル料を採用する)、また、上記パネル材料などを透過してチャネル領域に到達するために必要な所望のパワーに設定する。

#### 【0066】

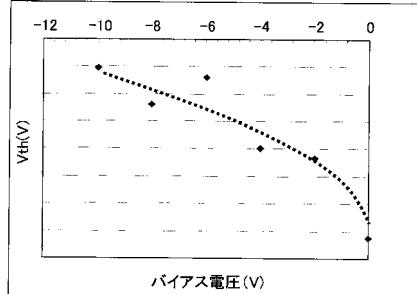

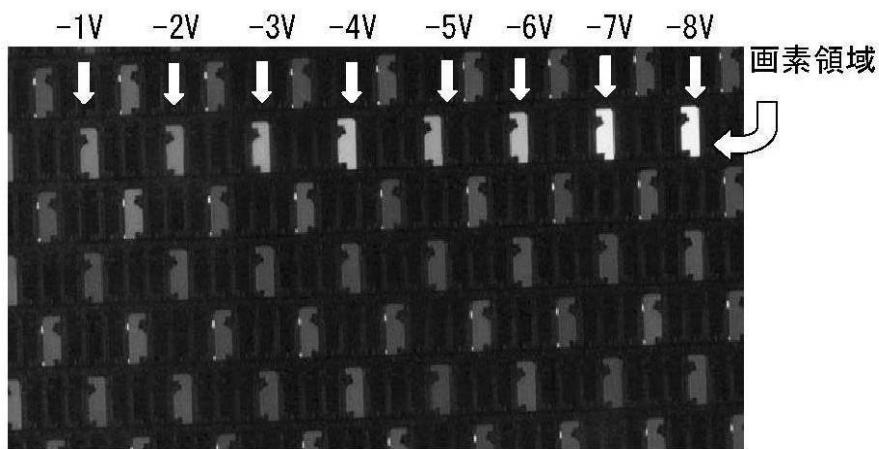

図10は、上記素子駆動T r 2 のソースドレイン間に印加するバイアス電圧V biasと、各バイアス条件でのリペア後のE L素子の発光状態の一例を示し、図11は、上記バイアス電圧V biasと、動作しきい値V t hとの関係の一例を示す。

#### 【0067】

図10において、画素の回路構成は、図1に示すような等価回路を採用し、素子駆動T

10

20

30

40

50

$r_2$  のゲートには、例えば 8.0 V を印加し、特性の等しい素子駆動  $T_{r2}$  に対して、それぞれ、バイアス電圧  $V_{bias}$  を -1 V、 -2 V、 -3 V、 -4 V、 -5 V、 -6 V、 -7 V、 -8 V を印加した。そして、同一条件で UV 光を照射した場合、図 10 に示すように、印加するバイアス電圧  $V_{bias}$  によって EL 素子の発光輝度に違いが生じている。より具体的には、バイアス電圧  $V_{bias}$  の絶対値が大きくなるにつれ発光輝度は大きくなっている。また、素子駆動  $T_{r2}$  の特性しきい値  $V_{th}$  の絶対値が、小さくなる方向にシフトし、その結果、対応する EL 素子により多くの電流が供給され発光輝度が上昇していることが理解できる。

#### 【0068】

図 11 に示すように、素子駆動  $T_{r2}$  の特性しきい値  $V_{th}$  の絶対値は、実際に印加するバイアス電圧  $V_{bias}$  の絶対値が大きくなるにつれて小さくなっている（図 11 の縦軸上方が  $V_{th}$  の 0 V 方向）。

#### 【0069】

このように、素子駆動  $T_{r2}$  のゲートと、ソースドレイン間に、所望の大電圧  $V_g - V_{bias}$  を印加しながら UV 光を照射することで、素子駆動  $T_{r2}$  の特性しきい値  $V_{th}$  を調整できる。したがって、EL 素子に要求される発光輝度になるようにバイアス電圧  $V_{bias}$  を設定すれば、素子駆動  $T_{r2}$  の特性ばらつきに起因した暗点欠陥を修正することができる。なお、高精度に暗点欠陥を修正するためには、例えば、上記図 5 に示す発光輝度と基準値との比較ステップ（S3）において、基準値との差を画素毎に記憶しておき、UV リペアステップ（S14）において、基準値の差に応じたバイアス電圧  $V_{bias}$  を印加して修正することで対応することができる。

#### 【0070】

次に、滅点欠陥画素に対して実行するレーザリペア（S14）について説明する。このレーザリペアは、滅点欠陥画素の EL 素子のショート発生領域に、所望の波長かつパワーのレーザ光を選択的に照射して、そのショート領域を焼き切る（電流供給経路を切断して絶縁化する）ことで、アノードとカソードのショート状態を解消する方法である。リペア用のレーザ光としては、一例として 355 nm ~ 1064 nm 程度の波長で、所望のパワーのレーザ光を採用することができる。

#### 【0071】

このように、本実施形態によれば、単に発光輝度の低い欠陥としてではなく、その欠陥の種別が暗点欠陥であるか滅点欠陥であるかを正確に検出することができ、直ちに、暗点及び滅点の修正に適した修正工程に進むことができ、検査及び修正を効率的に実行することが可能となる。

#### 【0072】

##### （カソード電流検査）

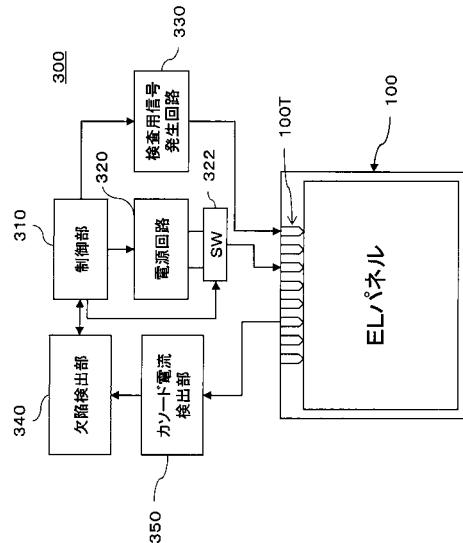

次に、EL 素子のカソード電流  $I_{cv}$  から暗点欠陥、滅点欠陥を検査する装置及び検査方法について説明する。図 12 は、カソード電流を測定して暗点・滅点欠陥を検出する検査装置の概略構成を示している。

#### 【0073】

図 12 に示す検査装置は、上記発光輝度から欠陥検査を実行する装置において採用されている発光検出部 250 ではなく、カソード電流  $I_{cv}$  を検出するカソード電流検出部 350 を備える点が大きく異なる。制御部 310、電源回路 320、電源切り替え部 322、検査用信号発生回路 330 は、上述の発光輝度を利用した欠陥検査装置と同様に、検査に必要な電源、検査用のタイミング信号や表示信号等を発生して EL パネル 100 に供給する。欠陥検出部 340 は、カソード電流検出部 350 が検出したカソード電流  $I_{cv}$  に基づいて滅点欠陥と、暗点欠陥を検出する。

#### 【0074】

この例では、EL 素子に流れる電流（ここではカソード電流  $I_{cv}$ ）を測定するので、滅点欠陥については、図 2 に示すように、素子駆動  $T_{r2}$  を線形領域で動作させた時の EL 素子のカソード電流を測定することで判別する。暗点欠陥については、図 3 に示すよう

10

20

30

40

50

に、素子駆動 Tr 2 を飽和領域で動作させた時の EL 素子のカソード電流を測定することで判別する。

#### 【0075】

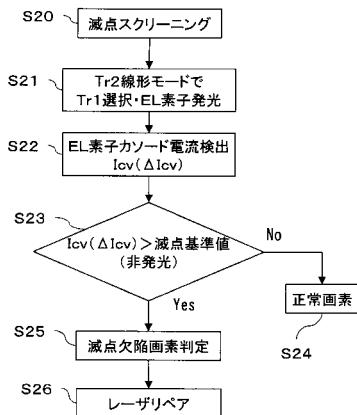

図13は、EL 素子のショートに起因した滅点欠陥の検査手順を示している。滅点欠陥の検査に先立って、まず、不安定な EL 素子のショートを顕在化させることが好適であり、上述のように、EL 素子のカソード・アノード間に逆バイアス電圧を印加して滅点スクリーニングを実行する(S20)。

#### 【0076】

次に、素子駆動 Tr 2 を線形領域で動作させ、選択 Tr 1 をオンさせ、かつ検査用オン表示信号を対応する画素の選択 Tr 1 を介して素子駆動 Tr 2 のゲートに印加する(S21)。

10

#### 【0077】

なお、素子駆動 Tr 2 を線形領域で動作させる条件は、上述の通り、 $V_{gs} - V_{th} > V_{ds}$  を満足するように設定する。素子駆動 Tr 2 として p チャネル型 TFT を採用する場合の電圧は、発光輝度検出の場合と同様、一例として、駆動電源 PVDD を 8.0V、カソード電源 CV を 3V とし、各画素に供給する検査用オン表示信号は、0V の信号を採用する。

#### 【0078】

カソード電流検出部 350 は、例えば、EL パネル 100 の外部接続端子 100T のうちのカソード端子に接続されており、このカソード端子に得られるカソード電流  $I_{cv}$  を検出する。ここで、EL 素子のカソードは、上述のように複数の画素に共通で形成されているため、画素を順次選択し、その選択期間に対応する期間にカソード端子に得られるカソード電流  $I_{cv}$  をその画素についてのカソード電流  $I_{cv}$  とする。なお、カソード電流  $I_{cv}$  は、その電流値に応じた電圧として検出することができる。

20

#### 【0079】

次に、欠陥検出部 340 は、カソード電流検出部 350 で得られた各画素のカソード電流  $I_{cv}$  が滅点基準値よりも大きいかどうか判断する(S23)。EL 素子にショートが発生した場合には、上述のように EL 素子の IV 特性の傾きが大きくなることから、素子駆動 Tr 2 を線形領域で動作させた時のカソード電流  $I_{cv}$  は正常の EL 素子のカソード電流  $I_{cv}$  よりも大きくなる。そこで、滅点基準値として、正常 EL 素子のカソード電流値に応じた値を設定し、検出したカソード電流  $I_{cv}$  がその滅点基準値以下の場合には(No)、正常画素と判断する(S24)。また、検出したカソード電流  $I_{cv}$  が滅点基準値を超える場合には、その画素を滅点欠陥画素と判定する(S25)。

30

#### 【0080】

滅点欠陥が検出されたパネル 100 は、滅点を修正するためのレーザリペア工程に進みここで修正を受ける(S26)。

#### 【0081】

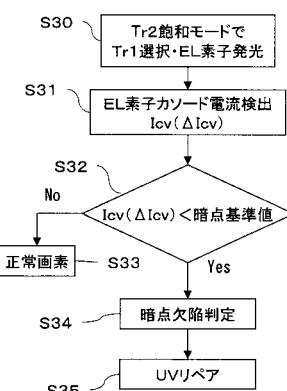

図14は、素子駆動 Tr 2 の特性ばらつきに起因した暗点欠陥の検出手順を示している。素子駆動 Tr 2 の特性ばらつきに起因した暗点欠陥については、上述のように素子駆動 Tr 2 を飽和領域で動作させ、選択 Tr 1 をオンさせ、かつ検査用オン表示信号を対応する画素の選択 Tr 1 を介して素子駆動 Tr 2 のゲートに印加する(S30)。

40

#### 【0082】

素子駆動 Tr 2 を飽和領域で動作させる条件は、上述の通り、 $V_{gs} - V_{th} < V_{ds}$  を満足するように設定する。素子駆動 Tr 2 として p チャネル型 TFT を採用する場合の電圧は、発光輝度検出の場合と同様、一例として、駆動電源 PVDD を 8.0V、カソード電源 CV を -3V とし、各画素に供給する検査用オン表示信号としては、0V の信号を採用する。

#### 【0083】

カソード電流検出部 350 は、素子駆動 Tr 2 を飽和領域で動作させ、EL 素子を発光させたときのカソード電流  $I_{cv}$  を検出する(S31)。また、欠陥検出部 340 は、検

50

出されたカソード電流  $I_{cv}$  が暗点基準値より小さいかどうか判断する (S32)。素子駆動  $Tr_2$  の動作しきい値が正常値よりも低下した画素のカソード電流  $I_{cv}$  は、上述のように、素子駆動  $Tr_2$  の飽和領域において、正常な画素におけるカソード電流  $I_{cv}$  よりも小さくなる。したがって、例えば、正常画素に対して許容される階調以上（一例として1階調～30階調相当）のずれを生ずるカソード電流  $I_{cv}$  を基準値として比較することで、正常画素と暗点欠陥画素とを区別することができる。

#### 【0084】

比較の結果、検出したカソード電流  $I_{cv}$  が基準値より小さくない場合 (No) には、その画素は正常と判定し (S33)、基準値より小さい場合 (Yes)、その画素を暗点欠陥画素と判定する (S34)。このようにして、カソード電流  $I_{cv}$  の検出結果に基づいて素子駆動  $Tr_2$  の特性ばらつきに起因した暗点欠陥画素を検出することができる。そして、この素子駆動  $Tr_2$  の特性ばらつきについては、上述のように、UVリペア工程に進み、素子駆動  $Tr_2$  の特性ばらつきが修正される (S35)。

#### 【0085】

以上のように、本実施形態によれば、素子駆動  $Tr_2$  の線形領域と飽和領域でそれぞれ動作させ、そのときのカソード電流  $I_{cv}$  を検出することで、EL素子のショートに起因した滅点欠陥についても、素子駆動  $Tr_2$  の特性ばらつきに起因した暗点欠陥についても区別して検出することができる。このような検査は、いずれも図12に示すような装置構成によって実行できる。

#### 【0086】

図12の装置を滅点検査専用の装置とする場合、電源回路320及び検査用信号発生回路330が、素子駆動  $Tr_2$  を線形領域で動作させてEL素子を発光させるために必要な電源、駆動信号を作成し、これを対応する画素に印加する構成とすればよい。なお、滅点スクリーニング装置を兼用する場合には、電源回路320が、図8及び図9に示したようなスクリーニング用の駆動電源PVD及びカソード電源CVを発生し、これを切り替え部322によって、選択的に各画素に印加する共に、検査用信号発生回路330が、データ信号Vsigとして任意のスクリーニング用表示信号を発生してこれを各画素に供給する。

#### 【0087】

図12の装置を暗点検査専用の装置とする場合には、素子駆動  $Tr_2$  を飽和領域で動作させて、EL素子を発光させるために必要な電源、駆動信号を作成し、これを対応する画素に印加する構成とすればよい。

#### 【0088】

滅点検査専用、暗点検査専用の装置においては、駆動電源PVD、カソード電源CVについて、それぞれ単一の検査用電源を発生すればよいため、図12の電源回路320は専用電源を発生し、電源切り替え回路322は省略することができる。通常表示動作を実行して目視による表示検査用の装置と、滅点検査装置を兼用する場合には、通常表示において素子駆動  $Tr_2$  を飽和領域で駆動するので、滅点検査時に電源を切り替えることが必要である。

#### 【0089】

また、カソード電流  $I_{cv}$  を利用した滅点検査装置及び暗点検査用装置は、单一装置として構成することも可能であり、この場合、図12に示す検査装置の各部は、制御部310の制御により、検査モード（滅点検査モード、暗点検査モード）に応じて、それぞれの検査に必要な動作を実行する。つまり、電源回路320、電源切り替え部322、検査用信号発生回路330は、各モードで必要な電源、検査用信号を発生し、欠陥検出部340は、モードに応じた基準値とカソード電流  $I_{cv}$  とを比較して、滅点判定、暗点判定を行う。

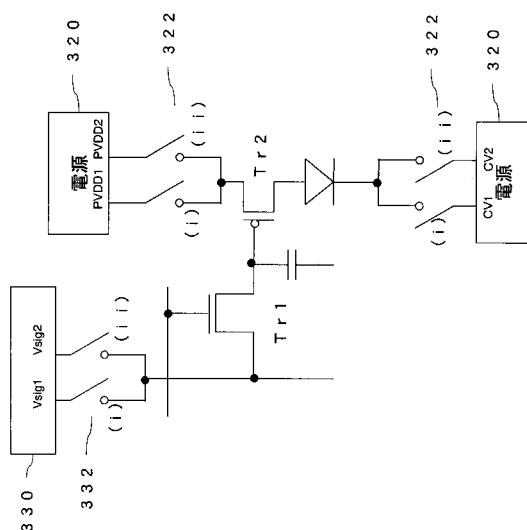

#### 【0090】

図15は、複数のモードや、異なる検査を実行する場合に、図12に示す検査装置に採用可能な電源及び表示信号の切り替え構成の一例を示している。切り替え回路322、3

10

20

30

40

50

32は、図12の制御部310によって切り替え制御される。また、電源回路320はモードに応じた複数種類の電源を発生し、切り替え回路322によって、例えば滅点検査モードの場合には、各電源ラインには端子(i)を介してPVDD1、CV1を供給する。同様に検査用信号発生回路330がモードに応じた複数種類の検査用表示信号を作成し、切り替え回路332によって、データラインDLには端子(i)を介してVsig1が供給される。別のモード(例えば暗点検査モード)の場合は、切り替え回路322, 332が対応する端子(ii)を介して、それぞれ電源(PVDD2, CV2)及び表示信号(Vsig2)を供給する。

#### 【0091】

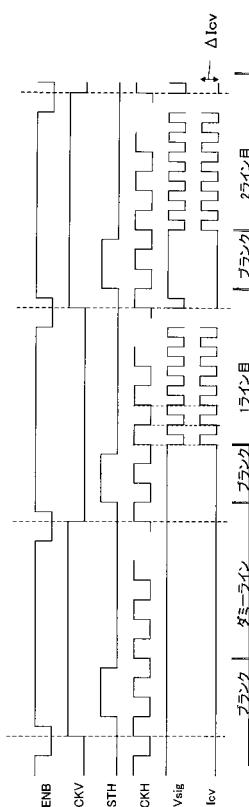

##### (高速検査方法)

図16は、カソード電流Icvを利用して高速に滅点欠陥、暗点欠陥を検査する場合のELパネル100の駆動波形を示している。図16に示す検査方法では、1画素を選択する期間中(1水平クロック信号の2分の1周期)に、該当する画素に対し、検査用表示信号Vsigとして、オン表示信号(EL発光)とオフ表示信号(EL非発光)とを連続して印加する。なお、この検査用表示信号は、図12の検査用信号発生回路330が、水平スタート信号STH、水平クロック信号CKH等を利用して作成する。カソード電流検出部350は、オン表示信号に対応したEL素子のカソード電流Icv<sub>on</sub>及びオフ表示信号に対応したEL素子のカソード電流Icv<sub>off</sub>をそれぞれ検出し(必要に応じて電流增幅する)、欠陥検出部340は、オンとオフのカソード電流の差分Icvを求め、その差分データと、例えば正常画素における差分データに基づいた基準値とを比較することで、滅点欠陥判定及び暗点欠陥判定をそれぞれ実行する。

#### 【0092】

また、図16に示す検査方法においても、上述のように、滅点欠陥検査モードでは、素子駆動Tr2が線形領域で動作するように駆動電源PVDD及びカソード電流CVを設定し、暗点欠陥検査モードでは素子駆動Tr2が飽和領域で動作するように駆動電源PVDD及びカソード電流CVを設定する。また、図16において、垂直クロック信号CKVは垂直方向の画素数に応じたクロック信号であり、イネーブル信号ENBは、1水平走査期間の最初と最後において、表示信号Vsigが確定しないうちに各水平走査ライン(ゲートラインGL)に選択信号が出力されることを防止するための禁止信号である。

#### 【0093】

このように、オフ表示信号の時のカソード電流Icv<sub>off</sub>を測定し、このIcv<sub>off</sub>を基準としてオン表示信号の時のカソード電流Icv<sub>on</sub>を相対的に把握することにより、オン表示信号の時のカソード電流Icv<sub>on</sub>の絶対値を正確に判断する必要や、別途基準となるオフ表示信号の時のカソード電流Icv<sub>off</sub>を測定する必要がなく、高速の自動検査を高精度に実行することが可能となる。

#### 【0094】

また、図16に示す検査方法では、マトリクス配置された画素の列方向、つまり各データラインDLに表示信号を出力する期間を決める水平スタート信号STHが、2列分の選択期間に設定されている。本実施形態において、通常表示時には、各水平走査ライン上の画素は、対応する1H期間だけ選択され、このとき対応するデータラインDLには、1H期間を1水平走査方向の画素数で割った期間に相当する期間づつ、表示信号Vsigが出力される。これに対し、欠陥検査時には検査用の水平スタート信号STHを用いることで、1データラインDLに対して2画素分の表示信号出力期間、検査用表示信号Vsigが供給される。つまり、同一の水平走査ラインに並ぶ画素は、隣接する2画素が同時に検査対象となる。なお、この画素の同時検査対象数は、2には限られず、例えば3画素づつを検査対象としても良い。このように1画素について複数回連続して検査対象とすることにより、タイミング信号や検査用表示信号Vsig等にノイズが重畠して画素が誤表示した場合にも、そのようなノイズ重畠が複数期間連続して発生する確率が小さいため、ノイズによる誤検出を低減することが可能となる。なお、複数画素を連続して選択する方法は、カソード電流を利用した検査方法だけでなく、上述の図4及び図5を用いて説明した発光

輝度を利用した検査方法においても適用することで、同様にノイズの影響を低減することが可能となる。

#### 【0095】

ここで、ELパネル100の表示部の各画素を駆動するための駆動回路のうち、水平方向駆動回路は、水平走査方向における画素数に応じた段数のシフトレジスタを備え、このシフトレジスタが、水平スタート信号STHを水平クロック信号CKHに応じて順次転送し、かつ、レジスタの各段から、サンプリング回路に対し、対応するデータラインDLに表示信号Vsigを出力する期間（サンプリング期間）を決めるサンプルホールド信号が出力される。そして、このサンプルホールド信号の示すサンプリング期間が、上記水平スタート信号STHの期間（ここではHレベル期間）に対応する。このため、ELパネル100の水平方向駆動回路に対し、欠陥検査時には、水平スタート信号STHとして、検査用信号発生回路330の作成した図16に示すような検査用の水平スタート信号STHを供給し、また、各データラインDLにサンプリング回路を介して接続されるビデオ信号ラインに図16に示すような検査用表示信号Vsigを出力すれば、複数画素ごとに検査用表示信号Vsigが供給され、検査を実行することが可能となる。10

#### 【0096】

なお、図16の駆動方法は、データラインDLに供給される表示信号の駆動波形の切り替わりタイミングに連動して、素子駆動Tr2のオンオフ（EL素子の発光、非発光）タイミングが設定される画素回路を備える場合に有効であり、一例として図1に示すような画素回路構成に対して適用することができる。また、各画素の保持容量Csの電位を制御するための容量ラインCLに、所望の交流信号が供給されるような画素回路構成であっても、検査時に容量ラインCLの電位を固定する容量電位制御スイッチなどを付加し、素子駆動Tr2を、データラインDLに供給する表示信号のタイミングに応じて動作させることで、図16のような検査方法を採用することができる。20

#### 【0097】

##### [EL表示装置の製造方法]

次に、さらに図17を参照して、EL表示装置の欠陥検査、欠陥修正を含む製造手順の一例を説明する。パネル基板上に必要な回路素子、EL素子などを形成して完成したEL表示装置（ELパネル）に対しては、まず一次検査が実行される（S40）。この一次検査は、多岐に亘り、ラスター画像を表示し、色むら、画素回路のショートなどによる輝点欠陥、滅点欠陥、暗点欠陥の検査を、例えば目視や、CCDカメラ等を用いた観察（輝度検出）によって実施する。また、モノスコバターンを表示させて表示装置の解像度検査等を実行する。なお、滅点欠陥、暗点欠陥については、本実施形態において上述したように、素子駆動Tr2を線形領域、飽和領域で動作させたときの、EL素子の特性（発光輝度、カソード電流）に基づいて検査し、滅点及び暗点欠陥を検出することがより好ましい。30

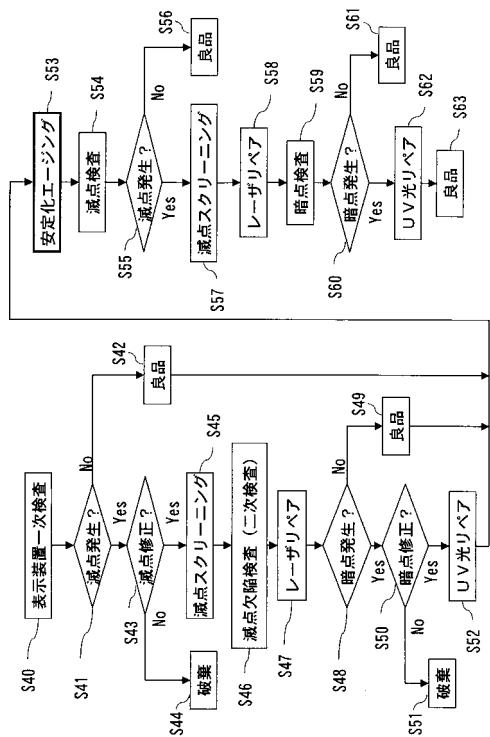

#### 【0098】

一次検査での滅点検査で滅点が発生したかどうか判断し（S41）、その結果、発生なれば（No）、良品とする（S42）。なお、図17では、この良品は、図示の都合上、他の検査項目でも良品と判定された表示装置を意味しており、この表示装置は、次に、後述する安定化エージング（S53）工程に進む。40

#### 【0099】

滅点が発生し（Yes）、例えばその滅点欠陥数や、滅点発生度合い、或いは発生位置などの情報から、次に滅点の修正を行うかどうか判断する（S43）。判断の結果、発生数が許容規格値より多い、或いは修正したとしても許容できない位置であるような理由で修正しないと判断した場合（No）、この表示装置は不良品として破棄される（S44）。

#### 【0100】

滅点修正を実行すると判断した場合（Yes）、次に、発生した滅点を修正するための前工程として、EL素子に逆バイアス電圧を印加することによる滅点スクリーニングを実行する（S45）。この滅点スクリーニングにより、滅点は顕在化し、次の滅点欠陥検査50

(二次検査) 時において (S 4 6)、確実に滅点欠陥(特にその発生位置)を検出するこ

とが可能となる。

#### 【0101】

滅点欠陥検査 (S 4 6) の結果、その発生位置が特定された滅点欠陥については、次に

レーザリペアが実行される (S 4 7)。このレーザリペアは、既に説明したように、EL

素子のショートに起因した滅点欠陥を、そのショート領域にレーザ光を照射することで絶

縁化して修正する方法である。

#### 【0102】

ここで、一次検査で確認された滅点欠陥がその修正工程で消滅する確率は、従来は例え

ば 50% 程度と高かったが、滅点スクリーニングを実行することで、スクリーニング後の

滅点欠陥の発生数は、例えば 500 時間の信頼性試験の後で 0 とすることが可能となっ

ている。また、レーザリペアに先立って、滅点スクリーニングを行うことで、一次検査で顯

在化していなかった滅点についても滅点欠陥として検出して、修正することができる。

10

#### 【0103】

次に、上記一次検査で暗点欠陥が検出されたかどうかを判断し (S 4 8)、発生してい

ない場合 (No)、良品と判断し (S 4 9)、安定化エージング工程 (S 5 3) に移行す

る。暗点欠陥が検出された場合 (Yes)、この暗点欠陥が修正可能な輝度ずれ(階調ず

れ)に収まっているかどうか、或いはその発生位置、発生数に応じて、暗点欠陥の修正を

実行するかどうか判断する (S 5 0)。修正しない判断した場合 (No)、この表示装置

は、不良品として破棄する (S 5 1)。

20

#### 【0104】

暗点修正をすると判断した場合 (Yes)、上述したように素子駆動 Tr 2 を飽和領域

で動作させ素子駆動 Tr 2 の特性ばらつきに起因する暗点欠陥を検査し、欠陥発生位置を

明らかにし、欠陥に対して UV 光を照射してリペアを実行する (S 5 2)。このような UV

光リペアにより、素子駆動 Tr 2 の特性ばらつきに起因した暗点欠陥が修正される。

#### 【0105】

以上のようにして一次検査で良品と判断され、又は滅点、暗点が修正された表示装置に

対しては、次に、安定化エージング処理が施される (S 5 3)。この安定化エージングは

、所定の高温、高湿度環境に EL 表示装置を晒す処理である。一般に、EL 素子の特性が

熱や水、酸素などによって劣化するため、原理的にはこのようなエージング処理は実行し

ない方が、より高性能な EL 表示装置を製品として提供することができる。しかし、EL

素子の初期劣化速度が大きいため、特性が多少劣化したとしても、その特性を安定化させ

てから製品として提供することが適切であるため採用されている。

30

#### 【0106】

このエージング処理は、上記のように高温高湿度環境に EL 表示装置を晒すため、この

エージング処理によって、新たに滅点欠陥や暗点欠陥などが生ずることがある。そこで、

本実施形態では、安定化エージング実行後、再び上述のような素子駆動 Tr 2 を線形領域

で動作させた滅点欠陥検査(二次検査)を行い (S 5 4)、滅点欠陥が発生していない場

合には (S 5 5; No)、この表示装置を良品とし (S 5 6)、さらに必要な組み立て工

程、検査工程などにまわす。滅点欠陥の発生が検出された場合 (S 5 5; Yes)、この

滅点をより確実に顯在化させるため滅点スクリーニングを実行する (S 5 6)。

40

#### 【0107】

スクリーニング実行後、滅点欠陥位置を特性するために欠陥検査を実行し、位置が特定

された滅点欠陥に対し、レーザリペアが施される (S 5 8)。

#### 【0108】

また、エージング実行後、暗点欠陥についても、再度、上述のように素子駆動 Tr 2 を

飽和領域で動作させて暗点欠陥検査を実行し (S 5 9)、暗点が検出されなかった場合 (S

6 0; No)、良品と判定する (S 6 1)。

#### 【0109】

暗点欠陥が検出された場合 (S 6 0; Yes)、検出された位置における暗点欠陥に対

50

してUV光リペアが実行され(S62)、リペアにより欠陥が修正された表示装置は良品として出荷用の製品にまわされる(S63)。

#### 【0110】

以上のように、一次検査で滅点欠陥が検出された場合、滅点スクリーニングを実行してから、二次検査として素子駆動Tr2を線形領域で動作させEL素子のショートに起因した滅点欠陥の検査を実行することで、滅点欠陥の存在とその位置を特定した上で、確実にレーザリペアによって修復することができ、不良品となってしまう表示装置数を削減し、また、高効率の欠陥検査を可能として製造コストの削減にも寄与することができる。

#### 【0111】

なお、上記一次検査において、滅点欠陥は、各画素の前記エレクトロルミネッセンス素子を発光状態に制御し、その発光輝度が基準値未満に相当する画素を該滅点欠陥として検出する。この発光輝度が基準値未満に相当する画素については、上述のように、ラスター画像を表示させて測定した各画素の発光輝度の測定から輝度が不十分と判断される画素の他、本実施形態において説明したような素子駆動Tr2を線形領域で動作させてEL素子を発光状態としたときの発光輝度や、カソード電流に基づき、発光輝度に換算した場合に基準値未満となる画素を意味する。

10

#### 【0112】

ここで、図17に示す製造方法の例では、一次検査や、エージング後の滅点欠陥検査の結果、滅点欠陥が検出された表示装置に対して滅点スクリーニングを実行している。しかし、例えば一次検査時及び安定化エージング処理の後に、全ての表示装置に対し、滅点スクリーニングを実行してもよい。全表示装置に対してスクリーニングを実行することで、後発的な滅点欠陥の発生の可能性を大幅に削減することができる。但し、処理数の増大は製造時間、つまり製造コストに影響を及ぼすので、図17に示すように先行する滅点欠陥検査で滅点が検出された表示装置にのみ実行することで、処理時間の削減を図ることが可能となる。また、後発的に滅点欠陥が発生する確率から、一次検査や、エージング処理後の欠陥検査で良品として判断可能な発生許容限界に近い数の滅点欠陥が検出された表示装置にのみ滅点スクリーニングを実行してもよい。発生許容限界に近い数の滅点欠陥が既に検出されている場合には、後発的にこの表示装置にさらに滅点欠陥が発生した場合、その時点で不良品となり、それまでの検査、修正工程に要した時間やコストが無駄になるためである。

20

#### 【0113】

また、滅点スクリーニングは、滅点欠陥と暗点欠陥の両方が所定数以上検出された場合に、その表示装置に対して実行してもよい。

#### 【図面の簡単な説明】

#### 【0114】

【図1】本発明の実施形態に係るEL表示装置の概略回路構成を説明する等価回路図である。

【図2】本発明の実施形態に係る滅点表示欠陥画素の特性を説明する図である。

【図3】本発明の実施形態に係る暗点(DIM)表示欠陥画素の特性を説明する図である。

30

【図4】EL素子の発光状態を利用した滅点・暗点表示欠陥検査装置の概略構成を示す図である。

【図5】図4の検査装置を利用した発光状態検査手順の一例を示す図である。

【図6】EL素子のショートの原理及びショート(滅点)の顕在化原理を示す図である。

【図7】ショートの発生の有無に応じたEL素子のIV特性を違い説明する図である。

【図8】滅点の顕在化のための駆動方法を示す図である。

【図9】滅点顕在化のための装置構成を説明する図である。

【図10】暗点欠陥修正するためのUVリペアにおけるバイアス条件と発光輝度との関係の一例を説明する図である。

【図11】暗点欠陥修正するためのUVリペアにおけるバイアス条件と動作しきい値Vt

40

50

$h$  のシフト量との関係の一例を説明する図である。

【図 1 2】EL 素子のカソード電流  $I_{cv}$  を利用した滅点・暗点表示欠陥検査装置の概略構成を示す図である。

【図 1 3】カソード電流を利用した滅点表示欠陥の検査手順の一例を示す図である。

【図 1 4】カソード電流を利用した暗点表示欠陥の検査手順の一例を示す図である。

【図 1 5】カソード電流を用いた滅点及び暗点の両方の検査機能を備える検査装置の電源及び駆動信号切り替え部の構成を示す図である。

【図 1 6】カソード電流を利用した高速の検査を実行するための駆動波形を示す図である。

【図 1 7】本発明の実施形態に係る EL 表示装置の欠陥検査及び修正工程を含む全体的な製造手順の一例を示す図である。 10

【符号の説明】

【0 1 1 5】

100 EL パネル、200, 300 欠陥検査装置、210, 310 制御部、22

0 電源回路、222, 322 電源切り替え部、230, 330 検査用信号発生回路

、240, 340 欠陥検出部、250 発光検出部、350 カソード電流検出部。

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図10】

---

フロントページの続き

(51)Int.Cl.

F I

|        |      |         |

|--------|------|---------|

| G 09 G | 3/20 | 6 2 4 B |

| G 09 G | 3/20 | 6 4 1 D |

| G 09 G | 3/20 | 6 1 2 R |

| G 09 G | 3/20 | 6 7 0 Q |

(56)参考文献 特開2002-040082(JP,A)

特開2006-092886(JP,A)

特開2001-159872(JP,A)

特開平11-231280(JP,A)

特開2004-101767(JP,A)

特開2006-107826(JP,A)

特開2005-115338(JP,A)

特開2005-149768(JP,A)

特開2005-149769(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 3 0

G 09 G 3 / 2 0

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于电致发光显示装置的缺陷检查方法和缺陷检查装置以及使用该装置制造电致发光显示装置的方法                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP4836718B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2011-12-14 |

| 申请号            | JP2006239626                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2006-09-04 |

| [标]申请(专利权)人(译) | 三洋电机株式会社<br>三洋半导体株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 三洋电机株式会社<br>三洋半导体有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 当前申请(专利权)人(译)  | 安森美半导体贸易有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 小川隆司                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 小川 隆司                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G09G3/30 H05B33/12 H01L51/50 H05B33/10 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| CPC分类号         | G09G3/006 G09G3/3225 G09G3/3233                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G09G3/30.H H05B33/12.Z H05B33/14.A H05B33/10 G09G3/30.J G09G3/20.624.B G09G3/20.641.D<br>G09G3/20.612.R G09G3/20.670.Q G09G3/3233 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                         |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC45 3K107/GG14 3K107/GG56 3K107/GG57 5C080/AA06 5C080/<br>/BB05 5C080/DD15 5C080/DD28 5C080/EE25 5C080/EE29 5C080/FF11 5C080/GG02 5C080/JJ01<br>5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5C080/JJ07 5C380/AA01 5C380/AB06<br>5C380/AB34 5C380/CA08 5C380/CA12 5C380/CC02 5C380/CC26 5C380/CC29 5C380/CC30 5C380<br>/CC33 5C380/CC62 5C380/CD012 5C380/DA02 5C380/DA06 5C380/FA05 5C380/FA21 5C380/GA03<br>5C380/GA05 |         |            |

| 审查员(译)         | 福村 拓                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 其他公开文献         | <a href="#">JP2008064806A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

## 摘要(译)

要解决的问题：根据其原因精确地检测EL显示装置的显示缺陷。

ŽSOLUTION：当用于控制提供给EL元件的驱动电流的元件驱动晶体管Tr2进行时，基于所获得的发光亮度或阴极电流，检测由EL元件短缺引起的缺失点缺陷。在其线性区域中操作并且EL元件保持在光发射水平。可以从元件驱动晶体管Tr2在其饱和区域中工作并且EL元件保持在发光电平时获得的阴极电流检测由元件驱动晶体管Tr2的特性变化引起的暗点缺陷。。当从发光亮度检测到异常显示像素时，从异常显示像素中发现未通过缺失检查确定为缺失缺陷像素的像素，并且该像素被检测为暗点缺陷由元件驱动晶体管Tr2的特性变化引起的像素。 Ž