(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3570394号

(P3570394)

(45) 発行日 平成16年9月29日(2004.9.29)

(24) 登録日 平成16年7月2日(2004.7.2)

(51) Int.Cl.<sup>7</sup>

F 1

|      |       |      |      |      |

|------|-------|------|------|------|

| GO9G | 3/30  | GO9G | 3/30 | K    |

| GO9F | 9/30  | GO9F | 9/30 | 338  |

| GO9G | 3/20  | GO9F | 9/30 | 365Z |

| H05B | 33/08 | GO9G | 3/20 | 611A |

| H05B | 33/14 | GO9G | 3/20 | 623B |

請求項の数 16 (全 15 頁) 最終頁に続く

(21) 出願番号

特願2001-156509 (P2001-156509)

(22) 出願日

平成13年5月25日(2001.5.25)

(65) 公開番号

特開2002-351402 (P2002-351402A)

(43) 公開日

平成14年12月6日(2002.12.6)

審査請求日

平成14年4月16日(2002.4.16)

(73) 特許権者 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100086298

弁理士 舟橋 國則

(72) 発明者 湯本 昭

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

審査官 橋本 直明

最終頁に続く

(54) 【発明の名称】アクティブマトリクス型表示装置およびアクティブマトリクス型有機エレクトロルミネッセンス表示装置、並びにそれらの駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

流れる電流によって輝度が変化する電気光学素子を有し、データ線を介して電流値として供給される輝度情報に基づいて前記電気光学素子を駆動する画素回路がマトリクス状に配置されてなる画素部と、

前記輝度情報の書き込みサイクル内で電流値の大きさが時間的に増加し、当該書き込みサイクルの終了時には所望の輝度情報に対応した電流値に到達する書き込み電流を前記画素回路の各々に対して前記データ線を介して供給する電流駆動回路とを備えたことを特徴とするアクティブマトリクス型表示装置。

## 【請求項 2】

前記電流駆動回路は、前記書き込みサイクルの初期では駆動電流を小さく制限し、前記書き込みサイクル内の途中から前記所望の輝度情報に対応した電流値の書き込み電流を流し始める

ことを特徴とする請求項1記載のアクティブマトリクス型表示装置。

## 【請求項 3】

前記電流駆動回路は、低輝度データの書き込み時には早いタイミングで、高輝度データの書き込み時には遅いタイミングで前記書き込み電流を流し始める

ことを特徴とする請求項2記載のアクティブマトリクス型表示装置。

## 【請求項 4】

前記電流駆動回路は、前記データ線に対して直列に接続された電流制限素子を有し、この 20

電流制限素子の制限電流値を前記書き込みサイクル内で時間的に増加させる

ことを特徴とする請求項1記載のアクティブマトリクス型表示装置。

【請求項5】

前記電流制限素子は電界効果トランジスタからなり、そのゲート電圧によって前記制限電流値が制御される

ことを特徴とする請求項4記載のアクティブマトリクス型表示装置。

【請求項6】

前記電流制限素子は並列に接続された複数個からなり、これら複数個の電流制限素子が前記書き込みサイクル内で時間をおいて順次導通状態になる

ことを特徴とする請求項4記載のアクティブマトリクス型表示装置。 10

【請求項7】

前記複数個の電流制限素子のうち、少なくとも一つの電流制限素子は残りの電流制限素子とは異なる電流駆動能力を持つ

ことを特徴とする請求項6記載のアクティブマトリクス型表示装置。

【請求項8】

流れる電流によって輝度が変化する電気光学素子を有し、データ線を介して電流値として供給される輝度情報に基づいて前記電気光学素子を駆動する画素回路がマトリクス状に配置されてなるアクティブマトリクス型表示装置において、

前記輝度情報の書き込みサイクル内で電流値の大きさが時間的に増加し、当該書き込みサイクルの終了時には所望の輝度情報に対応した電流値に到達する書き込み電流を前記画素回路の各々に対して前記データ線を介して供給する 20

ことを特徴とするアクティブマトリクス型表示装置の駆動方法。

【請求項9】

第1、第2の電極およびこれら電極間に発光層を含む有機層を有する有機エレクトロルミネッセンス素子を表示素子として用い、データ線を介して電流値として供給される輝度情報に基づいて前記有機エレクトロルミネッセンス素子を駆動する画素回路がマトリクス状に配置されてなる画素部と、

前記輝度情報の書き込みサイクル内で電流値の大きさが時間的に増加し、当該書き込みサイクルの終了時には所望の輝度情報に対応した電流値に到達する書き込み電流を前記画素回路の各々に対して前記データ線を介して供給する電流駆動回路と 30

を備えたことを特徴とするアクティブマトリクス型有機エレクトロルミネッセンス表示装置。

【請求項10】

前記電流駆動回路は、前記書き込みサイクルの初期では駆動電流を小さく制限し、前記書き込みサイクル内の途中から前記所望の輝度情報に対応した電流値の書き込み電流を流し始める

ことを特徴とする請求項9記載のアクティブマトリクス型有機エレクトロルミネッセンス表示装置。

【請求項11】

前記電流駆動回路は、低輝度データの書き込み時には早いタイミングで、高輝度データの書き込み時には遅いタイミングで前記書き込み電流を流し始める 40

ことを特徴とする請求項10記載のアクティブマトリクス型有機エレクトロルミネッセンス表示装置。

【請求項12】

前記電流駆動回路は、前記データ線に対して直列に接続された電流制限素子を有し、この電流制限素子の制限電流値を前記書き込みサイクル内で時間的に増加させる

ことを特徴とする請求項9記載のアクティブマトリクス型有機エレクトロルミネッセンス表示装置。

【請求項13】

前記電流制限素子は電界効果トランジスタからなり、そのゲート電圧によって前記制限電 50

流値が制御される

ことを特徴とする請求項 1 2 記載のアクティブマトリクス型有機エレクトロルミネッセンス表示装置。

【請求項 1 4】

前記電流制限素子は並列に接続された複数個からなり、これら複数個の電流制限素子が前記書き込みサイクル内で時間をおいて順次導通状態になる

ことを特徴とする請求項 1 2 記載のアクティブマトリクス型有機エレクトロルミネッセンス表示装置。

【請求項 1 5】

前記複数個の電流制限素子のうち、少なくとも一つの電流制限素子は残りの電流制限素子とは異なる電流駆動能力を持つ

10

ことを特徴とする請求項 1 4 記載のアクティブマトリクス型有機エレクトロルミネッセンス表示装置。

【請求項 1 6】

第 1、第 2 の電極およびこれら電極間に発光層を含む有機層を有する有機エレクトロルミネッセンス素子を表示素子として用い、データ線を介して電流値として供給される輝度情報に基づいて前記有機エレクトロルミネッセンス素子を駆動する画素回路がマトリクス状に配置されてなるアクティブマトリクス型有機エレクトロルミネッセンス表示装置において、

前記輝度情報の書き込みサイクル内で電流値の大きさが時間的に増加し、当該書き込みサイクルの終了時には所望の輝度情報に対応した電流値に到達する書き込み電流を前記画素回路の各々に対して前記データ線を介して供給する

20

ことを特徴とするアクティブマトリクス型有機エレクトロルミネッセンス表示装置の駆動方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、画素毎に能動素子を有して当該能動素子によって画素単位で表示制御が行われるアクティブマトリクス型表示装置およびその駆動方法に関し、特に流れる電流によって輝度が変化する電気光学素子を画素の表示素子として用いるアクティブマトリクス型表示装置および電気光学素子として有機材料のエレクトロルミネッセンス（以下、有機 E L（electroluminescence）と記す）素子を用いるアクティブマトリクス型有機 E L 表示装置およびそれらの駆動方法に関する。

30

【0002】

【従来の技術】

表示装置、例えば画素の表示素子として液晶セルを用いた液晶ディスプレイなどにおいては、多数の画素をマトリクス状に配列し、表示すべき画像情報に応じて画素毎に光強度を制御することによって画像の表示駆動が行われるようになっている。この表示駆動は、画素の表示素子として有機 E L 素子を用いた有機 E L ディスプレイなどでも同様である。

【0003】

ただし、有機 E L ディスプレイの場合は、画素の表示素子として発光素子を用いる、いわゆる自発光型のディスプレイであるため、液晶ディスプレイに比べて画像の視認性が高い、バックライトが不要、応答速度が速い等の利点を有する。また、各発光素子の輝度がそれに流れる電流値によって制御される、即ち有機 E L 素子が電流制御型であるという点で、液晶セルが電圧制御型である液晶ディスプレイなどとは大きく異なる。

40

【0004】

有機 E L ディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として単純（パッシブ）マトリクス方式とアクティブマトリクス方式とを探ることができる。ただし、前者は構造が単純であるものの、大型かつ高精細のディスプレイの実現が難しいなどの問題がある。このため、近年、画素内部の発光素子に流れる電流を、同様に画素内部に設け

50

た能動素子、例えば絶縁ゲート型電界効果トランジスタ（一般には、薄膜トランジスタ（Thin Film Transistor；TFT）によって制御する、アクティブマトリクス方式の開発が盛んに行われている。

#### 【0005】

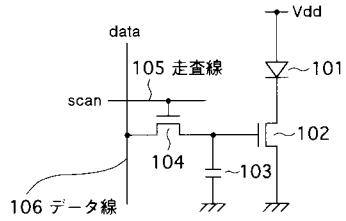

図10に、アクティブマトリクス型の有機ELディスプレイにおける画素回路（単位画素の回路）の従来例を示す（より詳細には、米国特許第5,684,365号公報、特開平8-234683号公報を参照）。

#### 【0006】

この従来例に係る画素回路は、図10から明らかなように、アノード（陽極）が正電源Vddに接続された有機EL素子101と、ドレインが有機EL素子101のカソード（陰極）に接続され、ソースがグランドに接続（以下、「接地」と記す）されたTFT102と、TFT102のゲートとグランドとの間に接続されたキャパシタ103と、ドレインがTFT102のゲートに、ソースがデータ線106に、ゲートが走査線105にそれぞれ接続されたTFT104とを有する構成となっている。

#### 【0007】

ここで、有機EL素子は多くの場合整流性があるため、OLED(Organic Light Emitting Diode)と呼ばれることがある。したがって、図10およびその他の図では、OLEDとしてダイオードの記号を用いて示している。ただし、以下の説明において、OLEDには必ずしも整流性を要求するものではない。

#### 【0008】

上記構成の画素回路の動作は次の通りである。先ず、走査線105の電位を選択状態（ここでは、高レベル）とし、データ線106に書き込み電位Vwを印加すると、TFT104が導通してキャパシタ103が充電または放電され、TFT102のゲート電位は書き込み電位Vwとなる。次に、走査線105の電位を非選択状態（ここでは、低レベル）とすると、走査線105とTFT102とは電気的に切り離されるが、TFT102のゲート電位はキャパシタ103によって安定に保持される。

#### 【0009】

そして、TFT102およびOLED101に流れる電流は、TFT102のゲート・ソース間電圧Vgsに応じた値となり、OLED101はその電流値に応じた輝度で発光し続ける。ここで、走査線105を選択してデータ線106に与えられた輝度情報を画素内部に伝える動作を、以下、「書き込み」と呼ぶこととする。上述のように、図10に示す画素回路では、一度電位Vwの書き込みを行えば、次に書き込みが行われるまでの間、OLED101は一定の輝度で発光を継続する。

#### 【0010】

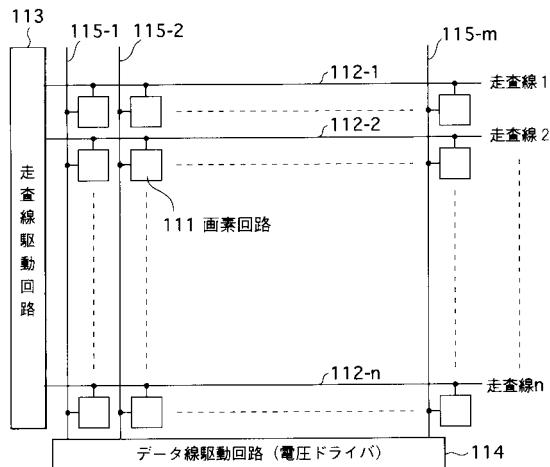

このような画素回路（以下、単に画素と記す場合もある）111を図11に示すようにマトリクス状に多数並べ、走査線112-1～112-nを走査線駆動回路113によって順次選択しながら、電圧駆動型のデータ線駆動回路（電圧ドライバ）114からデータ線115-1～115-mを通して書き込みを繰り返すことにより、アクティブマトリクス型表示装置（有機ELディスプレイ）を構成することができる。ここでは、m列n行の画素配列を示している。この場合、当然のことながら、データ線がm本、走査線がn本となる。

#### 【0011】

単純マトリクス型表示装置では、各発光素子は、選択された瞬間にのみ発光するのに対し、アクティブマトリクス型表示装置では、書き込み終了後も発光素子が発光を継続する。このため、アクティブマトリクス型表示装置は、単純マトリクス型表示装置に比べて発光素子のピーク輝度、ピーク電流を下げられるなどの点で、とりわけ大型・高精細のディスプレイでは有利となる。

#### 【0012】

ところで、アクティブマトリクス型有機ELディスプレイにおいては、能動素子として一般的に、ガラス基板上に形成されたTFT（薄膜電界効果トランジスタ）が利用される。

10

20

30

40

50

ところが、このTFTの形成に使用されるアモルファスシリコン（非晶質シリコン）やポリシリコン（多結晶シリコン）は、単結晶シリコンに比べて結晶性が悪く、導電機構の制御性が悪いために、形成されたTFTは特性のばらつきが大きいことが良く知られている。

#### 【0013】

特に、比較的大型のガラス基板上にポリシリコンTFTを形成する場合には、ガラス基板の熱変形等の問題を避けるため、通常、アモルファスシリコン膜の形成後、レーザアニール法によって結晶化が行われる。しかしながら、大きなガラス基板に均一にレーザエネルギーを照射することは難しく、ポリシリコンの結晶化の状態が基板内の場所によってばらつきを生ずることが避けられない。この結果、同一基板上に形成したTFTでも、そのしきい値 $V_{th}$ が画素によって数百mV、場合によっては1V以上ばらつくこともまれではない。10

#### 【0014】

この場合、例えば異なる画素に対して同じ電位 $V_w$ を書き込んでも、画素によってTFTのしきい値 $V_{th}$ がばらつくことになる。これにより、OLED（有機EL素子）に流れる電流 $I_{ds}$ は画素毎に大きくばらついて全く所望の値からはずれる結果となり、ディスプレイとして高い画質を期待することはできない。このことは、しきい値 $V_{th}$ のみではなく、キャリアの移動度 $\mu$ などのばらつきについても同様のことと言える。

#### 【0015】

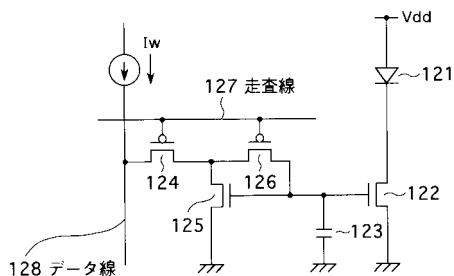

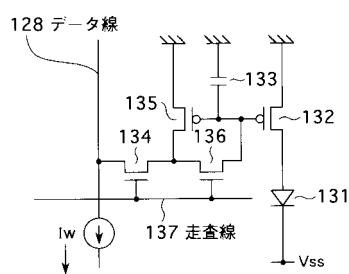

かかる問題を改善するため、本願発明者は、一例として、図12に示す電流書き込み型の画素回路を提案している（国際公開番号WO01/06484の公報参照）。20

#### 【0016】

この電流書き込み型画素回路は、図12から明らかなように、アノードが正電源 $V_{dd}$ に接続されたOLED121と、ドレンがOLED121のカソードに接続され、ソースがグランドに接地されたNチャネルTFT122と、このTFT122のゲートとグランドとの間に接続されたキャパシタ123と、ドレンがデータ線128に、ゲートが走査線127にそれぞれ接続されたPチャネルTFT124と、ドレンがTFT124のソースに接続され、ソースが接地されたNチャネルTFT125と、ドレンがTFT125のドレンに、ソースがTFT122のゲートに、ゲートが走査線127にそれぞれ接続されたPチャネルTFT126とを有する構成となっている。30

#### 【0017】

上記構成の画素回路が図10に示す画素回路と決定的に異なる点は、次の通りである。すなわち、図10に示す画素回路においては輝度データが電圧の形で画素に与えられるのに対し、図12に示す画素回路においては輝度データが電流の形で画素に与えられる点にある。

#### 【0018】

先ず、輝度情報を書き込む際には、走査線127を選択状態（ここでは、低レベル）にし、データ線128に輝度情報に応じた電流 $I_w$ を流す。この電流 $I_w$ は、TFT124を通してTFT125に流れる。このとき、TFT125に生ずるゲート・ソース間電圧を $V_{gs}$ とする。TFT125のゲート・ドレン間は短絡されているので、TFT125は飽和領域で動作する。40

#### 【0019】

よって、良く知られたMOSトランジスタの式にしたがって

$$I_w = \mu_1 C_o x_1 W_1 / L_1 / 2 (V_{gs} - V_{th})^2 \quad \dots \dots (1)$$

が成立する。（1）式において、 $V_{th}$ はTFT125のしきい値、 $\mu_1$ はキャリアの移動度、 $C_o x_1$ は単位面積当たりのゲート容量、 $W_1$ はチャネル幅、 $L_1$ はチャネル長である。

#### 【0020】

次に、OLED121に流れる電流を $I_{drv}$ とすると、この電流 $I_{drv}$ はOLED121と直列に接続されたTFT122によって電流値が制御される。図12に示す画素回

10

20

30

40

50

路では、TFT122のゲート・ソース間電圧が(1)式の $V_{gs}$ に一致するので、TFT122が飽和領域で動作すると仮定すれば、

$$I_{drv} = \mu_2 C_o x_2 W_2 / L_2 / 2 (V_{gs} - V_{th2})^2 \dots (2)$$

となる。

#### 【0021】

ちなみに、MOSトランジスタが飽和領域で動作する条件は、一般に、

$$|V_{ds}| > |V_{gs} - V_t| \dots (3)$$

であることが知られている。(2)式、(3)式の各パラメータの意味は(1)式と同様である。ここで、TFT125とTFT122とは、小さな画素内部に近接して形成されるため、事実上、 $\mu_1 = \mu_2$ 、 $C_o x_1 = C_o x_2$ 、 $V_{th1} = V_{th2}$ と考えられる。

すると、(1)式と(2)式とから容易に

$$I_{drv} / I_w = (W_2 / W_1) / (L_2 / L_1) \dots (4)$$

が導かれる。

#### 【0022】

すなわち、キャリアの移動度 $\mu$ 、単位面積当たりのゲート容量 $C_o x$ 、しきい値 $V_{th}$ の値自体がパネル面内で、あるいはパネル毎にばらついたとしても、OLED121に流れる電流 $I_{drv}$ は正確に書き込み電流 $I_w$ に比例するので、結果として、OLED121の発光輝度を正確に制御できる。例えば、特に $W_2 = W_1$ 、 $L_2 = L_1$ と設計すれば、 $I_{drv} / I_w = 1$ 、即ちTFT特性のばらつきによらず、書き込み電流 $I_w$ とOLED121に流れる電流 $I_{drv}$ とは同一の値となる。

20

#### 【0023】

図13は、電流書き込み型画素回路の他の回路例を示す回路図である。本回路例に係る画素回路は、図12に示す回路例の画素回路とはトランジスタの導電型(Nチャネル/Pチャネル)の関係が逆になっている。すなわち、図12のNチャネルTFT122, 125がPチャネルTFT132, 135に、図12のPチャネルTFT124, 126がNチャネルTFT134, 136にそれぞれ置換されている。また、電流の流れる向き等も異なっているが、動作原理は全く同じである。

#### 【0024】

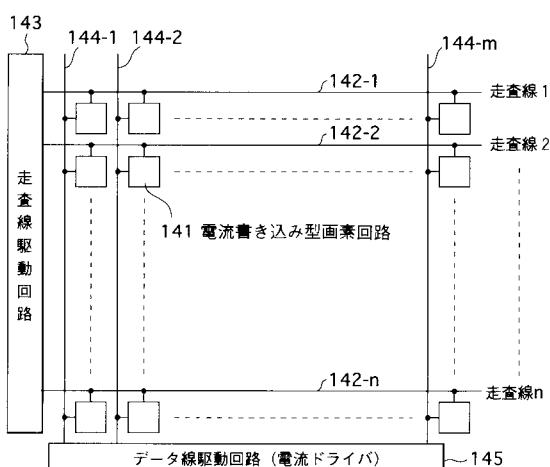

上述した図12および図13に示すような電流書き込み型画素回路をマトリクス状に並べることにより、アクティブマトリクス型有機EL表示装置を構成することが可能である。

30 図14にその構成例を示す。

#### 【0025】

図14において、マトリクス状にm列n行分だけ配置された電流書き込み型の画素回路141の各々に対して、各行毎に走査線142-1~142-nが配線されている。そして、走査線142-1~142-nに対して図12のTFT124のゲート(または、図13のTFT134のゲート)が、さらに図12のTFT126のゲート(または、図10のTFT136のゲート)がそれぞれ画素毎に接続される。走査線142-1~142-nは、走査線駆動回路143によって順に駆動される。

#### 【0026】

また、画素回路141の各々に対して、各列毎にデータ線144-1~144-mが配線されている。これらデータ線144-1~144-mの各一端は、電流駆動型のデータ線駆動回路(電流ドライバCS)145の各列の出力端に接続されている。そして、このデータ線駆動回路145によってデータ線144-1~144-mを通して各画素に対して輝度情報の書き込みが行われる。

40

#### 【0027】

##### 【発明が解決しようとする課題】

このように、画素回路として、図12または図13に示すような、輝度データが電流値の形で与えられる回路、即ち電流書き込み型画素回路を採用した場合、輝度データを書き込む際の消費電力が大きくなりがちである。その理由は次の通りである。すなわち、図10に示した電圧書き込み型画素回路およびこれを用いたアクティブマトリクス型表示装置で

は、データ線の駆動に際して直流電流を消費することはないのに対して、電流書き込み型画素回路およびこれを用いたアクティブマトリクス型表示装置では、データ線の駆動に際して直流電流を消費することに起因する。

#### 【0028】

例えば、現実的な数値として、書き込み電流の最大値をデータ線1本当たり $100\mu A$ 、電源電圧を $15V$ 、データ線の本数をフルカラーのXGA (extended graphics array) パネルを想定して、 $1024 \times 3$  (RGB) = 3072本とすると、書き込みに要する消費電力は、 $100\mu A \times 3072 \times 15V = 4.6W$ にもなる。詳細には、垂直プランギング期間は書き込み電流が流れないとこれよりは小さいが、大きく変わることはない。

10

#### 【0029】

消費電力を減らすには、単純には書き込み電流値を小さくすれば良いが、その場合、必要な書き込み時間が増大するという問題が生ずる。すなわち、電流書き込み方式において、電流源である電流駆動回路の出力インピーダンスはほぼ無限大なので、回路のインピーダンスは画素回路内部のトランジスタ、より具体的には、図12の画素回路の例ではTFT 125によって決まる。

#### 【0030】

詳しくは、前述したMOSトランジスタの(1)式の両辺をゲート・ソース間電圧 $V_{gs}$ で微分すると、

$$1/R_{pix} = \mu_1 C_o \times 1W1 / L1 (V_{gs} - V_{th1}) \dots (5)$$

20

となる。ここで、 $R_{pix}$ は、データ線128から見たTFT 125の微分抵抗である。

(1)式と(5)式より、

$$R_{pix} = 1 / (2\mu_1 C_o \times 1W1 / L1 \cdot I_w) \dots (6)$$

が得られる。

#### 【0031】

(6)式から明らかなように、微分抵抗 $R_{pix}$ は書き込み電流 $I_w$ の平方根に反比例する。一方、データ線128には一般に大きな寄生容量 $C_{data}$ が存在するので、書き込み回路の時定数 $\tau$ は、定常状態付近では概ね

$$\tau = C_{data} \times R_{pix} \dots (7)$$

となる。

30

#### 【0032】

電流書き込み方式においては、データ線電位を定常状態に安定させるために、上記時定数 $\tau$ に対して十分長い書き込み時間をとることが望ましい。ところが、(6)式、(7)式から明らかなように、時定数 $\tau$ は書き込み電流が小さくなると長くなり、特に黒データの書き込みでは $I_w = 0$ であるため、理論的に有限の時間内には書き込みが終了しない。実際は多少の誤差は許容できるなどのため、有限の書き込み時間でも実用的な書き込み動作を行うことは可能であるが、小さな電流の書き込み時には、大きな電流の書き込み時よりも本質的に長い書き込み時間が必要である。

#### 【0033】

これは、とりわけ電流値が小さくなる低輝度データの書き込みや、ディスプレイが大型化してデータ線128の寄生容量 $C_{data}$ が増大した場合、あるいは許容される書き込み時間(走査周期)が短くなる高精細ディスプレイにおいては深刻な問題である。すなわち、所定の時間内に書き込み動作を完了させるためには書き込み電流を大きくせざるを得ないが、そうすると消費電力の増大を招くからである。

40

#### 【0034】

本発明は、上記課題に鑑みて為されたものであり、その目的とするところは、電流書き込み型画素回路を用いた場合において、十分な書き込み性能を保ちながら輝度データの書き込みに要する消費電力を低減し、低消費電力化を可能としたアクティブマトリクス型表示装置およびアクティブマトリクス型有機EL表示装置、並びにそれらの駆動方法を提供することにある。

50

**【0035】****【課題を解決するための手段】**

上記目的を達成するために、本発明では、流れる電流によって輝度が変化する電気光学素子を有し、データ線を介して電流値として供給される輝度情報に基づいて電気光学素子を駆動する画素回路がマトリクス状に配置されてなるアクティブマトリクス型表示装置において、前記輝度情報の書き込みサイクル内で電流値の大きさが時間的に増加し、当該書き込みサイクルの終了時には所望の輝度情報に対応した電流値に到達する書き込み電流を前記画素回路の各々に対して前記データ線を介して供給する構成を探っている。

**【0036】**

上記構成のアクティブマトリクス型表示装置または電気光学素子として有機EL素子を用いたアクティブマトリクス型有機EL表示装置において、書き込み電流の電流値の大きさが書き込みサイクル内で時間的に増加することで、書き込みサイクルの初期には書き込み電流が小さく（もしくはゼロに）制限される。したがって、書き込み電流の平均値が小さくなる。

**【0037】****【発明の実施の形態】**

以下、本発明の実施の形態について図面を参照して詳細に説明する。

**【0038】**

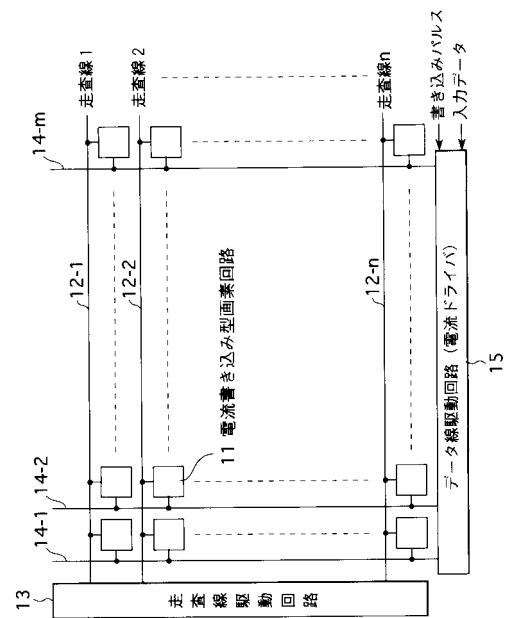

図1は、本発明の一実施形態に係るアクティブマトリクス型表示装置の概略構成図である。ここでは、各画素の電気光学素子として有機EL素子を、能動素子として電界効果トランジスタ、例えばポリシリコン TFT をそれぞれ用い、ポリシリコン TFT を形成した基板上に有機EL素子を形成してなるアクティブマトリクス型有機EL表示装置に適用した場合を例に探って説明するものとする。

**【0039】**

図1において、電流書き込み型画素回路11がマトリクス状にm列n行分だけ配置されている。電流書き込み型画素回路11としては、例えば、図12に示した回路構成のもの、あるいは図13に示した回路構成のものが用いられる。これら画素回路11の各々に対して、各行毎に走査線12-1~12-nが配線されている。走査線12-1~12-nは、走査線駆動回路13によって順に駆動される。

**【0040】**

また、画素回路11の各々に対して、各列毎にデータ線14-1~14-mが配線されている。これらデータ線14-1~14-mの各一端は、電流駆動型のデータ線駆動回路（電流駆動回路、以下「電流ドライバ」と記す）15の各列の出力端に接続されている。データ線駆動回路15には、入力データが電圧の形で与えられるとともに、書き込み電流を制御するための書き込みパルスが入力される。このデータ線駆動回路15は、データ線14-1~14-mを通して画素回路11の各々に対して輝度データを書き込む。

**【0041】**

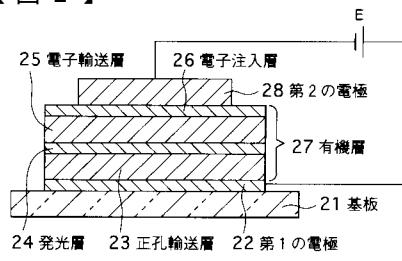

ここで、有機EL素子の構造の一例について説明する。図2に、有機EL素子の断面構造を示す。同図から明らかのように、有機EL素子は、透明ガラスなどからなる基板21上に、透明導電膜からなる第1の電極（例えば、陽極）22を形成し、その上にさらに正孔輸送層23、発光層24、電子輸送層25および電子注入層26を順次堆積させて有機層27を形成した後、この有機層27の上に金属からなる第2の電極（例えば、陰極）28を形成した構成となっている。そして、第1の電極22と第2の電極28との間に直流電圧Eを印加することで、発光層24において電子と正孔が再結合する際に発光するようになっている。

**【0042】**

また、上記構成のアクティブマトリクス型表示装置では、電流書き込み型画素回路11が電界効果トランジスタ（本例では、ポリシリコン TFT）を用いて構成されていることから、データ線駆動回路15を画素部と同一の基板上に搭載する構成を探る場合には、データ線駆動回路15についても電界効果トランジスタを用いて構成するのが好ましい。ただ

10

20

30

40

50

し、データ線駆動回路 15 としては、画素部の外付け回路とした構成を採ることも可能である。この場合には、バイポーラトランジスタを用いてデータ線駆動回路 15 を構成することも可能である。

#### 【0043】

以下、データ線駆動回路 15 の具体的な構成例について、いくつか例を挙げて説明する。

#### 【0044】

##### [第1具体例]

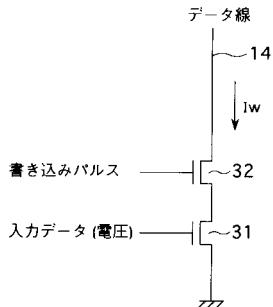

図3は、データ線駆動回路 15 の第1具体例を示す回路図である。この第1具体例に係る回路は、ある1本のデータ線に対応する単位回路であり、この単位回路のn列分の集合がデータ線駆動回路となる。

10

#### 【0045】

図3において、画素に書き込まれるべき輝度データ（入力データ）は、ソースが接地された例えばNチャネルのTFT31のゲートに電圧の形で与えられる。このTFT31は、輝度データ電圧を電流に変換してデータ線14に流す作用をなす。本例では、輝度データ電圧が高い場合が大電流、即ち高輝度の書き込み電流に対応することになる。

#### 【0046】

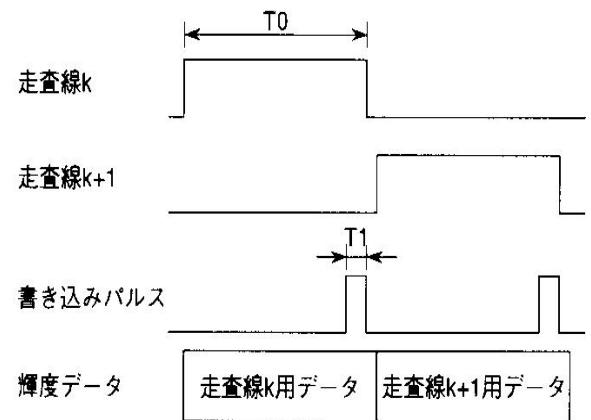

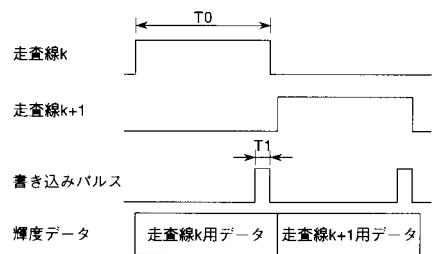

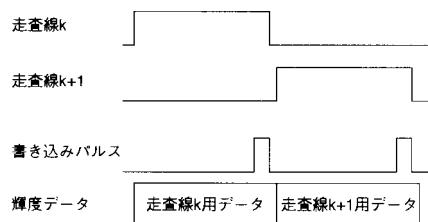

このTFT31のドレインとデータ線14の一端との間には、例えばNチャネルのTFT32が書き込みスイッチとして挿入されている。TFT32のゲートには書き込みパルスが与えられる。この書き込みパルスは、図4のタイミングチャートに示すように、輝度データの書き込みサイクル、即ち走査サイクルの終了付近においてのみ高レベルとなるパルスであり、各列毎に配されるTFT32の各ゲートに対して共通に与えられる。

20

#### 【0047】

この書き込みパルスがTFT32のゲートに印加されることにより、走査サイクルの終了付近の短い期間においてのみTFT32がオン状態となり、この期間に画素への輝度データの書き込みが行われる。逆に、走査サイクルの大部分では書き込みパルスが低レベルにあるため、輝度データの書き込みは行われず、データ線14には書き込み電流が流れない。すなわち、TFT32はデータ線14に流れる書き込み電流を制限する電流制限素子として機能する。

#### 【0048】

このように、第1具体例に係る回路構成においては、走査サイクルの終了付近の短い期間においてのみ輝度データの書き込みを行うようにすることで、1走査周期内の書き込みパルスが高レベルである時間をT1、1走査周期時間をT0とすると、書き込み電流による直流消費電力は、1走査周期時間T0を通して書き込みを行っていた従来例に比べて概ね、T1/T0に低減されることは明らかである。

30

#### 【0049】

ところで、低消費電力化のために書き込み時間を短縮すると、「発明が解決する課題」の項で述べた通り、低輝度データの書き込みに支障を来す懸念がある。したがって、書き込み時間の短縮には限界があり、結果的に、消費電力の低減効果にも限界が生じる。この対策として為されたのが、以下に説明する第2具体例である。

#### 【0050】

40

##### [第2具体例]

図5は、データ線駆動回路15の第2具体例を示す回路図であり、図中、図3と同等部分は同一符号を付して示している。この第2具体例では、書き込み時間を低輝度時には長く、高輝度時には短くなるように制御する構成を探っている。この第2具体例に係る回路も、ある1本のデータ線に対応する単位回路であり、この単位回路のn列分の集合がデータ線駆動回路となる。

#### 【0051】

図5において、正電源Vddとグランドとの間に、PチャネルTFT41およびNチャネルTFT42が直列に接続されている。TFT41のゲートには、TFT31のゲートと同様に入力データが電圧の形で印加される。TFT42のゲートには、正のリセットパル

50

スが印加される。TFT41, 42の各ドレインが共通に接続されたノードNとグランドとの間にはキャパシタ43が接続されている。

#### 【0052】

ノードNの電圧は、比較器44の比較入力端子inに与えられる。比較器44の参照電圧入力端子refには参照電圧Vrefが印加される。比較器44は、入力端子inの比較入力電圧と参照電圧Vrefとを比較し、比較入力電圧が参照電圧Vrefよりも大きい場合に限り、出力端子outから高レベルの信号を出力する。比較器44の出力信号は、書き込みスイッチであるTFT32のゲートに与えられる。

#### 【0053】

次に、上記構成の第2具体例の回路動作について説明する。先ず、輝度データの書き込み動作に先立ち、TFT42のゲートに正のリセットパルスが与えられる。すると、ノードNの電位が低レベルにリセットされる。このリセット状態で入力データ電圧が与えられると、TFT41が導通状態となってキャパシタ43を充電する。これにより、ノードNの電位が徐々に上昇する。

10

#### 【0054】

そして、ノードNの電位が参照電圧Vrefを超えると、比較器44の出力端子outの電位が高レベルとなり、書き込みスイッチであるTFT32を導通させる。このとき、入力データ電圧が高いほどTFT41に流れる電流が小さいため、キャパシタ43の充電に時間がかかり、ノードNの電位が参照電圧Vrefを超えるまでに時間を要する。したがって、高輝度データに対しては、TFT32が導通するまでに時間がかかるため、書き込み時間は短くなる。全体的な書き込み時間については、参照電圧Vrefの電圧値によって調整可能である。

20

#### 【0055】

このように、第2具体例に係る回路構成によれば、低輝度時に長い書き込み時間を確保しつつ、高輝度時の書き込み時間を短縮することができ、結果として、輝度データの書き込みに要する消費電力を減少させることができる。

#### 【0056】

##### [第3具体例]

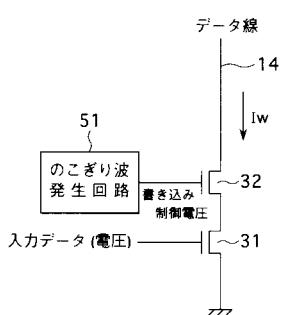

図6は、データ線駆動回路15の第3具体例を示す回路図であり、図中、図3と同等部分には同一符号を付して示している。この第3具体例に係る回路も、ある1本のデータ線に対応する単位回路であり、この単位回路のn列分の集合がデータ線駆動回路となる。

30

#### 【0057】

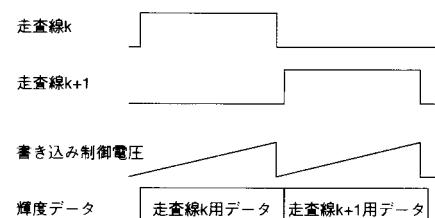

図6から明らかなように、本具体例に係る回路では、輝度データの書き込みサイクル内において時間的に徐々に増加する信号、例えばのこぎり波信号（図7のタイミングチャートを参照）を発生するのこぎり波信号発生回路51が設けられている。のこぎり波信号発生回路51で発生されたのこぎり波信号は、書き込みスイッチ（アナログスイッチ）であるTFT32のゲートに書き込み電圧として与えられる。

#### 【0058】

次に、上記構成の第3具体例の回路動作について、図7のタイミングチャートに基づいて説明する。

40

#### 【0059】

書き込み開始時付近において、TFT32はそのゲート電位が低いため大きな電流を流すことができない。すなわち、たとえTFT31の入力電圧が高い場合（高輝度データ時）でも、TFT32のインピーダンスが高いためそこでの電圧降下が大きい。これにより、TFT31のドレン電位が低下するため、TFT31は飽和領域では動作できず、小さな駆動電流しか流すことができない。すなわち、書き込み電流IwはTFT32によって制限される。

#### 【0060】

一方、TFT31の入力データ電圧が低い場合（低輝度データ時）は、TFT31およびTFT32に流れる電流は小さく、したがってTFT32での電圧降下も小さい。結果と

50

して、TFT31はそのゲート電圧が低く、ドレイン電圧も比較的高いため飽和領域で動作、言い換れば定電流源として動作しやすい。その場合は、書き込み動作に対して TFT32の存在は何らの制限をも与えないため、正常に書き込み動作が行われる訳である。書き込み終了時付近では TFT32のゲート電位が高く、そのインピーダンスが小さいため、高輝度データに対しても正常に書き込み動作が行われる。

#### 【0061】

結果として、本具体例に係る回路においては、書き込み時間が低輝度データに対しては長く、高輝度データに対しては実質的に短いことになる。したがって、正常な書き込み動作を実現しつつ書き込みに伴う消費電流を低く抑えることができる。また、その効果は第2具体例に係る回路の場合と同等であるが、これに加えて第2具体例に係る回路ではデータ線14毎に設ける必要がある比較器44およびその周辺回路が不要となるため、その分だけ回路構成を簡略化できるというメリットがある。

#### 【0062】

なお、本具体例では、書き込みスイッチである TFT32のゲート電位を直線的に変化させる構成を探っているが、このような連続的な制御を正確に行なうことが難しい場合は、ステップ的に制御を行う構成を探ることも可能である。要は、輝度データの書き込みサイクル内において、TFT32のゲート電位を時間的に徐々に増加できる構成であれば良い。

#### 【0063】

##### [第4具体例]

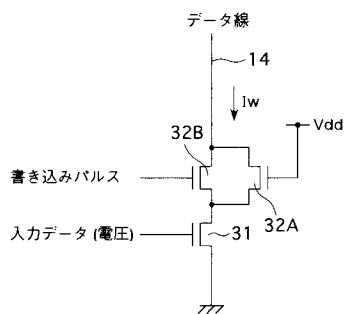

図8は、データ線駆動回路15の第4具体例を示す回路図であり、図中、図3と同等部分には同一符号を付して示している。この第4具体例に係る回路も、ある1本のデータ線に對応する単位回路であり、この単位回路のn列分の集合がデータ線駆動回路となる。

#### 【0064】

本具体例に係る回路では、書き込みスイッチとして、電流駆動能力が互いに異なる複数のTFT、ここでは電流駆動能力の小さな TFT32Aと、電流駆動能力が大きな TFT32Bとが並列に接続されている。そして、TFT32Aのゲートには、正の電源電圧Vd dが印加されている。また、TFT32Bのゲートには、走査サイクルの書き込み時間終了付近においてのみ高レベルとなる書き込みパルスが印加される。

#### 【0065】

電流駆動能力は、トランジスタのチャネル幅およびチャネル長の設定によって決めることができる。TFT31、TFT32AおよびTFT32Bとの間の電流駆動能力の大小関係については、一例として、TFT32Bの電流駆動能力がTFT31のそれと同等もしくはそれよりも大きく、そしてこのTFT32Bの電流駆動能力よりもTFT32Aのそれが小さくなるように設定される。

#### 【0066】

次に、上記構成の第4具体例の回路動作について、図9のタイミングチャートに基づいて説明する。

#### 【0067】

電流駆動能力の小さな TFT32Aはそのゲートが電源電圧Vd dによってバイアスされているため常に導通状態にあり、電流駆動能力が大きな TFT32Bはそのゲートに書き込みパルスが印加されることで、書き込み時間終了時付近のみに導通状態になる。TFT32Bが非導通である間は TFT32Aによって書き込み電流Iwが制限されるため消費電力が低減される一方、低輝度データ（小電流）は TFT32Aを通して正常に駆動される。

#### 【0068】

結果として、本具体例に係る回路においては、書き込み時間が低輝度データに対しては長く、高輝度データに対しては実質的に短いことになる。したがって、正常な書き込み動作を実現しつつ書き込みに伴う消費電流を低く抑えることができる。

#### 【0069】

なお、本具体例では、書き込みスイッチとして、電流駆動能力の小さな TFT32Aと電

10

20

30

40

50

流駆動能力が大きな T F T 3 2 B との 2 個を並列に接続し、書き込み電流  $I_w$  の制御を 2 段階で行う場合を例に採って説明したが、2 段階に限られるものではなく、電流駆動能力が異なるトランジスタを 3 個以上並列に接続して、さらに細かい段階的な電流制御を行うことも可能である。また、並列に接続する複数個のトランジスタの電流駆動能力は必ずしも互いに異なった値とする必要はなく、制御すべき電流領域の範囲に応じて、同程度の電流駆動能力を持つトランジスタを含む組み合わせとすることも可能である。

#### 【0070】

また、上記実施形態においては、画素の表示素子として有機 E L 素子を、能動素子としてポリシリコン薄膜トランジスタをそれぞれ用い、ポリシリコン薄膜トランジスタを形成した基板上有機 E L 素子を形成してなるアクティブマトリクス型有機 E L 表示装置に適用する場合を例に採って説明したが、本発明はこれに限られるものではなく、輝度情報が電流の形で与えられる電流書き込み型の画素回路を用いるアクティブマトリクス型表示装置全般に適用可能である。10

#### 【0071】

##### 【発明の効果】

以上説明したように、本発明によれば、書き込みサイクルの初期には書き込み電流が小さく（もしくはゼロに）制限されるため、書き込み電流の平均値が小さくなり、低消費電力化が図れる。

##### 【図面の簡単な説明】

【図 1】本発明の一実施形態に係るアクティブマトリクス型表示装置の概略構成図である20

。

【図 2】有機 E L 素子の構成の一例を示す断面構造図である。

【図 3】データ線駆動回路の第 1 具体例を示す回路図である。

【図 4】第 1 具体例に係るタイミングチャートである。

【図 5】データ線駆動回路の第 2 具体例を示す回路図である。

【図 6】データ線駆動回路の第 3 具体例を示す回路図である。

【図 7】第 3 具体例に係るタイミングチャートである。

【図 8】データ線駆動回路の第 4 具体例を示す回路図である。

【図 9】第 4 具体例に係るタイミングチャートである。

【図 10】従来例に係る電圧書き込み型画素回路の回路構成を示す回路図である。30

【図 11】従来例に係る電圧書き込み型画素回路を用いたアクティブマトリクス型表示装置の構成例を示すブロック図である。

【図 12】従来例 1 に係る電流書き込み型画素回路の回路構成を示す回路図である。

【図 13】従来例 2 に係る電流書き込み型画素回路の回路構成を示す回路図である。

【図 14】従来例に係る電流書き込み型画素回路を用いたアクティブマトリクス型表示装置の構成例を示すブロック図である。

##### 【符号の説明】

1 1 ... 有機 E L 素子、1 2 - 1 ~ 1 2 - n ... 走査線、1 3 ... 走査線駆動回路、1 4 , 1 4 - 1 ~ 1 4 - m ... データ線、1 5 ... データ線駆動回路、2 3 ... 正孔輸送層、2 4 ... 発光層

、2 5 ... 電子輸送層、2 7 ... 有機層40

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 14】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 4 B |

| G 0 9 G | 3/20  | 6 4 1 D |

| H 0 5 B | 33/08 |         |

| H 0 5 B | 33/14 | A       |

(56)参考文献 特開平11-219146 (JP, A)

国際公開第01/27910 (WO, A1)

国際公開第01/06484 (WO, A1)

特開平11-282419 (JP, A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

|      |       |     |

|------|-------|-----|

| G09G | 3/30  |     |

| G09F | 9/30  | 338 |

| G09F | 9/30  | 365 |

| G09G | 3/20  | 611 |

| G09G | 3/20  | 623 |

| G09G | 3/20  | 624 |

| G09G | 3/20  | 641 |

| H05B | 33/08 |     |

| H05B | 33/14 |     |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵型显示装置，有源矩阵型有机电致发光显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP3570394B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2004-09-29 |

| 申请号            | JP20011156509                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2001-05-25 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人         | 湯本昭                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 湯本 昭                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | H05B33/08 G09F9/30 G09G3/20 G09G3/30 G09G3/32 H01L27/32 H01L51/50 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| CPC分类号         | G09G3/2011 G09G3/3241 G09G3/325 G09G3/3283 G09G2310/066 G09G2330/021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| FI分类号          | G09G3/30.K G09F9/30.338 G09F9/30.365.Z G09G3/20.611.A G09G3/20.623.B G09G3/20.624.B<br>G09G3/20.641.D H05B33/08 H05B33/14.A G09F9/30.365 G09G3/3241 G09G3/3266 G09G3/3275<br>G09G3/3283 G09G3/3291 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| F-TERM分类号      | 3K007/AB02 3K007/AB04 3K007/AB05 3K007/AB18 3K007/BA06 3K007/CA01 3K007/CB01 3K007/<br>/DA00 3K007/DB03 3K007/EB00 3K007/FA01 3K107/AA01 3K107/BB01 3K107/CC14 3K107/EE03<br>3K107/HH02 3K107/HH04 5C080/AA06 5C080/BB05 5C080/DD26 5C080/EE29 5C080/FF11 5C080<br>/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C094/AA22 5C094/BA03 5C094/BA27 5C094/CA19<br>5C094/EA04 5C094/EA07 5C380/AA01 5C380/AB06 5C380/AB18 5C380/AB22 5C380/AB24 5C380<br>/AC04 5C380/BA01 5C380/BA05 5C380/BA12 5C380/BA13 5C380/BA19 5C380/BA31 5C380/BA38<br>5C380/BA39 5C380/BA46 5C380/BB01 5C380/BC20 5C380/CA02 5C380/CA08 5C380/CA12 5C380<br>/CA13 5C380/CA53 5C380/CA54 5C380/CB01 5C380/CC02 5C380/CC14 5C380/CC16 5C380/CC19<br>5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC52 5C380/CC62 5C380/CD012 5C380/CD014<br>5C380/CE04 5C380/CF51 5C380/CF61 5C380/DA02 5C380/DA06 5C380/DA30 5C380/DA47 5C380<br>/FA09 5C380/HA13 |         |            |

| 代理人(译)         | 船桥 国则                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 审查员(译)         | Naoaki桥本                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 其他公开文献         | JP2002351402A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

## 摘要(译)

要解决的问题：为了解决这样的问题，即当在显示装置中采用电流写入型像素电路时，由于电路在驱动数据线时消耗DC电流，所以当时电路的功耗写入亮度数据容易变大。解决方案：在有源矩阵型显示装置中，其中电流写入型像素电路11具有电光元件，该电光元件的亮度由流过元件的电流改变并基于要提供的亮度信息驱动电光元件当电流通过数据线14-1至14-m以矩阵形状排列时，使电流写入型像素驱动电路15向像素电路11的各个电路提供电流大小随时间增加的写入电流。在亮度信息的写入周期中通过数据线14-1到14-m。

【図4】