(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-59531

(P2009-59531A)

(43) 公開日 平成21年3月19日(2009.3.19)

(51) Int.Cl.

H05B 33/04

H01L 51/50(2006.01)

(2006.01)

F 1

H05B 33/04

H05B 33/14

テーマコード(参考)

3K107

A

審査請求 未請求 請求項の数 3 O L (全 13 頁)

(21) 出願番号

特願2007-224491 (P2007-224491)

(22) 出願日

平成19年8月30日 (2007.8.30)

(71) 出願人 302020207

東芝松下ディスプレイテクノロジー株式会社

東京都港区港南4-1-8

100058479

弁理士 鈴江 武彦

100091351

弁理士 河野 哲

100088683

弁理士 中村 誠

100108855

弁理士 蔵田 昌俊

100075672

弁理士 峰 隆司

最終頁に続く

(54) 【発明の名称】有機EL表示装置

## (57) 【要約】

【課題】アクティブマトリクス駆動方式を採用した上面発光型の有機EL表示装置において狭額縫化と共通電極電位の面内均一性向上とを達成可能とする。

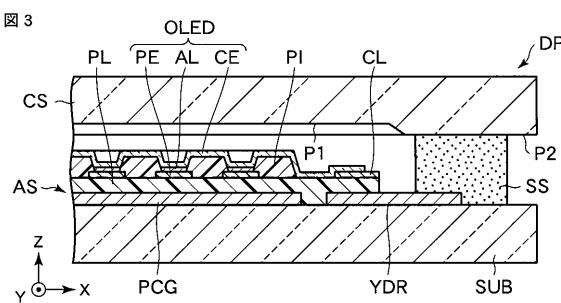

【解決手段】アレイ基板ASは、一方の主面に表示領域と周辺領域とが規定される絶縁基板SUBと、表示領域と周辺領域のうち表示領域に隣接した部分とを被覆した有機平坦化層PLと、周辺領域上に形成されると共に少なくとも一部が平坦化層PLによって被覆された走査信号線ドライバYDRと、平坦化層PL上であって表示領域に対応した位置で配列した画素電極PEと、平坦化層PLを間に挟んで走査信号線ドライバYDRと向き合ったコンタクト配線CLと、画素電極PEを被覆すると共に有機発光層を含んだ活性層ALと、活性層ALを被覆すると共にコンタクト配線CLに接続された光透過性の共通電極CEとを備えている。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

一方の主面に表示領域とこれを取り囲んだ枠形状の周辺領域とが規定される絶縁基板と、前記表示領域と前記周辺領域のうち前記表示領域に隣接した部分とを被覆した有機平坦化層と、前記表示領域と前記有機平坦化層との間でマトリクス状に配列した複数の画素回路と、前記周辺領域上に形成されると共に少なくとも一部が前記有機平坦化層によって被覆された走査信号線ドライバと、前記有機平坦化層上であって前記表示領域に対応した位置で配列すると共に前記複数の画素回路にそれぞれ接続された複数の画素電極と、前記有機平坦化層を間に挟んで前記走査信号線ドライバと向き合ったコンタクト配線と、前記有機平坦化層のうち前記複数の画素電極間の領域に対応した部分を被覆した隔壁絶縁層と、前記複数の画素電極をそれぞれ被覆すると共に各々が有機発光層を含んだ複数の活性層と、前記複数の活性層及び前記隔壁絶縁層を被覆すると共に前記コンタクト配線に接続された光透過性の共通電極とを備えたアレイ基板と、

前記アレイ基板の前記共通電極側の主面と向き合った封止基板と、

前記アレイ基板と前記封止基板との間に介在すると共に前記有機平坦化層を取り囲んだ枠形状のシール層とを具備したことを特徴とする有機EL表示装置。

**【請求項 2】**

前記封止基板の前記アレイ基板と向き合った主面は第1部分とこれを取り囲んだ枠形状の第2部分とを含み、前記第1部分は前記第2部分に対して凹んでおり、前記絶縁基板の前記主面への前記第2部分の正射影は前記絶縁基板の前記主面への前記有機平坦化層の正射影を取り囲んでいることを特徴とする請求項1に記載の有機EL表示装置。

**【請求項 3】**

前記有機平坦化層にはこれを前記表示領域と向き合った第1部分と前記走査信号線ドライバと向き合った第2部分とに分割する溝が設けられており、前記第1部分の前記封止基板と向き合った主面及び前記溝の側壁を構成している端面は前記共通電極で被覆されていることを特徴とする請求項1又は2に記載の有機EL表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、有機エレクトロルミネッセンス(EL)表示装置に関する。

**【背景技術】****【0002】**

特許文献1には、アクティブマトリクス駆動方式を採用した上面発光型の有機EL表示装置が記載されている。この表示装置は、マトリクス状に配列した複数の有機EL素子を含んでいる。これら有機EL素子の上部電極は、互いに電気的に接続されており、共通電極を形成している。

**【0003】**

上面発光型の有機EL表示装置では、有機EL素子の上部電極は、光透過率が高いことが望まれる。しかしながら、一般に、光透過率が高い電極は、シート抵抗が大きい。そのため、アクティブマトリクス駆動方式を採用した上面発光型の有機EL表示装置では、共通電極電位の面内均一性が不十分となり易い。

**【0004】**

また、有機EL表示装置では、表示領域に対する周辺領域の面積比はより小さいことが望まれる。この狭額縫化の要求は、アクティブマトリクス駆動方式を採用した有機EL表示装置において、画素回路を形成した基板上に走査信号線ドライバを更に形成する場合に特に大きい。

**【特許文献1】特開2006-100186号公報****【発明の開示】****【発明が解決しようとする課題】****【0005】**

本発明の目的は、アクティブマトリクス駆動方式を採用した上面発光型の有機EL表示装置において狭額縫化と共通電極電位の面内均一性向上とを達成可能とする技術を提供することにある。

**【課題を解決するための手段】**

**【0006】**

本発明の一側面によると、一方の主面に表示領域とこれを取り囲んだ枠形状の周辺領域とが規定される絶縁基板と、前記表示領域と前記周辺領域のうち前記表示領域に隣接した部分とを被覆した有機平坦化層と、前記表示領域と前記有機平坦化層との間でマトリクス状に配列した複数の画素回路と、前記周辺領域上に形成されると共に少なくとも一部が前記有機平坦化層によって被覆された走査信号線ドライバと、前記有機平坦化層上であって前記表示領域に対応した位置で配列すると共に前記複数の画素回路にそれぞれ接続された複数の画素電極と、前記有機平坦化層を間に挟んで前記走査信号線ドライバと向き合ったコンタクト配線と、前記有機平坦化層のうち前記複数の画素電極間の領域に対応した部分を被覆した隔壁絶縁層と、前記複数の画素電極をそれぞれ被覆すると共に各々が有機発光層を含んだ複数の活性層と、前記複数の活性層及び前記隔壁絶縁層を被覆すると共に前記コンタクト配線に接続された光透過性の共通電極とを備えたアレイ基板と、前記アレイ基板の前記共通電極側の主面と向き合った封止基板と、前記アレイ基板と前記封止基板との間に介在すると共に前記有機平坦化層を取り囲んだ枠形状のシール層とを具備したことを特徴とする有機EL表示装置が提供される。

10

**【発明の効果】**

**【0007】**

本発明によると、アクティブマトリクス駆動方式を採用した上面発光型の有機EL表示装置において狭額縫化と共通電極電位の面内均一性向上とを達成可能とする技術が提供される。

20

**【発明を実施するための最良の形態】**

**【0008】**

以下、本発明の態様について、図面を参照しながら詳細に説明する。なお、各図において、同様又は類似した機能を発揮する構成要素には同一の参照符号を付し、重複する説明は省略する。

30

**【0009】**

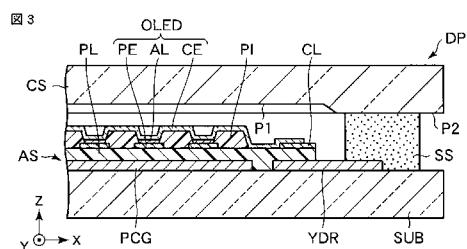

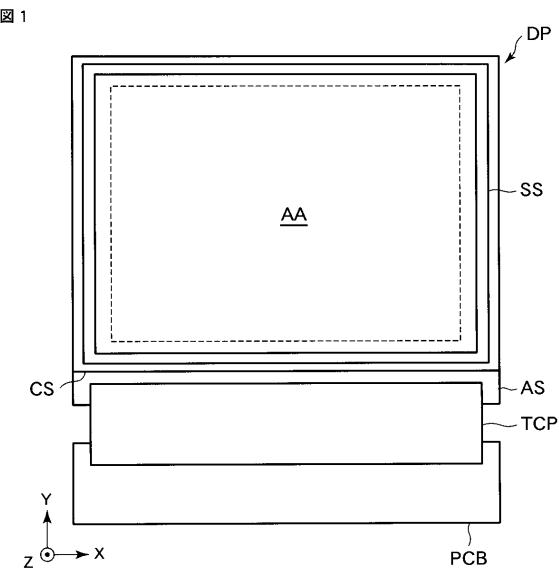

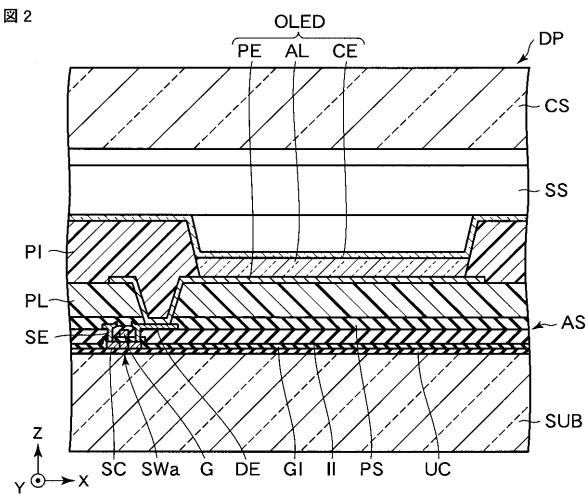

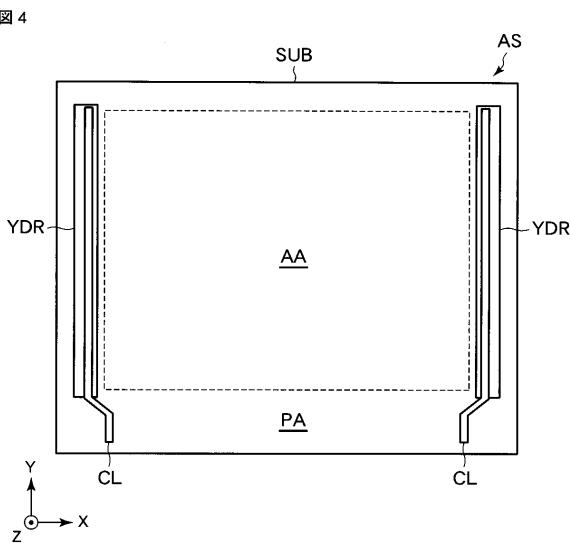

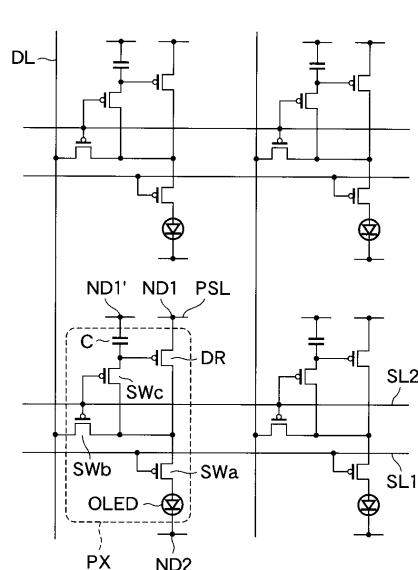

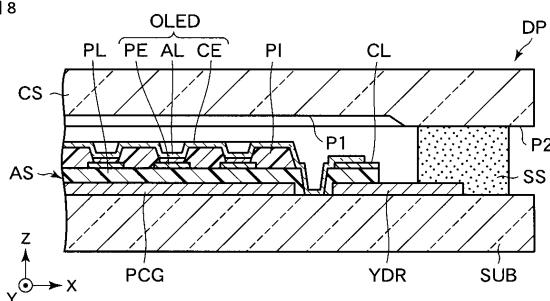

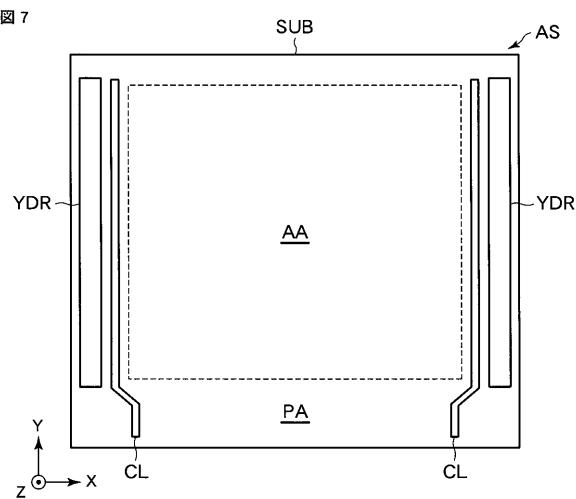

図1は、本発明の一態様に係る有機EL表示装置を概略的に示す平面図である。図2は、図1に示す有機EL表示装置が含んでいる表示パネルの一部を概略的に示す断面図である。図3は、図1に示す有機EL表示装置が含んでいる表示パネルの他の部分を概略的に示す断面図である。図4は、図2及び図3に示す表示パネルが含んでいるアレイ基板を概略的に示す平面図である。図5は、図4に示すアレイ基板の表示領域の等価回路図である。

**【0010】**

図1に示す表示装置は、アクティブマトリクス駆動方式を採用した上面発光型有機EL表示装置である。この表示装置は、表示パネルDPとテープキャリアパッケージTCPとプリント回路基板PCBとを含んでいる。

40

**【0011】**

表示パネルDPは、図1乃至図3に示すように、アレイ基板ASと封止基板CSとを含んでいる。アレイ基板ASと封止基板CSとは、向き合っており、中空体を形成している。具体的には、封止基板CSの中央部は、アレイ基板ASから離間している。封止基板CSの周縁部は、シール層SSを介して、アレイ基板ASの一方の主面に貼り付けられている。

**【0012】**

アレイ基板ASは、図2乃至図4に示す絶縁基板SUBを含んでいる。絶縁基板SUBは、例えばガラス基板である。

**【0013】**

50

なお、図1及び図4において、破線は、表示領域AAと、それを取り囲む周辺領域PAとの境界を示している。表示領域AA及び周辺領域PA上には、それぞれ、後述する画素PX及び走査信号線ドライバYDRが配置されている。

#### 【0014】

基板SUB上には、図2に示すアンダーコート層UCが形成されている。アンダーコート層UCは、例えば、基板SUB上に、シリコン窒化物層とシリコン酸化物層とをこの順に積層してなる。

#### 【0015】

アンダーコート層UC上には、例えば不純物を含有したポリシリコンからなる半導体パターンが形成されている。この半導体パターンの一部は、半導体層SCとして利用している。半導体層SCには、ソース及びドレインとして利用する不純物拡散領域が形成されている。また、この半導体パターンの他の一部は、後述するキャパシタの下部電極として利用している。

10

#### 【0016】

半導体パターンは、ゲート絶縁膜GIで被覆されている。ゲート絶縁膜GIは、例えばTEOS(tetraethyl orthosilicate)を用いて形成することができる。

#### 【0017】

ゲート絶縁膜GI上には、図5に示す走査信号線SL1及びSL2などの下層配線が形成されている。走査信号線SL1及びSL2は、画素PXの行に沿ったX方向に延びており、画素PXの列に沿ったY方向に交互に配列している。走査信号線SL1及びSL2は、例えばMOWからなる。なお、Z方向は、X方向とY方向とに垂直な方向である。

20

#### 【0018】

ゲート絶縁膜GI上には、キャパシタの上部電極が更に配置されている。これら上部電極は、上述した下部電極と向き合っている。上部電極は、例えばMOWからなり、走査信号線SL1及びSL2と同一の工程で形成することができる。

#### 【0019】

下層配線及び上部電極を含んだ第1導体パターンは、図2に示す半導体層SCと交差している。これらの交差部は、表示領域AA上では、図5に示す画素PXのトランジスタを構成し、周辺領域PA上では、図3及び図4に示す走査信号線ドライバYDRのトランジスタを構成している。

30

#### 【0020】

具体的には、走査信号線SL1と半導体層SCとの交差部は、図2及び図5に示すスイッチングトランジスタSWaを構成している。走査信号線SL2と半導体層SCとの交差部は、図5に示すスイッチングトランジスタSWb及びSWcを構成している。また、先に説明した下部電極と上部電極とそれらの間に介在した絶縁膜GIとは、図5に示すキャパシタCを構成している。上部電極は、キャパシタCからZ方向に垂直な方向に突き出た突出部を含んでおり、この突出部と半導体層SCとは交差している。この交差部は、図5に示す駆動トランジスタDRを構成している。

#### 【0021】

なお、この例では、画素PX及び走査信号線ドライバYDRが含んでいるトランジスタは、トップゲート型のpチャネル薄膜トランジスタである。また、図2に参照符号Gで示す部分は、スイッチングトランジスタSWaのゲートである。

40

#### 【0022】

ゲート絶縁膜GI及び第1導体パターンは、図2に示す層間絶縁膜IIで被覆されている。層間絶縁膜IIは、例えばプラズマCVD法により堆積させたシリコン酸化物からなる。

#### 【0023】

層間絶縁膜II上には、図5に示す映像信号線DL及び電源線PSLなどの上層配線が形成されている。映像信号線DLは、Y方向に延びており、X方向に配列している。電源線PSLは、例えば、Y方向に延びており、X方向に配列している。

50

## 【0024】

層間絶縁膜 I I 上には、図 2 に示すソース電極 S E 及びドレイン電極 D E が更に形成されている。ソース電極 S E 及びドレイン電極 D E は、画素 P X の各々において素子同士を接続している。

## 【0025】

映像信号線 D L と電源線 P S L とソース電極 S E とドレイン電極 D E とを含む第 2 導体パターンは、例えば、M o / A l / M o の三層構造を有している。これらは、同一工程で形成可能である。

## 【0026】

第 2 導体パターンは、パッシベーション膜 P S で被覆されている。パッシベーション膜 P S には、スイッチングトランジスタ S W a のドレインに接続されたドレイン電極 D E に対応した位置などに貫通孔が形成されている。パッシベーション膜 P S は、例えばシリコン窒化物からなる。

10

## 【0027】

パッシベーション膜 P S は、図 2 及び図 3 に示す有機平坦化層 P L で被覆されている。具体的には、平坦化層 P L は、パッシベーション膜 P S のうち、表示領域 A A 上に位置した部分と、これに隣接した部分とを被覆している。平坦化層 P L の各辺は、基板 S U B の辺から離れて位置している。また、平坦化層 P L は、走査信号線 ドライバ Y D R のうち、表示領域 A A に近い部分のみを被覆し、表示領域 A A から遠い部分は被覆していない。平坦化層 P L には、パッシベーション膜 P S の貫通孔と連続した貫通孔が設けられている。

20

## 【0028】

平坦化層 P L 上には、画素電極 P E が、画素 P X に対応して配置されている。画素電極 P E は、表示領域 A A 上で配列している。これら画素電極 P E は、光反射性の背面電極である。本態様では、画素電極 P E は陽極である。各画素電極 P E は、平坦化層 P L 及びパッシベーション膜 P S に設けた貫通孔を介してドレイン電極 D E に接続されており、このドレイン電極はスイッチングトランジスタ S W a のドレインに接続されている。

## 【0029】

画素電極 P E は、単層構造を有していてもよく、多層構造を有していてもよい。例えば、画素電極 P E として、金属層、透明導電体層、又は金属層と透明導電体層との積層体を使用することができる。金属層の材料としては、例えば、アルミニウム、銀又はそれらの合金を使用することができます。透明導電体層の材料としては、例えば、インジウム錫酸化物などの透明導電性酸化物を使用することができます。なお、画素電極 P E として透明導電体層を使用する場合、典型的には、画素電極 P E の背面側に反射層を設置する。また、画素電極 P E として金属層と透明導電体層との積層体を使用する場合、金属層は、透明導電体層と平坦化層 P L との間に設置する。

30

## 【0030】

図 4 に示すように、平坦化層 P L 上には、一対のコンタクト配線 C L が更に配置されている。これらコンタクト配線 C L は、周辺領域 P A 上に位置している。コンタクト配線 C L は、図 3 に示すように、平坦化層 P L を間に挟んで走査信号線 ドライバ Y D R と向き合っている。コンタクト配線 C L は、走査信号線 ドライバ Y D R から電気的に絶縁されている。各コンタクト配線 C L は、例えば、図 1 に示すテープキャリアパッケージ T C P と電気的に接続する。

40

## 【0031】

コンタクト配線 C L は、画素電極 P E が金属又は合金からなる単層構造を有している場合には、例えば、画素電極 P E と同一の材料からなる。コンタクト配線 C L は、画素電極 P E が透明導電体からなる単層構造を有している場合には、例えば、画素電極 P E と同一の材料からなるか、又は、画素電極 P E の背面側に設置する反射層と同一の材料からなる。画素電極 P E が多層構造を有している場合には、コンタクト配線 C L は、例えば、画素電極 P E と同一の構成を採用するか、又は、画素電極 P E の一部と同一の構成を採用する。

50

## 【0032】

図2に示すパッセーション膜PS上には、更に、絶縁樹脂層である隔壁絶縁層PIが形成されている。隔壁絶縁層PIには、図2及び図3に示すように、画素電極PEに対応した位置に開口が設けられている。これら開口は、例えば、画素電極PEに対応して配列した貫通孔であるか、或いは、画素電極PEが形成する列に対応して配列したスリットである。ここでは、一例として、先の開口は、画素電極PEに対応して配列した貫通孔であることとする。隔壁絶縁層PIは、例えば、フォトリソグラフィ技術を用いて形成することができる。

## 【0033】

各画素電極PE上には、活性層ALが形成されている。活性層ALが含んでいる各層は、画素PXに対応してパターニングされていてもよい。或いは、活性層ALが含んでいる各層は、画素PX間で繋がっていてもよい。

10

## 【0034】

活性層ALは、有機発光層を含んでいる。活性層ALは、発光層に加え、正孔輸送層及び電子輸送層の少なくとも一方を更に含むことができる。

## 【0035】

隔壁絶縁層PI及び活性層ALは、共通電極CEで被覆されている。共通電極CEは、可視光透過性の前面電極である。また、本態様では、共通電極CEは陰極である。

20

## 【0036】

共通電極CEは、図3に示すように、コンタクト配線CLと、平坦化層PLのうちコンタクト配線CLと隔壁絶縁層PIとの間の領域に対応した部分とを更に被覆している。即ち、共通電極CEは、コンタクト配線CLを介して、例えばテープキャリアパッケージTCPと電気的に接続され得る。

## 【0037】

各々の有機EL素子OLEDは、図2及び図3に示すように、画素電極PEと、活性層ALと、共通電極CEとを含んでいる。なお、発光層と正孔輸送層との間には、電子プロッキング層を挿入してもよい。発光層と電子輸送層との間には、正孔プロッキング層を挿入してもよい。また、正孔輸送層と陽極である画素電極PEとの間には、正孔注入層を挿入してもよい。電子輸送層と陰極である共通電極CEとの間には、電子注入層を挿入してもよい。

30

## 【0038】

画素PXの各々は、図5に示すように、駆動トランジスタDRと、スイッチングトランジスタSWa乃至SWcと、有機EL素子OLEDと、キャパシタCとを含んでいる。上記の通り、この例では、駆動トランジスタDR及びスイッチングトランジスタSWa乃至SWcはpチャネル薄膜トランジスタである。

## 【0039】

駆動トランジスタDRと、スイッチングトランジスタSWa乃至SWcと、キャパシタCとは、画素回路を構成している。図3に示すPCGは、画素回路群である。

## 【0040】

図5に示すように、駆動トランジスタDRとスイッチングトランジスタSWaと有機EL素子OLEDとは、第1電源端子ND1と第2電源端子ND2との間で、この順に直列に接続されている。この例では、電源端子ND1は高電位電源端子であり、電源端子ND2は低電位電源端子である。

40

## 【0041】

スイッチングトランジスタSWaのゲートは、走査信号線SL1に接続されている。スイッチングトランジスタSWbは、映像信号線DLと駆動トランジスタDRのドレインとの間に接続されており、そのゲートは走査信号線SL2に接続されている。スイッチングトランジスタSWcは、駆動トランジスタDRのドレインとゲートとの間に接続されており、そのゲートは走査信号線SL2に接続されている。

## 【0042】

50

キャパシタ C は、駆動トランジスタ D R のゲートと定電位端子 N D 1' との間に接続されている。この例では、定電位端子 N D 1' は、電源端子 N D 1 に接続されている。

#### 【 0 0 4 3 】

封止基板 C S は、図 1 乃至図 3 に示すように、アレイ基板 A S と向き合っている。具体的には、封止基板 C S は、有機 E L 素子 O L E D を間に挟んで基板 S U B と向き合っている。封止基板 C S は、例えばガラス基板である。

#### 【 0 0 4 4 】

封止基板 C S のアレイ基板 A S と向き合った主面は、図 3 に示すように、第 1 部分 P 1 とこれを取り囲んだ第 2 部分 P 2 を含んでいる。第 1 部分 P 1 は、第 2 部分 P 2 に対して凹んでいる。絶縁基板 S U B の封止基板 C S との対向面への第 2 部分 P 2 の正射影は、この対向面への平坦化層 P L の正射影を取り囲んでいる。10

#### 【 0 0 4 5 】

シール層 S S は、図 3 に示すように、アレイ基板 A S と封止基板 C S との間に介在している。シール層 S S は、周辺領域 P A 上に位置しており、枠形状を有している。シール層 S S の材料としては、例えば、接着剤を使用することができる。

#### 【 0 0 4 6 】

アレイ基板 A S と封止基板 C S とシール層 S S とは、気密な中空体を形成している。この空間は、例えば、真空とするか又は不活性ガスで満たす。

#### 【 0 0 4 7 】

走査信号線ドライバ Y D R は、図 3 及び図 4 に示すように、アレイ基板 A S に搭載されている。走査信号線ドライバ Y D R は、走査信号線 S L 1 及び S L 2 にそれぞれ第 1 及び第 2 走査信号を電圧信号として出力する。20

#### 【 0 0 4 8 】

図 1 に示すテープキャリアパッケージ T C P は、フレキシブルプリント回路基板と、これに搭載された映像信号線ドライバとを含んでいる。映像信号線ドライバは、フレキシブルプリント回路基板に搭載する代わりに、アレイ基板 A S に搭載してもよい。

#### 【 0 0 4 9 】

フレキシブルプリント回路基板の配線は、アレイ基板 A S 及びプリント回路基板 P C B の外部接続端子と接続されている。映像信号線ドライバには、フレキシブルプリント回路基板の配線を介して、図 5 に示す映像信号線 D L が接続されている。この例では、映像信号線ドライバには、電源線 P S L が更に接続されている。映像信号線ドライバは、映像信号線 D L に映像信号を電流信号として出力すると共に、電源線 P S L に電源電圧を供給する。30

#### 【 0 0 5 0 】

図 1 に示すプリント回路基板は、コントローラ及び電源回路などを搭載している。これらが出力する信号及び電力の一部は、プリント回路基板及びフレキシブルプリント回路基板の配線を介して、映像信号線ドライバに供給される。コントローラ及び電源回路などが出力する信号及び電力の他の一部は、プリント回路基板及びフレキシブルプリント回路基板などの配線を介して、図 3 及び図 4 に示す走査信号線ドライバ Y D R 及びコンタクト配線 C L に供給される。40

#### 【 0 0 5 1 】

この有機 E L 表示装置で画像を表示する場合、例えば、画素 P X を行毎に順次選択する。或る行を選択している選択期間では、その選択している行の画素 P X に対して書き動作を行う。そして、非選択期間では、その非選択中の行の画素 P X で表示動作を行う。

#### 【 0 0 5 2 】

具体的には、或る行を選択する選択期間では、まず、走査信号線ドライバ Y D R から、その行が含む画素 P X が接続された走査信号線 S L 1 に、スイッチングトランジスタ S W a を開く（非導通状態とする）走査信号を電圧信号として出力する。続いて、走査信号線ドライバ Y D R から、先の画素 P X が接続された走査信号線 S L 2 に、スイッチングトランジスタ S W b 及び S W c を閉じる（導通状態とする）走査信号を電圧信号として出力す50

る。この状態で、映像信号線ドライバYDRから、映像信号線DLに、映像信号を電流信号（書込電流） $I_{sig}$ として出力し、駆動トランジスタDRのゲート-ソース間電圧 $V_{gs}$ を、先の映像信号 $I_{sig}$ に対応した大きさに設定する。その後、走査信号線ドライバYDRから、先の画素PXが接続された走査信号線SL2に、スイッチングトランジスタSWb及びSWcを開く走査信号を電圧信号として出力する。続いて、走査信号線ドライバYDRから、先の画素PXが接続された走査信号線SL1に、スイッチングトランジスタSWaを閉じる走査信号を電圧信号として出力する。これにより、選択期間を終了する。

#### 【0053】

選択期間に続く非選択期間では、走査信号線ドライバYDRから、先の画素PXが接続された走査信号線SL1に、スイッチングトランジスタSWaを閉じる走査信号を電圧信号として出力する。スイッチングトランジスタSWaは閉じたままとし、スイッチングトランジスタSWb及びSWcは開いたままとする。非選択期間では、有機EL素子OLEDには、駆動トランジスタDRのゲート-ソース間電圧 $V_{gs}$ に対応した大きさの駆動電流 $I_{drv}$ が流れる。有機EL素子OLEDは、駆動電流 $I_{drv}$ の大きさに対応した輝度で発光する。

10

#### 【0054】

この有機EL表示装置では、図3及び図4に示すコンタクト配線CLを介して、共通電極CEに電力を供給する。コンタクト配線CLは、図1及び図4に示す周辺領域PA上に配置されているので、コンタクト配線CLを表示領域AA上に配置した場合と比較して幅広に形成することができる。例えば、周辺領域PA上には、幅が数100μmのコンタクト配線CLを形成することができる。それゆえ、コンタクト配線CLを周辺領域PA上に配置した場合、コンタクト配線CLを表示領域AA上に配置した場合と比較して、コンタクト配線CLの電気抵抗に起因した電圧降下を小さくすることができる。従って、この構造を採用すると、共通電極CEの電位の面内均一性が不十分となるのを防止できる。

20

#### 【0055】

また、この有機EL表示装置では、平坦化層PL上にコンタクト配線CLを配置している。以下に説明するように、この構造を採用した場合、平坦化層PLと絶縁基板SUBとの間にコンタクト配線CLを配置した場合と比較して、表示領域AAに対する周辺領域PAの面積比をより小さくすることができる。

30

#### 【0056】

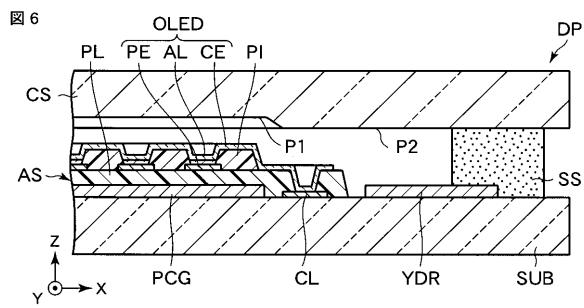

図6は、比較例に係る表示パネルを概略的に示す断面図である。図7は、図6に示す表示パネルが含んでいるアレイ基板を概略的に示す平面図である。

#### 【0057】

この表示パネルDPは、以下の構成を採用したこと以外は、図1乃至図5を参照しながら説明した表示パネルDPとほぼ同様である。即ち、この表示パネルDPでは、図6に示すように、コンタクト配線CLを平坦化層PLと絶縁基板SUBとの間に配置している。そして、コンタクト配線CLが画素回路群PCG又は走査信号線ドライバYDRと電気的に接続されるのを防ぐため、図6に示すように、各コンタクト配線CLを、画素回路群PCG及び走査信号線ドライバYDRから十分に離間させている。換言すれば、図7に示すように、各コンタクト配線CLを、表示領域AA及び走査信号線ドライバYDRから十分に離間させている。そして、この表示パネルDPは、共通電極CEとコンタクト配線CLとの間に平坦化層PLが介在しているので、平坦化層PLに貫通孔を設け、これら貫通孔を介して共通電極CEをコンタクト配線CLに接続している。

40

#### 【0058】

このように、図6に示す表示パネルDPでは、コンタクト配線CLは、画素回路群PCG及び走査信号線ドライバYDRとX方向に隣り合っている。他方、図3に示す表示パネルDPでは、コンタクト配線CLは、走査信号線ドライバYDRとはZ方向に隣り合っている。そして、それらが電気的に接続されるのを確実に防止するためには、それらを互いから例えば数100μm以上離間させることが望ましい。それゆえ、図4及び図7の対比から明らかなように、図1乃至図5を参照しながら説明した構造を採用すると、図6及び

50

図7を参照しながら説明した構造を採用した場合と比較して、X方向に関する表示領域AAから絶縁基板SUBの縁までの距離をより短くすること、例えば400μm乃至500μm程度短くすることができる。即ち、図1乃至図5を参照しながら説明した構造を採用すると、図6及び図7を参照しながら説明した構造を採用した場合と比較して、表示領域AAに対する周辺領域PAの面積比をより小さくすることができる。

#### 【0059】

また、上記の通り、図1乃至図5を参照しながら説明した有機EL表示装置では、図3に示すように、封止基板CSのアレイ基板ASと向き合った主面は、第1部分P1とこれを取り囲んだ第2部分P2とを含んでいる。第1部分P1は、第2部分P2に対して凹んでいる。絶縁基板SUBの封止基板CSとの対向面への第2部分P2の正射影は、この対向面への平坦化層PLの正射影を取り囲んでいる。この構造を採用すると、大気中の水分に起因した有機EL素子OLEDの劣化を生じ難い。これについて、図3と図6とを対比しながら説明する。

10

#### 【0060】

図3及び図6に示す表示パネルDPでは、大気中の水分が、シール層SSを介して、アレイ基板ASと封止基板CSとシール層SSとに囲まれた空間内に侵入する可能性がある。活性層ALなどに水分が侵入すると、有機EL素子OLEDが劣化する。

#### 【0061】

平坦化層PLは、水分を取り込み易い。そして、平坦化層PLに取り込まれた水分は、平坦化層PL内で速やかに拡散する。従って、有機EL素子OLEDの水分による劣化を抑制するには、平坦化層PLへの水分の侵入を抑制することが効果的である。

20

#### 【0062】

図6に示す表示パネルDPでは、図1乃至図5を参照しながら説明した表示パネルDPと同様に、封止基板CSのアレイ基板ASと向き合った主面は、第1部分P1とこれを取り囲んだ第2部分P2とを含んでいる。第1部分P1は、第2部分P2に対して凹んでいる。但し、図3の表示パネルDPでは、図1乃至図5を参照しながら説明した表示パネルDPとは異なり、絶縁基板SUBの封止基板CSとの対向面への第2部分P2の正射影は、この対向面への平坦化層PLの正射影を取り囲んでいない。

#### 【0063】

図6の構造は、平坦化層PLの縁から封止基板CSまでの距離が短い。そのため、この構造を採用した場合、シール層SSを介してアレイ基板ASと封止基板CSとシール層SSとに囲まれた空間内に侵入した水分は、共通電極と封止基板CSとの間の空間内に速やかに拡散せずに、長時間に亘って平坦化層PLの縁近傍に滞留する。その結果、平坦化層PLに比較的多量の水分が侵入し、有機EL素子OLEDが速やかに劣化する。

30

#### 【0064】

これに対し、図3の構造では、平坦化層PLの縁から封止基板CSまでの距離が比較的長い。そのため、この構造を採用した場合、シール層SSを介してアレイ基板ASと封止基板CSとシール層SSとに囲まれた空間内に侵入した水分は、共通電極と封止基板CSとの間の空間内に速やかに拡散する。従って、図1乃至図5を参照しながら説明した有機EL表示装置は、大気中の水分に起因した有機EL素子OLEDの劣化を生じ難い。

40

#### 【0065】

この有機EL表示装置には、様々な変形が可能である。

例えば、有機EL表示装置に映像信号として電流信号を書き込む構成を採用する代わりに、有機EL表示装置に映像信号として電圧信号を書き込む構成を採用してもよい。また、表示パネルDPに、図8に示す構造を採用してもよい。

#### 【0066】

図8は、図3に示す表示パネルの一変形例を概略的に示す断面図である。

図8に示す表示パネルDPでは、平坦化層PLに、これを表示領域AA（又は画素回路群PCG）と向き合った第1部分と走査信号線ドライバYDRと向き合った第2部分とに分割する溝が設けられている。第1部分の封止基板CSと向き合った主面及び溝の側壁を

50

構成している端面は、共通電極 C S で被覆されている。これ以外は、図 8 に示す表示パネル D P は、図 1 乃至図 5 を参照しながら説明した表示パネル D P と同様である。

#### 【0067】

この構造では、上記の通り、共通電極 C S が溝の側壁を被覆しているので、第 1 部分への水分の侵入が生じ難い。従って、図 8 に示す構造を採用すると、図 3 に示す構造を採用した場合と比較して、大気中の水分に起因した有機 E L 素子 O L E D の劣化をより生じ難くすることができる。

#### 【図面の簡単な説明】

#### 【0068】

【図 1】本発明の一態様に係る有機 E L 表示装置を概略的に示す平面図。

10

【図 2】図 1 に示す有機 E L 表示装置が含んでいる表示パネルの一部を概略的に示す断面図。

【図 3】図 1 に示す有機 E L 表示装置が含んでいる表示パネルの他の部分を概略的に示す断面図。

【図 4】図 2 及び図 3 に示す表示パネルが含んでいるアレイ基板を概略的に示す平面図。

【図 5】図 4 に示すアレイ基板の表示領域の等価回路図。

【図 6】比較例に係る表示パネルを概略的に示す断面図。

【図 7】図 6 に示す表示パネルが含んでいるアレイ基板を概略的に示す平面図。

【図 8】図 3 に示す表示パネルの一変形例を概略的に示す断面図。

20

#### 【符号の説明】

#### 【0069】

A A ... 表示領域、 A L ... 活性層、 A S ... アレイ基板、 C ... キャパシタ、 C E ... 共通電極、 C L ... コンタクト配線、 C S ... 封止基板、 D E ... ドレイン電極、 D L ... 映像信号線、 D P ... 表示パネル、 D R ... 駆動トランジスタ、 G ... ゲート、 G I ... 絶縁膜、 I I ... 層間絶縁膜、 N D 1 ... 電源端子、 N D 1 ' ... 定電位端子、 N D 2 ... 電源端子、 O L E D ... 有機 E L 素子、 P 1 ... 第 1 部分、 P 2 ... 第 2 部分、 P A ... 周辺領域、 P C B ... プリント回路基板、 P C G ... 画素回路群、 P E ... 画素電極、 P I ... 隔壁絶縁層、 P L ... 有機平坦化層、 P S ... パッシベーション膜、 P S L ... 電源線、 P X ... 画素、 S C ... 半導体層、 S E ... ソース電極、 S L 1 ... 走査信号線、 S L 2 ... 走査信号線、 S S ... シール層、 S U B ... 絶縁基板、 S W a ... スイッチングトランジスタ、 S W b ... スイッチングトランジスタ、 S W c ... スイッチングトランジスタ、 T C P ... テープキャリアパッケージ、 U C ... アンダーコート層、 Y D R ... 走査信号線ドライバ。

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図7】

---

フロントページの続き

(74)代理人 100109830

弁理士 福原 淑弘

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 小俣 一由

東京都港区港南四丁目 1 番 8 号 東芝松下ディスプレイテクノロジー株式会社内

F ターム(参考) 3K107 AA01 BB01 CC23 CC43 DD03 DD90 EE03 EE42 EE55

|                |                                                                                                    |         |            |

|----------------|----------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机EL表示装置                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP2009059531A</a>                                                                      | 公开(公告)日 | 2009-03-19 |

| 申请号            | JP2007224491                                                                                       | 申请日     | 2007-08-30 |

| [标]申请(专利权)人(译) | 东芝松下显示技术股份有限公司                                                                                     |         |            |

| 申请(专利权)人(译)    | 东芝松下显示技术有限公司                                                                                       |         |            |

| [标]发明人         | 小俣一由                                                                                               |         |            |

| 发明人            | 小俣 一由                                                                                              |         |            |

| IPC分类号         | H05B33/04 H01L51/50                                                                                |         |            |

| FI分类号          | H05B33/04 H05B33/14.A                                                                              |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC23 3K107/CC43 3K107/DD03 3K107/DD90 3K107/EE03 3K107/EE42 3K107/EE55 |         |            |

| 代理人(译)         | 河野 哲<br>中村诚                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                          |         |            |

### 摘要(译)

要解决的问题：在采用有源矩阵驱动方法的顶部发射有机EL显示装置中，为了实现窄边框并提高公共电极电位的面内均匀性。阵列基板AS是有机平坦化层，其覆盖绝缘基板SUB，该绝缘基板SUB在一个主表面上限定了显示区域和外围区域，并且该显示区域和外围区域的一部分与该显示区域相邻。PL，扫描信号线驱动器YDR形成在外围区域上并且至少一部分被平坦化层PL覆盖，并且像素电极PE布置在平坦化层PL上与显示区域相对应的位置处。并且，与扫描信号线驱动器YDR相对的接触布线CL隔着平坦化层PL而与像素电极PE和包括有机发光层的有源层AL接触，并且有源层AL与接触电极CL接触。设置有与配线CL连接的透光性公共电极CE。[选择图]图3